# CHIPS

Subu Iyer (s.s.iyer@ucla.edu)

UCLA ENGINEERING

Henry Samueli School of

Engineering and Applied Science

Birthplace of the Internet

# Three questions

What are we trying to do?

Why are we doing this?

How are we planning to do this?

# What are we trying to do?

Develop an "app-like" environment for Hardware that can

- Cut the time to market by 5-10X

- Cut the NRE cost by 10-20X

- Allow extreme heterogeneity including extensions to cyber-physical systems

- Develop a sophisticated manufacturing workforce

# Why now?

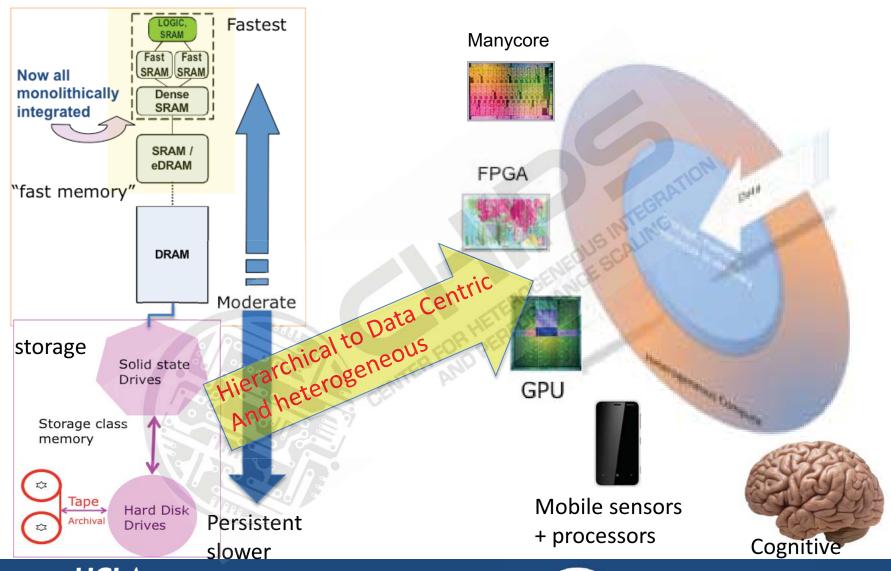

- The application space is transforming

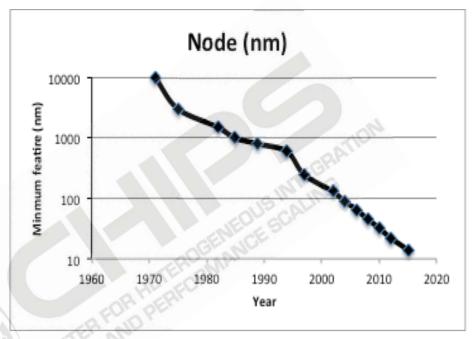

- CMOS scaling is saturating

- Systems are getting more heterogeneous and complex

- Holistic system Integration is the next frontier of Moore's law

### Computing is transforming

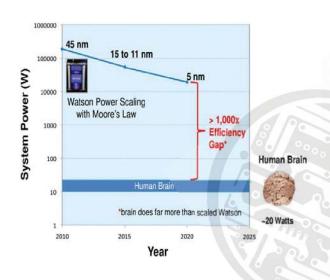

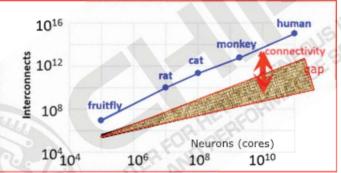

# "cognitive" computing – brawn Vs. brain

It is unlikely that we can just scale our selves out of the huge gap (10<sup>3</sup> to 10<sup>4</sup>) in power and interconnect density

### The Power of System on a Chip (SoC)

**1964 - Transistor**SLT module

6 transistors, 4 resistors

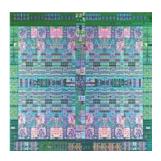

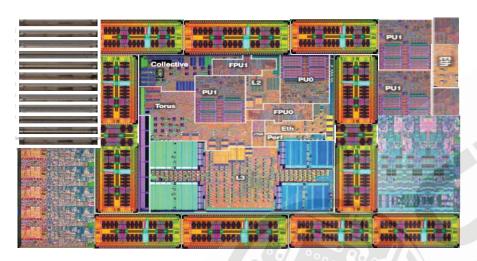

2014 – POWER8 Processor

22nm SOI eDRAM technology, 650mm<sup>2</sup>

12 cores and 96MB of on-chip memory

4.2 billion transistors

Courtesy IBM

#### Transistor scaling has made this possible

But as SoCs have gotten more complex

- NRE costs have skyrocketed

- Time to market has become huge

- Manufacturing costs have grown

- and yields have plummeted

#### What would Yogi Say?

1925-2015

# So, if you can't scale the chip

### you should try to scale something else!

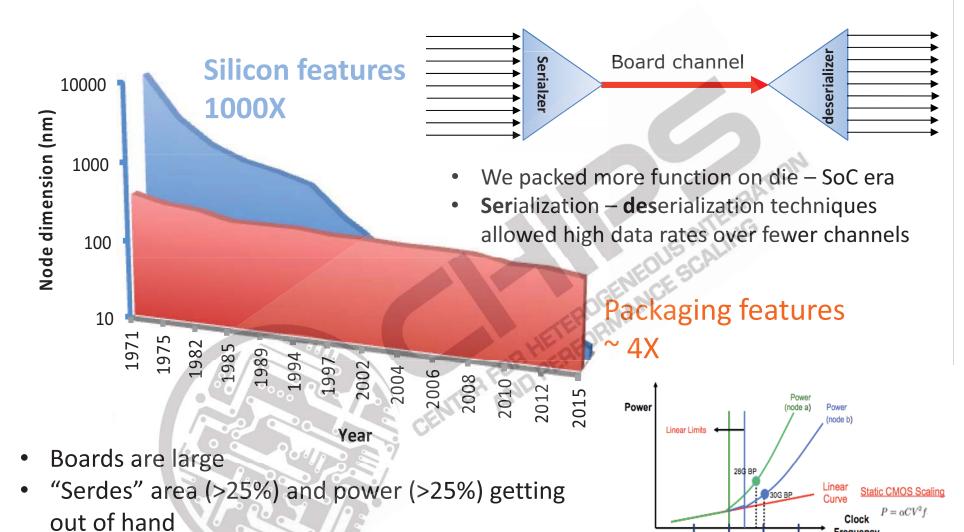

### Package/Board Features have scaled modestly

UCLA ENGINEERING

Henry Samueli School of

Engineering and Applied Science

Birthplace of the Internet

(GHz)

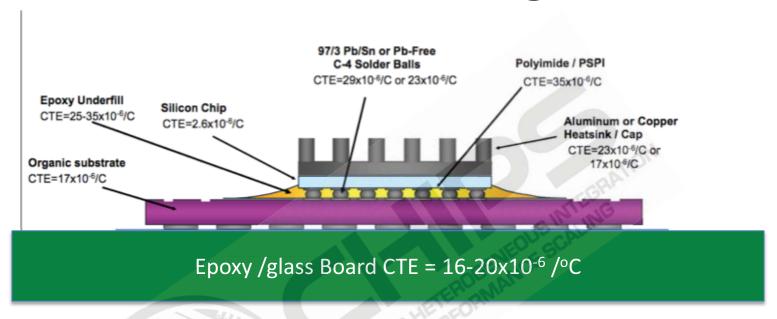

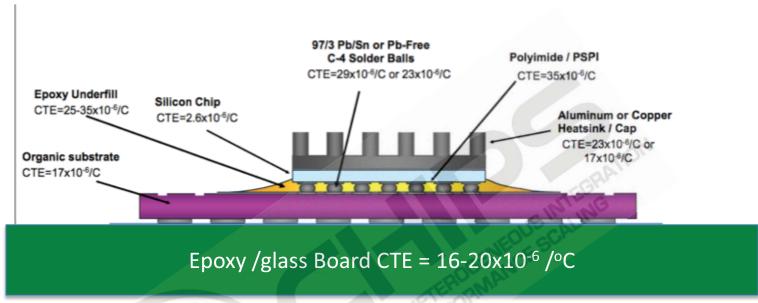

# Do we need Packages?

### Packages are supposed to:

- Protect the chip mechanically and thermally

- Connect the chip electrically to other chips

- Allows mission mode testing of the chip

# Do we need Packages ? - No!

#### Packages are supposed to:

- Protect the chip mechanically and thermally (not really)

- Connect the chip electrically to other chips (by progressive fan-out)

- Allows mission mode testing of the chip (this is true)

We can scale the package by getting rid of it

And mount the bare die directly on the board

# Shrinking the board

Without question the smallest board is a single large die with all the system functions

on it

Amdahl eventually declared the idea would only work with a 99.99% yield, which wouldn't happen for 100 years.

Hence the quest for the largest Yieldable Unit

the SoC (reticle size today will yield at 3 15%)

Gene Ahmdahl @Trilogy Systems

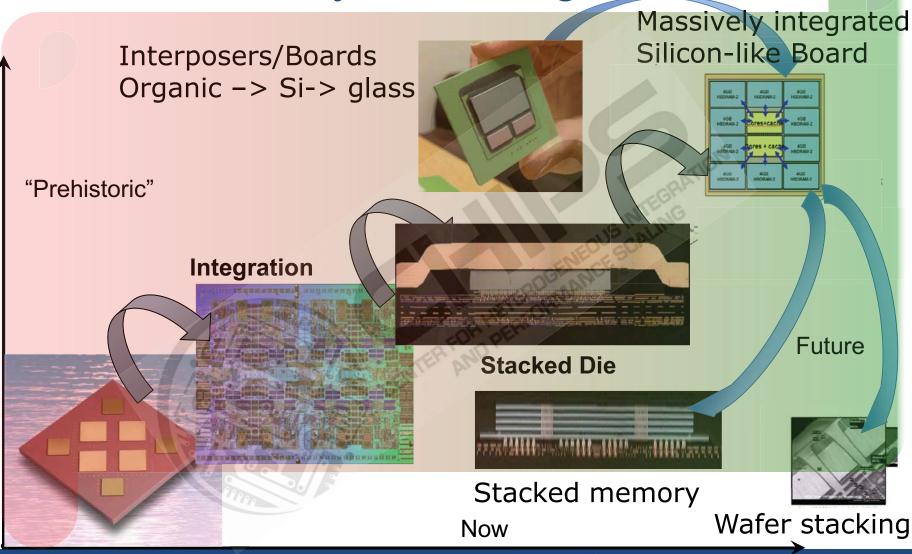

**Evolution Of System Integration**

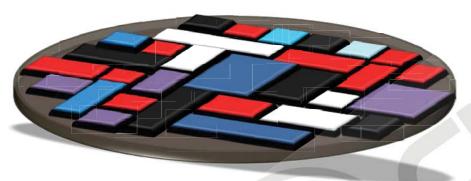

# Mega SolFs by re-integration on an Interconnect Fabric

The "right" interconnect fabric

- Mechanically robust (flat, stiff, tough...)

- Capable of fine wiring, fine pitch interconnects

- Thermally conductive

- Can have active and passive built-in components

Silicon Fits the Bill in many cases

### Challenges:

- Warpage

- Topography

- Assembly /Thru'put

- Thermal

>100 µm pitch Mass reflow

solder | cu† 100μm >pitch > 40 μm Mass re-flow+TCB Full contact – TCB

Proximate 2-10μm • Inductive

Capacitive

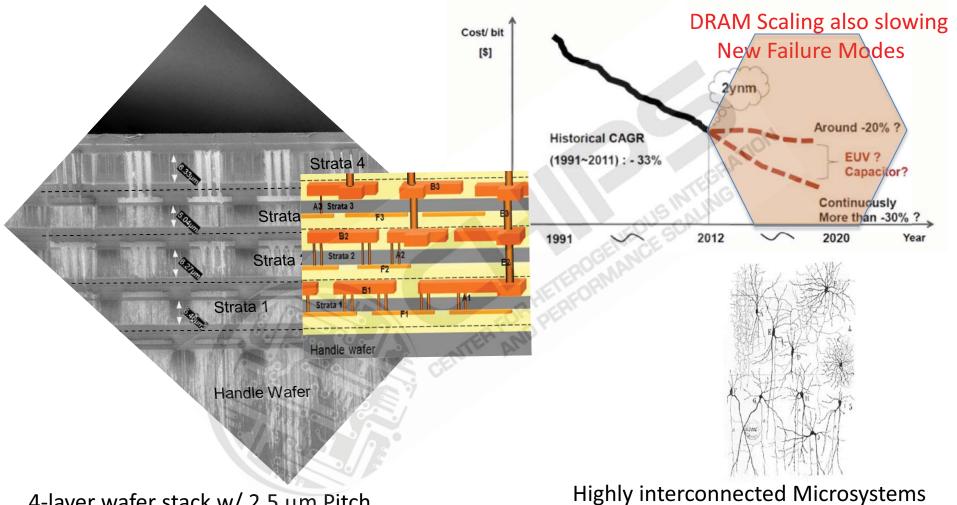

# Wafer to Wafer integration at tight pitch

4-layer wafer stack w/ 2.5 μm Pitch

# **CHIPS Framework**

**Tier 1 Equipment Partners**

New Tool Concepts Tool Development Scale-Up

Heterogeneous Systems

Approximate Computing

Cognitive Computing

Fault Tolerance

Supply chain Integrity

Security

Memory Subsystems

Processing in Memory DFT

**Applications & Architecture**

#### Integration

A processing facility for Interconnect Fabric (IF) & assembly

#### Silicon processing

- •Glass

- •Flexible substrates

- Additive manufacturing

- Thermal compression bonding

- Wafer thinning

- •Wafer-wafer integration

#### **Materials**

Fine Pitch Interconnect

Substrate Materials

Warpage, Stress Flexible

Materials

Thermal solutions

Materials for Additive Mfg.

Reliability

#### **Design Infrastructure**

Network on Board

Thermo-Mechanical

Electrical

Tools

Partitioning

DFT

Active IF Design

**Tier 1 Foundry Partners**

Si, Compound Semis, MEMS, and OSATs

#### **Devices/Components**

Novel switches New memory MEMS Sensors Passives, antennae Medical devices

UCLA ENGINEERING

Henry Samueli School of

Engineering and Applied Science

### Test Beds

"Mega SolF\*"

(~ wafer dimensions)

**Desktop Datacenter**

$\mu$ -Yodabot

autonomous origami  $\mu$ -Yodabot that thinks, walks, flies, swims and does stuff.....

\*System on Interconnect Fabric

# Chip Assembly

# Summary

- We are in the midst of a significant hardware transformation

- Semiconductor Scaling is saturating

- Computing models are changing

- Systems are getting more heterogeneous

- SoCs design costs and Times-to-Market huge

- CHIPS will drive a much more holistic Moore's Law

- We can't do it alone, we have to do it together

- Industry Partners

- University Partners: GINTI (Tohuku U),

Binghamton U, Georgia Tech,

- Government Agencies