19 日本国特許庁(JP) 10 特許出願公開

## <sup>10</sup> 公 開 特 許 公 報 (A) 昭62-34398

| ⑤Int.Cl.⁴    | 識別記号 | 庁内整理番号  | 43公開 | 昭和62年(1987)2月14日 |

|--------------|------|---------|------|------------------|

| G 11 C 17/00 | 101  | 6549-5B |      |                  |

審査請求 未請求 発明の数 1 (全3頁)

19

3

発明の名称

不揮発性メモリー

②特 願 昭60-175105 ②出 願 昭60(1985)8月8日

| 包発 | 明 | 者 | 北村    | 嘉 成  | 東京都港区芝5丁目33番1号 | 日本電気株式会社内 |

|----|---|---|-------|------|----------------|-----------|

| 创出 | 願 | 人 | 日本電気  | 株式会社 | 東京都港区芝5丁目33番1号 |           |

| 团代 | 理 | 人 | 弁理士 内 | 原 晋  |                |           |

明細書

- 2. 特許請求の範囲

書込によって特性が連続的に変化する半導体不 揮発性記憶業子と、書込モードと読出モードとを 一定時間毎に交互に切換える回路と、複数ビット のディジタル信号をアナログ信号に変換するD/A 変換回路とメモリーセルからの読出レベルを、前 記アナログ信号のレベルと比較し、この結果によ って書込動作を終了させる回路と、読出されたア ナログ信号レベルをディジタル信号に変換するA / D 変換回路とを含むことを特徴とする不揮発性 メモリー。

発明の詳細な説明

(産業上の利用分野)

本発明は不揮発性メモリーに関する。

〔従来の技術〕

従来、不揮発性メモリーとして、フローティン グゲートMOSやMNOSを記憶素子としたもの が実用化されているが、記憶素子1個当り1ビッ トの情報を記憶するだけであった。

〔発明が解決しようとする問題点〕

上述した従来の不揮発性メモリーはメモリーの ビット数と同数の記憶案子を必要とするので、集 積度の向上が困難であり、また価格が高いという 欠点があった。

本発明は1つの記憶素子に複数のビット数を記 憶させることにより、メモリーの素子数を減らす と共に低価格化を目的とする。

〔問題点を解決するための手段〕

本発明の不揮発性メモリーは、 書込によって特 性が連続的に変化する半導体不揮発性記憶素子と、 書込モードと説出モードとを一定時間毎に交互に 切換える回路と、 複数ビットのディジタル信号を アナログ信号に変換する D / A 変換回路と、メモ リーセルからの読出レベルを前記アナログ信号レ

## 特開昭62-34398(2)

ベルと比較し、この結果によって専込動作を終了 させる回路と、読出されたアナログ信号レベルを ディジタル信号に逆変換するA/D変換回路とを 含むことを特徴とするものである。 〔実施例〕

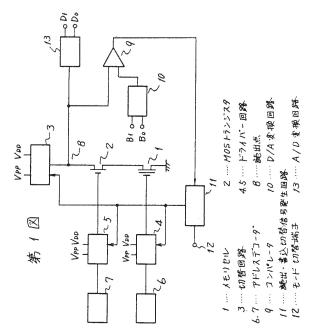

次に本発明について図面を参照して説明する。 第1図は本発明の一実施例の回路図である。1は フローティングゲートMOSトランジスタによる メモリセル、2はMOSトランジスタ、3は書込 用高電源(VPP)と読出用低電圧電源(VDD)を 切換える負荷回路、4,5は同じく電源をVPPと VDDとを切換えることによって書込時には高電圧、 読出時には低電圧を出力するドライバー回路、6. 7はアドレスデコーダー、8はメモリーセル1か らの読出点、9はコンパレータ、10は2ビット のD/A変換回路、11は読出・事込切換信号発 生回路、12はR/W切換端子、13は2ビット のA/D変換回路である。

データの書込の場合は、まず、外部からアドレ ステコーダ6,7にメモリセル1を選択するため

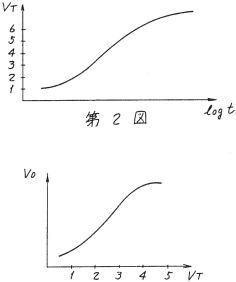

スタ1のV<sub>T</sub>が変化すると読出点8の出力電圧(V<sub>0</sub>) は第3図に示すように変化する。一方、書込むべ き2ビットの入力ディジタル信号B0,B1はD /A変換回路10でアナログ信号に変換され、こ のアナログ信号よりも低い間は書込・読出信号に よる動作を継続し、D/A変換回路10からのア ナログ信号よりもVoが高いことがコンパレータ9 で判定されると、読出・書込切書信号発生回路11 は書込・読出信号の出力を停止して審込動作を終 了する。したがって、この時点でのVoは入力ディ ジタル信号B1,B2に対応した電圧になってい る。

一方、データの説出の際には外部からアドレス デコーダ6,7にメモリセル1を選択するための アドレスを与え、モード切替端子12に説出モー ド信号を与える。この説出モード信号によって読 出・書込切替信号発生回路11は、前記書込・読 出信号は出力し、ドライバー回路4,5はV<sub>DD</sub>に 近い電圧をメモリセル1,MOSトランジスタ2 に与える。予め記憶されていた読出点8の出力電 のアドレスを与え、モード切替端子12に書込モ ード信号を与える。この再込モード信号によって 読出・書込切替信号発生回路11は、2値の一方 のレベルの書込期間と、2値の他方のレベルの税 出期間とを周期的に繰返す読出・書込信号が発生 され、書込期間には、ドライバー4,5からV<sub>PP</sub> に近い電圧が出力され、メモリセル1,MOSト ランジスタ2に与えられ、読出期間にはV<sub>DD</sub>に近 い電圧が出力されメモリセル1,MOSトランジ スタ2に与えられる。切替回路3は、書込期間に はV<sub>PP</sub>を、読出期間にはV<sub>DD</sub>を、読出点8に供給 する。

書込期間の横算値で与えられる、メモリセル1 の書込時間 t とメモリセル1のスレショールド電 E V<sub>T</sub> との関係は、一定の電圧条件のもとでは第2 図に示すような関係となり、書込時間が長くなる に従がって V<sub>T</sub> が上升する。またフローティングゲ ートMOSトランジスタ1とMOSトランジスタ 2とは負荷回路3との間でレジオ回路を構成して いるので、フローティングゲートMOSトランジ

EはA/D変換回路13を経て2ビットのディジ タル信号D0,D1として出力される。

なお、D/A変換回路10とA/D変換回路13 は特性を揃える意味から基準電圧原や分圧素子を 共用化するのが望ましく、また、回路10のD/A 変換特性と回路13のA/D変換特性との間には 動作マージンを最大にするため1/2LSBのレベ ル差を持たせることが望ましい。

第1図の実施例は1累子2ビットの不弾発性メ モリーの回路を示したが、MOSトランジスタ2 を並列に接続し各々のトランジスタ2に対しメモ リーセルを並列に接続し対応するアドレスデコー ダー及びドライバーを配置することによって任意 の数の記憶案子を持つメモリーを構成できる。

前記実施例では記憶素子として、フローティン グゲートMOSによるEPROM素子を用いている が、代りにMNOSやトンネル注入によるEEP ROM素子、その他任意の素子を用いることもで きる。 (発明の効果)

-1188 -

以上説明したように、本発明では、書込時間に よって V<sub>T</sub> 等の特性が連続的に変化する素子に対し て出力電圧が複数ビットディジタル信号を D / A 変換した電圧に一致するまで短かい周期で書込と 読出を繰返すことにより、1 素子のメモリーセル トランジスタに複数ビットのディジタルデータを 書込むことができ、ビット数に対してメモリーセ ルの数を少なくした不揮発性メモリーが実現でき る。

4. 図面の簡単な説明

第1図は本発明の一実施例の回路図、第2図は 第1図中のメモリセル1の特性図、第3図は第1 図中の説出点の電圧の特性図である。

1 ……フローティングゲートMOSトランジス ター、2 ……MOSトランジスター、3 ……負荷

回路、4,5 ……ドライバー回路、6,7 ……ア ドレスデコーダー、9 ……コンパレーター、10

……D/A変換回路、11 ……読出・書込切換信

号発生回路、13 ……A/D変換回路。

貭

代理人 弁理士 内

-1189 -