## UNITED STATES PATENT AND TRADEMARK OFFICE

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

# SILICON LABORATORIES, INC. Petitioner

**V**.

CRESTA TECHNOLOGY CORPORATION Patent Owner

> Case IPR Unassigned Patent 7,075,585

Title: Broadband Receiver Having a Multistandard Channel Filter

# DECLARATION OF DOUGLAS HOLBERG IN SUPPORT OF PETITION FOR INTER PARTES REVIEW OF U.S. PATENT NO. 7,075,585

11, 12, 13, 14 15, 20

Cresta Ex 2020-1 Silicon v Cresta IPR2015-00626

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Mail Stop PATENT BOARD

Alexandria, VA 22313-1450

P.O. Box 1450

U.S. Patent Trial & Trademark Office

# **TABLE OF CONTENTS**

| I.   | INTRODUCTION                     |                                                                                             |  |

|------|----------------------------------|---------------------------------------------------------------------------------------------|--|

| II.  | QUALIFICATIONS AND COMPENSATION1 |                                                                                             |  |

| III. | MATERIALS CONSIDERED             |                                                                                             |  |

| IV.  | THE '585 PATENT                  |                                                                                             |  |

|      | А.                               | Introduction                                                                                |  |

|      | B.                               | Prosecution History of the '585 Patent15                                                    |  |

|      | C.                               | Person of Ordinary Skill in the Art                                                         |  |

|      | D.                               | Claim Construction                                                                          |  |

|      |                                  | Board's Previous Constructions19                                                            |  |

|      |                                  | Additional Term                                                                             |  |

|      |                                  | Patent Owner's Proposed Constructions                                                       |  |

| V.   | OPIN                             | IONS RELATING TO EACH OF THE GROUNDS24                                                      |  |

|      | А.                               | Foundational Claims                                                                         |  |

|      |                                  | Claim 17 is anticipated by Thomson24                                                        |  |

|      |                                  | Claim 19 is anticipated by Thomson                                                          |  |

|      |                                  | Claim 1 is anticipated by Thomson                                                           |  |

|      |                                  | Claim 10 is obvious over Thomson in view of Harris                                          |  |

|      | B.                               | Ground 1: Claim 11 is obvious over Thomson in view of Harris,<br>further in view of Grumman |  |

2 1 2

e

|      | C.              | Ground 1: Claim 12 is obvious over Thomson in view of Harris,<br>further in view of Grumman               |

|------|-----------------|-----------------------------------------------------------------------------------------------------------|

|      | D.              | Ground 2: Claim 13 is obvious over Thomson in view of Harris,<br>further in view of Zenith45              |

|      | E.              | Ground 2: Claims 15 and 20 are obvious over Thomson in view of Harris, further in view of Zenith          |

|      | F.              | Ground 3: Claim 14 is obvious over Thomson and Harris, in view of Zenith, and further in view of Birleson |

|      | G.              | Summary Claim Charts for Challenged Claims54                                                              |

| VI.  | CONCLUSION      |                                                                                                           |

| VII. | ACKNOWLEDGEMENT |                                                                                                           |

.

### **DECLARATION BY DOUGLAS HOLBERG**

I, Douglas Holberg, hereby declare, affirm and state the following:

#### I. INTRODUCTION

1. The facts set forth below are known to me personally and I have firsthand knowledge of them. I am a U.S. citizen over eighteen years of age. I am fully competent to testify as to the matters addressed in this Declaration. I understand that this Declaration is being submitted along with a Petition for *inter partes* review of US Patent No. No. 7,075,585 ("the '585 patent").

2. I was asked to give my opinion on whether claims 11–15 and 20 of the '585 patent ("the challenged claims") are unpatentable in view of certain prior art references. As described in detail in this Declaration, it is my opinion that each of those claims is rendered obvious by the prior art.

### II. QUALIFICATIONS AND COMPENSATION

3. I have over 30 years of experience in the electronics field. During that time, I have worked for several different electronics companies including: Mostek, Crystal Semiconductor, Cygnal Integrated Products, and Silicon Laboratories. I joined Silicon Laboratories when it acquired Cygnal, which I co-founded in 1999. I am a named inventor on 39 U.S. patents. I have held a variety of engineering positions over that time from circuit designer to Director of Engineering and V.P. of Technology. In addition to my engineering experience, I also have served as an

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-4 Silicon v Cresta IPR2015-00626

adjunct faculty member at the University of Texas, where I earned my M.S.E. and Ph.D. degrees. A complete listing of my qualifications including a list of my patents is attached to this declaration as Appendix A.

4. My earliest experience with electronics began in High School where for three years, I took classes where I learned about radio and television architectures, built radios, repaired both radios and televisions. Concurrently, I was employed by a radio and television repair shop where I was paid to diagnose and repair radios and televisions. Naturally, this required intimate knowledge of the fundamental operation of radios and televisions of that era. I attended Texas A&M University where I studied electrical engineering with a focus on analog circuits for electives. One course (EE489) covered analog filters in detail from synthesis through implementation. Another course, Communications Circuits (EE428), covered radio receivers, oscillators, mixers, amplifiers, filters, transmitters, etc. A project of particular interest in EE428 was the design of a CB radio receiver using a standard broadcast-band AM receiver. This project involved designing a ~9 MHz, oscillator driving into a non-linear amplifier and filtering all but the third harmonic (~27 MHz) to mix with a signal derived from an antenna so that a ~27 MHz CB channel would mix to a frequency in the standard AM broadcast band. The AM receiver then performed the subsequent demodulation to audio so that CB radio communication was tuned and heard. I built this circuit in

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

the lab and demonstrated it to my professor—it worked—I received an A in my Communications Circuits class. Upon graduation, I went to work for Mostek Corporation designing integrated circuits for telecommunications applications. I designed an integrated DTMF tone generator (both digital and analog components) for which I acquired my first patent. After leaving Mostek, I joined a startup company as employee #2 where I designed a dual-channel (atrium-ventricle) This circuit used discrete-time switchedpacemaker sense amplifier/filter. capacitor technology operating transistors in subthreshold region. My next project was to design a universal switched capacitor filter (CS7008) comprising four biquad filters, each individually programmable. Coefficients for the each biquad filter were stored in an external PROM and upon power up, the memory of the PROM was indexed to load the coefficients of each biquad from the PROM to volatile memory on board the filter chip. During this same period, I was coauthoring the book "CMOS Analog Circuit Design" which was published in first edition in 1987. I enrolled in a masters/Ph.D. program and for the next five years worked on the application of bipolar technology to DRAM sense amplifier architectures and circuit simulation algorithms. Upon graduating with a Ph.D. I went to work for Crystal Semiconductor/Cirrus Logic where I designed highfrequency synthesizers (60 MHz) for read-channel circuits reading magnetic media (hard disk drives). I managed a group making CCD interface circuits for digital

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009 camera applications as well as television encoder chips. Upon leaving Cirrus, I started a company developing mixed-signal microcontrollers. Though I was a founder/CTO/VP Engineering, we had a small group, so I also acted as a circuit designer and layout designer as needed. I designed a novel A/D converter for which I received a patent, designed  $\Delta$ Vbe temp sensors, I/O pads (both design and layout) as well as other miscellaneous circuits. My company was purchased by Silicon Labs where I remained employed as a manager of the microcontroller group at first, followed by a role as VP of Technology where I managed the CAD group and the developed design methodologies for the designers at Silicon Labs. I left Silicon Labs in 2008 and began a consulting career in the area of patents and intellectual property. Based on my experience, both professional and educational, I believe I am more than qualified to give the opinions expressed herein.

5. I am being compensated at my normal rate of \$275 per hour for my work in connection with this matter. My compensation is not dependent in any way on the contents of this Declaration, the substance of any further opinions or testimony that I may provide, or the ultimate outcome of this matter.

### **III. MATERIALS CONSIDERED**

6. In forming the opinions expressed herein, I have reviewed and considered numerous documents, including the following materials:

A. U.S. Patent No. 7,075,585 ("the '585 patent").

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-7 Silicon v Cresta IPR2015-00626

- B. Return of Service of for the Complaint in *Cresta Technology Corporation v. Silicon Laboratories, Inc. et al.*, Case No. 1:14-cv-00078-RGA before the United States District Court for the District of Delaware (January 28, 2014) ("Return of Service").

- C. Complaint in ITC Investigation No. 377-TA-910 (January 28, 2014) ("ITC Complaint").

- D. European Patent Application No. EP 0696854, titled "Broadcast Receiver Adapted for Analog and Digital Signals," assigned to Thomson Multimedia S.A. ("*Thomson*").

- E. Clay Olmstead & Mike Petrowski of Harris Semiconductor, A Digital Tuner for Wideband Receivers, DSP Applications Magazine, Sep. 1992 ("Harris").

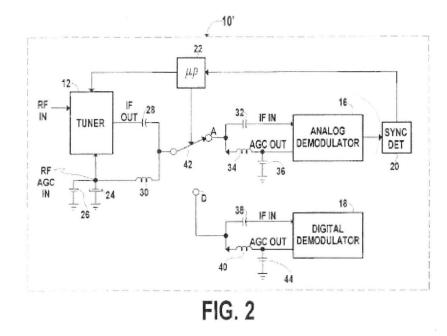

- F. Al Lovrich & Ray Simar, Jr., "Implementation of FIR/IIR Filters with the TMS3201/TMS32020," Application Report: SPRA003A (Texas Instruments 1989) ("TI App Note").

- G. U.S. Patent No. 6,643,502, titled "Multi-standard Reception," to Van De Plassche et al. ("VDP").

- H. U.S. Patent 5,381,357, titled "Complex Adaptive FIR Filter," to Wedgwood et al. ("Grumman").

- I. Excerpts of the prosecution file history of the '585 patent.

- J. U.S. Patent 6,377,316, titled "Tuner with Switched Analog and Digital Modulators," to Mycynek et al. ("Zenith").

- K. U.S. Patent 5,999,567, titled "Method for Recovering a Source Signal from a Composite Signal and Apparatus Therefor," to Torkkola. ("Torkkola").

- L. U.S. Patent 6,263,222, titled "Signal Processing Apparatus," to Diab et al. ("Diab").

- M. Order No. 50 in ITC Investigation No. 337-TA-910, "Initial Determination Granting Cresta Technology Corporation's Corrected Motion to Partially Terminate Investigation as to U.S. Patent No. 7,251,466 and Certain Claims of U.S. Patent Nos. 7,075,585 and 7,265,792" (November 12, 2014).

Cresta Ex 2020-8 Silicon v Cresta IPR2015-00626

- N. U.S. Patent 6,725,463, titled "Dual Mode Tuner for Co-Existing Digital and Analog Television Signals," to Birleson. ("Birleson").

- O. Advanced Television Systems Committee, "ATSC Digital Television Standard" (September 16, 1995).

- P. Microsoft Computer Dictionary, pp. 269, 270, Microsoft Press (5th ed. 2002).

- Q. European Patent Application No. EP 94300649.4, titled "Digital Filtering, Data Rate Conversion and Modem Design," filed January 28, 1994, to Terrell ("Terrell").

- R. Excerpts of "The Authoritative Dictionary of IEEE Standards Terms," (2000).

- S. Patent Owner's Response in IPR2014-00728 and the accompanying exhibits.

- T. U.S. Patent 5,796,442, titled "Multi-Format Television Receiver," to Gove et al. ("Gove").

- U. Trial testimony of Michael Caloyannides, Ph.D., in ITC Investigation No. 337-TA-910 (Dec. 5, 2014).

### IV. THE '585 PATENT

### A. Introduction

7. The '585 patent, entitled "Broadband Receiver having a Multistandard

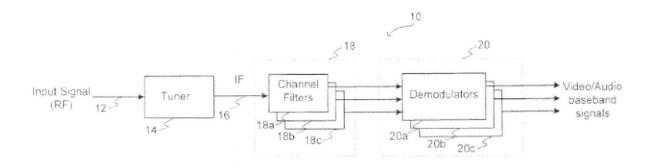

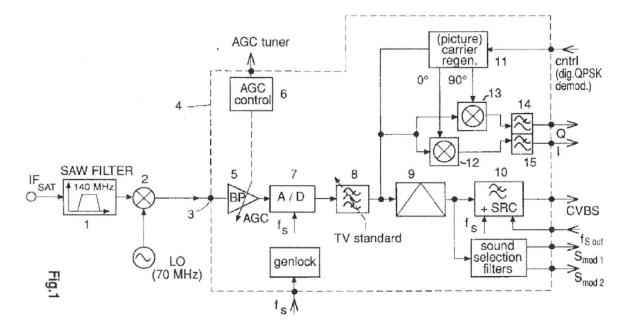

Channel Filter" claims priority to a provisional application filed on September 17, 2001. The '585 patent admits that television receivers capable of receiving multiple different television standards such as NTSC and PAL were known in the art. An example architecture of one multistandard receiver is described as "prior art" and shown in Fig. 1 of the patent:

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

8. (Ex. 1001, Fig. 1 ("Prior Art"); 1:43–2:26). As shown above, the prior art architecture included: a tuner for receiving an radio frequency ("RF") input signal; a tuner for converting that RF signal to an intermediate frequency ("IF") signal; a multichannel filter 18 comprised of a "bank of channel filters 18a to 18c," each corresponding to a "specific format and standard"; and a demodulator 20 comprised of a plurality of individual demodulators, each "receiving filtered signals from a corresponding channel filter." (*Id.* at 1:49–2:26). This "conventional multi-standard" television architecture could process both analog and digital TV formats as well as different TV standards. (*Id.*).

9. The '585 patent describes at least two problems with this architecture: "First, conventional television receivers use discrete analog and digital components," and "Second, the conventional multi-standard television receivers require duplicate components to support the different television standards." The inventors of the '585 patent contended that, as a result, the prior art television receivers were "bigger in size and more costly to manufacture." (*Id.* at 2:27–35).

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-10 Silicon v Cresta IPR2015-00626

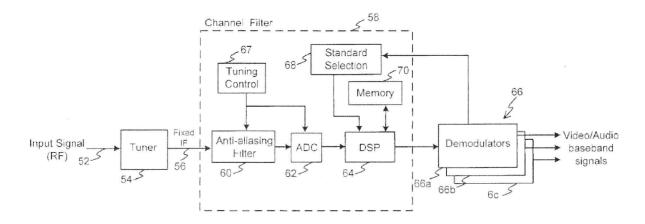

10. The '585 patent purports to solve the shortcomings of the prior art by processing the IF signal in the digital domain rather than in the analog domain by replacing the "bank of channel filters 18a to 18c" with a digital channel filter 58, as shown below:

(*Id.* at Fig. 2). This programmable channel filter converts the incoming analog IF signal to a digital representation (after performing anti-aliasing) using an analog-to-digital converter ("ADC") 62 and filters the digital signal in the digital domain using a digital signal processor ("DSP") 64. (*Id.* at 4:3–16). The DSP implements one of several filter functions depending on the television format and standard of the incoming RF signal, as indicated by the "standard selection circuit 68." (*Id.* at 4:51–64). The "coefficients of the filter functions" for each of those standard-specific filters is "stored in a look-up table in a memory 70." (*Id.* at 4:60–64).

11. The proposed digital-domain architecture described in the '585 patent was well known in the art at the time of the '585 patent. Almost a decade before

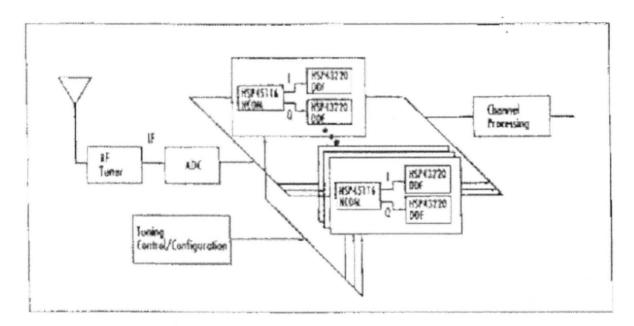

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009 the '585 patent was filed, the industry already recognized the benefits of processing communication signals in the digital domain using "standard off the shelf DSP IC's as digital replacements for the analog intermediate frequency (IF) processing state in wideband receivers." (Harris, Ex. 1005, p. 1). An exemplary implementation of such a "digital replacement[]" is shown in a 1992 Harris Semiconductor Application Note:

(*Id.* at p. 7).

12. In this example, a wideband "channelized receiver" uses an ADC to convert the incoming RF signal to an IF signal, which is processed by one of several digital "Finite Impulse Response (FIR) filter(s)" tuned to a particular center frequency. (*Id.* at 5–6). While this particular implementation uses a dedicated filter for each desired center frequency, "[i]n systems where the second IF filter

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

> Cresta Ex 2020-12 Silicon v Cresta IPR2015-00626

stage consists of a bank of filters to support various operational modes, cost and board space can be saved be [sic:by] reconfiguring a single [Digital Decimation Filter] DDF to implement the filter required by each operational mode." (*Id.* at 5). Thus, by 1992, the industry had already solved the problem that the '585 patent recognized in 2001. While this particular design was focused on voice communication, the author suggested that the "declining cost of technology is making DSP a desirable alternative for an expanding spectrum of communication problems." (*Id.* at 7).

13. In 1995, three years after publication of Harris, Thomson filed a European Patent Application entitled "Broadcast Receiver Adapted for Analog and Digital Signals." (Thomson, Ex. 1004, p.1). By this point, digital signal processing technology had progressed to the point where "direct IF sampling is becoming more cost effective than traditional analog signal processing in some radio applications and it seems that the point has been reached where a digital solution for video IF signals should no longer be excluded in the satellite TV receiver design." (*Id.* at 1:22–27). The resulting television receiver is shown below:

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-13 Silicon v Cresta IPR2015-00626

(*Id.* at Fig. 1).

14. The Thomson receiver is "suitable for digital and analog input signals . . . using a common A/D converter only for analog and digital transmission via satellite." (*Id.* at 1:30–33). The incoming RF satellite signal is filtered by SAW Filter 1 and then down-converted by mixer 2 to an intermediate frequency ("IF") signal. (*Id.* at 2:47–57). The IF signal is then passed through automatic gain amplifier "AGC 5," with "an internal bandpass limitation before the IF signal enters the input of the A/D-converter 7." (*Id.* at 2:57–3:3). Thomson teaches that the filtering is done in a way that "does not cause any aliasing problems." (*Id.* at 3:9:11). The A/D converter 7 converts the filtered, IF signal into a digital representation of the intermediate frequency signals. (*Id.*).

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-14 Silicon v Cresta IPR2015-00626

15. The digital output of the A/D converter is processed by an "adaptively controlled bandpass filter" that is tunable to the particular frequency range of the incoming "TV standard" (i.e., analog or digital). (Ex. 1004, 3:16–19, Fig. 2(g)). The digital output signals produced by this digital signal processor are "digital output signals that are indicative of information encoded in said input RF signal." (See Ex. 1001 at 6:67–7:2). These digital output signals are fed in parallel to two different demodulators: one capable of demodulating those signals encoded in the analog TV format ("FM-demodulator (9)") and the other one capable of demodulating signals encoded in the digital TV format ("QPSK-demodulator (12, 13)") to produce video and audio baseband signals. (Ex. 1004 at 4:10–12). Thus, Thomson describes a digital domain, multi-channel television receiver that uses a single digital filter to process television signals in a plurality of different television formats. Thomson therefore overcame both of the purported "shortcomings" of the prior art over six years before the '585 patent was filed.

16. In my opinion, Thomson anticipates independent apparatus claim 1 and independent method claim 17 of the '585 patent, as discussed below. Moreover, using a signal processor to apply a finite impulse response digital filter as recited in claim 10 was not novel, because the use of finite impulse filters was within the knowledge of a person of ordinary skill in the art as evidenced by the following:

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-15 Silicon v Cresta IPR2015-00626 17. Harris discloses a reconfigurable, reprogrammable signal processor implementing a plurality of FIR filters, each corresponding to a particular operating mode. (Ex. 1005, p. 6 ("the digital receiver structure also offers flexibilities like programmable filtering")).

18. A POSITA faced with the design of the adaptive filter in Thomson would have only two classes of digital filters from which to choose: finite impulse response (FIR) and infinite impulse response (IIR). The FIR implementation would be the obvious design choice in the Thomson application because it would produce "a linear phase, and only FIR filters can be designed to have linear phase," which is important in television applications such as Thomson. (*See* TI App Note, Ex. 1006, p. 21).

19. The '585 patent refers to a prior art specification teaching a linear FIR filter, namely a "filter response . . . as a raised root cosine with 0.114 roll-off." (Ex. 1001, 5:32–37; *see also* ATSC Digital Television Standard, Ex. 1016, at Fig. 12, p. 58 ("linear phase raised cosine Nyquist filter" which would necessitate a FIR filter implementation)). FIR filters also are less sensitive to coefficient quantization and are thus generally more stable than IIR filters.

20. With regard to claim 11 of the '585 patent, indexing into a block of *memory* storing coefficients for one of a plurality of digital FIR filters was well known in the art. Likewise, storing data in blocks of memory and accessing that

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-16 Silicon v Cresta IPR2015-00626

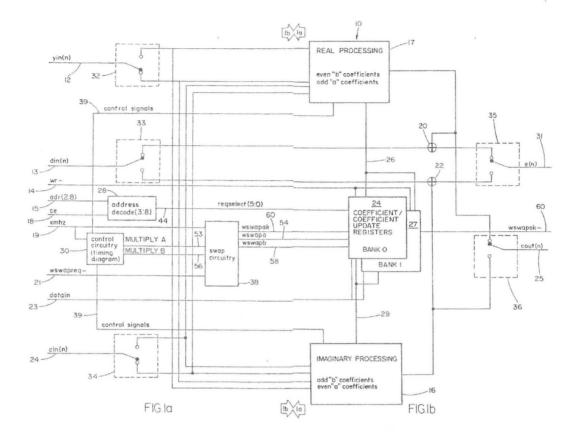

data by indexing into a block of memory was well known to a POSITA at the time the '585 patent application was filed. Furthermore, storing sets of FIR filter coefficients in memory and accessing those coefficients using a pointer into memory was also well known. For example, Terrell (EP App 94300649.4, Ex. 1018) discloses a FIR filter (Ex. 1018, 7:3–6) that can selectively retrieve different FIR filter coefficients from memory: "The coefficient store 3 supplies coefficients in accordance with the coefficient select signal from a control unit 5. The control unit 5 decides which coefficients should be selected from the coefficient store 3 and provided to the calculation unit 1 for each calculation." The control unit 5 responds to control inputs, and accordingly it can select the coefficients to be used at any given instant dynamically on the basis of the values of the control inputs." (Ex. 1018, 6:35–43). Furthermore, Terrell discloses that the input data can be used to select the FIR filter coefficients. (Id. at 6:43–48 ("In principle, any signals could provide the control inputs depending on the use to which the filter is to be put, and typically these will be obtained from the input data."); see also id. at 21:19–51, 25:13–24, Fig. 11, Fig. 15 (describing that the coefficients are stored as sets in memory and the initial value of a particular set of coefficients is generated based on a digital phase number)). Even a look up table to store FIR filter coefficients was well-known in the art. (See id. at 6:53–56).

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-17 Silicon v Cresta IPR2015-00626

21. Additionally, Grumman discloses a complex adaptive FIR filter having two memory banks, each memory bank storing one set of coefficients for a FIR filter. (Ex. 1008, Figs. 1a and 1b). The signal processor indexes into one of the two memory banks to access one set of filter coefficients. (*Id.* at Abstract, Fig. 1b, (banks 0 and 1), 2:7–11). Grumman further discloses swap circuitry that is responsible for selecting one of the two memory banks. (*Id.* at Fig. 1a, 6:51–54). An output from the swap circuitry determines which one of the two memory banks to access, and therefore, indexes one of the plurality of filter coefficients stored in memory. (*Id.* at Fig. 7b, 10:21–66). Thus, accessing sets of coefficients stored in memory via an index is not novel or unobvious.

### B. Prosecution History of the '585 Patent

22. As part of my analysis, I reviewed the prosecution history of the '585 patent before the United States Patent and Trademark Office. The '585 patent application was filed on September 6, 2002, and claims priority to Provisional Application No. 60/322,548, filed on September 17, 2001. In the first office action, all but three of the dependent claims were rejected in light of the prior art, which disclosed multi-mode receivers. Claims 1, 2, 5, 11, 13, 17–19 and 23 were rejected under §102(e) "as being anticipated by Van De Plassche et al. [Ex. 1007]." (Ex. 1010, p. 55). Claims 6, 12, 14–16, 20 and 21 were likewise rejected under §103(a) "as being unpatentable over Van De Plassche et al." (*Id.* at 56). Claims 7,

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-18 Silicon v Cresta IPR2015-00626 8, 10 and 22 were rejected as obvious "over Van De Plassche et al. in view of Balaban et al." (*Id.* at 57). Finally, claims 3, 4 and 9 "appear allowable over the prior art." (*Id.* at 58).

23. In response to that office action, applicant submitted an amendment to incorporate the limitation of claim 3 into the two independent claims 1 and 18 (now 17). Specifically, claim 1 was amended to add a "plurality of demodulators" as shown below:

a plurality of demodulators, each coupled to receive output signals from said signal processor, each of said demodulators for demodulating said digital output signals according to one of said formats of said input RF signal, each of said demodulators generating video and audio baseband signals corresponding to said format of said input RF signal.

(Ex. 1010, p. 45). The applicant made a similar amendment to claim 17:

demodulating said processing digitized signals to generate baseband signals corresponding to said format of said input RF signal.

(*Id.* at 47). In the accompanying remarks, the applicant explained that "claim 1 has been amendment [sic] to include the limitation in allowable claim 3.... Furthermore, in the present amendment, claim 18 has been amendment [sic] to include the limitation in claim 23 which is allowable for the same reasons claim 3 is allowable." (*Id.* at 50).

24. In the subsequent Office Action of December 6, 2005, the Examiner rejected claim 18 (issued claim 17) even in light of this amendment because it did

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009 not mirror that "plurality of demodulators" language in claim 3. Accordingly the Examiner rejected claim 18 (issued claim 17) and its dependent claims "as being anticipated by Van De Plassche et al." (Ex. 1010, pp. 36, 37). In response to this rejection, applicant expressly recited a "plurality of demodulators" in claim 18 (issued claim 17), as it had done in claim 1:

demodulating <u>using a plurality of demodulators</u> said <u>processed processing</u> digitized signals to generate baseband signals corresponding to said format of said input RF signal <u>signals</u>.

(*Id.* at 28). In response to this amendment, the Examiner allowed all of the claims. (*See* "Notice of Allowability," *id.* at 18).

25. What is notable from this prosecution is the rejection that the Examiner did not make. The Examiner recognized that Van De Plassche anticipated the applicant's original idea of a multistandard broadband television receiver that processes IF signals in the digital domain instead of the analog domain, but considered the notion of separate demodulators for each of those standards novel. However, the inventors themselves admitted that the prior art used separate demodulators for different standards, as shown in Fig. 1 of the '585 patent (above). Even if this were novel, which it is not, one skilled in the art would find this obvious in view of the admitted prior art.

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

# C. Person of Ordinary Skill in the Art

26. I have considered certain issues from the perspective of a person of ordinary skill in the art. It is my opinion, based upon a review of the file history of the '585 patent, that a person of ordinary skill in the art to the '585 patent, as of September 17, 2001,<sup>1</sup> a person of ordinary skill in the art at the time of the alleged invention of the '585 patent ("POSITA") would have held at least a Masters of Science or higher degree in electrical engineering, have at least four years of experience with mixed signal system design, including analog front ends and subsequent digital signal processing of various analog and digital signal formats of video and audio content.

### **D.** Claim Construction

27. I am informed that the claims in an *inter partes* review should be given their "broadest reasonable construction in light of the specification" as commonly understood by a person of ordinary skill in the art.

For purposes of this Declaration, I have been asked to assume that the challenged claims are entitled to the benefit of the priority date of the provisional application. However, I have not investigated and have formed no opinion on whether the provisional applicable provides an enabling disclosure of those claims. I reserve the right to express the contrary opinion that those claims are not entitled to the priority date of the provisional application.

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-21 Silicon v Cresta IPR2015-00626

## **Board's Previous Constructions**

28. In the previously filed proceeding, IPR2014-00728, the Board construed the following terms as follows:

- RF Signals—"Signals having a frequency between 10 kHz and 100 GHz";

- Format—"analog and digital signals are examples of distinct formats";

- Baseband signal—"a signal without transmission modulation"; and

- Signal Processor—"a digital module that processes signals in the digital domain."

IPR2014-00728, Paper 9 at 6–9. I agree that each of the constructions adopted by the Board is appropriate to the present proceeding.

## Additional Term

29. "Indexes"—Another term I believe requires further explanation for purposes of this Petition is the "indexes" term as used in claim 11. Specifically, "wherein said plurality of finite impulse response filters are stored in memory, and said signal processor indexes said memory to retrieve one of said plurality of finite impulse response filters." (Ex. 1001, claim 11).

30. As disclosed in the '585 patent, the standard selection circuit, depending on its state, selects "between the several analog and digital television

Cresta Ex 2020-22 Silicon v Cresta IPR2015-00626 standards." (Ex. 1001, 4:56–58). Based on the standard selection circuit, the DSP applies a filter function. The "coefficients of the filter functions are stored in a look-up table in a memory 70. DSP 64 retrieves the coefficients from memory 70 to be applied to the incoming digital signals." (*Id.* at 4:61–64). The signal processor indexes or points to a block of memory when retrieving a set of coefficients. This usage of the term indexing is consistent with the plain and ordinary meaning of that term. (*See* Microsoft Computer Dictionary, Ex. 1017, pp. 269, 270 (defining the verb "index" as "1. In data storage and retrieval, to create and use a list or table that contains reference information, pointing to stored data . . . 3. In indexed file storage, to find files stored on disk by using an index of file locations (addresses). 4. In programming and information processing, to locate information stored in a table by adding an offset amount, called the index, to the base address of the table.")).

### **Patent Owner's Proposed Constructions**

31. In its Patent Owner response in IPR2014-00728, Patent Owner offers constructions for several terms. As discussed below in detail, I do not agree with the Patent Owner's proposed constructions because they do not reflect the plain and ordinary meaning of those terms to a POSITA.

32. "Input RF signals"—Patent Owner proposes to construe this term as "a signal that is an incoming signal that comes out of the medium of propagation

Cresta Ex 2020-23 Silicon v Cresta IPR2015-00626 and is external to the tuner without any processing by the tuner." (IPR2014-00726, Paper No. 30 at 9–11). I disagree with this definition for the reasons discussed below.

33. First, the specification of the '585 patent uses the term "input signal" in a number of places. (See, e.g., Ex. 1001 at 5:20, 5:30, 5:55, 8:9, Figs. 1, 2). In each case, the term is used in its most direct and logical sense, *i.e.*, as a signal that is input to a circuit. (See id.). In some cases, the term "input signal" is modified to make clear what type of signal it is. For example, at column 5, line 55, the specification notes that the "analog demodulator 66a receives analog input signals only." (Id. at 5:55 (emphasis added)). This makes clear that the signal input to the analog modulator is an analog signal. Likewise, the specification refers in several places to an "input RF signal." (See, e.g., Ex. 1001 at 1:59, 2:49, 2:50, 2:58, 2:60, 2:61, 3:2, 3:46, 3:48, 3:49, 3:54, 5:23, 5:32). In each instance, the term is used solely to indicate that the signal that is input to the circuit is an RF signal. RF stands for "radio frequency," as noted in the specification itself. (Ex. 1001 at 1:52). A POSITA understood that radio frequency or RF refers to "signals having a frequency between 10 kHz and 100 GHz." (The Authoritative Dictionary of IEEE Standards Terms, p. 912 (2000)). In no place does the specification equate "input RF signals" to the source of those signals or the medium over which the signal is propagated. In fact, the specification uses permissive language when it

Cresta Ex 2020-24 Silicon v Cresta IPR2015-00626 describes the source of those signals. (*See, e.g.*, Ex. 1001 at 3:46–48 ("a television receiver 50 receives input RF signals, such as those received on an antenna or on a cable line, on an input terminal 52."). The patent specification does not require that cable line or input terminal 52 only receive input RF signals directly "out of a medium of propagation external and is external to the tuner without any processing by the tuner," as required by Patent Owner's construction.

34. The claims of the '585 patent use the term "input RF signals" in its plain and ordinary way. For example, Claim 1 requires "receiving input RF signals." (Ex. 1001, claim 1). Claim 1 makes no mention of the source of those input signals. The first element of the claim is the "tuner" that receives these signals. The term "input RF signal" likewise appears in the preamble of method claim 17. The first step of that method, like claim 1, refers simply to "receiving said input RF signal." (*Id.*). Once again, that claim does not refer to the source of the RF signal or the medium over which it is propagated. (*Id.* at claim 17).

35. "Tuner for receiving input RF signals and for converting said input RF signals to intermediate signals"—Patent Owner proposes that this term means "tuner that receives an incoming signal that comes out of the medium of propagation and is external to the tuner without any processing." (IPR2014-00726, Paper No. 30 at 12). I disagree with this construction for the same reasons as discussed above with respect to "input RF signals."

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-25 Silicon v Cresta IPR2015-00626 36. "Said input RF signals encoding information in one of a plurality of formats" —Patent Owner proposes that this term "requires receiving one format RF signal at a time." (IPR2014-00726, Paper No. 30 at 13). In my opinion, a POSITA would interpret the indefinite article "a" to mean "one or more," rather than "only one."

37. "Signal processor for processing . . . said format" and "Processing . . . said format"—Patent Owner construes these terms to mean "signal processing processes only one format RF signal and does not process a plurality of formats in parallel" (IPR2014-00726, Paper No. 30 at 13) and "processing of only one format RF signal and not the processing a plurality of formats in parallel," (IPR2014-00726, Paper No. 30 at 13) and "processing of only one format RF signal and not the processing a plurality of formats in parallel," (IPR2014-00726, Paper No. 30 at 13) and "processing of only one format reflect the broadest reasonable construction of this term in light of the specification. A POSITA would not interpret "said" to mean "only one."

38. "**Receiver**"—Patent Owner construes this term to mean "apparatus that first converts the incoming radio frequency (RF) signals to intermediate frequency (IF) signals and then second, it converts the intermediate frequency (IF) signals to baseband signals." (IPR2014-00726, Paper No. 30 at 13–15). In my opinion, the term "receiver," which is used only in the preamble of the claim, merely reflects the general purpose or intended use for the invention, *i.e.*, as a receiver for a television.

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-26 Silicon v Cresta IPR2015-00626

39. "Each of said demodulators generating video and audio baseband signals"—Patent Owner did not provide an explicit definition of this term in its Patent Owner response, but its expert apparently disagrees with the Board's construction of "baseband signals." (*See* IPR2014-00726, Ex. 2003 at 29–30.) Patent Owner's expert, however, provides no basis for his opinion. In my opinion, a POSITA would understand that the plain and ordinary meaning of "baseband signals" is as the Board previously construed that term.

### V. OPINIONS RELATING TO EACH OF THE GROUNDS

40. All of the challenged claims of the '585 patent depend from two independent claims: 1 and 17. Claim 1 recites a receiver, while claim 17 recites a substantially equivalent "method for receiving input RF signal[s]." Challenged claims 11–15 depend directly from claim 10, which in turn depends from independent claim 1. Claim 14 depends directly from claim 13. Claim 20 depends directly from claim 19, which in turn depends from independent claim 17. A detailed explanation is provided below for each ground for each of the challenged claims.

#### A. Foundational Claims

### Claim 17 is anticipated by Thomson

Preamble

41. I am told that preambles of patent claims are typically not limitations on the claims. However, even assuming preambles are limiting, Thomson clearly,

24

Cresta Ex 2020-27 Silicon v Cresta IPR2015-00626 in my opinion, describes a "receiver" that implements the claimed "method of receiving an input RF signal." (Ex. 1004 at 1:3–4 ("invention relates to a broadcast receiver")). Thomson describes a "multi-standard tuner" capable of receiving a radio frequency (RF) input signal in the form of a satellite broadcast, terrestrial, and cable transmissions in the range of "950-1750 MHz." (*See id.* at 1:55 to 2:19)<sup>2</sup>. Thomson teaches this element under the Board's construction of "RF signals." (IPR2014-00728; Paper No. 9 at 6).

"receiving said input RF signals encoding information in one of a plurality of formats"<sup>3</sup>

42. Thomson teaches that the "multi-standard tuner" can receive RF signals in a plurality of formats, including "analog or digital ones." (*See, e.g.*, Ex. 1004 at 1:42–43). The '585 patent likewise identifies "analog and digital TV" as two different "format[s]." (*Id.* at 2:6). For at least these reasons, Thomson teaches this element under the Board's construction of "RF signals" from IPR2014-00728. Paper No. 9 at 6.

"converting said input RF signals to intermediate signals having an intermediate frequency (IF)"<sup>4</sup>

<sup>&</sup>lt;sup>2</sup> This element corresponds to the "tuner" of claim 1.

<sup>&</sup>lt;sup>3</sup> This element corresponds to "said input RF signals encoding information in one of a plurality of formats" in claim 1.

43. The Thomson "multi-standard tuner" receives the RF signal from an "outdoor" satellite unit, which "supplies the satellite channels already down-converted in a frequency band covering 950-1750 MHz." (Ex. 1004 at 1:55–60). As explained in Thomson, this RF signal is converted to a "140 MHz Sat-IF signal" that forms the "IF<sub>SAT</sub>" input to the circuit shown in circuit above in Fig. 1. (Ex. 1004 at 2:17–19, Fig. 1). This signal then gets further "down-converted" by "mixer stage 2" into "an IF signal of around 75 MHz (see Figs. 2d and 2e)." (*Id.* at 2:53–57). Therefore, Thomson teaches this element.

• "applying a first filter function to said intermediate signals"<sup>5</sup>

44. Thomson describes an automatic gain control "AGC amplifier 5 filter with an internal bandpass limitation before the IF signal enters the input of A/Dconverter 7." (*Id.* at 2:58–3:1). This "internal bandpass" filter applies a first filter function to the "IF signal." (*Id.*). Therefore, Thomson's AGC 5 with internal bandpass limitation satisfies this element of the claim.

<sup>4</sup> This element corresponds to "and for converting said input RF signals to intermediate signals having an intermediate frequency (IF)" in claim 1.

<sup>5</sup> This element corresponds to "channel filter for receiving the intermediate signals, said channel filter comprising: an anti-aliasing filter for filtering said intermediate signals" in claim 1. The structural aspect of this element is addressed separately below.

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-29 Silicon v Cresta IPR2015-00626  "said first filter function being an anti-aliasing filter and having a center frequency;"<sup>6</sup>

45. Thomson's bandpass filter is designed to avoid aliasing. As explained in Thompson:

The A/D-converter 7 is operated in the sub-sampling mode, but this *does not cause any aliasing problems because of the bandlimited input signal.* Owing to the high sampling frequency, the effective dynamic resolution of the A/D-converter 7 may be somewhat reduced with respect to the nominal resolution. It is expected that due to the FM modulation the distortions can be neglected.

(Thomson, Ex. 1004 at 3:9–16). Because the filter provides a "bandlimited input signal" to avoid "aliasing problems," the "AGC amplifier 5 filter with an internal bandpass limitation" performs an "anti-aliasing function," as recited in the claim. The Patent Owner's expert in the ITC agrees. (Ex. 1021 at 1220 ("it should help reduce aliasing, yes")). A bandpass filter also inherently has a center frequency in the middle of the bandpass.

"digitizing said filtered intermediate signals at a sampling frequency;"<sup>7</sup>

<sup>&</sup>lt;sup>6</sup> This element corresponds to "an anti-aliasing filter for filtering said intermediate signals" in claim 1.

46. The filtered output of the AGC amplifier 5 in Thomson is coupled to an analog-to-digital converter ("A/D") 7. (Ex. 1004 at Fig. 1). The "A/Dconverter [is] necessary for the digiti[z]ing" of the bandpass-filtered intermediate frequency signal output of AGC 5. (Ex. 1004 at 1:47; *see also id.* at Fig. 1). As the name implies, A/D 7 converts the filtered IF signal to, in the words of claim 1, "a digital representation thereof." Fig. 1 shows that "A/D 7" has a sampling frequency of "f<sub>s</sub>". Thomson further teaches that in one embodiment the "A/D converter (7) operates with a sampling frequency of about 100MHz." (*Id.* at 4:14– 16). For at least these reasons, Thomson teaches this element.

> "processing said digitized signals in accordance with said format of said input RF signals and generating digital output

<sup>7</sup> This element corresponds to "an analog-to-digital converter for sampling said filtered intermediate signals and generating a digital representation thereof" in claim 1.

signals indicative of information encoded in said input RF signals;"<sup>8</sup>

47. As described above, Thomson's "multi-standard" television receiver is specifically designed to process incoming television signals broadcast in analog and digital TV formats. Just like the '585 patent, Thomson describes a "bandpass filter 8" that has "an adaptively controlled bandwidth" that passes the analog TV encoded information in the case of analog formatted signal or the digital TV encoded information in the case of digital formatted signal. (Ex. 1004 at 3:16–25). The adaptive filter 8 makes this selection based on the "TV standard" input to the filter. (*Id.* at Fig. 1). Thus, adaptive filter 8 "generates digital output signals indicative of information encoded in said input RF signals," as required by the claim. Therefore, Thomson teaches this element.

> "demodulating using a plurality of demodulators said processed digitized signals"<sup>9</sup>

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

<sup>&</sup>lt;sup>8</sup> This corresponds to "a signal processor for processing said digital representation of said intermediate signals in accordance with said format of said input RF signal, said signal processor generating digital output signals indicative of information encoded in said input RF signal" in claim 1. The structural aspects of this element are addressed below.

48. Thomson discloses two different demodulators, each dedicated to processing digitized signals in a particular TV format (*i.e.*, analog or digital). As shown in Fig. 1, the digitized output signals of the adaptive filter 8 are input to "an FM demodulator (9) and a QPSK demodulator (12, 13)." (Ex. 1004 at 4:10–11). For at least these reasons, Thomson teaches this element.

"to generate baseband signals corresponding to said format of said input RF signals."<sup>10</sup>

49. The FM-demodulator demodulates the digital signals broadcast in the analog TV format (*Id.* at 1:27–28, 3:55), and QPSK demodulator demodulates digital signals broadcast in the digital TV format (*Id.* at 1: 10–13) to generate baseband signals (*i.e.*, Composite Video Baseband Signal ("CVBS"), "S<sub>mod1</sub>," "S<sub>mod2</sub>," and I/Q). These baseband signals do not include transmission modulation. For at least these reasons, Thomson teaches this element.

<sup>9</sup> This corresponds to "a plurality of demodulators, each coupled to receive output signals from said signal processor" in claim 1. The structural aspects of this element are addressed separately below.

<sup>10</sup> This element corresponds to "each of said demodulators for demodulating said digital output signals according to one of said formats of said input RF signal" of claim 1.

Cresta Ex 2020-33 Silicon v Cresta IPR2015-00626

#### Claim 19 is anticipated by Thomson

"19. The method of claim 17, wherein said processing said digital signals is performed in response to a select signal indicative of said format of said input RF signal."

50. Thomson discloses a "bandpass filter 8 . . . with an adaptively controlled bandwidth [that] selects the desired signal with a minimal remainder of the adjacent channel signals." (Ex. 1004 at 3:16–25). The processing of the "desired signal" is performed in response to the setting of the "TV standard" signal provided to the bandpass filter 8. (*Id.* at Fig. 1). For at least these reasons, Thomson teaches this element.

#### Claim 1 is anticipated by Thomson

51. As described above, Thomson expressly describes all of the functional elements recited in method claim 17. All of those functions find corresponding counterparts in apparatus claim 1. Accordingly, I will not repeat those arguments again here for claim 1. Instead, I will show that one additional functional element and all of the additional structure elements of claim 1 are also taught by Thomson.

• "a channel filter for receiving intermediate signals"

52. The channel filter of claim 1 is somewhat of an abstraction as it comprises "an anti-aliasing filter," "an analog-to-digital converter," "a signal processor," and "a plurality of demodulators," according to claim 1. (Ex. 1001 at 6:58–7:9). As described above, Thomson teaches such a configuration. More

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-34 Silicon v Cresta IPR2015-00626 importantly, Thomson itself discloses a filter that processes TV signals received in channels using two different formats: analog and digital and, therefore, qualifies as a "channel filter."

• "an anti-aliasing filter for filtering said intermediate signals"

53. As described above, Thomson discloses an automatic gain control amplifier 5 with an internal bandpass filter. (Thomson, Ex. 1004 at 3:9–16). Because the bandpass filter filters the input IF signal to the ADC 7 to avoid "any aliasing problems," it constitutes an "anti-aliasing filter," as recited in the claim. (*See* Ex. 1021 at 1220 (bandpass filter in Thomson (aka "Boie") "should help reduce aliasing, yes")). The use of anti-aliasing filters prior to an analog-to-digital converter was well known to a POSITA for the purpose of bandlimiting the signal being sampled. Thus, an anti-aliasing filter is taught by Thomson.

"an analog-to-digital converter for sampling said filtered intermediate signals"

54. Thomson discloses an "A/D converter 7." (Ex. 1001 at Fig. 1). The input to A/D 7 is the filtered intermediate signals output by bandpass filter AGC 5. (*Id.*). This structural element is taught by Thomson.

"a signal processor for processing digital representations of said intermediate signals in accordance with said format of said input RF signal [and] generating digital output signals indicative of information encoded in said input RF signal"

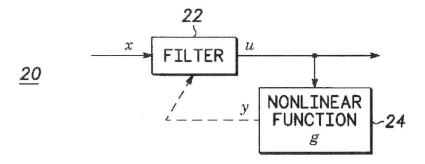

Cresta Ex 2020-35 Silicon v Cresta IPR2015-00626 55. Thomson teaches this element under the Board's construction of "signal processor." As discussed in detail above, Thomson discloses an adaptive bandpass filter that is a digital module that processes signals in the digital domain. Additional prior art makes clear that those skilled in the art would consider the adaptive filter shown and described in Thomson to be a "signal processor," as recited in claim 1. (*See, e.g.* U.S. Pat. Nos. 5,999,567 (Ex. 1012) and 6,263,222 (Exhibit 1013)). United States Patent Number 5,999,567, assigned to Motorola, for example, "shows a *signal processor 20* for processing a composite [television] signal." (Ex. 1012, 4:59–62). A schematic of the signal processor shows the following adaptive filter:

(*Id.* at Fig. 2). United States Patent No. 6,263,222, likewise teaches "wherein the signal processor comprises an adaptive filter." (Ex. 1013, 76:3–4). This demonstrates that an adaptive filter is considered a "signal processor" under the ordinary meaning of that term in the art.

56. The adaptive filter in Thomson also satisfies the functional limitation of this element. It is well known in the art, an "adaptive filter is a filter which can

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

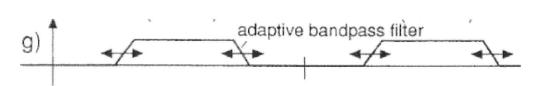

Cresta Ex 2020-36 Silicon v Cresta IPR2015-00626 change its characteristics by changing its filter coefficients." (U.S. Pat. No. 6,332,028); *see also* U.S. Pat. No. 6,142,942 ("Generally, an adaptive filter is a filter having a transfer function that can be adjusted, or changed, based on the sampled signal statistics, or signal features, associated with an input or output signal.")). The adaptive filter characteristic of the Thomson adaptive filter are graphically illustrated in the frequency map of Fig. 2(g) (reproduced below):

(Ex. 1004 at Fig. 2). As shown above, the upper and lower bounds of the Thomson filter vary or "adapt" according to the format of the input RF signal, as indicated by the "TV Standard" input to the filter, which is the only disclosed input other than the signal itself. (*See* Ex. 1004 at 3:16–19 ("bandpass filter 8 (see Fig. 2g) with an adaptively controlled bandwidth selects the desired signal"), Fig. 1). The bandpass filter executes one filter function if the RF input signal is in an analog TV format, as indicated by the status of the "TV standard" input, and another filter function if it is in a digital TV format. (*See* Ex. 1004 at Fig. 1 ("TV Standard" input to "filter 8")). Because the filter 8 receives the "digital representations of said intermediate signals" output by the A/D 7, and processes those digital representations "in accordance with said format of said input RF signal," as indicated by the TV standard input, and "generat[es] digital output signals

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

> Cresta Ex 2020-37 Silicon v Cresta IPR2015-00626

indicative of information encoded in said input RF signal," by adapting the filter to the frequency bounds of the particular TV format (*e.g.*, analog or digital), Thomson's bandpass filter 8 satisfies this function. Thomson therefore teaches this element.

57. The adaptive filter of Thomson satisfies the Board's construction of "signal processor." The Board construed "signal processor" to mean "a digital module that processes signals in the digital domain." (IPR 2014-000728, Paper No. 9 at 9). The bandpass filter 8 of Thomson is both a "digital module" and one that "processes signals in the digital domain." The Thomson bandpass filter is a digital module because it is a circuit that receives digital input signals that are output from the A/D 7. It processes those digital input signals in the digital domain (as opposed to the analog domain) to produce a bandlimited output signal. Accordingly, it satisfies the Board's definition of a "signal processor."

"a plurality of demodulators, each coupled to receive output signals from said signal processor, each of said demodulators for demodulating said digital output signals according to one of said formats of said input RF signal"

58. Thomson discloses a plurality of demodulators, each coupled to receive output signals from said signal processor. (Ex. 1004 at Fig. 1 showing FM-demodulator 9 and QPSK-demodulator (12, 13) connected in parallel to receive the output signals from the adaptive bandpass filter 8 (*i.e.*, "said signal processor")).

Cresta Ex 2020-38 Silicon v Cresta IPR2015-00626 As explained above, Thomson discloses that the "FM-demodulator (9)" is for demodulating the digital signals encoding information in the analog TV format and the "QPSK-demodulator (12, 13)" is for demodulating the digital signals encoding information in the digital TV format. (Ex. 1004 at 4:10–11). For at least these reasons, Thomson teaches this element.

"each of said demodulators generating video and audio baseband signals corresponding to said format of said input RF signal."

59. Thomson discloses this final element of claim 1. Thomson discloses a TV receiver that receives TV signals and expressly discloses that the TV signals include both audio and video. Thomson expressly discloses that "[t]he FM demodulator 9 converts the IF signal into the CVBS signal and the subcarrier modulated sound signals." (Ex. 1004 at 3:19–21). Thomson further discloses in the QPSK demodulation section, "synchronous demodulators 12, 13 for QPSK quadrature demodulation and low pass filters 14, 15 providing signal Q, I at outputs of circuit 4." (*Id.* at 2:41–44). One of ordinary skill in the art would understand that digital TV signals (such as MPEG) digitally encode the video and audio information in a single signal, and would know that the Q and I baseband signal components must carry both the video and audio information for the TV signals of Thomson to serve the expressly disclosed purpose of a digital TV receiver. Because MPEG encoding is performed on the video and audio data

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009 before transmission, it does not contain transmission modulation, MPEG encoded data is a baseband signal under the Board's construction of that term. For at least these reasons, Thomson teaches this element.

### Claim 10 is obvious over Thomson in view of Harris.

"10. The receiver of claim 1, wherein said signal processor applies one of a plurality of finite impulse response filters to said digital representation of said intermediate signal, each of said plurality of finite impulse response corresponding to a format of said input RF signal."

60. Thomson describes a digital adaptive filter with a filter function that corresponds to the unique frequency range of each format (*e.g.*, analog or digital TV). (Ex. 1004 at 3:16–18 ("bandpass filter 8 (Fig. 2g) with an adaptively controlled bandwidth selects the desired signal with a minimal remainder of adjacent channel signals.")). Harris discloses a reconfigurable, reprogrammable signal processor that implements a plurality of FIR filters, each corresponding to a particular operating mode. (Ex. 1005, p. 6 ("the digital receiver structure also offers flexibilities like programmable filtering")).

61. It would have been an obvious design choice to implement the signal processor of claim 1 as a plurality of finite impulse response filters. As described above, the use of FIR filters was well known to a POSITA. (*See, e.g.*, Exs. 1005 and 1006). A POSITA faced with the design of the adaptive filter in Thomson

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-40 Silicon v Cresta IPR2015-00626 would have two classes of digital filters from which to choose: finite impulse response (FIR) and infinite impulse response (IIR). The FIR implementation would be the obvious design choice in the Thomson application because it would produce "a linear phase, and only FIR filters can be designed to have linear phase," which is important in television applications such as Thomson. (Ex. 1006 at 21). Moreover, the '585 patent refers to a prior art specification teaching a linear FIR filter, namely a "filter response . . . as a raised root cosine with 0.114 roll-off." (Ex. 1001 at 5:32–37; *see also* Ex. 1016, Fig. 12, p. 58 ("linear phase raised cosine Nyquist filter")). FIR filters also are less sensitive to coefficient quantization and are thus generally more stable than IIR filters. For these reasons, a person of ordinary skill in the art would have been motivated to use well-known FIR filters as disclosed in Harris to implement the adaptive filter of Thomson, and the combination of Thomson in view of Harris renders this claim obvious.

- B. Ground 1: Claim 11 is obvious over Thomson in view of Harris, further in view of Grumman.

- 11. The receiver of claim 10, wherein said plurality of finite impulse response filters are stored in a memory, and

62. Claim 11 adds a well-known approach of implementing digital FIR filters, namely indexing a set of FIR filter coefficients stored in memory. Grumman describes the structure of "a complex Finite-Impulse-Response filter with adaptive weights for processing complex digital data having real and

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-41 Silicon v Cresta IPR2015-00626 imaginary input data portions." (Grumman, Ex. 1008, 3:31–34). The adaptive weights (coefficient data values) of the FIR filters "are stored in two memory storage banks for access by the filter or host processor," (*Id.* at 4:7–9), or are "stored in alternative memory storage banks." (*Id.* at 4:9–14). Thus, Grumman discloses the storage of two sets of coefficients, each set corresponding to a separate FIR filter. This two bank architecture allows the filter to operate with data present in one memory bank while the other memory bank "is being updated with the new set of coefficients." (Ex. 1008 at 11:25–29). Figs. 1a and 1b of Grumman are depicted below. The coefficients for the two FIR filters are stored in bank 0 and bank 1. The output of swap circuitry 38 controls access to bank 0 or bank 1. By outputting a "0," swap circuitry selects bank 0, else, by outputting a "1," swap circuitry selects bank 1. (*Id.* at Fig. 7c).

Cresta Ex 2020-42 Silicon v Cresta IPR2015-00626

(Ex. 1008 at Figs 1a and 1b). Because Grumman discloses storing coefficients for two FIR filters in memory, one set of coefficients for one FIR filter stored in bank 0 and another set of coefficients for another FIR filter stored in bank 1, this limitation is met by Grumman. (*See also id.* at Fig. 1b (banks 0 and 1)).

said signal processor indexes said memory to retrieve one of said plurality of finite impulse response filters.

63. Grumman discloses a signal processor that indexes memory to retrieve FIR filter coefficients via "weight swapping," which results in changing access of the adaptive weight data from one memory bank 24 to the other memory bank. (Ex. 1008, 9:10–15). Weight swapping circuitry performs the weight

Cresta Ex 2020-43 Silicon v Cresta IPR2015-00626

swapping function by providing "timing and control signals necessary to accomplish the weight swapping function in the real and imaginary coefficient/coefficient update memory banks 24 and 27." (Id. at 9:63–67). Weight swapping with a two-bank architecture provides efficiency because it allows one FIR filter to retrieve and operate with data present in one coefficient memory bank, while the alternative memory bank is being updated with a new set of coefficients. (Id. at 10:67–11:10). Just as the '585 patent indexes memory to retrieve a selected set of coefficients from one of a plurality of FIR filters, the signal processor of Grumman (e.g., the real processing circuitry 17 and imaginary processing circuitry 16) indexes memory by swapping between bank 0 and bank 1 to retrieve a selected set of adaptive weights corresponding to a unique FIR filter. (See id. at 9:10–15, Fig. 7c). "It is a further objective to provide a complex adaptive FIR filter that is able to do complex adaptive digital filtering without having to interrupt or stop the filtering process when the weight coefficients are being updated." (Ex. 1008 at 3:3–6). Thus, Grumman's FIR filter architecture is very efficient, especially in the context of minimizing any delays caused by selecting a different set of FIR coefficients by indexing memory.

64. A person of ordinary skill in the art would have been motivated to implement the FIR filter of Harris using the Grumman architecture. Because digital FIR filter processing requires operating on coefficient weights, digital FIR

filter processing requires both processor and memory resources. A natural design choice for a person of ordinary skill in the art would have been to store the set of coefficients of a plurality of FIR filters in memory using an index for easy and efficient access by a processor as taught by Grumman. Moreover, in addition to Grumman, Terrell teaches a FIR filter that selectively retrieves FIR filter coefficients from memory, including a look up table. The Grumman FIR filters permit processing of "complex digital signals more quickly and efficiently" where speed requirements would otherwise prohibit "commercially available FIR filter[s]." (Ex. 1008, 2:55–62). The Grumman FIR filter "architecture takes maximum advantage of the time available to do the required calculations." (Id. at 2:68–3:2). In short, storing FIR filter coefficients in memory as does Grumman, yields a plurality of FIR filters that that minimize delay when switching between different FIR filters. Accordingly, a POSITA would have been motivated to implement the adaptive filter of Thomas using the FIR filter disclosures of Harris and Grumman, especially in light of the ease and efficient approach of indexing memory storing a set of FIR filter coefficients. For at least these reasons, the combination of Thomson, Harris, and Grumman renders this claim obvious.

## C. Ground 1: Claim 12 is obvious over Thomson in view of Harris, further in view of Grumman.

12. The receiver of claim 10, wherein said signal processor comprises a first computing unit and a second computing unit,

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-45 Silicon v Cresta IPR2015-00626

65. Claim 12 is drawn to a signal processor that processes the real and imaginary parts of the finite impulse response in parallel. Such a claim is not novel or unobvious in light of Grumman. Grumman discloses a "FIR filter having an internal processing architecture that features two parallel data paths, one which filters the real data stream of the complex signal and another which filters the complex data stream." (Ex. 1008, 2:63-3:2). "The first data path includes a first plurality of adaptive weight circuits for multiplying the real input data by predetermined coefficients to generate a set of multiplication results." (Id. at 3:36– 39). "The second path includes a second plurality of adaptive weight circuits for multiplying the imaginary input data by predetermined coefficients to generate a set of multiplication results." (Id. at 3:41–44). Grumman further discloses in Fig. 2 "a 32 complex weight FIR filter 10 having a real processing circuit 17 and imaginary processing circuit 16." (Id. at 7:32-35). Thus, Grumman discloses a first computing unit (processing circuit 17) and a second computing unit (processing circuit 16).

> said first computing unit processing a real part of said finite impulse response filter operation

66. Grumman discloses "a complex adaptive FIR filter having an internal processing architecture that features two parallel data paths, one which filters the real data stream of the complex signal and another which filters the complex data stream." (Ex. 1008, 2:63–3:2). The first data path "filters the real data stream,"

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-46 Silicon v Cresta IPR2015-00626 (*Id.* at 2:66), and "process[es] the real input data portion of the input complex data" (*Id.* at 3:34–36). The real processing circuit 17 processes the real portion of the FIR. (*Id.* at 8:1–6, 6:64–7:10, Fig. 2, 5:44–56). Thus, Grumman discloses a first computing unit that processes the real part of the FIR.

while said second computing unit processing an imaginary part of said finite impulse response filter operation.

67. Grumman discloses "a complex adaptive FIR filter having an internal processing architecture that features two parallel data paths, one which filters the real data stream of the complex signal and another which filters the complex data stream." (Ex. 1008, 2:63–3:2). The second data path "filters the imaginary data stream," (*Id.* at 5:7–11), and "process[es] the imaginary input data portion of the input complex data" (*Id.* at 3:31–34). The imaginary processing circuit 16 processes the imaginary portion of the FIR. (*Id.* at 8:6–8, 7:1–10, Fig. 2). Thus, Grumman discloses a second computing unit that processes the imaginary part of the FIR filter operation.

68. A person of ordinary skill in the art would have been motivated to implement the adaptive filter in Thomas according to the highly efficient real and imaginary parallel implementation of Grumman. As discussed with respect to claim 11 a person of ordinary skill in the art would have been motivated to combine Thomson, Harris, and Grumman. Grumman's adaptive FIR filter architecture is very efficient, especially in the context of minimizing any delays

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009 caused by selecting a different set of FIR coefficients by indexing memory. (See Ex. 1008, claims 10, 11 (showing that a POSITA would have been motivated to combine Grumman with Thomson)). Grumman discloses "a complex adaptive FIR filter that is able to do complex adaptive digital filtering without having to interrupt or stop the filtering process when the weight coefficients are being updated." (Ex. 1008 at 3:3–6). The Grumman FIR filters permit processing of "complex digital signals more quickly and efficiently" where speed requirements would otherwise prohibit "commercially available FIR filter[s]." (Id. at 2:55–62). The Grumman FIR filter "architecture takes maximum advantage of the time available to do the required calculations." Because of the computational efficiency of Grumman in implementing adaptive FIR filters, a POSITA would have been motivated to implement the adaptive filter of Thomson using the FIR filter disclosures of Harris and Grumman. For at least these reasons, the combination of Thomson, Harris, and Grumman renders this claim obvious.

## **D.** Ground 2: Claim 13 is obvious over Thomson in view of Harris, further in view of Zenith.

13. The receiver of claim 10, wherein said channel filter further comprises a standard selection circuit coupled to said signal processor, said standard selection circuit generating a select signal indicative of a format of said input RF signal and

69. Thomson discloses a "signal processor" that has a "standard selection" input. This "standard selection" signal provides an explicit suggestion

Cresta Ex 2020-48 Silicon v Cresta IPR2015-00626 to a POSITA that a circuit should be used to generate this signal. Because the construction of such a circuit was well known to those skilled in the art, however, Thomson did not explicitly teach how to construct that circuit. Nonetheless, Zenith provides an exemplary embodiment of a "selection circuit" that a POSITA would have been motivated to use to generate the "select signal" in Thomson.

70. Zenith "relates generally to television receivers and specifically to television receivers that are capable of receiving both analog and digital signals." (Ex. 1011, 1:7–10). The output of the tuner is selectively coupled to either an analog demodulator or a digital demodulator. (*Id.* at Figs. 1–3). The selective coupling of the tuner to either the analog or digital demodulator is determined by the type of signal (analog or digital) received. (*Id.* at 3:13–15 ("As in Fig. 1 embodiment, microprocessor 22 controls the operation of switch 42 in accordance with the type of signal (analog or digital) that is received.")).

Cresta Ex 2020-49 Silicon v Cresta IPR2015-00626

71. Zenith discloses the actual details of generating a select signal based on the format of the incoming RF signal as shown in Fig. 2. If "the presence of syncs corresponding to a demodulated analog type signal," is detected by sync detector 20, "microprocessor 22 routes the IF signal from tuner 12 to analog demodulator 16." (Ex. 1011, 2:38–41). Otherwise, "[i]n the absence of syncs corresponding to a demodulated analog type signal, microprocessor causes switch 14 . . . to couple the IF signal to digital demodulator 18." (*Id.* at 2:42–45). Detecting syncs in the demodulated analog television signal would include detecting one or more of the horizontal or vertical sync signals. Since these sync signals are uniquely tied to a specific television standard, sync detection results in the identification of a specific television standard. Accordingly, the Zenith microprocessor is a standard selection circuit that generates a select signal (output

Cresta Ex 2020-50 Silicon v Cresta IPR2015-00626 of microprocessor 22) that is indicative of the format (analog or digital) of the input RF signal and is coupled to the signal processor when combined with Thomson to generate the select signal in Thomson.

"said signal processor selecting a finite impulse response filter in response to said select signal.

72. As described in detail above, Thomson describes an adaptive bandpass filter that selects a particular filter in response to the "TV standard" input signal. Harris discloses a reconfigurable, reprogrammable signal processor that implements a plurality of FIR filters, each corresponding to a particular operating mode. (Ex. 1005, p. 6 ("the digital receiver structure also offers flexibilities like programmable filtering")). Accordingly, Harris discloses a signal processor selecting a finite impulse response in response to the select signal of Thomson.

73. As discussed with respect to claim 10, a person of ordinary skill in the art would have been motivated to combine Thomas and Harris to implement the adaptive filter of Thomas with the well-known FIR filters of Harris. I incorporate that discussion herein and thus will not repeat it. In that case, the bandpass filter in Thomson would select the particular FIR filter function that corresponds to the incoming RF signal format, as indicated by the "TV standard" input.

74. A person of ordinary skill in the art would have been further motivated to combine Zenith with Harris and Thomson to implement a standard selection circuit as disclosed in Zenith to output the TV select signal of Thomson.

Cresta Ex 2020-51 Silicon v Cresta IPR2015-00626

Both Zenith and Thomson are directed toward a multistandard tuner capable of receiving both analog and digital television signals. (See Ex. 1011, 1:62-64 (an "object of the invention is to provide an improved low cost method of processing digital and analog television signals using a single tuner"); Ex. 1004, 1:29–33 ("It is an object of the invention to provide a broadcast receiver of the kind described which is suited for digital and analog input signals and using a common A/D converter only for analog and digital transmission via satellite.")). A receiver that can receive both analog and digital televisions signals must be able to identify the format or standard of the received signal for correct downstream processing. Fig. 2 of Zenith illustrates that the input to the analog or digital demodulator is controlled by a microprocessor, based on the format of the received RF signal. (Ex. 1001, Fig. 2, 3:13–15). Fig. 1 of Thomson shows an adaptive filter 8 controlled by an input labeled "TV standard." (Thomson at Fig. 1). Just as Thomson needs to be aware of the TV standard, and thus the format of the input RF signal, for correct processing of the signal through the signal processor (band pass filter 8) (Ex. 1004, Fig. 1 (TV standard input controls band pass filter 8), 3:16–19 ("The following bandpass filter 8 (see Fig. 2g) with an adaptively controlled bandwidth selects the desired signal with minimal remainder of the adjacent channel signals.")), so does Zenith need to be aware of the standard and thus the format of the input RF signal (Ex. 1011, Fig. 2 (sync detector controlling microprocessor); 3:13–15

Silicon Labs v. Cresta Technology Silabs IPR Exhibit 1009

Cresta Ex 2020-52 Silicon v Cresta IPR2015-00626 ("microprocessor 22 controls the operation of switch 42 in accordance with the type of signal (analog or digital) that is received")). Because Zenith and Thomson are directed to the same problem, a multistandard tuner capable of receiving and processing both digital and analog signals, each having different formats, a POSITA would naturally look to the selection circuit in Zenith to generate the select signal in Thomson in light of the explicit suggestion to use a standard selection circuit in Thomson.

75. Accordingly, Zenith and Harris would have been an obvious combination to a POSITA. Such an obvious combination could have been fashioned without undue experimentation by a POSITA because both the microprocessor and the sync detect circuit in Zenith were well-known circuits at the time. For at least these reasons, claim 13 is obvious over Thomson, Harris, and Zenith.

# E. Ground 2: Claims 15 and 20 are obvious over Thomson in view of Harris, further in view of Zenith.

- 15. The receiver of claim 13, wherein said standard select circuit generates said select signal by detecting carrier signals identifying one of said formats of said input RF signals.

- 20. The method of claim 19, further comprising: generating said select signal by detecting carrier signals in said input RF signal identifying said format of said input RF signal.

Cresta Ex 2020-53 Silicon v Cresta IPR2015-00626 76. Apparatus claim 15 relates to a "standard select circuit [that] generates said select signal by detecting carrier signals identifying one of said formats of said input RF signals," whereas method 20 recites the method of "generating said select signal by detecting carrier signals in said input RF signal identifying said format of said input RF signal." (Ex. 1001, claims 15, 20). Because both claims 15 and 20 concern the same general limitation, albeit in a different form, claims 15 and 20 will be analyzed together.

77. The standard selection circuit in the '585 patent automatically provides "an auto-detection capability in TV receiver 50." (Ex. 1001, 5:8–12). One disclosed embodiment of doing so is to detect "in the baseband signals, the presence or absence of carrier signals which uniquely identify the television standards." (Ex. 1001 at 5:12–15). The sync detector 20 and microprocessor 22 in Zenith operate identically. In Zenith "the presence of syncs associated with a demodulated analog signal is communicated to the microprocessor.") (Ex. 1011, 3:15–18). Just as in the '585 patent, by identifying syncs in the demodulated analog signal, Zenith identifies carrier signals in the input RF signal. (*Id.* at 3:15–18). Moreover, the detected carrier signals. (*Id.* at 3:12–15). Accordingly, the output select signal of microprocessor 22 is generated by detecting the syncs, which are carrier signals in the input RF signal identifying the type of format of the

Cresta Ex 2020-54 Silicon v Cresta IPR2015-00626 input RF signal. Thus, the select signal in Zenith (output of microprocessor 22) is generated by sync detect 20, which detects carrier signals in the input RF signal identifying said format of said input RF signal.