(19) Japan Patent Office (JP)

(11) Japanese Unexamined Patent Application Publication Number

## (12) Japanese Unexamined Patent Application Publication (A)

#### H4-63437

| (51) Int. Cl. <sup>5</sup> | Identification codes | JPO file number          | (43) Publication date 28 Feb 1992         |

|----------------------------|----------------------|--------------------------|-------------------------------------------|

| H011 21/336                |                      |                          |                                           |

| 21/027                     |                      |                          |                                           |

| 29/784                     |                      |                          |                                           |

|                            |                      | 8422-4M H01L 29/78       | 301 Z                                     |

|                            |                      | 7352-4M 21/30            | 301 Z                                     |

|                            |                      | 7352-4M                  | 301 P                                     |

|                            |                      | Examination request: Non | e Number of claims: 1 (Total of 12 pages) |

(54) Title of the invention SEMICONDUCTOR INTEGRATED CIRCUIT DEVICE

(21) Japanese Patent Application H2-177022(22) Date of Application July 2, 1990

(72) Inventor Michihiro Yamada c/o Mitsubishi Electric Co., Ltd. LSI Research Lab

4-1 Mizuhara, Itami-shi, Hyogo-ken

(71) Applicant Mitsubishi Electric Co., Ltd. 2-2-3 Marunouchi, Chiyoda-ku, Tokyo-to

(74) Agent Masuo Oiwa, patent attorney and 2 others

#### **SPECIFICATION**

#### 1. Title of the Invention

Semiconductor Integrated Circuit Device

#### 2. Claims

(1) A semiconductor integrated circuit device in which a plurality of field effect transistors having one or a plurality of gate electrodes are formed in a mixed manner, wherein

dummy patterns are formed in locations outside the gate electrodes of the field effect transistors a predetermined distance from the gate electrodes, positioned parallel thereto, and made from an identical material.

3. Detailed Description of the Invention

[Industrial Field of Use]

The present invention relates to a semiconductor integrated circuit device in which a plurality of field effect transistors such as MOS-FETs are formed in a mixed manner, and more particularly relates to a technology for making channel lengths in the mixed-formation field effect transistors uniform.

[Prior Art]

The best-known conventional example of this type of semiconductor integrated circuit device is a MOS integrated circuit configured by a plurality of fine MOS-FETs. As such, in the description of the present invention, the semiconductor integrated circuit device is a MOS integrated circuit device, and the MOS integrated circuit device is configured by a plurality of n-channel MOS-FETs.

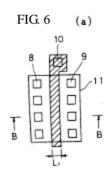

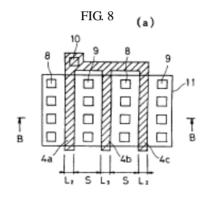

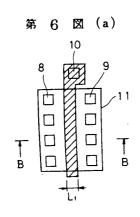

MOS-FETs come in two types, a single gate electrode type as shown in FIG. 6(a) and (b) which is provided with one gate electrode and has a short channel length, and a multiple gate electrode type as shown in FIG. 8(a) and (b) which is provided with a plurality of gate electrodes and has a long channel length. Normally in a general MOS integrated circuit device MOS-FETs of the single gate electrode type and multiple gate electrode type are formed on one chip in a mixed manner. Accordingly, in the following description, a single gate electrode MOS-FET is described first and then a multiple gate electrode type is described.

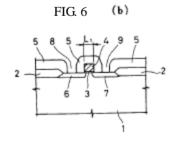

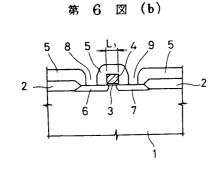

FIG. 6(a) is a plan view showing a schematic structure of a single gate electrode n-channel type MOS-FET in the middle of being fabricated, and FIG. 6(b) is a cross-sectional view showing a sectional structure along line B-B in FIG. 6(a). Reference numeral 1 in these drawings is a p-type silicon substrate, 2 is a device separation insulation film, 3 is a gate insulation film covering a MOS-FET channel, 4 is a gate electrode thereof, and 5 is an interlayer insulation film covering the device separation insulation film 2 and the gate electrode 4. Reference numerals 6 and 7 are a source and drain region of the MOS-FET which are n<sup>+</sup>-type. Electrical connection of the source and drain regions 6 and 7 is made via contact holes 8 and 9 formed in the interlayer insulation film 5. Reference numeral 10 is a contact hole for making an electrical connection of the gate electrode 4, 11 is a field pattern showing boundaries of the device separation insulation film 2, and L<sub>1</sub> shows a pattern width of the gate electrode 4 which determines the channel length of the MOS-FET.

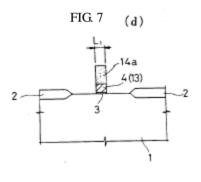

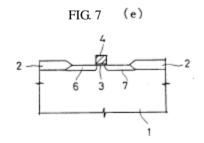

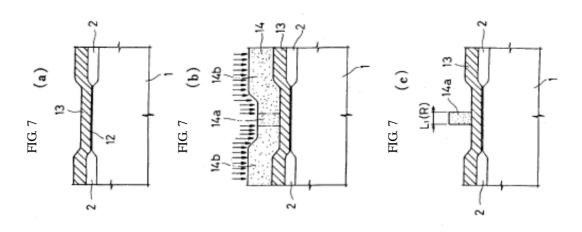

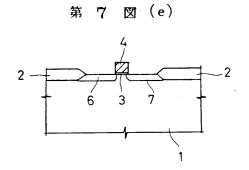

The order of fabrication of this MOS-FET is described based on cross-sectional views of steps shown in FIG. 7(a) to (e).

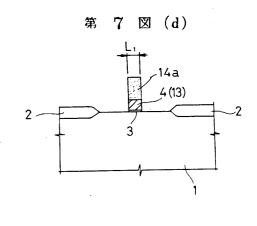

To start, an insulation film 12, which will serve as the device separation insulation film 2 and the gate insulation film 3, is formed on a surface of the silicon substrate 1, and then a polysilicon film 13 is formed covering the entire surface thereof (see FIG. 7(a)). Next, a positive (or negative type) photoresist is applied, covering the entire surface of the polysilicon film 13. Only an unexposable region 14a of a photoresist film 14 needed to form the gate electrode 4 is masked. Light is shined on an exposure region 14b of the photoresist film 14 which is not masked, using a reduced projection exposure device or the like, to expose that region (see FIG. 7(b)). After exposure is finished developing is performed, and if the photoresist film 14 is positive, only the unexposable region 14a is left on the polysilicon film 13 (see FIG. 7(c)). The pattern width  $L_1$  (R) of the unexposable region 14a is a major factor in determining the channel length of the MOS-FET.

Next, anisotropic etching, such as reactive ion etching, is performed, using the remaining unexposable region 14a as a mask, to remove unneeded portions of the polysilicon film 13. The polysilicon film 13 covered by the unexposable region 14a is partially left behind, thereby forming the gate electrode 4 (see FIG. 7(d)). The pattern width  $L_1$  of the gate electrode 4 determines the channel length of the MOS-FET. Next, an  $n^+$ -type impurity is implanted using the unexposable region 14a as a mask, and then unneeded portions of the unexposable region 14a and the insulation film 12 are removed. The  $n^+$ -type impurity is thermally diffused to form the  $n^+$ -type source and drain regions 6 and 7 inside the silicon substrate 1 located on either side of the gate electrode 4 (see FIG. 7(e)). After forming the interlayer insulation film 5, the contact holes 8

to 10 are formed in the interlayer insulation film 5, thereby completing the single gate electrode n-channel MOS-FET shows in FIG. 6(a) and (b).

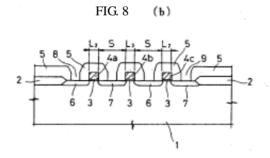

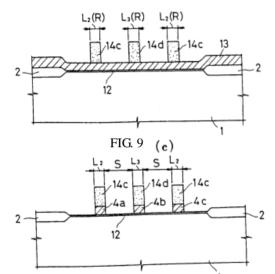

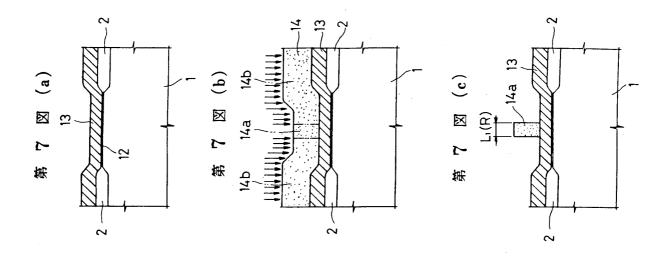

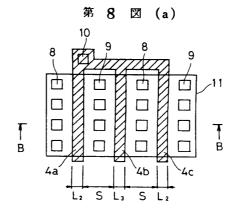

Now turning to FIG 8(a) and (b), a multiple gate electrode n-channel MOS-FET used to obtain large channel lengths is described.

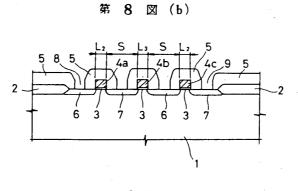

FIG. 8(a) is a plan view showing a schematic structure of a multiple gate electrode n-channel MOS-FET in the midst of being fabricated, and FIG. 8(b) is cross-sectional view showing a sectional structure along line B-B in FIG. 8(a). As is clear from the drawings, the difference between a multiple gate electrode MOS-FET and a single gate electrode MOS-FET is that the gate electrode 4, which is a single electrode in the former, is divided into multiple parts (three in the drawings) in the latter. Therefore, parts in FIG. 8(a) and (b), which are identical to or correspond to parts in FIG. 6(a) and (b), are given the same reference numerals and detailed descriptions thereof are omitted here.

Specifically, reference numerals 4a to 4c in FIG. 8(a) and (b) are gate electrodes formed a predetermined distance S apart from one another, and  $L_2$  is pattern width of the gate electrodes 4a and 4c located on either side of the MOS-FET.  $L_3$  is a pattern width of the gate electrode 4b which is located in the middle. Note that the separation distance S between the gate electrodes 4a to 4c is set when designing the MOS-FET. For example, the separation distance S is 1.1  $\mu m$  if the diameter of the contact holes 8 and 9 is 0.5  $\mu m$  and the distance between ends thereof and ends of the gate electrodes 4a to 4c is 0.3  $\mu m$ .

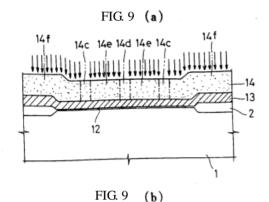

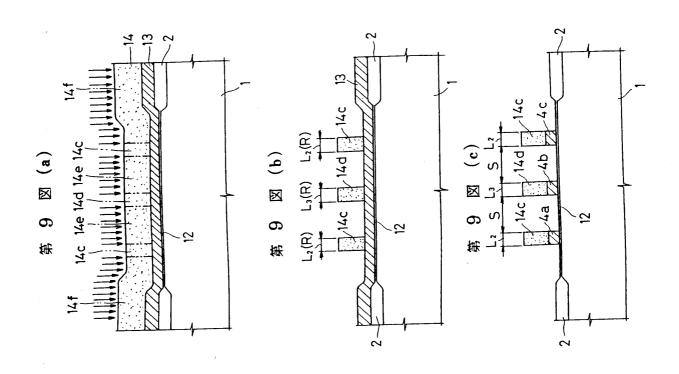

Next, a procedure for fabricating this multiple gate electrode n-channel MOS-FET is described. The fabricating procedure of this MOS-FET is the same as the procedure for fabricating the single gate electrode type described with reference to FIG. 7(a) to (e), so only those steps which require a description shall be discussed below with reference to the cross-sectional view step views shown in FIG. 9(a) to (c) which correspond to FIG. 7(b) to (d).

To start, using the same procedure described with reference to FIG. 7(a), the photoresist film 14 is formed over the polysilicon film 13 which covers the device separation insulation film 2 and the insulation film 12. Unexposable regions 14c and 14d of the photoresist film 14, which are needed to form the gate electrodes 4a and 4c which are separated from one another by the predetermined distance S, are masked, after which exposure regions 14e and 14f of the photoresist film 14 are exposed by being irradiated with light using a reduced projection exposure device or the like (see FIG. 9(a)).

Once exposure is done developing is performed, and if the photoresist film 14 is positive, the unexposable regions 14c and 14d remain on the polysilicon film 13 (see FIG. 9(b)). The pattern widths  $L_2$  (R) and  $L_3$  (R) of the unexposable regions 14c and 14d are major factors in determining the channel length of the MOS-FET.

Thereafter, anisotropic etching is performed, with the remaining unexposable regions 14c and 14d masked,

thereby removing unneeded portions of the polysilicon film 13 and forming the gate electrodes 4a to 4c separated from one another by the predetermined distance S (see FIG. 9(c)). The pattern widths  $L_2$  and  $L_3$  of the gate electrodes 4a to 4c determine the MOS-FET channel length. The same process as described in FIG. 7(e) is then performed, and the  $n^+$ -type source and drain regions 6 and 7 are formed in the silicon substrate 1, thus completing the multiple gate electrode n-channel MOS-FET shown in FIG. 8(a) and (b). [Problem to be Solved by the Invention]

With general MOS integrated circuit devices, the single electrode and multiple electrode type MOS-FETs described above are formed on the same chip in a mixed manner. However, if the patterning when fabricating these MOS-FETs is very fine, at 0.3 to 0.5  $\mu m$ , even if the pattern widths  $L_1$  to  $L_3$  of the gate electrodes 4 and 4a to 4c are set so as to be uniform and even if the photoresist film 14 is exposed using light of one wavelength, the problem sometimes occurs that the channel lengths of the MOS-FETs thus obtained are not uniform and vary.

This problem is thought to occur due to the following factors. First, in a single gate electrode MOS-FET, as shown in FIG. 7(b) and (c), the exposed region 14b of the photoresist film 14 has a satisfactory length relative to the wavelength of the light used for exposing the photoresist film 14 (e.g., 0.248 µm with excimer light), so the photosensitivity is satisfactory. The pattern width  $L_1$  (R) of the unexposable region 14a obtained by developing tends to be narrow as a result. However, in a multiple gate electrode MOS-FET, as shown in FIG. 9(a) and (b), the length of the exposed region 14f is sufficient relative to the wavelength of the light, but nevertheless the length of the exposed region 14e between the unexposable regions 14c and 14d is only double to 10 times the wavelength of the light (i.e., if the separation distance S, or the length of the exposed region 14e is set to be 1.1  $\mu$ m, then 1.1/0.248 = 4.4 times), meaning the exposed region 14e is affected by refraction or reflection of the light, making the photosensitivity thereof insufficient. Accordingly, the pattern width L<sub>2</sub> (R) of the unexposable region 14d sandwiched by the exposed region 14e tends to be thicker, and the pattern width L<sub>3</sub> (R) of the unexposable region 14c sandwiched between the exposed region 14e and the exposed region 14f tends to be the average thickness thereof due to a balance between tendencies to be thinner and thicker.

Therefore, even though in the original design the pattern widths  $L_1$  to  $L_3$  of the gate electrodes 4 and 4a to 4c of the MOS-FET formed in a mixed manner are set so as to be uniform, once the wafer process is finished the pattern widths  $L_1$  to  $L_3$  of the gate electrodes 4 and 4a to 4c which determine the channel lengths of the single gate electrode and multiple gate electrode MOS-FETS wind up being different, which has been a problem. Moreover, in the multiple gate electrode MOS-FET, the pattern widths  $L_2$  and  $L_3$  of the gate electrodes 4a and 4c, which are located on either side, and the gate electrode 4b located in the middle have been different.

The present invention was devised in light of this problem and has as an object to provide a semiconductor integrated circuit device whereby channel lengths of field effect transistors formed in a mixed manner can be made uniform and variation thereamong can be minimized.

[Means for Solving the Problem]

To achieve this object, the present invention is a semiconductor integrated circuit device in which a plurality of field effect transistors having one or a plurality of gate electrodes are formed in a mixed manner, wherein dummy patterns are formed in locations outside the gate electrodes of the field effect transistors a predetermined distance from the gate electrodes, positioned parallel thereto, and made from an identical material.

[Operation]

With this configuration, irrespective of whether the field effect transistors formed in a mixed manner on a semiconductor integrated circuit device are single gate electrode types or multiple gate electrode types, the gate electrodes are sandwiched by dummy patterns which are positioned parallel, separated from one another by a predetermined distance. The exposure conditions when fabricating these gate electrodes are thus uniform. [Embodiments]

Embodiments of the present invention are described below with reference to the drawings. Note that in the embodiments the semiconductor integrated circuit device is a MOS integrated circuit device comprising a plurality of n-channel MOS-FETs.

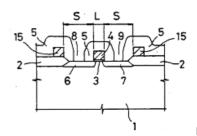

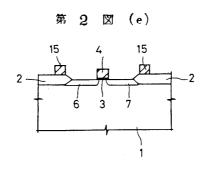

The MOS integrated circuit device in the embodiments is configured by a plurality of single gate electrode and multiple gate electrode n-channel MOS-FETs which are formed in a mixed manner on one chip. In the following description, first a configuration and fabrication procedure for the single gate electrode MOS-FETs is described with reference to FIG. 1(a) and (b) and FIG. 2(a) to (e), after which a configuration and fabrication procedure for multiple gate electrode MOS-FETs is described with reference to FIG. 4(a) and (b) and FIG. 5(a) to (c). Note that all MOS-FETs related to the present embodiment are fundamentally the same as the prior art examples in FIG. 6(a) and (b) and FIG. 8(a) and (b) aside from the dummy patterns described below being provided, so portions and parts which are identical or corresponding are given the same reference numerals.

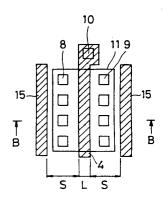

FIG. 1(a) is a plan view showing a schematic structure of a single gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 1(b) is a cross-sectional view showing a section structure along line B-B in FIG. 1(a). Reference numeral 1 in these drawings is a p-type silicon substrate, 2 is a device separation insulation film, 3 is a gate insulation film covering a MOS-FET channel, and 4 is a gate electrode comprising polysilicon or the like. Dummy patterns 15 are formed on the device separation insulation film 2 outside the gate electrode 4, separated therefrom by a predetermined distance S, positioned parallel thereto, and made from an identical material as the gate electrode 4.

Note that the dummy patterns 15 are formed electrically separated from the gate electrode 4, and the separation distance S from the gate electrode 4 is identical to or substantially equal to the separation distance S between gate electrodes 4a to 4c in a multiple gate electrode MOS-FET of the prior art.

Reference numeral 5 in the drawings is an interlayer insulation film 2 covering the gate electrode 4 and the dummy patterns 15, and 6 and 7 are n<sup>+</sup>-type source and drain regions of the MOS\_FET. Electrical connection of the source and drain regions 6 and 7 is made via contact holes 8 and 9 formed in the interlayer insulation film 5. Reference numeral 10 is a contact hole for electrical connection with the gate electrode 4, and 11 is a field pattern showing boundaries in the device separation insulation film 2. L is a pattern width of the gate electrode 4 which determines a channel length of the MOS-FET.

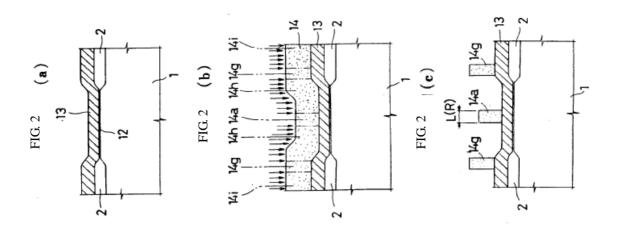

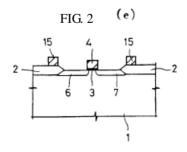

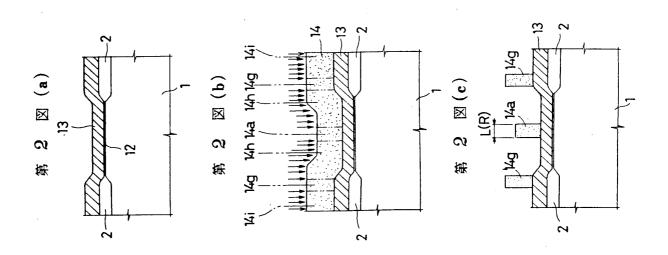

A fabrication procedure for this MOS-FET is described with reference to cross-sectional step views shown in FIG. 2(a) to (e).

To start, an insulation film 12 that will serve as the device separation insulation film 2 and the gate insulation film 3 is formed on a surface of the silicon substrate 1, and then a polysilicon film 13 is formed over the entire surface thereof (see FIG. 2(a)). Next, a positive (or negative) photoresist is applied to cover the entire polysilicon film 13, and only unexposable regions 14a and 14g of a photoresist film 14which are needed to form the gate electrode 4 and the dummy patterns 15 which are separated from one another by the predetermined distance S are masked. Exposed regions 14h and 14i, which have not been masked, of the photoresist film 14 are exposed by being irradiated with light with a reduced projection exposure device or the like (see FIG. 2(b)). After exposure is finished, developing is done, and if the photoresist film 14 is positive, the unexposable region 14a and the unexposable region 14g having the pattern width L (R) are left on the polysilicon film 13 (see FIG. 2(c)). Note that exposure of the photoresist 14 is done by light here, but exposure can also be done using x-rays, electron beams, or the like.

Next, anisotropic etching, e.g., reactive ion etching, with the remaining unexposable regions 14a and 14g masked, is performed, thereby removing unneeded portions of the polysilicon film 13, thereby causing only those parts of the polysilicon film 13 covered by the unexposable regions 14a and 14g to remain and forming the gate electrode 4 and the dummy patterns 15 with the pattern width L (see FIG. 2(d)). Next, an n<sup>+</sup>-type impurity is implanted, using the unexposable regions 14a and 14g as a mask, unneeded parts of the unexposable regions 14a and 14g and the insulation film 12 are removed, and the n<sup>+</sup>-type impurity is thermally diffused, thereby forming the n<sup>+</sup>-type source and drain regions 6 and 7 inside the silicon substrate 1 located on either side of the gate electrode 4 (see FIG. 2(e)). After forming the interlayer insulation film 5, contact holes 8 to 10 are formed in the interlayer insulation film 5, thereby completing the single gate electrode n-channel MOS-FET shows in FIG. 1(a) and (b). The dummy patterns 15 which are formed outside the gate electrode 4 of the MOS-FET, are positioned parallel thereto and the predetermined distance S therefrom.

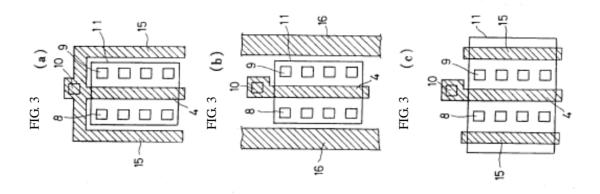

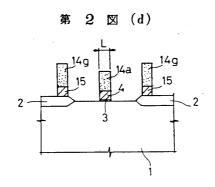

Note that in FIG. 1(a) and (b) the dummy patterns 15 are electrically separated from the gate electrode 4 and are formed on the device separation insulation film 2, but this is not a limitation. For example, as shown in FIG. 3(a), the dummy patterns 15 can be connected and unified with the gate electrode 4, or another wiring pattern 16 configuring a MOS integrated circuit device can be used as the dummy patterns 15 as shown in FIG. 3(b). Moreover, as shown in FIG. 3(c), the dummy patterns 15 can also be configured as dummy gate electrodes having the exact same configuration as the gate electrode 4.

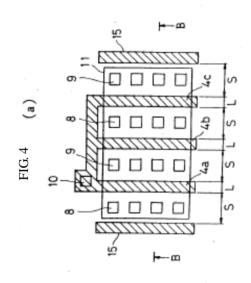

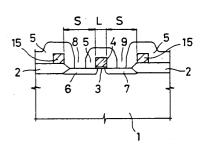

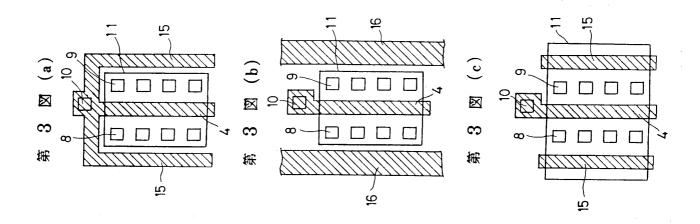

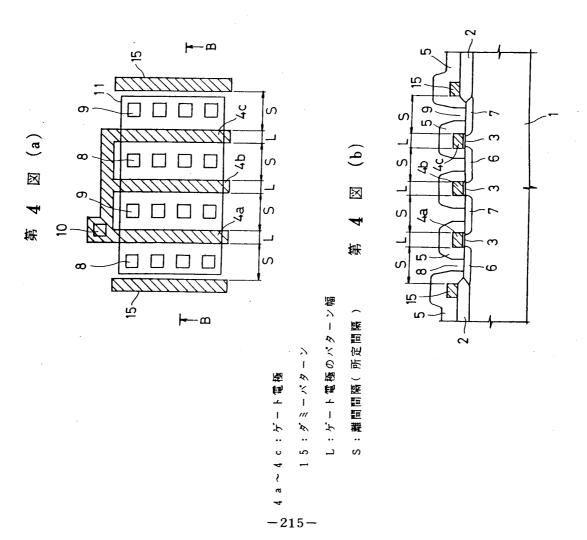

Now turning to FIG. 4(a) and (b), a multiple gate electrode n-channel MOS-FET is described.

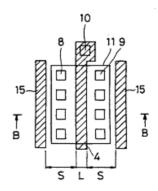

FIG. 4(a) is a plan view showing a schematic structure of a multiple gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 4(b) is a cross-sectional view showing a sectional structure along line B-B in FIG. 4(a). Note that basic configurations of the multiple gate electrode MOS-FET and the single gate electrode MOS-FET are the same, so parts in FIG. 4(a) and (b) which are identical or corresponding to parts in FIG. 1(a) and (b) are given the same reference numeral, and a detailed description thereof is omitted.

Specifically, in this multiple gate electrode MOS-FET, gate electrodes 4a to 4c comprising polysilicon are formed a predetermined distance S apart from one another, as shown in FIG. 4(a) and (b). Dummy patterns 15 are formed on the device separation insulation film 2 outside the gate electrodes 4a to 4c, separated by the predetermined distance S from the gate electrodes 4a and 4c which are located at either side, positioned parallel thereto, and made from the same material, namely polysilicon or the like. Note that the separation distance S between the gate electrode 4 and the dummy patterns 15 is set so as to be identical to or substantially equal to the separation distance S between the gate electrodes 4a to 4c.

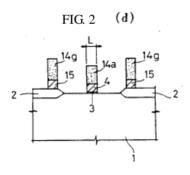

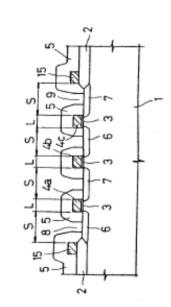

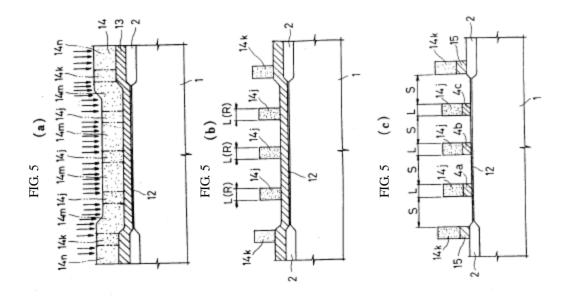

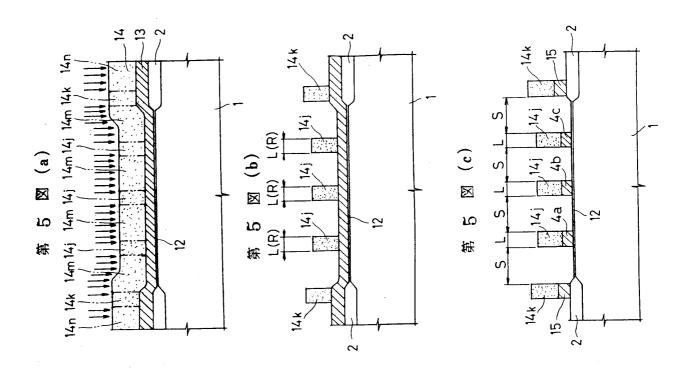

A procedure for fabricating this multiple gate electrode n-channel MOS-FET is described next. Note that the procedure for fabricating this MOS-FET is basically the same as that for the single gate electrode type shown in FIG. 2(a) to (e), so only those steps which are different are described below, with reference to the cross-sectional step view shown in FIG. 5(a) to (c), which corresponds to FIG. 2(b) to (d).

To start, the photoresist film 14 is formed on the polysilicon film 13 that covers the device separation insulation film 2 and the insulation film 12 using the same procedure as was described with reference to FIG. 2(a). Unexposable regions 14j and 14k in the photoresist film 14, which are needed to form the gate electrodes 4a to 4c and the dummy patterns 15, which are separated from one another by the predetermined distance S, are masked, and

exposed regions 14m and 14n in the photoresist film 14. which are not masked, are exposed by being irradiated with light by a reduced projection exposure device or the like (see FIG. 5(a)).

After exposure is finished, developing is done, and if the photoresist film 14 is positive, the unexposable regions 14j and 14k are left on the polysilicon film 13 (see FIG. 5(b)). The pattern width L (R) of the unexposable region 14j is a major factor in determining the channel length of the MOS-FET.

When unneeded portions of the polysilicon film 13 are removed by anisotropic etching with the remaining unexposable regions 14j and 14k masked, the gate electrodes 4a to 4c, separated from one another by the predetermined distance S, and the dummy patterns 15 are formed (see FIG. 5(c)). The MOS-FET channel length is determined by the pattern width L of the gate electrodes 4a to 4c. The same process is performed as was described with reference to FIG. 2(e) to form the n<sup>+</sup>-type source and drain regions 6 and 7 in the silicon substrate 1, thereby completing the multiple gate electrode n-channel MOS-FET shown in FIG. 4(a) and (b). The dummy patterns 15 are formed outside the gate electrodes 4a to 4c of the MOS-FET, separated therefrom by the predetermined distance S and positioned parallel thereto.

The single gate electrode and multiple gate electrode MOS-FETs thus described are formed on one chip in a mixed manner, and the dummy patterns 15 are formed parallel outside the gate electrodes 4 and 4a to 4c, separated therefrom by the predetermined distance S, meaning the gate electrodes 4 and 4a to 4c are sandwiched between the dummy patterns 15.

[Effects of the Invention]

As described above, with the semiconductor integrated circuit device according to the present invention, irrespective of whether the field effect transistors formed in a mixed manner thereon are single gate electrode types or multiple gate electrode types, the gate electrodes are sandwiched by dummy patterns which are positioned parallel thereto and separated from one another by a predetermined distance. The exposure conditions when fabricating these gate electrodes are thus uniform, and the pattern width between the gate electrodes thus obtained are substrate uniform. As a result, the outstanding effect can be provided of the channel lengths of the field-effect transistors formed in a mixed manner being able to be made uniform, and variation thereamong being able to be minimized.

#### 4. Brief Description of the Drawings

FIGs. 1 to 5 relate to embodiments of the present invention. FIG. 1(a) is a plan view showing a schematic structure of a single gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 1(b) is a cross-sectional view showing a section structure along line B-B in FIG. 1(a). FIG. 2(a) to (e) is a cross-sectional step view showing a fabrication procedure thereof. FIG. 3(a) to (c) is a plan view showing a variation thereof. FIG. 4(a) is a plan view

showing a schematic structure of a multiple gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 4(b) is a cross-sectional view showing a sectional structure along line B-B in FIG. 4(a). FIG. 5(a) to (c) is a cross-sectional step view showing a fabrication procedure thereof.

FIGs. 6 to 9 relate to a conventional example. FIG. 6(a) is a plan view showing a schematic structure of a single gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 6(b) is a cross-sectional view showing a section structure along line B-B in FIG. 6(a). FIG. 7(a) to (e) is a cross-sectional step view showing a fabrication procedure thereof. FIG. 8(a) is a plan view showing a schematic structure of a multiple gate electrode n-channel MOS-FET in the midst of being fabricated. FIG. 8(b) is a cross-sectional view showing a section structure along line B-B in FIG. 8(a). FIG. 9(a) to (c) is a cross-sectional step view showing a fabrication procedure thereof.

Reference numerals 4 to 4a to 4c in the drawings are gate electrodes, 15 is dummy patterns, L is gate electrode pattern widths, and S is a separation distance (predetermined distance).

Note that the same reference numerals in the drawings indicate identical or corresponding parts.

Agent: Masuo Oiwa

4: gate electrode

15: dummy patterns

L: gate electrode pattern width

S: separation distance (predetermined distance)

FIG. 1(a)

FIG. 1(b)

3

FIG. 4

FIG. 4(a)

4a to 4c: gate electrodes

15: dummy patterns

L: gate electrode pattern width

S: separation distance (predetermined distance)

#### Written Amendment (Voluntary)

[stamp: APPROVED] December 19, 1990

Attn: Commissioner of Patents

- 1. Indication of case: Heisei 2 Patent Application No. 177022

- 2. Title of the invention: Semiconductor Integrated Circuit Device

- 3. Parties to the amendment

Relationship to case: Applicant

Address: 2-2-3 Marunouchi, Chiyoda-ku, Tokyo-to Postal Code 100

Name: (601) Mitsubishi Electric Co., Ltd.

Moriya Shigi, representative

4. Agent

Address: c/o Mitsubishi Electric Co., Ltd.

2-2-3 Marunouchi, Chiyoda-ku, Tokyo-to

Postal Code 100

Name: (7375) Masuo Oiwa, patent attorney

[seal: illegible]

(Contact: Patent Dept., 03 (213) 3421)

- 5. Date of amendment order: voluntary amendment

- 6. Increased number of claims due to amendment: none

- 7. Amended sections: "Detailed Description of the Invention" in the Specification

- 8. Content of amendment: see separate

[seal: Patent Office/21 Dec 90/]

#### Content of the Amendment

- (1) The "Detailed Description of the Invention" in the Specification is amended as follows.

- (i) "short channel length" in Specification, page 2, line 11 is amended to "small channel width".

- (ii) "large channel length" in Specification, page 2, line 13 to line 14 is amended to "large channel width".

- (iii) "large channel length" in Specification, page 6, line 2 to line 3 is amended to "large channel width."

**END**

City of New York, State of New York, County of New York

l, Julianne Marzulla, hereby certify that the following document is, to the best of my knowledge and belief, a true and accurate translation from Japanese to English.

"Japanese Unexamined Patent App. Pub. H2-177022"

Julianne Marzulla

Sworn to before me this

Wednesday, May 06, 2015

Signature, Notary Public

SAMANTHA DEWAA, MALEFYT Notary Public - State of New York No. 0 1 DE 6320363 Qualified in NEW YORK County Commission Expires Mar 02, 2019

Stamp, Notary Public

#### ⑫ 公 開 特 許 公 報 (A) 平4-63437

(51)Int. Cl. 5

識別記号

庁内整理番号

43公開 平成 4年(1992) 2月28日

21/336 H 01 L 21/027 29/784

8422-4M 7352-4M 7352-4M

29/78 H 01 L 21/30

Z Z P 3 0 1 3 0 1 3 0 1

未請求 請求項の数 1 審査請求

(全12頁)

半導体集積回路装置 60発明の名称

> 平2-177022 願 21)特

> > 裕

平2(1990)7月2日 22出 顛

明 者  $\mathbf{H}$ 涌 Ш 72発

兵庫県伊丹市瑞原4丁目1番地 三菱電機株式会社エル・

エス・アイ研究所内

三菱電機株式会社 ②出 願 人

東京都千代田区丸の内2丁目2番3号

外2名 弁理士 大岩 増雄 理 人 個代

#### 明細書

1. 発明の名称

半導体集積回路装置

- 特許請求の範囲

- (1) 単一もしくは複数のゲート電極を有する複 数個の電界効果型トランジスタが混在形成された 半導体集積回路装置であって、

各電界効果型トランジスタのゲート電極の外側 位置それぞれに、このゲート電極と所定間隔だけ 離間して平行に位置決めされ、かつ、同一材料か らなるダミーパターンを形成したことを特徴とす る半導体集積回路装置。

3. 発明の詳細な説明

〔産業上の利用分野〕

この発明は、MOS-FETのような電界効果 型トランジスタの複数個が混在形成された半導体 集積回路装置に係り、詳しくは、混在形成された 電界効果型トランジスタそれぞれのチャネル長を 互いに揃えるための技術に関する。

〔従来の技術〕

従来から、この種の半導体集積回路装置として は、微細化された複数個のMOS-FETによっ て構成されたMOS集積回路装置が最もよく知ら れている。そこで、本発明の説明においては、半 基体集積回路装置がMOS集積回路装置であるも のとし、かつ、このMOS集積回路装置がnチャ ネル型MOS-FETの複数個によって構成され ているものとして説明する。

なお、MOS-FETとしては、第6図(a),(b) で構成を示すように、単一本のゲート電極を備え、 かつ、チャネル長の小さい単一ゲート電極型とい われるものと、第8図(a),(b) で構成を示すよう に、複数本のゲート電極を備えることによってチ + ネル長の大きい複数ゲート電極型といわれるも のとがある。そして、一般的なMOS集積回路装 置においては、単一ゲート電極型及び複数ゲート →電極型といわれるMOS-FETが、ともに同一 のチップ上に混在して形成されるのが通常である。 そこで、以下の説明では、まず、単一ゲート電極 型のMOS-FETについて述べたのち、複数ゲ

- ト電極型について述べることとする。

第6図(a) は単一ゲート電極型といわれるnチ ャネル型MOS-FETの製作途中工程における 概略構造を示す平面図であり、第6図(b) は第6 図(a) のB-B線に沿う切断構造を示す断面図で ある。そして、これらの図における符号1はp型 とされたシリコン基板、2は素子分離用絶縁膜、 3はMOS-FETのチャネルを覆うゲート絶縁 膜、4はそのゲート電極であり、5は素子分離用 絶縁膜2及びゲート電極4を覆う層間絶縁膜であ る。また、符号6、7はn \* 型とされたMOS-FETのソース及びドレイン領域であり、これら のソース及びドレイン領域 6, 7の電気的接続は 層間絶縁膜5に形成されたコンタクトホール8. 9を介して行われる。さらに、符号10はゲート 電極4の電気的接続を行うためのコンタクトホー ル、11は素子分離用絶縁膜2の境界を示すフィ ールドパターンであり、L, はMOS-FETの チャネル長を決定することになるゲート電極4の パターン幅を示している.

要因となる。

引き続き、この残存する露光不可領域14aを マスクとする異方性エッチング、例えば、反応性 イオンエッチング(Reactive Ion Etchine)を行 うことによってポリシリコン膜13の不要部分を 除去すると、露光不可領域14aで覆われたポリ シリコン膜13が部分的に残存することになり、 ゲート電極4が形成される(第7図(d)参照)。 そして、このときのゲート電極4のパターン幅L」 が、MOS-FETのチャネル長を決定すること になる。つぎに、この露光不可領域 1 4 a をマス クとしてn<sup>+</sup>型不純物の注入を行ったのち、露光 不可領域14a及び絶縁膜12の不要部分を除去 してn・型不純物の熱拡散を行うと、ゲート電極 4の面側に位置するシリコン基板1内にはn・型 のソース及びドレイン領域 6, 7が形成される( 第7図(e) 参照)。さらに、層間絶縁膜5を形成 したのち、この層間絶縁膜5にコンタクトホール 8~10を形成すると、第6図(a),(b) で示した 構成の単一ゲート電極型といわれるnチャネル型

このMOS-FETの製作手順を、第7図 (a) ~(e) で示す T 程 断 面 図 に 基 づ い て 説 明 する。

まず、シリコン基板1の表面上に素子分離用絶 縁膜2及びゲート絶縁膜3となるべき絶縁膜12 を形成したのち、その表面を全面的に覆うポリシ リコン膜 1 3 を形成する( 第 7 図(a) 参照 )。つ ぎに、ポジ型(もしくはネガ型)のフォトレジス トを塗布してポリシリコン膜13を全面的に覆っ たのち、ゲート智様 4 を形成するために必要とな るフェトレジスト膜14の露光不可領域14aの みをマスキングし、縮小投影露光装置などを用い ることによってマスキングされていないフォトレ ジスト膜14の露光領域14bに光を照射して露 光を行う(第7図(b)参照)。そこで、露光が終 了したのちに現像を行うと、フォトレジスト膜1 4 がポジ型である場合、ポリシリコン膜13上に は露光不可領域14aのみが除去されずに残存す ることになる(第7図(c)参照)。そして、この ときの露光不可領域14aのパターン幅L: ( R ) が、MOS-FETのチャネル長を決める大きな

MOS-FETが完成することになる。

つきに、第8図(a),(b) に基づき、チャネル長の大きなものを得たい場合に使用される複数ゲート電極型といわれる n チャネル型 M O S - F E T について説明する。

第8図(a) は複数ゲート電極型といわれる n チャネル型MOS-FETの製作途中工程における概略構造を示す平面図であり、第8図(b) は第8図(a) のB-B線に沿う切断構造を示す断面図である。なお、この複数ゲート電極型といわれるMOS-FETと単一ゲート電極型のMOS-FETとの相違点は、図から明らかなように、単一本であったゲート電極4が複数本に分割(図では、3分割)されている点にあるから、第8図(a),(b)において第6図(a),(b)と互いに同一もしくは相当する部分については同一符号を付し、ここでの詳しい説明は省略する。

すなわち、第8図(a),(b) における符号4a~ 4cは互いに所定間隔Sだけ離間して形成された ゲート電極であり、L。はMOS-FETの両端 に位置するゲート電極 4 a , 4 c のパターン幅、また、 L s は中央に位置するゲート電極 4 b のパターン幅を示している。なお、これらのゲート電極 4 a ~ 4 c の離間間隔 S は M O S - F E T を設計する際に設定されるものであり、例えば、コンタクトホール 8 , 9 の径を 0.5 μ m とし、これらの端とゲート電極 4 a ~ 4 c それぞれの端との距離を 0.3 μ m とした場合の離間間隔 S は 1.1 μ m となる。

引き続き、この複数ゲート電極型といわれる n チャネル型MOS-FETの製作手順について説 明するが、このMOS-FETの製作手順は、第 7図(a)~(e)に基づいて説明した単一ゲート電 極型の製作手順と同様であるから、ここでは、第 7図(b)~(d)と対応する第9図(a)~(c)で示 す工程断面図に基づき、説明が必要な工程につい てのみ述べることとする。

まず、第7図(a) に基づいて説明したと同一の 手順により、素子分離用絶縁膜2及び絶縁膜12 を覆うポリシリコン膜13上に、フォトレジスト

cが形成されることになる(第9図(c)参照)。そして、このときのゲート電極4a~4cのパターン幅しz, L, それぞれが、MOSーFETのチャネル長を決定することになる。さらに、第7図(e)に基づいて説明したと同様の操作を行うと、シリコン基板1内にはn・型とされたソース及びドレイン領域6、7が形成され、第8図(a),(b)で示した構成の複数ゲート電極型といわれるnチャネル型MOSーFETが完成することになる。「発明が解決しようとする課題)

ところで、一般的なMOS集積回路装置においては、以上説明した単一ゲート電極型及び複数ゲート電極型のMOSーFETが、ともに同一のチップ上に混在して形成されることになる。しかしながら、これらのMOSーFETを製作するを開発した場合には、各MOSーFETのように微細化した場合には、各MOSーFETのゲート電極4、4a~4cそれぞれのパターン幅 し、~し、が等しくなるように設定し、かつ、同一波長の光を用いることによってフォトレジスト 膜14を形成しておく。そののち、互いに所定間隔 S だけ離間したゲート電極4a~4cを形成するために必要となるフォトレジスト膜14の露光不可領域14c、14dをマスキングしたうえ、縮小投影露光装置などを用いることによってマスキングされていないフォトレジスト膜14の露光領域14e、14fに光を照射して露光を行う(第9図(a)参照)。

そこで、露光が終了したのちに現像を行うと、フォトレジスト膜14がポジ型である場合、ポリシリコン膜13上には露光不可領域14c,14dが除去されずに残存していることになる(第9図(b)参照)。そして、このときの露光不可領域14c,14dそれぞれのパターン幅L₂(R)、L;(R)が、MOS-FETのチャネル長を決める大きな要因となる。

そののち、この残存する露光不可領域14c, 14dをマスクとする異方性エッチングによって ポリシリコン膜13の不要部分を除去すると、互 いに所定間隔Sだけ離間したゲート電極4a~4

膜14の露光を行ったとしても、得られたMOS -FETそれぞれのチャネル長が互いに揃わず、 ばらついてしまうという不都合が生じることになっていた。

そして、このような不都合は、つぎのような要 因に基づいて発生すると考えられる。すなわち、 まず、単一ゲート電極型のMOS-FETにおい ては、第7図(b),(c) で示したように、フォトレ ジスト膜14を露光するために照射した光の波長 ( 例えば、エキシマレーザ光では 0.248 μm )に 対してフォトレジスト膜14の露光領域14bが 充分な長さを有していることから、その感光が充 分に行われることになる結果、現像によって得ら れた露光不可領域14aのパターン幅L」( R ) が細くなる傾向がある。ところが、複数ゲート電 極型のMOS-FETでは、第9図(a),(b) で示 したように、露光領域14fの長さは光の波長に 対して充分であるにも拘わらず、露光不可領域1 4 c. 1 4 d 間の露光領域14 e の長さが光の波 長の数倍から10倍程度(前述した離間間隔5、

すなわち、露光領域14eの長さを 1.1μmと設定した場合には、 1.1/ 0.248 = 4.4倍)に過ぎないため、これらの露光領域14eは光の回折や反射などによる影響を受けることになり、その感光が不充分となる。そこで、これらの露光領域14cの露光ではよって挟まれた露光不可領域14dのに対し、露光領域14cのパターン幅L;(R)は細くなる傾向と太さとなる傾向にある。

そのため、当初の設計においては、混在形成されるMOSーFETのゲート電極 4、4 a~4 c c それぞれのパターン幅 L i ~L i が等しくなっても拘わらず、ウェハアとでは、単一ゲート電極型及びでは、単一ゲート電極型では、単一ゲート電極型でれぞれのMOSーFETのチャパート電極型を表が一ト電極4、4 a~4 c のパックーを決定するゲート電極4、4 a~4 c のパックーン幅 L i ~L i が互いに相違数ゲート電極型でいた。また、複数ゲート電極型と

形成された電界効果型トランジスタが単一ゲート 電極型であるか複数ゲート電極型であるかに拘わ らず、そのゲート電極がともに所定間隔だけ離間 して平行に位置決めされたダミーパターンによっ て挟まれていることになる。そこで、これらのゲ ート電極を製作する際における露光条件は、相等 しいことになる。

#### (実施例)

以下、本発明の実施例を図面に基づいて説明する。なお、本実施例においては、半導体集積回路装置が複数個のnチャネル型MOS-FETからなるMOS集積回路装置であるものとしている。

本実施例におけるMOS集積回路装置は、単一ゲート電極型及び複数ゲート電極型といわれる n チャネル型MOS-FETの複数個によって構成されており、これらのMOS-FETは同一のチップ上に混在して形成されている。そこで、以下の説明においては、まず、第1図(a),(b)及び第2図(a)~(e) に基づいて単一ゲート電極型といわれるMOS-FETの構成及び製作手順を説明

されたMOS-FETそのものにおいても、その 両端に位置するゲート電極4a、4cと中央に位 置するゲート電極4bとでパターン幅Lz 、Lz が異なることになっていた。

本発明は、このような不都合に鑑みて創案されたものであって、混在形成された電界効果型トランジスタそれぞれのチャネル長を互いに揃えることができ、そのばらつきを抑制することができる 半導体集積回路装置の提供を目的としている。

#### (課題を解決するための手段)

本発明は、このような目的を達成するために、 単一もしくは複数のゲート電極を有する複数個の 電界効果型トランジスタが混在形成された半導体 集積回路装置であって、各電界効果型トランジス タのゲート電極の外側それぞれに、このゲート電 極と所定間隔だけ離間して平行に位置決めされ、 かつ、同一材料からなるダミーパターンを形成し たことを特徴とするものである。

#### (作用)

上記構成によれば、半導体集積回路装置に混在

したのち、第4図(a),(b) 及び第5図(a)~(c) に基づいて複数ゲート電極型といわれるMOSーFETの構成及び製作手順について述べることとする。なお、本実施例に係るMOSーFETの全体構成については、後述するダミーパターンを設けた点を除き、第6図(a),(b) 及び第8図(a),(b) で示した従来例と基本的に異ならないので、互いに同一もしくは相当する部品、部分には同一符号を付している。

第1図(a) は単一ゲート電極型といわれるnチャネル型MOS-FETの製作途中工程における概略構造を示す平面図であり、第1図(b) は第1図(a) のB-B線に沿う切断構造を示す断面図である。そして、これらの図における符号1はp型とされたシリコン基板、2は素子分離用絶縁膜、3はMOS-FETのチャネルを覆うゲート電極4と開、4はポリシリコンなどからなるゲート電極4でおれには、これと所定間隔Sだけ離間して平行に位置決めされ、かつ、ゲート電極4と同一材料で

あるボリシリコンなどからなるダミーパターン15が素子分離用絶縁膜2上に形成されている。なお、これらのダミーパターン15はゲート電極4と電気的に分離した状態で形成されており、これらのそれぞれとゲート電極4との離間間隔Sは、前記従来例で説明した複数ゲート電極型といわれるMOS-FETにおけるゲート電極4a~4c同士の離間間隔Sと同一もしくは略等しく設定されている。

また、図中の符号 5 は素子分離用絶縁膜 2、ゲート電極 4 及びダミーパターン1 5 のそれぞれを 覆う層間絶縁膜、6、7はn・型とされたMOSーFETのソース及びドレイン領域であり、これ 6のソース及びドレイン領域 6、7 の電気的接続は層間絶縁膜 5 に形成されたコンタクトホール8、9 を介して行われる。さらに、符号10はゲート電極 4 の電気的接続を行うためのコンタクトホール、11 は素子分離用絶縁膜 2 の境界を示すフィールドパターンであり、 L は MOSーFETのチャネル長を決定することになるゲート電極 4 のパ

gが除去されずに残存することになる(第2図(c)参照)。なお、ここでは、光によってフォトレジスト膜14の露光を行うものとしているが、例えば、X線や電子線などによる露光であっても同様である。

ターン幅を示している。

このMOS-FETの製作手順を、第2図 (a) ~(e) で示す工程断面図に基づいて説明する。

まず、シリコン基板1の表面上に素子分離用絶 縁膜2及びゲート絶縁膜3となるべき絶縁膜12 を形成したのち、その表面を全面的に覆うポリシ リコン膜13を形成する(第2図(a)参照)。つ ぎに、ポジ型(もしくはネガ型)のフォトレジス トを塗布してポリシリコン膜13を全面的に覆っ たのち、互いに所定間隔Sだけ離間したゲート電 極4及びダミーバターン15を形成するために必 要となるフォトレジスト膜14の露光不可領域1 4 a, 1 4 g のみをマスキングし、縮小投影露光 装置などを用いることによってマスキングされて いないフォトレジスト膜14の露光領域14h、 14 i に光を照射して露光を行う(第2図(b) 参 照 )。そこで、露光が終了したのちに現像を行う と、フォトレジスト膜14がポジ型である場合、 ポリシリコン膜13上にはパターン幅L(R)の 露光不可領域14aとともに、露光不可領域14

縁膜 5 にコンタクトホール 8 ~ 1.0 を形成すると、第 1 図 (a), (b) で示した構成の単一ゲート電極型といわれる n チャネル型MOSーFETが完成することになる。そこで、このMOSーFETのゲート電極 4 の外側位置それぞれには、これと所定間隔 S だけ離間して平行に位置決めされたダミーパターン 1.5 が形成されていることになる。

なお、第1図(a),(b) においては、ダミーパターン15がゲート電極4と電気的に分離され、かつ、素子分離用絶縁膜2上に形成されているものとしているが、これに限定されるものではない。すなわち、例えば、第3図(a) で示すように、がゲート電極4と接続一体化されたものであってもよいし、第3図(b) で示すように、これらのダミーパターン15を付してMOS集積回路装置を構成する他の配線パターン16を利用してもよい。また、第3図(c) で示すように、ダッショート電極として構成することも可能成のダミーゲート電極として構成する。

つぎに、第 4 図(a),(b) に基づき、複数ゲート電極型といわれる n チャネル型 M O S - F E T について説明する。

第4図(a) は複数ゲート電極型といわれる n チャネル型MOS-FETの製作途中工程における 概略構造を示す平面図であり、第4図(b) は第4図(a) のB-B線に沿う切断構造を示す断面図である。なお、この複数ゲート電極型といわれるMOS-FET及び単一ゲート電極型のMOS-FETの基本構成は互いに共通するものであるから、第4図(a),(b) において第1図(a),(b) と互いに同一もしくは相当する部分については同一符号を付し、ここでの詳しい説明は省略する。

すなわち、この複数ゲート電極型といわれる MOS-FETにおいては、第4図(a),(b) で示すように、ポリシリコンからなるゲート電極4a~4cが互いに所定間隔Sだけ離間した状態で形成されている。そして、これらのゲート電極4a~4cの外側位置それぞれには、その両端に位置するゲート電極4a,4cと所定間隔Sだけ離間し

トレジスト膜14の露光不可領域14 j、14 kをマスキングしたうえ、縮小投影露光装置などを用いることによってマスキングされていないフォトレジスト膜14の露光領域14m、14 n に光を照射して露光を行う(第5図(a)参照)。

そこで、露光が終了したのちに現像を行うと、フォトレジスト膜14がポジ型である場合、ポリシリコン膜13上には露光不可領域14j、14kが除去されずに残存していることになる(第5図(b)参照)。そして、このときの露光不可領域14jのパターン幅L(R)が、MOS-FETのチャネル長を決める大きな要因となる。

そののち、この残存する露光不可領域 1 4 j , 1 4 k をマスクとする異方性エッチングによってポリシリコン膜 1 3 の不要部分を除去すると、互いに所定間隔 S だけ離間したゲート電極 4 a ~ 4 c 及びダミーパターン 1 5 が形成されることになる(第5図(c)参照)。そして、このときのゲート電極 4 a ~ 4 c のパターン幅しによって M O S ー F E T のチャネル長が決定される。さらに、第

て平行に位置決めされ、同一材料であるポリシリコンなどからなるダミーパターン15が素子分離用絶縁膜2上に形成されている。なお、ここで、ゲート電極4とダミーパターン15のそれぞれとの離間間隔5は、ゲート電極4a~4c同士の離間間隔5と同一もしくは略等しく設定されている。

つぎに、この複数ゲート電極型といわれる n チャネル型M O S ー F E T の製作手順について説明する。なお、このM O S ー F E T の製作手順は、第2図 (a)~(e) に基づいて説明した単一ゲート電極型の製作手順と基本的に同一であるから、ここでは、第2図 (b)~(d) と対応する第5図 (a)~(c) で示す工程断面図に基づいて相違する工程についてのみ述べることとする。

まず、第2図(a) に基づいて説明したと同一の手順により、素子分離用絶縁膜2及び絶縁膜12を覆うポリシリコン膜13上に、フォトレジスト膜14を形成しておく。そののち、互いに所定間隔5だけ離間したゲート電極4a~4c及びダミーパターン15を形成するために必要となるフォ

2図(e) に基づいて説明したと同一の操作を行うと、シリコン基板 1 内には n・型とされたソース及びドレイン領域 6 、 7 が形成され、第 4 図(a),(b) で示した構成の複数ゲート電極型といわれるnチャネル型MOS-FETが完成することになる。そこで、このMOS-FETのゲート電極 4 a ~ 4 c の外側位置それぞれには、これと所定間隔 S だけ離間して平行に位置決めされたダミーパターン 1 5 が形成されていることになる。

そして、以上説明した単一ゲート電極型及び複数ゲート電極型といわれるMOSーFETはともに同一のチップ上に混在して形成されることになるが、このとき、各MOSーFETにおけるゲート電極4、4a~4cの外側位置それぞれには所定間隔Sだけ離間したダミーパターン15が平行状に形成されており、ゲート電極4、4a~4cのそれぞれはダミーパターン15に挟まれた状態で配設されていることになる。

#### 〔発明の効果〕

以上説明したように、本発明に係る半導体集積

回路装置によれば、これに混在して形成された電界効果型トランジスタが単一ゲート電極型であるか複数ゲート電極型であるかに拘わらず、そのゲート電極型であるがけれたがであるが、からではなる。そこで、これらのゲートで電極のパターンにはでいる。そこで変におけれていいないが、かられるゲート電極のパターンには略等しくなる。その結果、混在形成された電界効果型トランとができるという優れた効果が得られる。

#### 4. 図面の簡単な説明

第1図ないし第5図は本発明の実施例に係り、第1図(a) は単一ゲート電極型といわれるnチャネル型MOS-FETの製作途中工程における概略構造を示す平面図、第1図(b) は第1図(a) のB-B線に沿う切断構造を示す断面図、第2図(a)~(e) はその製作手順を示す工程断面図であり、第3図(a)~(c) はその変形例を示す平面図

極のパターン幅、Sは離間間隔(所定間隔)である。

なお、図中の同一符号は、互いに同一もしくは 相当部分を示している。

代理人 大岩 增雄

である。また、第4図(a) は複数ゲート電極型といわれるn チャネル型MOS-FETの製作途中工程における概略構造を示す平面図、第4図(b) は第4図(a) のB-B線に沿う切断構造を示す断面図であり、第5図(a)~(c) はその製作手順を示す工程断面図である。

さらに、第6図ないし第9図は従来例に係り、第6図(a) は単一ゲート電極型といわれる n チャネル型MOSーFETの製作途中工程における概略構造を示す平面図、第6図(b) は第6図(a) のB-B線に沿う切断構造を示す断面図、第7図(a)~(e) はその製作手順を示す工程断面図である。また、第8図(a) は複数ゲート電極型といわれる n チャネル型MOSーFETの製作途中工程における概略構造を示す平面図、第8図(b) は第8図(a) のB-B線に沿う切断構造を示す断面図であり、第9図(a)~(c) はその製作手順を示す工程断面図である。

図における符号 4. 4 a ~ 4 c のそれぞれはゲート電極、15 はダミーパターン、L はゲート電

#### 第 1 図(a)

4:ゲート電極

15:ダミーパターン

L:ゲート電極のパターン幅

S:離間間隔(所定間隔)

第 1 図(b)

### 手続補正書(自発)

平成 年 月 日 12 19

特許庁長官 殿

1、事件の表示 平成2年特許願第177022号

2、発明の名称 半導体集積回路装置

3、補正をする者

事件との関係 特許出願人

郵便番号 100

住 所 東京都千代田区丸の内二丁目2番3号

名称(601)三菱電機株式会社代表者志岐守哉

4、代理人 郵便番号 100

住 所 東京都千代田区丸の内二丁目2番3号

三 菱 電 機 株式会社内

氏 名 (7375)弁理士 大 岩 増 雄 (連絡先03(213)3421特許部)

5、補正命令の日付 自発補正

6、補正により増加する請求項の数

7、補正の対象 明細書の「発明の詳細な説明」の欄

8、補正の内容 別紙のとおり

# 特許庁

なし

#### 補正の内容

- (1)明細書の「発明の詳細な説明」の欄を次のとおり補正する。

- (i)明細書の第2頁第11行目に「チャネル長の小さい」とあるのを「チャネル幅の小さい」と補正する。

- (ii)明細書の第2頁第13行目から14行目にかけて「チャネル長の大きい」とあるのを「チャネル幅の大きい」と補正する。

- (iii)明細書の第6頁第2行目から3行目にかけて「チャネル長の大きな」とあるのを「チャネル幅の大きな」と補正する。

以上