| Original Copy                                                                                                  | •                                      |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|------------|------------------------|-----------|----------|----------|---------|-------------------|---------------|----------|---------|---------|--|

|                                                                                                                | Main class                             | ification          |            |                        | Form      | examin   | ation    | App     | lication n        | umber: 0      | 21255    |         |         |  |

| IPC                                                                                                            | Sub classif                            | Sub classification |            |                        |           | section  |          |         | rson in charge    |               | Examiner |         |         |  |

| classification                                                                                                 |                                        |                    |            |                        | 1         |          |          |         | led:] Eui         |               | [Seale   | :d:] D  | ae Kyu  |  |

| code                                                                                                           |                                        |                    |            |                        |           |          |          | -       | ng, [Aug          |               | Park,    |         |         |  |

|                                                                                                                |                                        |                    |            |                        |           |          |          | 199     |                   | ,             | 1994]    |         | - ,     |  |

|                                                                                                                | [Stamped:]                             |                    |            |                        |           |          |          |         |                   | I             |          |         |         |  |

|                                                                                                                | Application D                          |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

| Received by                                                                                                    | Korean Intelle<br>Property Office      |                    |            |                        | I         | Datan    | t An     | nlic    | ation (           | (1)           |          |         |         |  |

| Received by                                                                                                    |                                        |                    |            | Patent Application (1) |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                | Received                               |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                | No.                                    | D 4                | · D.       |                        | T 3.4     |          | 1104     | T)      | 4                 | A 1'          |          |         |         |  |

| A 12                                                                                                           | Name                                   | _                  | tive Dii   | ector Jeong F          | iwan M    | loon, G  | oid Stai | r Elec  | tron              | Applica       | ants     |         |         |  |

| Applicant                                                                                                      | A 11                                   | Co., Ltd.          |            |                        |           |          |          |         |                   | Code          |          |         |         |  |

|                                                                                                                | Address                                | 0 0 1              | <b>3</b> 7 | I Ave                  |           |          |          |         |                   | Phone 1       | No.      |         |         |  |

|                                                                                                                | Name                                   | Soon Seok          | Yang       | Attorney co            | ode       |          |          |         | Tel               |               |          |         |         |  |

| Attorney                                                                                                       |                                        |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                | Address                                |                    |            | 1                      |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                | Name                                   | Jeung Sang         | g Lee      | Resident re            | gistratio | on       |          |         | Nationa           | lity          |          | public  | of      |  |

| Inventor                                                                                                       |                                        |                    |            | number                 |           |          |          |         |                   |               | Ko       | rea     |         |  |

|                                                                                                                | Address                                |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

| Name of inventio                                                                                               | n                                      |                    |            | d for Semicor          | nductor   |          |          |         |                   |               |          |         |         |  |

|                                                                                                                |                                        | Country of         |            | Type of                |           | Date of  |          |         | Applica           | tion          |          | rificat |         |  |

| Priority claim in a                                                                                            | accordance                             | application        | l          | application            |           | applic   | ation    |         | number            |               |          | umen    |         |  |

| with the provision                                                                                             |                                        |                    |            |                        |           |          |          |         |                   |               |          | ach     | Unatta  |  |

| Patent Law (Artic                                                                                              |                                        |                    |            |                        |           |          |          |         |                   |               | ed       |         | ched    |  |

| 55)                                                                                                            |                                        |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

| ,                                                                                                              |                                        |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                |                                        |                    |            | L                      |           | 10 01    |          |         |                   |               |          |         |         |  |

| The application is                                                                                             | s filed as des                         | scribed above      | in acco    | ordance with A         | Article 4 | 42 of th | e Paten  | it Law  | 7.                |               |          |         |         |  |

|                                                                                                                |                                        |                    |            |                        |           |          |          |         |                   | 1004          |          |         |         |  |

|                                                                                                                |                                        |                    |            |                        |           |          |          |         | August 27         |               |          |         |         |  |

|                                                                                                                | Agent: Soon Seok Yang, Patent Attorney |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

| т с · ·                                                                                                        | C.1 IZ                                 | T 1 4 1            | 1 D        | , O.C.                 |           |          |          |         |                   |               |          |         |         |  |

| To: Commissione                                                                                                |                                        |                    |            |                        |           | 1        | *:1 A :: | . 1 .   | 0 C4 D            | T             |          |         |         |  |

| The review of the application is requested as described above in accordance with Article 60 of the Patent Law. |                                        |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

|                                                                                                                |                                        |                    |            |                        |           | A cont.  | Soon C   | ook V   | ona Dotos         | at Attorn     | 21.      |         |         |  |

|                                                                                                                |                                        |                    |            |                        | 1         | Agent.   | 30011 36 | OK I    | ang, Patei        | n Anom        | ЕУ       |         |         |  |

| To: Commissions                                                                                                | er of the Kor                          | ean Industria      | l Prope    | rty Office             |           |          |          |         |                   |               |          |         |         |  |

| To: Commissioner of the Korean Industrial Property Office Attachments: 1. 2 copies of the application Fees     |                                        |                    |            |                        |           |          |          |         |                   |               |          |         |         |  |

| Attachments.                                                                                                   |                                        |                    |            | Abstract and l         | Drawin    | œ        | Appli    | ic I    | Basic             | 17            | 18 (     | 000 W   | on      |  |

|                                                                                                                |                                        | of Power of        |            |                        | Diawin    | gs       | ation    |         | Dasic             |               | 10,0     | JUU W   | OII     |  |

|                                                                                                                | 3. 1 сору                              | of Lower of        | Attorne    | y                      |           |          | fee      | _       | Additi            | pages         | +        | 13.7    | on      |  |

|                                                                                                                |                                        |                    |            |                        |           |          | 100      |         | on                | Pages         |          | vv      | OII     |  |

|                                                                                                                |                                        |                    |            |                        |           |          | Drion    |         | im fee            | rages         | +        | 137     | on      |  |

|                                                                                                                |                                        |                    |            |                        |           | 076      | 1 11011  | ity Cla | 1111 166          | Cases         |          | vv      | OII     |  |

|                                                                                                                |                                        |                    |            |                        |           | 0,0      | Revie    | NV ***  | nuet              |               | 277      | V 000,  | Von     |  |

|                                                                                                                |                                        |                    |            |                        |           |          | fee      | w rec   | <sub>I</sub> uest | 4/11<br>Items | 211      | ,000 1  | V OII   |  |

|                                                                                                                |                                        |                    |            |                        |           |          |          |         | +                 | 1101118       | 1        |         | 205.000 |  |

|                                                                                                                |                                        |                    |            |                        |           |          | Total    |         |                   |               |          |         | 295,000 |  |

#### **SPECIFICATIONS**

### 1. Name of invention

A Method for Fabricating Semiconductor Device

### 2. Brief Explanation of the Drawings

FIG. 1 and FIG. 2 are the drawings of the prior art and FIGs. 3 to 6 illustrate the technology of the present invention.

\* Explanation on the numbers marked for the major parts of the drawings

11, 21, 31: semiconductor substrate 12, 22, 32: field oxide layer

13, 23, 33: source and drain region 14, 24, 34: gate

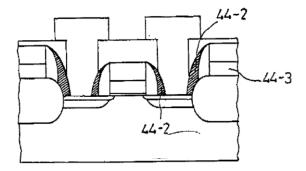

14', 24', 25', 34-1: sidewall 44-3: connection line

15, 25, 35: interlayer insulation film 57: step

34-1, 34-2, 44-2, 54-2, 64-2, 67: etch stop layer 16, 26, 36: conductive layer

### 3. Detailed Explanation of the Invention

The present invention relates to a method for fabricating a semiconductor device, and specifically pertains to a method for fabricating a semiconductor device, in which the characteristics of the device are improved by securing an align margin upon formation of the contact hole.

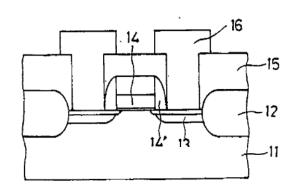

FIG. 1 (a) is a cross-sectional view of a source and drain region according to the prior art, and FIG. 1 (b) illustrates the problem of the prior art.

078

In order to make the structure illustrated in FIG. 1 (a), the active region is isolated by a field oxide layer (12) on a semiconductor substrate (11) and a MOS gate (14) is formed by depositing gate oxide layer, poly and gate caps in this sequence and then etching them.

After forming a low concentration impurity region by the following ion implantation process and forming a gate sidewall (14') using a deposition and etch-back process, a source and drain region (13) is made by implanting the sidewall into the mask in order to form a high concentration impurity region.

A contact hole that opens the source and drain region is formed by depositing an interlayer insulation film (15) on the following transistor and etching the interlayer insulation film.

And then, the process is completed by depositing a conductive layer (16) to form a junction contact with the source and drain region of the transistor.

As illustrated in FIG. 1 (b), the prior art described above depended on the alignment accuracy of a photographic process for the adjustment of the thickness of the interlayer insulation film to secure a sufficient breakdown voltage between gate and junction contact.

However, when a mis-alignment occurs, the gate sidewall (14') is damaged as shown in the area B or the field oxide layer that separates an active region is also damaged (area A of the drawing) and thus, it becomes the cause of junction leakage.

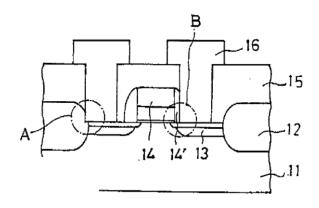

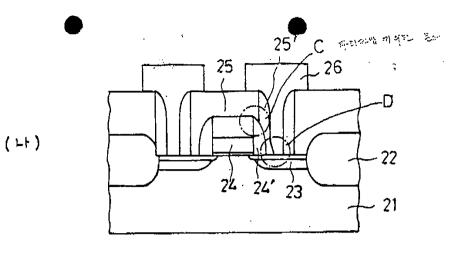

Therefore, a structure illustrated FIG. 2 was proposed in an effort to improve this problem.

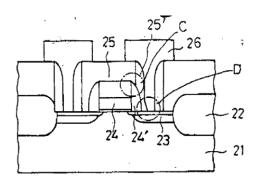

FIG. 2 (a) is a cross-sectional view showing an improvement over the structure in FIG. 1, and FIG. 2 (b) is the cross-sectional view of a problematic area of FIG. 2 (a).

As illustrated in FIG. 2 (a), after forming a transistor using a general method, an interlayer insulation film (25) is deposited for interlayer isolation and a contact hole is formed by etching the interlayer insulation film so that the source and drain region of the transistor is to be opened.

In this drawing, the number 21 represents a semiconductor substrate, 22 represents a field oxide layer, 24 represents a gate, and 24' represents a gate sidewall.

Subsequently, in order to enhance the characteristics of a breakdown voltage by securing an alignment margin, a sidewall (25') is formed on the side wall of the interlayer insulation film within the contact hole using a deposition and etch-back process.

And then, a conductive layer (26) is formed within the contact hole by depositing conductive material.

However, as illustrated in FIG. 2 (b), the process forming a sidewall on the side wall of the interlayer insulation film within a contact hole can have a problem caused by the breakdown voltage on the area C when the contact hole is laid over the jaw of a gate as the contact alignment deviates from the margin.

080

Further, when a contact hole has been defined in a small size that is below a certain size according to the tendency of high density integration, the inside of the contact hole is filled by the process forming a sidewall on the side wall of the interlayer insulation film, and a problem happens to the opening of the contact (Area D of the drawing) due to this and a problem is also encountered in the scale-down of a device.

The present invention has been conceived to solve these problems and it relates to the structure of a semiconductor device in which a process alignment margin is secured when forming a contact hole by forming an etch stop layer on the contact hole area to protect the lower insulation layer and a method for fabricating this structure.

The method of the present invention comprises of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate; b) a step of forming an etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and c) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area in a method for fabricating a semiconductor device.

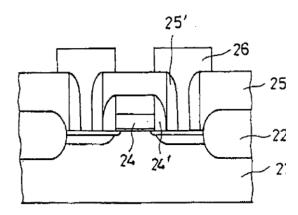

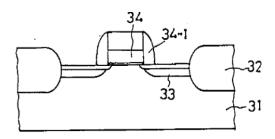

FIG. 3 illustrates the semiconductor device fabricating process in accordance with the present invention.

One embodiment of the present invention can be explained referring to drawings as follows:

As illustrated in FIG. 3 (a), an active region is isolated electrically from the surrounding active regions by forming a field oxide layer (32) on a semiconductor substrate (31), and a MOS gate (34) is formed by depositing and etching gate oxide layer, poly and gate cap in order.

After forming a low concentration impurity region by the following ion implantation process and forming a gate sidewall (34-1) using a deposition and etch-back process, a source and drain region (33) is made by implanting sidewall into mask to form a high concentration impurity region.

Up to this process, it is conducted in the same way with the process of the prior art.

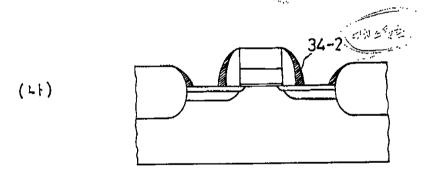

Subsequently, as illustrated in FIG. 3 (b), an etch stop layer (34-2) of the contact etching process is formed around the impurity region in the form of a sidewall by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process to the surface of the gate sidewall and then, conducting etch-back.

At this time, the etch stop layer is formed with conductive or non-conductive material, and it is formed in the form of a sidewall through a deposition and etch-back process using the step area formed on the lower layer without any additional mask.

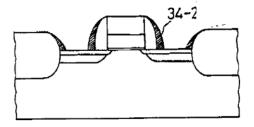

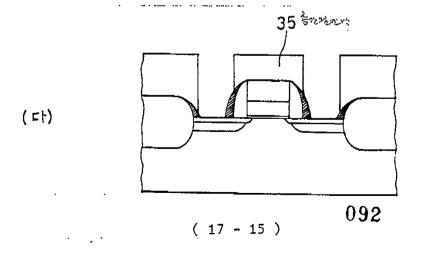

As illustrated in FIG. 3 (c), a contact hole is formed by depositing an interlayer insulation film (35) and etching the interlayer insulation film ensuring that it doesn't deviate from the range of the etch stop layer (34-2).

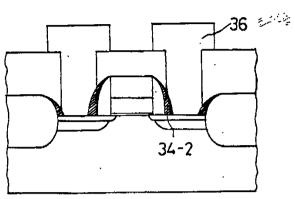

As illustrated in FIG. 3 (d), the junction contact with the source and drain region of the transistor is to be formed with the conductive layer (36) composed of conductive material.

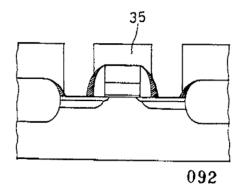

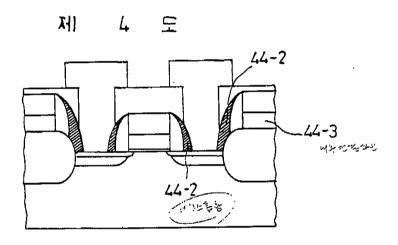

FIG. 4 illustrates the second embodiment of the present invention. This is a method of forming an etch stop layer (44-2) using an internal connection line (44-3) passing adjacently or the step of a dummy pattern when the step at the lower layer used to form the etch stop layer in the first embodiment is not sufficient.

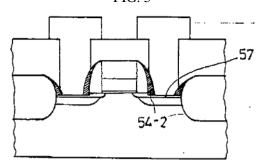

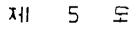

FIG. 5 is the drawing of the third embodiment of the present invention.

When the step at the lower layer used to form the etch stop layer is not sufficient and the method of the second embodiment can't be used, the step for forming an etch stop layer (54-2) is secured in this method using the step (57) randomly formed by etching the semiconductor substrate using the oxide layers on the substrate (field oxide layer, gate sidewall, cap oxide layer) as mask.

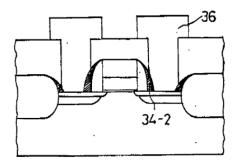

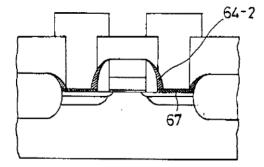

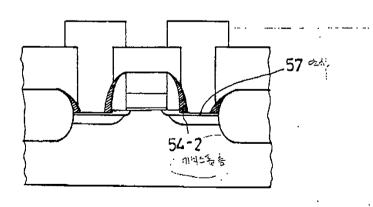

FIG. 6 is another embodiment illustrating the device according to the present invention.

This is a method of forming another etch stop layer (67) on the source and drain region prior to forming an etch stop layer to prevent the damage to the lower layer caused by the anisotropic etching when an etch stop layer (64-2) is formed in the embodiments 1 to 5.

In this case, the material of the etch stop layer can be conductive or non-conductive and when it is formed using non-conductive material, it is removed by etching when forming the contact hole.

The effects of the present invention are as follows:

First, since the etch stop layer formed additionally in the present invention can be formed through self-alignment without a separate mask, there is no additional process.

Secondly, since the heavily stressed site is protected by the etch stop layer, the area in which junction leakage can happen can be protected from the etching process.

Thirdly, the breakdown voltage between a gate and a contact can be secured only with the adjustment of the thickness of a gate sidewall by protecting the gate sidewall from being peeled by the etch stop layer.

Fourthly, an alignment margin can be secured easily at contact photographing.

Fifthly, after forming the contact hole, the scale-down of the contact hole is easy since a separate sidewall within the hole is not used.

### 4. Scope of Patent Claims

- 1. A method for fabricating a semiconductor device which comprises of

- a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate;

- b) a step of forming an etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and

- c) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

- 2. The method for fabricating a semiconductor device in Claim 1, wherein the sidewall for etch stop is composed of a conductive material.

- 3. The method for fabricating a semiconductor device in Claim 1, wherein the sidewall for etch stop is composed of a non-conductive material.

- 4. The method for fabricating a semiconductor device in Claim 1, wherein the sidewall is formed using the step at the lower layer.

- 5. The method for fabricating a semiconductor device in Claim 1, wherein the sidewall uses either the step of the connection line at the adjacent lower layer or uses the step by forming an adjacent dummy pattern.

- 6. A method for fabricating a semiconductor device which comprises of

- a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate;

- b) a step of forming the second etch stop layer on said source and drain region;

- c) a step of forming the first etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and

- d) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

- 7. The method for fabricating a semiconductor device in Claim 6, wherein the first etch stop layer is composed of a conductive material.

- 8. The method for fabricating a semiconductor device in Claim 6, wherein the first etch stop layer is composed of a non-conductive material.

- 9. The method for fabricating a semiconductor device in Claim 6, wherein the second etch stop layer is composed of a conductive material.

- 10. The method for fabricating a semiconductor device in Claim 6, wherein the second etch stop layer is composed of a non-conductive material and it is removed together when the compared to is formed.

- 11. A method for fabricating a semiconductor device which comprises of

- a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region defined by a field oxide layer on a semiconductor substrate and the substrate around the gate;

- b) a step of forming a step on the substrate in the source and drain region by etching the semiconductor substrate using the insulation layer and field oxide layer forming the transistor as a mask,

- c) a step of forming the etch stop layer around said source and drain region using said step of the substrate by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and

- d) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the interlayer insulation film to the front, and then connecting the conductive layer to the opened area.

- 12. The method for fabricating a semiconductor device in Claim 11, wherein the first etch stop layer is composed of a conductive material.

- 13. The method for fabricating a semiconductor device in Claim 11, wherein the first etch stop layer is composed of a non-conductive material.

- 14. The method of fabricating the semiconductor device which comprises of a gate for which gate oxide layer and conductive layer gate cap are formed on the active region defined by a field oxide layer on a semiconductor substrate and a gate sidewall is formed, a transistor composed of a source and drain region, an interlayer insulation film formed on the transistor, a contact hole which opens the source and drain region of the transistor and penetrates the above interlayer insulation film, and the conductive layer filling the contact hole, wherein a material having a high etch selectivity with the interlayer insulation film is formed under the interlayer insulation film in the area surrounding the source and drain region.

- 15. The semiconductor device in Claim 14, wherein the material having a high etch selectivity is conductive.

#### Abstract

The present invention relates to the structure of a semiconductor device in which a process alignment margin is secured when forming a contact hole by forming an etch stop layer on the contact hole area to protect the lower insulation layer and a method for fabricating this structure.

The present invention fabricates a semiconductor device using a method comprised of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate; b) a step of forming an etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and c) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

(b)

FIG. 2

(a)

(17 - 14) 091

(b)

FIG. 3

(b)

(c)

FIG. 4

FIG. 5

FIG. 6

City of New York, State of New York, County of New York

I, Kelly Kim, hereby certify that the following document is, to the best of my knowledge and belief, a true and accurate translation from Korean to English

"KR App. No. 1994/021255"

Kelly Kim

Sworn to before me this

Tuesday, April 28, 2015

Signature, Notary Public

AMY LEONG

Notary Public - State of New York

No. 01LE6314554

Qualified in Richmond County

Commission Expires Nov 10, 2018

Stamp, Notary Public

정본

| 분류 부기호 접수 인 특경 1994 8. 함 물 원 명                   | 분류 성 한 사 식 만 <b>등 하 출</b> 27 가 금성일렉트몬주식회사 대표이사 | 출원번호 021255<br>답당 심사관<br>전 시시 (1)<br>문정 환 출원인 코드              |  |  |  |  |  |  |

|--------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|

| 인 주 소<br>대 성 명<br>리<br>인 주 소                     | 양 순 석 대리인 코드                                   | 우 펀 번 호 전화번호                                                  |  |  |  |  |  |  |

| 발 성 명<br>명<br>자 주 소                              | 이 중 상 주민등록번호 국석 대한민국                           |                                                               |  |  |  |  |  |  |

| 발명의 명칭                                           | 반도체 장치의 제조방법                                   |                                                               |  |  |  |  |  |  |

| 특허법(제 54<br>조 또는 제 55<br>조)의 규정에<br>의한<br>우선권 주장 | 출원국명 출원종류 출원일자                                 | 출원 번 호 점 부 미첨부                                                |  |  |  |  |  |  |

| <b>투</b> 허법                                      | 채 42조의 규정에 의하여 위와 같이 출원합니다.                    | 1994년 8월 27일                                                  |  |  |  |  |  |  |

|                                                  | 장 거하                                           | 인 번리사 양 순 석                                                   |  |  |  |  |  |  |

|                                                  | 60조의 규정에 의하여 위와 같이 출원심사를 청년<br>대리역             | 구합니다.<br>인 번리사 양 순 석                                          |  |  |  |  |  |  |

|                                                  | 출원서 부본 2통                                      | 수 수 료                                                         |  |  |  |  |  |  |

|                                                  | 명세서,요약서 및 도면 각 3통<br>위임장 1통                    | 출 원 로 기 본 17 먼 18,000 원 : · · · · · · · · · · · · · · · · · · |  |  |  |  |  |  |

|                                                  | 076                                            | 심사청구료 4/11항 277,000 원                                         |  |  |  |  |  |  |

- 梁淳錫特許法律事務所 -

\$ 569-4653 569-4654, FAX 569-4655

295,000 원

# 명 섀 서

## 1. 발명의 명칭

반도체장치의 제조방법

# 2. 도먼의 간단한 설명

제 1 도 및 제 2 도는 종래기술의 도면이고,

제 3 도 내지 제 6 도는 본 발명의 기술을 도시한 것이다.

※ 도면의 주요부분에 대한 부호의 설명

11,21,31. 반도체기판

12,22,32. 필드산화막

13,23,33. 소오스 및 트레인영역

14,24,34. 게이트

14',24',25',34-1. 사이드월

44-3, 연결라인

15,25,35. 충간절연막

57. 단차

34-1,34-2,44-2,54-2,64-2,67. 에치스탑층 16,26,36. 도전층

# 3. 발명의 상세한 설명

본 발명은 반도체장치의 제조방법에 관한 것으로서, 특히 콘택홀 형성 시에 얼라인마진 확보하여 소자의 특성을 개선하는 반도체장치의 제조방법 에 관한 것이다.

078

제 1 도의 (가)는 종태의 반도체장치의 단면도이고, 제 1 도의 (나)는

(17 - 1)

종래기술의 문제점을 도시한 것이다.

제 1 도의 (가)에 도시한 구조를 만들기 위하여 먼저, 반도체기판(11)에 필드산화막(12)으로 액티브영역을 격리하고, 게이트산화막, 폴리 및 게이트캡을 차례로 중착한 후, 식각하여 MOS 게이트(14)를 형성한다.

다음 이온주입공정으로 저농도불순물영역을 형성하고 증착 및 에치백공 정을 이용하여 게이트 사이드월(14')을 형성한 다음 사이드월을 마스크로 이온주입하여 고농도 불순물영역을 형성하여 소오스 및 드레인영역(13)을 만든다.

다음 트랜지스터 상에 충간절언막(I5)을 증착하고 충간절언막을 식각하여 소오스 및 드레인영역을 오픈하는 콘택홀을 형성한다.

이어 도전층(16)을 중착하여 트랜지스터의 소오스 및 드레인영역과 정 션콘택을 형성하도록 하여 공정을 완료한다.

제 1 도의 (나)에 도시한 바와 같이 위의 종래의 기술에서는 게이트와 정션콘택간의 충분한 파괴전압을 확보하기 위한 충간절연막의 두꼐조절을 사진공정의 얼라인 정확도에 의존하게 된다.

그런대 미스얼라인 발생시 B부분과 같이 게이트사이드월(14')에 손상을 . 주어서 문제가 되거나, 액티브영역을 격리하는 필드산화막에도 손상(도면의

(17-2) 079

A부분)을 주게 되어 정선리키지의 원인이 되었다.

따라서 이러한 문제점을 개선하고자 하는 노력으로 제 2 도에 도시한 . 바와 같은 구조가 제안되었다.

제 2 도의 (가)는 재 1 도의 구조를 개선한 단면도이고, (나)도는 제 2 도의 (가)의 문제발생부위의 단면도이다.

제 2 도의 (가)와 같이 일반적인 방법으로 트랜지스터를 형성한 다음, 총간의 격리를 위하여 총간절연막(25)을 증착하고 트랜지스터의 소오스 및 드레인영역이 오픈되도록 총간절연막을 식각하여 콘택홀을 형성한다.

여기서 도면부호 21은 반도계기판, 22는 필드산화막, 24는 게이트, 24'는 게이트사이드월을 나타낸다.

다음 얼라인 마진을 확보하여 파괴전압 특성을 좋게 하기 위하여 증착 및 애치백공정을 사용하여 콘택홀 내부의 충간절연막 축벽에 사이드월(25') 을 형성한다.

다음 전도성 물질을 증착하여 콘택홀 내에 도전층(26)을 형성한다.

그러나 제 2 도의 (나)에 도시한 바와 같이 콘택홀 내부의 충간절연막 축벽에 사이드월을 형성하는 공정은 콘택얼라인이 마진에서 벗어나서 콘택 홀이 게이트의 턱에 걸쳐지는 경우 C부분에서 파괴전압에 의한 문제가 발생

080

negret

할 수 있는 문제가 있다.

또한 고집적화 경향에 따라 콘택홀의 사이즈가 일정사이즈 이하로 작게 디파인 되었을 경우, 충간절연막 측벽의 사이트월형성공정에 의하여 콘택홀의 내부를 필링하는 효과가 발생하게 되고, 이로 인해 콘택오픈(도면의 D부분)에 문제가 발생하며 소자의 스케일 다운에도 문제가 있다.

본 발명은 이와 같은 문제를 해결하기 위하여 안출되었으며, 콘택홀부분에 에치스톱층을 형성하여 하부의 절연막을 보호함으로서 콘택홀 형성시 공정 얼라인마진을 확보하는 반도체장치의 구조 및 그 제조방법에 관한 것 이다.

본 발명의 방법은 반도체장치의 제조방법에 있어서, 가) 반도체기판 상의 액티브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나) 상기 트랜지스터의 전면에 이후의 공정에서 형성할 충간철연막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 애치백하여 상기 소오스 및 드레인영역 둘레에 에치스톱층을 형성하는 단계와, 다) 전면에 충간 격리용 절연물질을 중착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱층의 법위 내에 콘택홀을 형성하여 소오스 및 드레인영역을 오

(17 - 4)

픈하고, 오픈 부위에 도전층을 언결하는 단계를 포함한다.

제 3 도는 본 발명의 방법에 의한 반도체장치의 제조공정을 도시한 것이다.

도면을 참조하여 본 발명의 일실시에를 설명하면 다음과 같다.

제 3 도의 (가)에서 도시하여 보인 바라 같이, 반도체기판(31)에 필드산화막(32)을 형성하여 액티브영역을 주변의 액티브영역과 전기적으로 격리시키고, 게이트산화막, 폴리 및 게이트캡을 차례로 증착한 후, 식각하여 MOS 게이트(34)를 형성한다.

다음 이온주입공정으로 저농도불순물영역을 형성하고 증착 및 에치백공 정을 이용하여 개이트 사이드월(34-1)을 형성한 다음 사이드월을 마스크로 이온주입하여 고농도 불순물영역을 형성하여 소오스 및 드레인영역(33)을 만든다.

이러한 공정까지는 종래의 공정과 동일하게 진행한다.

다음 제 3 도의 (나)와 같이 게이트사이드월의 표면에 이후의 공정에서 형성하는 충간절연막과 식각선택비가 큰 물질을 증착한 후, 에치백하여서 콘택식각공정의 에치스롭층(34-2)을 사이드월의 형태로 불순물영역의 둘레 에 형성한다.

(17 - 5)

Sim.

이때 에치스톱층은 전도성 또는 비전도성 물질로 형성하며, 추가 마스크 없이 하층에 형성한 단차부분을 이용하여 증착 및 에치백공정으로 사이드월형태로 형성한다.

제 3 도의 (다)와 같이 층간절면막(35)을 증착하고 에치스룹층(34~2)의 범위에서 벗어나지 않도록 층간절연막을 식각하여 콘택홀을 형성한다.

제 3 도의 (라)와 같이 다음 전도성 물질로 형성한 도전층(36)으로 트 랜지스터의 소오스 및 드레인영역과 정선콘택을 형성하도록 한다.

제 4 도는 본 발명의 제 2 실시예를 도시한 것으로서, 제 1 실시예의 애치스톱층형성시 이용하는 하층의 단차가 불충분 할 경우, 인접해서 지나가는 내부연결라인(44-3) 또는 더미패턴(Dummy Patern)의 단차를 이용하여 애치스톱층(44-2)을 형성하는 방법이다.

제 5 도는 본 발명의 제 3 실시예의 도면이다.

에치스톱층을 형성하기 위한 하층의 단차가 불충분하고 제 2 실시여의 방법을 사용할 수 없을 경우, 기판 상의 산화막(필드산화막, 게이트사이드 월, 캡산화막)을 마스크로 하여 반도채기판을 식각하여 단차를 임의로 형성 한 단차(57)를 이용하여 에치스톱층(54-2) 형성을 위한 단차를 확보하는 방 법을 사용한다.

(17 - 6) 083

제 6 도는 본 발명의 또다른 실시예이다.

제 1 내지 제 5 실시에의 에치스룹층(64-2)형성시 비등방성식각으로 인한 하층의 손상을 방지하기 위하여 에치스룹층의 형성전에 또하나의 에치스룹층(67)을 소오스 및 드레인영역 상에 형성하는 방법이다.

이 경우 에치스톱층의 재질은 전도성 또는 비전도성 물질 모두 가능하며 비전도성물질로 형성할 경우 콘택홀 형성시 식각하여 제거한다.

본 발명의 효과는 다음과 같다.

첫째, 본 발명에서 추가로 형성하는 에치스톱층을 별도의 마스크없이 셀프얼라인으로 형성할 수 있으므로 추가공정이 없다.

둘째, 에치스톱층으로 스트레스가 집중되는 부위를 보호하므로 정선리 키지의 발생점이 될 수 있는 부분을 식각공정으로부터 보호할 수 있다.

셋째, 에치스톱층에 의하여 게이트사이드월이 깎이는 것을 방지함으로 서 게이트사이드월의 두깨의 조절만으로 게이트와 콘택간의 파괴전압(Break Down Voltage)을 확보함 수 있다.

넷째, 콘택사진시 얼라인 마진확보에 용이하다.

다섯째, 콘택홀 형성 후, 홀 내부에 벌도의 사이드월을 사용하지 않으므로 콘택홀스캐일다운에 용이하다.

### 4. 특허청구의 범위

- 1. 반도체장치의 재조방법에 있어서,

- 가) 반도체기판 상의 액티브영역에 개이트와 게이트 주변의 기판에 불 순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와,

- 나) 상기 트랜지스터의 전면에 이후의 공정에서 형성할 충간절면막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 에치백하여 상기 소오스 및 드레인영역 둘레에 에치스롭층을 형성하는 단계와,

- 다) 전면에 층간 격리용 절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱층의 범위 내에 콘택홀을 형성하여 소오스 및 드래인영역을 오픈하고, 오픈 부위에 도전층을 연결하는 단계를 포함하는 반도체장치 제조방법.

- 2. 제 1 항에 있어서,

상기 <u>에치스톱용 사이드</u>월은 전도성물질인 것이 특징인 반도체장치 제조방법.

3. 제 1 항에 있어서,

상기 에<u>치스톱</u>용 사이드월은 비전도성 물질인 것이 특징인 반도체장치

(17 - 8)

제조방법.

4. 제 1 항에 있어서,

상기 사이드웰의 형성은 하층의 단차를 이용하는 것이 특징인 반도채장 치 제조방법.

5. 제 1 항에 있어서,

상기 사이드월은 인접한 하층의 연결라인의 단차를 이용하거나, 혹은 인접한 더미패턴을 형성하여 그 단차를 이용하는 것이 특징인 반도체장치 제조방법.

- 6. 반도체장치의 제조방법에 있어서,

- 가) 반도채기판 상의 액티브영역에 게이트와 게이트 주변의 기판에 불 순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와,

- 나) 상기 소오스 및 드레인영역 상에 <u>제 2 에치스톱층을 형성하는</u> 단계 와,

- 다) 상기 트렌지스터의 전면에 이후의 공정에서 형성할 충간절연막과 식각선택비가 큰 물질을 충착한 후, 비등방성식각공정으로 에치백하여 상기 소오스 및 드레인영역 둘레에 제 1 에치스톱충을 형성하는 단계와,

(17 - 9)

라) 전면에 총간 격리용 절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스룹층의 법위 내에 콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전총을 연결하는 단계를 포함하는 반도체장치 제조방법.

7. 제 6 항에 있어서,

상기 제 1 에치스톱층은 전도성물질인 것이 특징인 반도채장치 제조방법.

8. 제 6 항에 있어서,

상기 제 1 에치스튬층은 비전도성물질인 것이 특징인 반도체장치 제조 방법.

9. 제 6 항에 있어서,

상기 제 2 에치스톱층은 전도성물질인 것이 특징인 반도체장치 제조방법.

10. 제 6 항에 있어서,

상기 쟤 2 에치스뽑층은 비전도성 물질이며,

콘택홀형성시 함께 제거하는 것이 특징인 반도체장치 제조방법.

11. 반도체장치의 재조방법에 있어서,

( 17 - 10 ) 87

가) 반도체기판 상의 필드산화막으로 정의한 액티브영역에 개이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와,

나) 트랜지스터를 형성하는 절연막 및 필드산화막을 마스크로 하여 반 도체기판을 셀프얼라인으로 식각하여 소오스 및 드레인영역의 기판에 단차 를 형성하는 단계와,

다) 상기 트랜지스터의 전면에 이후의 공정에서 형성할 충간절연막과 식각선택비가 큰 물질을 중착한 후, 비등방성식각공정으로 에치백하여 상기 기판의 단차를 이용하여 소오스 및 드레인영역 둘레에 에치스톱층을 형성하 는 단계와,

라) 전면에 충간절연막을 증착한 후, 포토리소그래피공정을이용하여 사이드월 안쪽에 에치스뽑층의 범위 내에 콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전층을 연결하는 단계를 포함하는 반도체장치 제조방법.

12. 제 11 항에 있어서,

상기 제 1 에치스톱층은 전도성물질인 것이 특징인 반도체장치 제조방법.

088

13. 제 11 항에 있어서,

상기 제 1 에치스폽층은 비전도성물질인 것이 특징인 반도체장치 제조 방법.

14. 반도체기판 상에 필드산화막으로 정의 한 액티브영역에 게이트산화막, 도전층 게이트캡으로 형성하며 게이트사이드월을 형성한 게이트와, 소오스 및 드레인영역으로 구성한 트랜지스터와,

상기 트랜지스터상에 형성한 충간절언막과,

트랜지스터의 소오스 및 드레인영역을 오픈하며 상기 충간절언막을 관통하는 콘택홀과,

상기 콘택홀을 채우는 도전층을 포함하는 반도체장치에 있어서,

상기 소오스 및 드레인영역 둘레의 영역에 충간절연막 아래에 충간절연 막과 식각선택비가 큰 물질을 형성한 것이 특징인 반도체장치.

15. 제 14 항에 있어서,

상기 식각선택비가 큰 물질은 전도성물질인 것이 특징인 반도채장치.

-089

요 약 서

본 발명은 콘택홀부분에 에치스톱층을 형성하여 하부의 절연막을 보호 함으로서 콘택홀 형성시 공정 얼라인마진을 확보하는 반도계장치의 구조 및 그 제조방법에 관한 것이다.

본 발명은 반도채장치의 제조방법에 있어서, 가) 반도체기판 상의 액티 브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나) 상기 트랜지스터의 전면에 이후의 공정에서 형성할 충간절언막과 식각선택비가 큰물질을 중착한 후, 비등방성식각공정으로 에치백하여 상기 소오스 및 드레인영역 둘레에 에치스톱층을 형성하는 단계와, 다) 전면에 충간 격리용 절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱층의 법위 내에 콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전층을 연결하는 단계를 포함하는 방법으로 제조한다.

(  $_{17}$  -  $_{13}$  ) 090

مدا. شهرعه 제 1 25=47/4 M.5 7.75 - 16 . 14 -15 (17) -12 13 22/500022 -11 A-1: 25% B -16 enis .15 @xx/grive ( Lt ) -12 A٠ A

Bendander Bendander Anderse und Bendander Beigen auf Bendander Bendander Bendander Bendander und Bendander Beigen auf Bendander Bendander Beigen auf Bendander Bendande 21 ≥ pipe 14' 13 4 2 11.ر 舏 2 모 25' 9m254 -26 邮告 - 25 (1F) -22 24 515 ~ 21 091 ( 17 - 14 )

.32 ⊙<sub>∞</sub> ç

-31

( 권 )

A STATE OF THE STA

093 ( 17 - 16 )

#### **X**{| 6

- D 1996年1996年 被车车时代放伏

- D 刚并生就蒙电影 二色环识别 特殊识先 英於鞋 肚乳

- A 四川三部参加 明知·州州东西公安縣日 智川先次专 1857

- p 2% Now while with the second

- o how he crawed the