(19) Korean Intellectual Property Office (KR)

(12) Office Gazette on a Published Patent (A)

(51) Int. Cl.<sup>6</sup> H01L 21/128 (11) Publication number Teuk 1996-0009001

(43) Date of publication: March 22, 1996

(21) Application number: Teuk 1994-0021255(22) Date of application: August 27, 1994

(71) Applicant: Jeong Hwan Moon, Gold Star Electron Co., Ltd.

50 Hyangjeong-dong, Cheongju-si, Chungcheongbuk-do (Postal Code: 360-480)

(72) Inventor: Jeung Sang Lee

1390 (35/2) Wooncheon-dong, Cheongju-si, Chungcheongbuk-do

(74) Attorney: Soon Seok Yang

## Examination application: Yes

### (54) A Method for Fabricating Semiconductor Device

#### **ABSTRACT**

The present invention relates to the structure of a semiconductor device in which a process alignment margin is secured when forming a contact hole by forming an etch stop layer on the contact hole area to protect the lower insulation layer and a method for fabricating this structure.

The present invention fabricates a semiconductor device using a method comprised of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate; b) a step of forming an etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and c) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

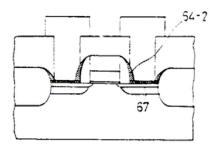

# Representative Drawing

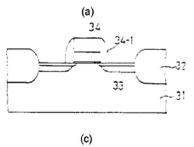

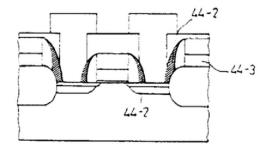

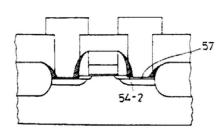

## FIG. 3

# SPECIFICATIONS

[Name of invention]

A Method for Fabricating Semiconductor Device

[Brief explanation of the drawings]

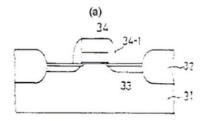

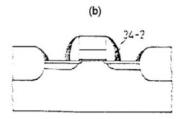

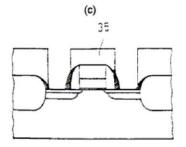

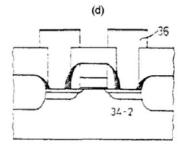

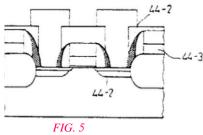

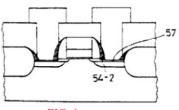

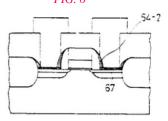

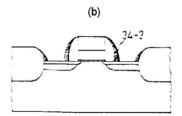

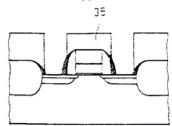

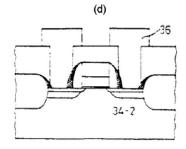

FIGs. 3 to 6 illustrate the technology of the present invention.

The whole text of this patent is not contained herein since this is a case of summarized publication.

### (57) Scope of claims

### Claim 1

A method for fabricating a semiconductor device which comprises of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate; b) a step of forming an etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and c) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

### Claim 2

The method for fabricating a semiconductor device in Claim 1, wherein the sidewall for etch stop is composed of a conductive material.

# Claim 3

The method for fabricating a semiconductor device in Claim 1, wherein the sidewall for etch stop is composed of a non-conductive material.

### Claim 4

The method for fabricating a semiconductor device in Claim 1, wherein the sidewall is formed using the step at the lower layer.

### Claim 5

The method for fabricating a semiconductor device in Claim 1, wherein the sidewall uses either the step of the connection line at the adjacent lower layer or uses the step by forming an adjacent dummy pattern.

#### Claim 6

A method for fabricating a semiconductor device which comprises of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region on a semiconductor substrate and the substrate around the gate; b) a step of forming the second etch stop layer on said source and drain region; c) a step of forming the first etch stop layer around said source and drain region by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and d) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the insulating material for interlayer isolation to the front, and then connecting the conductive layer to the opened area.

### Claim 7

The method for fabricating a semiconductor device in Claim 6, wherein the first etch stop layer is composed of a conductive material.

### Claim 8

The method for fabricating a semiconductor device in Claim 6, wherein the first etch stop layer is composed of a non-conductive material.

### Claim 9

The method for fabricating a semiconductor device in Claim 6, wherein the second etch stop layer is composed of a conductive material.

## Claim 10

The method for fabricating a semiconductor device in Claim 6, wherein the second etch stop layer is composed of a non-conductive material and it is removed together when the compared to is formed.

## Claim 11

A method for fabricating a semiconductor device which comprises of a) a step of fabricating a transistor by making a source and drain region which is formed by doping impurity on the gate in the active region defined by a field oxide layer on a semiconductor substrate and the substrate around the gate; b) a step of from a step on the substrate in the source and drain region by etching the semiconductor substrate using the insulation layer and field oxide layer forming the transistor as a mask, c) a step of forming the etch stop layer around said source and drain region using said step of the substrate by depositing a material having a high etch selectivity with an interlayer insulation film, which is going to be formed in a later process, to the front of said transistor and then, conducting etch-back using an anisotropic etching process; and d) a step of opening the source and drain region by forming a contact hole within the range of the etch stop layer inside the sidewall using a photo lithography process after depositing the interlayer insulation film to the front, and then connecting the conductive layer to the opened area.

### Claim 12

The method for fabricating a semiconductor device in Claim 11, wherein the first etch stop layer is composed of a conductive material.

# Claim 13

The method for fabricating a semiconductor device in Claim 11, wherein the first etch stop layer is composed of a non-conductive material.

### Claim 14

The semiconductor device which comprises of a gate for which gate oxide layer and conductive layer gate cap are formed on the active region defined by a field oxide layer on a semiconductor substrate and a gate sidewall is formed, a transistor composed of a source and drain region, a interlayer insulation film formed on the transistor, a contact hole which opens the source and drain region of the transistor and penetrates the above interlayer insulation film, and the conductive layer filling the contact hole, wherein a material having a high etch selectivity with the interlayer insulation film is formed under the interlayer insulation film in the area surrounding the source and drain region.

## Claim 15

The semiconductor device in Claim 14, wherein the material with a high etch selectivity is conductive.

\* Note: This is a disclosure by the contents of the first application.

# Drawings

# FIG. 3

FIG. 4

*FIG.* 6

3-3

City of New York, State of New York, County of New York

I, Kelly Kim, hereby certify that the following document is, to the best of my knowledge and belief, a true and accurate translation from Korean to English

"KR Pub. No. 1996-0009001"

Kelly Kim

Sworn to before me this

Tuesday, April 28, 2015

Signature, Notary Public

AMY LEONG

Notary Public - State of New York

No. 01 LE6314554

Qualified in Richmond County

Commission Expires Nov 10, 2018

Stamp, Notary Public

# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>6</sup><br>_HO1L_21/128 | (11) 공개번호 특1996-0009001<br>(43) 공개일자 1996년03월22일 |  |

|--------------------------------------------|--------------------------------------------------|--|

| (21) 출원번호<br>_(22) 출원일자                    | 특 1994-0021255<br>1994년08월27일                    |  |

| (71) 출원인                                   | 금성일렌트론 주식회사 문정환                                  |  |

| (72) 발명자                                   | 충청북도 청주시 향정동 50번지 (우 : 360-480 )<br>이증상          |  |

| (74) 대리인                                   | 충청북도 청주시 운천동 1390(35/2)<br>양순석                   |  |

| 실사청구 : 있음                                  |                                                  |  |

# (54) 반도체 장치의 제조방법

#### 요약

본 발명은 콘택홀부분에 에치스톱층을 형성하여 하부의 절연막을 보호함으로서 콘택홀 형성시 공정 얼라 인마진을 확보하는 반도체장치의 구조 및 그 제조방법에 관한 것이다.

본 발명은 반도체장치의 제조방법에 있어서, 가)반도체기판 상의 액티브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나)상기 트랜지스터의 전면에 이후의 공정에서 형성할 총간절연막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 에치백하여 상기 소오스 및 드레인영역 둘레에 에치스톱총을 형성하는 단계와, 다)전면에 총간 격리용절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱 총의 범위 내에 콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전총을 연결하는 단계를 포함하는 방법으로 제조한다.

## 대표도

# *⊊3*

# 명세서

[발명의 명칭]

반도체 장치의 제조방법

[도면의 간단한 설명]

제3도 내지 제6도는 본 발명의 기술을 도시한 것이다.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음.

# (57) 청구의 범위

# 청구항 1

반도체장치의 제조방법에 있어서, 가)반도체기판 상의 액티브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나)상기 트랜지스터의 전면에 이후의 공정에서 형성할 총간절연막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 에치백하여 상기 소오스 및 드레인영역 둘레에 에치스톱총을 형성하는 단계와, 다)전면에 총간 격리용 절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱총의 범위내에 콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전총을 연결하는 단계를 포함하는 반도체장치 제조방법.

# 청구항 2

제1항에 있어서, 상기 에치스톱용 사이드월은 전도성물질인 것이 특징인 반도체장치 제조방법.

## 청구항 3

제1항에 있어서, 상기 에치스톱용 사이드월은 비전도성 물질인 것이 특징인 반도체장치 제조방법.

# 청구항 4

제1항에 있어서, 상기 사이드월의 형성은 하층의 단차를 이용하는 것이 특징인 반도체장치 제조방법.

# 청구항 5

제1항에 있어서, 상기 사이드월은 인접한 하층의 연결라인의 단차를 이용하거나, 혹은 인접한 더미패턴을 형성하여 그 단차를 이용하는 것이 특징인 반도체장치 제조방법.

#### 청구항 6

반도체장치의 제조방법에 있어서, 가)반도체기판 상의 액티브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나)상기 소오스 및 드레인영역 상에 제2에치스톱층을 형성하는 단계와, 다)상기 트랜지스터의 전면에 이후의 공정에서 형성할 총간절연막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 에치백하여 상기소오스 및 드레인영역 둘레에 제1에치스톱층을 형성하는 단계와, 라)전면에 총간 격리용 절연물질을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱층의 범위 내에 콘택홀을 형성하여소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전층을 연결하는 단계를 포함하는 반도체장치 제조방법.

## 청구항 7

제6항에 있어서, 상기 제1에치스톱층은 전도성물질인 것이 특징인 반도체장치 제조방법.

### 청구항 8

제6항에 있어서, 상기 제1에치스톱층은 비전도성물질인 것이 특징인 반도체장치 제조방법.

#### 청구항 9

제6항에 있이시, 상기 제2에치스톱층은 전도성물질인 것이 특징인 반도체장치 제조방법.

## 청구항 10

제6항에 있어서, 상기 제2에치스톱층은 비전도성 물질이며, 콘택홀형성시 함께 제거하는 것이 특징인 반도체장치 제조방법.

#### 청구항 11

반도체장치의 제조방법에 있어서, 가)반도체기판 상의 필드산화막으로 정의한 액티브영역에 게이트와 게이트 주변의 기판에 불순물을 도핑하여 형성하는 소오스 및 드레인영역을 만들어서 트랜지스터를 제조하는 단계와, 나)트랜지스터를 형성하는 절연막 및 필드산화막을 마스크로 하여 반도체기판을 셀프얼라인으로 식각하여 소오스 및 드레인영역의 기판에 단차를 형성하는 단계와, 다)상기 트랜지스터의 전면에이후의 공정에서 형성할 층간절연막과 식각선택비가 큰 물질을 증착한 후, 비등방성식각공정으로 에치백하여 상기 기판의 단차를 이용하여 소오스 및 드레인영역 둘레에 에치스톱층을 형성하는 단계와, 라)전면에 층간절연막을 증착한 후, 포토리소그래피공정을 이용하여 사이드월 안쪽에 에치스톱층의 범위 내에콘택홀을 형성하여 소오스 및 드레인영역을 오픈하고, 오픈 부위에 도전층을 연결하는 단계를 포함하는 반도체장치 제조방법.

# 청구항 12

제11항에 있어서, 상기 제1에치스톱층은 전도성물질인 것이 특징인 반도체장치 제조방법.

## 청구항 13

제11항에 있어서, 상기 제1에치스톱층은 비전도성물질인 것이 특징인 반도체장치 제조방법.

# 청구항 14

반도체기판 상에 필드산화막을 정의 한 액티브영역에 게이트산화막, 도전층 게이트캡으로 형성하며 게이트사이드월을 형성한 게이트와, 소오스 및 드레인영역으로 구성한 트랜지스터와, 상기 트랜지스터상에 형성한 층간절연막과, 트랜지스터의 소오스 및 드레인영역을 오픈하여 상기 층간절연막을 관통하는 콘택홀과, 상기 콘택홀을 채우는 도전층을 포함하는 반도체장치에 있어서, 상기 소오스 및 드레인영역 둘레의 영역에 층간절연막 아래에 층간절연막과 식각선택비가 큰 물질을 형성한 것이 특징인 반도체장치.

# 청구항 15

제14항에 있어서, 상기 식각선택비가 큰 물질은 전도성물질인 것이 특징인 반도체장치.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

# 도면

# 도면3

도면4

도면5

도면6