Paper No. \_\_\_\_\_ Filed: March 10, 2016

Filed on behalf of: Samsung Electronics Company, Ltd.

By: Naveen Modi (nVidia-Samsung-IPR@paulhastings.com)

Joseph E. Palys (nVidia-Samsung-IPR@paulhastings.com)

Paul Hastings LLP

NVIDIA CORPORATION

Petitioner

v.

SAMSUNG ELECTRONICS COMPANY, LTD.

Patent Owner

Case IPR2015-01327 Patent No. 6,287,902

DECLARATION OF DR. RICHARD B. FAIR

## TABLE OF CONTENTS

|       |                                                                                  |                               |                                                                                                                                  | Page |  |  |  |

|-------|----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| I.    | INTRO                                                                            | ODUCT                         | ION                                                                                                                              | 1    |  |  |  |

| II.   | RESO                                                                             | RESOURCES CONSULTED1          |                                                                                                                                  |      |  |  |  |

| III.  | BACK                                                                             | BACKGROUND AND QUALIFICATIONS |                                                                                                                                  |      |  |  |  |

| IV.   | LEVE                                                                             | LEVEL OF ORDINARY SKILL       |                                                                                                                                  |      |  |  |  |

| V.    | SCOPE OF PROJECT                                                                 |                               |                                                                                                                                  |      |  |  |  |

| VI.   | CLAIM CONSTRUCTION                                                               |                               |                                                                                                                                  |      |  |  |  |

|       | A.                                                                               |                               | culating spacer along a sidewall of the [second] patterned conductive (Claims 1, 11, 12, 15, and 18)                             | 9    |  |  |  |

|       | B.                                                                               | "an ins                       | ulating layer" (Claims 1, 2, 8, 11, 12, 14-18)                                                                                   | 10   |  |  |  |

|       | C.                                                                               |                               | ng a trench in said substrate, and wherein said field isolation layer id trench" (Claim 6)                                       | 10   |  |  |  |

| VII.  | OVERVIEW OF THE '902 PATENT AND CITED REFERENCES 1                               |                               |                                                                                                                                  |      |  |  |  |

|       | A.                                                                               | Overvi                        | ew of the '902 Patent                                                                                                            | 11   |  |  |  |

|       | B.                                                                               | Overvi                        | ew of <i>Lee</i>                                                                                                                 | 13   |  |  |  |

|       | C.                                                                               | Overvi                        | ew of Yasushige                                                                                                                  | 15   |  |  |  |

| VIII. | RESPONSE TO PETITIONER'S MAPPING OF THE CLAIMED FEATURES TO THE CITED REFERENCES |                               |                                                                                                                                  |      |  |  |  |

|       | A.                                                                               | Independent Claim 1           |                                                                                                                                  | 19   |  |  |  |

|       |                                                                                  | 1.                            | Lee Does Not Disclose or Suggest a "Second Patterned Conductive Layer [that] Is a Dummy Pattern"                                 | 19   |  |  |  |

|       |                                                                                  | 2.                            | Lee Does Not Disclose or Suggest that the "Dummy Pattern" is "Electrically Isolated from the Substrate and Circuits Thereon"     | 22   |  |  |  |

|       |                                                                                  | 3.                            | Lee Does Not Disclose an "Insulating Spacer Along a Sidewall of the Second Patterned Conductive Layer [That] Is a Dummy Pattern" | 28   |  |  |  |

|       |                                                                                  | 4.                            | One of Ordinary Skill in the Art Would Not Have Combined <i>Lee</i> with <i>Yasushige</i> as Proposed by Petitioner              | 30   |  |  |  |

|       | B.                                                                               | Claims                        | 3-5, 7-12, 14-16, and 18                                                                                                         | 32   |  |  |  |

|       |                                                                                  | 1.                            | Claim 7                                                                                                                          | 33   |  |  |  |

|       |                                                                                  | 2.                            | Claim 10                                                                                                                         | 34   |  |  |  |

|       | C.                                                                               | Claims                        | 2 and 17                                                                                                                         | 35   |  |  |  |

|       | D.                                                                               | Claims                        | 6 and 13                                                                                                                         | 35   |  |  |  |

| IX.   | CONC                                                                             | CLUSIO                        | N                                                                                                                                | 37   |  |  |  |

#### I. INTRODUCTION

1. I have been retained by Samsung Electronics Company, Ltd. ("Patent Owner" or "Samsung") for this *inter partes* review proceeding. I understand that this proceeding involves U.S. Patent No. 6,287,902 ("the '902 patent"). I understand the '902 patent is assigned to Samsung and issued from U.S. Patent Application No. 09/318,188, which is a division of U.S. Patent Application No. 08/748,148, filed on November 12, 1996 (now abandoned).

#### II. RESOURCES CONSULTED

- 2. I have reviewed the '902 patent, including claims 1-18. I have also reviewed the Petition for *Inter Partes* Review (Paper No. 2) filed with the U.S. Patent and Trademark Office ("Office") by nVidia Corporation ("Petitioner" or "nVidia") on June 2, 2015 (Paper No. 2, the "Petition"). I have also reviewed the Patent Trial and Appeal Board's ("Board") decision to institute *inter partes* review (Paper No. 9, the "Decision") of December 9, 2015, and any other materials identified in this declaration.

- 3. I understand that in this proceeding the Board instituted review of the '902 patent on three grounds: (1) obviousness of claims 1, 3-5, 7-12, 14-16, and 18 over KR App. No. 1994/021255 to Lee ("Lee", Ex. 1107) in view of JP Pub. No. H7-86158 to Yasushige ("Yasushige", Ex. 1109); (2) obviousness of claims 2 and 17 over Lee, Yasushige, and U.S. Patent No. 4,916,514 to Nowak ("Nowak",

Ex. 1110); and (3) obviousness of claims 6 and 13 over *Lee*, *Yasushige*, and U.S. Patent No. 4,952,524 to Lee et al. ("*Lee II*", Ex. 1111). (Decision at 19.) I have reviewed the exhibits and other documentation supporting the Petition that are relevant to the Decision and the instituted grounds, and any other material that I reference in this declaration.

## III. BACKGROUND AND QUALIFICATIONS

- 4. I have summarized in this section my educational background, career history, publications, and other relevant qualifications. A more detailed account of my work experience, qualifications, and publications is included in my *curriculum vitae*, which is appended to this declaration.

- 5. By way of summary, I have been a professor in the Department of Electrical and Computer Engineering at Duke University since 1981. My current tenured position is the Lord-Chandran Professor of Engineering in the Pratt School of Engineering.

- 6. I received my Bachelor of Science degree in Electrical Engineering from Duke University in 1964. In 1966, I received a Master of Science degree in Electrical Engineering from Penn State University. In 1969, I received a Ph.D. in Electrical Engineering from Duke University.

- 7. Since 1969, I have been involved in the research, teaching, development, design, and manufacturing of semiconductor devices and processes.

For example, I have experience with thin film processes such as physical and chemical vapor deposition methods, modeling semiconductor technology, designing integrated circuits and semiconductor chips, designing high-density memory and analog circuit layouts, and fabricating integrated circuits. In addition, I have experience in the design, layout, and simulation of analog and digital integrated circuits.

- 8. From 1969 to 1981, I worked at Bell Laboratories and I had direct experience with the manufacturing, design, and testing of numerous semiconductor devices and integrated circuits, including metal-oxide-semiconductor (MOS) dynamic memory chips. I researched and developed numerous semiconductor devices, including silicon and gallium arsenide transistors, analog and digital integrated circuits, photovoltaic devices, and thin film transistors ("TFTs") fabricated in laser recrystallized polycrystalline silicon.

- 9. During my time at Bell Laboratories, I worked on advanced silicon process development in the areas of photolithography, thin film deposition, metallization, etching, cleaning, plasma-assisted processing, LPCVD, ion implantation doping, and annealing/oxidation.

- 10. In 1981, I became Professor of Electrical Engineering at Duke

University. At the same time, I also served in a joint role as Vice President of the

Microelectronics Center of North Carolina ("MCNC") in Research Triangle Park,

North Carolina. During 1990-1993, I led the Center for Microelectronic Systems. The MCNC and the Center for Microelectronic Systems were devoted to the development of advanced technologies for fabricating integrated circuits and for improvements in semiconductor manufacturing processes in general. My areas of responsibility as Vice President included analog and digital integrated circuit design, system design, semiconductor fabrication technology, advanced multichip module packaging, and studies in electronic materials, including amorphous semiconductors and multi-layered aluminum and copper interconnects. In my division at MCNC, we designed, fabricated, and tested the world's first onemillion-transistor processor chip in 1987. I also was responsible for the MCNC analytical lab, which included electron microscopy, atomic composition analysis, and sample preparation for reverse engineering studies. I have used such analytical tools to perform reverse engineering of semiconductor devices.

11. While at MCNC, I helped setup a state-of-the-art CMOS processing facility and directed research on semiconductor processing including photolithography, wafer cleaning, annealing, ion implantation, plasma-enhanced CVD of thin films, metallization, and anisotropic etching processes. I was also involved in the development of an advanced patterning program that included advanced photoresist development, DUV lithography, and the design and development of a magnetron reactive etching tool. We conducted research on

multi-level metal interconnects, barrier metallurgy, organic and inorganic intermetal dielectrics, anti-reflective coatings, via and trench etching processes, and selective tungsten deposition for via filling. We also had an active research program in characterizing point defects in ion implanted amorphous and single crystal silicon, with the goal of understanding implantation defect annealing effects on dopant impurity diffusion.

- 12. In 1994, I returned to Duke University full-time. Since then I have continued to teach courses on (1) the design and analysis of analog and digital integrated circuits, (2) semiconductor devices, (3) the chemistry and physics of transistor and integrated circuit fabrication, and (4) thin-film microfluidic devices, fluid dynamics, and applications. In addition, I have an active funded research program that involves undergraduate and graduate students.

- 13. I have published over 170 papers in refereed and peer-reviewed journals and conference proceedings, contributed chapters to 12 books, edited nine books or conference proceedings, given over 130 invited talks in the field of electrical engineering, and I am a named inventor on 30 granted U.S. patents and 24 pending U.S. patent applications.

- 14. I am also a Life Fellow of the Institute of Electrical and Electronic Engineers ("IEEE"), a Fellow of the Electrochemical Society, past Editor-in-Chief of the Proceedings of the IEEE, and past Associate Editor of the IEEE

Transactions on Electron Devices. I have been listed in Who's Who in America, Who's Who in Engineering, Who's Who in the Semiconductor Industry, Who's Who in Frontiers of Science and Technology, Who's Who in Technology Today, and American Men and Women in Science. I am a recipient of the IEEE Third Millennium Medal, and I was awarded the Solid State Science and Technology Medal of the Electrochemical Society in April 2003.

Based on my over 45 years of experience in thin film and bulk 15. semiconductor device design, processing technology research and development, integrated circuit fabrication, research in point defects in amorphous and single crystal silicon, and the acceptance of my publications and professional recognition by societies in my field, I believe that I am considered to be an expert in the art of semiconductor processing, semiconductor device design and fabrication, and integrated circuit design and fabrication. I have extensive experience both in research and development, and in the implementation of semiconductor manufacturing processes. I have been qualified numerous times as an expert, and I have given expert opinion testimony relating to semiconductor processing, including MOSFET transistor gate formation, shallow-trench isolation, the use of dummy layer features in patterning, and chemical mechanical planarization. Additionally, I have extensive publications in the field of semiconductor

technology, and my accomplishments have been recognized by both academic and professional societies.

16. I am an independent consultant retained by Patent Owner to work on this case. I am compensated for my services in this case at the rate of \$600 per hour. My compensation is not dependent upon my opinions or testimony or the outcome of this case.

#### IV. LEVEL OF ORDINARY SKILL

17. I am familiar with the level of ordinary skill in the art with respect to the inventions of the '902 patent as of what I understand is the patent's November 12, 1996 effective filing date. Specifically, based on my review of the technology, the educational level and experience of active workers in the field, the types of problems faced by workers in the field, the solutions found to those problems, the sophistication of the technology in the field, and drawing on my own experience, I believe a person of ordinary skill in art at that time would have had (i) a bachelor's degree in electrical engineering, chemical engineering, materials science or physics and 2-3 years of experience in the development of semiconductor fabrication technology, or (ii) a master's degree in the same areas with 1-2 years of the same work experience. All of my opinions in this declaration are from the perspective of one of ordinary skill in the art as I have defined it here.

18. Petitioner's expert, Dr. Jack C. Lee, has defined the person of ordinary skill in the art as a person with an undergraduate degree in electrical engineering (or an equivalent subject) together with three to four years of post-graduate experience designing semiconductor devices and fabrication processes, or a master's degree in electrical engineering (or an equivalent subject) together with one to two years of post-graduate experience in designing semiconductor devices and fabrication processes. (Ex. 1116 at ¶ 19.) In my opinion, my definition is similar to the definition of Dr. Lee offers. While my analysis is based on my definition of the person of ordinary skill in the art, I believe my analysis and opinion would apply equally even under the definition of a person of ordinary skill in the art Dr. Lee proposes.

## V. SCOPE OF PROJECT

19. I have been asked to respond to certain of Petitioner's positions and opinions offered by Dr. Lee, including consider how one of ordinary skill in the art would have understood the references mentioned above in relation to the claims of the '902 patent.<sup>1</sup> I understand that the Board relied on Petitioner's positions and Dr. Lee's opinions in its Decision. As such, when I respond to Petitioner's

<sup>&</sup>lt;sup>1</sup> If I do not address a particular statement made by Petitioner, the Board, or Dr. Lee that does not mean that I necessarily agree with that statement.

positions and Dr. Lee's opinions in this declaration, I am necessarily responding to the Board's Decision as well. My findings are set forth below.

#### VI. CLAIM CONSTRUCTION

20. I understand that Petitioner identified certain terms for construction in the Petition. (Pet. at 25-27; *see also* Ex. 1116 at ¶¶ 70-79.) Below is a what I understand to be a summary of the constructions proposed by Petitioner and Patent Owner, along with the construction (if any) adopted by the Board in its institution decision.

A. "an insulating spacer along a sidewall of the [second] patterned conductive layer" (Claims 1, 11, 12, 15, and 18)<sup>2</sup>

| Patent Owner's Proposed    | Petitioner's Proposed           | Board's Construction |

|----------------------------|---------------------------------|----------------------|

| Construction               | Construction                    |                      |

| Plain and ordinary meaning | an insulating spacer, along     | No construction      |

|                            | a sidewall of the [second]      | proposed             |

|                            | patterned conductive layer,     |                      |

|                            | that prevents etch damage       |                      |

|                            | to the field isolation layer if |                      |

|                            | the contact hole is             |                      |

|                            | misaligned                      |                      |

|                            |                                 |                      |

<sup>&</sup>lt;sup>2</sup> I identify only the challenged claims that expressly recite the terms at issue.

## B. "an insulating layer" (Claims 1, 2, 8, 11, 12, 14-18)

| Patent Owner's Proposed    | Petitioner's Proposed      | Board's Construction |

|----------------------------|----------------------------|----------------------|

| Construction               | Construction               |                      |

| a structure comprising one | Plain and ordinary meaning | No construction      |

| or more electrically       |                            | proposed             |

| insulating sublayers       |                            |                      |

|                            |                            |                      |

# C. "forming a trench in said substrate, and wherein said field isolation layer fills said trench" (Claim 6)

| Patent Owner's Proposed    | Petitioner's Proposed      | Board's Construction |

|----------------------------|----------------------------|----------------------|

| Construction               | Construction               |                      |

| Plain and ordinary meaning | Plain and ordinary meaning | No construction      |

|                            |                            | proposed             |

|                            |                            |                      |

- 21. I also understand that the Board construed "dummy pattern," which is a term recited in claims 1, 11, 12, 15, and 18, as "a patterned conductive layer that serves no electrical purpose and is electrically isolated from the substrate and circuits thereon." (Decision at 7.)

- 22. I have considered the constructions proposed by the Petitioner, the Patent Owner, and the Board. My analysis and conclusions as set forth below in Section VIII remain the same under any of these constructions. For the remaining claim terms of the '902 patent that were not identified for construction by any party (including the Board), I have given those terms their plain and ordinary meaning, as would be understood by a person of ordinary skill in the art, at the

time of the invention, having taken into consideration the language of the claims, the specification, and the prosecution history of record.

#### VII. OVERVIEW OF THE '902 PATENT AND CITED REFERENCES

#### A. Overview of the '902 Patent

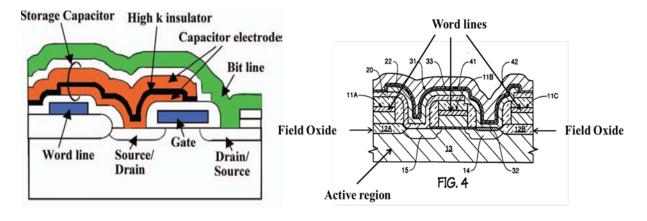

- 23. The '902 patent is directed to a method of providing improved alignment tolerances for contact holes made to scaled microelectronic structures. (Ex. 1001 at 2:44-48.) A problem that the '902 patent addresses is how to reliably make contact holes for MOSFETs in smaller and smaller spaces on a wafer when device integration density increases. (*Id.* at 2:10-41.) For instance, the '902 patent notes that a misaligned contact hole 24 may expose a portion of the active region of a MOSFET and an adjacent field region that may lead to the flow of leakage currents into the well area of the MOSFET. (*Id.* at 2:10-20, Fig. 2.)

- 24. To remedy the above problem resulting from contact hole misalignment, the '902 patent discloses an exemplary method of forming etch inhibiting layers on the field isolation region adjacent to the active region (where transistors are formed). The etch inhibiting layer improves alignment tolerance for a contact hole between a first patterned conductive layer on an active region of the substrate and an adjacent field region (which isolates an active region). (*Id.* at 4:41-50.) The exemplary solution disclosed in the '902 patent may be better understood by referring to the description associated with figures 4-8.

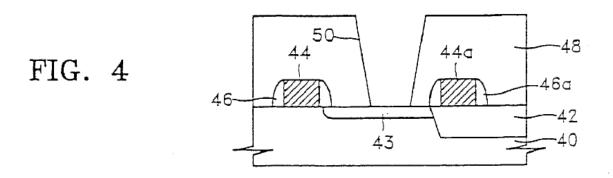

25. Figure 4 of the '902 patent discloses an exemplary embodiment in which a contact hole 50 is placed between first and second patterned conductive layers 44, 44a to make contact to the doped area 43 (source or drain of a transistor) in the active region. (*Id.* at 4:10-37.)

- 26. An insulating layer 48 covering the first and second patterned conductive layers 44, 44a, active region 43, and field isolation layer 42 is etched to form contact hole 50. (*Id.* at 5:62-65, 6:8-11, Fig. 7.)

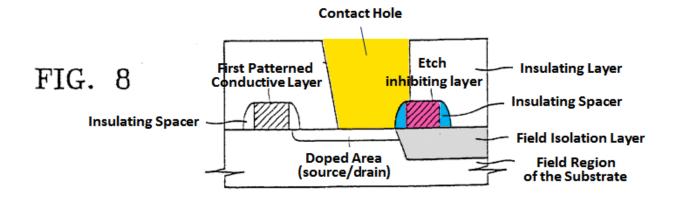

- 27. Conductive layer 44a (annotated in pink below), which is formed on the field isolation layer 42, in combination with sidewall spacers 46a (annotated in blue below) acts as an etch inhibiting layer protecting the field isolation layer from any undesired etching in case of a contact hole misalignment. (*Id.* at 6:1-18, Fig. 8 (annotated below).) Conductive layer 44a, which is electrically isolated, is a dummy pattern that protects against contact hole misalignment. (*Id.* at 4:25-30, 5:33-44, 6:20-23.) According to the '902 patent, forming an electrically isolated

conductive layer 44a that serves no electrical function was "unlike methods of the prior art." (*Id.* at 5:33-44.)

(*Id.* at Fig. 8 (annotated).)

28. Claims 1-18 of the '902 patent recite some of the novel features discussed above that protect the field region from contact-hole misalignment, resulting in improved margins for forming contact holes. For instance, claim 1 of the '902 patent recites, *inter alia*, "forming an etch inhibiting layer on said field isolation layer adjacent said active region of said substrate, . . . wherein said etch inhibiting layer comprises a second patterned conductive layer and an insulating spacer along a sidewall of the second patterned conductive layer, . . . wherein the second patterned conductive layer is a dummy pattern electrically isolated from the substrate and circuits thereon." (Ex. 1001, claim 1.)

#### B. Overview of *Lee*

29. *Lee* discloses a prior art structure in Fig. 1(a), in which the active region is isolated by a field oxide layer 12 on a semiconductor substrate 11. (Ex.

- 1107 at 3.) A MOS gate 14 is also shown that is "formed by depositing gate oxide layer, poly and gate caps in . . . sequence and then etching them." (*Id.*) *Lee* recognizes that in prior art devices, a contact hole misalignment may cause damage to the gate sidewall of the MOS gate or may damage the field oxide layer resulting in junction leakage. (*Id.*) *Lee* illustrates these issues in figure 1(b). (*Id.*)

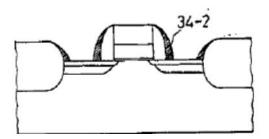

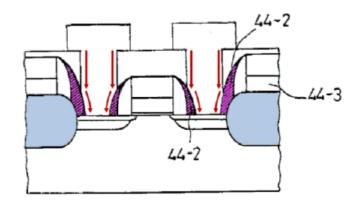

- 30. *Lee*'s first embodiment is described with reference to figure 3b, which is shown below:

(b)

(*Id.* at Fig. 3(b).)

31. Lee describes the first embodiment as follows: "At this time, the etch stop layer is formed ... in the form of a sidewall through a deposition and etch-back process using the step area formed on the lower layer without any additional mask." (*Id.* at 6.). In Fig. 3b above, it can be seen that the step area referred to by *Lee* is the field oxide layer on which the etch stop layer 34-2 is formed "on the lower layer." (*Id.*)

32. In a second embodiment, *Lee* discloses "forming an etch stop layer (44-2) using an internal connection line (44-3) passing adjacently or the step of a dummy pattern when the step at the lower layer used to form the etch stop layer in the first embodiment is not sufficient." (*Id.* at 7.) *Lee* is completely silent on the structure or the constituent layers of the "dummy pattern." For instance, *Lee* does not explain whether the "dummy pattern" takes the shape of a gate (such as MOS gate 34 in Fig. 3(a)) or any other structure. Nor does *Lee* disclose whether the "dummy pattern" includes a conductive portion. Neither does *Lee* disclose that the "dummy pattern" is electrically isolated. All *Lee* discloses is that the etch stop layer 44-2 may be formed using a "dummy pattern" as a step when the step area of the field oxide layer is insufficient.

## C. Overview of Yasushige

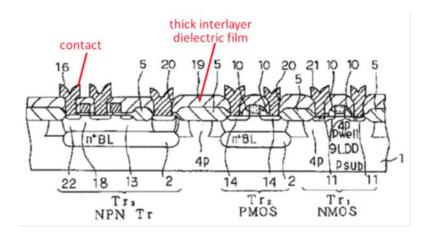

33. *Yasushige* relates to a method of forming a BiCMOS semiconductor device with a lightly doped drain (LDD) structure. (Ex. 1109 at abstract.) In certain embodiments of *Yasushige*, dummy patterns are formed around the base region of a bipolar transistor simultaneously with the gate electrode of a MOS

<sup>&</sup>lt;sup>3</sup> The discussion here is specific to *Lee*'s disclosure of "dummy pattern" and is not to be confused with the term "dummy pattern" recited in the claims of the '902 patent.

transistor. For instance, figure 1 of *Yasushige* illustrates dummy patterns (7d) formed on an insulation film (5).

[FIG. 1]

The semiconductor device of Embodiment 1

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductor device of Embodiment 1

The semiconductor device of Embodiment 1

To conductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 5 10 7 10 9

The semiconductive film collector in 10 10 7 10 9

(*Id.* at Fig. 1.)

34. One of ordinary skill in the art would have understood that the problem *Yasushige* was trying to solve was how to form lightly doped drain (LDD) sidewalls on MOS transistors without deterioration in the base regions of bipolar transistors formed in the BiCMOS device. (*Id.* at  $\P$  [0027] – [0028].) As shown in figures 4 and 5, dummy patterns 7d are formed around the base region 14b of a bipolar transistor Tr3, and the dummy patterns 7d and are "electrically isolated from the base region by an isolation region 5." (*Id.* at  $\P$  [0041].) When film 12 of the base region is removed by wet etching, the dummy patterns 7d act as an etch stopper. (*Id.* at Figs. 4, 5,  $\P$  [0045]-[0046].) At this time, the MOSFET portion of the device is covered by a resist pattern 33. (*Id.* at Fig. 4.) But during this wet etch

of the base region isolation film, the sidewall spacers that would have formed on the side of the dummy patterns 7d are removed from one side of the dummy patterns 7d. (*See id.* at Fig. 7, illustrating that the dummy patterns only have spacers 37 on one side.) By doing so, the area of isolation region 5 adjacent to the active area in the bipolar junction portion is left unprotected during any subsequent etching, such as contact hole formation.

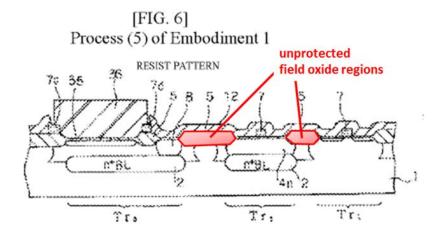

35. One of ordinary skill in the art would have also understood that *Yasushige* is not concerned about avoiding damage to the isolation region 5. This is evident from the fact that there is no dummy pattern 7d or any other mask present over the field oxide regions during the anisotropic etching of the  $SiO_2$  film 12. (*See id.* at Fig. 6 (below with annotations added).) Rather, the dummy patterns 7d are added to provide larger tolerance during the formation of resist pattern 36. (*Id.* at ¶ [0049].) It is the resist pattern 36 that carries out *Yasushige*'s purpose of protecting the active region of the transistor (35) during the anisotropic etching process. (*Id.* at ¶ [0049].)

36. Moreover, one of ordinary skill in the art would have understood that *Yasushige* is not concerned about avoiding damage to the field oxide region during the contact hole formation. For instance, the only discussion of the contact hole, as shown in figure 8 of *Yasushige*, relates to an embodiment where dummy patterns are not used. In the embodiment relating to figure 8, the contact holes are made through the thick interlayer dielectric film (19), without any protection from a dummy gate and the sidewall spacers of the dummy pattern for any field oxide region. (*See id.* at Fig. 8 (annotated).)

37. As is shown in Figure 8, the field isolation regions (5) are covered only by the dielectric film (19) and are not protected by a dummy pattern.

## VIII. RESPONSE TO PETITIONER'S MAPPING OF THE CLAIMED FEATURES TO THE CITED REFERENCES

### A. Independent Claim 1

38. I understand that independent claim 1 recites a "second patterned conductive layer [that] is a dummy pattern electrically isolated from the substrate and circuits thereon." I also understand that independent claim 1 further recites "an insulating spacer along a sidewall of the second patterned conductive layer." It is also my understanding that Petitioner and Dr. Lee contend that *Lee* and *Yasushige* disclose these features. (Pet. at 31-41; Ex. 1116 at ¶¶ 95-108; *see also* Decision at 12-15.) In my opinion, this is not correct for at least the following reasons.

## 1. Lee Does Not Disclose or Suggest a "Second Patterned Conductive Layer [that] Is a Dummy Pattern"

39. Lee discloses a "second embodiment" with respect to figure 4. Lee does not provide a detailed discussion of figure 4 and simply states that figure 4 discloses "a method of forming an etch stop layer (44-2) using an internal connection line (44-3) passing adjacently or the step of a dummy pattern when the step at the lower layer used to form the etch stop layer in the first embodiment is not sufficient." (Ex. 1107 at 7, emphasis added.) It is my understanding that

Petitioner assumes that element "44-3" in *Lee* refers to the "dummy pattern" and it is my understanding that Dr. Lee confirmed this assumption during his deposition. (Pet. at 36, "dummy pattern 44-3"; *see also* Ex. 2005 at 152:25-153:5, 153:18-19.) This is incorrect because *Lee* never annotates the "dummy pattern" by element 44-3. (*See* Ex. 1107 generally.) *Lee* only refers to an internal connection line 44-3 and not a dummy pattern 44-3.

Having assumed that Lee discloses a "dummy pattern 44-3," which it 40. does not, Petitioner and Dr. Lee try to analogize "dummy pattern 44-3" with MOS gate 34 and from that analogy, they conclude that the "dummy pattern" in Lee is a "patterned conductive layer" like the polysilicon layer in MOS gate 34. (Pet. at 36-37; see also Ex. 1116 at ¶ 102.) One of ordinary skill in the art would not have understood that the "dummy pattern" in *Lee* is a "patterned conductive layer" because there is no disclosure in Lee whether the internal connection line 44-3, let alone the "dummy pattern," has the same structure and composition as MOS gate 34. Nor is there any disclosure in *Lee* that the layers of internal connection line 44-3, let alone the "dummy pattern," would have been patterned in the same sequence as MOS gate 34. In fact, Petitioner and Dr. Lee acknowledge that "other mechanical structures are possible" for forming the "dummy pattern" in Lee. (Pet. at 37; Ex. 1116 at ¶ 104.) Therefore, it is my opinion that one of ordinary skill in the art would not have concluded from *Lee*'s silence regarding the "dummy pattern" that the "dummy pattern" has the same structure as MOS gate 34, and that by implication the "dummy pattern" is a "patterned conductive layer" because MOS gate 34 has a patterned poly layer.

41. It is my understanding that Dr. Lee contends that the "dummy pattern" in *Lee* is most likely to be a gate structure like MOS gate 34 because "forming a gate pattern is most efficient given the already existing patterning process for gates throughout the chip." (Pet. at 37, citing Ex. 1116 at ¶ 104.) Dr. Lee also contends that a mechanical structure such as a "dummy pattern" should be "electrically isolated . . . to prevent accidental electrical connections or shorting damage." (Ex. 1116 at ¶ 104.) However, one of ordinary skill in the art would have known that a simple way to prevent accidental electrical connection or shorting is to make the "dummy pattern" from a non-conductive material so that there is no chance of any shorting. This implies that the "dummy pattern" is not a gate structure. Accordingly, if, as Dr. Lee contends, the "dummy pattern" should necessarily be "electrically isolated," then the "most" efficient way to construct the "dummy pattern" would be to form the "dummy pattern" with a non-conductive material instead of using a gate structure likes MOS gate 34. After all, Lee only utilizes the

<sup>&</sup>lt;sup>4</sup> The term "dummy pattern" as used in the above discussion refers to the "dummy pattern" as recited in *Lee* and not as recited in the claims of the '902 patent.

"dummy pattern" as a step for the etch-stop layer 44-2 and it is not necessary to use a gate structure having a conductive portion to form a step.

- 2. Lee Does Not Disclose or Suggest that the "Dummy Pattern" is "Electrically Isolated from the Substrate and Circuits Thereon"

- 42. It is my understanding that Petitioner and Dr. Lee contend that the "dummy pattern" in *Lee* must be "electrically isolated from the substrate and circuits thereon." (Pet. at 37-38; Ex 1116 at ¶¶ 103-05.) It is also my understanding that Petitioner provides four reasons for this conclusion. In my opinion, each of these reasons is incorrect.

- 43. Petitioner and Dr. Lee first contend that the "dummy pattern" is electrically isolated because it does not extend over the active region and is disposed on the field oxide layer. (Pet. at 37; Ex. 1116 at ¶ 103.) Under this rationale, the internal connection line 44-3 would also be "electrically isolated" because the internal connection line 44-3 is also formed over the field oxide layer. (Ex. 1107 at Fig. 4.) But one of ordinary skill in the art would have understood that an "internal connection line" is not "electrically isolated." Dr. Lee himself confirms this. (Ex. 2005 at 154:13-17; *see also* Pet. at 37, contending that "internal connection line" has connections and dummy pattern does not.)

Accordingly, even assuming for the sake of argument that the "dummy pattern" is situated over the field oxide layer, such an assumption cannot lead to a conclusion

that the "dummy pattern" is "electrically isolated from the substrate and circuits thereon."

44. Petitioner's first reasoning is incorrect for the additional reason that the literature prior to 1996 was replete with semiconductor devices in which conductive layers formed on field oxide layers were not "electrically isolated." For instance, as shown in the annotated figures below, well known semiconductor devices had "word lines" disposed on the field oxide layer. A stacked capacitor DRAM cell invented in the 1970s had a "word line" disposed on a field oxide layer. (Ex. 2007 at 1.) Another stacked capacitor DRAM cell from the early 1990s disclosed in U.S. Patent No. 5,142,438 had two word lines 11A and 11C "traversing field oxide regions 12A and 12B respectively." (Ex. 2008 at 2:20-27, Fig. 4.) One of ordinary skill in the art would have understood that a word line is not "electrically isolated" despite being disposed on the field oxide layer.

(Ex. 2007 at 1, annotated)

(Ex. 2008 at Fig. 4,annotated)

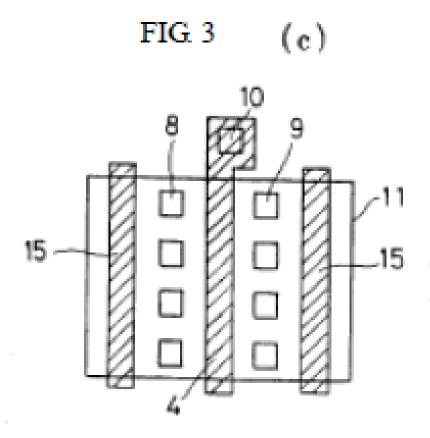

45. It is my understanding that Petitioner's second reasoning is that because "dummy pattern" is not an "internal connection line," it cannot have any connections and is therefore, "electrically isolated from the substrate and circuits thereon." (Pet. at 37; Ex. 1116 at ¶¶ 103, 104; see also Ex. 2005 at 155:17-20, "the dummy pattern is not a connection line, meaning that it is not connected to the substrate or the circuit.") In my opinion, neither Lee's disclosure nor the understanding of one of ordinary skill in the art at the time of the invention of the '902 patent supports Petitioner's analysis. Just because the "dummy pattern" is not an "internal connection line," does not mean that the "dummy pattern" must be "electrically isolated." Dummy patterns can be located anywhere on active regions or on isolation regions. For instance, one of the prior art references cited during prosecution of the '902 Patent, Japanese Patent Application Publication H4-63437 ("Michihiro") (Ex. 1104) discloses "dummy patterns" 15 formed on the active region that are not "internal connection lines" but are still electrically coupled to the substrate (i.e., not electrically isolated). (Ex. 1104 at 4, Fig. 3(c).) These dummy patterns have "the exact same configuration as the gate electrode 4." (*Id.* at 4.) Because "dummy patterns 15" have the same configuration as the gate electrode 4 and they are formed on the active region, one of ordinary skill in the art would have understood that the "dummy patterns 15" are electrically coupled to the underlying substrate. One of ordinary skill in the art would know that such an

equilibrium electrostatic potential in the silicon due to the difference in potential between the conductive dummy gate material and the silicon. (*See, e.g.*, C.G. Fonstad, *Microelectronic Devices and Circuits*, McGraw Hill, 1994, pp. 241-242 (Ex. 2009).) That is, "dummy patterns 15" are not electrically isolated from the substrate.

46. Moreover, one of ordinary skill in the art would have understood that the "dummy patterns 15" are not "internal connection lines" at least because they do not connect to any other circuit in Fig. 3(c). Therefore, it is incorrect for Petitioner and Dr. Lee to conclude that because the "dummy pattern" is not an "internal connection line," it has to be electrically isolated from the substrate and circuits thereon.

(Ex. 1004 at Fig. 3(c).)

47. It is my understanding that Petitioner and Dr. Lee's third reasoning is that the "dummy pattern" in *Lee* would be "electrically isolated" because a "POSITA would know that keeping the mechanical structure electrically isolated is the best and most efficient practice to prevent accidental electrical connections or shorting damage." (Pet. at 38, citing Ex. 1116 at ¶ 104.) Petitioner's theory, however, assumes that the "dummy pattern" has no electrical function to begin with. In my opinion, nothing in *Lee* prevents the "dummy pattern" from having an

electrical function. The following is the entirety of what *Lee* discloses regarding a dummy pattern in its second embodiment:

"FIG. 4 illustrates the second embodiment of the present invention. This is a method of forming an etch stop layer (44-2) using an internal connection line (44-3) passing adjacently or the step of a dummy pattern when the step at the lower layer used to form the etch stop layer in the first embodiment is not sufficient."

Lee 17-6.

(Ex. 1107 at 7.)

"5. The method for fabricating a semiconductor device in Claim 1, wherein the sidewall use either the step of the connection line at the adjacent lower layer or uses the step by forming an adjacent dummy pattern."

(*Id.* at 10.)

48. Petitioner and Dr. Lee's fourth reasoning is that a "dummy pattern" must be "electrically isolated" based on the definition of the term "dummy" as understood by one of ordinary skill in the art. (Pet. at 38-39, citing Ex. 1116 at ¶ 105.) According to Dr. Lee, "a dummy pattern is a gate pattern that performs no electrical function, as confirmed by contemporary electrical engineering and microelectronics dictionaries." (Ex. 1116 at ¶ 105; see also Ex. 2005 at

155:24-156:7, contending that the term "dummy pattern" would be "universally understood by one of ordinary skill in the art as not performing an electrical function.") I disagree with Dr. Lee that a "dummy pattern" must always be "electrically isolated from the substrate and circuits thereon." For instance, Michihiro discloses that "dummy patterns" 15 can be electrically coupled to the substrate. (Ex. 1104 at 4, Fig. 3(c).)

- 3. Lee Does Not Disclose an "Insulating Spacer Along a Sidewall of the Second Patterned Conductive Layer... [That] Is a Dummy Pattern"

- 49. It is my understanding that claim 1 recites "an insulating spacer along a sidewall of the second patterned conductive layer," which is "a dummy pattern electrically isolated from the substrate and circuits thereon." Therefore, I understand that claim 1 recites an insulating spacer along a sidewall of a dummy pattern. I also understand that Petitioner and Dr. Lee contend that the "etch stop layer 44-3" is the claimed "insulating spacer" because it is allegedly formed on a sidewall of "dummy pattern 44-3." (Pet. at 32-33; Ex. 1116 at ¶¶ 95-98.) I disagree with Petitioner and Dr. Lee for at least the following reasons.

- 50. First, as discussed above in Section VIII.A.2, *Lee* does not disclose that element 44-3 corresponds to the "dummy pattern" recited in *Lee*. Therefore, it is improper for Dr. Lee and Petitioner to assume from the disclosure of figure 4

(which shows "internal connection line 44-3" and "etch stop layer 44-2") that the etch stop layer 44-2 is also formed on the "dummy pattern" in *Lee*.

51. Second, one of ordinary skill in the art would not have understood that the etch stop layer 44-2 is an "insulating spacer" if as Dr. Lee contends the "dummy pattern" in *Lee* is a conductive portion and that 44-3 is a gate structure. (See Pet. at 36-37, alleging that 44-3 is formed to have a gate structure and includes a conductive portion like in a MOS gate; see also Ex. 1116 at ¶ 102.) Lee discloses that the etch stop layer 44-2 may be both "conductive or non-conductive." (Ex. 1107 at 7.) But it was well understood by one of ordinary skill in the art that a "spacer" for a gate structure *must* be an insulator. Dr. Lee's testimony in a related proceeding (IPR2016-00134) confirms this understanding. (IPR2016-00134, Ex. 1103 at ¶ 92- "Given that the spacers are in contact with both the gate electrode and the source and drain regions, if they were not electrically insulating, the gate electrode would be short circuited with the source and drain regions, thereby causing the transistor to malfunction.") Therefore, given Lee's disclosure that the etch stop layer 44-2 may be both "conductive and non-conductive," one of ordinary skill in the art would not have understood the etch stop layer to be an "insulating spacer."

- 4. One of Ordinary Skill in the Art Would Not Have Combined *Lee* with *Yasushige* as Proposed by Petitioner

- 52. It is my understanding that relying on *Yasushige's* disclosure of dummy pattern 7d formed on field oxide layer 5, Petitioner and Dr. Lee contend that one of ordinary skill in the art would have been motivated to combine the teachings of *Lee* and *Yasushige* such that the "dummy pattern" in *Lee* becomes "electrically isolated." (Pet. at 39; Ex. 1116 at ¶ 106; *see also* Decision at 14-15.) That is, I understand Petitioner proposes to make *Lee*'s dummy pattern "electrically isolated from the circuits and substrate thereon" based on *Yasushige*'s disclosure that dummy pattern 7d is electrically isolated. Petitioner and Dr. Lee are incorrect.

- pattern 7d is "electrically isolated *from the substrate and circuits thereon*," as required by claim 1. *Yasushige* simply states that it includes a "conductive film identical to the gate electrode of [a] MOS transistor [that] is formed around the base region of [a] bipolar transistor, and said conductive film is electrically isolated from the base region." (Ex. 1109 at ¶ [0029]; *see also id.* at ¶ [0041].) *Yasushige* does not disclose, nor does Petitioner allege that *Yasushige* discloses, that the "conductive film" is electrically isolated from anything other than the "base region." (*See id.* at ¶¶ [0029], [0041].) So even if *Yasushige* discloses electrically isolating

dummy pattern 7d from the "substrate," which I disagree with, *Yasushige* has no disclosure whether dummy pattern 7d is also electrically isolated from the circuits on the substrate.

54. In my opinion, one of ordinary skill in the art would not have been motivated to combine the teachings of *Lee* and *Yasushige* in the manner proposed by Petitioner. For instance, *Yasushige* does not offer any reasons, nor does Petitioner allege otherwise, for why it would have been desirable to *electrically isolate* the dummy pattern 7d. (*See* Pet. at 19-21, 39-40.) Petitioner and Dr. Lee nevertheless contend that "electrically isolating the dummy pattern on a field oxide layer would improve the functionality of *Lee*'s disclosure of the dummy pattern and etch stop layer along its sidewall." (Pet. at 40.) Specifically, they contend:

"Positioning the dummy pattern around the active region would protect the edge of the field oxide layer from being etched by a contact hole formation process. By not positioning the dummy pattern on the active region itself, there is no encroachment onto active region, which would take up valuable space otherwise devoted to active transistors and contact holes."

55. But the above reasons relate to the placement of the "dummy pattern" and do not explain why a "dummy pattern" would be "electrically isolated." They do not explain any advantage that would result by electrically isolating *Lee*'s "dummy pattern." And even if the above reasons provide motivation to place a

"dummy pattern" on the field oxide region, such placement does not ensure that the "dummy pattern" is "electrically isolated." (*See supra* section VIII.A.1, explaining that placement of a layer over the field oxide region does not result in the layer being "electrically isolated.")

56. Petitioner and Dr. Lee additionally contend that "keeping the dummy pattern electrically isolated ensures that the dummy pattern will not accidentally cause a short to other circuits of the device, should a contact hole be misaligned far enough to etch into the conductive material of the dummy pattern." (Pet. at 40; Ex. 1116 at ¶ 108.) This is not correct because the reasoning assumes that adding a layer of insulation around a dummy pattern prevents etching of the layer(s) of the dummy pattern whatever those layer(s) may be. An insulator is not necessary for preventing etching of an underlying layer. This is evident from Lee where the etch stop layer is "conductive or non-conductive" and serves as an etch stopper. (Ex. 1107 at 6-8.) Additionally, Lee is unconcerned that his etch-stop layer might not protect any constituent structures beneath it, since his second embodiment forms an etch stop layer (44-2) over an internal connection line (44-3) in Fig. 4. Connection line (44-3) is not electrically isolated.

### B. Claims 3-5, 7-12, 14-16, and 18

57. Each of the remaining independent claims 11, 12, 15, and 18 recite a "patterned conductive layer" that "is a dummy pattern electrically isolated from the

substrate and circuits thereon." Moreover, Petitioner's analysis with respect to this limitation of claims 11, 12, 15, and 18 mirrors Petitioner's analysis for claim 1 for these features (Pet. at 51-54), which as discussed above are not disclosed or suggested by *Lee* and *Yasushige*. Furthermore, as discussed above, in my opinion, one of ordinary skill in the art would not have combined the teachings of *Lee* and *Yasushige* in the manner proposed by Petitioner. I understand that claims 3-5, 7-10, 14, and 16 depend from one of independent claims 1, 12, and 15, and thus require the limitations discussed above for claims 1, 12, and 15. Accordingly, the above discussed shortcomings of the cited references also applies to claims 3-5, 7-10, 14, and 16.

#### 1. Claim 7

58. For claim 7, Petitioner's analysis is incorrect for an additional reason. I understand that claim 7 recites that "the insulating spacer of the etch inhibiting layer extends to the active region of the substrate." Petitioner and Dr. Lee contend that Lee discloses this feature because the "etch stop layer 44-2 is formed partially on the field oxide layer . . . ." (Pet. at 46; Ex. 1116 at ¶ 122.) But as discussed above in Section VIII.A.3, one of ordinary skill in the art would have understood that the "etch stop layer 44-2" is not an "insulating spacer." For at least this reason, in my opinion, Lee does not disclose the recited feature of claim 7.

#### 2. Claim 10

59. For claim 10, Petitioner's analysis is incorrect for an additional reason. I understand that claim 10 recites that "at least a portion of the contact hole is self-aligned with respect to the first patterned conductive layer and the etch inhibiting layer." Petitioner contends that *Lee* discloses that the "etch stop layer (44-2) is formed along the sidewalls of both a first patterned conductive layer and a dummy pattern," and relies on figure 4 of *Lee* for support. (Pet. at 49; Ex. 1116 at ¶¶ 128-29.) An annotated version of figure 4 which Petitioner relies upon is reproduced below<sup>5</sup>:

(Pet. at 49.)

60. In the above annotated figure, Petitioner assumes that 44-3 refers to a "dummy pattern," which as discussed above in Section VIII.A.1 is not correct. In

<sup>&</sup>lt;sup>5</sup> The corresponding figure is not found in the declaration of Dr. Lee. (See Ex. 1116 at ¶ 128.)

fact, Petitioner's entire analysis for claim 10 is based on this assumption (Pet. at 49-50), which is not true as discussed in Section VIII.A.1.

# C. Claims 2 and 17

61. I understand that for claims 2 and 17, Petitioner and Dr. Lee rely on *Nowak* in addition to *Lee* and *Yasushige*. (Pet. at 55; Ex. 1116 at ¶¶ 150-53; *see also* Decision at 16-17.) I have reviewed *Nowak* and in my opinion *Nowak* does not remedy the deficiencies of *Lee* and *Yasushige* I identified in Section VIII.A.

## D. Claims 6 and 13

- 62. I understand that for claims 6 and 13, Petitioner and Dr. Lee rely on Lee II in addition to Lee and Yasushige. (Pet. at 58-60; Ex. 1116 at ¶¶ 58-60; see also Decision at 17-18.) They allege that Lee would have been modified based on the teachings of Lee II. I disagree.

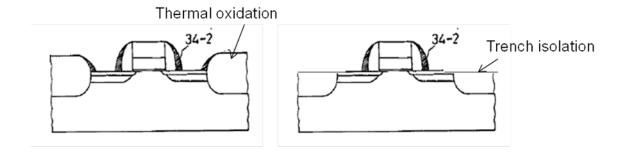

- 63. In my opinion, one of ordinary skill in the art would have realized that modifying *Lee* to incorporate *Lee II'* s techniques as proposed by Petitioner would render *Lee* inoperable for its intended purpose. The figures of *Lee* make clear that the field oxide layer is formed by a process known as local oxidation of silicon (LOCOS) by thermal oxidation. In LOCOS thermally grown field oxide is grown by consuming silicon such that the upper surface of the field isolation region is above the substrate surface. This effect is caused by silicon dioxide having about twice the volume as silicon. (S. Wolf and R.N. Tauber, *Silicon Processing*, Vol. 2,

Lattice Press, 1990, pp. 17-28 (Ex. 2010).) Based on the shape of *Lee*'s field oxide layer 32, one of ordinary skill in the art would have understood that *Lee* used thermal oxidation to form field oxide layer 32, i.e., *Lee* used LOCOS. LOCOS, however, is different from forming a trench and filling the trench with oxide, which is what claims 6 and 13 require. Thus, claims 6 and 13 of the '902 patent do not cover the LOCOS field isolation layers formed by thermal oxidation.

64. Lee's embodiments require the field oxide layer 32 to be formed using the LOCOS method because they require the field oxide layer 32 to protrude above the substrate surface. For instance, Lee discloses (in Fig. 3(b)) forming the etchstop layer on the field oxide layer by using the protruded field oxide layer as a step. (Ex. 1107 at 7.) In trench isolation, the trench is only filled with oxide and then made flush with the substrate surface, as shown below. Thus, Lee could not have implemented the embodiment of figure 3(b) without using LOCOS field isolation. A side-by-side comparison of Fig. 3(b) implemented with LOCOS (left) and trench isolation (right) shows why a trench isolation technique would not be desired for Lee's purpose.

- 65. Similarly, *Lee* bases his third embodiment (*see* Ex. 1107 at Fig. 5) on utilizing the field oxide layer as a mask for forming etch stop layer (54-2), which again suggests that *Lee* uses the LOCOS field isolation layer for forming an etch stop layer (54-2). (Ex. 1107 at 7, "formed by etching the semiconductor substrate using the oxide layers on the substrate (field oxide layer, gate sidewall, cap oxide layer) as mask.")

- 66. In view of the above, one of ordinary skill in the art would not have modified *Lee* to incorporate *Lee II*'s techniques because they would render *Lee* inoperable for its intended purpose.

## IX. CONCLUSION

67. I declare that all statements made herein on my own knowledge are true and that all statements made on information and belief are believed to be true, and further, that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 or Title 18 of the United States Code, and that such willful false statements may jeopardize the validity of the '902 patent.

Executed this 10<sup>th</sup> day of March 2016 in Durham, North Carolina.

Richard B. Fair, Ph.D.

# **Appendix**

#### RESUME

# Richard B. Fair 3414 CAMBRIDGE RD. DURHAM, NORTH CAROLINA 27707

## **EDUCATION AND HONORS**

BSEE - Duke University, Durham, N.C., 1964, Presbyterian Church Scholarship, 1961.

MSEE - Penn State University, University Park, Pa., 1966, Sylvania Fellow, 9-64/6-66.

Ph.D. - Duke University, Durham, N.C., 1969, NDEA Fellow, 9-66/6-69.

## **Awards**

- (1) Outstanding Paper Award IEEE Spring Symp., Duke University, 1969.

- (2) "Outstanding Young Men of America" Award, 1973.

- (3) "Outstanding Young Electrical Engineer of the Year" Award, 1974 -National Award from Eta Kappa Nu.

- (4) American Men and Women in Science, 1979 Present

- (5) Who's Who in Technology Today, 1980, 81.

- (6) Adjunct Professor, Dept. of Electrical Eng., Duke University, 1980-81.

- (7) Who's Who in Frontiers of Science and Technology, 1985, 1986

- (8) Who's Who in the Semiconductor Industry, 1986.

- (9) Fellow Award, IEEE, 1990

- (10) Who's Who in Engineering, 1991, 1993

- [11] Who's Who in America, 1991, 1993

- (12) Fellow Award, Electrochemical Society, 1994

- (13) Professor James F. Gibbons Achievement Award, 4th International

Conference on Advanced Thermal Processing, 1996

- (14) Third Millennium Medal, IEEE, 2000

- (15) Solid State Science and Technology Award The Electrochemical Society, 2003

#### MEMBERSHIPS / PROFESSIONAL ACTIVITIES

- (1) Member, Sigma Xi

- (2) Fellow, Electrochemical Society

- a. Session Chairman numerous times, 1975-present

- b. Symposium Chairman "Diffusion Processes in Semiconducting Materials," St. Louis, 1980

- c. Member of Electronics Division Executive Committee, 1987 -

- d. Organizing Committee 6th International Symposium on ULSI Science and Technology

- e. Organizing Committee 1<sup>st</sup> Inter. Conf. On ULSI Process Integration 1999.

- f. Organizing Committee Joint Electronics/Dielectric General Session 1997-

- g. Co-chair, Sixth International Symposium on ULSI Science and Technology, Montreal (1997)

- (3) Life Fellow- IEEE

- a. Session Chairman at 1977-78 International Electron Device Meetings (IEDM)

- b. Chairman, Solid State Device Committee for 1978 IEDM

- c. Member, Integrated Circuit Technology Subcommittee for 1982 IEDM

- d. Member of Editorial Board Proceedings of the IEEE 1988-

- e. Editor, Proceedings of IEEE 1993-2001

- f. Associate Editor Trans. Electron Devices 1990-1993

- g. Guest Editor, Special Issue on NSF Engineering Research Centers, Proceedings of IEEE, Jan. 1993.

- h. Member, IEEE Publications Board 1993-

- (4) Electronic Materials Committee of AIME 1985 1989

- (5) Materials Research Society

- a. Symposium Co-Chairman "Impurity Diffusion and Gettering in Silicon" 1984

- b. Member of Editorial Board Bulletin of Materials Research Society 1985-1987

- (6) Co-chair, 1st International Rapid Thermal Processing Conference, Phoenix (1993).

- (7) Co-chair, 2nd International Rapid Thermal Processing Conference, Monterey (1994).

- [8] Co-chair, 3rd International Rapid Thermal Processing Conference, Amsterdam (1995).

- (9) Co-chair, 4th International Rapid Thermal Processing Conference, Boise (1996).

- (10) Co-chair, 5th International Rapid Thermal Processing Conference, New Orleans (1997).

- (11) Co-Chair, Fourth International Workshop on Meas., Characterization, and Modeling of Ultra- shallow Doping Profiles in Semiconductors, Research Triangle Park, (1999).

- (12) Member of Editorial Advisory Board, Journal Microfluidics and Nanofluidics, (2008-

### **International Activities**

- (1) Instructor, CEI Europe 1985 present

- (2) Member, International Advisory Panel, Microelectronics Systems '91 Conference, Kuala Lumpur, Malaysia

- (3) Member, International Advisory Committee, Annual Semiconductor Conference '92-99, Bucharest, Romania

- (4) Member, International Advisory Committee, 1993 Symposium on Semiconductor Modeling and Simulation, Taipei, Taiwan

- (5) Member, Program Committee, Inter. Symposium on Advanced Microelectronic Devices and Processing 1993, Sendai, Japan

## **Employment Experience**

Present- - Lord-Chandran Professor of Engineering, Pratt School of Engineering

1993-1994 - Director, Microfabrication Technology and the associated Research Institute of MCNC; Professor, Electrical Engineering, Duke University

1990-1993 - Vice President, MCNC and Executive Director, Center for Microelectronic Systems Technologies; Professor, Electrical Engineering, Duke University

1986-1990 - Vice President, Design Research and Technology, MCNC; Professor, Electrical Engineering, Duke University

10/88-3/89 - Acting President, MCNC; Professor, Electrical Engineering, Duke University

1981-1985 - Vice President, Research Program Management, MCNC; Professor, Electrical Engineering, Duke University

1973-1981 - Supervisor, Bell Laboratories, Reading, PA.

1969-1973 - Member of Technical Staff, Bell Laboratories, Reading, PA.

## **Board Memberships**

1992-1994 - Advanced Technology Applications, Inc.

1993- Microelectronic Technology Corp.

1995- present -Engineering Advisory for the Aurora Fund.

1996- present - Technical Advisory Board, Thunderbird Technologies, Inc.

2003- present - Technical Advisory Board, R.J. Mears, Inc.

2004-present - Chairman, Scientific Advisory Board, Advanced Liquid Logic

## **Courses Taught**

EE218 (Integrated Circuit Engineering) Spring Semester 1982-present EE163 (Introduction to Integrated Circuits) Fall/Spring Semester, 1995-99 EE62 (Introduction to Semiconductor Devices), Spring Semester, 1999-present ECE299 (Biochip Engineering), Fall Semester, 2005-2007

#### **U.S Patents**

(1) U.S. Patent 4,033,027 - Dividing Metal Plated Semiconductor Wafers - July 5, 1977

- (2) U.S. Patent 6,911,132 Apparatus for Manipulating Droplets by Electrowetting-based Techniques – June 28, 2005

- (3) U.S. Patent 6,989,234 Method and Apparatus for Non-Contact Electrostatic Actuation of Droplets – January 24, 2006

- (4) U.S. Patent 7,329,545 Methods for Sampling a Liquid Flow February 12, 2008

- (5) U.S. Patent 7,439,014 Droplet-based Surface Modification and Washing October 21, 2008

- (6) U.S. Patent 7,569,129 Methods for manipulating droplets by electrowetting-based techniques – August 4, 2009

- (7) U.S. Patent 7,727,723 Droplet-based pyrosequencing June 1, 2010.

- (8) U.S. Patent 7,759,132 Methods for performing microfluidic sampling July 20, 2010.

- (9) U.S. Patent 8,048,628 Methods for nucleic acid amplification on a printed circuit board Nov. 1, 2011

- (10) U.S. Patent 8,147,668 Apparatus for manipulating droplets April 3, 2012.

- (11) U.S. Patent 8,221,605 Apparatus for manipulating droplets July 17, 2012.

- (12) U.S. Patent 8,287,711 Apparatus for manipulating droplets October 16, 2012.

- (13) U.S. Patent 8,313,895 Droplet-based surface modification and washing Nov. 20, 2012

- (14) U.S. Patent 8,349,276 Apparatus and methods for manipulating droplets on a printed circuit board – Jan. 8, 2013.

- (15) U.S. Patent 8,388,909 Apparatus and methods for manipulating droplets Mar.5, 2013.

- (16) U.S. Patent 8,389,297 Droplet-based affinity assay device and system Mar.5, 2013.

- (17) U.S. Patent 8,394,249 Methods for manipulating droplets by electrowetting-based techniques – Mar. 12, 2013.

- (18) U.S. Patent 8,613,889 Droplet-based washing December 24, 2013.

- (19) U.S. Patent 8,541,176 Droplet-based surface modification and washing September 24,

- (20) U.S. Patent 8,524,506 Methods for sampling a liquid flow September 3, 2013.

- (21) U.S. Patent 8,492,168 Droplet-based affinity assays July 23, 2013.

- (22) U.S. Patent 8,470,606 Manipulation of beads in droplets and methods for splitting droplets - June 25, 2013.

- (23) U.S. Patent 8,685, 754 Droplet actuator devices and methods for immunoassays and washing – April 1, 2014.

- (24) U.S. Patent 8,846,414 Detection of cardiac markers on a droplet actuator Sept. 30, 2014.

- (25) US Patent 8,871,071, "Droplet manipulation device", Oct. 28, 2014.

- (26) US Patent 8,906,627, "Apparatuses and methods for manipulating droplets", Dec. 9, 2014. (27) US Patent 8,951,721, "Droplet-based surface modification and washing," Feb. 10, 2015

- (28) US Patent 8,980,198, "Filler fluids for droplet operations," Mar. 17, 2015

- (29) US Patent 9,046,514, "Droplet actuator devices and methods employing magnetic beads," -

- (30) US Patent 9,110,017, "Apparatuses and methods for manipulating droplets", Aug. 18, 2015.

### **U.S. Applications:**

- 1 20130252262 DROPLET-BASED AFFINITY ASSAYS

- 2 20130164742 Droplet-Based Pyrosequencing

- 3 20130146455 Droplet Manipulation Device

- 4 20120165238 Droplet-Based Surface Modification and Washing

- 5 20110076734 Electrowetting Microarray Printing System and Methods for Bioactive Tissue **Construct Manufacturing**

- 6 20100291578 Droplet-Based Pyrosequencing

- 7 20100140093 Droplet-Based Surface Modification and Washing

- 8 20100116640 Droplet-Based Surface Modification and Washing

- 9 20100025242 APPARATUSES AND METHODS FOR MANIPULATING DROPLETS

- 10 20090280475 Droplet-based pyrosequencing

- 11 20090260988 Methods for Manipulating Droplets by Electrowetting-Based Techniques

- 12 20080264797 Apparatus for Manipulating Droplets

- 13 20080247920 Apparatus for Manipulating Droplets

- 14 20080105549 Methods for performing microfluidic sampling

- 15 20070243634 Droplet-based surface modification and washing

- 16 20070241068 Droplet-based washing

- 17 20070217956 METHODS FOR NUCLEIC ACID AMPLIFICATION ON A PRINTED CIRCUIT BOARD

- 18 20070045117 Apparatuses for mixing droplets

- 19 20070037294 Methods for performing microfluidic sampling

- 20 20060194331 Apparatuses and methods for manipulating droplets on a printed circuit board

- 21 20060054503 Methods for manipulating droplets by electrowetting-based techniques

- 22 20040058450 Methods and apparatus for manipulating droplets by electrowetting-based techniques

- 23 20040055891 Methods and apparatus for manipulating droplets by electrowetting-based techniques

- 24 20040055536 Method and apparatus for non-contact electrostatic actuation of droplets

### **WO and EP Patents**

- 1. EP1859330B1

- 17. EP1554568A2

- 2. EP2016189B1

- 18. WO/2004/030820A2

- 3. EP1479365B1

- 19. WO/2004/029608A1

- 4. EP2016091B1

- 20. WO/2004/029585A1

- 5. WO/2009/111723A1 21.

- 6. WO/2009/111723A9

- 7. EP2016189A2

- 8. EP2016091A2

- 9. EP1859330A2

- 10. WO/2007/120241A3

- 11. WO/2007/120241A2

- 12. WO/2007/120240A2

- 13. WO/2007/120240A3

- 14. WO/2006/081558A2

- 15. WO/2006/081558A3

- 16. EP1554568A4

# PUBLICATIONS REFEREED ARCHIVAL JOURNALS

- (1) R. B. Fair, "A Wide Slit Scanning Method for Measuring Electron and Ion Beam Profiles," J. Phys. E., 4, 35 (1971).

- (2) R. B. Fair, "A Self-Consistent Method of Estimating Non-Step Junction Doping Profiles from Capacitance Voltage Measurements," J. Electrochem. Soc.,118, 971 (1971).

- (3) R. B. Fair, "Analysis and Design of Ion Beam Deposition Apparatus," J. Appl. Phys., 42, 3176 (1971).

- (4) R. B. Fair, "Harmonic Distortion in the Junction Field-Effect Transistor with Field-Dependent Mobility," IEEE Trans. Electron Dev., ED-19, 9 (1972).

- (5) R. B. Fair, "Profile Estimation of High Concentration Arsenic Diffusion," J. Appl. Phys., 43, 1278 (1972).

- (6) R. B. Fair, "High Concentration Arsenic Diffusion in Silicon form A Doped Oxide Source," J. Electrochem. Soc., 119, 1389 (1972).

- (7) R. B. Fair and G. R. Weber, "The Effect of Complex Formation on the Diffusion of Arsenic in Silicon," J. Appl. Phys., 44, 273 (1973).

- (8) R. B. Fair, "Quantitative Theory of Retarded Base Diffusion in Silicon NPN Structures with Arsenic Emitters," J. Appl. Phys., 44, 283 (1973).

- (9) Total Arsenic Concentration in Heavily Doped n and p Type Silicon," J. Appl. Phys., 44, 280 (1973).

- (10) R. B. Fair, "Explanation of Anomalous Base Regions in Transistors," Appl. Phys. Lett., 22, 186 (1973).

- (11) R. B. Fair, "Optimum Low-Level Injection Efficiency of Silicon Transistors with Shallow Arsenic Emitters," IEEE Trans. Electron Devices, Vol. ED-20, 642 (1973).

- (12) R. B. Fair, "Correction of Calculated Vacancy Diffusion Length at 1000 C in Silicon," J. Appl. Phys., 44, 3794 (1973).

- (13) R. B. Fair, "Cooperative Effects Between Arsenic and Boron in Silicon During Simultaneous Diffusions from Ion-Implanted and Chemical Source Predepositions," Solid State Electronics, 17, 17 (1974).

- (14) R. B. Fair, "Graphical Design and Iterative Analysis of the DC Parameters of GaAs FETS," IEEE Trans. Electron Devices, Vol. ED-21, 357 (1974).

- (15) R. B. Fair, "Boron Diffusion in Silicon-Concentration and Orientation Dependence, Background Effects and Profile Estimation," J. Electrochem. Soc., 122, 800 (1975).

- (16) R. B. Fair and P.N. Pappas, "Diffusion of Ion Implanted Boron in High Concentration P and As-Doped Silicon," J. Electrochemical Soc., 122, 1241 (1975).

- (17) R.B. Fair and P.N. Pappas, "The Gettering of Boron by an Ion-Implanted Antimony Layer in Silicon," Solid State Electrons, 18, 1131 (1975).

- (18) R. B. Fair, "Performance Estimation and Optimized Design Considerations for Microwave Power GaAs FETS," IEEE Trans. Electron Dev., ED-22, (1975).

- (19) R. B. Fair and J. C. C. Tsai, "The Diffusion of Ion-Implanted As in Si," J. Electrochem. Soc., 122, 1689 (1975).

- (20) R. B. Fair and J. C. C. Tsai, "Profile Parameters of Implanted-Diffused Arsenic Layers in Silicon," J. Electrochem. Soc., 123, 583 (1976).

- (21) R. B. Fair, "Transistor Design Considerations for Low-Noise Preamplifiers," IEEE Trans. Nuclear Sci., Vol. NS-23, 218 (Feb. 1976).

- (22) R. B. Fair, H. W. Wivell, "Zener and Avalanche Breakdown in As-Implanted Low-Voltage Si n-p Junctions," IEEE Trans. Electron Dev., Vol. ED-23, p. 512 (May 1976).

- (23) R. B. Fair and J. C. C. Tsai, "A Quantitative Model of the Diffusion of Phosphorus in Silicon and the Emitter Dip Effect," J. Electrochem Soc., Vol. 124, 1107 (1977).

- (24) R. B. Fair, "Analysis of Phosphorus-Diffused Layers in Silicon," J. Electrochem. Soc., 125, 323-327 (Feb. 1978).

- (25) R. B. Fair, "Quantified Conditions for Emitter-Misfit Dislocation Formation in Silicon," J. Electrochem. Soc., 125, 928-926 (June, 1978).

- (26) R. B. Fair and J. C. C. Tsai, "Discussion of A Quantitative Model for the Diffusion of Phosphorus in Silicon and the Emitter Dip Effect," J. Electrochem. Soc, 125, 997-998 (June 1978).

- (27) R. B. Fair and J. C. C. Tsai, "Theory and Direct Measurement of Boron Segregation in SiO2 During Dry, Near Dry, and Wet O2 Oxidation, J. Electrochem. Soc., 125, 2050 (1978).

- (28) R. B. Fair, "Effect of Strain-Induced Band Gap Narrowing on E-centre Concentrations in Si," Inst. Phys. Conf. Ser., No. 46, Chapter 9, 559 (1979).

- (29) R. B. Fair, "The Effect of Strain-Induced Band-Gap Narrowing on High Concentration Phosphorus Diffusion in Silicon," J. Appl. Phys., 50, 860 (1979).

- (30) R. B. Fair, "Modeling Laser-Induced Diffusion of Implanted Arsenic in Silicon," J. Appl. Phys., 50, 6552 (1979).

- (31) R. B. Fair, "On the Role of Self-Interstitials in Impurity Diffusion in Silicon," J. Appl. Phys., 51, 5828 (1980).

- (32) R. B. Fair, "Oxidation, Impurity Diffusion and Defect Growth in Silicon An Overview," J. Electrochem. Soc., 128, 1360 (1981).

- (33) R. B. Fair and R. C. Sun, "Threshold Voltage Instability in MOSFET's, Due to Channel Hot Hole Emission," IEEE Trans. Electron. Devices, ED-28, 83 (1981).

- (34) R. B. Fair, "Molecular Transport and Diffusion in Solids," Sensors and Activators, 1, 305 (1981).

- (35) R. B. Fair and A. Carim, "On the Doping Dependence of Oxidation-Induced Stacking Fault Shrinkage in Silicon," J. Electrochem Soc., 129, 2319 (1982).

- (36) R. B. Fair, "The Silicon Process Balancing Act for VLSI," Solid State Tech., 25, 220 (1982).

- (37) W. G. Meyer and R. B. Fair, "Dynamic Behavior of the Build-up of Fixed Charge and Interface States During Hot Carrier Injection in Encapsulated MOSFET's," IEEE Trans. Electron Dev., Vol. ED-30, 96 (1983).

- (38) R. B. Fair, "MCNC-Organizing Research on the State Level," IEEE Spectrum, Vol. 20, p. 58 (1983).

- (39) R. B. Fair, J. J. Wortman, J. Liu, M. Tischler and N.A. Masnari, "Modeling Physical Limitations on Junction Scaling for CMOS," IEEE Trans. Electron Dev., Vol ED-31, 1180 (1984).

- (40) R. B. Fair, J. J. Wortman and J. Liu, "Modeling Rapid Thermal Diffusion of Arsenic and Boron in Silicon," J. Electrochem. Soc., 131, 2387 (1984).

- (41) R. B. Fair, "The Role of Vacancies and Self-Interstitials in Impurity Diffusion in Silicon," Materials Science Forum, Vol. 1. (Trans. Tech. Pub. Switzerland) pp. 109-132 (1984).

- (42) W. B. Wilson, H. Z Massoud, E. T. Swanson, R. T. George and R. B. Fair "Measurement and Modeling of Charge Feedthrough in n-Channel MOS Analog Switches," IEEE J. Solid State Cir. Vol. SC-20, pp. 1206-1213 (1985).

- (43) J. Liu, J. J. Wortman and R. B. Fair, Shallow p +-n Junction for CMOS VLSI Application Using Germanium Preamorphization, IEEE Trans. Electron. Dev., Vol ED-32, 2533 (1985).

- (44) R.B. Fair, "Modeling of Dopant Diffusion During Rapid Thermal Annealing," J. Vac. Sci. Technology A4, 926 (1986).

- (45) R. B. Fair, M. L. Manda and J. J. Wortman, "The Diffusion of Antimony in Heavily Doped n- and p-type Silicon," J. Mates. Res., 1,705 -717 (1986).

- (46) J. C. C. Tsai, D. G. Schimmel, R. B. Fair and W. Maszara, "Point Defect Generation During Phosphorus Diffusion in Silicon-1. Concentrations Above Solid Solubility," J. Electrochem. Soc., .134, 1508 (1987).

- (47) R. Subrahmanyan, H. Z. Massoud and R. B. Fair, "The Influence of HCl on the Oxidation Enhanced Diffusion of Boron and Arsenic in Silicon," J. Appl. Phys., 61, 4804 (1987).

- (48) J. C. Tsai, D. G. Schimmel, R. E. Ahrens and R. B. Fair, "Point Defect Generation During Phosphorus Diffusion in Silicon II. Concentrations below Solid Solubility, Ion-Implanted Phosphorus," J. Electrochem. Soc., 134, 2348 (1987).

- (49) R. B. Fair, "Reply to Comments of F. F. Morehead," J. Mater. Res., 2, 539 (1987).

- (50) R. B. Fair, ."Low-Thermal Budget Process Modeling with the PREDICT Computer Program," IEEE Trans. Electron. Dev., .35, 285 (1988).

- (51) A. C. Ajmera, G. A. Rozgonyi and R. B. Fair "Point Defect/Dopant Diffusion Considerations Following Preamorphization of Silicon via Si+ and Ge+ Implantation," Appl. Phys. Lett., 52 (10), 813 (1988).

- (52) R.B. Fair and J.E. Rose, "Process Simulation of Submicron Technologies" Semicond. Int.,13, 72, (1987).

- (53) M. C. Ozturk, J. J. Wortman and R. B. Fair,."Very Shallow P+n Junction Formation by Low Energy BF2+ Ion Implantation into Crystalline and Germanium Preamorphized Silicon," Appl. Phys. Lett., 52 (12), 963 (1988).

- (54) R. Subrahmanyan, H. Z. Massoud and R. B. Fair, "Experimental Characterization of Two-Dimensional Dopant Profiles in Silicon Using Chemical Staining," Appl. Phys. Lett., 52 (25), 2145 (1988).

- (55) Y. Kim, H.Z. Massoud and R.B. Fair, "Boron Profile Changes During Low-Temperature Annealing of BF2+-implanted Silicon," Appl. Phys. Lett., .53, 2197 (1988).

- (56) Y. Kim, H.Z. Massoud and R.B. Fair, "The Effect of Ion-Implantation Damage on Dopant Diffusion in Silicon During Shallow-Junction Formation," J. Electronic Mater., 18, 143 (1989).