# The Stacked Capacitor DRAM Cell and Three-Dimensional Memory

Mitsumasa Koyanagi, Department of Bioengineering and Robotics, Toboku University, Japan koyanagi@sd.mecb.toboku.ac.jp

#### Device scaling and the DRAM cell

The key component in a computer system is memory, since both data and instructions in a stored-program-type computer are stored in main memory. Magnetic core memories, used in the early stages of computers, were replaced by semiconductor memories early in the 1970's. The first high density semiconductor memory was 1-Kbit dynamic random access memory (DRAM), developed by Intel. Since the advent of this 1-Kbit DRAM, the packing density and capacity of DRAM have continued to increase to today's 4Gbit. Such increases were achieved by the evolution of the memory cell from a four-transistortype, three-transistor-type to a one-transistor-type. The invention of the one-transistor-type cell (1-T cell) by Robert Dennard especially accelerated the evolution of DRAM in conjunction with his device scaling theory [1, 2].

### Scaling limitation of the planar (2D) DRAM cell

The one-transistor-type cell (1-T cell) consists of one transistor and one capacitor. A transistor acts as a switch, and the signal charges are stored in a capacitor. The first 1-T cell was realized using one switching transistor and one MOS capacitor. The number of signal charges stored in the storage capacitor has to be maintained at almost a constant, or can be only slightly reduced, as the memory cell size is scaled down. However, MOS capacitor value -- and hence the amount of signal charges - is significantly reduced as the memory cell size is reduced, even if the capacitor oxide thickness is scaled-down. Therefore, I forecast in 1975 that the 1-T cell with a twodimensional (2D) structure using a planar MOS capacitor eventually would encounter a scalingdown limitation because we cannot reduce the MOS capacitor area according to scaling theory. In addition, I pointed out that the use of a MOS capacitor in the 1-T cell would be a problem because the signal charges are seriously reduced due to the influence of the minority carriers generated in a silicon substrate. An inversion layer capacitance and a depletion layer capacitance are connected with the gate oxide capacitance in parallel in the MOS capacitor. The charges in the inversion layer and the depletion layer are easily affected by the minority carriers, which are thermally or optically generated or generated by the irradiation of energetic particles in a silicon substrate. Therefore, I predicted that the 1-T cell using an MOS capacitor would encounter a scaling-down limitation due to the influence of the minority carriers as well.

### Invention of the three-dimensional (3D)

In my Ph.D. research during 1971-1974 [3], I had commented on the silicon surface and the inversion layer in MOS structures. To evaluate the electrical properties of the interface states and the inversion layer, I myself built an impedance analyzer with the frequency range of 0.01Hz to 100MHz. I examined various kinds of capacitors, including high-k (high dielectric constant) capacitors as a reference capacitor of this impedance analyzer. Eventually, I made a vacuum capacitor for a reference capacitor in which fintype capacitor electrodes were encapsulated in a vacuum container. From these studies, I learned that an ideal capacitor with low loss should consist of metal electrodes and a low loss insulator (MIM structure); a three-dimensional structure of capacitor electrodes is effective to increase the capacitance value, and there is a trade-off between high-k and loss in the capacitor insulator. In addition, I knew through my Ph.D. research that the charges in the inversion layer and the depletion layer are easily influenced by the minority carriers. Therefore, I questioned why the MOS capacitor with inversion capacitance and the depletion capacitance was used as the storage capacitor in the 1-T cell when I first knew about it in 1975. Then, I tried to eliminate the inversion capacitance and the depletion capacitance by employing a passive capacitor such as the MIM as a storage capacitor and thus proposed a three-dimensional (3D) cell in 1976 [4, 5]. I called this new 3D memory cell a stacked capacitor cell (STC).

## Fabrication and evaluation of the three-dimensional stacked capacitor cell

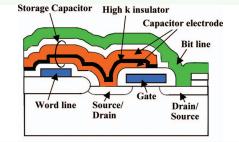

Figure 1 shows the basic structure of a stacked capacitor cell (STC) where the storage capacitor is three-dimensionally stacked on a switching transistor [6, 7]. A passive capacitor with the structure of an electrode-

Fig. 1. Basic structure of stacked capacitor cell (STC).

Winter 2008 © 2008 IEEE IEEE SICS NEWS 37

### TECHNICAL LITERATURE

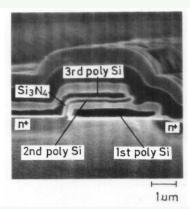

insulator-electrode is used as a storage capacitor. The bottom electrode of the storage capacitor is connected to the source/drain region. I proposed to use selfaligned contacts to connect the bottom electrode of the storage capacitor and a bit line to the source/ drain of the switching transistor. This self-aligned technique was also used for the formation of capacitor electrodes. By three-dimensionally stacking the storage capacitor on the switching transistor we can dramatically reduce the memory cell area. In addition, we can use a high-k material as a capacitor insulator to increase the storage capacitance, since a passive capacitor is used as a storage capacitor. This is also useful for reducing memory cell size. Furthermore, we can solve the problem that the signal charges in the inversion layer and depletion layer are influenced by the minority carriers since an inversion capacitance is not used in a stacked capacitor cell. In 1977, I fabricated the first DRAM test chip with a stacked capacitor cell using 3µm NMOS technology and presented a paper on the stacked capacitor cell in 1978 IEDM (IEEE International Electron Devices Meeting) [6]. Figure 2 shows the SEM cross section of a stacked capacitor cell fabricated using 3µm NMOS technology.

Fig. 2. SEM cross section of a stacked capacitor cell fabricated using 3um nMOS technology.

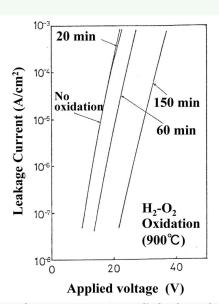

In this figure it is clearly shown that a storage capacitor is stacked on a switching transistor and a self-aligned contact is successfully formed, although plasma etching and RIE (reactive ion etching) were not available at the time. The self-aligned contact is widely used in today's memory LSI's. In this stacked capacitor cell, I employed polycrystalline silicon (poly-Si)- Si $_3N_4$  - polycrystalline silicon (poly-Si) as a storage capacitor. Thermal SiO $_2$  had been used as a capacitor insulator in a conventional 1-T cell with a MOS storage capacitor. In the stacked capacitor cell, I used Si $_3N_4$  instead of SiO $_2$  as a capacitor insulator to increase the storage capacitance. The dielectric constant of Si $_3N_4$  is approximately two times larger than that of SiO $_2$ . I found that the leakage current of Si $_3N_4$  was significantly reduced by oxidizing its surface, as shown in Fig.3.

Fig. 3. Leakage-current versus applied-voltage characteristics for Si<sub>3</sub>N<sub>4</sub> films with thin oxides on their surfaces.

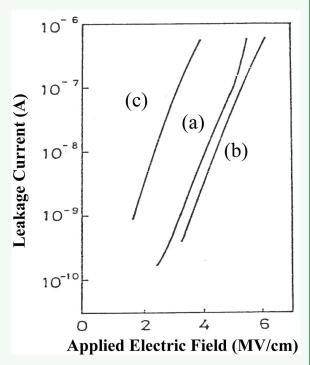

I also used a  ${\rm Ta_2O_5}$  film as a capacitor insulator for the first time [7].  ${\rm Ta_2O_5}$  has a dielectric constant five or six times larger than that of  ${\rm SiO_2}$ . Therefore, we can greatly increase the storage capacitance, although the leakage current is larger compared to those of  ${\rm SiO_2}$  and  ${\rm Si_3N_4}$ , as shown in Fig.4.

Fig. 4. Leakage current – applied electric field characteristics of storage capacitors. (a) poly-Si-SiO<sub>2</sub>-poly-Si, (b) poly-Si-SiO<sub>2</sub> /Si<sub>3</sub>N<sub>4</sub> (ON)-poly-Si, (c) poly-Si/Ta-Ta<sub>2</sub>O<sub>5</sub>-poly-Si.

38 IEEE SSCS NEWS Winter 2008

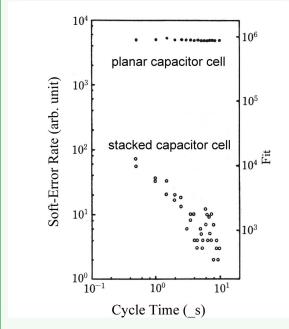

In 1978, when I presented the first stacked capacitor cell paper in IEDM, it was revealed that the data retention characteristics of DRAM are seriously degraded due to "soft-error," which is caused by the carriers generated by alpha-particle irradiation in the silicon substrate. At that time, I believed that a stacked capacitor cell is tolerant of soft-error, since the signal charges stored in the passive capacitor are not influenced by the carriers generated in the substrate. Figure 5 shows the dependence of soft-error rate on cycle time in a DRAM test chip [8]. As I expected, the soft-error rate was dramatically reduced by employing a stacked capacitor cell.

Fig. 5. Dependence of soft-error rate on cycle time in 16 K-bit DRAM test chip.

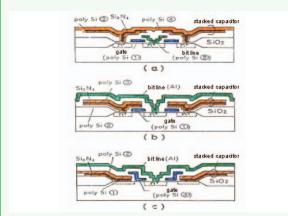

Eventually I proposed three types of stacked capacitor cells as shown in Fig.6 [9].

Fig. 6. Cross-sectional configuration of three types of stacked capacitor cells. (a) top-capacitor-type cell, (b) intermediate-capacitor-type cell, (c) bottom-capacitor-type cell.

A storage capacitor is stacked on the switching transistor and the bit line in a top-capacitor-type cell, on the switching transistor in the intermediate-capacitor-type cell (original stacked capacitor cell) and on the isolation oxide (LOCOS) in the bottom-capacitor-type cell. The top-capacitor-type STC cell is another name for the capacitor-over-bit line (COB) stacked capacitor cell and widely used in current DRAM [10]. We can use various kinds of materials for the capacitor insulator and electrodes, and can employ low temperature processes in the formation of the storage capacitor in the COB-type stacked capacitor cell since the storage capacitor is formed on the top of the memory cell.

# Evolution of the three-dimensional (3D) memory cell and future memory

In 1979, I fabricated 16K-bit DRAM using a stacked capacitor cell with the oxidized Si<sub>2</sub>N<sub>4</sub> (O/N) capacitor insulator [9]. Then I tried to introduce a stacked capacitor cell in 64K-bit DRAM production. However, it was too early to do this due to cost. As a result, the oxidized Si<sub>3</sub>N<sub>4</sub> (O/N) capacitor insulator was employed in 64K-bit DRAM production. Since then, the oxidized Si<sub>2</sub>N<sub>4</sub> (O/N) capacitor insulator has been widely used for DRAM production. A stacked capacitor cell was employed in a 1Mbit DRAM production for the first time by Fujitsu [11]. Hitachi also employed a stacked capacitor cell in 4Mbit DRAM production [12]. Many other DRAM companies used a trench capacitor cell in the early stage of 4Mbit DRAM production. However, the stacked capacitor cell, which eventually came to occupy a major position in 4Mbit to 4Gbit DRAM's, has evolved by introducing the three-dimensional capacitor structures with fin-type electrode [13] and cylindrical electrode [14] in conjunction with a capacitor electrode surface morphology of hemi-spherical grain (HSG) [15]. In addition to the introduction of the three-dimensional capacitor structure, a storage capacitor insulator with high dielectric constant (high-k) was employed in high density DRAM's. In general, the leakage current of high-k material increases by high temperature processing. Therefore, a COB-type stacked capacitor cell is suitable for introducing a high-k capacitor insulator since the storage capacitor can be formed by a lower temperature process. Thus, the Ta<sub>2</sub>O<sub>5</sub> capacitor insulator was employed in 64Mbit and 256Mbit DRAM's with a COB-type stacked capacitor cell. Since then, various kinds of high-k materials have been studied as storage capacitor insulators in high density DRAM's beyond 1Gbit. The concept of the COB-type stacked capacitor cell -- that various kinds of materials can be stacked on the switching transistor using a lower temperature process -- has been carried on in new memories with a three-dimensional structure such as Fe-RAM (Ferroelectric RAM), P-RAM (Phase Change RAM), R-RAM (Resistive RAM) and M-RAM (Magnetic RAM).

In a high density stacked capacitor DRAM beyond 16 Gbit, a twitching transistor with a three-dimensional structure such as a Fin-FET and a vertical transistor

Winter 2008 IEEE SSCS NEWS 39

### **TECHNICAL LITERATURE**

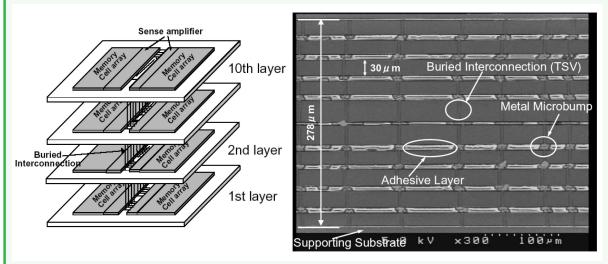

Fig. 7. SEM cross section of 3D-DRAM test chip with ten memory layers fabricated by wafer-on-wafer bonding technology with through-silicon-vias (TSV's).

will be employed together with a cylindrical capacitor and high-k capacitor insulator. Furthermore, many DRAM chips eventually will be vertically stacked to realize 3D-DRAM in which the memory capacity dramatically increases. We have already succeeded in fabricating a 3D-DRAM test chip with ten memory layers as shown in Fig.7 [16, 17].

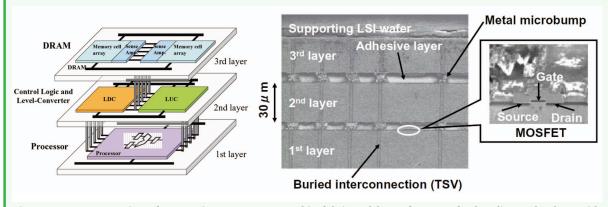

This 3D-DRAM test chip was fabricated using a newly developed wafer-on-wafer bonding technology with through-silicon-vias (TSV's) [18-20]. Such a 3D-DRAM can be directly stacked on a microprocessor chip to realize a 3D-microprocessor and to solve the problems of memory data-bandwidth between the memory and the processor. We also fabricated a 3D-microprocessor test chip in which a DRAM chip is stacked on a processor chip, as shown in Fig.8 [21].

In the future, various kinds of LSI chips, sensor chips and MEMs chips will be vertically stacked into an ultimate 3D-LSI which we call a super-chip [17, 22]. We have developed a new super-chip integration technology using a novel self-assembly method.

#### References

- [1] R.H. Dennard, USP-3387286, June 4, 1968.

- [2] R.H. Dennard, F.H. Gaensslen, H.N. Yu, V.L. Rideout, E. Bassous, and A.R. LeBlanc, "Design of Ion Implanted MOSFET's with Very Small Physical Dimensions", IEEE J. Solid-State Circuits, Vol. SC-9, pp. 256-268, Oct. 1974.

- [3] J. Nishizawa, M. Koyanagi and M. Kimura, "Impedance Measurements to Study Semiconductor Surface and Thin Insulating Films on Its Surface", Japanese J. Applied Phys., Suppl. 2, pp.773-779, 1974.

- [4] M. Koyanagi and K. Sato, Japanese patent application, Tokugansho 51-78967, 1976.

- [5] M. Koyanagi and K. Sato, USP-4151607, Jan. 5, 1977.

- [6] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, "Novel High Density, Staked Capacitor MOS RAM", IEDM Tech. Dig., pp. 348-351, Dec. 1978.

- [7] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, "Novel High Density, Staked Capacitor MOS RAM", Extended Abstracts of the 10th Confer-

Fig. 8 SEM cross section of a 3D-microprocessor test chip fabricated by wafer-on-wafer bonding technology with through-silicon-vias (TSV's).

40 IEEE SSCS NEWS Winter 2008

- ence on Solid State Devices, 1978.

- [8] M. Koyanagi, Y. Sakai, M. Ishihara, M. Tazunoki and N. Hashimoto, "16-kbit Stacked Capacitor MOS RAM", IEICE Technical Report (Japanese), SSD80-30, 1980.

- [9] M. Koyanagi, Y. Sakai, M. Ishihara, M. Tazunoki and N. Hashimoto, "A 5-V Only 16-kbit Stacked Capacitor MOS RAM", IEEE Trans. on Electron Devices, ED-8, pp.1596-1601, 1980/ IEEE J. Solid-State Circuits, SC-15, pp.661-666, 1980.

- [10] S. Kimura, Y. Kawamoto, T. Kure, N. Hasegawa, J. Etoh, M. Aoki, E. Takeda, H. Sunami and K. Itoh, "A New Stacked Capacitor DRAM Cell Characterized by a Storage Capacitor on a Bit-line Structure", IEDM Tech. Dig., pp. 596-599, Dec. 1988.

- [11] Y. Takemae, T. Ema, M. Nakano, F. Baba, T. Yabu, K. Miyasaka, K. Shirai, "A 1Mb DRAM with 3-Dimensional Stacked Capacitor Cells", ISSCC Dig. Tech. Papers, pp. 250-251, Feb. 1985.

- [12] K. Kimura, K. Shimohigashi, J. Etoh, M. Ishihara, K. Miyazawa, S. Shimizu, Y. Sakai, and K. Yagi, "A 65-ns 4-Mbit CMOS DRAM with a Twisted Driveline Sense Amplifier", IEEE J. Solid-State Circuits, SC-22, pp.651-656, 1987.

- [13] T. Ema, S. Kawanago, T. Nishi, S. Yoshida, H. Nishide, T. Yabu, Y. Kodama, T. Nakano, M. Taguchi, "3-Dimensional Stacked Capacitor Cell for 16M and 64M DRAMs", IEDM Tech. Dig., pp. 592-595, Dec. 1988.

- [14] W. Wakamiya, Y. Tanaka, H. Kimura, H. Miyatake and S. Satoh, "Novel Stacked Capacitor Cell for 64Mb DRAM", Symposium on VLSI Technology Dig. Tech. Papers, pp. 69-70, 1989.

- [15] H. Watanabe, T. Tatsumi, S. Ohnishi, T. Hamada, I. Honma, T. Kikkawa, "A New Cylindrical Capacitor Using Hemispherical Grained Si (HSG-Si) for 256Mb DRAMs," IEDM Tech. Dig., pp. 259 - 262, Dec. 1992.

- [16] K.W. Lee, T. Nakamura, T. Ono, Y. Yamada, T. Mizukusa, H. Hashimoto, K.T. Park, H. Kurino and M. Koyanagi, "Three-Dimensional Shared Memory Fabricated Using Wafer Stacking Technology", IEDM Tech. Dig., pp. 165-168, Dec. 2000.

- [17] T. Fukushima, Y. Yamada, H. Kikuchi, and M. Koyanagi, "New Three-Dimensional Integration Technology Using Self-Assembly Technique", IEDM Tech. Dig., pp. 359-362, Dec. 2005.

- [18] M. Koyanagi, "Roadblocks in Achieving Three-Dimensional LSI", 8th Symposium on Future Electron Devices Tech. Dig., pp.55-60, 1989.

- [19] H. Takata, T. Nakano, S. Yokoyama, S. Horiuchi, H. Itani, H. Tsukamoto and M. Koyanagi, "A novel fabrication technology for optically interconnected three-dimensional LSI by wafer aligning and bonding technique," Proc. Int. Semiconductor Device Research Symposium, pp.327-330, 1991.

- [20] M. Koyanagi, T. Nakamura, Y. Yamada, H. Kikuchi, T. Fukushima, T. Tanaka, and H. Kurino, "Three-Dimensional Integration Technology Based on Wafer Bonding With Vertical Buried Interconnections", IEEE Trans.

- on Electron Devices, vol.53, pp. 2799-2808, 2006.

- [21] T. Ono, T. Mizukusa, T. Nakamura, Y. Yamada, Y. Igarashi, T. Morooka, H. Kurino and M. Koyanagi, "Three-Dimensional Processor System Fabricated by Wafer Stacking Technology", IEEE COOL Chips V Tech. Dig., pp.186-193, 2002.

- [22] T. Fukushima, Y. Yamada, H. Kikuchi, T. Konno, J. Liang, K. Sasaki, K. Inamura, T. Tanaka, and M. Koyanagi, "New Three-Dimensional Integration Technology Based on Reconfigured Wafer-on-Wafer Bonding Technique", IEDM Tech. Dig., pp. 985-988, Dec. 2007.

#### **About the Author**

**Mitsumasa Koyanagi** was born in 1947 in Hokkaido, Japan. He received the B.S. degree from Department of Electrical Engineering, Muroran Institute of Technology, Japan in 1969 and the M.S. and Ph.D. degrees from Department of Electronic Engineering,

Tohoku University in 1971 and 1974, respectively.

He joined the Central Research Laboratory, Hitachi Co. Ltd. in 1974 where he had engaged in the research and development of DRAM and ASIC process and device technologies and invented a Stacked Capacitor DRAM memory cell which has been widely used in DRAM production. In 1985, he joined Xerox Palo Alto Research Center, where he was responsible for research on submicron CMOS devices, poly-Si TFT devices and analog/digital sensor LSI design. In 1988, he became a professor in the Research Center for Integrated Systems, Hiroshima University, Japan where he engaged in the research of sub-0.1um device fabrication and characterization, device modeling, poly-Si TFT devices, 3-D integration technology, optical interconnection and parallel computer system. He proposed a 3-D integration technology based on wafer-to-wafer bonding and through-Si vias (TSVs) in 1989. Since 1994, he has been a professor in the Intelligent System Design Lab., Department of Machine Intelligence and Systems Engineering, and is currently a member of the Department of Bioengineering and Robotics, Graduate School of Engineering, Tohoku University, Japan. His current interests are 3-D integration technology, optical interconnection, nano-CMOS devices, memory devices, parallel computer system specific for scientific computation, real-time image processing system, artificial retina chip and retinal prosthesis chip, brain-machine interface (BMI) and neural prosthesis chip, brain-like computer system.

Dr. Koyanagi was awarded the IEEE Jun-Ichi Nishizawa Medal (2006), the IEEE Cledo Brunetti Award (1996) and Japan's Ministry of Education, Culture, Sports, Science and Technology Award (2002), in addition to the Ohkouchi Prize (1992), SSDM (Solid-State Devices and Materials Conf.) Award (1994) and the Opto-Electronic Integration Technology (Izuo Hayashi) Award in 2004. He is an IEEE fellow.

Winter 2008 IEEE SSCS NEWS 41