Ericsson Ex. 2072, Page 1 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806

Preeti Ranjan Panda, Aviral Shrivastava, B. V. N. Silpa and Krishnaiah Gummidipudi, *Power-efficient System Design*, DOI: 10.1007/978-1-4419-6388-8, © Springer Science+Business Media, LLC 2010

Preeti Ranjan Panda, Aviral Shrivastava, B. V. N. Silpa and Krishnaiah Gummidipudi

# **Power-efficient System Design**

#### Preeti Ranjan Panda

Department of Computer Science and Engineering, Indian Institute of Technology, New Delhi, India

#### Aviral Shrivastava

Department of Computer Science and Engineering, Arizona State University, Tempe, USA

#### B. V. N. Silpa

Department of Computer Science and Engineering, Indian Institute of Technology, New Delhi, India

#### Krishnaiah Gummidipudi

Department of Computer Science and Engineering, Indian Institute of Technology, New Delhi, India

ISBN 978-1-4419-6387-1 e-ISBN 978-1-4419-6388-8

Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010929487

© Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Preface**

The Information and communication technology (ICT) industry is said to account for 2% of the worldwide carbon emissions – a fraction that continues to grow with the relentless push for more and more sophisticated computing equipment, communications infrastructure, and mobile devices. While computers evolved in the direction of higher and higher performance for most of the latter half of the 20th century, the late 1990's and early 2000's saw a new emerging fundamental concern that has begun to shape our day-to-day thinking in system design – power dissipation. As we elaborate in Chapter 1, a variety of factors colluded to raise power-efficiency as a first class design concern in the designer's mind, with profound consequences all over the field: semiconductor process design, circuit design, design automation tools, system and application software, all the way to large data centers.

Power-efficient System Design originated from a desire to capture and highlight the exciting developments in the rapidly evolving field of power and energy optimization in electronic and computer based systems. Tremendous progress has been made in the last two decades, and the topic continues to be a fascinating research area. To develop a clearer focus, we have concentrated on the relatively higher level of design abstraction that is loosely called the *system level*. In addition to the extensive coverage of traditional power reduction targets such as CPU and memory, the book is distinguished by detailed coverage of relatively modern power optimization ideas focussing on components such as compilers, operating systems, servers, data centers, and graphics processors.

The book is primarily intended to serve as a graduate-level text. An elementary familiarity with digital design, computer architecture, and system software utilities such as compilers and operating systems, is necessary in order to appreciate the contents of the book. However, in Chapter 2, we do attempt to quickly cover some of the background material on which the later discussion is based. After reading this book, the reader can expect to obtain a reasonable understanding of the opportunities for introducing power and energy efficiency into electronic and computer based systems, the current approaches targeting this objective, and the challenges ahead.

We gratefully acknowledge the feedback given by Sorav Bansal, Kolin Paul, Neeraj Goel, Anoop Nair, and Kumar S. S. Vemuri on an earlier version of the manuscript. We owe our gratitude to Chuck Glaser for his words of encouragement and valuable advice during the writing process; it has been an immense pleasure working with him.

Finally, we would like to place on record our heartfelt thanks to Lima Das for working very hard to design the impressive and very appropriately conceived cover artwork.

Preeti Ranjan Panda

Aviral Shrivastava

B. V. N. Silpa

Krishnaiah Gummidipudi

New Delhi, India and Tempe, USA

June 2010

# **Contents**

- 1 Low Power Design: An Introduction

- 1.1 The Emergence of Power as an Important Design Metric

- 1.2 Power Efficiency vs. Energy Efficiency

- 1.3 Power-Performance Tradeoff

- 1.4 Power Density

- 1.5 Power and Energy Benchmarks

- 1.6 Power Optimizations at the System Level

- 1.7 Organization of this Book

#### References

- 2 Basic Low Power Digital Design

- **2.1 CMOS Transistor Power Consumption**

- 2.2 Trends in Power Consumption

- 2.3 Techniques for Reducing Dynamic Power

- 2.4 Techniques for Reducing Short Circuit Power

- 2.5 Techniques for Reducing Leakage Power

- 2.6 Summary

#### References

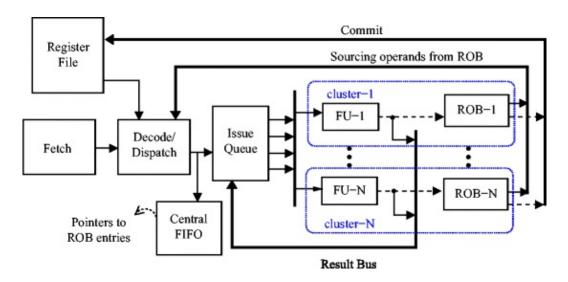

- 3 Power-efficient Processor Architecture

- 3.1 Introduction

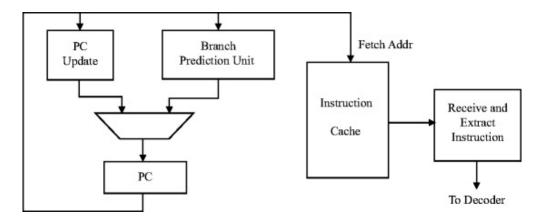

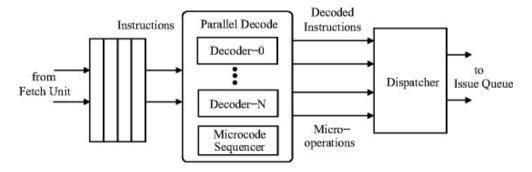

- 3.2 Front-end: Fetch and Decode Logic

- 3.3 Issue Queue / Dispatch Buffer

- 3.4 Register File

| 3.5 Execution Units                                                  |  |  |  |

|----------------------------------------------------------------------|--|--|--|

| 3.6 Reorder Buffer                                                   |  |  |  |

| 3.7 Branch Prediction Unit                                           |  |  |  |

| 3.8 Summary                                                          |  |  |  |

| References                                                           |  |  |  |

| 4 Power-efficientMemory and Cache                                    |  |  |  |

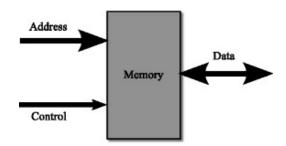

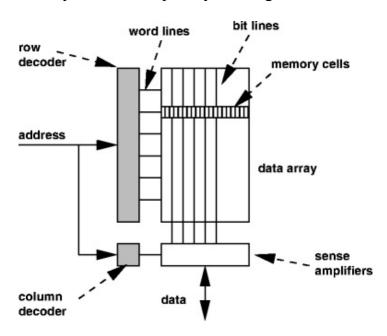

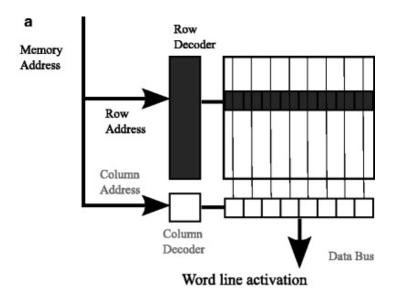

| 4.1 Introduction and Memory Structure                                |  |  |  |

| 4.2 Power-efficient Memory Architectures                             |  |  |  |

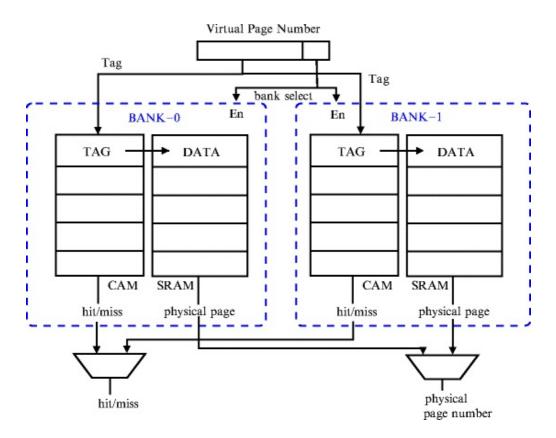

| 4.3 Translation Look-aside Buffer (TLB)                              |  |  |  |

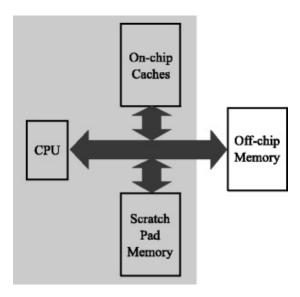

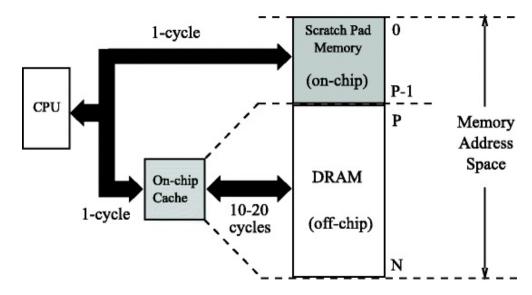

| 4.4 Scratch Pad Memory                                               |  |  |  |

| 4.5 Memory Banking                                                   |  |  |  |

| 4.6 Memory Customization                                             |  |  |  |

| 4.7 Reducing Address Bus Switching                                   |  |  |  |

| 4.8 DRAM Power Optimization                                          |  |  |  |

| 4.9 Summary                                                          |  |  |  |

| References                                                           |  |  |  |

| 5 Power Aware Operating Systems, Compilers, and Application Software |  |  |  |

| 5.1 Operating System Optimizations                                   |  |  |  |

| 5.2 Compiler Optimizations                                           |  |  |  |

| 5.3 Application Software                                             |  |  |  |

| 5.4 Summary                                                          |  |  |  |

| References                                                           |  |  |  |

| 6 Power Issues in Servers and Data Centers                           |  |  |  |

| 6.1 Power Efficiency Challenges                                      |  |  |  |

Ericsson Ex. 2072, Page 7 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806

| 6.2 Where does the Power go?                 |

|----------------------------------------------|

| 6.3 Server Power Modeling and Measurement    |

| 6.4 Server Power Management                  |

| 6.5 Cluster and Data Center Power Management |

| 6.6 Summary                                  |

| References                                   |

| 7 Low Power Graphics Processors              |

| 7.1 Introduction to Graphics Processing      |

| 7.2 Programmable Units                       |

| 7.3 Texture Unit                             |

| 7.4 Raster Operations                        |

| 7.5 System Level Power Management            |

| 7.6 Summary                                  |

| References                                   |

Index

| Preeti Ranjan Panda, B. V. N. Silpa, Aviral Shrivastava and Krishnaiah Gummidipudi, <i>Power-efficient System Design</i> , DOI: 10.1007/978-1-4419-6388-8_1, © Springer Science+Business Media, LLC 2010 |                                                 |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          |                                                 |  |  |  |

|                                                                                                                                                                                                          | Ericsson Ex. 2072, Page 9 TCL et al. v Ericsson |  |  |  |

IPR2015-01674, -01676, -01761, -01806

# 1. Low Power Design: An Introduction

Preeti Ranjan Panda<sup>1™</sup>, Aviral Shrivastava<sup>2™</sup>, B. V. N. Silpa<sup>1™</sup> and Krishnaiah Gummidipudi<sup>1™</sup>

- (1) Department Computer Science and Engineering, Indian Institute of Technology, Hauz Khas, 110016 New Delhi, India

- (2) Department of Computer Science and Engineering, Arizona State University, 699 South Mill Avenue, 85281 Tempe, USA

- **Preeti Ranjan Panda (Corresponding author)**

Email: panda@cse.iitd.ac.in

**Marial Shrivastava** ■ Aviral Shrivastava

Email: Aviral.Shrivastava@asu.edu

**■** B. V. N. Silpa

Email: silpa@cse.iitd.ac.in

Krishnaiah Gummidipudi

Email: krishna@cse.iitd.ac.in

#### **Abstract**

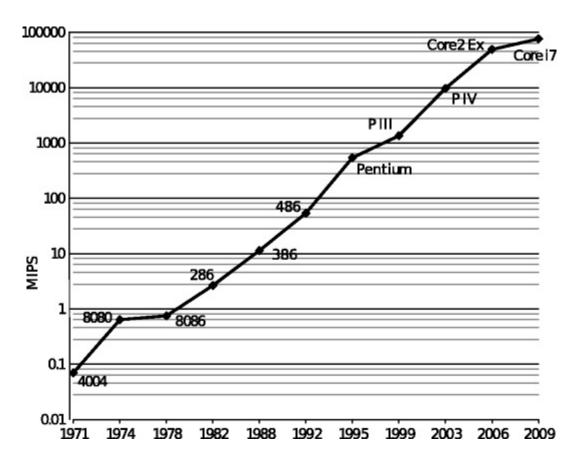

Through most of the evolution of the electronics and computer industry in the twentieth century, technological progress was defined in terms of the inexorable march of *density* and *speed*. Increasing density resulted from process improvements that led to smaller and smaller geometries of semiconductor devices, so the number of transistors packed into a given area kept increasing. Increasing processing speed indirectly resulted from the same causes: more processing power on the same chip meant more computation resources and more data storage on-chip, leading to higher levels of parallelism and hence, more computations completed per unit time. Circuit and architectural innovations were also responsible for the increased speed. In the case of processors, deeper pipelines and expanding parallelism available led to improvements in the effective execution speed. In the case of memories, density continued to make remarkable improvements; performance improvements were not commensurate, but nevertheless, architectural innovations led to increased bandwidth at the memory interface.

# 1.1 The Emergence of Power as an Important Design Metric

Through most of the evolution of the electronics and computer industry in the twentieth century, technological progress was defined in terms of the inexorable march of *density* and *speed*. Increasing density resulted from process improvements that led to smaller and smaller geometries of semiconductor devices, so the number of transistors packed into a given area kept increasing. Increasing processing speed indirectly resulted from the same causes: more processing power on the same chip meant more computation resources and more data storage on-chip, leading to higher levels of parallelism and hence, more computations completed per unit time. Circuit and architectural innovations were also responsible for the increased speed. In the case of processors, deeper pipelines and expanding parallelism available led to improvements in the effective execution speed. In the case of memories, density continued to make remarkable improvements; performance improvements were not commensurate, but nevertheless, architectural innovations led to increased bandwidth at the memory interface.

In parallel to the steady march in the density and performance of high-end chips such as processors, a quiet mobile revolution was ignited in the 1990s. The specification for components targeting mobile systems were very different from the high-end processors. These chips had to fit into very tight power budgets defined by battery life considerations, which led to a significant investment in low power design techniques, methodologies, and tools. Starting early 1990s, researchers began to consider modifying the entire electronic design automation tool chain by incorporating power awareness. Even as the complexity of Systems-on-a-Chip (SoC) increased significantly and proceeded in the direction of integration of a large number of modules (cores), the individual cores were still designed to tight power constraints and intelligence was introduced in the overall power management of these SoCs in order to meet chip-level power budgets. Many of these cores were processors in themselves, but these were architected very differently from the standard high-end desktop or server processor – speed of individual cores was heavily compromised to meet power constraints by keeping the design simple. It was a prescient move – the high-end multicore processors of the early 21st century would later adopt the same philosophy.

Through the late 1990s and early 2000s, the parallel evolution of the two seemingly unrelated lines of products continued unabated. High end processor systems delivered on the traditional density and performance scaling promise through increased architectural sophistication, while the mobile revolution was well under way, spearheaded by the ubiquitous cell phone.

Towards the mid-2000s, important directional changes were visible in the evolution of these technologies. Cell phone makers began packing more and more functionality into their devices, making them look increasingly similar to general purpose programmable devices. All the functionality still had to be delivered within the tight power envelope of a few watts – imposed by the simple physical requirement that the device should fit and stay within the pocket without burning a hole through it. Desktop processors, at the same time, ran up against an unexpected barrier – the *power wall*, which imposed an upper limit on the power dissipation. It turned out that, if the processor power exceeded around 150 W, then the simple fan-based cooling mechanism used in desktop computers might be inadequate. More sophisticated cooling would increase the cost of the systems to inordinate levels – the consumer had got used to price drops with increasing performance over the years. Suddenly, power related innovation became a top concern even in high-end processors, altering the designer's priorities radically after decades of riding the predictable performance and density curves.

A third front had opened with the exploding Internet revolution – the world was getting more and more connected, powered by infrastructural re-organization that was not obviously visible to the enduser, but nevertheless, an important enabling innovation. Large scale distributed storage and processing capabilities had become necessary. To handle the terabytes of data continuously being generated, stored, and retrieved, data had to be organized in non-trivial ways. Similarly, the huge processing and computation power also needed similar architectural paradigm shifts. Data centers were the offshoot of these pressing requirements. Designers realized the economies of scale provided by aggregations of tens of thousands of computers stacked into a warehouse-style environment, which would make more efficient utilization of space than the maintenance of a large number of small server rooms in individual companies. Service models began to evolve based on this idea. There was just one issue – power. Large data centers draw megawatts of power. It is well established that the annual energy cost of operating a large data center rivals the cost of the equipment itself. The time had come to start worrying about ways to reduce the energy bills. Further, the concentration of a large number of powerful computers in a data center leads to a very high thermal density, with significant consequences on the cooling technology required to maintain the systems within the operating temperature range, ultimately impacting the cost of maintaining the infrastructure.

As we proceed to the 2010s, it is amply clear that no one can run away from the looming power wall. Far from being limited to battery-operated devices, power and energy efficiency now has to be built into products at every level of abstraction, starting from the semiconductor device level, through circuit and chip levels, all the way to compilers, operating systems, and large data centers. While earlier generations of hardware designers invariably optimized the product for high performance and reported the power dissipation merely as a documentation exercise to generate complete data sheets for the customer, newer generations of designers now need to aggressively optimize for power – even at the expense of performance. Power is now elevated to what is referred to as a *first class design concern*.

Power awareness on the software side of the computation stack expressed itself as an issue somewhat later, as expected. This followed after appropriate hooks were provided by the hardware. It didn't take long for researchers to realize that a huge opportunity lay ahead for power aware system and application software. This followed the observation that at least some of the hardware power optimizations would work better if there were hints passed on to the hardware by the software and vice versa. For example, a higher level macroscopic view of a system as a whole is available to an application designer or a compiler that is able to view and analyze an extended piece of code, than a processor that is able to view only one small window of instructions at a time. Power efficiency demands are now placed on compilers, application developers, and operating systems.

The need for energy efficiency in electronic and computer systems tracks the global need for energy efficiency in every other walk of life. At a time when the world is acutely aware of the environmental consequences of the huge collective footprint of our individual actions, and struggling to evolve a sustainable solution, it is natural that power efficiency and energy efficiency concerns should permeate into everything we do. With electronic and computer systems beginning to play such a dominant role in our day-to-day lives, they present themselves as perfect targets on which to focus our power efficiency efforts.

# 1.2 Power Efficiency vs. Energy Efficiency

Since the terms *power efficiency* and *energy efficiency* are both used in literature, often interchangeably, let us look at the elementary definitions of power and energy and clarify the distinction between power and energy efficiency and between the objectives of power and energy optimizations.

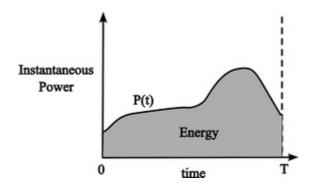

Figure 1.1 shows the instantaneous power dissipated by a system S as a function of time. The power P(t) will vary from time to time because the work done inside the system typically changes with time. In electronic systems, power is, in turn, determined by the current drawn by the system and the voltage at which it operates, as a function of time:

$$P(t) = V(t) \times I(t) \tag{1.1}$$

where *V* and *I* are the instantaneous voltage and current respectively. If the external supply voltage remains constant, as is common in many systems, power is directly proportional to the current drawn, and the power curve essentially tracks the variation of the current over time.

Fig. 1.1 The relationship between power and energy: the area under the power curve over a time interval gives the energy consumed

What about energy dissipation by the same system S? Power is simply the rate at which energy is dissipated, so the energy dissipated over a period t = 0 to t = T is given by:

$$E = \int_0^T P(t) dt \tag{1.2}$$

This corresponds to the area under the P(t) curve as indicated in Fig. 1.1.

A system S' that delivers the same work as the one in Fig. 1.1 in the same duration T, but is characterized by a different power curve P'(t), as shown in Fig. 1.2(a), would be called more power-efficient because the P' curve is always lower than P. What about its energy dissipation? Its energy E' corresponds to the area under the P' curve, which is clearly less than E. Hence, E' is also more energy-efficient.

**Fig. 1.2** Power efficiency and energy efficiency. Three systems S, S', and S' have power curves P, P', and P' respectively. (a) S' is more power-efficient and more energy-efficient than S. (b) S' has lower peak power than S. S' has lower average power/energy than S in time period [0, T'] if E' < E

On the other hand, let us consider the power characteristic of a different system S' shown in Fig. 1.2(b). System S' has a power curve P' that is under P most of the time, but it takes longer to complete its task (T' > T). The energy dissipated is now given by:

$$E''; l = \int_{0}^{T''} P''(t) dt \tag{1.3}$$

Which of S, S' is more power efficient? Which is more energy-efficient?

The energy efficiency question is easier to answer -S' is more energy efficient if E' < E. This is a clearer question because energy corresponds to the total work done by a system, independent of completion time.

Power, on the other hand, is intricately tied to completion times, and the definition of power-efficiency needs to be clarified in a given context. Two major power efficiency criteria are commonly relevant:

#### 1. Peak power

#### 2. Average power

The peak power criterion is sometimes externally imposed on a system. If minimizing peak power is the objective, then S' is more efficient. If a peak power constraint is imposed on the system, then the design has to be adjusted to ensure that the power curve is always under the horizontal line corresponding to the power constraint, irrespective of how long it takes for completion.

Average power is defined with respect to a time interval. In Fig. 1.2(b), if we take the time interval [0, T], then we have:

Average Power for

$$S = \frac{E}{T''}$$

(1.4)

Ericsson Ex. 2072, Page 14 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806 Average Power for  $S'' = \frac{E''}{T''}$  (1.5)

Note that, for a fair comparison of the two systems, the time durations should be the same. S' has completed its task at time T, and is consuming zero power between T and T', which should be accounted for in the average power calculation. Since the two denominators are the same, the relationship between the average power dissipation between the two systems is identical to the relationship between the total energy.

Requirements for energy efficiency or average power reduction usually stem from battery life considerations. To a level of approximation, battery capacity can be viewed in terms of a fixed amount of total energy that it can supply.

Requirements for peak power usually stem from two sources:

- external power supply may impose a constraint on the maximum instantaneous power that can be supplied; or

- there may be a cap on the maximum temperature (which is indirectly determined by peak power) that a device is allowed to reach. This could be applicable to both mobile devices as well as powerful server computers.

In this book we discuss different classes of mechanisms that target the reduction of either energy (average power) or peak power. The actual objective is clarified from the context in which it appears.

#### 1.3 Power-Performance Tradeoff

Figure 1.2(b) illustrates an important trade-off between peak power and performance that is not merely theoretical. The trade-off is real and has tremendously influenced the direction taken by the mobile computer industry. The explosion of interest in ultra-portable computers (also referred to as *netbooks*) in recent times, along with the evolution of cell phones into more sophisticated gadgets that make them look more like handheld computers, clearly shows that there is a huge potential for the market segment where computer systems are held within a tight power budget while sacrificing performance. Netbooks run on processors with very low peak power and correspondingly weak performance; their acceptance in the market may imply that the average set of applications run by many users just don't require very high speed. Instead of raw speed, other important features such as network connectivity, mobility, and battery life are valued. The race to deliver higher and higher raw performance may have transformed into a more nuanced battle, with new battle grounds being created that squarely put power and energy at the center.

Design metrics such as *energy-delay product* are some times used to evaluate the relative merits of two implementations in a way that accounts for both energy and performance [1]. Such metrics help in discriminating between alternatives that are equivalent in total energy dissipation but different in performance. Energy-delay products for the two systems above are given by:

```

Energy-Delay Product for S = E \times T

Energy-Delay Product for S'' = E'' \times T''

```

The term *performance-per-watt* is sometimes used in the industry to characterize energy efficiency of hardware [2]. This term is effectively a direct or indirect computation of 1/E, with E defined as above. The *performance* measure here can be interpreted in different ways, for example, execution frequency or throughput of computation. If performance is interpreted as the inverse of latency T, then we have:

Performance-per-watt =

$$\frac{1}{T} \times \frac{1}{P} = \frac{1}{E}$$

Higher performance-per-watt means more energy-efficient (lower total energy) and vice versa.

The performance-per-watt metric gives equal emphasis to power and performance, while the energy-delay product  $(E \times T = P \times T^2)$  gives higher emphasis to performance (the latter varies quadratically with delay).

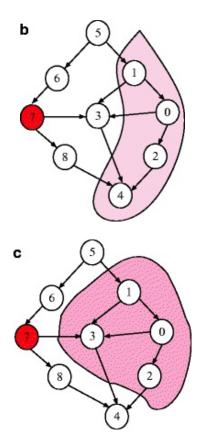

# 1.4 Power Density

Power density is an additional important concern that is not captured in a straightforward way by the power and energy efficiency metrics discussed above. This refers to the fact that the distribution of power dissipation across a chip is never uniform because different modules exhibit different degrees of activity in any fixed period of time. Thus, the power density – the dynamic energy dissipated per unit area – is non-uniformly distributed on the chip, leading to hotspots where the power density is significantly high. Higher power density leads to higher temperatures, and a non-uniform power density leads to a non-uniform temperature variation on the chip, leading to some associated problems. Even if the average and peak power numbers are acceptable, power density variations can cause regions on the chip to have unacceptably high temperatures leading to failures. Thus, the chip designer also needs to target a relatively uniform distribution of power density in the resulting chip.

# 1.5 Power and Energy Benchmarks

The rising importance of power and energy motivated the eventual development of benchmarking efforts targeting the evaluation of different classes of systems with respect to power and energy. *Powerstone* [3] was among the early reported efforts targeting power evaluation of mobile embedded systems. The Powerstone benchmark contained applications selected from the following domains: automobile control (*auto* and *engine*), signal and image processing (*fir\_int* – integer FIR filter, *jpeg* – JPEG decompression, *g721* – voice compression, and *g3fax* – fax decode), graphics (*bilt*), and several utilities (*compress* – UNIX file compression, *crc* – cyclic redundancy check, *bilv* – bit vector operations, *des* – data encryption, etc.).

Joulesort [4] is a more modern benchmarking effort aimed at power evaluation of high-end server, cluster, and data center class computer systems. The benchmark consists of essentially an application for sorting a randomly permuted collection of records. Different categories of the benchmark contain different input data sizes (10 GB, 100 GB, and 1 TB). Thus, the benchmark has I/O as the primary emphasis, with secondary emphasis on CPU and memory. Joulesort is good at exercising whole system level power efficiencies. The proposed evaluation metric used here is the energy consumed for processing a fixed input size.

# 1.6 Power Optimizations at the System Level

In this book we will explore power optimizations at the *system level* of abstraction. Since the word *system* is very generic, it is important to clarify its interpretation as used in this book. The following different levels of abstraction could possibly be considered in the context of power optimizations. They are arranged in the increasing level of granularity.

This refers to the choice of the appropriate semiconductor materials and processes used to fabricate transistors and other devices in this class which form the building blocks of electronic technology.

This refers to the interconnection of transistors and the related class of components, along with the choice of appropriate geometry for these devices.

This refers to the logic level of abstraction, where the components (*gates*) implement simple combinational and sequential functions (such as AND, MUX, flip-flops, etc.). A logic synthesis tool generates an optimized logic netlist starting from an unoptimized gate level description, or some other simple format such as a truth table.

This refers to a description that is usually expressed in a Hardware Description Language (HDL), containing a cycle-accurate description of the hardware to be designed. RTL synthesis tools automate the generation of a gate netlist from an RTL HDL description. The architecture view of a processor or other hardware falls in this level of abstraction.

At this level, the hardware is still described in an HDL, but the level of detail is lesser than RTL. For example, we may specify an algorithm implemented in hardware, but indicate nothing about which operation is performed in which clock cycle. A behavioral synthesis tool takes a behavioral level model as input, performs a series of *high level synthesis* optimizations, and finally generates an RTL HDL design, to be processed further.

At this level – pertaining to SoC design – the design is no longer a pure hardware design. In fact, the decision of which part of the specification will go into hardware and which into software, has not been finalized yet. The details of the computation in individual blocks and communication across blocks of the SoC are not specified yet.

At this level, we have moved to software executing on a processor hardware. This level encompasses all application software and key system software such as compilers that have a deeper view of a single application, and operating systems that have a wider view of the run-time environment.

This level of abstraction refers to an aggregation of electronic and computer systems that can be considered complete in some sense - for example, cell phones, laptops, dedicated servers, all the way up to data centers.

Our focus on system-level design covers the behavioral and higher levels. That is, in this book we focus on the Behavioral Level, Transaction Level, Application and System Software Level, and Full System, Server, and Data Center Levels. Key power optimization strategies at lower levels of abstraction are summarized briefly in Chapter 2.

## 1.7 Organization of this Book

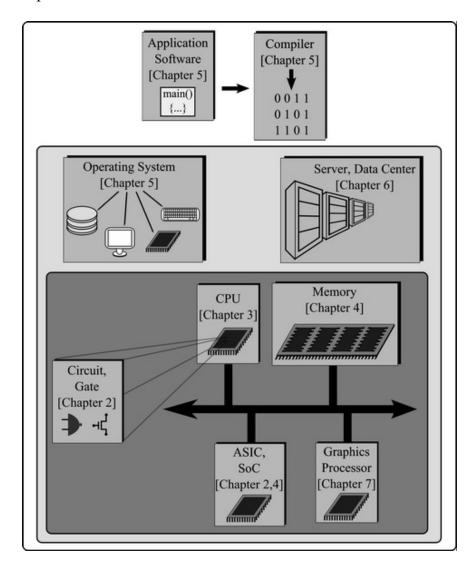

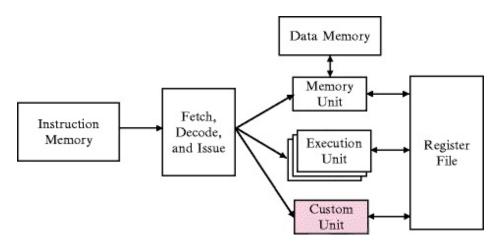

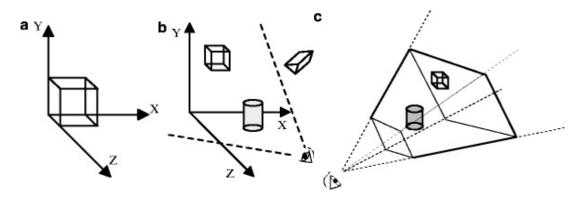

In this book we explore various mechanisms that have been proposed for reducing power dissipation in electronic and computer systems. Figure 1.3 gives a pictorial view of the contents of the book. The organization of the chapters is as follows.

*Fig. 1.3* Contents and organization of this book. Chapter 2 outlines the electronic foundations and basic synthesis/automation techniques. Chapter 3 and 4 focus on CPU and memory respectively. Chapter 5 discusses power-aware operating systems, compilers, and applications. Chapter 6 covers servers and data centers. Chapter 7 describes low power graphics processors

In Chapter 2 ("Basic Low Power Digital Design") we introduce the avenues for power dissipation in electronic systems based on CMOS processes, and the basic techniques employed for reducing dynamic and static power. The chapter covers the electronic foundations that form the basis of most of the higher level power optimizations discussed in subsequent chapters.

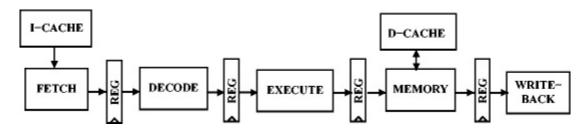

In Chapter 3 ("Power-efficient Processor Architecture") we delve into the details of modern processor architecture and point out some of the major strategies for reducing power in various components. While circuit level enhancements for power reduction naturally apply to processor design, our focus here is on the architecture-level modifications that reduce power.

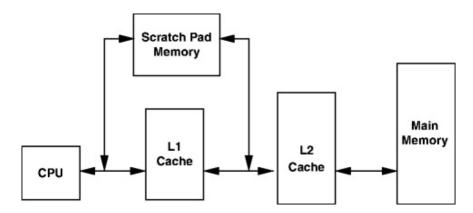

In Chapter 4 ("Power-efficient Memory and Cache") we discuss the basics of memory architecture and point out several techniques for reducing memory power in different contexts. In

Ericsson Ex. 2072, Page 20 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806 addition to power-aware cache memory design in the context of processors, we also discuss power reduction opportunities afforded by scratch pad memory and banked memory in the SoC context, as well as other components such as translation look-aside buffers and dynamic memory (DRAM).

In Chapter 5 ("Power Aware Operating Systems, Compilers, and Application Software") we move up another level in the compute stack – system software such as operating systems and compilers, and application software. Once the proper power optimization hooks are provided by the hardware, new opportunities open up with regard to their exploitation in software, starting from power-aware compilers.

In Chapter 6 ("Power Issues in Servers and Data Centers") we examine power awareness issues being introduced into high-end server-class computers and aggregations of servers constituting data centers. High level operating system features such as task allocation can now take power into account, exploiting mechanisms provided by the hardware for controlling performance and power states of individual computers.

In Chapter 7 ("Low Power Graphics Processors") we do a detailed study of system level power optimizations in graphics processors. The chapter gives a brief introduction to the graphics processing domain and proceeds to illustrate the application of several of the ideas introduced in previous chapters in the context of a complex processing system whose components bear some similarity to general purpose processors, but nevertheless, the overall architecture is application specific.

## References

- 1. Gonzalez, R., Horowitz, M.: Energy dissipation in general purpose microprocessors. IEEE Journal of Solid-State Circuits **31**(9), 1277–1284 (1996) [CrossRef]

- 2. Laudon, J.: Performance/watt: the new server focus. SIGARCH Computer Architecture News **33**(4), 5–13 (2005) [CrossRef]

- 3. Malik, A., Moyer, B., Cermak, D.: The M·CORE<sup>TM</sup> M340 unified cache architecture. In: Proceedings of the IEEE International Conference On Computer Design: VLSI in computers & processors, pp. 577–580 (2000)

- 4. Rivoire, S., Shah, M.A., Ranganathan, P., Kozyrakis, C.: Joulesort: a balanced energy-efficiency benchmark. In: SIGMOD '07: Proceedings of the 2007 ACM SIGMOD international conference on Management of data, pp. 365–376. ACM, New York, NY, USA (2007). DOI http://doi.acm.org/10.1145/1247480.1247522

| Preeti Ranjan Panda, B. V. N. Silpa, Aviral Shrivastava and Krishnaiah Gummidipudi, <i>Power-efficient System Design</i> , DOI: 10.1007/978-1-4419-6388-8_2, © Springer Science+Business Media, LLC 2010 |                                                     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          |                                                     |  |  |  |

|                                                                                                                                                                                                          | Ericsson Ex. 2072, Page 22<br>TCL et al. v Ericsson |  |  |  |

IPR2015-01674, -01676, -01761, -01806

# 2. Basic Low Power Digital Design

Preeti Ranjan Panda<sup>1™</sup>, Aviral Shrivastava<sup>2™</sup>, B. V. N. Silpa<sup>1™</sup> and Krishnaiah Gummidipudi<sup>1™</sup>

- (1) Department Computer Science and Engineering, Indian Institute of Technology, Hauz Khas, 110016 New Delhi, India

- (2) Department of Computer Science and Engineering, Arizona State University, 699 South Mill Avenue, 85281 Tempe, USA

- **Preeti Ranjan Panda (Corresponding author)**

Email: panda@cse.iitd.ac.in

**△** Aviral Shrivastava

Email: Aviral.Shrivastava@asu.edu

**■** B. V. N. Silpa

Email: silpa@cse.iitd.ac.in

Krishnaiah Gummidipudi

Email: krishna@cse.iitd.ac.in

#### **Abstract**

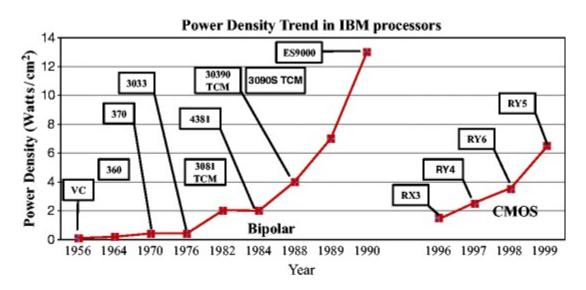

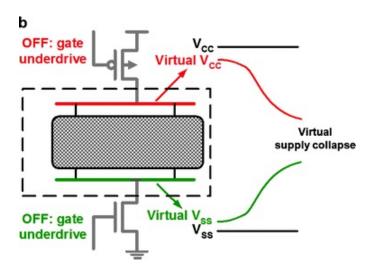

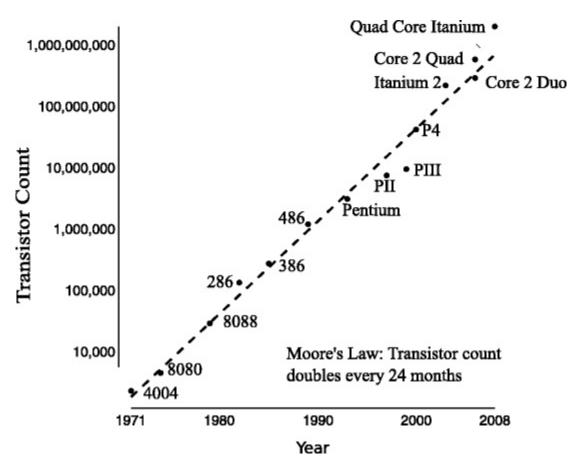

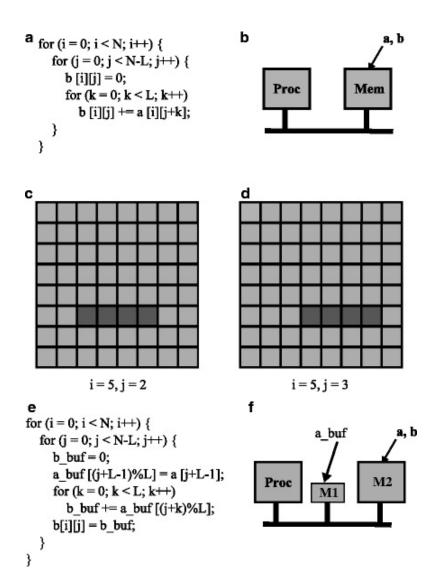

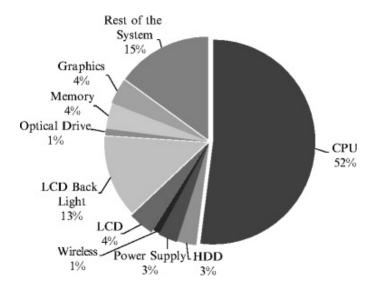

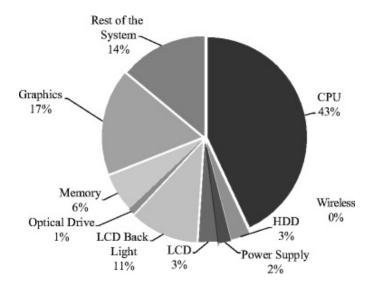

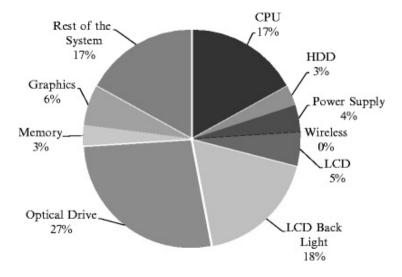

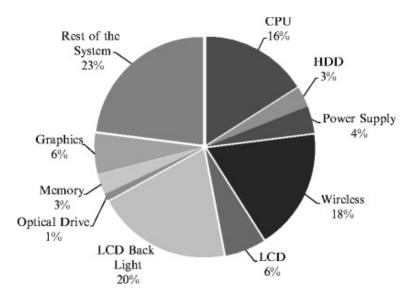

Moore's law [12], which states that the "number of transistors that can be placed inexpensively on an integrated circuit will double approximately every two years," has often been subject to the following criticism: while it boldly states the blessing of technology scaling, it fails to expose its bane. A direct consequence of Moore's law is that the "power density of the integrated circuit increases exponentially with every technology generation". History is witness to the fact that this was not a benign outcome. This implicit trend has arguably brought about some of the most important changes in electronic and computer designs. Since the 1970s, most popular electronics manufacturing technologies used bipolar and nMOS transistors. However, bipolar and nMOS transistors consume energy even in a stable combinatorial state, and consequently, by 1980s, the power density of bipolar designs was considered too high to be sustainable. IBM and Cray started developing liquid, and nitrogen cooling solutions for high-performance computing systems [5, 11, 16, 19, 21, 23–25]. The 1990s saw an inevitable switch to a slower, but lower-power CMOS technology (Fig. 2.1). CMOS transistors consume lower power largely because, to a first order of approximation, power is dissipated only when they switch states, and not when the state is steady. Now, in the late 2000s, we are witnessing a paradigm shift in computing: the shift to multi-core computing. The power density has once again increased so much that there is little option but to keep the hardware simple, and transfer complexity to higher layers of the system design abstraction, including software layers.

Moore's law [12], which states that the "number of transistors that can be placed inexpensively on an integrated circuit will double approximately every two years," has often been subject to the following criticism: while it boldly states the blessing of technology scaling, it fails to expose its bane. A direct consequence of Moore's law is that the "power density of the integrated circuit increases exponentially with every technology generation". History is witness to the fact that this was not a benign outcome. This implicit trend has arguably brought about some of the most important changes in electronic and computer designs. Since the 1970s, most popular electronics manufacturing technologies used bipolar and nMOS transistors. However, bipolar and nMOS transistors consume energy even in a stable combinatorial state, and consequently, by 1980s, the power density of bipolar designs was considered too high to be sustainable. IBM and Cray started developing liquid, and nitrogen cooling solutions for high-performance computing systems [5,11,16,19,21, 23–25]. The 1990s saw an inevitable switch to a slower, but lower-power CMOS technology (Fig. 2.1). CMOS transistors consume lower power largely because, to a first order of approximation, power is dissipated only when they switch states, and not when the state is steady. Now, in the late 2000s, we are witnessing a paradigm shift in computing: the shift to multi-core computing. The power density has once again increased so much that there is little option but to keep the hardware simple, and transfer complexity to higher layers of the system design abstraction, including software layers.

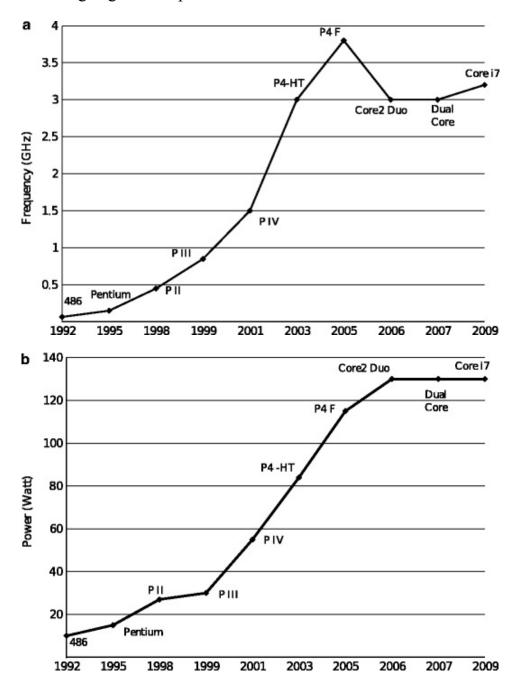

Fig. 2.1 Unsustainable increase in the power density caused a switch from fast, but high-power bipolar transistors to slow, but low-power CMOS transistor technology. We are at the doorsteps of the same problem again (Data courtesy IBM Corp)

This chapter explains the basics of power consumption and dissipation in the operation of CMOS transistors, and also discusses some of the fundamental mechanisms employed for power reduction.

# 2.1 CMOS Transistor Power Consumption

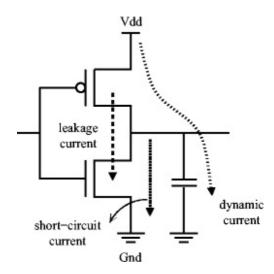

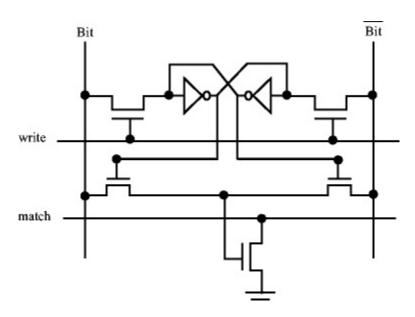

The power consumption of a CMOS transistor can be divided into three different components: dynamic, static (or leakage) and short circuit power consumption. Figure 2.2 illustrates the three components of power consumption. Switching power, which includes both dynamic power and short-circuit power, is consumed when signals through CMOS circuits change their logic state, resulting in the charging and discharging of load capacitors. Leakage power is primarily due to the sub-threshold currents and reverse biased diodes in a CMOS transistor. Thus,

$$P_{total} = P_{dynamic} + P_{short-circuit} + P_{leakage}. (2.1)$$

*Fig. 2.2* The dynamic, short circuit and leakage power components of transistor power consumption. Dynamic and short circuit power are also collectively known as switching power, and are consumed when transistors change their logic state, but leakage power is consumed merely because the circuit is "powered-on"

# 2.1.1 Switching Power

When signals change their logic state in a CMOS transistor, energy is drawn from the power supply to charge up the load capacitance from 0 to  $V_{\{dd\}}$ . For the inverter example in Fig. 2.2, the power drawn from the power supply is dissipated as heat in pMOS transistor during the charging process. Energy is needed whenever charge is moved against some potential. Thus, dE = d(QV). When the output of the invertor transitions from logical 0 to 1, the load capacitance is charged. The energy drawn from the power supply during the charging process is given by,

$$dE_P = d(VQ) = V_{dd}.dQ_L$$

since the power supply provides power at a constant voltage  $V_{\{dd\}}$ . Now, since  $Q_L = C_L$ .  $V_L$ , we have:

$$dQ_L = C_L.dV_L$$

Therefore,

$$dE_P = V_{dd}.C_L.dV_L$$

Integrating for full charging of the load capacitance,

Ericsson Ex. 2072, Page 25 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806

$$E_{P} = \int_{0}^{V_{dd}} V_{dd} . C_{L} . dV_{L}$$

$$= V_{dd} . C_{L} . \int_{0}^{V_{dd}} dV_{L}$$

$$= C_{L} . V_{dd}^{2}$$

(2.2)

Thus a total of  $C_L$ .  $V_{\{dd\}}^2$  energy is drawn from the power source. The energy  $E_L$  stored in the capacitor at the end of transition can be computed as follows:

$$dE_L = d(VQ) = V_L.dQ_L$$

where  $\boldsymbol{V}_L$  is the instantaneous voltage across the load capacitance, and  $\boldsymbol{Q}_L$  is the instantaneous charge of the load capacitance during the loading process. Therefore,

$$dE_L = V_L.C_LdV_L$$

Integrating for full charging of the load capacitance,

$$E_L = \int_0^{V_{dd}} C_L \cdot V_L \cdot dV_L$$

$$= \frac{(C_L \cdot V_{dd}^2)}{2}$$

(2.3)

Comparing Equations 2.2 and 2.3, we notice that only half of the energy drawn from the power supply is stored in the load capacitance; the rest is dissipated as heat. This  $\frac{1}{2}$   $C_L \cdot V_{dd}^2$  energy stored in the output capacitance is released during the discharging of the load capacitance, which occurs when the output of the invertor transitions from logical 1 to 0. The load capacitance of the CMOS logic gate consists of the output node capacitance of the logic gate, the effective capacitance of the interconnects, and the input node capacitance of the driven gate.

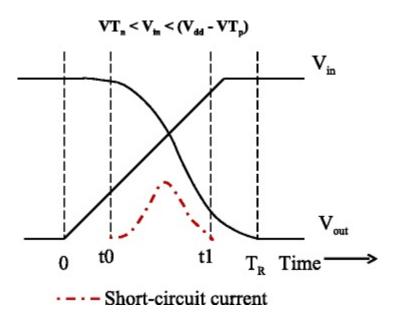

### 2.1.2 Short Circuit Power

Another component of power, short-circuit power (also known as crowbar power, or —em rush-through power) becomes important because of finite non-zero rise and fall times of transistors, which causes a direct current path between the supply and ground. This power component is usually not significant in logic design, but it appears in transistors that are used to drive large capacitances, such as bus wires and especially off-chip circuitry. As wires on chip became narrower, long wires became more resistive. CMOS gates at the end of those resistive wires see slow input transitions. Consider the inverter in Fig. 2.2. Figure 2.3 shows the variation of the short circuit current  $I_{SC}$  as the inverter is driven by a rising ramp input from time 0 to  $I_R$ . As the input voltage rises, at time  $I_R$ , we have  $I_R$  i.e., the input voltage become higher than the threshold voltage of the nMOS transistor. At this time a short-circuit current path is established. This short circuit current increases as the nMOS transistor turns "on". Thereafter, the short circuit current first increases and then decreases until, after  $I_R$ , we have  $I_R$  in the duration when  $I_R$  i.e., the pMOS transistor turns off, signalling the end of short-circuit current. Therefore, in the duration when  $I_R$  in the nMOS and pMOS devices will be simultaneously on. Short-circuit power is typically estimated as:

$$P_{short-circuit} = 1/12.k.\tau.F_{clk}.(V_{dd} - 2V_t)^3$$

(2.4)

where  $\tau$  is the rise time and fall time (assumed equal) and *k* is the gain factor of the transistor [22].

Ericsson Ex. 2072, Page 26 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806

Fig. 2.3 Short circuit power is consumed in a circuit when both the nMOS and pMOS transistors are "on"

# 2.1.3 Leakage Power

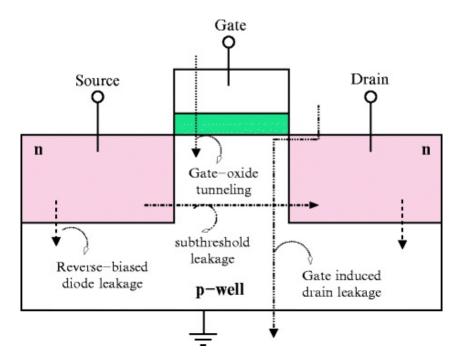

The third component of power dissipation in CMOS circuits, as shown in Equation2.1, is the static or leakage power. Even though a transistor is in a stable logic state, just because it is powered-on, it continues to leak small amounts of power at almost all junctions due to various effects. Next we discuss about the significant components of leakage power.

# 2.1.3.1 Reverse Biased Diode Leakage

The reverse biased diode leakage is due to the reverse bias current in the parasitic diodes that are formed between the diffusion region of the transistor and substrate. It results from minority carrier diffusion and drift near the edge of depletion regions, and also from the generation of electron hole pairs in the depletion regions of reverse-bias junctions. As shown in Fig. 2.4, when the input of inverter in Fig. 2.2 is high, a reverse potential difference of  $V_{\{dd\}}$  is established between the drain and the n-well, which causes diode leakage through the drain junction. In addition, the n-well region of the pMOS transistor is also reverse biased with respect to the p-type substrate. This also leads to reverse bias leakage at the n-well junction. The reverse bias leakage current is typically expressed as,

$$I_{rbdl} = A.Js.(e^{q.V_{bias}/kT} - 1)$$

$$(2.5)$$

where A is the area of the junction,  $J_s$  is the reverse saturation current density, and  $V_{\{bias\}}$  is the reverse bias voltage across the junction, and  $V_{\{th\}} = kT/q$  is the thermal voltage. Reverse biased diode leakage will further become important as we continue to heavily dope the n- and p-regions. As a result, zener and band-to-band tunneling [14] will also become contributing factors to the reverse bias current.

Fig. 2.4 Components of Leakage Power: (i) Subthreshold current flows between source and drain; (ii) Reverse-biased diode leakage flows across the parasitic diodes; (iii) Gate induced drain leakage flows between the drain and substrate

# 2.1.3.2 Gate Induced Drain Leakage

Gate-induced drain leakage (GIDL) is caused by high field effect in the drain junction of MOS transistors [2]. In an nMOS transistor, when the gate is biased to form accumulation layer in the silicon surface under the gate, the silicon surface has almost the same potential as the p-type substrate, and the surface acts like a p-region more heavily doped than the substrate. However, when the gate is at zero or negative voltage and the drain is at the supply voltage level, there can be a dramatic increase of effects like avalanche multiplication and band-to-band tunneling. Minority carriers underneath the gate are swept to the substrate, creating GIDL current. GIDL current or  $I_{\{GIDL\}}$  is typically estimated as:

$$I_{GIDL} = AE_s.e^{-\frac{B}{E_s}} \tag{2.6}$$

where  $E_s$  is the transverse electric field at the surface [3]. Thinner oxide  $T_{\{ox\}}$  and higher supply voltage  $V_{\{dd\}}$  increase GIDL. GIDL is also referred to as surface band-to-band tunneling leakage.

## 2.1.3.3 Gate Oxide Tunneling

Gate oxide tunneling current  $I_{\{ox\}}$ , flows from the gate through the oxide insulation to the substrate. In oxide layers thicker than 3-4 nm, this type of current results from the Fowler-Nordheim tunneling of electrons into the conduction band of the oxide layer under a high applied electric field across the oxide layer [17]. As oxides get thinner, this current could surpass many other smaller leakages, e.g., weak inversion and DIBL as a dominant leakage mechanism in the future.  $I_{ox}$  is typically estimated as:

$$I_{ox} = A.E_{ox}^2 \cdot e^{-\frac{B}{E_{ox}}} \tag{2.7}$$

where  $E_{ox}$  is the electric field across the oxide.

Ericsson Ex. 2072, Page 28 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806 In oxide layers less than 3-4 nm thick, there can also be direct tunneling through the silicon oxide layer. Mechanisms for direct tunneling include electron tunneling in the conduction band (ECB), electron tunneling in the valence band (EVB), and hole tunneling in the valence band (HVB).

# 2.1.3.4 Subthreshold Leakage

Subthreshold current flows from the source to drain even if the gate to source voltage is below the threshold voltage of the device. This happens due to several reasons. First is the weak inversion effect: when the gate voltage is below  $V_T$ , carriers move by diffusion along the surface similar to charge transport across the base of bipolar transistors. Weak inversion current becomes significant when the gate to source voltage is smaller than but very close to the threshold voltage of the device. The second prominent effect is the Drain-Induced Barrier Lowering (DIBL). DIBL is essentially the reduction of threshold voltage of the transistor at higher drain voltages. As the drain voltage is increased, the depletion region of the p-n junction between the drain and body increases in size and extends under the gate, so the drain assumes a greater portion of the burden of balancing depletion region charge, leaving a smaller burden for the gate. As a result, the charge present on the gate retains the charge balance by attracting more carriers into the channel, an effect equivalent to lowering the threshold voltage of the device. DIBL is enhanced at higher drain voltage and shorter effective channel length  $(L_{feff})[14]$ . The third effect is the direct punch-through of the electrons between drain and source. It occurs when when the drain and source depletion regions approach each other and electrically "touch" deep in the channel. In a sense, punch-through current is a subsurface version of DIBL.

As a combination of all these sub-currents,  $I_{sub}$  is typically modeled as:

$$I_{sub} = I_0 e^{\frac{V_G - V_{S} - V_{T0} - \gamma V_S + \eta V_{DS}}{nV_{th}}} \left( 1 - e^{\frac{-V_{DS}}{V_{th}}} \right), \tag{2.8}$$

where  $V_{\{th\}} = kT/q$  is the thermal voltage, n is the subthreshold swing coefficient constant,  $\gamma$  is the linearized body effect coefficient,  $\eta$  is the DIBL coefficient, and  $I_0$  is the technology dependent subthreshold leakage which can be represented as,

$$I_0 = \mu_0 C_{\alpha x} \frac{W}{L} V_{th}^2 e^{1.8}. \tag{2.9}$$

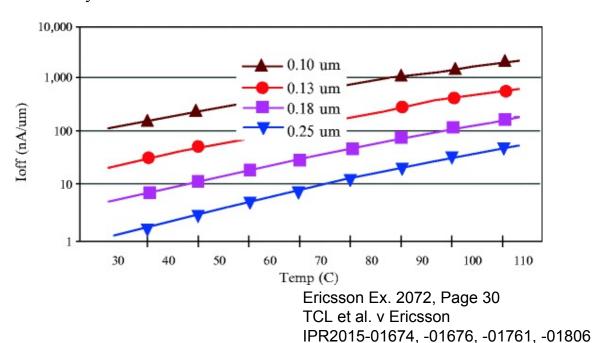

## 2.2 Trends in Power Consumption

At the macro-level, the most significant trend is the increasing contribution of leakage power in the total power dissipation of an electronic system designed in CMOS technology. For a long time, the switching component of the dynamic power was the major component of the total power dissipated by a circuit. However, in order to keep power dissipation and power delivery costs under control, the operational voltage  $V_{dd}$  was scaled down at the historical rate of 30% per technology generation. In conjunction, to improve transistor and circuit performance the threshold voltage  $V_t$  was also reduced at the same rate so that a sufficiently large gate overdrive ( $V_{dd} - V_t$ ) is maintained. However, as seen from Equation2.8, reduction in  $V_t$  causes transistor subthreshold leakage current ( $I_{sub}$ ) to increase exponentially. Furthermore, other components of leakage current, e.g., the gate leakage and reverse-biased junction Band To Band Tunneling (BTBT) become important as we scale fabrication technology to 45 nm and downwards. Other factors such as gate-induced drain leakage (GIDL) and drain-induced barrier lowering (DIBL) will also become increasingly significant.

In addition to the increasing dominance of leakage power, the subthreshold leakage and the gate-oxide tunneling increase extremely rapidly (exponentially) with technology scaling, and dwarf dynamic power. We are already at a point where  $V_{dd} - V_t$  is low, and leakage power is comparable to dynamic switching power, and in some cases, may actually even dominate the overall power dissipation. Large leakage comes with several associated problems such as lower noise immunity of dynamic logic circuits, instability of SRAM cells, and eventually, lower yield.

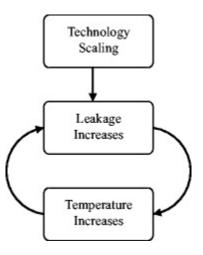

Another dimension of worry is added by the fact that unlike dynamic power, leakage power increases exponentially with temperature. In order to improve performance we have been continuously scaling the supply and threshold voltages. While this results in high frequency of operation, temperatures rise due to large active power consumption. The high temperature increases the sub-threshold leakage (which is a strong function of temperature), further increasing temperature. This circular situation is depicted in Fig. 2.5. If heat cannot be dissipated effectively, a positive feedback between leakage power and temperature can result in thermal runaway. Such a situation can have disastrous consequences, including permanent physical damage of the circuit. Most processors are now equipped with thermal sensors and hardware circuitry that will stop the processor if the temperature increases beyond safe limits.

Fig. 2.5 Leakage increases exponentially with temperature. This can create a positive feedback loop, where high power-density increases temperature, which in turn further increases the power-density, causing a thermal runaway

## 2.3 Techniques for Reducing Dynamic Power

The dynamic power of a circuit in which all the transistors switch exactly once per clock cycle will be  $\frac{1}{2}CV^2F$ , if C is the switched capacitance, V is the supply voltage, and F is the clock frequency.

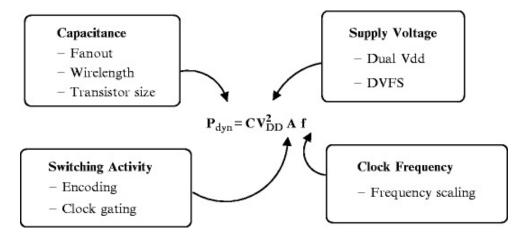

However, most of the transistors in a circuit rarely switch from most input changes. Hence, a constant called the activity factor  $(0 \le A \le 1)$  is used to model the average switching activity in the circuit. Using *A*, the dynamic power of a circuit composed of CMOS transistors can be estimated as:

$$P = ACV^2F (2.10)$$

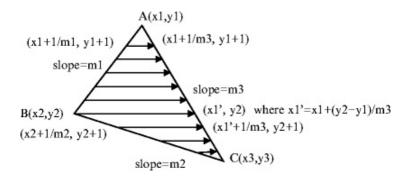

The importance of this equation lies in pointing us towards the fundamental mechanisms of reducing switching power. Figure 2.6 shows that one scheme is by reducing the activity factor A. The question here is: "how to achieve the same functionality by switching only a minimal number of transistors?" Techniques to do this span several design hierarchy levels, right from the synthesis level, where, for example, we can encode states so that the most frequent transitions occur with minimal bit switches, to the algorithmic level, where, for example, changing the sorting algorithm from insertion sort to quick sort, will asymptotically reduce the resulting switching activity. The second fundamental scheme is to reduce the load capacitance,  $C_L$ . This can be done by using small transistors with low capacitances in non-critical parts of the circuit. Reducing the frequency of operation F will cause a linear reduction in dynamic power, but reducing the supply voltage  $V_{DD}$  will cause a quadratic reduction. In the following sections we discuss some of the established and effective mechanisms for dynamic power reduction.

Fig. 2.6 Fundamental techniques to reduce dynamic power

## 2.3.1 Gate Sizing

The power dissipated by a gate is directly proportional to its capacitive  $load C_L$ , whose main components are: i) output capacitance of the gate itself (due to parasitics), ii) the wire capacitance, and iii) input capacitance of the gates in its fanout. The output and input capacitances of gates are proportional to the gate size. Reducing the gate size reduces its capacitance, but increases its delay. Therefore, in order to preserve the timing behavior of the circuit, not all gates can be made smaller; only the ones that do not belong to a critical path can be slowed down.

Any gate re-sizing method to reduce the power dissipated by a circuit will heavily depend on the accuracy of the timing analysis tool in calculating the true delay of the circuit paths, and also

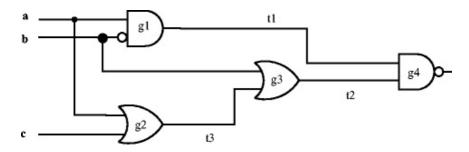

Ericsson Ex. 2072, Page 32 TCL et al. v Ericsson IPR2015-01674, -01676, -01761, -01806 discovering false paths. Delay calculation is relatively easier. A circuit is modeled as a directed acyclic graph. The vertices and edges of the graph represent the components and the connection between the components in the design respectively. The weight associated with a vertex (an edge) is the delay of the corresponding component (connection). The delay of a path is represented by the sum of the weights of all vertices and edges in the path. The arrival time at the output of a gate is computed by the length of the longest path from the primary inputs to this gate. For a given delay constraint on the primary outputs, the required time is the time at which the output of the gate is required to be stable. The time slack is defined as the difference of the required time and the arrival time of a gate. If the time slack is greater than zero, the gate can be down-sized. Consider the example circuit in Fig. 2.7. Assuming the delay of AND and OR gates to be 4 units, delay of NOT gate to be 1 unit, and wire delays to be 0, the top 3 timing-critical paths in the circuit are:

Fig. 2.7 False paths, which do not affect the timing, must be discovered and excluded during timing analysis before performing gate sizing

$$p_1: a \to g_2 \to g_3 \to g_4 \to d$$

$$p_2: b \to g_1 \to g_4 \to d$$

$$p_3: c \to g_2 \to g_3 \to g_4 \to d$$

The delay of the path $p_1$  is 10 units,  $p_2$  is 13 units, and  $p_3$  is 13 units. Therefore static timing analysis will conclude that the gates in both the paths  $p_2$  and  $p_3$  cannot be down-sized. However, by logic analysis, it is easy to figure out that both these seemingly timing critical paths are actually false paths, and can never affect the final stable value of output d. Logically, we have:

$$d = \overline{t1.t2} \\ = \overline{(a.\overline{b}).(b+t3)} \\ = \overline{(a.\overline{b}).(b+(a+c))} \\ = \overline{(a.\overline{b}).(a+b+c)} \\ = \overline{(a.\overline{b}).(a+b+c)} \\ = \overline{(a.\overline{b}.a) + (a.\overline{b}.b) + (a.\overline{b}.c)} \\ = \overline{(a.\overline{b}) + (a.\overline{b}.c)} \\ = \overline{(a.\overline{b}).(1+c)} \\ = \overline{(a.\overline{b})}$$

Thus, the actual critical path of output d is  $p_1$ , which has a delay of only 10 units. Therefore, from the perspective of output d, gates that constitute paths  $p_2$  and  $p_3$ , e.g.,  $p_2$  and  $p_3$  can be down-sized. The question now is: how to find out if a path is false? A false path is a path that is not sensitizable. A path  $p_1 = (i, g_1, g_2, g_3, g_4, g_5, g_6)$  from  $p_1 = (i, g_1, g_2, g_3, g_4, g_6)$  from  $p_2 = (i, g_2, g_3, g_4, g_6)$  from  $p_3 = (i, g_1, g_2, g_4, g_6)$  from  $p_4 = (i, g_4, g_5, g_6)$  from  $p_4 = (i, g_4, g_5, g_6)$  from  $p_4 = (i, g_5, g_6)$  from  $p_4 = (i, g_6, g_6)$  f

primary inputs, there are  $2^n$  possible input vectors, finding out whether a path is sensitizable by enumerating all the input values is clearly infeasible.

To work around this, typically a path-based approach is taken [6,10,26]. In order to allow a signal to go through pathp from primary inputi to the primary outputo, we need to set all the other signals feeding to gates alongp to be non-control values. The non-control value for an AND (OR) gate is 1 (0). For the path $p_1 = (b, g_1, g_4, d)$ , we must set  $t_2$  to be 1, and $t_3$  to be 1.  $t_4$  can be set to 1 by setting $t_4$  to 1, and $t_5$  to 0. Finally, $t_4$  can be set to 1 by setting $t_4$  to 1, and $t_5$  can be anything. In this case, there is an assignment of primary inputs that will allow this. On the other hand, if there is no consistent assignment of primary inputs resulting in non-control values of the other inputs of the gates along a path, then the path is non-sensitizable, or a false path. For example, sensitizing path $t_4$  requires  $t_4$  to be 1, $t_4$  to be 0, and $t_4$  to be 0. But this is not possible, because  $t_4$  cannot be 1 with $t_4$  set to 0. Therefore, path $t_4$  is a false path.

Taking path sensitizability into account, the calculation of slack time can now be formulated. For an input vector v, let  $AT(g_i, v)$  be the arrival time of gate  $g_i$  and  $RT(g_i, v)$  be the required time of gate  $g_i$  under a given delay constraint. The time slack of gate  $g_i$  with respect to the input vector v is given by:

$$slack(g_i, v) = RT(g_i, v) - AT(g_i, v)$$

For all input vectors, the slack of gateg i is defined as:

$$slack(g_i) = min_{\forall v} slack(g_i, v)$$

All gates with slack time greater than zero are candidates for down-sizing. However, to choose a specific one, we must consider several factors, such as the power reduction achievable, and the slack consumption by resizing it. To achieve maximum power reduction, the gate with least delay increment should have higher priority, but to save the total consumed time slack of multiple paths by down-sizing a gate, the gate belonging to a smaller number of paths is preferable for resizing. A combined metric could be:

$$gain(g_i) = \frac{\delta power(g_i)}{\delta delay(g_i) \times |P_{a_i}|}$$

where where  $\delta power(g_i)$  is the reduction in power,  $\delta delay(g_i)$  is the increase in delay by down-sizing gateg<sub>i</sub>, and  $|P_{g_i}|$  is the number of noncritical paths passing through gateg<sub>i</sub>. The gate with the maximum gain value is selected for resizing [10].

After a gate on a non-critical path is down-sized, a critical path may become non-critical since the load capacitances of some gates on the critical path may decrease. Consequently, the gates on the original critical path may be down-sized. Thus, simultaneous down-sizing and up-sizing multiple gates may reduce power consumption. The satisfaction of delay constraint can be retained if up-sizing gates can compensate the loss in delay caused by downsizing gates on the critical path.

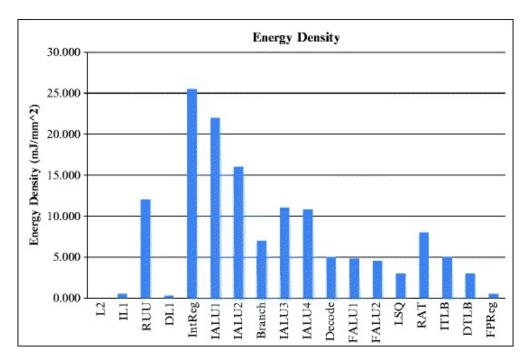

# 2.3.2 Control Synthesis

Most control circuits are conceived as Finite State Machines (FSM), formally defined as graphs where the nodes represent states, and directed edges, labeled with inputs and outputs, describe the transition relation between states. The state machine is eventually implemented using a state register and combinational logic, that takes in the current state, the current inputs and computes the outputs and

the new state, which is then written into the state register at the end of the cycle. The binary values of the inputs and outputs of the FSM are usually determined by external requirements, while the state encoding is left to the designer. Depending on the complexity of the circuit, a large fraction of the power is consumed due to the switching of the state register; this power is very dependent on the selected state encoding. The objective of low power approaches is therefore to choose a state encoding that minimizes the switching power of the state register.

Given a state encoding, the power consumption can be modeled as:

$$P = \frac{1}{2}V_{dd}^2 f \times C_{sr} \times E_{sr}$$

where f is the clock frequency of the state machine,  $C_{sr}$  is the effective capacitance of the state register, and  $E_{sr}$  is the expected state register switching activity. If S is the set of all states, we can estimate  $E_{sr}$  as:

$$E_{sr} = \sum\nolimits_{i,j \in S} p_{ij} \times h_{ij}$$

where  $p_{ij}$  is the probability of a transition between states i and j, and  $k_{ij}$  is the Hamming Distance between the codes of states i and j. The best way to estimate  $p_{ij}$  is to apply a sufficiently long series of input patterns until the state occurrence and transition probabilities converge towards discrete values [13]. Otherwise, equal probabilities of all input patterns can be assumed, and  $p_{ij}$  can be determined stochastically by solving Chapman Kolmogorov equations [4].

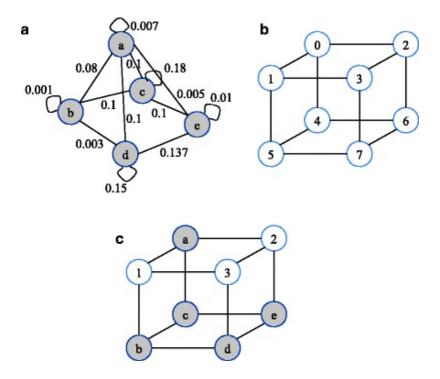

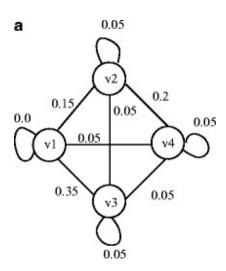

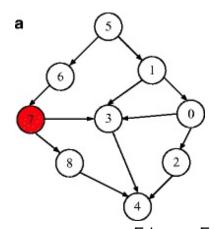

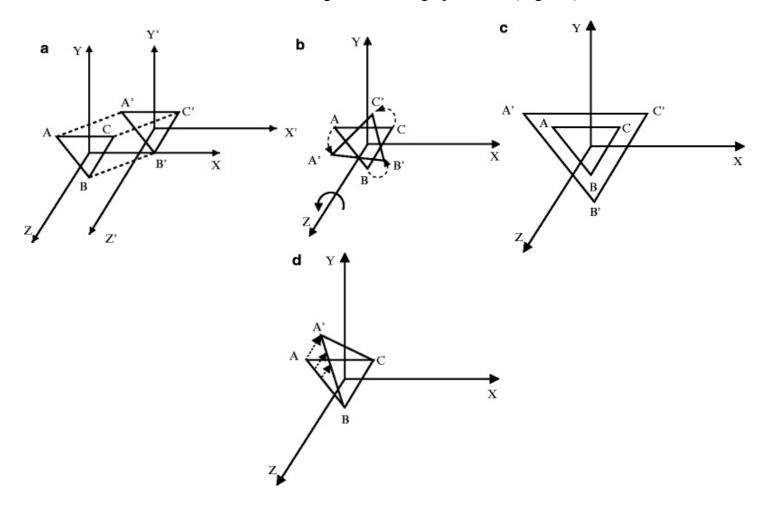

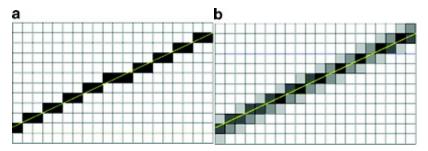

Once we have the state transition probabilities, the state encoding problem can be formulated as an embedding of the state transition graph into a Boolean hypercube Fig. 2.8. A Boolean hypercube of dimension n is a graph with  $2^n$  nodes, where every node is labeled with a unique binary value from n to n 1. Every node n is connected to n edges labeled n 1,... n leading to all nodes whose encodings have a Hamming Distance of 1 from n 2. Consequently, the hamming distance between any two nodes in the hypercube is equal to the length of the shortest path between the nodes. An embedding of a graph n into a host graph n is an injective mapping of the nodes of n to the nodes of n, so that every edge in n corresponds to the shortest path between the mappings of its terminal nodes in n 1. The dilation of an edge of n is defined as the length of the corresponding path in n 1.

Fig. 2.8 (a) State transition graph (STG) contains nodes as states, and switching probabilities as edge weights. The problem of state encoding for low-power is of embedding the STG onto a k-dimensional hypercube. (b) A n-dimensional hypercube has 2 <sup>n</sup> nodes and edges connect nodes that have hamming distance of 1. (c) The problem is then to find an injective mapping of nodes from STG to nodes of the hybercube so that the sum of product of distances between nodes and switching frequency is minimized

The dimensionality of a hypercube refers to the number of bits in the state register. To optimize the switching power, a graph embedding with small dilation in a small hypercube must be found. We can always find a low dilation embedding in a hypercube of high dimensionality, but this increases the area and also the power cost of the implementation.

Given the dimensionality of the hypercube, the best solution would be an embedding with dilation 1 for all edges. While such an embedding is possible for cubical graphs, for many graphs it is not possible. The problem of finding an embedding with minimal dilation is NP-complete[7]. The problem of finding the minimum dimension in which a given graph can be embedded, is also NP-complete.

One of the effective solutions for this problem was suggested by Noth et al. [15], in which they create a cubical subgraph of G, which contains the edges with the highest weights, and find a dilation-1 embedding of this subgraph. Since all trees are cubical, a good choice for a subgraph is the maximum spanning tree (MST), which can be easily extracted using greedy algorithms, e.g., Prim's algorithm [9]. Since the dimension of the embedding is strongly connected to the degree of nodes in the tree, tighter embeddings can be found by limiting the degree of any node in the resulting spanning tree. Once the MST is obtained, they embed the MST onto the hypercube using a divide and conquer approach. For this, they first find the center of the tree  $V_c$ ,  $E_c$  with respect to the longest paths. If  $P = (v_0, \dots, v_k)$  is the longest path of the MST, then  $V_C^p = \{v_{\lfloor k/2 \rfloor}, v_{\lceil k/2 \rceil}\}$  is the set of nodes in the center of P, where P is the length of longest path P. The center of the tree can then be defined as the set of center nodes of each path. Thus, P is a length of longest path P is center of the tree can then be shown that every tree has a unique center, essentially proving that there will be either one two nodes in the center of the tree. If there is one node, we can pick an edge of P along any of the longest paths; if there are two

nodes in  $V_c$ , then the two nodes must be connected by an edge, and that edge is our  $E_c$ . Removing the edge  $E_c$  breaks up the longest path at or near its center, leaving two subtrees of unknown size and structure. Both subtrees are then embedded recursively. Clearly it would be best to balance the subtree embeddings with respect to dimension in order to minimize the dimension of the overall embedding. One approach is to select an edge  $(v, w) \in E_c$ , whose removal from E leads to the most evenly sized subtrees with respect to the number of edges of the subtrees.

The low power state encoding problem is similar to the classical state encoding problem that targets low area and high performance, but sufficiently different that the resulting encodings will have different properties. Relatively low state register power consumption can be expected.

# 2.3.3 Clock Gating

Clock signals are omnipresent in synchronous circuits. The clock signal is used in a majority of the circuit blocks, and since it switches every cycle, it has an activity factor of 1. Consequently, the clock network ends up consuming a huge fraction of the on-chip dynamic power. Clock gating has been heavily used in reducing the power consumption of the clock network by limiting its activity factor. Fundamentally, clock gating reduces the dynamic power dissipation by disconnecting the clock from an unused circuit block.

Traditionally, the system clock is connected to the clock pin on every flip-flop in the design. This results in three major components of power consumption:

- 1. power consumed by combinatorial logic whose values are changing on each clock edge;

- 2. power consumed by flip-flops this has a non-zero value even if the inputs to the flip-flops are steady, and the internal state of the flip-flops is constant; and

- 3. power consumed by the clock buffer tree in the design. Clock gating has the potential of reducing both the power consumed by flip-flops and the power consumed by the clock distribution network.

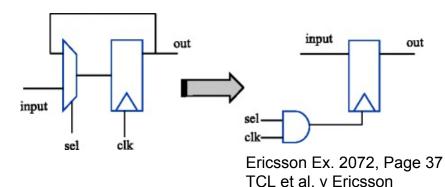

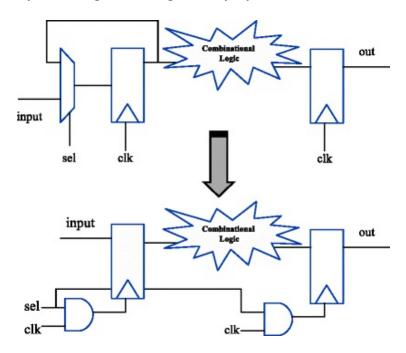

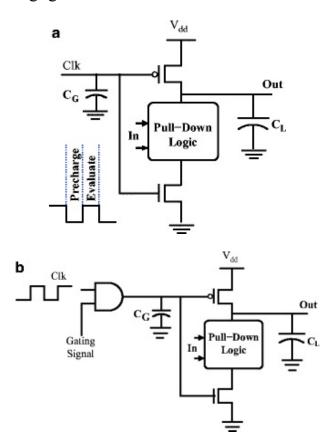

Clock gating works by identifying groups of flip-flops sharing a common*enable* signal (which indicates that a new value should be clocked into the flip-flops). This enable signal is ANDed with the clock to generate the *gated clock*, which is fed to the clock ports of all of the flip-flops that had the common enable signal. In Fig. 2.9, the *sel* signal encodes whether the latch retains its earlier value, or takes a new input. This *sel* signal is ANDed with the *clk* signal to generate the gated clock for the latch. This transformation preserves the functional correctness of the circuit, and therefore does not increase the burden of verification. This simple transformation can reduce the dynamic power of a synchronous circuit by 5–10%.

IPR2015-01674, -01676, -01761, -01806

Fig. 2.9 In its simplest form, clock gating can be implemented by finding out the signal that determines whether the latch will have a new data at the end of the cycle. If not, the clock is disabled using the signal

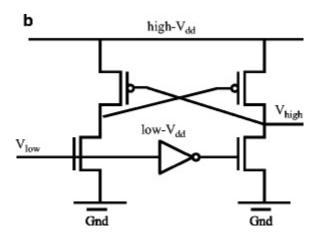

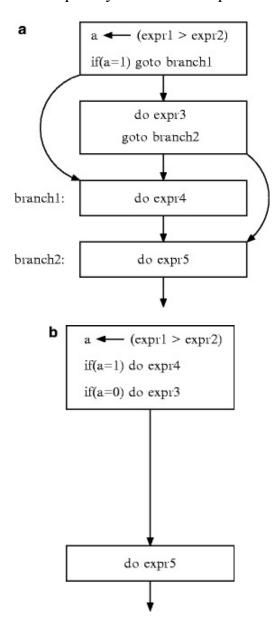

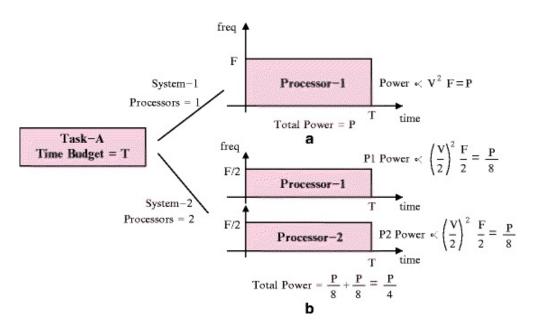

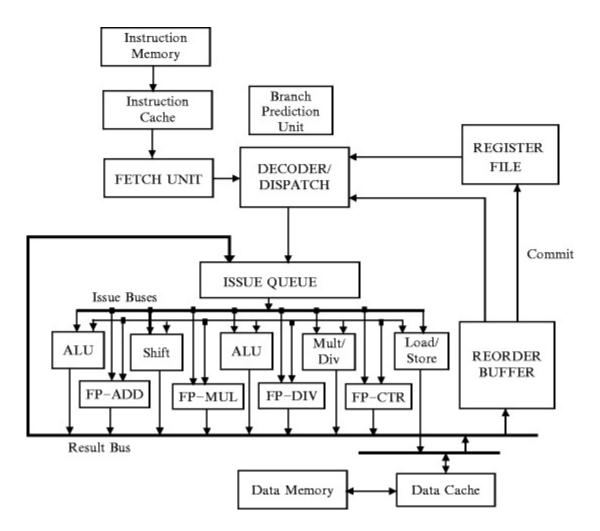

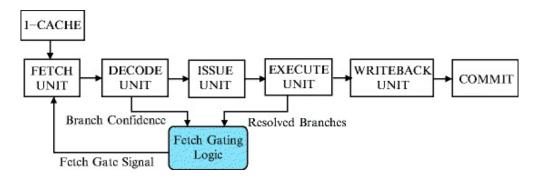

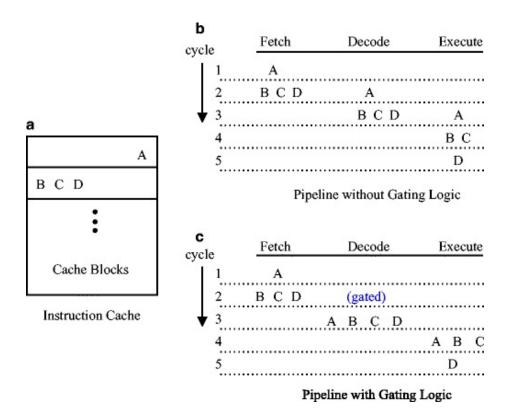

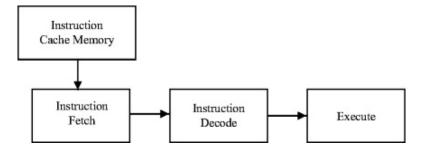

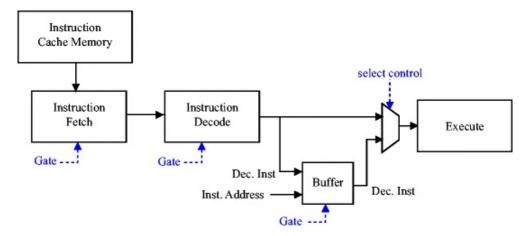

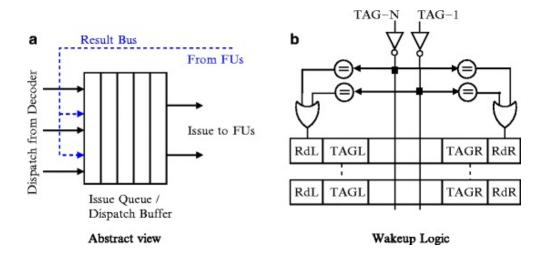

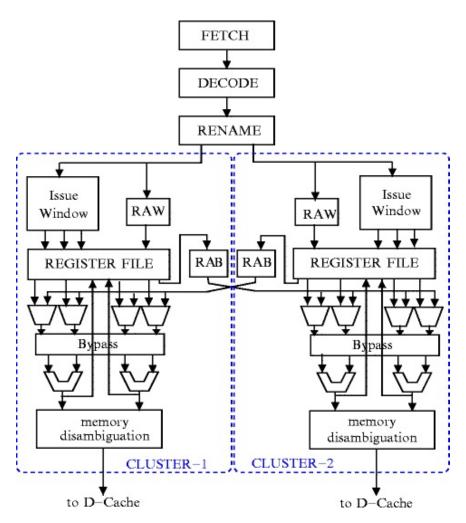

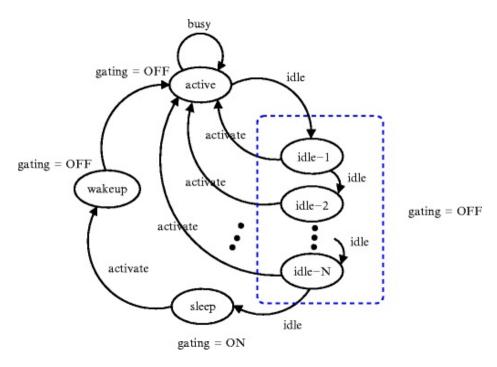

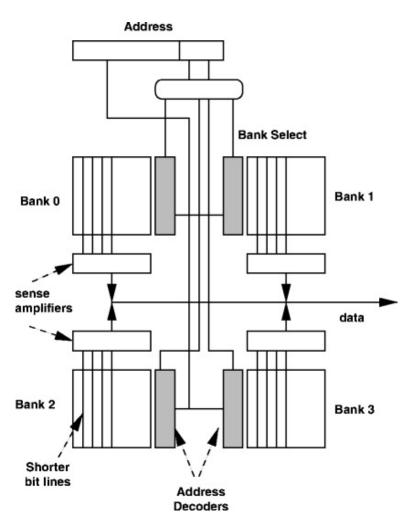

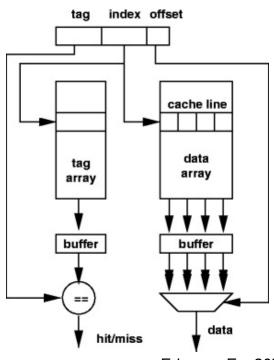

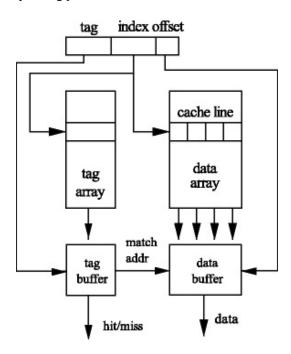

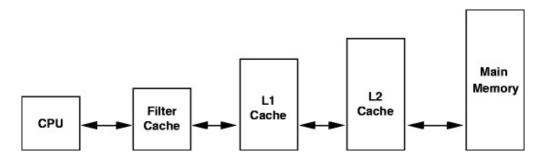

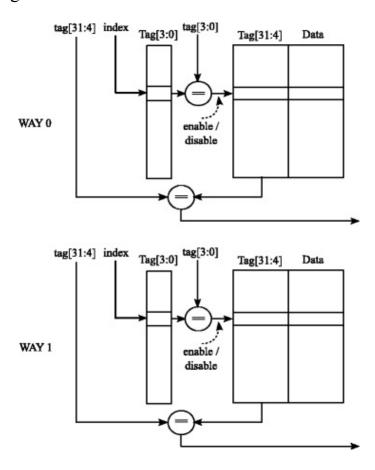

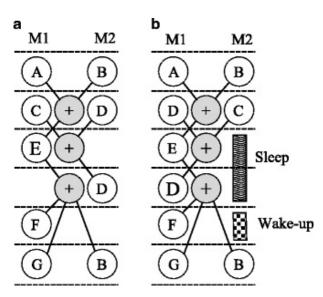

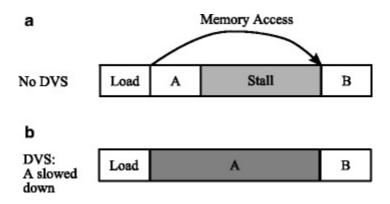

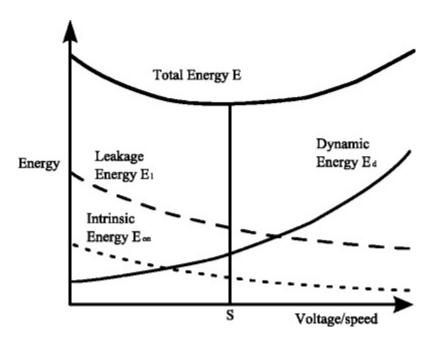

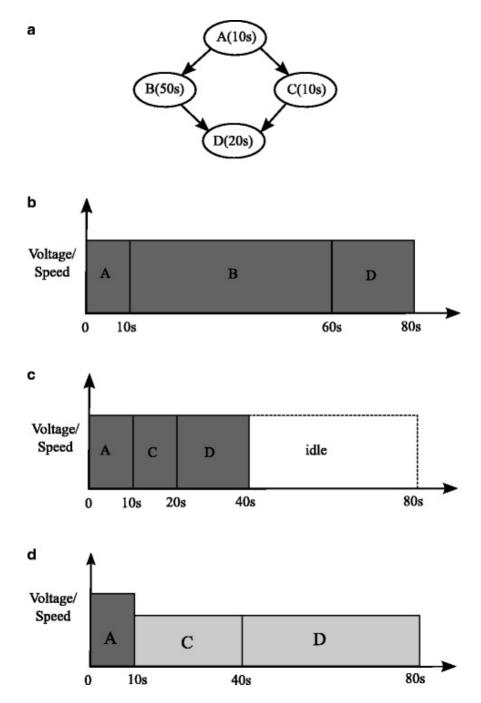

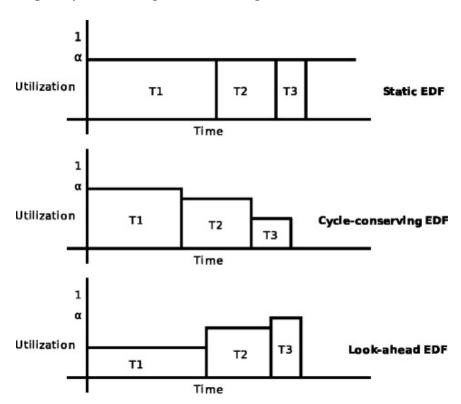

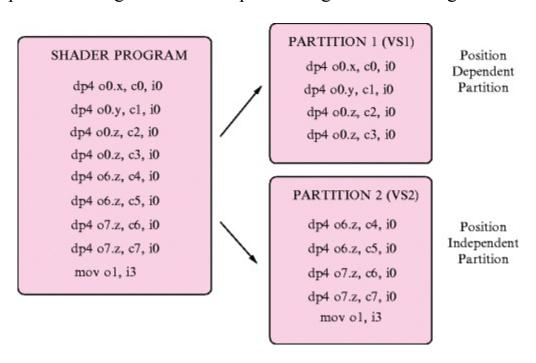

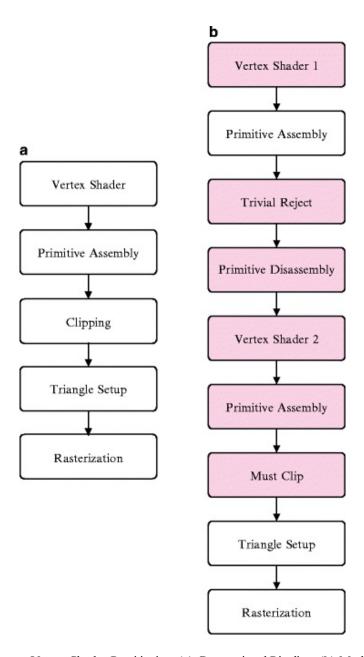

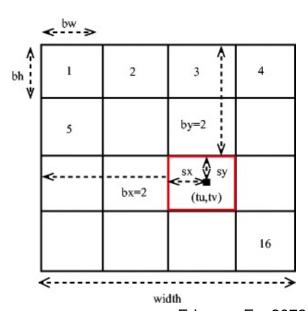

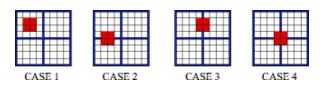

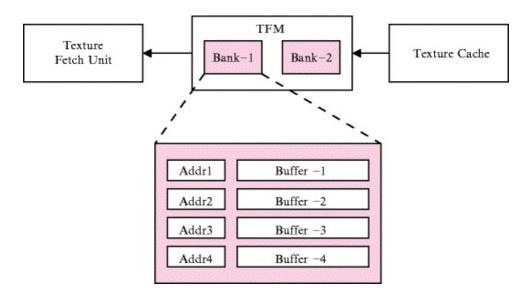

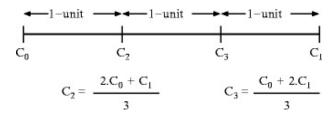

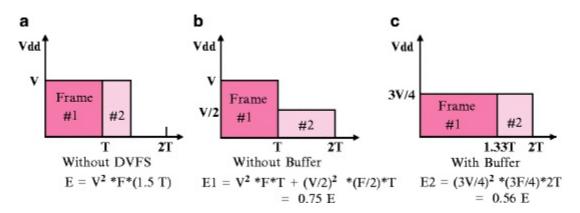

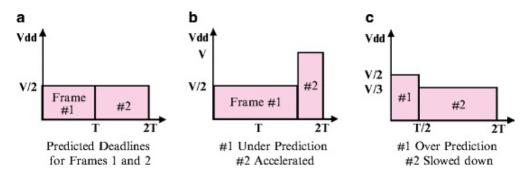

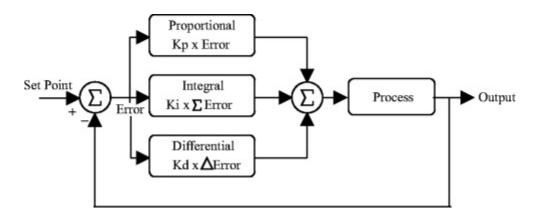

There are several considerations in implementing clock gating. First, the enable signal should remain stable when clock is high and can only switch when clock is in low phase. Second, in order to guarantee correct functioning of the logic implementation after the gated-clock, it should be turned on in time and glitches on the gated clock should be avoided. Third, the AND gate may result in additional clock skew. For high-performance design with short-clock cycle time, the clock skew could be significant and needs to be taken into careful consideration.