| Paper No |  |

|----------|--|

|----------|--|

## UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

## BEFORE THE PATENT TRIAL AND APPEAL BOARD

Sony Corporation

Petitioner

v.

Collabo Innovations, Inc.

(record) Patent Owner

Patent No. 5,952,714

## DECLARATION OF R. MICHAEL GUIDASH

# TABLE OF CONTENTS

| Table | of Contents                                                                                                           | i  |

|-------|-----------------------------------------------------------------------------------------------------------------------|----|

| I.    | Engagement and compensation                                                                                           | 1  |

| II.   | Summary of opinions                                                                                                   | 1  |

| III.  | Qualifications                                                                                                        | 3  |

| IV.   | My understanding of the relevant law                                                                                  | 5  |

| A.    | Claim construction                                                                                                    | 5  |

| B.    | Anticipation                                                                                                          | 6  |

| C.    | Obviousness                                                                                                           | 6  |

| V.    | Technical introduction                                                                                                | 10 |

| A.    | Background                                                                                                            | 10 |

| VI.   | Level of ordinary skill in the art                                                                                    | 19 |

| VII.  | Predictability of the art                                                                                             | 22 |

| VIII. | Relevant time frame for determining obviousness                                                                       | 22 |

| IX.   | Overview of the claims                                                                                                | 23 |

| X.    | Overview of the primary prior art references                                                                          | 24 |

| A.    | Overview of Yoshino                                                                                                   | 24 |

| B.    | Overview of Wakabayashi                                                                                               | 27 |

| XI.   | Construction of the claims                                                                                            | 31 |

| A.    | Claims 2—"solid-state image apparatus"                                                                                | 31 |

| B.    | Claims 2-7, 9-11, 13-16—"electrode pad(s)"                                                                            | 33 |

| C.    | Claims 3, 9, 13-16—"bump"                                                                                             | 35 |

| D.    | Claim 8—"covers an entire upper surface of said substrate except an usurface of the solid-state image sensing device" |    |

| E.    | Claim 7—"plastic package"                                                                                             | 38 |

| F.    | Claim 15—"substrate"/"semiconductor substrate"                                                                        | 38 |

| XII.  | Claim 1 is anticipated by Yoshino.                                                                                    | 41 |

| A.    | Summary of opinion                                                                                                    | 41 |

| B.    | Yoshino is prior art                                                                                                  | 41 |

| C.    | Summary of Yoshino                                                                                             | 41     |

|-------|----------------------------------------------------------------------------------------------------------------|--------|

| D.    | Element-by-element analysis of claim 1 over Yoshino                                                            | 42     |

| 1.    | Claim 1                                                                                                        | 42     |

| XIII. | Claim 6 is obvious over Yoshino in view of Izumi                                                               | 49     |

| A.    | Summary of opinion                                                                                             | 49     |

| B.    | Izumi is prior art                                                                                             | 49     |

| C.    | Summary of Izumi                                                                                               | 49     |

| D.    | Element-by-element analysis of claim 6 over Yoshino in view of Iz                                              | zumi49 |

| 1.    | Claim 6                                                                                                        | 49     |

| XIV.  | Claim 7 is obvious over Yoshino in view of Nagano, in further view Wakabayashi.                                |        |

| A.    | Summary of opinion                                                                                             | 58     |

| B.    | Nagano is prior art                                                                                            | 58     |

| C.    | Summary of Nagano                                                                                              | 58     |

| D.    | Wakabayashi is prior art                                                                                       | 59     |

| E.    | Summary of Wakabayashi                                                                                         | 59     |

| F.    | Element-by-element analysis of claim 7 over Yoshino in view of N in further view of Wakabayashi                | _      |

| 1.    | Claim 7                                                                                                        | 59     |

| XV.   | Claim 8 is obvious over Yoshino in view Izumi or Nagano, in furth of Hirosawa and Nita.                        |        |

| A.    | Summary of opinion                                                                                             | 65     |

| B.    | Hirosawa is prior art                                                                                          | 65     |

| C.    | Summary of Hirosawa                                                                                            | 65     |

| D.    | Nita is prior art                                                                                              | 66     |

| E.    | Summary of Nita                                                                                                | 66     |

| F.    | Element-by-element analysis of claim 8 over Yoshino in view of Iz Nagano, in further view of Hirosawa and Nita |        |

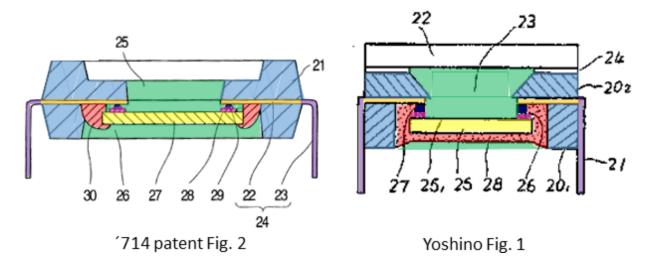

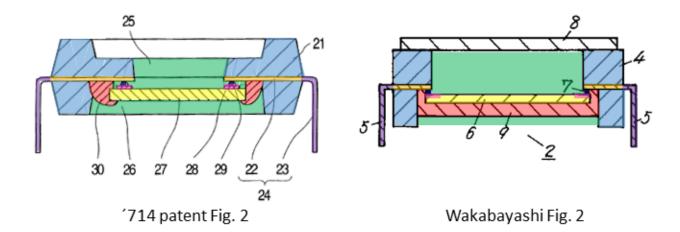

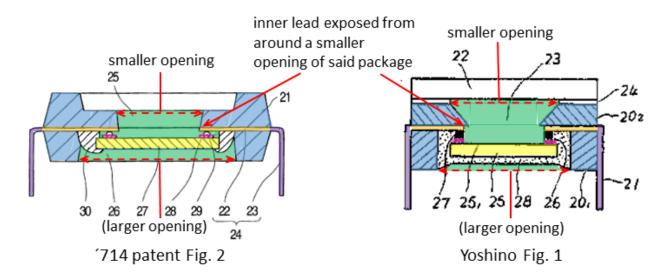

| 1.    | Claim 8                                                                                                        | 66     |

| XVI.  | Claim 9 is obvious over Yoshino in view of Izumi or Nagano                                                     | 73     |

| A.     | Summary of opinion                                                                                            | 73 |

|--------|---------------------------------------------------------------------------------------------------------------|----|

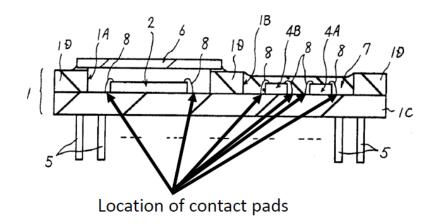

| B.     | Element-by-element analysis of claim 9 over Yoshino in view of Izur<br>Nagano                                 |    |

| 1.     | Claim 9                                                                                                       | 74 |

| XVII.  | Claim 10 is obvious over Yoshino in view of Izumi or Nagano, in furview of Wakabayashi                        |    |

| A.     | Summary of opinion                                                                                            | 76 |

| B.     | Element-by-element analysis of claim 10 over Yoshino in view of Iza<br>Nagano, in further view of Wakabayashi |    |

| 1.     | Claim 10                                                                                                      | 77 |

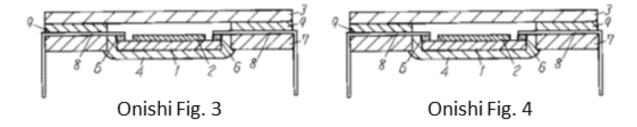

| XVIII. | Claim 11 is obvious over Yoshino in view of Izumi or Nagano, in fur view of Onishi.                           |    |

| A.     | Summary of opinion                                                                                            | 78 |

| B.     | Onishi is prior art                                                                                           | 79 |

| C.     | Summary of Onishi                                                                                             | 79 |

| D.     | Element-by-element analysis of claim 11 over Yoshino in view of Iza<br>Nagano, in further view of Onishi.     |    |

| 1.     | Claim 11                                                                                                      | 79 |

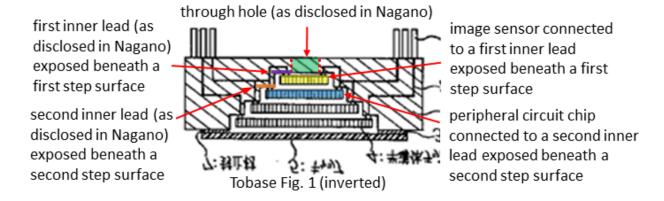

| XIX.   | Claim 12 is obvious over Yoshino in view of Tobase                                                            | 82 |

| A.     | Summary of opinion                                                                                            | 82 |

| B.     | Tobase is prior art                                                                                           | 82 |

| C.     | Summary of Tobase                                                                                             | 83 |

| D.     | Element-by-element analysis of claim 12 over Yoshino in view of To                                            |    |

| 1.     | Claim 12                                                                                                      | 83 |

| XX.    | Claim 13 is obvious over Yoshino in view of Hikosaka                                                          | 88 |

| A.     | Summary of opinion                                                                                            | 88 |

| B.     | Hikosaka is prior art                                                                                         | 88 |

| C.     | Summary of Hikosaka                                                                                           | 88 |

| D.     | Element-by-element analysis of claim 13 over Yoshino in view of Hikosaka                                      | 89 |

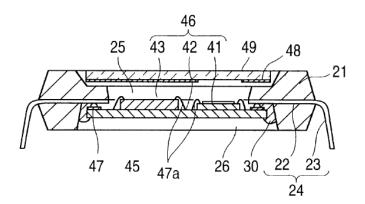

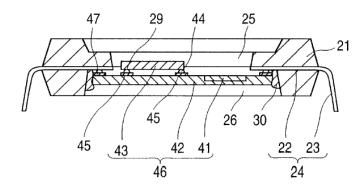

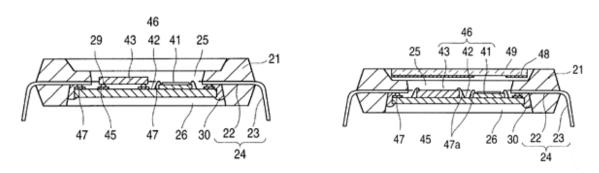

| 1.     | Claim 13                                                                                           | 89   |

|--------|----------------------------------------------------------------------------------------------------|------|

| XXI.   | Claim 15 is obvious over Yoshino in view of Izumi and Nagano, in fur view of Hikosaka              |      |

| A.     | Summary of opinion                                                                                 | 98   |

| B.     | Element-by-element analysis of claim 15 over Yoshino in view of Izun in further view of Hikosaka   |      |

| 1.     | Claim 15                                                                                           | 98   |

| XXII.  | Claim 16 is obvious over Yoshino in view of Tobase, in further view of Hikosaka.                   |      |

| A.     | Summary of opinion                                                                                 | .102 |

| B.     | Element-by-element analysis of claim 16 over Yoshino in view of Toba in further view of Hikosaka   |      |

| 1.     | Claim 16                                                                                           | 103  |

| XXIII. | Claim 1 is obvious over Wakabayashi.                                                               | .106 |

| A.     | Summary of opinion                                                                                 | .106 |

| B.     | Element-by-element analysis of claim 1 over Wakabayashi                                            | 106  |

| 1.     | Claim 1                                                                                            | 106  |

| XXIV.  | Claims 2-4 are obvious over Wakabayashi in view of Fujii                                           | 113  |

| A.     | Summary of opinion                                                                                 | .113 |

| B.     | Fujii is prior art.                                                                                | .114 |

| C.     | Summary of Fujii                                                                                   | .114 |

| D.     | Element-by-element analysis of claims 2-4 over Wakabayashi in view Fujii.                          |      |

| 1.     | Claim 2                                                                                            | 114  |

| 2.     | Claim 3                                                                                            | 120  |

| 3.     | Claim 4                                                                                            | 121  |

| XXV.   | Claim 5 is obvious over Wakabayashi in view of Fujii, in further in vie Onishi.                    |      |

| A.     | Summary of opinion                                                                                 | .122 |

| B.     | Element-by-element analysis of claim 5 over Wakabayashi in view of Fujii in further view of Onishi | 122  |

| 1.    | Claim 5                                                                       | 122  |

|-------|-------------------------------------------------------------------------------|------|

| XXVI. | Claim 13 is obvious over Wakabayashi in view of Hikosaka                      | 123  |

| A.    | Summary of opinion                                                            | .123 |

| B.    | Element-by-element analysis of claim 13 over Wakabayashi in view of Hikosaka. |      |

| 1.    | Claim 13                                                                      | 123  |

| XXVII | . Oath                                                                        | .127 |

1. I, R. Michael Guidash hereby declare as follows:

### I. Engagement and compensation

2. I have been retained by Sony Corporation to serve as an expert in the *inter partes* review proceeding described above. I have been asked to provide my technical review, analysis, insights, and opinions regarding the references that form the basis for the grounds of unpatentability set forth in the Petition for *inter partes* review of US 5,952,714 (the '714 Patent). For this service, my billing rate is an hourly consulting fee of \$400/hour, and I am reimbursed for actual expenses. My compensation in no way depends on the outcome of this matter.

### II. Summary of opinions

- 3. It is my opinion that claim 1 is anticipated by Japanese Pat. App. Pub. No. S61-131690 ("Yoshino").

- 4. It is further my opinion that claim 6 is obvious over Yoshino in view of Japanese Pat. App. Pub. No. S63-221667 ("Izumi").

- 5. It is further my opinion that claim 7 is obvious over Yoshino in view of Japanese Pat. App. Pub. No. H06-029507 ("Nagano"), in further view of Japanese Pat. App. Pub. No. H07-045803 ("Wakabayashi").

- 6. It is further my opinion that claim 8 is obvious over Yoshino in view of Izumi or Nagano, in further view of Japanese Pat. App. Pub. No. S60-74880 ("Hirosawa") and Japanese Pat. App. Pub. No. H07-78951 ("Nita").

- 7. It is further my opinion that claim 9 is obvious over Yoshino in view of Izumi or Nagano.

- 8. It is further my opinion that claim 10 is obvious over Yoshino in view of Izumi or Nagano, in further view of Wakabayashi.

- 9. It is further my opinion that claim 11 is obvious over Yoshino in view of Izumi or Nagano, in further view of Japanese Pat. App. Pub. No. H05-006989 ("Onishi").

- 10. It is further my opinion that claim 12 is obvious over Yoshino in view of Japanese Pat. App. Pub. No. H05-275611 ("Tobase").

- 11. It is further my opinion that claim 13 is obvious over Yoshino in view of Japanese Pat. App. Pub. No. S59-225560 ("Hikosaka").

- 12. It is further my opinion that claim 15 is obvious over Yoshino in view of Izumi and Nagano, in further view of Hikosaka.

- 13. It is further my opinion that claim 16 is obvious over Yoshino in view of Tobase, in further view of Hikosaka.

- 14. It is further my opinion that claim 1 is obvious over Wakabayashi.

- 15. It is further my opinion that claims 2-4 are obvious over Wakabayashi, in view of Japanese Pat. App. Pub. No. H06-85221 ("Fujii").

- 16. It is further my opinion that claim 5 is obvious over Wakabayashi in view of Fujii, in further view of Onishi.

17. It is further my opinion that claim 13 is obvious over Wakabayashi in view of Hikosaka.

### III. Qualifications

- 18. I started my career with Eastman Kodak as a product engineer for Photometer ASIC's for Kodak film cameras after graduating with a Bachelor of Science in Electrical Engineering from the University of Delaware in 1981. In 1986, I transferred to the Kodak Research Laboratories and CCD wafer fabrication facility. During my time with the Kodak Research Laboratories and CCD wafer fabrication facility, I developed 2um and 1um CMOS processes, and a 30V 4um BiCMOS process. These processes were used for gate arrays for many Kodak products and output driver ASICs for all of Kodak's copiers. During this time, I was also awarded entrance into the Special Opportunity Graduate Program that allowed me to obtain a Master's of Science in Electrical Engineering from the Rochester Institute of Technology.

- 19. In 1989, I transferred to the Smart Sensor Group which developed BiCMOS-CCD processes to provide fully integrated CCD systems on a chip. I also served as product engineer and yield enhancement engineer for Kodak's high volume CCD's. During this time, I led product delivery and technology development of all ASIC and smart sensor products. I developed a number of products during this time to include an interline CCD integrated with 2um CMOS

on the same chip, the world's 1st pinned photodiode Active Pixel CMOS Sensor, and linear CCD image sensor with on-chip timing and control. I also led & directed the CCD dark current and point defect reduction team.

- In 1996, I formally started the CMOS Image Sensor group at Kodak. 20. From 1996 to 2009, I managed the R&D and product development of CMOS Image Sensor (CIS) programs. As is further shown in my curriculum vitae, I was the inventor or co-inventor inventor of many key patents in the field of CMOS Image sensors including Pinned Photodiode Pixels, Camera-on-a-Chip architecture, and shared amplifier pixel architectures. During this time, I led the development of the world's 1st pinned photodiode CIS, Megapixel CIS device, and Shared amplifier CIS pixel product and the world's first ½ inch optical format 1.3 megapixel CMOS image sensor into mass production, providing successful delivery to several compact digital camera products. I also led the development of the 1st 3D hybrid stacked BSI CIS architecture. This led to demonstration of very high performance, low dark current BSI prototype sensors with pixel sizes ranging from 0.9um to 5.0um.

- 21. In 2009, when Kodak closed its CMOS Image Sensor Business, I transitioned into a role as an intellectual property technologist and coordinator.

This role included managing remaining image sensor patent applications and office actions, managing broad electronic components patent applications and office

actions, and providing technical support for intellectual property sales and licensing teams.

- 22. I have since left Kodak and transitioned into a role of providing technical consulting services for CMOS image sensors. In this role I provide consulting services for process, pixels, circuits, sensor architectures, systems and intellectual property to companies and clients.

- 23. My qualifications and publications are set forth more fully in my curriculum vitae, attached as Ex. 1026.

## IV. My understanding of the relevant law

#### A. Claim construction

24. I understand that, when a patent is expired, a claim term in an *inter* partes review is to be interpreted in the following manner: First, the language of the claims themselves is of primary importance in the effort to determine precisely what it is that is patented. The terms used in a claim are generally given the ordinary and customary meaning that the terms would have to a person of ordinary skill in the art in question at the time of the alleged invention, unless the term is expressly defined in the patent. The person of ordinary skill in the art reads the claim in the context of the entire patent, including the specification. Next to the language of the claims, the specification is the single best source for interpreting the claim terms. The claims may also be interpreted using the record of

correspondence between the patent applicant and the Patent Office, and also with reference to other sources of evidence that can help to define the meaning of terms to a person of ordinary skill in the relevant time frame. I define the relevant time frame in ¶ 61, below.

### **B.** Anticipation

- 25. I understand that a claim in an issued patent can be invalid if it is anticipated. In this case, "anticipation" means that there is a single prior art reference that discloses every element of the claim, arranged in the way required by the claim.

- 26. I understand that an anticipating prior art reference must disclose each of the claim elements expressly or inherently. I understand that "inherent" disclosure means that the claim element, although not expressly described by the prior art reference, must necessarily be present based on the disclosure. I understand that a mere probability that the element is present is not sufficient to qualify as "inherent disclosure".

#### C. Obviousness

27. I understand that a claim in an issued patent can be invalid if it is obvious. Unlike anticipation, obviousness does not require that every element of the claim be in a single prior art reference. Instead, it is possible for claim

elements to be described in different prior art references, so long as there is motivation or sufficient reasoning to combine the references.

- 28. I understand that a claim is invalid for obviousness if the differences between the claimed subject matter and the prior art are such that the subject matter as a whole would have been obvious at the time the alleged invention was made to a person having ordinary skill in the art to which said subject matter pertains.

- 29. I understand, therefore, that when evaluating obviousness, one must consider obviousness of the claim "as a whole". This consideration must be from the perspective of the person of ordinary skill in the relevant art, and that such perspective must be considered as of the "time the invention was made".

- 30. The level of ordinary skill in the art is discussed in  $\P$  52-59 below.

- 31. The relevant time frame for obviousness, the "time the invention was made", is discussed in ¶ 61, below.

- 32. I understand that in considering the obviousness of a claim, one must consider four things. These include the scope and content of the prior art, the level of ordinary skill in the art at the relevant time, the differences between the prior art and the claim, and any "secondary considerations".

- 33. I understand that "secondary considerations" include real-world evidence that can tend to make a conclusion of obviousness either more probable

or less probable. For example, the commercial success of a product embodying a claim of the patent could provide evidence tending to show that the claimed invention is not obvious. In order to understand the strength of the evidence, one would want to know whether the commercial success is traceable to a certain aspect of the claim not disclosed in a single prior art reference (i.e., whether there is a causal "nexus" to the claim language). One would also want to know how the market reacted to disclosure of the invention, and whether commercial success might be traceable to things other than innovation, for example the market power of the seller, an advertising campaign, or the existence of a complex system having many features beyond the claims that might be desirable to a consumer. One would also want to know how the product compared to similar products not embodying the claim. I understand that commercial success evidence should be reasonably commensurate with the scope of the claim, but that it is not necessary for a commercial product to embody the full scope of the claim.

34. Other kinds of secondary considerations are possible. For example, evidence that the relevant field had a long-established, unsolved problem or need that was later provided by the claimed invention could be indicative of non-obviousness. Evidence that others had tried, but failed to make an aspect of the claim might indicate that the art lacked the requisite skill to do so. Evidence of copying of the patent owner's products before the patent was published might also

indicate that its approach to solving a particular problem was not obvious.

Evidence that the art recognized the value of products embodying a claim, for example, by praising the named inventors' work, might tend to show that the claim was non-obvious.

- 35. I further understand that prior art references can be combined where there is an express or implied rationale to do so. Such a rationale might include an expected advantage to be obtained, or might be implied under the circumstances. For example, a claim is likely obvious if design needs or market pressures existing in the prior art make it natural for one or more known components to be combined, where each component continues to function in the expected manner when combined (i.e., when there are no unpredictable results). A claim is also likely invalid where it is the combination of a known base system with a known technique that can be applied to the base system without an unpredictable result. In these cases, the combination must be within the capabilities of a person of ordinary skill in the art.

- 36. I understand that when considering obviousness, one must not refer to teachings in the specification of the patent itself. One can, however, refer to portions of the specification admitted to be prior art, including the "BACKGROUND" section. Furthermore, a lack of discussion in the patent specification concerning how to implement a disclosed technique can support an

inference that the ability to implement the technique was within the ordinary skill in the prior art.

#### V. Technical introduction

### A. Background

- 37. The following is a brief technical background covering some concepts relevant to the '714 patent specification and its claims.

- 38. The '714 patent has the title "SOLID-STATE IMAGE SENSING APPARATUS AND MANUFACTURING METHOD THEREOF". It concerns a package for a semiconductor image sensor. An image sensor is a component, used in image capture and optical devices, that converts light into an electrical signal. The electrical signal is generated by semiconductor elements that make up the image sensor, and may be used to generate an image. Image sensors are used in various different types of image capture and optical devices, such as digital cameras, digital scanners, and copiers.

- 39. Semiconductor devices (sometimes referred to as "chips"), including image sensors, are contained in a housing referred to as a "package". A package provides protection for the semiconductor device, and also provides electrical connections to circuits external to the device.

- 40. There are many different types of packages. Some are designed according to industry standards; others are particular to a manufacturer. Some

packages include features appropriate for the type of chip the package houses. For example, an image sensor's package must have an opening to allow light to strike the image sensor. The package's opening is typically covered with a transparent window.

- 41. The light that enters into the opening of an image sensor's package must strike the photosensitive portions of the image sensor without being obstructed. It must also be aligned with the optical system of the image capture device so that image capture of the scene associated with the light striking the image sensor is accurate.

- 42. Therefore, an image sensor must be positioned within its package within certain tolerances. Positioning is often performed using optical inspection of the image sensor and package, using measurements taken by an optical device, for example, a video camera.

- 43. "Mounting" refers to the process of aligning and securing a chip (such as an image sensor) in a package. One method is described in the Admitted Prior Art of the '714 patent:

- "FIG. 9 and FIG. 10 depict a conventional solid-state image sensing apparatus. FIG. 9 is a cross section of a solid-state image sensing apparatus in a ceramic package which was once a mainstream. A ceramic package 1, on which metallized conductor 2 is formed, has a concave part 3 in the center thereof. On the concave part 3, a CCD

chip 4 is mounted by die bonding, and an electrode pad 6 of CCD chip 4 is wire-bonded to the metallized conductor 2 by a metal lead 7. A lead terminal 8 is deposited to an end face of metallized conductor 2 exposing itself from the side of ceramic package 1.

FIG. 10 is a cross section of a solid-state image sensing apparatus in a plastic package. A lead frame 11 comprising an inner lead 9 and an outer lead 10 is inmolded in a plastic package 12. At a center of the plastic package, a concave portion 13 is situated. The CCD chip 4 is di-bonded [sic.: die-bonded] by conductive paste 14 to the concave portion 13, and the electrode pad 6 on the CCD chip 4 is wire-bonded to the inner lead 9 by the metal lead 7 as same as the case of the ceramic package shown in FIG. 9." (Ex. 1001, 1:42-61, *see also* Figs. 9 and 10).

44. The above passage from the Admitted Prior Art of the '714 patent describes an image sensor mounted by "die bonding". A semiconductor chip is sometimes referred to as a "die" because in fabrication, integrated circuits are typically formed in large batches on a single semiconductor wafer, which is then "diced" into many pieces, each containing a copy of the circuit. Each piece is referred to as a "die". "Die bonding" refers to affixing the back side of a chip (a "die") to substrate, for example, the base of a package. This leaves the upper (or front side) surface of the chip exposed. The chip's upper/front side surface has metal interconnections along its edges with "pads", which are electrical contacts.

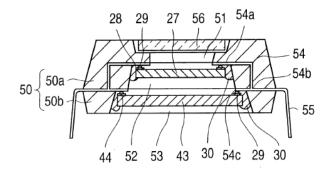

45. Prior art Fig. 10 of the '714 patent (reproduced below and described in the passage described in ¶ 43 above) shows an apparatus constructed in the above-described fashion. Fig. 10 shows an image sensor chip (4) having pads (6). The pads (6) are connected, using wires (7), to flat metallic strips (9 and 10), called "leads". The leads are divided into two parts: inner leads (9) and outer leads (10). The inner leads are located inside the package and connect to the chip's pads. The inner leads run into outer leads. The outer leads project out of the package to facilitate connection of the image sensor to external circuitry. (Ex. 1001, 1:53-61).

FIG. 10

PRIOR ART

6

4

7

10

11

13

14

12

46. The package of Fig. 10 uses wire bonding (wires 7). This has several problems. Wire bonding limits how small a package can be, since the wires require vertical and horizontal space to make the connections between the pads and the leads. Also, the wires must be carefully placed and bonded to pads (6) and leads (9), which is costly and complex. The materials used and processing time required add to the cost. The requirements that wires be carefully placed and

bonded to the pads adds processing time. Also, wire bonds can cause unwanted reflections of light onto the image sensor.

- 47. To address these problems, the prior art developed another mounting method. In this method, the inner leads are extended and coated with an amount of a conductive material, referred to as a "bump". The bumps are press bonded or melted directly onto the contact pads of the chip. This process eliminates the need for intermediate wires (7) and thus leads to space saving and fabrication time.

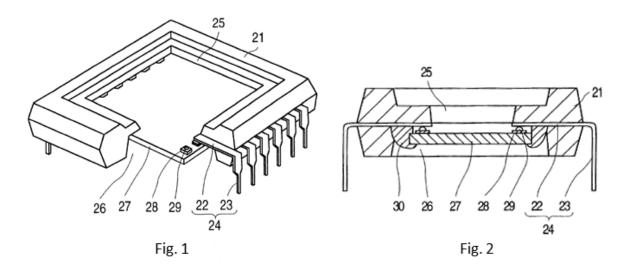

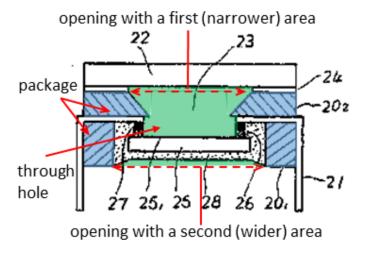

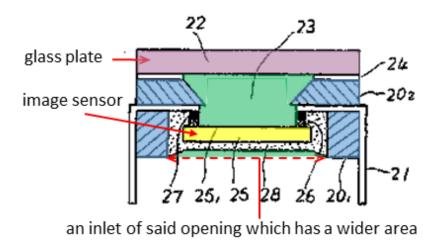

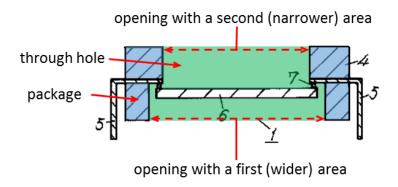

- 48. The '714 patent describes a similar, already known optical positioning and bonding process for a package for an image sensor. Figs. 1 (cutaway) and 2 (cross-section) of the '714 patent show the '714 patent's "solid-state image sensing apparatus", or image sensor package. These figures are reproduced below, and their structure is described in the below passage from the '714 patent's specification. They show a solid-state image sensor (27) mounted in a package (21).

"An exemplary embodiment of the present invention is stated here by referring to FIG. 1, which is a cutaway perspective view of an exemplary embodiment according to the present invention. A lead frame 24 comprising an inner lead 22 and an outer lead 23 is inmolded in a package 21. As FIG. 1 depicts, a through hole is provided at the center of the package 21, and in front side of the package 21, an opening 25 which has a smaller opening area is situated, and another opening 26 (hereinafter called 'inlet' which has a

wider opening area is situated at the back side thereof. The area of opening 25 is smaller than that of CCD chip 27. An inner lead 22 is exposed from the back side of a step between the opening 25 and the inlet 26, and the inner lead 22 is electrically connected to a bump 29 disposed on an electrode 28 of CCD chip 27." (Ex. 1001, 4:49-63).

49. As expected for an image sensor package, package 21 allows light to reach the light-detecting upper/front side surface (not numbered) of image sensor 27, via an opening (25). The opening extends through the package's center, creating a through hole:

"As FIG. 1 depicts, a through hole is provided at the center of the package 21, and in front side of the package 21, an opening 25 which has a smaller opening area is situated, and another opening 26 (hereinafter called 'inlet' which has a wider opening area is situated at the back side thereof." (Ex. 1001, 4:53-58).

As described above, the back of this through hole is indicated by "inlet 26" in Fig.

1. It is the access point for inserting the image sensor into the package. After

being inserted, the image sensor ("CCD chip 27") is electrically connected to inner leads 22 (which are part of "lead frame (24)"). The image sensor is then secured with an adhesive (30):

"[T]he CCD chip 27 is inserted into the package 21 from the [inlet] 26. Then, the bump 29 is press-fitted and connected to the inner lead 22 which is exposed from a back side of the step situated between the opening 25 and the net 26. During this press-fit operation, a position signal is feedbacked from a optical position adjusting device(not shown) disposed in front of the CCD chip 27 to the mounting jig, thereby finely adjusting an orientation of the CCD chip 27 and disposing the CCD chip 27 on the back side of the step of the package 21. At the same time, ultra-violet hardening adhesive 30 is injected in a specified quantity from a dispenser which is situated beside a press-fit jig to glue four sides of the CCD chip 27 to the package 21, and finally, the CCD chip 27 is accurately mounted to the package 21." (Ex. 1001, 5:9-22).

50. This arrangement allows light to enter from the top of the package (via opening 25) and reach the light-receiving upper (or front side) surface of the image sensor. That light enters from the top of the package (and that light-receiving surface of the image sensor is its upper surface in the figures) is indicated in the following passages and Figs. 7 and 8 of the '714 patent (reproduced below). These passages and figures describe minor variations on the '714 patent's package

that feature a transparent "glass substrate 49" or "protection panel 56" at the top of the package so as to allow light to reach the upper surface of the image sensor:

"Since the surface on which the circuit elements 43 are formed is situated upward, a shading film 48 is required; however, when defects are found in the CCD chip 41 or the peripheral circuit elements 43, the defective parts can be easily replaced and the other parts also can be used again. In FIG. 7, a glass substrate 49 is made from the shading film by being deposited with metal or by sputtering." (Ex. 1001, 7:26-32).

## FIG. 7

Figure 8, shown below, is described relative to the arrangement as follows:

"A protection panel 56, made of transparent material such as glass, is shown in FIG. 8. The protection panel 56 protects the inside of solid-state image sensing apparatus ...." (Ex. 1001, 8:43-45).

FIG. 8

the common understanding of that term. The term "package" in common usage ordinarily refers to the whole apparatus to which the chip is mounted (including, *e.g.*, the lead frame, the transparent lid, etc.). The '714 patent uses the term to refer to just a part of the apparatus—the body part, made, *e.g.*, of "plastic, ceramic or glass", to which the other components are mounted—which one of ordinary skill would typically have referred to as the package body or substrate. (Ex. 1001, 1:8-9). This usage is shown in the embodiments and figures that consistently label this body part of the assembly as simply the "package". For example, the following passage describes "package 21" (as seen in Fig. 1) as a separate component from "lead frame 24". The term is used the same way in the other embodiments.

term "package", so as to be able to clearly and consistently distinguish between the various elements recited in the '714 patent and the prior art.

"An exemplary embodiment of the present invention is stated here by referring to FIG. 1, which is a cutaway perspective view of an exemplary embodiment according to the present invention. A lead frame 24 comprising an inner lead 22 and an outer lead 23 is inmolded in a package 21." (Ex. 1001, 4:49-53; *see also* Fig. 1).

### VI. Level of ordinary skill in the art

- 52. I have considered what the level of ordinary skill in the art of the '714 patent was in the relevant time frame. In considering the level of ordinary skill, I have taken into account the levels of education and experience of persons working in the field, the types of problems encountered in the field; and the sophistication of the technology. I understand that a person of ordinary skill in the art is a hypothetical person that is deemed to be aware of the content of all analogous prior art.

- 53. In the relevant time frame, one of ordinary skill in the art of the patent in my opinion would have had a Bachelor's degree in electrical engineering, physics, or material science and approximately 3-5 years of industrial experience or equivalent research or teaching experience, or a Master's degree in the same fields and 1-3 years of industrial experience or equivalent research or teaching experience. The levels of education, experience and knowledge can trade off

against one another. I believe that I have at least that level of skill and that I can opine as to the perspective of a person of a person of ordinary skill in the art in the relevant time frame.

- 54. Examples of particular skills possessed by the person of ordinary skill in the art are visible from the prior art and the specification of the '714 patent.

- 55. The person of ordinary skill in the relevant time frame would have been familiar with solid-state image sensing devices, including CCD type solid-state image sensing devices. The person of ordinary skill would have been familiar with packages for semiconductor devices, including for solid-state image sensors. The person of ordinary skill would also have been able to employ various standard techniques for mounting a chip (such as a solid-state image sensor) in a package, including mounting a chip face up to the package's base by "die bonding" (Ex. 1001, 1:40-61), and mounting a chip by bonding the chip's pads to the package's leads, as described below.

- 56. The person of ordinary skill would have known that a package serves to electrically connect the chip housed in the package to external circuits, and would have been familiar with packages that use a lead frame (including inner leads located in the package's interior and outer leads that project outside the package), and would have been able to connect the leads to pads on the chip to make this electrical connection. The person of ordinary skill would also have been

familiar with various methods of connecting a chip's pads to the package's leads, including using wire bonds, bump bonds, or a conductive adhesive such as an anisotropic conductor.

- 57. The person of ordinary skill would have been familiar with a variety of the different shapes and structures semiconductor packages can take, in particular packages for solid-state image sensors. For example, the person of ordinary skill would have been familiar with multi-chip packages, and would have known that an image sensor may be housed within a single package with a peripheral circuit chip such as an image signal processor. The person of ordinary skill would have been familiar with various different methods of combining multiple chips into a single package, including packages in which chips are mounted on a common substrate inside the package, and packages in which multiple chips are mounted separately inside the package.

- 58. The person of ordinary skill would have known the process steps used in the fabrication of a semiconductor package, including: forming the package itself (*e.g.*, by a molding process) with a lead frame sealed in it such that the inner leads project inside and the outer leads project outside the package; mounting a chip (*i.e.*, a solid-state image sensor or a peripheral chip) on a substrate or forming a chip on a semiconductor substrate; inserting a chip (or substrate on which

multiple chips are formed and/or mounted) into the package; connecting the chip's or substrate's pads to the package's leads via standard bonding methods (*e.g.*, wire bonds, bumps, or an anisotropic conductor); and using an adhesive to secure the chip or substrate to the package.

59. The person of ordinary skill would also have been familiar with the need to precisely adjust the optical positioning of an image sensor (*e.g.*, for use within a lens system). The person of ordinary would be familiar with various methods for performing the optical positioning, such as using reference marks on the image sensor, the package, or a separate positioning element, and using measurements obtained via an optical device to perform an accurate positioning.

### VII. Predictability of the art

60. In my opinion, the field of the '714 patent was predictable in the relevant time frame. In particular, the fabrication of a solid-state image sensing apparatus consisting of a package having a through hole in which a solid-state image sensor (or an image sensor and a peripheral circuit chip) are mounted, connected to the inner leads of the package's lead frame, precisely optically positioned, and secured via an adhesive, could be predictably implemented using solid-state image sensor and semiconductor package fabrication techniques readily available to most engineers in the field at the time the '714 patent was filed.

## VIII. Relevant time frame for determining obviousness

61. I understand that obviousness must be evaluated at the time the alleged invention was made. From the front page of the '714 patent (left column, field "[30] Foreign Application Priority data"), I understand that the first patent application was filed on Aug. 2, 1995. I will assume for the purpose of this report that Aug. 2, 1995 is the date the purported invention was made, with the understanding that my testimony will also be applicable to some time prior to Aug. 2, 1995, approximately the early 1990s. I may refer to this time period as the "relevant time frame", and my testimony concerning obviousness is directed to this time frame, even if I occasionally do not explicitly use a past tense.

#### IX. Overview of the claims

- 62. The '714 patent contains 16 claims. Nine of these claims, 1, 2, 6, 7, 12, 13, 14, 15, and 16, are independent claims, because they do not recite dependencies from any other claims in their preambles.

- 63. Independent claim 1 of the '714 patent reflects the package described in ¶¶ 48-49 above:

- "1. A solid-state image sensing apparatus comprising:

- a package having a through hole therein, openings on both end faces thereof, and different opening areas of said openings,

- a lead frame comprising inner leads and outer leads, said lead frame being sealed in said package, and

- a solid-state image sensing device mounted in said package by being inserted from an inlet of said opening which has a wider area, and

thereby sealing said through hole, said solid-state image sensing device being secured to said package via an adhesive." (Ex. 1001, Claim 1).

64. Claim 1 recites an image sensor mounted in a package. The package has a lead frame consisting of inner leads and outer leads. The package also has a through hole with two openings. One opening is wider than the other. The wider of the openings (which, as shown in Fig. 1, reproduced for ¶ 48 above, is the bottom opening) is used to insert the image sensor into the package. This seals the through hole. The image sensor is the secured to the package using an adhesive—in other words, the image sensor is glued to the package. The remaining claims add various minor features that are addressed below.

## X. Overview of the primary prior art references

65. Japanese Pat. App. Pub. No. S61-131690 ("Yoshino") (Ex. 1006, certified translation as Ex. 1003) and Japanese Pat. App. Pub. No. H07-045803 ("Wakabayashi") (Ex. 1007, certified translation as Ex. 1004), disclose the concepts of claim 1. Yoshino is the base reference applied in Grounds 1-11, for claims 1, 6-13, and 15-16. Wakabayashi is the base reference applied in Grounds 12-15, for claims 1-5 and 13.

#### A. Overview of Yoshino

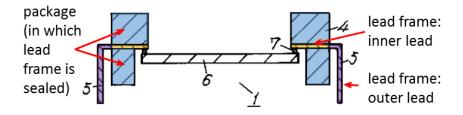

- 66. Yoshino discloses a package for a solid-state image sensing device, in which the image sensor is mounted in a through hole and bonded to the inner leads, like the '714 patent, as described in the following passage:

- "(1) A solid-state image pickup device characterized by comprising a solid-state image sensor, a packaging substrate supporting said solid-state image sensor and having an opening tapered so as to expand the edge as it becomes more distant from said solid-state image sensor's photoreceptive surface, a light transmitting glass plate adhesive bonded to said packaging substrate so as to cover said opening, and electrode leads connected to said solid-state image sensor's bonding pads via a conductive bonding material." (Ex. 1003, p. 1).

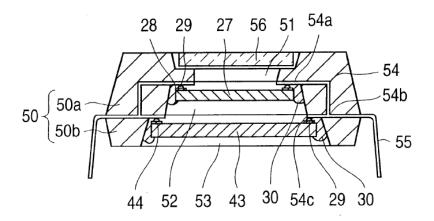

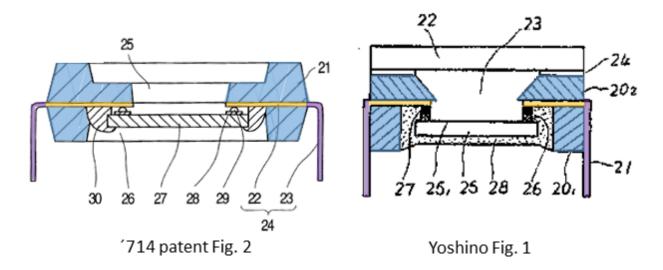

- 67. Petitioner has accurately illustrated similarities between the teachings of Yoshino and the '714 patent in the in the following versions of the '714 patent's Fig. 2 (left side) and Yoshino's Fig. 1 (right side). In these figures, Petitioner has accurately highlighted the like elements.

- 68. For example, Yoshino describes an apparatus like that of claim 1 of the '714 patent. Yoshino's package has a solid-state image sensing apparatus comprising a package ("packaging substrate (20)", highlighted light blue in the above figures) with a through hole ("opening (23)", highlighted green) itself having openings at the top and bottom ends having different areas. Yoshino also discloses a lead frame ("electrode leads (21)"). The inner leads are highlighted orange in the figures above; the outer leads are highlighted purple. Yoshino states:

- "FIG. 1 is a cross-sectional view of one example of the invention. In this solid-state image pickup device, the packaging substrate (20), for example, a black ceramic substrate, is constructed by stacking ceramic molded frames  $(20_1)$  and  $(20_2)$ , and the electrode leads (21) are provided in a pin-socket format disposed so as to penetrate the packaging substrate (20) above the ceramic molded frame  $(20_1)$ . The light transmitting glass plate (22) is hermetically secured to the ceramic molded frame  $(20_2)$  using black fritted glass beforehand so as to cover the tapered opening (23) of the packaging substrate (20)." (Ex. 1003, p. 2).

- 69. As indicated in the following passage, Yoshino also discloses a solid-state image sensing device ("image sensor (25)", highlighted yellow in the above figures) mounted in the package and secured via an adhesive ("molded resin (28)", highlighted red). Molded resin is a material sometimes used for fabricating a package body or package substrate. When used in the manner taught in Yoshino—

for "supporting the solid-state image sensor (25) in the packaging substrate"—it functions as an adhesive: *i.e.*, it adheres the image sensor to the package body. (Ex. 1003, p. 2).

70. Furthermore, Yoshino discloses elements of other claims. For example, Yoshino discloses connecting an electrode pad ("bonding pads (26)", highlighted pink in the above figures) of the image sensor to the inner lead via a bump ("conductive bonding material (27)", highlighted dark blue).

"The solid-state image sensor (25) is placed so that the bonding pads (26) of the solid-state image sensor (25) are aligned with the electrode leads (21), and the bonding pads (26) and the electrode leads (21) aligned therewith are connected via a conductive bonding material (27), for example, indium. The electrode leads (21) are coated with the conductive bonding material (27) by means of plating, brazing, or the like. By supporting the solid-state image sensor (25) in the packaging substrate (20) via a molded resin (28), a desired solid-state image pickup device is obtained." (Ex. 1003, p. 2).

## B. Overview of Wakabayashi

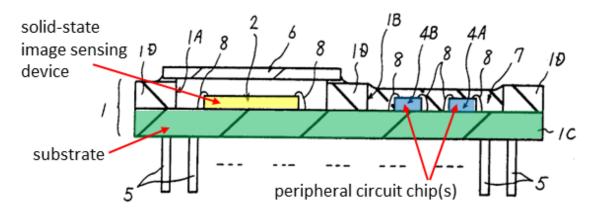

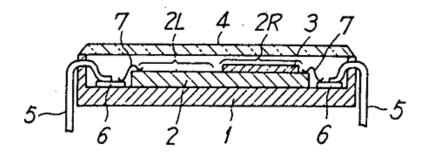

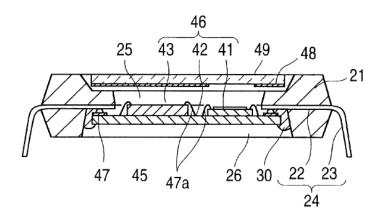

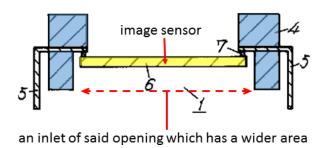

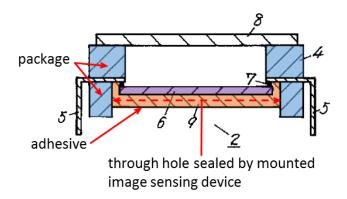

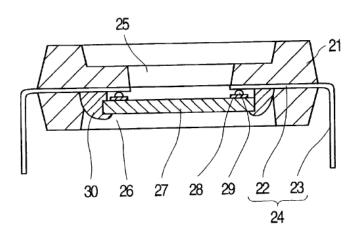

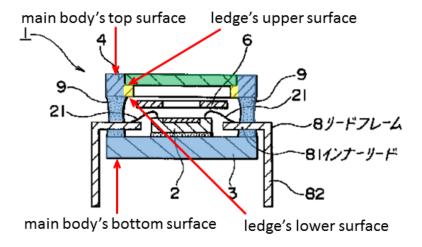

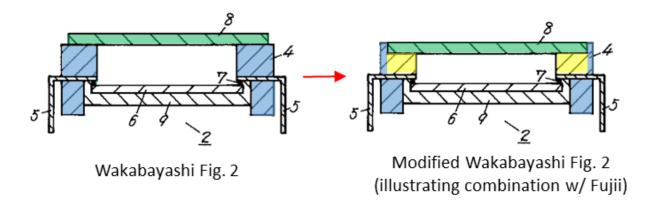

71. Wakabayashi discloses the basic embodiments of the '714 patent. As taught in the following passage and shown in Figs. 1 and 2 of Wakabayashi, Wakabayashi discloses a package in which a solid-state image sensing device is mounted in the through hole of a package, bonded directly to the inner leads, and secured to the package with an adhesive, like claim 1 of the '714 patent:

- "(Construction) The solid-state image pickup device is comprised of a package 4 made of a transparent resin, leads 5, a CCD chip 6, and bumps 7 which join the inner leads to the CCD chip 4 [sic.: CCD chip 6]. A microlens is formed at the light-receiving face of the CCD chip 6. A space is provided between the microlens face provided at the light receiving face of the CCD chip 6 and the inner face of the light receiving section of the package 4. The spacing can be suitably selected. The package 4 and the leads 5 are produced by transfer molding, or the like, by clamping the lead frame with a pair of dies forming a prescribed cavity." (Ex. 1004, Abstract).

- 72. The above passage describes "clamping the lead frame with a pair of dies". Although a "die" may refer to a semiconductor wafer, this is not what Wakabayashi is referring to here. Rather, the "die" Wakabayashi refers to here is a manufacturing die, which is a specialized manufacturing tool used to cut or shape material such as sheet metal or plastic.

- 73. Petitioner has accurately illustrated similarities between the teachings of Wakabayashi and the '714 patent in the following versions of the '714 patent's Fig. 2 (left side) and Wakabayashi's Fig. 2 (right side). In these figures, Petitioner has accurately highlighted the like elements. The highlighting indicates the same elements as in the figures (from Yoshino and the '714 patent) discussed in ¶¶ 67-69 above.

74. As shown in Fig. 2 and described in the above passage (and also in the passages below), Wakabayashi discloses a package ("package 4", highlighted light blue in the above figures) having a through hole with different opening areas at its top and bottom end faces. Wakabayashi discloses a lead frame ("lead frame" or "leads 5") having an inner lead (highlighted orange in the above figures) and outer lead (highlighted purple). Wakabayashi also discloses mounting a solid-state image sensing device ("CCD chip 6", highlighted yellow in the above passage), in the package, sealing the through hole, using an adhesive ("adhesive resin 7 [sic.:

"(Claim 1) A solid-state image pickup device characterized by comprising a CCD chip joined via bumps to the inner lead sections of a package made of a transparent resin comprising a light-receiving section and side wall sections integrally formed while interposing a lead frame and having, in its interior, a space for disposing a CDD [sic.: CCD] chip, the inner lead sections of said lead frame being exposed to the space, and the face opposite to the light-receiving face

adhesive resin 9]", highlighted red, labeled "9" in Fig. 2).

being open." (Ex. 1004, Claim 1).

"(Means for Solving the Problems) The solid-state image pickup device according the invention has the basic construction of comprising a CCD chip joined via bumps to the inner lead sections of a package made of a transparent resin comprising a light-receiving section and side wall sections integrally formed while interposing a lead frame and having, in its interior, a space for disposing a CDD [sic.: CCD] chip, the inner lead sections of the lead frame being exposed to the space, and the face opposite to the light-receiving face being open." (Ex. 1004, ¶ 0005).

"In another aspect, it is constructed by sealing the back face side of the chip with an adhesive resin." (Ex. 1004, ¶ 0007).

"In FIG. 1, reference numeral 1 is a cross section of the basic construction of the solid-state image pickup device, which includes a package 4 formed with a transparent resin, leads 5, a CCD chip 6, bumps 7 which join the inner lead sections to the CCD chip 4 [sic.: CCD chip 6]. A microlens is formed on the light-receiving face of the CCD chip 6." (Ex. 1004, ¶ 0010).

"FIG. 2 is a cross section of a solid-state image pickup device in which, in addition to the basic structure discussed above, the back face side of the chip is further sealed with an adhesive resin 7 [sic.: adhesive resin 9]. By constructing the device in this way, the bump joints are reinforced, and at the same time, the penetration of dust from the outside can be prevented." (Ex. 1004, ¶ 0015).

#### **XI.** Construction of the claims

- 75. My understanding of the legal requirements for claim construction is provided beginning at ¶ 24, above.

- 76. I have reviewed the claim constructions applied in the petition for *inter partes* review that this declaration supports, and I find that the constructions would have been reasonable to a person of ordinary skill in art in the relevant time frame. I have applied these claim constructions in my analysis in this declaration.

## A. Claims 2—"solid-state image apparatus"

- 77. Claim 1 and 3-16 recite the phrase "solid-state image sensing apparatus". Claim 2 recites the phrase "solid-state image apparatus". The '714 patent—although it does not expressly define the phrase—indicates that a "solid-state image sensing apparatus" may comprise the "solid-state image sensing device", the package, a lead frame, adhesive, and various other components such as a "substrate … and a peripheral circuit chip". For example:

- "1. A solid-state image sensing apparatus comprising:

- a package having a through hole therein, openings on both end faces thereof, and different opening areas of said openings,

- a lead frame comprising inner leads and outer leads, said lead frame being sealed in said package, and

- a solid-state image sensing device mounted in said package by being inserted from an inlet of said opening which has a wider area, and

thereby sealing said through hole, said solid-state image sensing device being secured to said package via an adhesive." (Ex. 1001, 9:20-30).

"6. A solid-state image sensing apparatus comprising:

a package having a through hole therein, openings on both end faces thereof, and different opening areas of said openings,

a lead frame comprising inner leads and outer leads, said lead frame being sealed in said package,

a substrate on which a solid-state image sensing device and a peripheral circuit chip are mounted ...." (Ex. 1001, 9:59-66).

78. The '714 does not teach that the entire "solid-state image sensing apparatus" must be solid-state (meaning made of semiconductor material or containing no empty space). Rather, the '714 patent treats this phrase to mean an apparatus that features a solid-state image sensor. For example, some elements are not necessarily a semiconductor (*e.g.*, the package may be plastic, ceramic, or glass), as indicated in the passage below:

"The present invention relates to a solid-state image sensing apparatus using a solid-state image sensing device (hereinafter called CCD chip) in a package made of plastic, ceramic or glass ...." (Ex. 1001, 1:6-9).

79. In my opinion, the omission of the word "sensing" in claim 2 does not change the meaning of the phrase.

80. Therefore, I conclude that the term "solid-state image apparatus" should be interpreted interchangeably with the term "solid-state image sensing apparatus".

## B. Claims 2-7, 9-11, 13-16—"electrode pad(s)"

81. The '714 patent does not expressly define this phrase. The specification also refers to "electrode pad(s)" in one place (as follows) as an "electrode", but in my opinion this does not have any impact on the meaning of the term:

"An inner lead 22 is exposed from the back side of a step between the opening 25 and the inlet 26, and the inner lead 22 is electrically connected to a bump 29 disposed on an electrode 28 of CCD chip 27." (Ex. 1001, 4:59-63).

82. The '714 patent indicates (in the claims and the following passages from the specification) that an "electrode pad" is an electrical connection point on a "solid-state image sensing device", "peripheral circuit chip", or "substrate". For example:

"The bump 29 is formed on the electrode pad 28 of the CCD chip 27 ...." (Ex. 1001, 5:6-8).

"A bump 29 disposed on an electrode pad 44 of the peripheral circuit elements is connected to an electrode pad 45 of the group of wirings on the substrate 42 ...." (Ex. 1001, 6:7-9).

"connecting an electrode pad of the solid-state image sensing device ...." (Ex. 1001, 10:64-65).

83. The '714 patent also indicates that the "electrode pad(s)" electrically connect the device or substrate to conductive elements in the package: to the inner lead of the "lead frame" or, in the Admitted Prior Art, a "metallized conductor". For example:

"The electrode pad of solid-state image sensing apparatus is coupled to the inner lead via a bump or an anisotropic conductor having only vertical conductivity so that optical positioning as well as electrical connecting is completed." (Ex. 1001, 3:6-10).

"The electrode pad disposed around the upper surface of the substrate is connected to the inner lead via the bump or anisotropic conductor so that the optical positioning as well as electrical connection is completed." (Ex. 1001, 3:23-26).

"The CCD chip is loaded into the through hole of the package from the opening which has the wider opening area, and the electrode pad is connected to the first inner lead via the bump or the anisotropic conductor so that optical positioning as well as electrical connection is completed." (Ex. 1001, 3:53-63).

"connecting an electrode pad disposed on a periphery of the substrate to the inner lead via a bump or an anisotropic conductor having only vertical conductivity ...." (Ex. 1001, 10:64-66).

84. Therefore, I conclude that "electrode pad(s)" should be construed as "an electrical connection point on a substrate or semiconductor device."

### C. Claims 3, 9, 13-16—"bump"

85. The '714 patent does not expressly define "bump". The '714 patent teaches that a "bump" is a means by which the pads (of the image sensor, peripheral chip, or substrate) electrically connected to a lead. This is shown, for example, in the passages from the '714 patent cited in ¶ 83 above. (*E.g.*, Ex. 1001, 3:6-10; 3:23-26; 3:53-63; 10:64-66). Thus, one of ordinary skill would have understood the term to mean an amount of conductive material used for electrically connecting the device using a number of different methods. This agrees with the definition of the term found in Charles A. Harper & Martin B. Miller, *Electronic Packaging, Microelectronics, and Interconnection Dictionary* (1993) ("Harper")(Ex. 1012):

"A small metal mound or hump that is formed on the chip or the substrate bonding pad and is used as a contact in face-bonding. It is a means of providing connections to terminal areas of a device." (Ex. 1012, p. 23).

- 86. Therefore, I conclude that "bump" should be construed as "an amount of conductive material used for an electrical connection."

- D. Claim 8—"covers an entire upper surface of said substrate except an upper surface of the solid-state image sensing device"

- 87. This phrase in claim 8 does not require that the shading film be located *on* the substrate. Instead, it means that the shading film "covers" in the sense of "provides shade for" an entire upper surface of said substrate except an upper surface of the solid-state image sensing device. This is to protect the peripheral circuit elements on the substrate from light, which can interfere with the function of those elements.

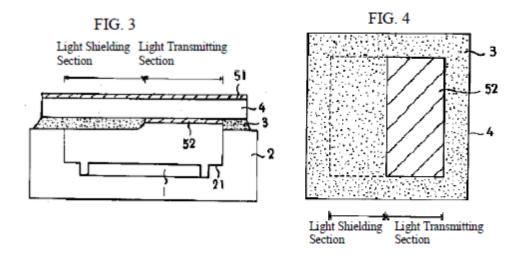

- 88. Thus, this phrase means that the shading film could be on the substrate itself, or it could be *above* the substrate, as shown in the '714 patent's Fig. 7. Fig. 7 shows the only embodiment in the specification that features a shading film. As seen in Fig. 7 (and described in the below passage), this embodiment places "shading film 48" above the substrate (42), on the package's glass cover ("glass substrate 49"):

"Since the surface on which the circuit elements 43 are formed is situated upward, a shading film 48 is required .... In FIG. 7, a glass substrate 49 is made from the shading film by being deposited with metal or by sputtering." (Ex. 1001, 7:26-32).

- 89. Also, claim 8 is multiply dependent from claim 6 or claim 7. Claim 6 discloses a solid-state image sensing device and a peripheral circuit chip "mounted" on the substrate. (Ex. 1001, 9:65-66). If "covers an entire upper surface of said substrate except an upper surface of the solid-state image sensing device" required that the shading film actually be on the surface of the substrate, then in this case (because the peripheral chip is *mounted* on the substrate's surface), the shading film would not provide shade for the peripheral circuit chip. *I.e.*, the film would be *on* the substrate, underneath the mounted peripheral chip, rather than above the peripheral chip. Thus, the shading film would not fulfill its function of protecting the peripheral chip from light.

- 90. Thus, it is my opinion that this phrase should be construed to require that the shading film is located on or above the entire upper surface of the substrate except for the portion of the substrate on which the solid-state image sensing device is disposed.

# E. Claim 7—"plastic package"

91. Although claim 7 recites both a "package" and a "plastic package", there is no embodiment of the '714 patent with two packages. Claim 7 corresponds to Fig. 5 (reproduced below), which depicts only one package.

FIG. 5

92. Thus, it is my opinion that the term "plastic package" refers back to the earlier recitation of the term "package". It is further my opinion that the term "plastic package" in claim 7 should be construed to refer to the earlier use of the term "package", which is a shorthand reference for "plastic package".

### F. Claim 15—"substrate"/"semiconductor substrate"

93. Claim 15 recites mounting an image sensor and peripheral chip on "a substrate", then "inserting the semiconductor substrate", then connecting "the substrate", then securing "the semiconductor substrate". In particular, Claim 15 recites:

"mounting said solid-state image sensing device and said peripheral circuit chip on a substrate where a group of wirings is disposed in

order to connect the solid-state image sensing device and the peripheral circuit chip to the group of wirings,

inserting the semiconductor substrate into the through hole,

connecting an electrode pad disposed on a periphery of the substrate to the inner lead via a bump or an anisotropic conductor having only vertical conductivity, while simultaneously adjusting the optical positioning of the solid-state image sensing device, and

securing the semiconductor substrate ...." (Ex. 1001, 11:36-12:9).

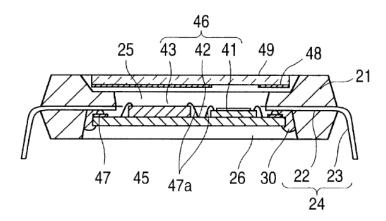

94. It is my opinion that claim 15 discloses only one substrate, and that "semiconductor substrate" here refers back to the "substrate". This is shown by Figs. 6 and 7 of the '714 patent (reproduced below), which correspond to claim 15, and supported by the following passages from the specification which describe those figures.

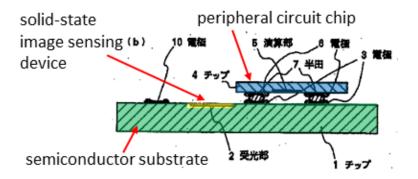

"FIG. 6 is a cross section of the solid-state image sensing apparatus used in Embodiment 5 of the present invention. This embodiment is one of variations of Embodiment 4 described above. The method of accurately mounting the CCD chip 41 to the package 21 is the same as that of the Embodiment 4 from the standpoints of structure and manufacturing, namely, the CCD module 46 on which the CCD chip, peripheral circuit elements and the group of wirings are formed, is inserted from the inlet 26, and the CCD module 46 is fixed to the package 21, while the optical position of CCD chip 41 is fine adjusted. A different point from the Embodiment 4 is this: in

Embodiment 4, the CCD chip is formed directly on the semiconductor substrate, which is to be the substrate 42 of the CCD module 46, through a circuit-chip-forming-process such as a direct diffusion process, on the other hand in Embodiment 5, the CCD chip 41 as well as peripheral circuit elements 43 was already produced in a separate process, and the CCD chip 41 and peripheral circuit elements 43 are disposed on the substrate 42 on which the group of wirings have been formed, and thereby they are electrically connected to form the CCD module 46.

Accordingly, the substrate 42 used in this embodiment may be made of a material other than semiconductor. As shown in FIG. 6, when the CCD chip 41 produced in the separate process is mounted on the substrate 42, the electrode of CCD chip 41 is wire-bonded to the electrode terminal of the group of wirings by using a metal wire 47a.

FIG. 7 is a cross section of the solid-state image sensing apparatus used in Embodiment 6. This embodiment is also one of variations of Embodiment 5 above mentioned. A different point from Embodiment 5 is this: in Embodiment 5, the peripheral circuit elements 43 are connected to the substrate 42 via the bump 29 in the face-down way same as that in Embodiment 4; however, in this Embodiment 6, the peripheral circuit elements 43 are disposed on the substrate 42 in the face-up way(the face on which a circuit is formed is situated upward) as the CCD chip 41 is in Embodiment 5, and the electrode of peripheral circuit elements is wire-bonded to the electrode terminal of the group of wiring by using the metal wire 47a." (Ex. 1001, 6:29-7:2).

FIG. 6 FIG. 7

95. Thus, it is further my opinion that the term "semiconductor substrate" in claim 15 should be construed to refer to the earlier use of the term "substrate", which is just a shorthand reference for "semiconductor substrate".

## XII. Claim 1 is anticipated by Yoshino.

### A. Summary of opinion

- 96. It is my opinion that Claim 1 is anticipated by Japanese Pat. App. Pub. No. S61-131690 ("Yoshino") (Ex. 1006, certified translation as Ex. 1003).

- 97. Yoshino discloses a package like that of the '714 patent. As explained below, Yoshino's through hole allows an image sensor to be mounted from the back side of the package and bonded to the inner leads of the package's lead frame, just like that of the '714 patent.

## B. Yoshino is prior art

98. I understand that Yoshino is prior art to the '714 patent, because it was published on June 19, 1986.

# C. Summary of Yoshino

99. Yoshino is summarized in ¶¶ 66-69 above.

# D. Element-by-element analysis of claim 1 over Yoshino

### 1. Claim 1

[1a]. "A solid-state image sensing apparatus comprising:"

100. In the following passage, Yoshino discloses a solid-state image sensing apparatus (an apparatus comprising a "solid-state" image sensing device):

"A solid-state image pickup device characterized by comprising a solid-state image sensor, a packaging substrate supporting said solid-state image sensor ...." (Ex. 1003, p. 1, Claim 1).

"[1b]. a package having a through hole therein, openings on both end faces thereof, and different opening areas of said openings,"

101. In the following passage, Yoshino teaches a package having a through hole therein:

"a packaging substrate supporting said solid-state image sensor and having an opening tapered so as to expand the edge ...." (Ex. 1003, p. 1, Claim 1).

102. Below is a version of Yoshino's Fig. 1 that Petitioner has annotated to accurately show the through hole, and that the package has openings on both end faces thereof, and different opening areas of said openings. The package ("packaging substrate (20)") is highlighted in light blue and the through hole

("tapered opening (23)") is highlighted in green. (Ex. 1003, p. 2). The openings on both end faces, having different opening areas, are indicated with red arrows.

103. Yoshino's Fig. 1 shows the apparatus after one end is covered by "glass plate (22)" and the through hole is sealed by an adhesive ("molded resin 28"). (Ex. 1003, p. 2). Yoshino's openings are nevertheless essentially the same as those of the '714 patent. With regard to Yoshino's top opening, the '714 patent also teaches that one opening may be covered by glass "protection panel 56 [which] protects the inside of solid-state image sensing apparatus":

"A protection panel 56, made of transparent material such as glass, is shown in FIG. 8. The protection panel 56 protects the inside of solid-state image sensing apparatus; however, whether using of this protection panel 56 or not does not change the functions as well as effects of the present invention described in the above embodiments." (Ex. 1001, 8:43-48).

With regard to Yoshino's bottom opening, the '714 patent also requires that this opening be sealed with an image sensor, followed by application of an adhesive, as discussed with regard to claim element [1d] in ¶¶ 106-113 below.

"[1c]. a lead frame comprising inner leads and outer leads, said lead frame being sealed in said package, and"

104. Yoshino discloses "electrode leads (21)", which is a lead frame comprising inner leads and outer leads, in the following passage:

"The solid-state image sensor (25) is placed so that the bonding pads (26) of the solid-state image sensor (25) are aligned with the electrode leads (21), and the bonding pads (26) and the electrode leads (21) aligned therewith are connected via a conductive bonding material (27), for example, indium." (Ex. 1003, p. 2).

105. Petitioner has accurately highlighted the '714 patent's Fig. 2 (reproduced below on the left side) and Yoshino's Fig. 1 (below on the right side), to show that Yoshino's lead frame is nearly identical to that of the '714 patent. For reference, the '714 patent labels its lead frame as "inner lead 22" and "outer lead 23" of "lead frame 24". (Ex. 1001, 4:52-53). In both figures, Petitioner has highlighted the inner leads orange. The outer leads are highlighted purple. The figures also show that Yoshino's lead frame is sealed in said package (highlighted blue), just as the lead frame of the '714 patent is.

"[1d]. a solid-state image sensing device mounted in said package by being inserted from an inlet of said opening which has a wider area, and thereby sealing said through hole, said solid-state image sensing device being secured to said package via an adhesive."

106. Yoshino teaches that the image sensor is mounted in the package by being inserted from an inlet of said opening which has a wider area. As indicated in the below passages, Yoshino teaches that the package is assembled and "light transmitting glass plate (22)" is affixed to it, and *then* the image sensor is placed onto the inner lead of the lead frame.

"FIG. 1 is a cross-sectional view of one example of the invention. In this solid-state image pickup device, the packaging substrate (20), for example, a black ceramic substrate, is constructed by stacking ceramic molded frames (201) and (202), and the electrode leads (21) are provided in a pin-socket format disposed so as to penetrate the packaging substrate (20) above the ceramic molded frame (201). The light transmitting glass plate (22) is hermetically secured to the

ceramic molded frame (202) using black fritted glass beforehand so as to cover the tapered opening (23) of the packaging substrate (20). The solid-state image sensor (25) is placed so that the bonding pads (26) of the solid-state image sensor (25) are aligned with the electrode leads (21), and the bonding pads (26) and the electrode leads (21) aligned therewith are connected via a conductive bonding material (27), for example, indium." (Ex. 1003, p. 2).

"[N]o heating is required in the step of incorporating the solid-state image sensor (25) into the packaging substrate (20) to which the light transmitting glass plate (22) has already been hermetically bonded." (Ex. 1003, p. 2).

annotated and highlighted to show that "light transmitting glass plate (22)" covers the narrower opening. Thus, since Yoshino teaches that the image sensor is inserted ("placed" or "incorporate[ed]"), there are only two openings, and the narrower opening is covered at the time the image sensing device is inserted, Yoshino teaches that the image sensing device is inserted, Yoshino teaches that the image sensing device is inserted into the wider opening. In the below version of Fig. 1, Petitioner has highlighted the glass plate purple. The image sensor, highlighted yellow, is inserted into the wider opening of the through hole (highlighted green) of the package (highlighted blue).

108. Fig. 1 shows the bottom (wider) opening sealed by "molded resin (28)". (Ex. 1003, p. 2). As discussed in ¶ 69 above, molded resin is a material sometimes used in the fabrication of package bodies that functions here as an

adhesive. It serves here to secure the image sensor to the package, just as in the

'714 patent. It does not prevent the image sensor from being inserted into the

wider opening, since it would not be applied until after the image sensor was

inserted. It would make no sense to apply the adhesive (as it is shown in Fig. 1, on

the back side of the image sensor) before the image sensor was inserted.

109. Fig. 1 shows a cross-section of the package disclosed by Yoshino. As shown by the hatching on the cross-sectional faces of the package, such a package would extend all the way around or enclose the image sensor. This is typically the case for this type of package, in order to protect the chip. In an image sensor package, also, the packaging substrate would extend all the way around the package so that only wanted light, received through the light receiving window on

the top of the package, would strike the image sensor. If the package were open along the sides or periphery, unwanted light would strike the image sensor. This would interfere with accurate image capture.

- 110. Also, the passage cited in ¶ 106 above describes the "light transmitting glass plate (22)" as "hermetically secured". In order for the glass plate (22) to be "hermetically secured" the packaging substrate 202 would have to extend all the way around the package.

- 111. Thus, there would have been no side openings through which the image sensor could be inserted. Since the narrower (top) opening is covered by the glass plate, the image sensor could only have been inserted through the wider opening, shown as the bottom opening in Fig. 1. This is inherent in Yoshino's disclosure. If it is not inherent, it is my opinion that it is at least obvious.

- 112. Yoshino teaches the image sensor sealing the through hole, since Yoshino's Fig. 1 shows the image sensor blocking the through hole in the same manner as the '714 patent.

- 113. Finally, Yoshino discloses the image sensor being secured to said package via "molded resin (28)", as recited in the passage below. As discussed in ¶ 69 above, molded resin is a material sometimes used in the fabrication of package bodies that functions here as an adhesive.

"By supporting the solid-state image sensor (25) in the packaging

substrate (20) via a molded resin (28), a desired solid-state image pickup device is obtained." (Ex. 1003, p. 2).

114. Thus, for the foregoing reasons, I conclude that claim 1 was anticipated by Yoshino.

### XIII. Claim 6 is obvious over Yoshino in view of Izumi.

## A. Summary of opinion

115. It is my opinion that Claim 6 is obvious over Yoshino in view of Japanese Pat. App. Pub. No. S63-221667 ("Izumi") (Ex. 1017, certified translation as Ex. 1016).

### B. Izumi is prior art