## Electronic Packaging, Microelectronics, and Interconnection Dictionary

Charles A. Harper Martin B. Miller

## McGraw-Hill, Inc.

New York San Francisco Washington, D.C. Auckland Bogotá

Caracas Lisbon London Madrid Mexico City Milan

Montreal New Delhi San Juan Singapore

Sydney Tokyo Toronto

MH92

## Library of Congress Cataloging-in-Publication Data

Harper, Charles A.

Electronic packaging, microelectronics, and interconnection dictionary / Charles A. Harper, Martin B. Miller.

p. cm. — (Electronic packaging and interconnection series)

Includes index.

ISBN 0-07-026688-3

1. Electronic packaging—Dictionaries. 2. Microelectronic packaging—Dictionaries. 3. Electronic apparatus and appliances—Design and construction—Dictionaries. I. Miller, Martin B. (Martin Boniface). II. Title. III. Series.

TK7804.H34 1993

621.381'046'3---dc20

92-40712

CIP

Copyright © 1993 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1 2 3 4 5 6 7 8 9 0 DOC/DOC 9 9 8 7 6 5 4 3

ISBN 0-07-026688-3

The sponsoring editor for this book was Daniel A. Gonneau, the editing supervisor was Kimberly A. Goff, and the production supervisor was Donald F. Schmidt.

Printed and bound by R. R. Donnelley & Sons Company.

It has bee aging, mic The reaso sionals fro terials, as facturing, are quite neer to ur for a mate croelectro acronyms uation, to terdepend systems d tions to ac

This wa This dictic range of a subject ar anyone in cess the te nary inclusymbols, a a constant dictionary has ever be serve its rethis magnibols, we ver garding achat removes om conduction stripper.

nickness of a cially magnet ation.

uits included ent expressly viding for on-

oupled Device narge-Coupled

Conductance of a homoge-

ity of a moldar, nodular, or ressed as a volume (e.g.,

of the volume owder to the veight of resin

A connector ted in a panel nponent side.

nat portion of ttributed to the n, and type of Contact Resis-

mpound Moldwith thickened fibers less than ½ inch long. Supplied as rope, it molds with excellent flow and surface appearance.

Bump A small metal mound or hump that is formed on the chip or the substrate bonding pad and is used as a contact in face-bonding. It is a means of providing connections to terminal areas of a device.

Bump Contacts (1) Raised areas on a device, such as the base, emitter, and collector of a transistor chip, that are used for alloying with pads on a substrate during the mounting and interconnecting operations. (2) Contacting pads that rise substantially above the surface level of the chip. (3) Raised pads on the substrate that contact the flat land areas of the chip.

Bumped Chip A chip that has on its termination pads a bump of solder or gold used for bonding to external contacts. This allows for bonding of all leads simultaneously as opposed to one at a time, as in wire bonding. See also Gang Bonding.

Bumped TAB Tape-automated bonding (TAB) wherein the raised solder bump is attached to the tape material instead of the bump being on the chip. See also Tape-Automated Bonding.

Bumped Tape See Bumped TAB.

**Buried Channel** A transfer channel beneath the surface of the semiconductor. *See also Channel.*

Buried-Channel Charge-Coupled Device (BCCD) A charge-coupled device that confines the flow of charges to a channel lying beneath the surface of the semiconductor. See also Charge-Coupled Device.

Buried Layer (1) A distinguishable region introduced under a semiconductor circuit element, such as under the collector region of a transistor, to reduce the series collector resistance. (2) In multilayer printed wiring boards, the inner conductor layers.

Buried Resistors Thick film resistors that are located on inner layers of multilayer substrates in order to reduce conductor lengths.

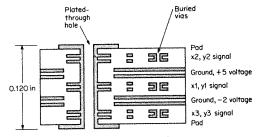

Buried Via A via that connects inner layers but does not extend to the surface of a substrate or board. Also called hidden via. See Fig. 1.

Figure 1: Buried Via

Burn-In Subjecting electronic components to elevated temperatures, normally 125°C, for an extended period of time, such as a commonly used standard of 168 hours, to stabilize their characteristics or cause failure to marginal devices.