# **ULSI** Technology

#### EDITED BY

## C. Y. Chang

Chair Professor, College of Electrical Engineering and Computer Science National Chiao Tung University Director, National Nano Device Laboratories Hsinchu, Taiwan, ROC

## S. M. Sze

UMC Chair Professor

Department of Electronics Engineering

Director, Microelectronics and Information Systems Research Center

National Chiao Tung University

Hsinchu, Taiwan, ROC

#### THE McGRAW-HILL COMPANIES, INC.

New York St. Louis San Francisco Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto

## McGraw-Hill

A Division of The McGraw-Hill Companies

#### ULSI TECHNOLOGY

Copyright ©1996 by The McGraw-Hill Companies, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

Acknowledgments begin on page 724 and appear on this page by reference.

This book is printed on acid-free paper.

234567890 DOC DOC 909876

ISBN 0-07-063062-3

This book was set in Times Roman by Publication Services, Inc.

The editors were Lynn Cox and John M. Morriss;

the production supervisor was Denise L. Puryean.

The cover was designed by Farenga Design Group.

Project supervision was done by Publication Services, Inc.

R. R. Donnelley & Sons Company was printer and binder.

Cover photo: Electron micrograph of contact holes filled with CVD tungsten plugs (see Chapter 8). The diameter is 0.25 micron. Courtesy of the National Nano Device Laboratories, National Science Council, R.O.C.

Library of Congress Catalog Card Number: 95-81366

## CONTENTS

|   | List  | of Contributors                  | xiii |

|---|-------|----------------------------------|------|

|   | Prefa | nce                              | xv   |

|   | Intro | duction                          | xvii |

| 1 | Clea  | nroom Technology                 | 1    |

|   | H. P. | Tseng and R. Jansen              |      |

|   | 1.1   | Introduction                     | 1    |

|   | 1.2   | Cleanroom Classification         | 4    |

|   | 1.3   | Cleanroom Design Concept         | 8    |

|   | 1.4   | Cleanroom Installation           | 24   |

|   | 1.5   | Cleanroom Operations             | 32   |

|   | 1.6   | Automation                       | 34   |

|   | 1.7   | Related Facility Systems         | 38   |

|   | 1.8   | Summary and Future Trends        | 54   |

|   |       | References                       | 55   |

|   |       | Problems                         | 58   |

| 2 | Wat   | fer-Cleaning Technology          | 60   |

|   |       | Chang and T. S. Chao             |      |

|   | 2.1   | Introduction                     | 60   |

|   | 2.2   | Basic Concepts of Wafer Cleaning | 60   |

|   | 2.3   | Wet-Cleaning Technology          | 92   |

|   | 2.4   | Dry-Cleaning Technology          | 93   |

|   | 2.5   | Summary and Future Trends        | 100  |

|   |       | References                       | 101  |

|   |       | Problems                         | 104  |

| 3 | Epi   | itaxy                            | 105  |

|   | P. V  | Vang                             |      |

|   | 3.1   | Introduction                     | 105  |

|   | 3.2   | Fundamental Aspects of Epitaxy   | 107  |

|   | 3.3   | Conventional Si Epitaxy          | 115  |

|   | 3.4   | Low-Temperature Epitaxy of Si    | 125  |

|   | 3.5   |                                  | 131  |

|   |       |                                  | vii  |

|   | 3.6  | Characterization of Epitaxial Films                                                                                    | 135 |

|---|------|------------------------------------------------------------------------------------------------------------------------|-----|

|   | 3.7  | Summary and Future Trends                                                                                              | 138 |

|   |      | References                                                                                                             | 139 |

|   |      | Problems                                                                                                               | 143 |

| 4 | Cor  | nventional and Rapid Thermal Processes                                                                                 | 144 |

|   | R. B | . Fair                                                                                                                 |     |

|   | 4.1  | Introduction                                                                                                           | 144 |

|   | 4.2  | Requirements for Thermal Processes                                                                                     | 151 |

|   | 4.3  | Rapid Thermal Processing                                                                                               | 159 |

|   | 4.4  | Summary and Future Trends                                                                                              | 196 |

|   |      | References                                                                                                             | 198 |

|   |      | Problems                                                                                                               | 203 |

| 5 |      | lectric and Polysilicon Film Deposition                                                                                | 205 |

|   |      | C. Cheng                                                                                                               | 205 |

|   |      | Introduction                                                                                                           | 205 |

|   | 5.2  | Deposition Processes                                                                                                   | 205 |

|   | 5.3  | Atmospheric-Pressure Chemical-Vapor-Deposited (APCVD) and Low-Pressure Chemical-Vapor-Deposited (LPCVD) Silicon Oxides | 215 |

|   | 5.4  |                                                                                                                        | 225 |

|   | 5.5  | LPCVD Polysilicon Films                                                                                                | 226 |

|   |      | Plasma-Assisted Depositions                                                                                            | 240 |

|   |      | Other Deposition Methods                                                                                               | 247 |

|   |      | Applications of Deposited Polysilicon, Silicon Oxide, and Silicon Nitride Films                                        | 257 |

|   | 5.9  | Summary and Future Trends                                                                                              | 262 |

|   |      | References                                                                                                             | 264 |

|   |      | Problems                                                                                                               | 268 |

| 6 | Lit  | hography                                                                                                               | 270 |

|   |      | Nakamura                                                                                                               |     |

|   | 6.1  | Introduction                                                                                                           | 270 |

|   | 6.2  | Optical Lithography                                                                                                    | 272 |

|   | 6.3  | Electron Lithography                                                                                                   | 295 |

|   | 6.4  | X-Ray Lithography                                                                                                      | 312 |

|   | 6.5  | Ion Lithography                                                                                                        | 320 |

|   |          |                                                         | Contents ix |

|---|----------|---------------------------------------------------------|-------------|

|   | 6.6      | Summary and Future Trends                               | 323         |

|   | -5/60    | References                                              | 324         |

|   |          | Problems                                                | 327         |

| 7 | Etc      | hing                                                    | 329         |

|   | Y, $J$ . | T. Lii                                                  |             |

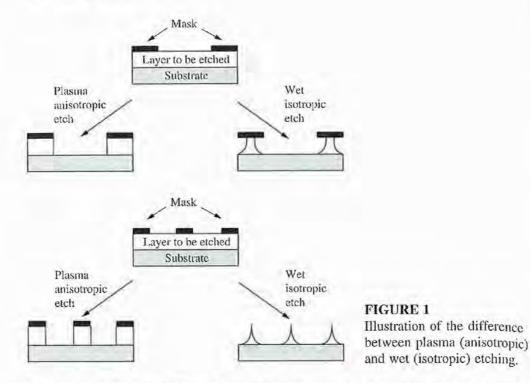

|   | 7.1      | Introduction                                            | 329         |

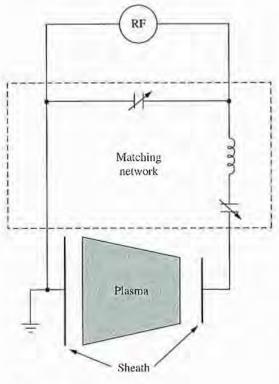

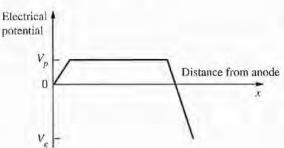

|   | 7.2      | Low-Pressure Gas Discharge                              | 330         |

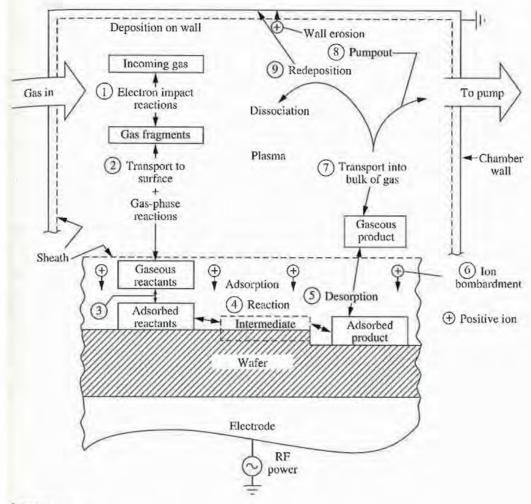

|   | 7.3      | Etch Mechanisms, Selectivity, and Profile Control       | 334         |

|   | 7.4      | Reactive Plasma Etching Techniques and Equipment        | nt 343      |

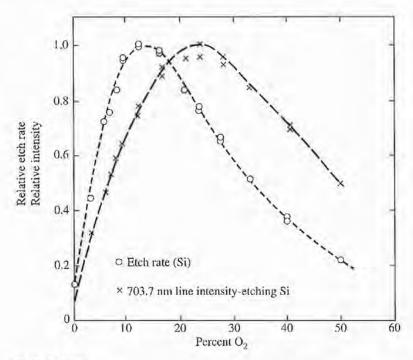

|   | 7.5      | Plasma Processing Processes                             | 353         |

|   | 7.6      | Diagnostics, End Point Control, and Damage              | 362         |

|   | 7.7      | Wet Chemical Etching                                    | 364         |

|   | 7.8      | Summary and Future Trends                               | 366         |

|   |          | References                                              | 367         |

|   |          | Problems                                                | 369         |

| 8 | Me       | tallization                                             | 371         |

|   | R. L     | iu                                                      |             |

|   | 8.1      | Introduction                                            | 371         |

|   | 8.2      | Metal Deposition Techniques                             | 379         |

|   | 8.3      | Silicide Process                                        | 395         |

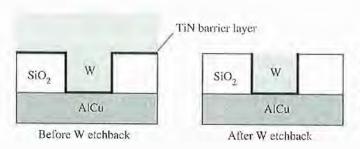

|   | 8.4      | CVD Tungsten Plug and Other Plug Processes              | 406         |

|   | 8.5      | Multilevel Metallization                                | 412         |

|   | 8.6      | Metallization Reliability                               | 448         |

|   | 8.7      | Summary and Future Trends                               | 451         |

|   |          | References                                              | 457         |

|   |          | Problems                                                | 468         |

| 9 | Pro      | ocess Integration                                       | 472         |

|   | C. 1     | Y. Lu and W. Y. Lee                                     |             |

|   | 9.1      | Introduction                                            | 472         |

|   | 9,2      | Basic Process Modules and Device Considerations<br>ULSI | for 473     |

|   | 9.3      | CMOS Technology                                         | 489         |

|   | 9.4      |                                                         | 495         |

|   | 9.5      |                                                         | 502         |

|   |          | MOS Memory Technology                                   | 510         |

## x Contents

|    | 9.7   | Process Integration Considerations in ULSI Fabrication<br>Technology | 519 |

|----|-------|----------------------------------------------------------------------|-----|

|    | 9.8   | Summary and Future Trends                                            | 523 |

|    | 7.0   | References                                                           | 525 |

|    |       | Problems                                                             | 529 |

| 10 | Asse  | mbly and Packaging                                                   | 530 |

|    |       | chikawa                                                              |     |

|    | 10.1  | Introduction                                                         | 530 |

|    | 10.2  | Package Types                                                        | 531 |

|    |       | ULSI Assembly Technologies                                           | 540 |

|    | 10.4  | Package Fabrication Technologies                                     | 552 |

|    | 10.5  | Package Design Considerations                                        | 557 |

|    | 10.6  | Special Package Considerations                                       | 569 |

|    | 10.7  |                                                                      | 573 |

|    |       | Summary and Future Trends                                            | 580 |

|    |       | References                                                           | 583 |

|    |       | Problems                                                             | 585 |

| 11 | Waf   | er Fab Manufacturing Technology                                      | 587 |

|    | T. F. | Shao and F. C. Wang                                                  |     |

|    | 11.1  | What Is Manufacturing?                                               | 587 |

|    | 11.2  | Wafer Fab Manufacturing Considerations                               | 593 |

|    | 11.3  | Manufacturing Start-Up Technology                                    | 609 |

|    | 11.4  | Volume Ramp-Up Considerations                                        | 639 |

|    | 11.5  | Continuous Improvement                                               | 646 |

|    | 11.6  | Summary and Future Trends                                            | 652 |

|    |       | References                                                           | 653 |

|    |       | Problems                                                             | 655 |

| 12 | Reli  | ability                                                              | 656 |

|    | J. T. | Yue                                                                  |     |

|    | 12,1  | Introduction                                                         | 656 |

|    | 12,2  | Hot Carrier Injection                                                | 657 |

|    | 12.3  | Electromigration                                                     | 663 |

|    | 12.4  | Stress Migration                                                     | 674 |

|    | 12.5  | Oxide Breakdown                                                      | 679 |

|    | 12.6  | Effect of Scaling on Device Reliability                              | 684 |

|       |                                       | Contents | xi  |

|-------|---------------------------------------|----------|-----|

| 12.7  | Relations between DC and AC Lifetimes | 6        | 586 |

| 12.8  | Some Recent ULSI Reliability Concerns | (        | 590 |

| 12.9  | Mathematics of Failure Distribution   | (        | 592 |

| 12.10 | Summary and Future Trends             | (        | 696 |

|       | References                            | (        | 697 |

|       | Problems                              |          | 703 |

| Appe  | endixes                               |          | 705 |

| A. 1  | Properties of Si at 300 K             | •        | 705 |

| B. 1  | List of Symbols                       |          | 707 |

| C.    | International System of Units         | 1        | 709 |

| D.    | Physical Constants                    |          | 710 |

| Inde  | v.                                    |          | 711 |

#### GROWTH OF THE INDUSTRY

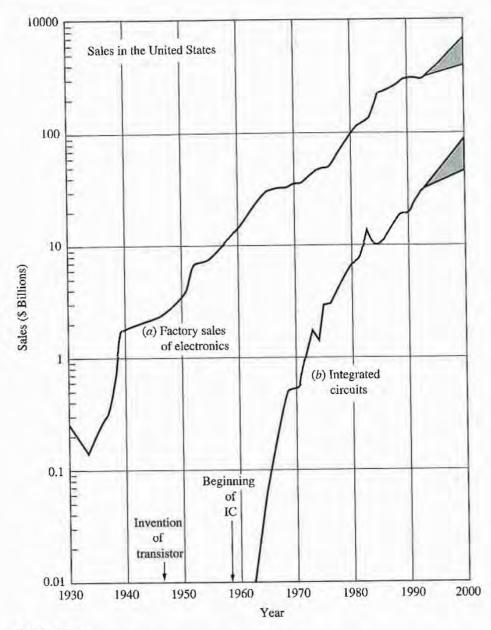

The United States has the largest electronics industry in the world, with a global market share of over 40%. Since 1958, the beginning of the integrated-circuit (IC) era, the factory sales of electronic products have increased by about thirty times [see Fig. 1, curve  $(a)^{1.2}$ ]. Electronics sales, which were \$303 billion in 1993, are projected to increase at an average annual rate of 8.5% and reach a half-trillion-dollar level by the year 2000. In the same period, the IC market itself has increased at an even higher rate [see Fig. 1, curve  $(b)^{1.2}$ ].\* IC sales in the United States were \$28 billion in 1993 and are expected to grow by 13% annually, reaching \$65 billion by the year 2000. The main impetuses for such phenomenal market growth are the intrinsic pervasiveness of electronic products and the continued technological breakthroughs in integrated circuits.

The world markets of electronics and semiconductor industries will grow at comparable rates. Figure 2 shows the 1993 world electronics industry with a global sales volume of \$679.7 billion. Also shown are the market shares of the six major electronics applications: computer and peripherals equipment at 32.3%, consumer electronics at 21.2%, telecommunication equipment at 16.5%, industrial electronics at 14.3%, defense and space at 11.5%, and transportation at 4.2%. By the year 2000, the world electronics industry is projected to reach \$1200 billion, which will surpass the automobile, chemical, and steel industries in sales volume.

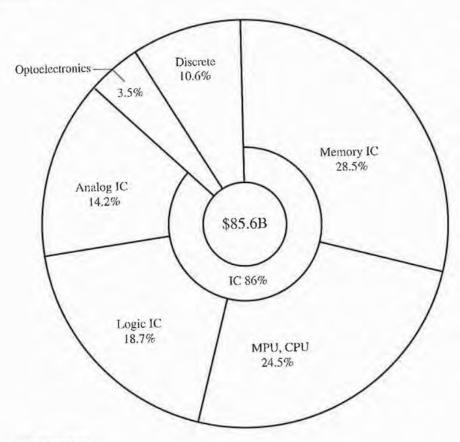

Figure 3 shows the 1993 world semiconductor industry, with total sales of \$85.6 billion. Only 14% is related to optoelectronics and discrete semiconductor devices. IC sales constitute 86% of the total volume, with the largest segment being memory ICs, followed by microprocessor and microcontroller units, logic ICs, and analog ICs. In 2000, the semiconductor industry is projected to reach \$200 billion, with over \$170 billion in integrated circuits.

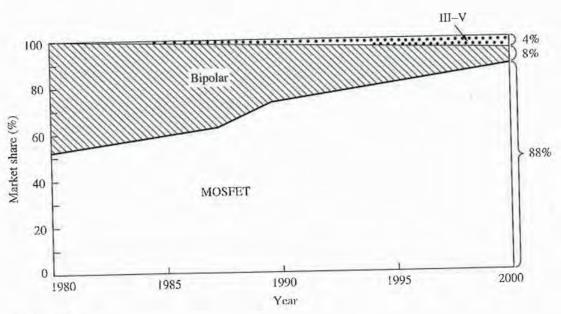

Figure 4 shows the market shares of the three major IC groups: MOSFET, bipolar transistor, and ICs made from III–V compound semiconductors.<sup>3</sup> At the beginning of the IC era, the IC market was broadly based on bipolar transistors. However, because of the advantages in device miniaturization, low power consumption, and high yield, sales volume of MOS-based ICs has increased steadily and in 1993 amounted to 75% of the total IC market. By the year 2000, MOS ICs will capture the largest market share (88%) of all ICs sold. This book, therefore, emphasizes MOS-related ULSI technology.

<sup>\*</sup>There were only two years in which the growths were negative: in 1974, due to the Middle East oil embargo, and in 1985, due to overproduction of personal computers.

FIGURE 1

(a) Factory sales of electronics in the United States for the 64 years between 1930 and 1993 and projected to 2000. (b) Integrated circuit market in the United States for 32 years between 1962 and 1993 and projected to 2000. (After Refs. 1 and 2.)

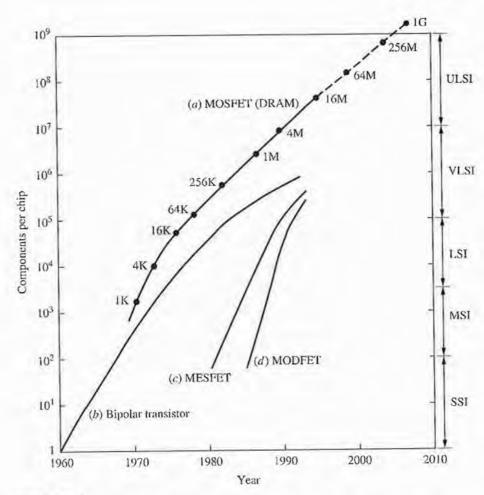

## DEVICE MINIATURIZATION

Figure 5, curve (a), shows the rapid growth in the number of components per MOS memory chip.<sup>4,5</sup> Note that the MOS IC complexity has advanced from small-scale integration (SSI), to medium-scale integration (MSI), to large-scale integration (LSI), to very-large-scale integration (VLSI), and finally to ultralarge-scale integration (ULSI), which has 10<sup>7</sup> or more components per chip. We note that since 1975 the growth has been maintained at a rate of about 40% annually; in other words, the

FIGURE 2

1993 world electronics industry. (After Dataquest, 1994.)

number of components has doubled every two years. At this rate, over 100 million components per chip will be available before the year 2000; in the early 21st century we will move into the gigabit range, with IC chips having more than one billion components. Also shown in Fig. 5 is the growth of the number of components for bipolar, MESFET, and MODFET ICs. They are about two orders of magnitude lower in complexity compared with MOS-based ICs.

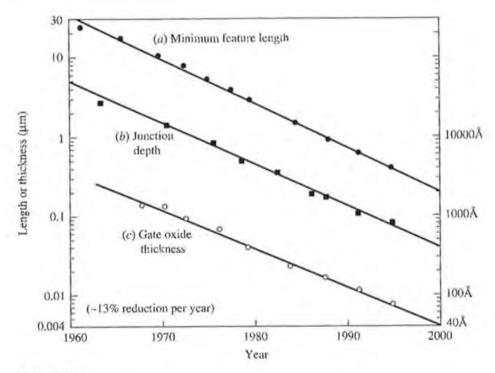

The most important factor in achieving the ULSI complexity is the continued reduction of the minimum device-feature length [see Fig. 6, curve (a)]. Since 1960, the annual rate of reduction has been 13%, which corresponds to a reduction by a factor of two every six years. At this rate, the minimum feature length will shrink from its present length of  $0.5 \, \mu m$  to  $0.2 \, \mu m$  in the year 2000. The junction depth of the source and drain junctions, and the gate oxide thickness are also being reduced at a similar rate as shown in curves (b) and (c) of Fig. 6, respectively.

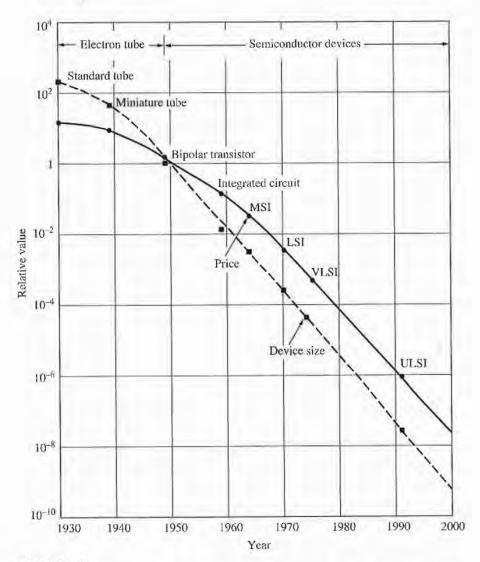

The reduction of the device feature length and related dimensions has resulted in reduced overall device size and unit price per function. Figure 7 shows the relative price and size reductions.<sup>8</sup> In the past fifty years, prices have gone down by 100 million times, and the size has been reduced by a factor of one billion. By 2000 the price per bit is expected to be less than 0.1 millicent for a 64-megabit memory chip. Similar price reductions are expected for logic ICs. Additional benefits from device

## xx Introduction

FIGURE 3

1993 world semiconductor industry. (After Dataquest, 1994.)

FIGURE 4

World IC market (1980–2000). (After Zdebel, Ref.3.)

FIGURE 5

(a) Exponential growth of the number of components per MOS IC chip. (After Moore, Ref. 4, and Myers, Ref. 5.) (b), (c). and (d) Components per chip versus year for bipolar, MESFET, and MODFET ICs, respectively.

miniaturization include improvement of device speed (which varies inversely with the device feature length) and reduction of power consumption (which varies approximately with the square of the feature length). Higher speeds lead to expanded IC functional throughput rates, so that future ICs can perform data processing, numerical computation, and signal conditioning at 100 and higher gigabit-per-second rates. Reduced power consumption results in lowering the energy required for each switching operation. Since 1960 the required energy, called the *power-delay product*, has decreased by six orders of magnitude. 10

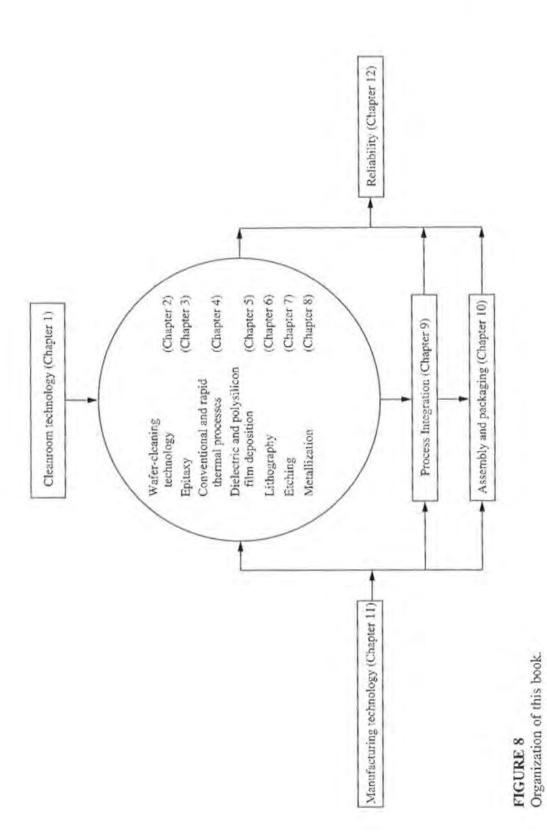

## ORGANIZATION OF THE BOOK

Figure 8 shows how the 12 chapters of this book are organized. Chapter 1 considers cleanroom technology. The continued miniaturization in ULSI devices implies more

FIGURE 6

Exponential decrease of (a) minimum feature length, (b) junction depth, and (c) gate oxide thickness of MOSFET.

stringent requirements with respect to contamination control. Without an ultraclean processing environment, ULSI circuits simply cannot be realized.<sup>11</sup>

ULSI technology is synonymous with *silicon* ULSI technology. The unique combination of silicon's adequate bandgap, stable oxide, and abundance in nature ensures that in the foresecable future no other semiconductor will seriously challenge its preeminent position in ULSI applications. Some important properties of silicon are listed in Appendix A.

Once the silicon wafers are in the cleanroom, we enter into the wafer-processing sequence, described in Chapters 2 through 8 and depicted in the wafer-shaped central circle of Fig. 8. Each of these chapters considers a specific process step. Of course, many processing steps are repeated many times in IC fabrication; for example, lithography and etching steps may be repeated 10 to 20 times. In ULSI technology the wafer-cleaning technology is as important as the cleanroom technology. Without a contamination-free wafer surface, the ICs will suffer from low yield and poor reliability. Because of limitations on the total length of the book, many classic topics, such as crystal growth, oxidation, diffusion, and ion implantation, are only briefly mentioned. The reader may consult textbooks on VLSI technology for details. 12

The individual processing steps described in Chapters 2 through 8 are combined in Chapter 9 to form devices and integrated circuits. Chapter 9 considers the fundamental building process modules and four important IC families: CMOS (complementary MOSFET), bipolar ICs, BiCMOS (a combination of bipolar and CMOS),

FIGURE 7

Price and size reduction of active electronic compents. (After Shoda, Ref. 8.)

and MOS memory ICs. After the completely processed wafers are tested, those chips that pass the tests are ready to be packaged. Chapter 10 describes the assembly and packaging of ULSI chips. Chapter 11 considers the manufacturing technology, that is, the strategy and logistics to implement various technologies to produce ULSI chips that meet customers' specifications in a timely fashion and to generate adequate return on investment for the IC manufacturer. Chapter 12 describes a multitude of reliability issues related to ULSI processes. As device dimensions move to the sub-half-micron and sub-quarter-micron regime, ULSI processing becomes more automated, resulting in tighter control of all processing parameters. At every step of production, from wafer cleaning to device packaging, numerous requirements are being imposed to improve the device performance and reliability.

To keep the notation simple in this book, we sometimes found it necessary to use a symbol more than once, with different meanings. However, within each chapter a

xxiv

symbol has only one meaning and is defined the first time it appears. Many symbols do have the same or similar meanings consistently throughout this book; they are summarized in Appendix B.\*

ULSI technology is presently moving at a rapid pace. The number of ULSI publications has doubled every year since 1990, the beginning of the ULSI era. Many topics, such as lithography, rapid thermal processing, and metallization, are still under intensive study. Their ultimate capabilities are not fully understood. The material presented in this book is intended to serve as a foundation. The references listed at the end of each chapter can supply more information.

#### REFERENCES

- 1. 1994 Electronic Market Data Book, Electronic Industries Association, Washington, D.C., 1994.

- 2. 1994 Annual Report of Semiconductor Industry, Industrial Technology Research Institute, Hsinchu, Taiwan, ROC, 1994.

- 3. P. J. Zdebel, "Current Status of High Performance Silicon Bipolar Technology," 14th Annual IEEE GaAs IC Symp. Tech. Digest, 15 (1992).

- 4. G. Moore, "VLSI, What Does the Future Hold," Electron Aust., 42, 14 (1980).

- 5. W. Myers, "The Drive to the Year 2000," IEEE Micro, 11, 10 (1991).

- 6. P. K. Chatterjee and G. B. Larrabee, "Gigabit Age Microelectronics and Their Manufacture," *IEEE Trans. VLSI Syst.***1**, 7 (1993).

- K. Mori, H. Yamada, and S. Takizawa, "System on Chip Age," Proceedings of the International Symposium on VLSI Technology, Systems, and Applications, k15 (1993).

- 8. K. Shoda, "Home Electronics in the 1990s," Proceedings of the International Symposium on VLSI Technology, Systems, and Applications, 1(1991).

- H. Komiya, M. Yoshimoto, and H. Ishikura, "Future Technological and Economic Prospects for VLSI," *IEICE Trans. Electron.* E76-C, 1555 (1993).

- R. W. Keyes, "Limitations of Small Devices and Large Systems," in N. G. Einspruch, Ed., VLSI Electronics, Academic, New York, 1981, Vol. 1, p. 186.

- T. Ohmi, "ULSI Reliability through Ultraclean Processing," Proc. IEEE, 81, 716 (1993).

- For example, S. M. Sze, Ed., VLSI Technology, 2nd Ed., McGraw-Hill, New York, 1988.

<sup>\*</sup>Also included are the International System of Units (Appendix C) and Physical Constants (Appendix D).

## Lithography

K. Nakamura

#### 6.1 INTRODUCTION

Lithography is a kind of art made by impressing, in turn, several flat embossed slabs, each covered with greasy ink of a particular color, onto a piece of paper. The various colors or levels must be accurately aligned with respect to one another within some registration tolerance. Many "originals" can be made from the same slabs as long as the quality remains adequately high.

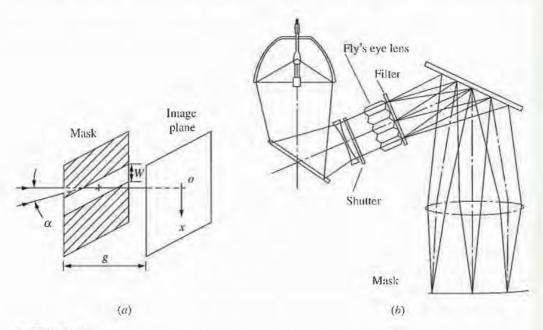

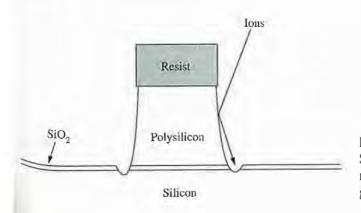

Several methods can be used to make ULSI circuit patterns on wafers, as shown in Fig. 1a. The most common process is to make the master photomask using an electron beam exposure system and replicating its image by optical printers, as shown in Fig. 1b. The exposing radiation is transmitted through the "clear" part of a mask. The opaque part of the circuit pattern blocks some of the radiation. The resist, which is sensitive to the radiation and has resistance to the etching, is coated on the wafer surface. The mask is aligned within the required tolerance on the wafer; then radiation is applied through the mask, the resist image is developed, and the layer underneath the resist is etched.

Therefore, lithography for integrated circuit manufacturing is analogous to the lithography of the art world. The slabs correspond to masks for the various circuit levels. The press corresponds to the exposure system, which not only exposes each level but also aligns it to a completed level. The ink may be compared to either the exposing radiation or the radiation-sensitive resist; the paper can represent the wafer into which the pattern will be etched, using the resist as a stencil.

Lithography is the key technology in semiconductor manufacturing, because it is used repeatedly in a process sequence that depends on the device design. It determines the device dimensions, which affect not only the device's quality but also its product amount and manufacturing cost.

FIGURE 1 Device lithography generalization. (a) Lithographic process for ULSI. (b) Optical replication process.

#### 6.2 OPTICAL LITHOGRAPHY

Optical lithography comprises the formation of images with visible or ultraviolet radiation in a photoresist using proximity or projection printing. Two methods are available to make masks for optical lithography: electron beam exposure and laser beam scanning. These are described in the next section. In the 1970s, the major technology was the combination of a negative resist and proximity printing. At present the most common method is the combination of a positive resist and a stepper. However, proximity printing is still used because of its convenience and low cost.

Table 1 lists examples of commercially available optical printers<sup>1</sup> designed to manufacture ULSI circuits. These machines are classified into three groups: proximity, reflective projection, and refractive projection. The key parameters such as numerical aperture (NA), depth of focus (DOF), resolution (usable linewidth), overlay accuracy, and throughput are also listed.

The most advanced ULSI has a minimum feature size of 0.3  $\mu m$  to 0.4  $\mu m$ , which has been reported by several organizations in 64-Mbit dynamic random access memories (DRAMs). It is believed that the linewidth limit of optical lithography lies near 0.2  $\mu m$  using phase-shifting masks combined with a high numerical aperture projector and a short-wavelength light source. The performances of the machines listed in Table 1 are very close to the resolution limit of optical lithography.

#### 6.2.1 Contact and Proximity Printing

Contact and proximity printings are relatively simple because they do not have any means of image formation between masks and wafers. A typical contact or proximity mask aligner consists of a light source, a condenser, a filter, a mirror, a shutter, the wafer stage, and the alignment microscope. In contact printing, a photomask is pressed against the resist-covered wafer, with pressures typically in the range of 0.05 atm to 0.3 atm, and is exposed by light with a wavelength near 400 nm. Very high resolution of less than 0.5 µm linewidth is possible, but because of spatial nonuniformity of the contact, resolution may vary considerably across the wafer. To provide better contact over the whole wafer, a thin (0.2 mm) flexible mask has been used; 0.2-µm space patterns have been formed by using 3-µm-thick PMMA (poly-methyl methacrylate) resist and 200 to 260 nm radiation.<sup>2</sup> Quartz or Al<sub>2</sub>O<sub>3</sub> mask substrates must be used to pass these shorter wavelengths, since the usual borosilicate glass strongly absorbs wavelengths less than 300 nm.

Contact printing produces defects in both the mask and the wafer while the two are in contact and as they are separated from each other, so that the mask, whether thick or thin, may have to be replaced after a short period of use. Nevertheless, contact printing is still widely used. It is the most convenient way to get high resolution. Strictly speaking, contact printing is never actually practiced, because of the difficulty of uniform contact. When a typical mask and wafer are brought into hard contact, the nonuniform gap can be as large as 15  $\mu$ m because of unevenness of the surfaces. Besides that, the thickness of the resist between the mask and the wafer cannot be neglected for features of less than 1  $\mu$ m.

TABLE 1 Commercially available optical printers<sup>1</sup>

| Category          | Model         | Maker     | NA+       | DOF† | Field size (mm)                   | Usable<br>linewidth<br>(µ.m) | Overlay<br>accuracy<br>(µm) | Throughput/6"-hr |

|-------------------|---------------|-----------|-----------|------|-----------------------------------|------------------------------|-----------------------------|------------------|

| Contact/proximity | PLA600        | Canon     |           |      | 160                               | -                            | 0.5                         | 120              |

|                   | 3HRP          | JBA       |           |      |                                   | 0.25                         | 0.5                         | 45/10"           |

|                   | 0009-0        | Quintel   |           |      |                                   | 0.25                         |                             | 09               |

|                   | MA150M        | Karl Suss |           |      |                                   | 0.5                          | 0.5                         | 09               |

| Catadioptric/4×   | Micrascan IIi | SVG       | 0.5       | 1.2  | 22 × 32.5                         | 0.5                          | 0.07                        | 51/8"            |

| /1×               | Micralign 700 | SVG       | 0.167     | 9    | $150 \times 135$                  | 1.0-1.2                      | 0.25                        | 100              |

| /1×               | 2000gh        | Ultratech | 0.24-0.40 | 2-3  | $18 \times 18 - 39 \times 11$     | 0.8-1.0                      |                             | 78               |

| I-line stepper    | PAS5500/100   | ASM       | 9.0       | 1    | $22 \times 27.6$                  | 0.4                          | 0.07                        | 88               |

|                   | XLS7500/29    | GCA       | 0.55      | 1.1  | $21 \times 21$                    | 0.5                          | 60.0                        | 70               |

|                   | NSR2005i9C    | Nikon     |           |      | $21.2 \times 22.8/18 \times 25.2$ | 0.45                         | 0.1                         | 47/8"            |

|                   | FPA2500i3     | Canon     | 9.0       | 1    | $20 \times 20$                    | 0.4                          | 0.12                        | 62               |

| KrF stepper       | PASS500/90    | ASM       | 0.5       | -    | $21 \times 27.7$                  | 0.35                         | 0.07                        | 80               |

|                   | XLS7800/31    | GCA       | 0.53      | 12   | $22 \times 22$                    | 0.35                         | 0.07                        | 72               |

|                   | ISR2005EXBA   | Nikon     |           |      | $21.2 \times 21.2/16 \times 25.2$ | 0.4                          | 0.1                         | 34/8"            |

|                   | FPA3000EX1    | Canon     | 0.45      | -    | 20×20                             | 0.3                          | 0.1                         | 99               |

+NA - numerical aperture DOF - depth of focus

Masks used for proximity printing have the advantage of longer life because there is no contact between the mask and the wafer. Typical separations between mask and wafer are in the range of 20 to 50  $\mu m$ . Resolution is not so good as in contact printing or projection printing. Commercial machines can select the mode automatically and switch to either contact or proximity printing.

Figure 2a shows proximity printing schematically with a slit of width W, illuminated by a monochromatic source, separated from a parallel image plane (wafer) by a gap g. We assume that g and W are larger than the wavelength  $\lambda$  of the imaging light and that  $\lambda \ll g < W^2/\lambda$ —the region of Fresnel diffraction. In this case, the diffraction that forms the image of the slit is a function only of the particular combination of  $\lambda$ , W, and g, which we call the parameter Q, where

$$Q = W \sqrt{2/g\lambda} \tag{6.1}$$

This parameter can be considered as a normalized slit width. The lower limit of the nearfield diffraction region is at  $Q=\sqrt{2}$  from Eq. (6.1), or  $g=(W^2/\lambda)(2/Q^2)< W^2/\lambda$ . Thus, the resolution, W in Eq. (6.1), becomes better at smaller gaps and shorter wavelengths. The resist image heights, which for practical purposes are converted to resist thickness and mask-wafer gap, have been measured as a function of linewidth, wavelength, and intensity tolerance.<sup>3</sup> The optimum image heights of 0.25- $\mu$ m and 0.5- $\mu$ m patterns are 0.9  $\mu$ m and 3.2  $\mu$ m, respectively, in the case of a deep UV (wavelength less than about 200 nm) light source with  $\pm 5\%$  intensity tolerance.

Another parameter is the divergence of the illuminating beam as a result of the size of the light source. One effect is to smooth out the undulations in the image intensity profile, and the other is to produce a greater linewidth variation as the mask-to-wafer distance varies. The apparent source size of the illumination system must

FIGURE 2 Schematic illustration of a proximity printer and illumination system. (a) Proximity printing schematic. (b) Illumination system of the Canon PLA600.

FIGURE 3 Spectrum of a high-pressure mercury lamp.

be large enough to give a value of  $\alpha$  (Fig. 2) that allows the smallest features to be printed, typically, a few degrees. The mercury arc lamp used as the source<sup>5</sup> is too small to yield the required  $\alpha$ . The illumination is telecentric or normally incident at the mask to prevent runout (magnification) error similar to that in x-ray lithography. The optical system must also minimize nonuniformity of the intensity across the field. The illumination system illustrated in Fig. 2b attains  $\pm 3\%$  uniformity across a 6-inch wafer, as well as a large enough  $\alpha$  and normal incidence. With a Hg arc source, the strong lines at 436 nm, 405 nm, and 365 nm provide the exposure flux shown in Fig. 3. The same printer is available with a Xe-Hg source for enhanced output in the 200-300 nm spectral region.

Commercially available machines are listed in the first group in Table 1.

## 6.2,2 Projection Printing

Projection printing offers higher resolution than proximity printing. It has a larger separation between the mask and the wafer because of its image formation system. According to Rayleigh's criterion, the resolution W of the optical systems and the depth of focus (DOF) are given in the following equations, where the numerical aperture NA =  $n \sin \alpha$ , n is the refractive index = unity for air,  $2\alpha$  is the solid angle of the ray reaching the imaging point from the objective lens, and  $\lambda$  is the wavelength:6

$$W = 0.6\lambda/NA \tag{6.2}$$

$$DOF = \pm \lambda/2(NA)^2$$

(6.3)

Modern projection printers employ diffraction-limited optics, which means that the design and fabrication of the optical elements are not a source of optical problems. Accordingly, the image characteristics are dominated by diffraction effects associated with the finite apertures in the condenser and with projection optics rather than by aberrations. When monochromatic light from a very small point is imaged by a diffraction-limited lens, the image consists of diffraction rings of light surrounding a central bright spot called the *Airy disc*. The diameter of the pattern is  $1.2\lambda/NA$ .

It is very useful to apply a modulation transfer function (MTF) to characterize the resolution capability of projection printers and proximity printers as well. We consider the mask pattern as consisting of a periodic grid (line and space) with equal linewidths b. Light intensities in the center of dark lines and of bright lines are assigned as  $I_{\min}$  and  $I_{\max}$ , respectively. Modulation is defined as

$$M = \frac{I_{\text{max}} - I_{\text{min}}}{I_{\text{max}} + I_{\text{min}}} \tag{6.4}$$

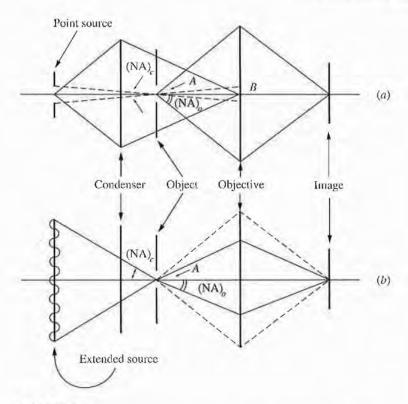

The MTF is the ratio of the modulation in the image plane (wafer) to that in the object plane (mask). It is a function of the spatial frequency ( $\nu=1/2b$ ) of the mask and the NA. The shape of the MTF, related to the spatial frequency curve, depends on the coherence of the illumination system.<sup>7</sup> The degree of coherence is defined by  $\sigma=(NA)_c/(NA)_o$ , where  $(NA)_c$  is the numerical aperture of the condenser and  $(NA)_o$  is the numerical aperture of the objective as shown in Fig. 4. In the coherent system, Fig. 4a, an object at point A is illuminated by only a narrow angle. Hence, all the light diffracted by A is coherent in amplitude at the image plane. In Fig. 4b, A is illuminated by rays from all portions of the extended incoherent source. Each ray is diffracted by the object A and forms an image in the image plane.

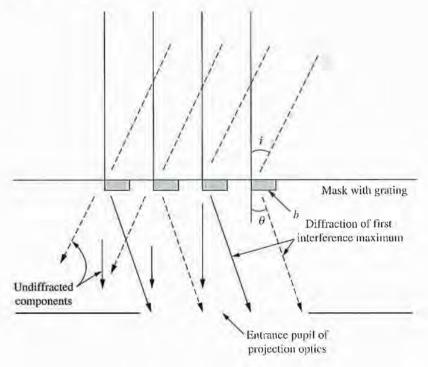

In Fig. 5, the solid lines show a plane wave front  $[\sigma = (NA)_c/(NA)_o \rightarrow 0]$  incident normal to the mask, which contains a grating pattern with b width lines and spaces (spatial frequency  $\nu = 1/2b$ ). The undiffracted component of light emerging from the mask contains no information about  $\nu$ . This information is contained only in the diffracted light. The direction of the first diffraction peak is given by the grating formula  $2b \sin \theta = \lambda$ , so that  $\nu = \sin \theta/\lambda$ . If the light diffracted to direction  $\theta$  is to reach the image plane,  $\theta \approx \alpha$  where NA =  $\sin \alpha$ . Therefore, the highest grating frequency that can be imaged by an optical system with coherent illumination becomes the result of Eq. (6.5).

For incoherent illumination (shown by dotted lines in Fig. 5), incident at a general angle i, the direction of the first maximum is given by  $2b(\sin i + \sin \theta) = \lambda$ . For both the undiffracted beam and the first diffraction peak to reach the image plane, i and  $\theta$  both  $\leq \alpha$ . Therefore,  $2b \geq \lambda/2 \sin \alpha$  and  $\nu_{\text{max}} = 2b = 2\text{NA}/\lambda$ . Consequently,  $\nu_{\text{max}}$  (incoherent) =  $2\nu_{\text{max}}$  (coherent). In modern printers the illumination is intermediate between the coherent and the incoherent limit.

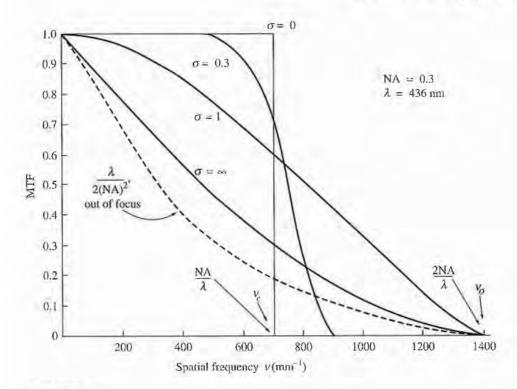

The curve for MTF  $(H(\nu))$  vs. spatial frequency is shown in Fig. 6 and is described as 5

$$\nu_{\text{max}} = \text{NA}/\lambda$$

(coherent) (6.5)

FIGURE 4

Coherent and incoherent illumination of projection printers. (After King and Goldrick, Ref. 7.) (a) Coherent system. (b) Incoherent system.

$$H(\nu) = \frac{2}{\pi} [\cos^{-1}(\nu/\nu_{\text{max}}) - \nu/\nu_{\text{max}} \sqrt{1 - (\nu/\nu_{\text{max}})^2}] \qquad \text{(incoherent)} \quad (6.6)$$

where  $\nu_{\text{max}} = 2\text{NA}/\lambda$

Figure 6 shows the modulation of the image intensity versus the spatial frequency for different values of coherence  $\sigma$  with a 0.3 NA lens. Note that the MTF of a fully coherent optical system has a spatial frequency cutoff that is half that of an incoherent system as explained in Eq. (6.5) and Eq. (6.6). Partially coherent illumination has a higher MTF in the region of  $\nu$  larger than  $\frac{1}{2}\nu_0$ . The useful range, MTF > 0.6, is extended to higher spatial frequencies; edge gradients in the image become steeper, and the image is somewhat less sensitive to focusing.

The focus error is a simple but important aberration. The error is a displacement of best focus away from its intended position. In Fig. 6, the dashed curve shows the effect of a displacement of the image plane or wafer from the focal plane by one Rayleigh unit  $w = \lambda/2(NA)^2$ , corresponding to a phase error of  $\pi/2$  at the edge of the pupil.

It was once believed that a high NA is always better. However, in the submicrometer region there is an optimum NA if a resolution requirement and the imaging wavelength are given. 10 If the NA is too low, the resolution cannot be achieved, but if the NA is too high, the DOF, which is inversely proportional to (NA)2, becomes

FIGURE 5

Diffraction of coherent and incoherent light by a grating pattern. (After Cuthbert, Ref. 8.)

unacceptable. There is an optimum NA at which the DOF is maximum. The normalization of the resolution W is given by

$$k_1 = W \frac{\text{NA}}{\lambda} \tag{6.7}$$

where  $k_1$  is usually known as Rayleigh's coefficient for resolution but is now redefined as the normalized resolution. The normalized DOF is given by

$$k_2 = \Delta Z \frac{(\text{NA})^2}{\lambda} \tag{6.8}$$

where  $\Delta Z$  is the physical axial displacement from the focal plane, and  $k_2$ , which is usually known as Rayleigh's coefficient for DOF, is now redefined as the normalized DOF.

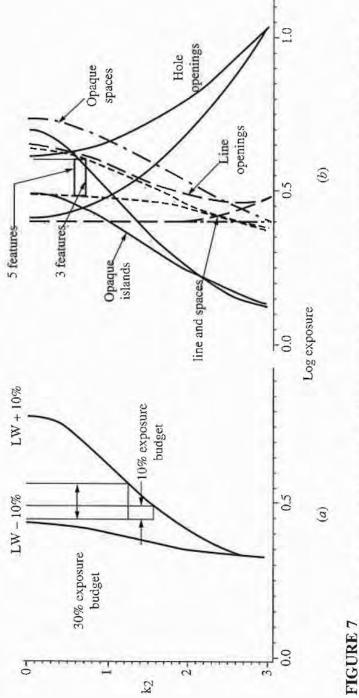

With normalized resolution and defocus, the lithographic imaging behavior of a given feature and illumination can be universally plotted in the exposure-defocus (E-D) space in the form of constant linewidth contours. The exposure dosage required to keep the image linewidth constant at each defocal plane is evaluated to form contours. This set of contours, which is the E-D tree of the particular feature and illumination condition, is universally applicable for all  $W-\lambda$ -NA combinations leading to an identical  $k_1$ . The DOF is defined as the total amount of defocus allowed without violating a given linewidth tolerance. Typically, a  $\pm 10\%$  tolerance is

FIGURE 6 Comparison of MTFs for different optical conditions. (After Lacombat et al., Ref. 9.)

adopted. The DOF is the height of the largest window whose width is the exposure budget (process margin) that accommodates the tolerances that can affect the actual exposure dosage. Figure 7a shows the DOF determined by 10% and 30% exposure budgets, respectively. Figure 7b shows two E-D windows. One is bound by the common zone of three kinds of feature (line and spaces, isolated line openings, isolated spaces), and the other by five kinds of feature (including holes and islands).

The DOF equation is produced from Eq. (6.7) and Eq. (6.8) as

$$DOF = \frac{k_2}{k_1^2} \frac{W^2}{\lambda} \tag{6.9}$$

where  $\lambda/W = NA$  coefficient

$W^2/\lambda = DOF$  coefficient

$k_2/k_1^2$  = DOF, normalized to W and  $\lambda$

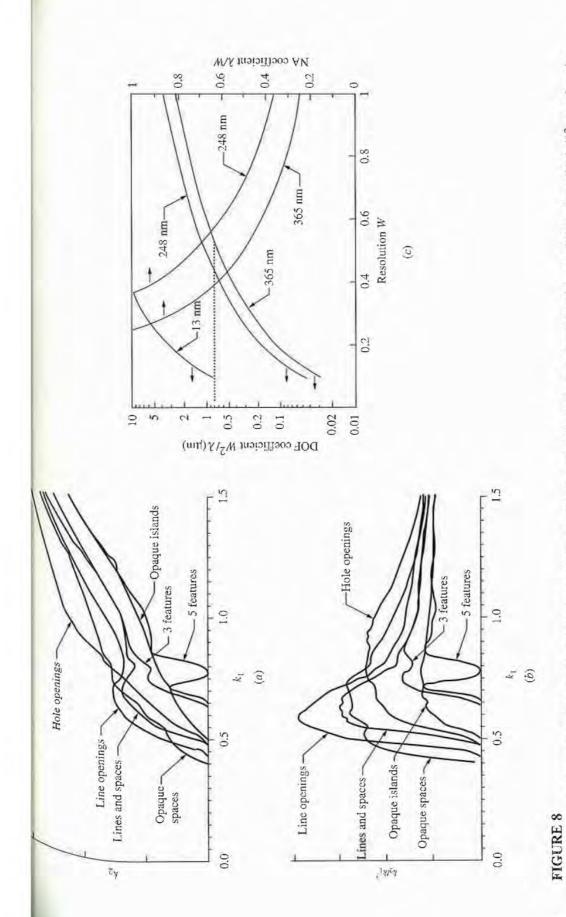

Figure 8a and 8b shows  $k_2$  and  $k_2/k_1^2$ , respectively, as a function of  $k_1$ , and Fig. 8c shows  $W^2/\lambda$  and  $\lambda/W$  as a function of W. The normalized DOF and  $k_1$  can be converted to physical DOF and NA by multiplying by the DOF coefficient and the NA coefficient, respectively, which are plotted in Fig. 8c.

The optimum NA for individual feature shapes is much lower than expected, as a result of Fig. 8c. The results lead to the problems that occur in reducing the usable  $k_1$  factor for manufacturing. The optimum  $k_1$  for the single-layer resist process (10%) linewidth budget estimated) ranges from 0.57 to 0.87 depending on the feature shape.

E-D windows. (After Lin, Ref. 10.) (a) The 10% and 30% E-D window bounded by ±10% E-D branches of line and space pairs at  $k_1 = 0.8$ ,  $\sigma = 0.4$ . (b) The 3-feature and 5-feature E-D windows at  $k_1 = 0.7$ ,  $\sigma = 0.52$ .

NA optimization parameters for optical projection printers. (After Lin, Ref. 10.) (a)  $k_2$  as a function of  $k_1$  at 10% budget. (b)  $k_2/k_1^2$  as a function of  $k_1$  at 10% budget. (c) The DOF coefficient and NA coefficient as a function of W. The dotted line shows the similar difficulty of achieving 0.1  $\mu$ m by X-ray and 0.5  $\mu$ m by I-line.

For a multilayer resist process (30% budget),  $k_1$  ranges from 0.42 to 0.7, although it is generally defined as 0.6 as shown in Eq. (6.2).

#### Reflection and catadioptric projection

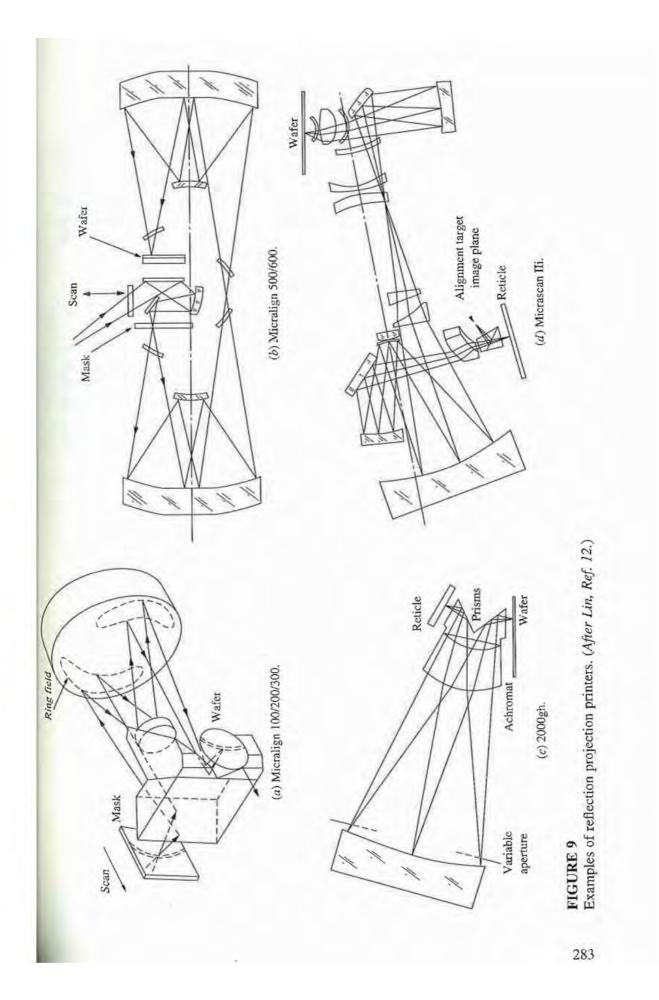

A significant advantage of the reflective or the catadioptric system<sup>11</sup> (combining reflecting and refracting components) is the larger spectral bandwidth. Reflection projection systems generally have higher throughput with less standing-wave interference than refraction systems because of their polychromatic characteristics. Catadioptric systems usually require more than just one optical axis and thus can lead to great difficulty in aligning the optical elements. Several systems of this type<sup>12</sup> have been developed as shown in the second category of Table 1 and in Fig. 9.

The Micralign®, made by Perkin Elmer, consists of only three optical components, as shown in Fig. 9a. It has a bandwidth of 400 nm. The aberrations vary as a function of the distance from the center and can be zero for a narrow zone about the center. Only a small zone of the spherical mirror is used, limited by the slit, providing nearly diffraction-limited imaging. The mask and the wafer are swept in unison through an arc to form an image of the whole mask. Figure 9b is the catadioptric system, also by Perkin Elmer, which is still widely used as a  $1 \times$  full-scan system. The throughput is very high, as shown in Table 1, but the disadvantages of these systems are the low resolution and the difficulty of alignment during scanning; hence, the overlay accuracy is rather poor, as listed in Table 1.

Figure 9c is a catadioptric  $1 \times$  stepper made by Ultratech (Table 1). Only the wafer has a step-and-repeat movement, and a die-by-die alignment is done. This system also has a very simple optical configuration, featuring a variable NA that depends on object field size—a low NA corresponds to a large field size. The practical resolution is  $0.7 \mu m$ .

Figure 9d shows a  $4\times$  catadioptric reduction projector (Table 1) developed by Perkin Elmer that has 0.5- $\mu$ m resolution. This machine also has a *ring field* similar to Fig. 9a and 9b with field-by-field alignment and a focus adjustment. The image field is larger than in I-line steppers.

#### Refraction projection

In refraction projection, the image of the mask is projected on the wafer through a high-resolution lens. A refraction projection system consists of a light source, a condenser, a heat-removing filter, beam-orienting mirrors, a shutter, and the mask and wafer stages. The refraction projection system is very similar to the proximity printers except for the imaging lens between the mask and the wafer. The optical stepper has become the most common lithography tool for ULSI production. The resolution is  $0.4~\mu m$  using the I-line of the Hg lamp with the Kohler method, which images the exposure source through a condenser lens in an entrance pupil of the projection lens. However, the DOF is reduced to  $1~\mu m$  because of the stepper's large NA and short wavelength. The features of the stepper are high resolution, and overlay accuracy as shown in Table 1.

The last group in Table 1 is an excimer laser stepper 13 whose wavelength is 248 nm. It can obtain the highest resolution of the equipment listed in Table 1 based on the excimer's shortest wavelength. The system configuration is almost the same as an I-line stepper, but the light source and the lens system are different. In the deep

UV region, the materials of the optical components are limited to fused silica and several crystalline fluorides because of UV transmittance characteristics. The lenses are made entirely of fused silica and therefore are chromatic. The source bandwidth must be narrow to achieve sufficient resolution. The focus and the magnification differences due to wavelength difference are 0.15 μm/pm and 0.3 ppm/pm, respectively. The current performance of the KrF laser source, such as a 2.2-pm bandwidth and a ±0.25-pm wavelength stability, is considered adequate to meet the requirement for practical use. A 0.35-μm resolution within the 0.03-μm critical dimension spread is reported. The use of the excimer laser is another possible way to fabricate ULSI patterns without resists by using the damaging effect of a short-wavelength light.

#### 6.2.3 Enhancement

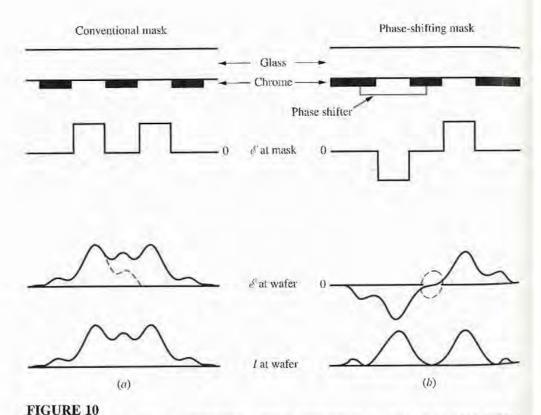

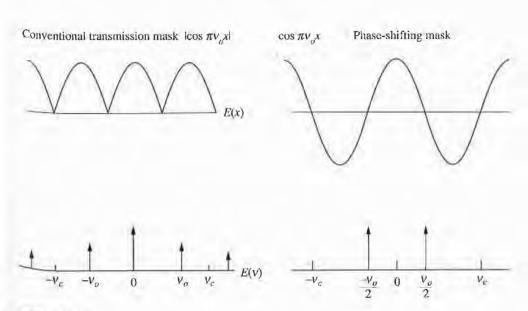

Many efforts have been made to solve optical lithography problems arising from wavelength or DOF. Among these, the phase-shifting mask and the off-axis illumination technique seem to be useful. The basic concept of the phase-shifting mask is shown in Fig. 10. At the transmission mask, the electric field & has the same phase at every aperture (clear area) in Fig. 10a. Diffraction and the limited resolution of the optical system spread the electric field & at the wafer, as shown by the dotted

The principle of phase-shift technology. (After Levenson et al., Ref. 14. © 1992 IEEE.)

(a) Conventional technology. (b) Phase-shifting technology.

line. Interference between waves diffracted by the adjacent apertures enhances the field between them. The intensity I is proportional to the square of the electric field.

The phase-shifting layer that covers adjacent apertures reverses the sign of the electric field as shown in Fig. 10b. The intensity at the mask is unchanged. The electric field of these images at the wafer, shown by the dotted line, can be canceled. Consequently, images that are projected close to one another can be separated completely. A 180° phase change occurs when a transparent layer of thickness  $d = \lambda/2(n-1)$ , where n is the refraction index and  $\lambda$  is the wavelength, covers one aperture as shown in Fig. 10b.

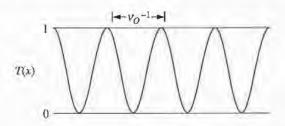

The Fourier analysis <sup>14</sup> of phase-shifting and conventional transmission masks is explained in Fig. 11. The conventional resolution power of a projection system for transmission objects is the critical frequency  $\nu_c = \text{NA}/\lambda$ , which is related to the wavelength  $\lambda$  and numerical aperture NA and assumes coherent illumination. With incoherent illumination some spatial modulation is transmitted through such a system up to a frequency of  $2\nu_c$ ; but for coherent illumination the modulation transmission function is unity up to  $\nu_c$  and zero for  $\nu > \nu_c$ , as shown in Fig. 6. For the purpose of calculation it is convenient to define for the mask a transmission function that has sinusoidal intensity, as illustrated at the top of Fig. 11. In each case,

FIGURE 11

Fourier analysis of the optics of transmission and phase-shifting masks. (After Levenson et al., Ref. 14. © 1992 IEEE.)

the intensity transmitted by the mask is assumed to be

$$T(x) = \frac{1}{2}(1 + \cos 2\pi \nu_0 x) \tag{6.10}$$

The electric field at the mask plane can have two possible forms when the illumination is normally incident and coherent. A transmission mask would produce an electric field profile  $\mathscr E$  that is proportional to  $|\cos \pi \nu_0 x|$ , as in the left side of Fig. 11, whereas a phase-shifting mask would produce the electric field on the right, or  $\mathscr E \propto \cos \pi \nu_0 x$ . Both profiles can be Fourier-analyzed as shown at the bottom of Fig. 11. The transmission mask yields a Fourier spectrum of the form

$$\mathscr{E}_{T}(\nu) = \frac{4}{\pi} \left\{ \frac{1}{2} \delta(\nu) + \frac{1}{6} [\delta(\nu - \nu_{0}) + \delta(\nu + \nu_{0})] - \frac{1}{30} [\delta(\nu - 2\nu_{0}) + \delta(\nu + 2\nu_{0})] + \cdots \right\}$$

(6.11)

where  $\delta(\nu)$  is the Dirac delta function and higher harmonics have been ignored. The phase-shifting mask projects only two Fourier components:

$$\mathcal{E}_{\phi}(\nu) = \frac{1}{2} [\delta(\nu - \nu_0/2) + \delta(\nu + \nu_0/2)] \tag{6.12}$$

The same information, in the sense of an optical intensity, is transmitted in each case, but the phase-shifting mask requires less spatial bandwidth than the transmission mask.

The optical system through which these Fourier components must propagate can be modeled as having a response function equal to unity for  $\nu \leq \nu_c$  and zero for  $\nu > \nu_c$ , where  $\nu_c$  is the cutoff frequency. Thus, the Fourier components of the electric field at the image plane are (except for a scale factor that can be set to unity) identical to those at the mask plane for  $\nu < \nu_c$  and zero otherwise. From this treatment, the critical frequency for the transmission of modulation produced by a phase-shifting mask is  $\nu_0 = 2\nu_c$ , twice that of a transmission mask.

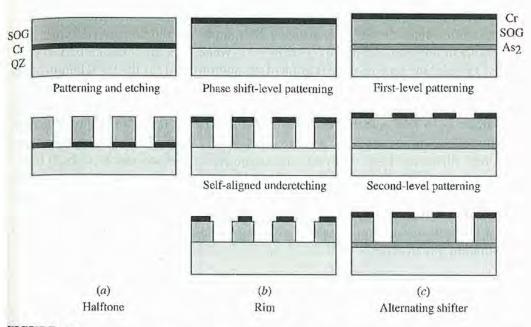

It is expected that an I-line stepper can resolve features down to 0.2 µm using a phase-shifting mask without reducing the DOF. The problem with this technology is the restriction on the pattern layout. It is very difficult to apply this technology to random patterns, although it is very useful in a periodic layout. Several ideas have been proposed to solve the problem, as shown in Fig. 12. The halftone method, shown in Fig. 12a, has advantages such as not requiring extra data and ease of processing, but the resolution is not so good as the alternative method of Fig. 12c.

Phase-shifting masks are made by using an electron-beam (e-beam) direct-writing method. After the first layer is etched, the second layer is exposed on a newly coated resist, referenced to the alignment marks made in the first layer. In Fig. 12b or 12c, two kinds of patterns are necessary for each wafer layer. The problems of phase-shift technology are the design of the shifter pattern and the complexity of the mask process. Other key technologies required to make phase-shifting masks are improved inspection and repair technologies for the shifter patterns and the opaque patterns.

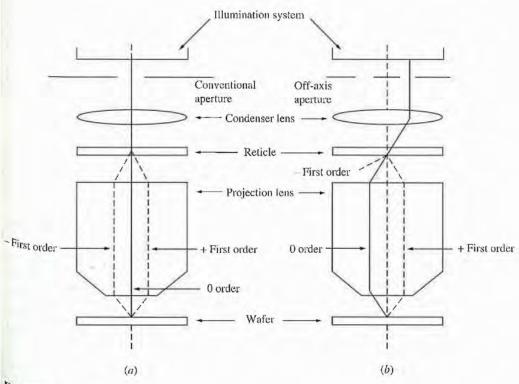

Off-axis illumination 16 is another useful method to enhance the resolution and DOF. The basic principle is to tilt the illumination to an angle that passes through both the undiffracted light and the first-order diffracted light symmetrically as shown

FIGURE 12 Examples of phase-shifting masks. (After Ronse et al., Ref. 15.) (a) Halftone. (b) Rim. (c) Alternating shifter.

FIGURE 13 The off-axis illumination principle. (After Shiraishi et al., Ref. 16.) (a) Conventional illumination. (b) Off-axis illumination.

in Fig. 13b, compared with the conventional method in Fig. 13a. The light beams transmitted through the off-axis aperture illuminate the reticle pattern with a specific incident angle  $\phi$ , defined as  $f \sin \phi = x$ , where x is the distance between the optical axis and the transmissive portion of the aperture and f is the focal length of the condenser. The light beams are diffracted by the reticle pattern. The —first-order or higher-order diffracted light will not enter the projection lens because the pitch of the pattern is so fine and the diffraction angle  $(\sin \theta)$  is larger than the numerical aperture of the projection lens, as explained in Fig. 5. As a result, only zero- and first-order diffracted light will interfere on the wafer surface and contribute to the image formation. It is reported that this technique has a line-and-space resolution of  $0.27~\mu m$  and a  $2.8-\mu m$  DOF for a  $0.35-\mu m$  line-and-space pattern with a  $1.18-\mu m$  resist thickness. It is necessary to adjust the incident angle depending on pattern spatial frequencies and to increase the exposure time to compensate for the loss of illumination due to tilting.

## 6.2.4 Overlay Accuracy

To this point we have emphasized resolution, but overlay accuracy is another fundamental technology component. Overlay error is generated mainly in two process steps—the alignment and the exposure. Many types of errors are included in the exposure process, such as the relative placement error between the mask and the wafer, distortion or magnification error of the lens, and mechanical instability of the exposure system caused by vibration, temperature drift, or atmospheric pressure drift.

Alignment methods are classified into two types: off-axis and TTL (through the lens). Off-axis offers the possibility of using nonactinic rays and of broad-band and high-NA viewing, with the flexibility of brightfield, darkfield, or even phase-contrast viewing. It is also easy to upgrade the off-axis alignment system because of its total separation from the imaging optics. However, off-axis requires high mechanical stability and precision as well as accurate means to refer the positions of the mask, the wafer, and the alignment microscopes to each other.

TTL offers the inherent advantage of a direct mask-to-wafer reference and thus relaxes the requirement for high mechanical stability and precision. However, some accuracy of the direct reference is lost if nonactinic alignment is used or if the wafer has to be moved into the exposure position after alignment. Both of these process steps require compensation.

Brightfield alignment suffers from multiple interferences of the wafer film stacks in case of TTL narrow-bandwidth illumination. The alignment signal is sensitive to variation in film thickness, on the order of 10 nm. This problem is reduced by using broad-band illumination. Alternatively, darkfield alignment removes the dependence on film thickness but does not completely nullify the effect of uneven resist coverage. Also, darkfield alignment has the potential problem of signal degradation on a grainy substrate. The solution to this problem is using the slit beam and the periodic alignment marks. One way to solve the aforementioned problems is to remove the resist over the alignment marks in the positive resist process, but this is impossible in the case of multilayer resist and negative resist processes.

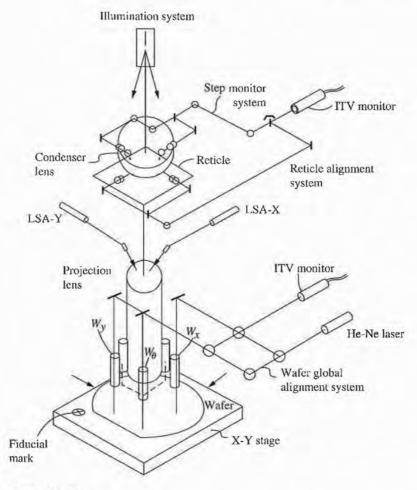

An alignment system<sup>17</sup> is illustrated in Fig. 14. Off-axis global alignment measures the relative position of the wafer with a He-Ne laser. Die-by-die alignment is

FIGURE 14 Wafer alignment system of an optical stepper. (After Shiotake and Yoshida, Ref. 17.)

more accurate because it uses an extra laser source (LSA-X, LSA-Y) through the projection optical path, i.e., the TTL method. Step-and-repeat exposure offers levelto-level registration, which is independent of wafer size, by separate alignment of each exposure field. In the reduction projection system, the mask pattern dimensions are larger than in systems imaged with unity magnification, and therefore it is more convenient to adjust the overlay position.

The basic sources of overlay error are listed in Table 2. The problem of overlay is common to both optical and x-ray lithography. X-ray lithography and e-beam direct Write are considered distortionless. The registration error, defined as the ability to locate the alignment marks, is assumed to be identical for all optical alignment systems. Resist-induced alignment error is considered to be systematically removable. Wafer inplane distortion is caused by various hot processes. The major part of the magnification error of reduction systems is eliminated by fine tuning, but not easily, owing to the inherent symmetry of 1× optical systems. Coupled with the linear part of wafer inplane distortion, the magnification error of 1× optical systems can be as large as 0.15 μm. Similarly, x-ray systems have an error of 0.1 μm as a result

TABLE 2 Sources of overlay errors<sup>12</sup>

| Items                                              | 5× optics<br>(μm) | 1× optics<br>(μm) | 1× x-ray<br>(μm) | E-beam dir <sub>ect</sub><br>write (μm) |

|----------------------------------------------------|-------------------|-------------------|------------------|-----------------------------------------|

| 1. Lens distortion                                 | 0.07              | 0.06              | 0                | 0                                       |

| 2. Registration error                              | 0.05              | 0.05              | 0.05             | 0.05                                    |

| Wafer implane distortion                           | 0.05              | 0.05              | 0.05             | 0.05                                    |

| 4. Magnification error                             | 0.01              | 0.1               | 0.1              | 10.0                                    |

| 5. Mask-to-mask placement error                    | 0.05              | 0.05              | 0.05             | 0.05                                    |

| 6. Total contributions (RSS)                       | 0.1               | 0.15              | 0.13             | 0.09                                    |

| 7. Total without lens distortion                   | 0.07              | 0.13              | 0.13             | 0.09                                    |

| 8. Total without magnification error               | 0.1               | 0.11              | 0.09             | 0.09                                    |

| Total without distortion or<br>magnification error | 0.07              | 0.09              | 0.09             | 0.09                                    |

of wafer inplane distortion and mask heating during exposure. The mask-to-mask placement error reflects the accuracy of e-beam mask making. For x-ray systems, the placement error of the membrane mask can be worse than for the optical mask, but it is not included here. In the case of e-beam direct write, the mask error is simply the composite placement error of the e-beam between two masking levels. In the case of 5× lithography, the mask-to-mask placement error is divided by 5 before being included in the RSS (square root of the sum of the squares) total of the contributions.

### 6.2.5 Optical Resists

Photoresist is the general term for polymers that can create patterns by the use of solvents after irradiation. The development of the resist is based on a chemical reaction and depends on the solubility difference between irradiated and unirradiated areas. Photoresists are of two types: negative, which on exposure to light become less soluble in a developer solution, and positive, which become more soluble.

Negative resists generally consist of a chemically inert polyisoprene rubber, which is the film-forming component, and a photoactive agent. The photoactive agent releases nitrogen gas on exposure to light, and the radicals generated react with the double bonds to form cross-links between rubber molecules, making the rubber less soluble in an organic developer solvent. The reactive species formed during the exposure can react with oxygen and be rendered ineffective for cross-linking, so an inert atmosphere is used. The developer solvent dissolves the unexposed resist. The exposed resist has low molecular weight, so it swells as the uncrosslinked molecules are dissolved. The swelling distorts the pattern features and limits resolution to 2 to 3 times the initial film thickness. For VLSI/ULSI applications, the use of negative resists has been supplanted by positive resists because negative resists have a resolution limit of about 2 μm, although they have many advantages such as resistance to etching and good adhesion to the substrate.

Positive resists have two components: a resin and a photoactive compound dissolved in a solvent. The photoactive compound is a dissolution inhibitor. When the photoactive compound is destroyed by exposure to light, the resin becomes more soluble in an aqueous developer solution. The unexposed regions have high molecular weight and so do not swell much in the developer solution; therefore higher resolution, suitable for ULSI, is possible with positive resists. The development process of projection-printed images in positive resists has been modeled theoretically; it is an isotropic etching or removal process.

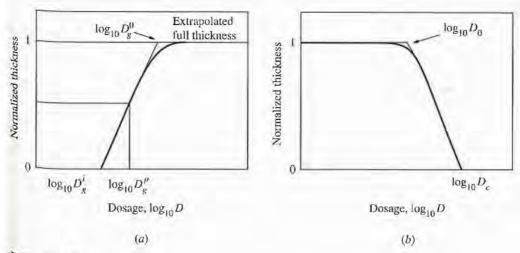

One of the fundamental properties of a resist, which determines resolution, is the contrast. <sup>19</sup> Contrast, in the case of negative resist, is related to the rate of formation of a cross-linked network and may be measured by exposing pads of known area to varying radiation doses.  $D_g^i$  is the minimum dosage required to form the first insoluble film. Thereafter, the film thickness, and consequently the thickness remaining after development, increases with increasing dose until, ultimately, the thickness of the developed pad is not detectably different from the original film thickness (in practice it is slightly less owing to volume contraction during cross-linking). This process is shown schematically in Fig. 15a. The resist contrast  $\gamma_n$  is then defined as

$$\gamma_n = 1/(\log D_g^0 - \log D_g^i) \tag{6.13}$$

For a positive resist, the film thickness of the irradiated region that remains after development decreases with increasing dose until eventually a dose  $D_c$  is reached, which results in complete removal of the film on development, as shown in Fig. 15b. The contrast of positive resist  $\gamma_p$  is defined as

$$\gamma_p = 1/(\log D_c - \log D_0) \tag{6.14}$$

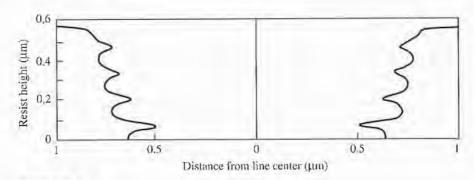

When photoresist films are exposed using monochromatic radiation, standing waves are formed in the resist.<sup>20</sup> These are caused by coherent interference effects due to a reflecting substrate. Coherent interference results in periodic intensity distributions in the direction perpendicular to the plane of the resist with a period  $\lambda_r/2$ , where  $\lambda_r$  is the wavelength in the resist. The refractive index of most resists is about 1.6, leading to an optical mismatch at the air/resist interface. Figure 16 shows

FIGURE 15

Sensitivity curves of negative and positive resists. (After Thompson, Ref. 19.) (a) Negative resist. (b) Positive resist.

FIGURE 16

Simulated standing wave edge profile for a nominal 1-μm line in AZ1350 photoresist developed for 85 sec in 1 : 1 AZ developer : water. (*After Dill et al.*, *Ref.* 20. © 1975 IEEE.) Substrate: Si + SiO<sub>2</sub>, 60 mm; resist thickness: 583.6 nm; exposure wavelength: 435.8 nm (G-line); exposure energy: 57 mJ/cm<sup>2</sup>

the standing wave. This variation in peak intensity with resist thickness becomes less with decreasing substrate reflectivity and increasing absorption by the resist. Since resist thickness varies at a step in the substrate topography, the resulting difference in effective exposure leads to size variations in the resist image.

Commercially available resists are listed in Table 3. The negative RD2000N-type resists, which have a diazide compound as a reactor with polyvinylphenol resin, have a resolution similar to a positive resist and do not swell on development. Photoresists are being developed for exposure at shorter wavelengths where higher resolution is possible. A few such deep-UV resists are PMMA, sensitive for  $\lambda < 250$  nm; polybutene sulfone, sensitive for  $\lambda < 200$  nm; and Microposit MP-2400, sensitive for  $\lambda = 250$  nm. At these shorter wavelengths, the radiation quantum is large enough to produce scission of the molecular chain.

The other very important resists for deep UV are the chemically amplified resists, which exhibit high photo-speed, excellent resolution, and process tolerance.<sup>21</sup> The chemically amplified resist consists of a polymer host and a generator of acid in the presence of light. In the postexposure bake the photogenerated acid catalyzes thermal reactions that alter the solubility of the exposed region. Generally, resolution and sensitivity are affected by postexposure bake conditions. Some chemically amplified resists are applicable to electron lithography.

Other important properties of resists are adhesion to the substrate and resistance to wet and dry etch processing. In general, the commercially available optical resists are compatible with such processes.

Some inorganic materials are also effective as resists. Fundamental functions are based on the Ag-doping effect, which is induced by photoirradiation or electron-beam irradiation on a stacked-layer system of Ag and Se-Ge chalcogenide-glass film. When doped with Ag, the chalcogenide-glass films become almost insoluble in an alkaline solution. The light source, such as a Hg lamp, should have a wavelength that is shorter than the absorption edge of Se-Ge. This method is expected to have high resolution, with applications in dry processing. <sup>22,23</sup>

TABLE 3 Commercial optical resists

| Name             | Maker                      | Туре     | Chemical structure              | Remarks    |

|------------------|----------------------------|----------|---------------------------------|------------|

| OMR83            | Tokyo-oka                  | Negative | Isoprene rubber, azide compound | 1× aligner |

| CIR              | Nippon Synthetic<br>Rubber |          | "                               | - 33       |

| RD-2000N         | Hitachi Chemical           |          | Phenol resin, azide compound    | Deep UV    |

| MES-U            | Nippon Synthetic<br>Rubber |          | Chloropolystyrene               | -10        |

| THMR-iN200       | Tokyo-oka                  | -11      | Novolac resin, azide            | I-line     |

| TDUR-N7          | "                          | - 11     | Phenol resin                    | Deep UV    |

| Microposit 1350J | Shipley                    | Positive | Novolac resin,                  | G-line     |

|                  |                            |          | O-kyniadiazide                  |            |

| AZ1350J          | Hoechst                    | **       | 31                              | 451        |

| OFPR800          | Tokyo-oka                  | **       | 33                              | 31         |

| Microposit2400   | Shipley                    | 39       | **                              | Deep UV    |

| ODUR-120         | Tokyo-oka                  | **       | PMMA                            | **         |

| ODUR1000         |                            | ,,       | PMIPK                           | I-line     |

| THMR-IP3000      | 0                          | ***      | Novolac resin, azide            | in.        |

| TSCR-80I         | 11                         | 2.9      | "                               | -11        |

| PFI28            | Sumitomo<br>Chemical       | - 11     | -91                             | "          |

| PFRIX060         | Nippon Synthetic<br>Rubber |          | w                               | -10-       |

| PFRIX061         | n n                        | H        | 1.82                            | ***        |

| FHI-3950         | Fuji Hunt                  | 198      | - 11                            | **         |

| AZ7500           | Hoechst                    | **       | 11                              | 11         |

| NPR-A18SH7       | Nagase                     | **       | 91                              | - 11       |

# 6.2.6 Process Technologies

Increasing the NA and decreasing the wavelength are logical approaches to improving resolution. However, if these techniques are used, DOF decreases, based on Eq. (6.3). In the actual production process, many possible causes of interference to focusing arise. Some occur during the wafer process, such as surface topography and warping. Others are due to the exposure process, such as vibration, illumination nonuniformity, and aberrations. One solution to these problems is the combination of planarization and surface imaging. The thick bottom planarization layer reduces optical reflection and pattern-width degradation due to the surface topography beneath. The thin top layer enhances resolution, pattern-width control, and process latitude.

Surface-imaging resist processes are summarized in Fig. 17. The first item is treatment through a development cycle to enhance the contrast of the resist.<sup>24</sup> In this cycle the wafer is dipped in the developer, rinsed, and dried. This sequence is repeated until the resist film of the exposed area is completely dissolved. This interrupted development process promotes the formation of a passivation layer on the

#### 294 ULSI Technology

FIGURE 17

Advanced resist processes.

|                           | Bleaching | Surface modification |     |

|---------------------------|-----------|----------------------|-----|

| Contrast<br>enhancement   |           |                      |     |

| Surface<br>imaging        |           | Silylation           | RIE |

| Bilayer                   |           | RIE                  |     |

| Trilayer                  |           | RIE                  | RIE |

| Conventional single layer |           |                      |     |

unexposed surface. As a result, the side walls become vertical and sensitivity is improved 30 to 50% in AZ resist. This technology is also used in electron lithography.

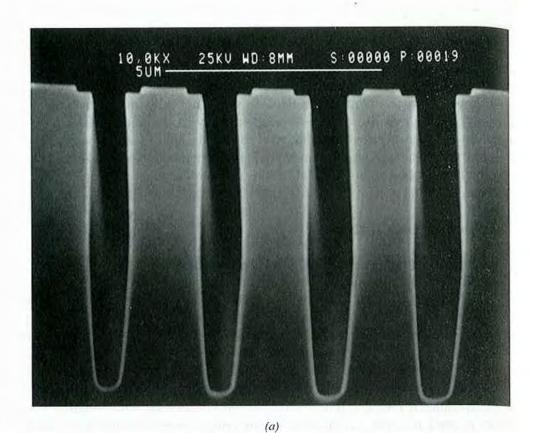

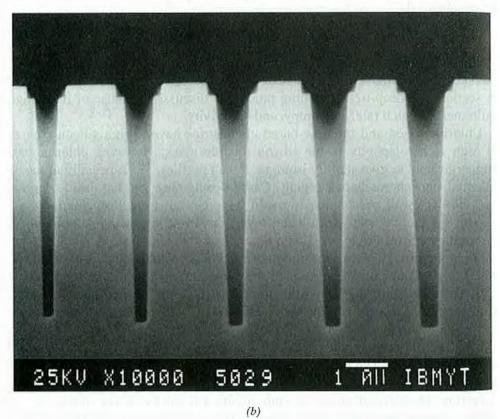

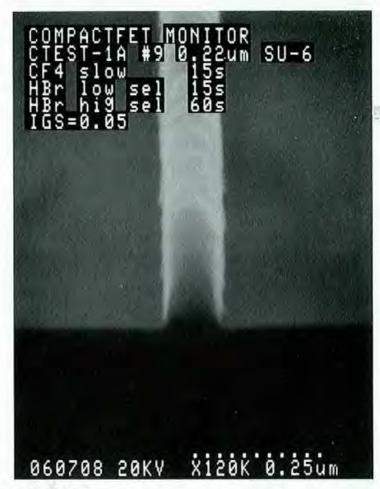

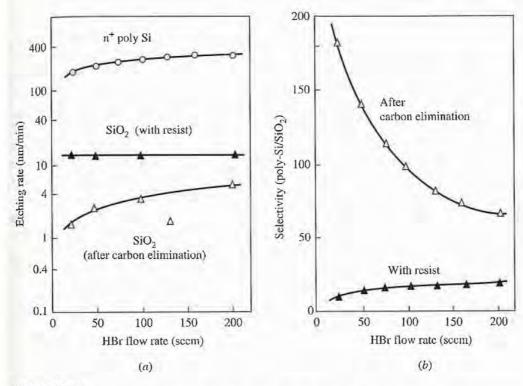

The second process in Fig. 17 is silylation. A single layer of PLASMASK® (UCB from Belgium) resist is spincoated onto the substrate, with a thickness from 1.5 to 2.5 μm, and prebaked to a self-planarizing layer. After exposure, the wafers are treated with a gas-phase silylating agent (hexamethyldisilazane) at elevated temperature to reduce the silylation time. The resist material of the exposed areas selectively bonds chemically with silicon to a depth of 100–200 nm, and remains stable for a long time. The wafers are developed in oxygen plasma. During this treatment, the silicon is converted into silicon dioxide, which forms a thin protective mask that stops the etching of these exposed areas. It is reported that 0.35-μm features can be achieved using a 248-nm source. 26