Lett., edl-1, 217 (1980).

K. Mochiji, Y. Maruyama, F. Murai, S. Okazaki, Y. Takeda, and S. Asai, Jpn. J. Appl. Phys., 20, Suppl. 20-1, 63 (1981).

J. M. Shaw and M. Hatzakis, IEEE Trans. Electron Dev., ed.-25, 425 (1978).

T. D. Berker and D. D. Casey, ibid., ed-29, 524 (1982).

# A Three-Layer Resist System for Deep U.V. and RIE Microlithography on Nonplanar Surfaces

E. Bassous,\*<sup>1</sup> L. M. Ephrath,\* G. Pepper, and D. J. Mikalsen

IBM, Thomas J. Watson Research Center, Yorktown Heights, New York 10598

#### ABSTRACT

The three-layer resist system AZ1350J/Si/PMMA was used to define high-resolution patterns on nonplanar surfaces with topographical features typically encountered in the fabrication of VLSI circuits. The substrate was coated successively with a thick layer of polymethyl methacrylate (PMMA) for planarization, a thin layer of amorphous silicon for masking, and a thin AZ1350J resist layer in which the optical or electron beam exposed pattern was defined. Transfer of the resist image pattern into the amorphous silicon film was performed anisotropically by reactive ion etching (RIE) in a CF<sub>4</sub> plasma. The pattern in the Si layer was then replicated in the underlying PMMA layer either by blanket deep u.v. exposure (200-300 nm) and solvent development or by in situ RIE in an O<sub>2</sub> plasma. Both patterning techniques were comparable in defining submicrometer features in PMMA films 1-3  $\mu$ m thick with good linewidth control and high aspect ratio over steps 1  $\mu$ m high. Experimental details are described and the complexity of deep u.v. and RIE patterning techniques are discussed with particular emphasis on the planarizing characteristics of PMMA.

High-resolution submicrometer resist patterns for VLSI applications are often difficult to generate on nonplanar surfaces due primarily to the nonuniform thickness of the resist layer covering topographical structures. Good linewidth control with high resolution requires, ideally, a uniform resist film less than 1  $\mu m$  thick on a perfectly planar surface. Good step coverage and large height-to-width aspect ratio over 1  $\mu m$  high topography demand, however, the use of a resist layer substantially thicker than 1  $\mu m$  (1).

To overcome the conflicting requirements imposed on the resist film thickness, multilayer resist systems have been developed which separate the imaging and step-coverage functions in different layers. Sensitivity of the imaging process and definition of resist patterns could thus be enhanced independently, without sacrificing step coverage or aspect ratio (1-33). In twolayer systems (4-18), a thick resist film is first applied over the surface to cover vertical features and to planarize its topography. The thick layer is then overcoated with a thin resist film in which the image pattern is defined. The small thickness of the top imaging layer, and its relatively large distance from the sub-strate surface, enhance the resolution of patterns obtained by optical and electron beam exposure. This is due to a reduction of diffraction effects in the optical case and a decrease of electron scattering effects in the latter. Transfer of the top image pattern to the underlying thick layer has been accomplished by the use of solvents (7-9), selective developers (10, 34, 35), deep u.v. exposure and development (4, 15-18), and by dry etching in an oxygen plasma (11-14, 19-29).

One of the drawbacks of two-layer resist systems is the nonuniform mixing which sometimes occurs at the interface between the layers, resulting in processing difficulties and poor pattern definition. To minimize this effect, and to improve processing selectivity, three-layer resist systems have been introduced which incorporate a barrier film sandwiched between the two resist layers (17-32). The barrier film prevents mixing between the top and bottom layers, and thus, permits a wider choice of resist materials and pattern transfer techniques. The increased processing flexibility serves

to enhance imaging sensitivity, and to achieve better control of pattern geometry. The pattern transfer processes in two-layer and three-layer resist systems are similar and their selectivity determines how faithfully the exposed image is replicated.

This study was undertaken to explore the feasibility and processing complexity associated with the use of a silicon barrier layer in a three-layer system for patterning submicrometer features over 1  $\mu$ m topography employing wet and dry processes. The imaging layer used was AZ1350J, and the planarizing layer was polymethyl methacrylate (PMMA). Silicon was selected as the barrier material (23, 25, 26) in the AZ1350J/Sil/PMMA three-layer system because of its compatibility with Si integrated circuit fabrication processes, its very low etch rate in an oxygen plasma, and its opacity in the deep u.v. region of the spectrum (200-300 nm). Amorphous Si barrier layers with smooth uniform surfaces are readily deposited as doped or undoped films on resist surfaces (36-38). The use of doped Si films is advantageous in electron beam exposures because an electrically conducting layer is less subject to surface charging, and thus, misregistration associated with this effect is significantly reduced (25).

The pattern in AZ1350J resist was defined by either optical or electron beam exposure, and then replicated in the Si film by RIE. Amorphous Si films were obtained by plasma CVD of silane or by electron-gun evaporation of silicon (38). Pattern transfer to the PMMA planarizing layer was accomplished either by blanket deep u.v. exposure and solvent development or by in situ RIE in an oxygen plasma. Processing details will first be described, followed by a discussion of the experimental results.

#### **Experimental Procedure**

High-resolution test patterns in the AZ/Si/PMMA system were defined on 57 mm diameter Si wafers patterned with surface steps 1  $\mu m$  high. The steps were repetitive grating structures of different size, defined photolithographically in an SiO2 film 1  $\mu m$  thick. The stepped surface was first coated with a layer of PMMA 1.5-3  $\mu m$  thick followed by a thin silicon film  $\sim\!100$  nm thick and finally a film of AZ1350J photoresist  $\sim\!0.5$   $\mu m$  thick to serve as the top imaging layer. The high-resolution line/space test pattern which

The high-resolution line/space test pattern which ranged from 0.5 to 5  $\mu m$  was defined in the AZ imaging

Electrochemical Society Active Member.

Present address: IBM Corporation, White Plains, NY 10604.

Key words: multilayer lithography, submicron lithography, trilevel resist, planarization, topography.

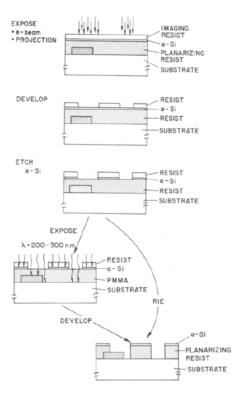

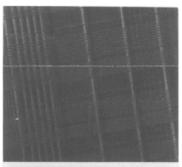

layer perpendicular to the underlying grating structures. Exposures were performed either with a direct write Vector Scan electron beam system (39) or with a  $5\times$  step-and-repeat optical projection printer (40). The exposed and developed image pattern in the AZ resist layer was replicated in the sandwiched Si film by RIE in a CF4 plasma (41). Transfer of the Si pattern to the underlying PMMA layer was performed either by flood exposure to deep u.v. radiation (200-260 nm) followed by development of the image pattern in organic solvents, or by in situ RIE in an oxygen plasma (11-14, 19-29). A typical process sequence is outlined below and is illustrated schematically in Fig. 1. Typical patterns of PMMA resist lines crossing over SiO<sub>2</sub> steps are shown in Fig. 2.

Process sequence.—Spin-coat HMDS. Spin-coat 1 µm PMMA. (Dupont Elvacite 2041, 10% by weight in 2-methoxyethyl ether). Bake 15 min at 85°C. Repeat, spin-coat 1 μm PMMA. Bake 1 hr at 160°C. Deposit amorphous Si 30-200 nm by plasma CVD of SiH4 or by electron gun evaporation of Si. Bake 1 hr at 100°C in air. Spin-coat HMDS. Spin-coat 0.45 μm AZ1350J using 2 AZ1350J:1 AZ thinner. Bake 15 min at 85°C. Expose test pattern either by (i) electron beam at 30  $\mu$ C/cm<sup>2</sup>, 20 keV, or (ii) on a 5× optical projection printer at 15 mJ/cm<sup>2</sup> using 405 nm monochromatic radiation. Develop image in AZ developer, then bake 30 min at 100°C. RIE Si in CF<sub>4</sub>. RIE patterning: (i) In situ RIE PMMA in O<sub>2</sub> plasma, and (ii) dip etch 5-10 sec in buffered HF to clean off residues. Deep u.v. patterning: (i) flood expose to deep u.v. at 0.5-1 J/cm2, and (ii) develop image in either chlorobenzene or methyl isobutyl ketone (MIBK).

Resist films.—Although resist films other than PMMA were used for planarization, PMMA was selected for

Fig. 1. Deep u.v. and RIE processes for patterning over topography using the three-layer resist system AZ1350J/Si/PMMA. The electron beam or optically exposed pattern is generated in the thin top AZ layer, and then replicated in the sandwiched amorphous silicon film by RIE in CF<sub>4</sub>. The Si pattern is transferred to the thick bottom PMMA planarizing layer by deep u.v. exposure and solvent development or by RIE in oxygen.

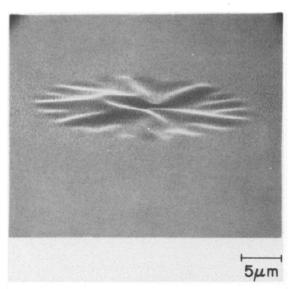

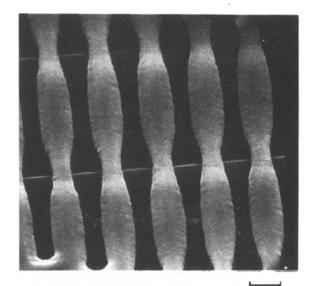

Fig. 2. Typical high resolution line/space test patterns in the three-layer system AZ/Si/PMMA defined over 1 μm high grating structures etched in an SiO<sub>2</sub> film. Top: Optical micrograph of part of the test pattern showing line/space features ranging between 0.5-5 μm. Bottom: SEM of equal line/space features 3 μm wide in 3 μm thick PMMA generated by RIE in oxygen.

detailed study because of its deep u.v. sensitivity (42) and its high etching rate in an  $O_2$  plasma. PMMA films  $>1~\mu m$  thick were obtained by applying multiple coatings in order to avoid cracking, and to promote better planarization of the substrate surface as discussed below. Adhesion of PMMA to Si and SiO<sub>2</sub> surfaces was enhanced by prior coating with the adhesion promoter hexamethyl disilazane (HMDS). However, the use of HMDS was essential to ensure adequate adhesion of AZ1350J photoresist to the Si surface.

Despite its low sensitivity, AZ1350J resist was selected as an imaging layer because it offered the convenience of both optical and electron beam sensitivity. The initial thickness of AZ1350J resist was reduced by  $\sim\!0.1~\mu\mathrm{m}$  after development to a final nominal thickness of 0.4  $\mu\mathrm{m}$ . The latter was quite adequate to mask the underlying Si layer in a CF<sub>4</sub> plasma during the pattern transfer process.

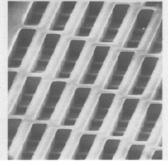

Silicon films.—Plasma CVD silicon films were deposited in the plasma reactor illustrated in Fig. 3 using a mixture of SiH<sub>4</sub> and He at 4 and 65 mTorr partial pressures, respectively. The wafers were placed on the 125 mm diameter lower electrode, and after pumping to a pressure of  $5\times10^{-7}$  Torr, the deposition was performed at 50°C substrate temperature, at a rate of 15 nm/min using a power density of 0.6 W/cm². Films deposited under these conditions were hydrogenated amorphous silicon containing as much as 30% H<sub>2</sub> (43-46). Films obtained by electron gun evaporation of pure silicon on substrates maintained at or slightly above room temperature were functionally indistinguishable from CVD Si films.

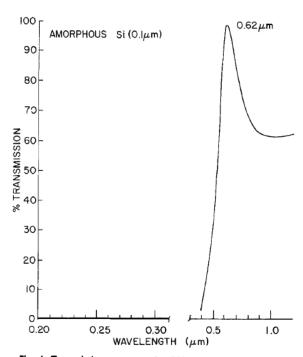

Thin films obtained by plasma CVD of silane and electron gun evaporation of silicon were particularly well suited for lithographic processing because the films were clear, smooth, and amorphous. The optimum thickness for most patterning applications was  $90 \pm 20$  nm although patterns were defined in films 30-200 nm thick. Silicon films were transparent in the visible spectrum as shown in Fig. 4, but more importantly,

PLASMA CVD DEPOSITION SYSTEM

Fig. 3. Sketch of plasma CVD system for the deposition of hydrogenated amorphous silicon films from a silane/helium mixture. The 14 cm diameter electrodes 6 cm apart operated at 13.56 MHz. Typical conditions: SiH<sub>4</sub> 4 mTorr, He 65 mTorr, upper electrode 850V, lower (substrate) electrode 0V, power 0.6 W/cm<sup>2</sup>, deposition rate 15 nm/min.

they were totally opaque in the deep u.v. region below 300 nm. The films were excellent blocking layers for deep u.v. pattern transfer applications as suggested by the PCM techniques discussed by Lin (1, 4, 16-18).

Pattern replication.—Transfer of the image pattern from the top AZ layer to the Si film was performed by RIE in a diode reactor with a perforated grounded aluminum catcher plate positioned between the electrodes to minimize backscattering of sputtered aluminum

Fig. 4. Transmission spectrum of a 100 nm thick film of hydrogenated amorphous silicon deposited by plasma CVD of a silane/helium mixture on a quartz (suprasil) substrate. The film is transparent in the visible region with a peak at 620 nm and is totally opaque below 400 nm. Similar spectra are exhibited by films as thin as 20 nm including those obtained by electron-gun evaporation.

(47). The system was first pumped down to  $10^{-6}$  Torr, and Si was then etched in CF<sub>4</sub> at 2.5 mTorr pressure, 0.25 W/cm² rf power density at 13.56 MHz. Using endpoint laser detection (48) and 50% overetching beyond end point ensured complete and uniform removal of the Si layer.

Etching of the underlying PMMA or polymer layer was performed in an oxygen plasma at 20 mTorr pressure and 0.06 W/cm² rf power density. Overetching varied between 50 and 100% depending on the topography present and the maximum thickness of resist. The etch rates of the 3 layers viz., Si, AZ1350J, and PMMA in CF<sub>4</sub> were 40, 50, and 70 nm/min, respectively, while in O<sub>2</sub> the etch rates of the same films were 0, 35, and 70 nm/min, respectively. Replication of the AZ image pattern in an Si film 100 nm thick resulted in an AZ film loss of 200 nm, while replication into a PMMA layer  $\leq 1~\mu$ m resulted in the total loss of the AZ film.

Transfer of the Si image pattern to the PMMA layer was also performed by flood exposure to deep u.v. radiation, followed by development in either chlorobenzene or MIBK at room temperature. A 1 kW Hg-Xe deep u.v. source manufactured by Hanovia was used to expose individual wafers in air. The exposure time varied between 2-10 min depending on the sensitivity and thickness of the planarizing resist as well as on the composition of the developing solvent. To obtain the same dissolution rate of PMMA, the deep u.v. exposure necessary for MIBK development was approximately twice that required for chlorobenzene.

#### Results and Discussion

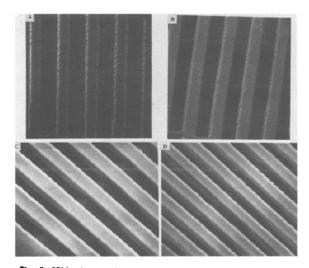

High-resolution line/space features over 1  $\mu$ m topography were defined in the three-layer system AZ/Si/PMMA using RIE and deep u.v. patterning techniques. The minimum dimension defined in PMMA layers 1-3  $\mu$ m thick was 0.5  $\mu$ m using electron beam exposure of the top AZ layer. Optical exposure on a 5 $\times$  step-and-repeat projection system using 405 nm monochromatic radiation produced minimum line/space features of 1  $\mu$ m. Figure 5 shows 1  $\mu$ m and 0.75  $\mu$ m line/space features defined in the Si layer, and replicated in 2  $\mu$ m thick PMMA by deep u.v. exposure, and development in chlorobenzene. Similar test patterns 1  $\mu$ m/0.5  $\mu$ m

Fig. 5. SEM micrographs of high resolution line/space test patterns defined in the AZ/Si/PMMA system over 1  $\mu m$  high topography. A: Equal 1  $\mu m$  line/space features in AZ1350J and Si obtained by electron beam exposure followed by RIE etching of Si. B: Same pattern after deep u.v. exposure and development of PMMA 2  $\mu m$  thick. C: Same as B showing vertical sidewalls of PMMA crossing over an oxide step 1  $\mu m$  high. D: Equal 0.75  $\mu m$  line/space features similar to C.

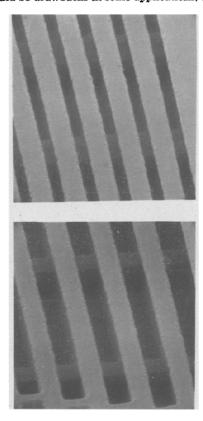

and 1  $\mu$ m/1  $\mu$ m were obtained by RIE of PMMA in an oxygen plasma as shown in Fig. 6.

The RIE and deep u.v. patterning techniques were equally capable of generating uniform resist features with good linewidth control, quasi-vertical sidewalls, and high aspect ratio over 1 µm topography as illustrated in Fig. 2, 5, and 6. Such patterns are highly desirable for subtractive and additive processes in VLSI fabrication. The differences between the RIE and deep u.v. patterning techniques were mainly determined by the characteristics of the planarizing layer as discussed below.

RIE patterning.—RIE processing was more tolerant of variations in thickness and composition of the planarizing layer by virtue of the anisotropy of RIE, and the high etch rate of organic resist materials relative to Si in an oxygen plasma. Radiation sensitivity of the planarizing layer was also not a requirement in RIE processing. The selection of useful organic coatings was, therefore, wider, and the processing flexibility, for example with respect to high-temperature baking and thermal cycling, was greater than deep u.v. processing.

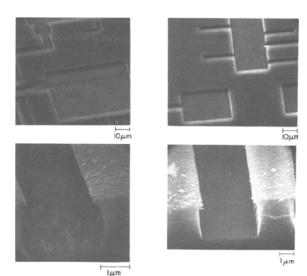

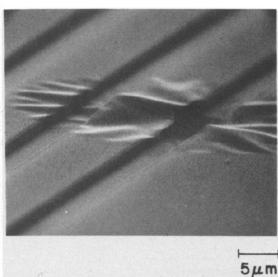

Undesirable resist residues, which appeared on surfaces after etching by RIE, were removed by a cleaning procedure such as dip-etching in dilute HF solution. Figure 7 illustrates the effectiveness of the HF dip-etching technique in cleaning off all traces of residues from RIE-patterned surfaces. Where exposure to HF was incompatible with the materials on the wafer surface, alternate cleaning procedures were used in conjunction with modified RIE conditions. Potential contamination from metals sputtered from the substrate holder and radiation damage from energetic photons could be drawbacks in some applications, but their

Fig. 6. SEM micrographs of line/space patterns defined in the AZ/Si/PMMA three-layer system over 0.8  $\mu$ m high topography. Top: Line/space pattern 1  $\mu$ m/0.5  $\mu$ m obtained by RIE of PMMA 2.5  $\mu$ m thick. Bottom: Similar pattern with line/space features 1  $\mu$ m/1  $\mu$ m. Decrease in linewidth is less than 0.1  $\mu$ m.

Fig. 7. SEM micrographs of patterns defined in a PMMA film 2 µm thick by RIE in oxygen. Resist residues on etched surfaces were cleaned off by dip etching in buffered HF for 10-15 sec. A,C: After RIE. B,D: After cleaning.

effects could be eliminated or minimized by adjusting RIE conditions (47).

Deep u.v. patterning.—In deep u.v. patterning, resist residues seldom appeared after solvent development of adequately exposed PMMA. Residues tended to appear when the overall PMMA thickness was excessive, or the thickness variation over steps was large. This could be attributed to the strong attenuation of the deep u.v. intensity in thick layers, resulting from the strong absorption of PMMA in the spectral region between 200-260 nm (42). As the solubility of PMMA was a strong function of the energy absorbed, the attenuation from top to bottom of thick PMMA layers resulted in a corresponding decrease in development rate. This phenomenon influenced residue-formation, as well as the cross-sectional profile and aspect ratio of resist features. Where PMMA thickness variations due to topography were large, development in chlorobenzene resulted in better linewidth control than undiluted MIBK. Development in chlorobenzene could also be used to retain the top imaging resist film, and generate a three-layer structure which is potentially useful in lift-off applications (49-51). Similar structures could also be generated by RIE using a top imaging resist film which is stable in an oxygen plasma.

An advantage of the deep u.v. patterning process was its relative insensitivity to pinholes or cracks in the barrier layer when the top imaging film was intact and opaque in the deep u.v. In the absence of the Si barrier layer, a film of AZ1350J photoresist 0.3  $\mu \rm m$  thick is sufficient to block deep u.v. radiation from exposing the PMMA layer (4). Despite the infinite solubility of exposed PMMA relative to silicon, the maximum useful thickness of PMMA was limited to 3  $\mu \rm m$  due to the severe attenuation of the deep u.v. intensity, and the tendency of thicker layers to crack after baking or pattern development.

Film integrity.—Successful patterning of the AZ/Si/PMMA system required careful optimization of the film thicknesses and the experimental conditions which affected the integrity of the 3 layers. In particular, the stress, the adhesion, and defect levels in one layer affected directly the integrity of the two other layers during processing. The film characteristics and the processing tolerances varied with the horizontal and vertical geometry of the underlying topography.

Hydrogenated amorphous Si films deposited by plasma CVD often formed blisters (Fig. 8) on poorly planarized PMMA surfaces. Such blister formation was presumably due to excessive stress induced in the Si film by the underlying topography. Silicon films deposited at room temperature by electron gun evaporation were more susceptible to loss of adhesion than plasma CVD Si films. The evaporated films were more specular and uniform, resulting in better defined patterns. The etching and deep u.v. blocking characteristics of evaporated and CVD films were identical.

Poorly adhering and highly stressed silicon films often cracked and peeled after the imaging layer was patterned. Deposition above room temperature and annealing of the films prior to the application of the top imaging layer alleviated this problem. Similar behavior was observed with evaporated films of Al and Ti used as barrier layers between PMMA and AZ1350J.

The thickness of the top imaging resist layer and the baking conditions also influenced the integrity of the silicon barrier layer. Resist films  $\leq$ 0.5  $\mu$ m thick baked

Fig. 8. Hydrogenated amorphous silicon films 100 nm thick deposited on PMMA at room temperature. Blisters indicative of compressive stress in the film are randomly distributed on the surface. Top: Single blister after film deposition. Bottom: Appearance of blister after patterning.

at about 100°C were readily processed over a wide range of PMMA and Si film thicknesses. Good step coverage and adequate planarization were essential to obtain a uniformly thick imaging layer. Inadequate planarization resulted in variations in thickness of the imaging layer with corresponding variations in linewidth and profile geometry. Multiple reflections at the resist-silicon interface also contribute to linewidth variations in the case of optically exposed patterns. The effect is clearly illustrated in Fig. 9 which shows the systematic variation in linewidth of 5 parallel resist lines nominally 2  $\mu m$  wide crossing over 2 raised oxide steps 1  $\mu m$  thick and 2  $\mu m$  wide.

Planarization.—Due to the importance of the planarizing function of PMMA, an empirical evaluation of the coating characteristics of a variety of films was made using single and multiple coatings on stepped surfaces. Oxidized wafers, with sets of periodic line/space structures 2.5-25  $\mu m$  wide, were coated by conventional resist spinning and baking methods. The undulations of the resist surface profile conforming to the substrate topography were scanned with a mechanical stylus to determine the planarization or leveling accomplished by a coating layer.

The curves in Fig. 10 show the peak-to-valley amplitude of the resist surface profile covering surface steps 0.8 µm high. The degree of planarization, represented by the amplitude, varied with the molecular weight of PMMA, the thickness and number of PMMA layers, the line/space dimensions of the substrate topography, and their periodicity or pitch. As the average molecular weight of PMMA decreased, the amplitude of the surface undulations decreased indicating enhanced planarization. This effect is illustrated in Fig. 10 (a) with three PMMA compositions of average molecular weight 500,000, 150,000, and 33,000. The films were nominally 2 µm thick coated on sets of parallel steps 5 µm wide and varying pitch.

The expected improvement in planarization with increasing PMMA thickness is illustrated in Fig. 10 (b) for the same sets of steps 5  $\mu$ m wide and 0.8  $\mu$ m high. The amplitude of the surface undulations also progressively decreased as the number of PMMA layers increased. It is interesting to note that better planar-

$2\mu$ m

Fig. 9. Linewidth variation of PMMA resist lines that run from top to bottom of the micrograph traversing two 1  $\mu$ m high SiO $_2$  steps. Narrowing of the resist lines occurs at the top of the steps where the resist is thinnest.

Fig. 10. Planarization of 0.8  $\mu m$  high steps with PMMA films of various thickness. The steps consisted of repetitive grating structures 2.5-25  $\mu \mathrm{m}$  wide. The amplitude representing the vertical distance between the maxima and minima of the undulations of the PMMA surface profile is plotted against the pitch, i.e., width of step or gap. (a) Amplitude decreases, i.e., planarization improves as the average molecular weight decreases from 500,000 to 150,000 to 33,000. The PMMA films were 2  $\mu m$  thick covering steps 5  $\mu m$ wide; (b) Amplitude decreases as the thickness of PMMA is increased by succesive coat-and-bake cycles. From the top down: 1 layer 1.1  $\mu\text{m}$ , 2 layers 1  $\mu\text{m}$  each, 3 layers 1  $\mu\text{m}$  each, and 5 layers 0.5  $\mu m$  each. Despite the lower overall thickness, 5 imes 0.5  $\mu m$ layers planarize more effectively than 3 imes 1  $\mu$ m layers. PMMA 2041 (avg. MW = 500,000), covered steps 5  $\mu m$  wide; (c) Amplitude increases or planarization degrades as the pitch increases for steps 2.5, 3.8, and 5  $\mu m$  wide, and for gaps 2.5 and 3.8  $\mu m$  wide. PMMA 2041 was 2  $\mu m$  thick and covered steps 0.8  $\mu m$  high.

ization was achieved with five  $0.5~\mu m$  layers than with three 1  $\mu m$  layers. A PMMA film nominally 2.5  $\mu m$  thick was thus more effective than a 3  $\mu m$  film to planarize the same substrate topography. This result suggests that multiple thin coatings could be applied to planarize severe topography without unduly increasing the overall resist thickness.

Planarization also improved as the horizontal dimensions of line/space patterns and their periodicity decreased as shown in Fig. 10(c). For a given line/space pattern between 2.5-5  $\mu m$ , the amplitude of the surface undulations increased as the pitch increased. Isolated lines were thus more difficult to planarize than closely spaced lines or isolated spaces. This observation suggests that nonfunctional topographical steps deliberately introduced in the vicinity of critical surface regions would promote better planarization and consequently achieve better control of pattern dimensions. Similar effects on the planarization of metal patterns with thin polyimide films have been reported by Rothman (52).

The planarization experiments, though limited, lead to the conclusion that step coverage cannot be predicted from step height and resist thickness only. Important factors which also affect the planarization of topography include the horizontal geometry and periodicity of surface structures, as well as the molecular weight of the resist and its mode of application.

Patterning by deep u.v. and RIE was also accomplished in a variety of three-layer systems using highsensitivity imaging resists, Ti and Al barrier layers, and Novolak-based planarizing photoresists baked at elevated temperature. The processing complexity was essentially similar to AZ/Si/PMMA, and their lithographic performance was comparable.

#### Conclusions

Deep u.v. and RIE patterning of submicrometer features over 1  $\mu m$  topography were achieved in the three-layer system AZ1350J/Si/PMMA. The patterns in PMMA 1-3 µm thick exhibited uniform linewidth and high aspect ratio which are desirable attributes for VLSI applications. The two patterning methods were comparable in processing complexity, and were equally sensitive to defect levels in the three layers. Adequate planarization of topography, and optimization of the adhesion and stress in the Si layer were essential requirements for both processes. Planarization of topography was strongly influenced by the horizontal geometry and periodicity of surface structures, as well as by the resist composition and its mode of application. Deep u.v. patterning was performed by conventional wet processing methods which are adaptable to large-scale fabrication. New positive and negative deep u.v. resists (53-61) offer the potential for deep u.v. patterning of both imaging and planarizing layers in the same threelayer system. RIE patterning allowed a wider selection of imaging and planarizing resist materials as well as a greater latitude in processing. RIE was more readily adaptable to all-dry processing, and was particularly useful in the generation of resist patterns with vertical sidewalls and large aspect ratio over extreme topography.

## Acknowledgments

We wish to thank R. C. Guarnieri and J. J. Cuomo for supporting the plasma CVD work, and S. Krongelb, J. Harper, R. S. Bennett, and J. L. Speidell for their cooperation in the RIE experiments. We also thank J. V. Powers for the electron beam exposures, C. Lapadula for the  $5\times$  optical exposures, and E. J. Petrillo, C. J. Lucchese, S. B. Brodsky, and D. L. Quinlan for expert technical assistance. We gratefully acknowledge the many helpful discussions with M. Hatzakis, J. M. Shaw, and L. B. Rothman, and the support of B. J. Lin throughout this work.

Manuscript submitted July 30, 1982; revised manuscript received Sept. 30, 1982.

Any discussion of this paper will appear in a Discussion Section to be published in the December 1983 JOURNAL, All discussions for the December 1983 Discussions for the Decembe cussion Section should be submitted by Aug. 1, 1983.

Publication costs of this article were assisted by IBM T. J. Watson Research Center.

#### REFERENCES

- 1. "Fine Line Lithography," R. North-Holland Publishing Newman, Editor, Co., Amsterdam

- w.` Moreau and C. H. Ting, U.S. Pat. 3,934,057

- W. Moreau and C. H. Ting, U.S. Pat. 3,934,057 (1976).

C. M. Horwitz, Appl. Phys. Lett., 32, 803 (1978).

B. J. Lin, SPIE Proc., 174, 114 (1979).

T. H. P. Chang, U.S. Pat. 4,165,395 (1979).

M. Hatzakis, D. Hofer, and T. H. P. Chang, J. Vac. Sci. Technol., 16, 1631 (1979).

M. Hatzakis, ibid., 16, 1984 (1979).

J. R. Kitcher, ibid., 16, 2030 (1979).

W. D. Grobman, H. E. Luhn, T. P. Donohue, A. J. Speth, A. Wilson, M. Hatzakis, and T. H. P. Chang, IEEE Trans. Electron Dev., ed-26, 360 (1980).

- (1980)10. C. Li and J. Richards, in Proc. IEDM, p. 1112, Washington, D.C. (1980).

- K. L. Tai, W. R. Sinclair, R. G. Vadimsky, J. M. Moran, and M. J. Rand, J. Vac. Sci. Technol., 16, 1977 (1979).

- J. M. Moran and D. Maydan, *ibid.*, 16, 1620 (1979).

K. L. Tai, R. G. Vadimsky, C. T. Kemmerer, J. S. Wagner, V. E. Lamberti, and A. G. Timko, *ibid.*, 17, 1169 (1980).

- 14. M. Sato and K. Kawabuchi, *ibid.*, 19, 1329 (1981).

15. B. F. Griffing, P. D. Johnson, and J. F. Norton, Semiconductor Microlithography VI, 275, 136

- *ibid.*, 19, 1313 (1981).

19. J. R. Havas, J. Franco, and H. A. Levine, U.S. Pat.

- 3,873,361 (1975).

- 3,873,361 (1975).

J. R. Havas, J. Franco, and L. Rompala, U.S. Pat. 4,004,004 (1977).

J. R. Havas and G. Paal, U.S. Pat. 4,202,914 (1980).

J. S. Logan, G. C. Schwartz, and L. B. Zielinsky, IBM Tech. Discl. Bull., 20, 1024 (1977).

E. C. Fredericks, G. C. Schwartz, and L. B. Zielinski, ibid., 20, 989 (1977).

D. Maydan, J. Vac. Sci. Technol., 17, 1164 (1980).

R. K. Watts, W. Fichtner, E. N. Fuls, L. R. Thibault, and R. L. Johnston, in Proc. IEDM, Washington, D.C. (1980).

J. B. Kriger, P. Rissman, and M. S. Chang, J. Vac. Sci. Technol., 19, 1320 (1981).

S. P. Lyman, J. L. Jackel, and P. L. Liu, ibid., 19, 1325 (1981).

- 1325 (1981).

28. D. M. Tennant, L. D. Jackel, R. E. Howard, E. L. Hu, P. Grabbe, R. J. Capik, and B. S. Schneider, *ibid.*, 19, 1304 (1981).

- M. M. O'Toole, E. D. Liu, and M. S. Chang, Semiconductor Microlithography VI, Vol. 275, 128, SPIE, Washington, D.C. (1981).

J. H. Bruning, J. Vac. Sci. Technol., 17, 1147 (1980).

M. J. Bowden, Solid State Technol., 24 (6), 73 (1981).

- (1981).

- M. Hatzakis, *ibid.*, 24 (8), 74 (1981).

B. F. Griffing, *J. Vac. Sci. Technol.*, 19, 1423 (1981).

K. Grebe, I. Ames, and A. Ginzberg, *ibid.*, 11, 458

- (1974)

- G. J. Dolan, Appl. Phys. Lett., 31, 337 (1977).

W. E. Spear, P. G. Le Comber, S. Kinmond, and M. H. Brodsky, ibid., 28, 105 (1976).

W. E. Spear and P. G. Le Comber, Philos. Mag., 33, 935 (1976).

- J. R. Hollahan and R. S. Rosler, "Thin Film Processes," J. L. Vossen and W. Kern, Editors, Academic Press, New York (1978).

- demic Press, New York (1978).

39. T. H. P. Chang, A. D. Wilson, A. J. Speth, and C. H. Ting, Proceedings of the Symposium on "Electron and Ion Beam Science and Technology, Seventh International Conference," R. Bakish, Editor, p. 392, The Electrochemical Society Softbound Proceedings Series, Princeton, N.J. (1976).

40. J. S. Wilczynski J. Vac. Sci. Technol., 16, 1929

- (1979)

- C. M. Melliar-Smith and C. J. Mogab, "Thin Film Processes," J. L. Vossen and W. Kern, Editors, Academic Press, New York (1978).

B. J. Lin, J. Vac. Sci. Technol., 12, 1317 (1975).

M. H. Brodsky, M. A. Frisch, J. F. Ziegler, and W. A. Lanford, Appl. Phys. Lett., 30, 561 (1977).

M. H. Brodsky, M. Cardona, and J. J. Cuomo, Phys. Rev. B, 16, 3556 (1977).

"Amorphous Semiconductors." M. H. Brodsky, Edi-

- 45. "Amorphous Semiconductors," M. H. Brodsky, Editor, Springer-Verlag, New York (1977).

46. J. I. Pankove and D. E. Carlson, Appl. Phys. Lett., 30, 561 (1977).

- 30, 561 (1977).

47. L. M. Ephrath, This Journal, 129, 62C (1982).

48. K. Sugawara, T. Yashimi, H. Okuyama, and T. Shirasu ibid., 121, 1233 (1974).

49. M. Hatzakis, ibid., 116, 1033 (1969).

50. M. Hatzakis, U.S. Pat. 4,024,293 (1977).

51. M. Hatzakis, B. J. Canavello, and J. M. Shaw, IBM J. Res. Dev., 24, 452 (1980).

- J. Res. Dev., 24, 452 (1980).

L. B. Rothman, This Journal, 127, 2216 (1980).

P. van Pelt, Semiconductor Microlithography VI, Vol. 275, 150, SPIE, Washington, D.C. (1981).

R. L. Hartless and E. A. Chandross, J. Vac. Sci. Technol., 19, 1333 (1981).

Y. Mimura, T. Ohkubo, T. Takeuchi, and K. Sekikawa, Jpn. J. Appl. Phys., 17, 541 (1978).

Y. Yamashita, K. Ogura, M. Kunishi, R. Kawazu, S. Ohno, and Y. Mizokami, J. Vac. Sci. Technol., 16, 2026 (1979).

C. W. Wilkins, Jr. E. Beichmanis, and E. A. Changella, 18, 2022, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2023, 2

- 2026 (1979).

57. C. W. Wilkins, Jr., E. Reichmanis, and E. A. Chandross, This Journal, 127, 2510 (1980).

58. M. Tsuda, T. Tsumori, Y. Nakamura, H. Nagata, A. Yokota, H. Nakane, T. Tsumori, Y. Nakane, and T. Mifune, Photogr. Sci. Eng., 23, 290 (1979).

59. S. Imamura, This Journal, 126, 1623 (1979).

60. T. Iwayanagi, T. Kohashi, S. Nonogaki, T. Matsuzawa, K. Douta, and H. Yanazawa, IEEE Trans. Electron Dev., ed-28, 1306 (1981).

61. E. Gipstein, A. C. Ouano, and T. Tompkins, This Journal, 129, 201 (1982).

# **Short Time Annealing**

# T. O. Sedawick\*

IBM Corporation, T. J. Watson Research Center, Yorktown Heights, New York 10598

### ABSTRACT

Short time annealing has recently become of interest in silicon processing as a technique to activate ion implanted dopants, remove defects, and regrow amorphized silicon, with minimal diffusion of the dopant atoms. Short time annealing is carried out using a variety of energy sources ranging from arc lamps and resistance heaters with heating times of a few tens of seconds, to laser, electron, and ion sources with heating times of a few milliseconds down to nanoseconds. The annealing processes are grouped according to the time durations of the anneal and with reference to the thermal response time of the silicon. These are designated as adiabatic for  $< 10^{-6}$  sec; thermal flux for  $10^{-6}$ - $10^{-2}$  sec, and isothermal for  $> 10^{-2}$  sec. Processes in the adiabatic regime result in surface melting, regrowth of silicon free of sex, and complete dopant activation. However, the dopant diffuses throughout the melt zone. In the thermal flux and isothermal annealing regimes the dopant can be activated, and amorphous silicon regrown epitaxially with little dopant diffusion. In the limited results reported to date, the complete removal of extended defects has not been achieved. Further investigation may yield new results in extended defect removal.

Short time annealing (STA) encompasses a wide range of processing techniques that can thermally process materials over an extremely wide range of times, 10-8-102 sec, all short compared to standard annealing. This paper deals with the application of STA techniques in silicon technology particularly to activate, regrow, and remove damage in ion implanted junctions. The scaling down of device dimensions, which is a continuing trend and an integral part of VLSI device design, requires shallower junctions, higher doping levels, and reduced defect density. The inadequacy of standard furnace annealing to achieve

\* Electrochemical Society Active Member. Key words: silicon, ion implant.