# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD., Petitioner, v. GODO KAISHA IP BRIDGE 1, Patent Owner. Case No. IPR2016-01376

Before JUSTIN T. ARBES, MICHAEL J. FITZPATRICK, and JENNIFER MEYER CHAGNON, *Administrative Patent Judges*.

Patent Number 6,197,696

DECLARATION OF ALEXANDER GLEW, Ph.D.

# TABLE OF CONTENTS

|            | <u>Page</u>                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I.         | Qualifications1                                                                                                                                                                                                                                    |

| II.        | Materials Considered8                                                                                                                                                                                                                              |

| III.       | Level of Ordinary Skill for the '696 Patent                                                                                                                                                                                                        |

| IV.        | Relevant Legal Standards                                                                                                                                                                                                                           |

| Α.         | Anticipation                                                                                                                                                                                                                                       |

| В.         | Obviousness14                                                                                                                                                                                                                                      |

| C.         | Priority Date of a Patent                                                                                                                                                                                                                          |

| D.         | Standard for Claim Construction in <i>Inter Partes Review</i>                                                                                                                                                                                      |

| V.         | Background of the '696 Patent                                                                                                                                                                                                                      |

| VI.        | Claim Construction                                                                                                                                                                                                                                 |

| A. pat 13) | Proper construction of "using the [first resist pattern/second resist tern and the mask pattern/patterned third insulating film] as a mask" (Claim                                                                                                 |

|            | 1. The exclusion of using two layers having flush edges as a mask is inconsistent with the understanding of a skilled person in view of the disclosure of the '696 patent and the '371 application27                                               |

|            | 2. The exclusion of using two layers having flush edges as a mask is inconsistent with the plain and ordinary meaning in view of the disclosure of the '696 patent and the '371 application as understood by a person of ordinary skill in the art |

| VII.       | Grill Is Not Prior Art to the '696 Patent                                                                                                                                                                                                          |

| A.<br>do   | Claim 13 of the '696 Patent is fully supported by the foreign priority cument and is entitled to the claimed March 28, 1998 priority date                                                                                                          |

|            | 1. Claim 13 (Preamble) – "A method for forming an interconnection structure, comprising the steps of:"                                                                                                                                             |

|            | 2. Claim 13 (step a) – "forming a first insulating film over lower-level metal interconnects;"                                                                                                                                                     |

|            | 3. Claim 13 (step b) – "forming a second insulating film, having a different composition than that of the first insulating film, over the first insulating film;"                                                                                  |

# TABLE OF CONTENTS

|                   | 4. Claim 13 (step c) — "forming a third insulating film, having a different composition than that of the second insulating film, over the second insulating film;"                                                                                                                                                               | .44 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   | 5. Claim 13 (step d) – "forming a thin film over the third insulating film;"                                                                                                                                                                                                                                                     | .45 |

|                   | 6. Claim 13 (step e) – "forming a first resist pattern on the thin film, the first resist pattern having openings for forming wiring grooves;"                                                                                                                                                                                   | .45 |

|                   | 7. Claim 13 (step f) – "etching the thin film using the first resist pattern as a mask, thereby forming a mask pattern out of the thin film to have the openings for forming wiring grooves;"                                                                                                                                    | .46 |

|                   | 8. Claim 13 (step g) — "removing the first resist pattern and then forming a second resist pattern on the third insulating film and the mask pattern, the second resist pattern having openings for forming contact holes;"                                                                                                      | .47 |

|                   | 9. Claim 13 (step h) — "dry-etching the third insulating film using the second resist pattern and the mask pattern as a mask, thereby patterning the third insulating film to have the openings for forming contact holes;"                                                                                                      | .48 |

|                   | 10. Claim 13 (step i) — "dry-etching the second insulating film using the patterned third insulating film as a mask, thereby patterning the second insulating film to have the openings for forming contact holes;"                                                                                                              | .52 |

|                   | 11. Claim 13 (step j)— "dry-etching the patterned third insulating film and the first insulating film using the mask pattern and the patterned second insulating film as respective masks, thereby forming wiring grooves and contact holes in the patterned third insulating film and the first insulating film, respectively;" | .55 |

|                   | 12. Claim 13 (step k) — "filling in the wiring grooves and the contact holes with a metal film, thereby forming upper-level metal interconnects and contacts connecting the lower- and upper-level metal interconnects together."                                                                                                | .56 |

| B.<br>priority da | Petitioner has not shown and cannot show that Grill is entitled to the ate of the Grill Provisional                                                                                                                                                                                                                              |     |

|                   | 1. Grill includes multiple statements that were added to and not disclosed in Grill's provisional                                                                                                                                                                                                                                | .60 |

|                   |                                                                                                                                                                                                                                                                                                                                  |     |

# TABLE OF CONTENTS

|                 | 2. Dr. Smith has failed to show that the '628 provides written                                                                                  |     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                 | description support for the claims of Grill                                                                                                     | 62  |

| VIII. Over      | view of Petitioner's Prior Art References                                                                                                       | 75  |

| Α.              | Grill                                                                                                                                           | 75  |

| В.              | Aoyama                                                                                                                                          | 75  |

| IX. The         | Combination of Grill and Aoyama is not obvious                                                                                                  | 76  |

| A.<br>dual-reli | Petitioner's proposed modification of Grill eliminates Grill's use of patterns to form dual-relief cavities                                     |     |

| B. control o    | Petitioner's proposed modifications of Grill would eliminate Grill wer its wiring dimensions.                                                   |     |

| C.              | Grill teaches away from incorporating Aoyama's disclosures                                                                                      | 98  |

|                 | 1. Grill teaches away from incorporating processes that expose carbon based compounds to wet etching or photoresist stripping, and ashing steps | 99  |

|                 | 2. Grill teaches away from incorporating processes that have a thick resist over via holes                                                      | 104 |

| X. Conc         | clusion                                                                                                                                         | 107 |

I, Dr. Alexander Glew, Ph.D., hereby declare under penalty of perjury under the laws of the United States of America:

### I. Qualifications

- 1. I am currently President of Glew Engineering Consulting, Inc. ("Glew Engineering") of Mountain View, California. Glew Engineering provides consulting and engineering services relating to various technology or engineering areas, including CVD technology. My responsibilities at Glew Engineering include acting as a consultant and as a principal managing the company. <sup>1</sup>

- 2. I received a Bachelors of Science degree in Mechanical Engineering from University of California, Berkeley in 1985; a Master of Science degree in Mechanical Engineering from University of California, Berkeley in 1987; a Master of Science in Materials Science and Engineering from Stanford University in 1995. I later also obtained a Doctor of Philosophy degree in Materials Science and Engineering from Stanford University in 2003. A copy of my Curriculum Vitae is attached to this report as **Attachment A**.

<sup>&</sup>lt;sup>1</sup> All emphasis and annotations added unless otherwise noted. A list of exhibits considered is attached to this Declaration as **Attachment B**. Citations to the exhibits in this declaration are exemplary and are not meant to be limiting.

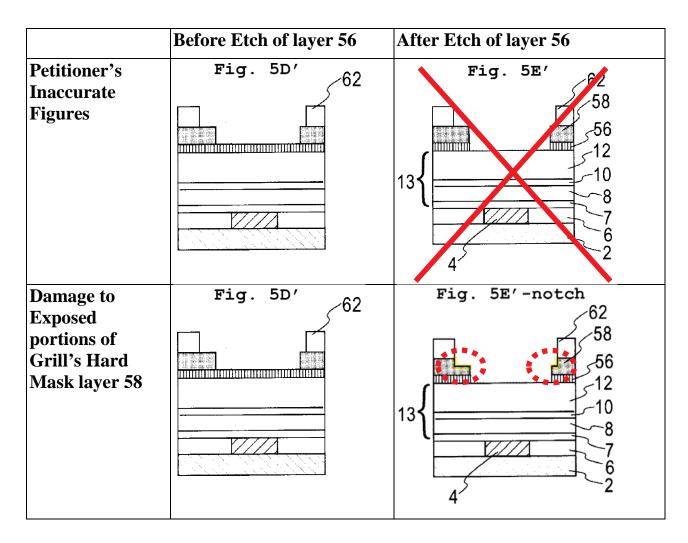

- The subject matter of my doctoral dissertation at Stanford University 3. related to chemical vapor deposition ("CVD") of dielectric films. CVD generally consists of mixing two or more gases in a process reactor or chamber, and having the gases meet on the surface of a substrate to deposit a thin film. Many of the CVD films that I worked on were deposited on undoped silicon glass (SiO2), and boron and phosphorous doped glass. The CVD equipment to be manufactured in this case was to mix various gaseous chemicals and to deposit the chemicals onto glass to produce certain types of specialty glasses. For my doctoral dissertation, I constructed a CVD reactor. Then, I developed CVD processes for certain low k dielectric films such as diamond-like carbon and fluorinated amorphous carbon. Further, I characterized those thin films for their engineering properties, including optical, electrical, and mechanical. Also, I analyzed the chemical composition of the thin films.

- 4. From 1987-1997, I was employed by Applied Materials, Inc. ("Applied Materials"), one of the world's largest and most advanced manufacturers of, among other things, CVD-related equipment. I was hired by the CVD division. The first process tool that I worked on was the Precision 5000 CVD tool. It was the first cluster tool, a tool with multiple CVD processing chambers. Because this tool represented the major advance in tool architecture, multiple chambers attached to a central vacuum load lock chamber, resulting in the ability to process one

workpiece at a time instead of in batch, it was eventually placed in the Smithsonian Institute, Natural History Museum.

- 5. From approximately 1987-1989, I was a Systems Engineer for Applied Materials. In this position, I designed semiconductor processing equipment, and worked with all aspects of the process tool. After a period of time, along with the product marketing manager, I signed off on every tool or machine that we shipped. My signature was required to ensure that the manufactured process tool and the chemical processes it produced matched what was required by the purchase order, and that it was built accordingly and safely.

- 6. Subsequent to being a Systems Engineer, from approximately 1989-1991, I was an Engineering Manager at Applied Materials responsible for customer engineering specials ("CES"). This included customization of equipment to meet customer requests and specifications. The CES requests were diverse and covered nearly all aspects of the equipment, including modifying process chambers, gas panels, wafer handlers/robotics, wafer storage elevators, sensors, vacuum systems, framing, and other components. We worked on very tight schedules, and exercised disciplined project management. If our engineering work was not completed on time, and the materials not procured, then this would hold up the shipment of a multimillion dollar CVD process tool. Because we exercised disciplined project management, such delays rarely happened. We also had to accurately estimate the

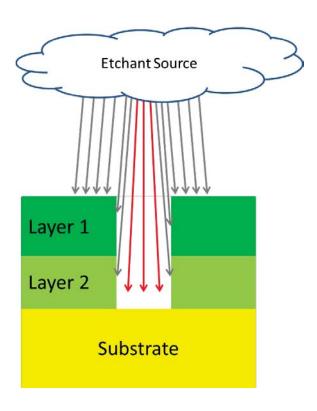

cost of our work, materials and labor, because the CES projects were billed to the customer.

- 7. Next, I was the manager of the engineering design and support group for the CVD division of Applied Materials. In this capacity, I was in charge of all of the designers and drafters, generating all of the engineering drawings, and reviewing all of the engineering design work. I am intimately familiar with computer aided design ("CAD") and engineering documentation.

- In the early 1990s, I was awarded the position of Core Technologist 8. (one of only 15 at Applied Materials). My area of expertise was gas and chemical systems and components. The gas and chemical systems largely delivered ultrahigh purity fluids to the process chambers and reactors. Components used in the systems included the following: valves, flow controllers, pressure regulators, filters, purifiers, pressure transducers and related devices, and systems as a whole. As a core technologist, I was responsible for consulting with different divisions during the design of new products, testing fluid delivery components, reviewing invention disclosures, and reviewing papers written by Applied Materials personnel, holding meetings across the divisions for workers in the field, setting technology trends with suppliers, and reviewing technology trends with customers. Our different divisions included product lines such as CVD, ETCH, CMP, implant, TFT, and others. I also represented the company at industry consortium meetings. The core

technology group met monthly with the president or other senior executives of the company.

- 9. From 1994-1996, I managed a project funded by SEMATECH (Semiconductor Manufacturing Technology—a non-profit R&D consortium to advance chip manufacturing) that I proposed to its factory working group. These efforts resulted in the publication of two SEMATECH technology transfer standards. The goal of this project was to develop industry standard methods to determine the effects of trace chemicals and contamination on semiconductor processing and on semiconductor equipment reliability. As part of this project, I designed, built, and tested gas delivery systems, including the components contained therein, such as filter cartridges or assemblies, flow controllers, valves, and pressure regulators, and tested them to failure. Approximately 90% of wafer yield loss is from particles, so the industry was very interested in the particle effects of the chemical delivery system. I also tested the effects of microcontamination in the process gas stream on tungsten CVD deposition and on metal etching. In some of the tests, we introduced controlled amounts of fluid into corrosive gas streams, and then measured the effect on system reliability, including particle generation.

- 10. As part of the SEMATCH project, we studied the effects of trace chemical contamination on tungsten CVD processing and on metal etching. We

introduced trace chemicals into a standard process, measured the amounts of chemical in the process chamber by residual gas analyzer (RGA), and then measured the resulting film quality and properties by multiple techniques, and measured incorporation of the trace chemicals into the deposited layers.

- 11. From 1994-1997, I was a CVD Supplier Quality Engineering Manager at Applied Materials. During this time, I was the engineering manager responsible for the suppliers of the components of the fluid delivery systems, such as valves, flow controllers, pressure regulators, filters, purifiers, pressure transducers and related devices, and systems as a whole. I tested and evaluated fluid delivery components. I both supervised and personally conducted this testing.

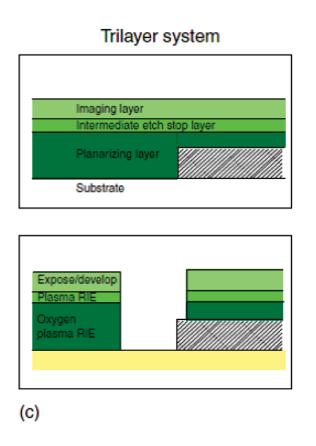

- 12. Since leaving Applied Materials in 1997 and until the present, I have served as president of Glew Engineering. At Glew Engineering, I have worked on projects that include for example: project turnaround for failed projects, testing / metrology, gas panel design, integrated circuits failures, semiconductor equipment failures, Excimer laser sources for photolithography, KrF and ArF. I have assisted component suppliers, and equipment suppliers, and, to a lesser extent, investors.

- 13. My practice at Glew Engineering also includes multi-physics finite element analysis and CAD modeling, which includes three dimensional modeling of machinery, and analysis of the heat transfer, radiation, fluid flow, resultant stresses and strains from running such machinery.

- 14. I am or have been a member of a number of professional organizations including: American Society of Mechanical Engineers, Materials Research Society, and IEEE (Institute of Electrical and Electronics Engineers). Glew Engineering is an Affiliate Member of the Semiconductor Equipment and Materials Institute (SEMI). In addition to being a member of these professional organizations, I have served on committees at SEMATECH.

- 15. I have authored or co-authored dozens of papers, reports, and presentations relating to semiconductor processing, and semiconductor equipment, fluid delivery components in semiconductor processing, and equipment reliability.

- 16. I am an inventor of three issued U.S. Patents, Nos. 6,679,476, related to a high-purity control valve; 6,204,174, related to semiconductor processing; and 7,118,090, related to a high-purity fluid control valve. I have another patent application pending relating to design of CVD equipment components.

- 17. For more aspects of my qualifications and publications, see my curriculum vitae ("CV"), attached hereto as **Attachment A**.

- 18. I have been retained on behalf of Patent Owner Godo Kaisha IP Bridge 1 ("IP Bridge" or "Patent Owner") to offer opinions regarding certain issues relating to U.S. Patent No. 6,197,696 ("the '696 patent") assigned to Patent Owner, as well as other references presented to me by counsel for Patent Owner. I

have also been retained by Patent Owner to offer certain opinions relating to the '696 patent in a co-pending litigation in the Eastern District of Texas.

19. Glew Engineering charges an hourly rate of \$665 per hour plus expenses for my work performed in connection with this *Inter Partes* Review. I have received no additional compensation for my work in this *Inter Partes* Review, and my compensation does not depend on the contents of this report, any testimony I provide, or the ultimate outcome of this or any other *Inter Partes* Review.

### II. <u>Materials Considered</u>

- 20. In developing my opinions below relating to the '696 Patent, I have considered the following materials:

- U.S. Patent No. 6,197,696 (Exhibit EX1001);

- U.S. Patent No. 6,197,696 Patent File History (Exhibit EX1012);

- Petition for *Inter Partes* Review of U.S. Patent No. 6,197,696 (IPR2016-01376) ("Petition" or "Pet.") (Paper No. 1);

- Patent Owner's Preliminary Response (IPR2016-01376) (Paper No.6;

- Decision Institution of *Inter Partes* Review (IPR2016-01376) (Paper No. 11) ("ID");

- Declaration of Bruce W. Smith (IPR2016-01376) (Exhibit EX1002);

- Japanese Patent Application No. 10-079371 to Aoi (Exhibit EX1013)

- Certified Translation of Japanese Patent Application No. 10-079371 to Aoi (Exhibit EX1014)

- Japanese Patent Application No. 11-075519 to Aoi (Exhibit EX1015)

- Certified Translation of Japanese Patent Application No. 11-075519 to Aoi (Exhibit EX1016)

- U.S. Patent No. 6,140,226 to Grill et al ("Grill") (Exhibit EX1005)

- U.S. Provisional Patent Application No. 60-071,628 ("'628" or "Grill Provisional") (Exhibit EX1017)

- U.S. Patent No. 5,592,024 to Aoyama et al ("Aoyama") (Exhibit EX1018)

- U.S. Patent No. 3,617,824 to Shinoda et al ("Shinoda") (Exhibit EX1003)

- U.S. Patent No. 3,838,442 to Humphreys ("Humphreys") (Exhibit EX1004)

- U.S. Patent No. 5,635,423 to Huang et al ("Huang") (Exhibit EX1006)

- U.S. Patent No. 5,741,626 to Jain et al ("Jain") (Exhibit EX1007)

- C. Akrout et al., "A 480-MHz Microprocessor in a 0.12μm Leff CMOS Technology with Copper Interconnects," IEEE J. of Solid-State Circuits, Vol. 33, no. 11 (November 1998) ("Akrout") (Exhibit EX1008)

- J.N. Burghartz et al., "Monolithic Spiral Inductors Fabricated Using a VLSI Cu-Damascene Interconnect Tech. & Low-Loss Substrates," Int'l Electron Devices Mtg (Dec. 1996) ("Burghartz") (Exhibit EX1009)

- U.S. Patent No. 6,100,184 to Zhao et al (Exhibit EX1010)

- U.S. Patent No. 6,103,616 to Yu et al (Exhibit EX1011)

- Transcript of the Deposition of Bruce W. Smith, Ph.D. (March 23, 2017) ("Smith Dep.") (Exhibit EX2010);

- Redline Comparing Grill (EX1005) with Grill's Provisional (EX1017) Application (Exhibit EX2011)

- Translation of Japanese Application 10-079371 to Aoi as Submitted in European Patent Application No. 99 105 946.0 (Exhibit EX2012)

- Declaration of Takeo Ohashi, Ph.D. (Exhibit EX2013)

- Influence of reactor wall conditions on etch processes in inductively coupled fluorocarbon plasmas by M. Schaepkens, et al. (Exhibit EX2014)

- Handbook of VLSI Microlithography, Second Edition, Principles, Technology, and Applications by John N. Helbert (excerpted) (Exhibit EX2015)

- Silicon VLSI Technology Fundamentals, Practice and Modeling by James D. Plummer, et al. (excerpted) (Exhibit EX2016)

- Microlithography: Science and Technology by James R. Sheats and Bruce W. Smith (excerpted) [First Edition] (Exhibit EX2017)

- Microlithography: Science and Technology by Kazuaki Suzuki and Bruce W. Smith (excerpted) [Second Edition] [Ch 12] (Smith Dep. Exhibit 3) (Exhibit EX2018)

- Microlithography: Science and Technology by Kazuaki Suzuki and Bruce W. Smith (excerpted) [Second Edition] [Ch 11] (Smith Dep. Exhibit 9) (Exhibit EX2019)

- Silicon Processing for the VLSI Era Vol. 1 by S. Wolf and R.N. Tauber (excerpted) [Ch 16] (Exhibit EX2020)

- Mask Definition, Merriam-Webster.com (last accessed Dec. 17,2016) (https://www.merriam-webster.com/dictionary/mask) (Exhibit EX3001)

- District Court Claim Construction, 2:16-CV-134-JRG-RSP (E.D. Tex.) (Exhibit EX3002)

- All other materials referenced herein, including those referenced in Attachment B.

## III. Level of Ordinary Skill for the '696 Patent

21. I understand that the factors that may be considered in determining the ordinary level of skill in the art include: (1) the levels of education and experience of persons working in the field; (2) the types of problems encountered in the field; and (3) the sophistication of the technology. I understand that a person of ordinary

skill in the art (also referred to as a "skilled person") is not a specific real individual, but rather a hypothetical individual having the qualities reflected by the factors above.

- 22. At least as of March 26, 1998, the foreign priority date of the '696 patent, a person of ordinary skill in the art would have had a Bachelor's of Science degree in materials science engineering, electrical engineering, mechanical engineering, chemical engineering, or an equivalent degree, and at least two years of experience in semiconductor processing or equipment.

- 23. I met and surpassed these criteria as of at least March 26, 1998 (and thereafter), and consider myself to be a person with at least ordinary skill in the art of the '696 patent. My analyses set forth herein are from the perspective of a person of ordinary skill in March 26, 1998, as set forth above. My opinions would not change even if the '696 patent is only entitled to the later priority date of March 23, 1999 (see §VII).

- 24. I note that Dr. Smith has opined that a person of ordinary skill in the relevant art for the '696 patent would have at least a Master of Science degree in Electrical Engineering, Materials Science, Physics, or the equivalent, a working knowledge of semiconductor processing technologies for integrated circuits, and at least two years of experience in related semiconductor processing analysis, design and development. EX1002 at ¶141. Dr. Smith has further opined that "[a]dditional

graduate education could substitute for professional experience, and significant work experience could substitute for formal education." EX1002 at ¶141. I disagree with Dr. Smith that this is the appropriate level of skill in the art, but even applying Dr. Smith's standard, my opinions herein would not change.

25. Unless otherwise stated, when I state that something would have been known or understood by a person of ordinary skill in the art, I am referring to a person with the level of education and experience expressed in ¶121-24 above, as of March 26, 1998. As described above and in my CV (Attachment A), I have decades of experience with semiconductor devices, including the design and fabrication of memory devices. As of March 28, 1998, I had a Master degree of Science in Materials Science and Engineering, and in Mechanical Engineering, and over 10 years of industry as well as academic experience in semiconductor processing or equipment. I would have qualified as one of ordinary skill in the art according to any of the above definitions. Therefore, I am qualified to testify about what a person of ordinary skill in the art would have known and understood at that time.

### IV. Relevant Legal Standards

26. I have been informed that if an independent claim is found to be novel and non-obvious, every claim that depends from it is also novel and non-obvious. I have also been informed that if an independent claim is not found to be novel and

non-obvious, the claims which depend from it may still be found to be novel and non-obvious. I understand that to be valid, a patent claim must be novel and non-obvious.

27. I understand that a party challenging validity carries the burden of proving invalidity by a preponderance of the evidence on a claim-by-claim basis. Each claim is analyzed independently. It is my understanding that when a party has the burden of proving a claim or defense by a preponderance of the evidence, that party must show that it is more likely than not.

# A. Anticipation

28. I also understand that a patent claim is not novel if is anticipated by a single prior art reference – that is, a single prior art reference discloses each and every element of the claim either expressly or inherently. I also understand that a single reference cannot merely disclose each element. Rather, it must disclose all of the elements as arranged in the claim. I further understand that for a reference to "inherently" disclose something, the missing descriptive matter must necessarily be present in the reference, not merely probably or possibly present, and that it would be so recognized by a person of ordinary skill. I understand that if an element of the claim is not disclosed by one prior art reference, then the claim is not anticipated.

29. I understand that a limitation is found inherently within a reference only if that limitation is necessarily disclosed by the reference (*e.g.*, "necessarily present" in the reference). The mere fact that something may result from a given set of circumstances is not sufficient to show inherency, as inherency cannot be established by probabilities or possibilities. Instead, there must be no other possible alternative to the implementation of the feature, in view of the prior art reference's disclosure.

### B. Obviousness

- 30. I understand that under §103 of the patent statutes, a patent claim is deemed obvious if the differences between it and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art. That is, a person of ordinary skill must have had a reasonable expectation of success in making or practicing the claimed invention, based on the prior art. I also understand that the obviousness analysis does not permit the use of hindsight. One way of avoiding a hindsight analysis is to point to a suggestion or a motivation in the prior art to make or practice the claimed invention.

- 31. I have been informed that to render a claim obvious, a combination of prior art references must disclose each and every claim element of that claim, and that obviousness is a question of law (*i.e.*, for the Board to determine) based on the

underlying facts. I understand that the underlying factual inquiries are: (1) the scope and content of the prior art, (2) the differences between the prior art and the claims at issue, (3) the level of ordinary skill in the pertinent art, and (4) secondary considerations of nonobviousness. I also understand that a patent composed of several elements is not proven to be obvious by simply demonstrating that each of its elements was, independently, known in the prior art. Instead, I understand that there must be some rationale given to support the conclusion.

- 32. I have also been advised that in considering whether an invention for a claimed combination would have been obvious, I may assess whether there are apparent reasons to combine known elements in the prior art in the manner claimed in view of interrelated teachings of multiple prior art references, the effects of demands known to the design community or present in the marketplace, and/or the background knowledge possessed by a person having ordinary skill in the art. I understand that other principles may be relied on in evaluating whether a claimed invention would have been obvious, and that these principles include the following:

- A combination of familiar elements according to known methods is likely to be obvious when it does no more than yield predictable results;

- When a device or technology is available in one field of endeavor, design incentives and other market forces can prompt variations of it, either in

- the same field or in a different one, so that if a person of ordinary skill can implement a predictable variation, the variation is likely obvious;

- If a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that it would improve similar devices in the same way, using the technique is obvious unless its actual application is beyond his or her skill;

- An explicit or implicit teaching, suggestion, or motivation to combine

two prior art references to form the claimed combination may

demonstrate obviousness, but proof of obviousness does not depend on or

require showing a teaching, suggestion, or motivation to combine;

- Market demand, rather than scientific literature, can drive design trends and may show obviousness;

- In determining whether the subject matter of a patent claim would have been obvious, neither the particular motivation nor the avowed purpose of the named inventor controls;

- One of the ways in which a patent's subject can be proved obvious is by noting that there existed at the time of invention a known problem for which there was an obvious solution encompassed by the patent's claims;

- Any need or problem known in the field of endeavor at the time of invention and addressed by the patent can provide a reason for combining the elements in the manner claimed;

- "Common sense" teaches that familiar items may have obvious uses beyond their primary purposes, and in many cases a person of ordinary skill will be able to fit the teachings of multiple patents together like pieces of a puzzle;

- A person of ordinary skill in the art is also a person of ordinary creativity, and is not an automaton;

- A patent claim can be proved obvious by showing that the claimed combination of elements was "obvious to try," particularly when there is a design need or market pressure to solve a problem and there are a finite number of identified, predictable solutions such that a person of ordinary skill in the art would have had good reason to pursue the known options within his or her technical grasp; and

- One should be cautious of using hindsight in evaluating whether a claimed invention would have been obvious.

- 33. I understand that an invention might not be obvious if (1) the combination requires an expert to rely on the patent itself as a roadmap, (2) the prior art teaches away from the invention or the combination because a person of

ordinary skill in the art would be discouraged from following the path set out in the reference or would be led in a direction divergent from the path that was taken by the inventor, (3) the combination would change the basic principles under which the prior art was designed to operate, or (4) the combination would render the prior art inoperable for its intended purpose.

### C. Priority Date of a Patent

I understand that a patent reference may claim the benefit of a filing 34. date of a provisional application that may predate the filing date of the patent reference in the United States Patent & Trademark Office ("USPTO"). In order to claim the benefit of the filing date of the provisional application, the patent reference must expressly claim the benefit of the earlier filing date and the disclosure of the provisional application must provide support for the claims of the patent reference. I understand that in order to provide support for the claims of the patent reference, the provisional application must enable and provide written description support for the claims. I understand that the written description requirement is met if the claimed subject matter is described by the provisional application, or if the invention is disclosed such that a person or ordinary skill in the art can reasonably understand that the inventor was in possession of the claimed subject matter. I also understand that the enablement requirement is

satisfied when one skilled in the art, after reading the specification, could practice the claimed invention without undue experimentation.

35. My understanding is that, similarly, a claim of a patent can claim priority to an earlier filing date of a foreign patent application in the same manner that a claim of a patent can claim priority to an earlier filing date of a provisional application.

### D. Standard for Claim Construction in Inter Partes Review

- 36. I have also been informed that for purposes of *inter partes* review a claim in an unexpired patent shall be given its broadest reasonable construction in light of the specification of the patent in which it appears. While claim terms are generally given their ordinary and customary meaning, which is the meaning that the term would have to a person of ordinary skill in the art in question at the time of the invention, the construction must also be consistent with the specification, and the claim language should be read in light of the specification as it would be interpreted by one of ordinary skill in the art.

- 37. I understand that the Board has instituted an *inter partes* review of claims 13 and 15 of the '696 patent. I understand that trial is limited to the following ground: whether claims 13 and 15 are rendered obvious by Grill and Aoyama. ID at 43. I further understand that the Petition was denied as to all other grounds and trial is accordingly limited to this ground. I understand that the Board

"has not made a final determination with respect to the patentability of any claim term." *Id*.

### V. Background of the '696 Patent

- 38. The '696 patent, entitled "Method for Forming Interconnection Structure," was filed on March 23, 1999, and issued on March 6, 2001, and claims priority to Japanese Provisional Patent Application No. 10-079371 ("the '371 application) filed March 26, 1998. The patent names inventor Nobuo Aoi.

- 39. The '696 patent has 4 independent claims and 11 dependent claims. The '696 patent relates to a complex process for multiple masking to form interconnect structures using low-k dielectric constant ("low-k") materials. Interconnect structures connect the millions of semiconductor circuits, devices and elements formed within a physical semiconductor device (*e.g.*, a "die") and are thus essential to the operation of any semiconductor product. Interconnect structures formed with low-k materials can be scaled to smaller dimensions than interconnect structures formed without low-k materials. The inventor of the '696 patent succeeded in developing a method to use standard lithography techniques to form dense interconnect structures using low-k materials.

- 40. An interconnect structure includes at least two groups of materials—conductors (metals) and insulators. The shapes, arrangements, and compositions of these materials within the interconnect structure affect electrical performance

(described by, e.g., resistivity and capacitance) of the interconnect structure. The electrical performance of the interconnect structure in turn affects the speed, electrical-signal integrity, heat dissipation, and power consumption of an overall semiconductor product, which is filled with such interconnect structures. For example, the dielectric constant—referred to as "k"—of the low-k insulating materials used in the interconnect structure reduces capacitance among interconnect structures. This reduced capacitance improves electrical performance and permits denser packing of interconnect structures. The improved electrical performance reduces the need for additional circuitry and/or metal wiring which may otherwise be needed to improve the integrity of electric signals that are routed around a semiconductor product. Thus, the denser packing of interconnect structures and reduction in additional circuitry and wiring facilitated by using lowk insulators also leads to reduction in area of the chip, and thus a smaller die size.

- 41. Low-k dielectric films can be particularly difficult to pattern by semiconductor photolithographic methods. The claimed invention of the '696 patent allows for the use of standard lithography techniques to form interconnect structures having low-k dielectric materials. *See, e.g.*, EX1001 3:2-4:67.

- 42. In prior processing methods, a low-k dielectric would be damaged in the ashing process used to remove polymer based photoresist layers. *See, e.g.*, EX1001 2:41-52, 3:47-62. Ashing is a process of exposing a polymer-based

photoresist to an oxygen plasma and burning it off the wafer, thereby turning the photoresist into "ash." Many low-k materials are carbon compounds, and cannot withstand exposure to oxygen based plasma used in an ashing process.

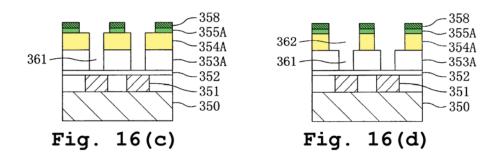

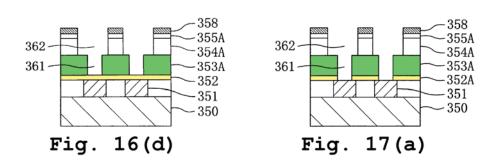

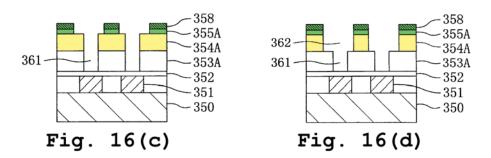

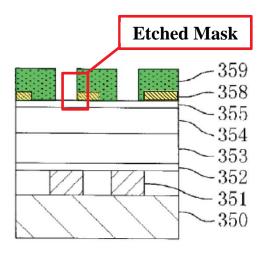

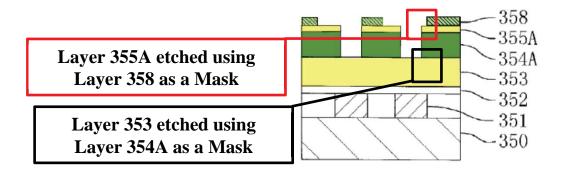

43. The '696 patent avoids damaging low-k materials by practicing certain patterning, lithography and etching, methods. An intermediary material is patterned with a photolithography resist, and the resist is removed by ashing without damaging an underlying delicate low-k material. *See, e.g.*, EX1001 3:2-4:67. This process may also be part of a photo-resist strip ("PRS"). The '696 discloses, for example, that the interconnection structure of the modified third embodiment can be formed by a method illustrated in Figures 15(a)-17(c). EX1001 18:59-20:49. For example, as illustrated in Figures 16(c)-16(d), annotated below, the patterned organic film 354A is dry-etched using the mask pattern 358 and the patterned second silicon dioxide film 355A as a mask (*e.g.*, using, as a mask, two layers having flush edges).<sup>2</sup> EX1001 19:50-54.

\_

<sup>&</sup>lt;sup>2</sup> As illustrated herein layers being used as a mask for a certain step are indicated in green, layers to be or having been etched for a certain step are indicated in yellow, and other layers are sometimes indicated in blue.

As illustrated in Figures 16(d)-17(a), annotated below, the silicon nitride film 352 is dry-etched using the patterned first silicon dioxide film 353A as a mask. EX1001 20:9-13.

### VI. Claim Construction

- A. Proper construction of "using the [first resist pattern/second resist pattern and the mask pattern/patterned third insulating film] as a mask" (Claim 13)

- 44. Claim 13 requires etching "using" various layers "as a mask." I understand that this term has already been preliminarily construed by the Board at Institution. ID at 15. Per the Board's construction, "using" one or more layers "as a mask" during etching means using the one or more layers to define areas for etching. *Id.* (defining the term "using the [designated layer] for etching" as "using

the [designated layer] to define areas for etching").<sup>3</sup> I agree with this construction. I also agree with the Board that a layer positioned between an overlying layer and an underlying layer being etched also acts as a mask, within the meaning of claim 13, in an instance where the overlying layer also is removed during etching, and thus, the intermediate layer acts to shield the layer being etched. *See* ID 18, fn.7.

- 45. This construction of the term is consistent with the use of the term throughout the '696 patent specification, which discloses numerous examples of structures being used as masks during etching; in each case, the structures are defining areas for etching. *See, e.g.*, EX1001 22:47-24:19, 24:54-26:34, 26:52-27:60, 27:62-29:20, 29:62-31:26, 31:49-32:9; Figs. 21-37. For example, for the limitation "using the second resist pattern and the mask pattern as a mask" in step 13(h), both the second resist pattern and the mask pattern must actually be *used* to *define areas for etching*—it would not satisfy this limitation to have either a second resist pattern or a mask pattern that does not define such an area.

- 46. By way of further example, the '696 patent teaches how both the second resist pattern and the mask pattern are used to define areas for etching: the underlying layer is patterned (etched) where the openings of the resist pattern and

<sup>&</sup>lt;sup>3</sup> The Board has replaced the terms "[first resist pattern/second resist pattern and the mask pattern/patterned third insulating film]" with "[designated layer]." ID 15.

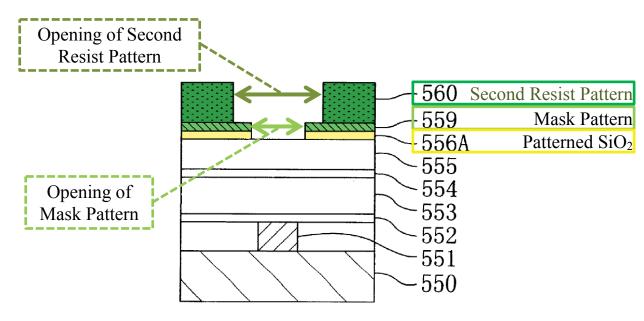

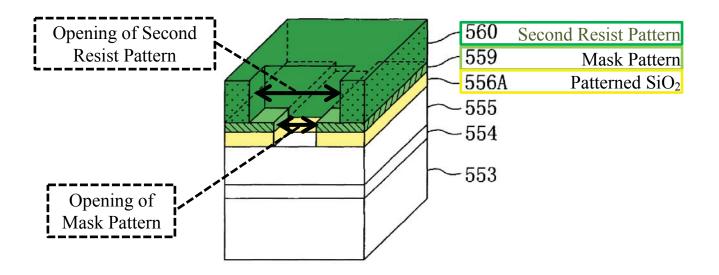

the openings of the mask pattern overlap. *See, e.g.*, EX1001 8:1-6 ("[T]he openings of the patterned third insulating film for forming contact holes are formed in respective regions where the openings of the second resist pattern for forming contact holes overlap with corresponding openings of the mask pattern for forming wiring grooves."), 7:62-8:7, 25:52-57, 26:63-27:3, 27:19-60, 31:60-67, Figs. 25(c), 27(b), 34(b), 37(a)-(b). Figures 25(c) and 27(b), for example, together illustrate using both the second resist pattern and the mask pattern as a mask, showing that the underlying insulating film (556A) is etched only where the openings of the second resist pattern (560) and the mask pattern (559) overlap, and that both the second resist pattern (560) and the mask pattern (559) define the area to be etched:

EX1001, FIG. 25(c).

EX1001, FIG. 27(b).

47. Contemporaneous dictionary definitions further support the above construction of "using the [designated layer] as a mask." *See*, *e.g.*, EX2001, 3 (defining masking as "[a]pplying a covering or coating on a semiconductor surface to provide a masked area for selective deposition or etching"); EX2002, 3 (defining a mask as "[a] device ... used to shield selected portions of a base during a deposition process," and a "template used to etch circuit patterns on semiconductor wafers"); EX2003, 4; EX2004, 3 (defining a mask as "[a]n object, stencil, or other device which is applied or placed upon a surface, so as to permit the selective passing of particles, beams, rays, substances, and so on, to form any desired patterns," and the use of said object "to selectively shield portions of semiconductor wafers, or other materials, during manufacturing").

- 48. I understand that the Board, based on the record then before it and without the benefit of my testimony about how this term would be understood by a person of ordinary skill in the art, has imposed an additional negative limitation upon the construction of "using the [designated layer] as a mask." Although the Board construed "using the [designated layer] as a mask" as "using the [designated layer] to define areas for etching," the Board has also imposed an additional negative limitation to exclude "a layer, positioned between an overlying layer and the layer being etched and having an edge in line and flush with an edge of the overlying layer" from being "used as a mask" within the context of claim 13. ID 18. I disagree with this additional negative limitation.

- 49. This exclusion of using two layers having flush edges as a mask is not supported by the claim language and is: (1) inconsistent with the disclosure the '696 patent and the priority document of the '696 patent (the '371 application) as understood by a person of ordinary skill in the art, and (2) inconsistent with the plain and ordinary meaning and understanding of a person of ordinary skill in the art as further demonstrated by a publication by Petitioner's expert.

- 1. The exclusion of using two layers having flush edges as a mask is inconsistent with the understanding of a skilled person in view of the disclosure of the '696 patent and the '371 application

- 50. I understand that claim constructions that exclude a preferred embodiment are rarely, if ever, correct.

- 51. The '696 patent discloses three preferred embodiments that use two layers having flush edges as a mask (the modified third embodiment (also referred to as the "third embodiment variant" or "variant of third embodiment"), third embodiment, and modified fifth embodiment).

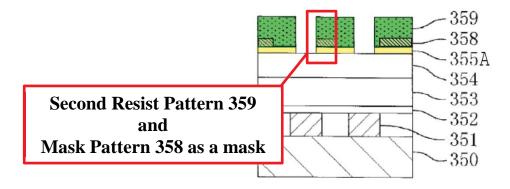

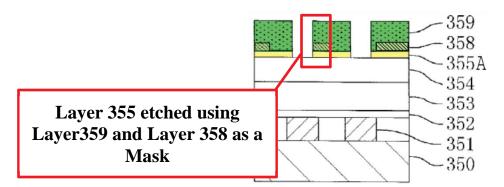

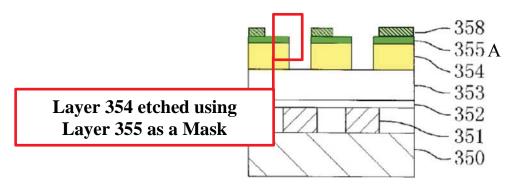

- 52. In the modified third embodiment, the '696 patent discloses dryetching the patterned organic film 354A "using the mask pattern 358 and the patterned second silicon dioxide film 355A ... as a mask." EX1001 19:50-53. This process of using two flush layers (358 and 355A) as a mask to etch layer 354A is illustrated in annotated Figures 16(c) and 16(d), provided below. Layer 358 (green) and layer 355A (light green) have edges that are flush, and are used as a mask to etch underlying layer 354A (yellow) in Fig. 16(c) to form the structure of Fig. 16(d).<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> As illustrated herein layers being used as a mask for a certain step are indicated in green, layers to be or having been etched for a certain step are indicated in yellow, and other layers are sometimes indicated in blue.

- 53. This modified third embodiment of the '696 patent is fully supported by the '371 application. Figures 16(c) and 16(d) of the '696 patent correspond to Figures 16(c) and 16(d) of the '371 application. *Cf.* EX1001 Figs.16(c)-(d) with EX1014 Figs.16(c)-(d). The passages of the '696 patent that describe "using the mask pattern 358 and the patterned second silicon dioxide film 355A ... as a mask" are present in the '371 application. *cf.* EX1001 19:50-53 with EX1014 ¶0095].

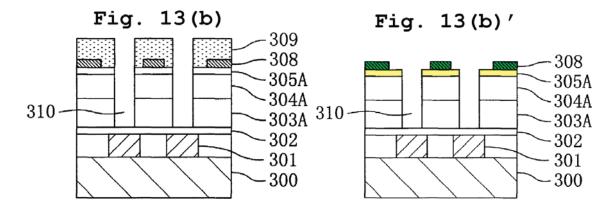

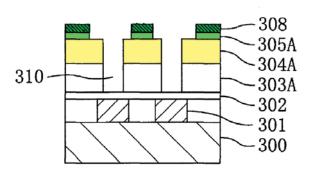

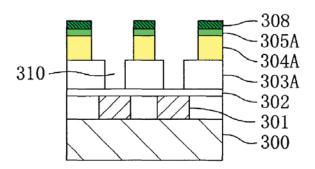

- 54. In the third embodiment, the '696 patent discloses dry-etching a patterned low-dielectric-constant SOG film 304A "using the mask pattern 308 and the patterned second organic-containing silicon dioxide film 305A ... as a mask." EX1001 17:34-40. This process of using two flush layers (308 and 305A) as a mask to etch layer 304A is illustrated in the sequence of annotated figures based on Figures 13(b) and 13(c), provided below, forming wiring grooves 311 in the example.

- 55. Starting from Fig. 13(b), resist layer 309 is removed, resulting in the structure of Fig. 13(b)'. EX1001 Fig. 13(b), 17:30-31.

<sup>&</sup>lt;sup>5</sup> Figures indicated with a ', '', or ''' or -[ ] herein have been modified from their original appearance to reflect other disclosures as discussed herein.

56. Next, from Fig. 13(b)', layer 305A is dry-etched using layer 308 as a mask, resulting in the structure of Fig. 13(b)'', where underlying layer 305A has an edge that is in line and flush with overlying layer 308. EX1001 17:31-35.

Fig. 13(b)"

57. Next, from Fig. 13(b)", layer 304A is dry-etched "using the mask pattern 308 and the patterned second organic-containing silicon dioxide film 305A" (which have flush edges) "as a mask," resulting in the structure of Fig. 13(c). EX1001 17:35-40, Fig. 13(c).

Fig. 13(c)

- 58. This third embodiment of the '696 patent is fully supported by the '371 application. Figures 13(b) and 13(c) of the '696 patent correspond to Figures 13(b) and 13(c) of the '371 application. *Cf.* EX1001 Figs.13(b)-(c) with EX1014 Figs.13(b)-(c). The passages of the '696 patent that describe the sequence of operations that includes "using the mask pattern 308 and the patterned second organic containing-silicon dioxide film 305A ... as a mask" are present in the '371 application. *cf.* EX1001 17:30-40 with EX1014 ¶[0080].

- 59. In a certified translation of the '371 application to which the '696 patent claims priority provided by Petitioner, paragraph [0094] (describing the modified third embodiment) has been translated to recite using layers 355A and 354A "as masks" to etch layer 353, and paragraph [0095] (also describing the modified third embodiment) has been translated to recite using layers 358 and 355A "as masks" to etch layer 354A. However, I understand these translated paragraphs to be inconsistencies and errors in the translation, and that the correct translations for paragraph [0094] should recite using layers 355A and 354A "as a

mask" to etch layer 353 and should recite using layers 358 and 355A "as a mask" to etch layer 354A. EX2013 ¶¶8-17. Even if the word could be translated to mean "a mask" or "masks," a person having ordinary skill in the art would have understood the word to refer to "a mask" in the context of these paragraphs.

For example, within the same certified translation provided by 60. Petitioner, a similar passage at paragraph [0080] has been translated to describe using two layers 308 and 305A "as a mask" to etch layer 304A. EX1014 ¶[0080]; EX2013 ¶8-9. I understand that other paragraphs within the certified translation use the same Japanese characters and are translated in singular form. EX1014 ¶¶[0094],[0095]; EX2013 ¶¶8-17. Additionally, in an English language translation of the '371 application provided by the applicant to the European Patent Office, the passages at paragraphs [0080], [0094], and [0095] were translated as using two layers having flush edges "as a mask" in the singular form. EX2012 at 30:11-15, 34:20-24, 35:1-4. This understanding of using two layers having flush edges "as a mask" is consistent with the understanding of a person of ordinary skill, as I describe further below in the context of multi-layer resists as masks. See §VI.2. Nonetheless, both translations have substantially the same meaning in the context of flush edges. Using two layers as "masks" to etch a third layer, or using two layers as "a mask" to etch a third layer, have the same result when the first two

layers have flush edges. Even if it were determined that Petitioner's translation were not in error, it would not alter my opinions.

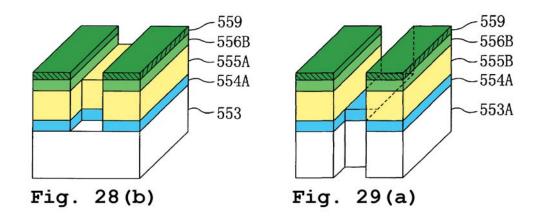

61. The modified fifth embodiment of the '696 patent discloses dryetching a patterned second organic film 55A "using the mask pattern 559 and the patterned silicon dioxide film 556B as a mask ...." EX1001 26:15-19. This process is illustrated below in annotated versions of Figs.28(b) and 29(a). *Id.* Figs.28(b) and 29(a). These annotated figures provide a three dimensional view of the process of using two layers having flush edges as a mask. As seen below, layers 559 and 556B (both colored green), are used to etch layer 555A to uncover layer 554A.

62. Thus, at least three embodiments, two of which are supported by the '371 application, clearly disclose using two layers having flush edges as a mask. Excluding the use of two layers having flush edges as a mask is inconsistent with these disclosures, incorrectly excludes these three embodiments, and thus is incorrect.

- 2. The exclusion of using two layers having flush edges as a mask is inconsistent with the plain and ordinary meaning in view of the disclosure of the '696 patent and the '371 application as understood by a person of ordinary skill in the art.

- (1) A skilled person understands that two layers having flush edges may be used as a mask

- (a) The Sidewalls and Top Surfaces of a Layer Serve as a Mask

- 63. In imposing the additional negative limitation, the Board has taken a narrow view that considers only top surfaces of a layer and excludes sidewalls of a layer from defining areas for etching that is inconsistent with the term's plain and ordinary meaning in view of the claims and the specification for at least the reasons discussed above. *See* ID 18. A person of ordinary skill in the art would have understood that two layers together act as a mask (*i.e.*, define areas for etching) when etching is performed if each of the two layers has at least some part of its surface exposed to the etchant and thereby defines areas for etching by substantially preventing the etchant from reaching certain areas. That is, even if the top surface of the interlayer material (*i.e.*, the layer underlying the top layer) is not exposed, it still defines an area for etching if its exposed side surface substantially prevents the etchant from reaching and etching certain areas.

- 64. A person of ordinary skill in the art would have understood that in an etching process, etchant does not flow in a perfectly vertical direction. For example, in an anisotropic process, there is some amount of etchant that flows in a

horizontal direction impacting against sidewalls of a pattern. Thus, a mask's function is not only to define areas for etching by blocking the etchant at the mask's top surface, but also to define areas for etching by blocking the etchant through its side surface. This resistance of the sidewalls to etching becomes important when, *e.g.*, defining high aspect ratio patterns (*e.g.*, as used in the formation of contact holes).

- 65. One example of an orientation where two layers act as a mask is when edges of the two layers line up—*i.e.*, are "flush"—and an etchant extends down to a layer that underlies the two layers. In such an orientation, an interlayer material (the layer that is underlying the top layer) acts as a mask if at least some part of a side surface of the interlayer is exposed such that it substantially blocks the etchant from reaching certain areas, thereby defining an area for etching. As discussed further above (§VI.A.1), the '696 patent describes several embodiments that use two layers having flush edges as a mask to define areas for patterning lower layers.

- 66. By blocking the horizontal flow of etchant, sidewalls of a layer (*e.g.*, an overlying layer or intermittent layer) controls the flow of etchant thereby defining areas of an underlying film for patterning. I have provided a figure below to illustrate this. The resulting etch would also be different without the intervening layer (*e.g.*, Layer 2 below)—etching a wider hole than the opening in the first layer (*e.g.*, Layer 1 below).

- 67. A person of ordinary skill in the art would have understood that Layer 1's bottom portion bordering the hole is part of the mask. There is no meaningful difference between the function of the material bordering the hole at the top of Layer 2 from the material bordering the hole at the very bottom of Layer 1. Layer 1 and Layer 2 act together as a mask as shown above. A person or ordinary skill in the art would have understood that Layer 1 and Layer 2 together act as "a pattern of opaque material used to shield selected areas of a surface (as of a semiconductor) in deposition or etching (as in producing an integrated circuit)." EX3001 (Merriam-Webster Dictionary) 1.

- 68. I note that a person of ordinary skill would have understood the concept of etch selectivity, where particular materials are more sensitive to (e.g.,

more readily etched by) an etchant than other materials. Etch selectivity would cause the etchant to etch those particular materials at a faster rate than the other materials. A material used in semiconductor fabrication generally has at least some etch sensitivity to a conventional etchant, and so at least some amount (even if insignificant or barely noticeable) would be etched by the etchant. But when the material has a very low sensitivity to an etchant, a person of ordinary skill in the art would have understood that the material's exposed surface can substantially block the etchant during etching (*i.e.*, act as a mask).

#### (b) Multi-Layer Resists are an Example of Using Two Flush Layers as a Mask

69. Using two flush layers as mask can provide technical benefits. For example, as described in §4.3.1 of the "Handbook of VLSI Microlithography" ("Helbert") (2001), "[m]ulti-layer processing techniques" where layers of radiation sensitive, non-photoresistive organic, and/or inorganic materials are stacked together to server as a "total patterning layer." EX2015 at pp.260-261 ("Multi-layer processing techniques, where layers of radiation sensitive (top), nonphotosensitive organic, and/or inorganic materials sandwiched together to become the total patterning layer…").

- (2) Dr. Smith's Assertion that the '696 Patent's Disclosure of Using Two Layers having Flush Edges as a Mask is Inconsistent with the Rest of the '696 Patent Disclosure is Incorrect

- 70. I understand that Dr. Smith has asserted during his deposition that passages from the '696 patent that describes using two layers that have flush edges (e.g., layers 358 and 355A) as a mask to etch underlying layer 354A are inconsistent with the other embodiments of the '696 patent. EX2010 45:1-47:8. I disagree. As discussed above, the '696 patent discloses three embodiments that expressly use two layers having flush edges as a mask (the modified third embodiment, third embodiment and modified fifth embodiment). Dr. Smith gives no basis to justify simply ignoring these disclosures by labeling them (incorrectly) as inconsistent.

- 71. Dr. Smith's testimony is also inconsistent with his own publication which describes using multiple layers in a resist (*e.g.*, a multi-layer resist). Dr. Smith is an author and editor of a book chapter entitled "Multilayer Resist Technology." EX2010 49:6-50:9; EX2018 at 657. As Dr. Smith himself confirmed, his book states that a multilayer resist techniques use "physically distinct layers to separate the imaging function from the etch resistance, planarization and reflection suppression function." EX2010 49:6-50:9; EX2018 at 657. An earlier edition of Dr. Smith's book published in 1998 also includes this passage. EX2017 at 592. As illustrated in Fig. 12.3(c), reproduced below from

Smith's book chapter, a multi-layer resist including multiple layers having flush edges (*e.g.*, a planarizing layer, an intermediate etch stop layer, and an imaging layer) is used to define areas for etching a substrate. EX2010 50:10-20, 58:8-59:1; EX2018 at 642-643 ("Three resist layers may be used to allow specific feature shaping..."). This passage is also present in the earlier edition of Dr. Smith's book published in 1998. EX2017 at 574, 592.

EX2017, Fig. 12.3(c) (annotated to show masking layers in green and substrate in yellow)

72. Dr. Smith himself acknowledged that these multiple layers are used to etch a "substrate thin film material…using this process" EX2010 64:5-65:8. Thus,

Petitioner's expert Smith, himself has acknowledged that multiple layers having flush edges (like the multilayer resist in his own text) may be used as a mask.

73. Other references recognize that "multi-layer processing techniques" that collectively form a "total patterning layer" for etching – *i.e.*, for use as a mask – were "common in semiconductor and computer manufacturing R & D labs." *See*, *e.g.*, EX2015 at p.260 ("Multi-layer processing techniques, where layers of radiation sensitive (top), nonphotosensitive organic, and/or inorganic materials sandwiched together to become the total patterning layer, have become common in semiconductor and computer manufacturing R & D labs."). These same techniques were in use in the field in the late 1990s as well. *E.g.*, EX2017 574, 592.

#### VII. Grill Is Not Prior Art to the '696 Patent

74. I understand that Petitioner is asserting that Grill (U.S. Patent No. 6,140,226) is prior art to the '696 patent. Pet. at 24-31. I also understand that in order for Grill to serve as prior art to the '696 patent, the priority date of Grill (*e.g.*, earliest filing date to which Grill is entitled) must antedate the priority date of the '696 patent (*e.g.*, earliest filing date to which the '696 patent is entitled). I understand Grill was filed on July 30, 1998, and claims priority to U.S. Provisional Patent No. 60/071,628 ("the '628 application," also "Grill provisional"), filed on January 16, 1998. EX1005 1:6-8. I understand the '696 patent was filed on March 23, 1999, and claims priority to Japanese Patent Application No. 10-079371

("the '371 application"), filed on March 26, 1998. I further understand that in order for a patent reference to be entitled to the filing date of its provisional application, the disclosure of the provisional application must provide written description and enablement support for the claims of the patent reference. *See* §IV.C. I further understand that, similarly, in order for a claim of a patent to be entitled to the filing date of a foreign patent application, the claim of the patent must be supported by the foreign patent application. *See id*.

75. As discussed below, based on my review of Grill and the '628 application, Grill is not entitled to the priority date of the '628 application at least because it does not disclose a step of transferring a pattern into a dielectric layer while concurrently removing a layer or portion of resist, as required by each of Grill's independent claims. Thus, because Grill is not entitled to the priority date of the '628 application, the earliest date to which Grill is entitled to priority is the filing date of Grill, July 30, 1998. Furthermore, as discussed below, based on my review of the '696 patent and the '371 application, claim 13 of '696 patent is entitled to the priority date of the '371 application, March 26, 1998. Because Grill's earliest priority date does not antedate the earliest priority date of claim 13 of the '696 patent, I understand that Grill is not prior art to claim 13 of the '696 patent.

- A. Claim 13 of the '696 Patent is fully supported by the foreign priority document and is entitled to the claimed March 28, 1998 priority date

- 76. I understand that a claim is entitled to an earlier filing date of a foreign priority document if the foreign priority document enables and provides written description support for the claims, as explained above in § IV.C.

- 77. I understand that Petitioner and Dr. Smith assert that claim 13 reads onto the fifth and sixth embodiments of the '696. Pet. at 7; EX1002 at ¶48. However, as discussed below, the '371 application includes several embodiments, such as the third embodiment and variant of the third embodiment. Claim 13 of the '696 patent is fully supported by at least the variant of the third embodiment. The '371 describes the claimed invention in sufficient detail that one skilled in the art can reasonably conclude that applicant had possession of the claimed invention. The '371 application describes the subject matter claimed in claim 13 and enables one skilled in the art to practice the claimed invention without undue experimentation. I provide a brief summary of the support below.

- 1. Claim 13 (Preamble) "A method for forming an interconnection structure, comprising the steps of:"

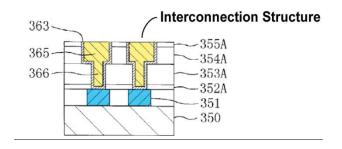

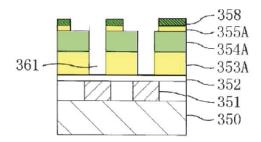

- 78. The '371 application discloses a method for "forming an interconnection structure" over first metal wiring 351. *See*, *e.g.*, EX1014 ¶¶[0089]-[0090], FIG. 17(c).

EX1014, Fig. 17(c) (annotations and coloring added to show wiring structure in yellow, and first metal wiring 351 in blue).

## 2. Claim 13 (step a) – "forming a first insulating film over lower-level metal interconnects;"

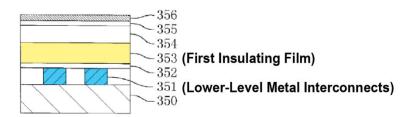

79. The '371 application discloses a step of forming a first insulating film (e.g., first silicon dioxide film 353) over lower-level metal interconnects (e.g., first metal wiring 351). See, e.g., EX1014 ¶[0090], Fig. 15(a).

EX1014, Fig. 15(a) (annotations and coloring added to show first insulating film 353 in yellow and lower-level metal interconnects 351 in blue)

- 3. Claim 13 (step b) "forming a second insulating film, having a different composition than that of the first insulating film, over the first insulating film;"

- 80. The '371 application discloses a step of forming a second insulating film (e.g., organic film 354), having a different composition than that of the first

insulating film (*e.g.*, first silicon dioxide film 353), over the first insulating film (*e.g.*, first silicon dioxide film 353). *See*, *e.g.*, EX1014 ¶[0090], Fig. 15(a). Silicon dioxide film 353 is not an organic film, and thus has a different composition than organic film 354.

EX1014, Fig. 15(a) (annotations and coloring added to show second insulating film 354 in yellow and first insulating film 353 in blue).

- 4. Claim 13 (step c) "forming a third insulating film, having a different composition than that of the second insulating film, over the second insulating film;"

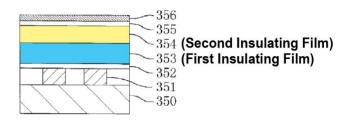

- 81. The '371 application discloses a step of forming a third insulating film (e.g., a second silicon dioxide film 355), having a different composition than that of the second insulating film (e.g., organic film 354), over the second insulating film (e.g., organic film 354). See, e.g., EX1014 ¶[0090], Fig. 15(a). Second silicon dioxide film 355 is not an organic film, and thus has a different composition than organic film 354.

EX1014, Fig. 15(a) (annotations and coloring added to show third insulating film 355 in yellow and second insulating film 354 in blue).

## 5. Claim 13 (step d) – "forming a thin film over the third insulating film;"

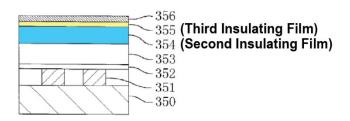

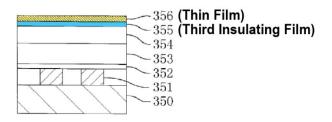

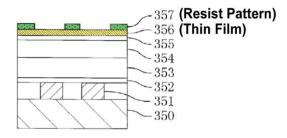

82. The '371 application discloses a step of forming a thin film (e.g., titanium nitride film 356) over the third insulating film (e.g., a second silicon dioxide film 355). See, e.g., EX1014 ¶[0090], Fig. 15(a).

EX1014, Fig. 15(a) (annotations and coloring added to show thin film 356 in yellow and third insulating film 355 in blue).

- 6. Claim 13 (step e) "forming a first resist pattern on the thin film, the first resist pattern having openings for forming wiring grooves;"

- 83. The '371 application discloses a step of forming a first resist pattern (e.g., first resist pattern 357) having opening for the formation of wiring grooves

on the thin film (e.g., titanium nitride film 356). See, e.g., EX1014 ¶[0092], Fig. 15(b).

EX1014, Fig. 15(b) (annotations and coloring added to show first resist pattern 357 in green and thin film 356 to be etched in yellow).

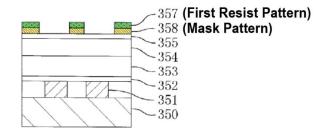

- 7. Claim 13 (step f) "etching the thin film using the first resist pattern as a mask, thereby forming a mask pattern out of the thin film to have the openings for forming wiring grooves;"

- 84. The '371 application discloses a step of etching the thin film (*e.g.*, titanium nitride film 356) using the first resist pattern (*e.g.*, first resist pattern 357) as a mask, thereby forming a mask pattern (*e.g.*, mask pattern 358) out of the thin film (*e.g.*, titanium nitride film 356) to have the openings for forming wiring grooves. *See*, *e.g.*, EX1014 ¶[0092], Fig. 15(c).

EX1014, Fig. 15(c) (annotations and coloring added to show first resist pattern 357 in green and mask pattern 358 in yellow).

- 8. Claim 13 (step g) "removing the first resist pattern and then forming a second resist pattern on the third insulating film and the mask pattern, the second resist pattern having openings for forming contact holes;"

- 85. I understand that Petitioner asserts that this step is not disclosed in the '371 application's first, second, and fourth embodiments. Pet. at 16-23; EX1002 ¶¶122-127. However, Petitioner never argues this step is missing in the '371 application's third embodiment variant (See Pet. at 16-23(raising this issue only in connection with first, second, and fourth embodiments)), and for good reason: the variant of the third embodiment discloses this step. See, e.g., EX1014 ('371 application) ¶[0093]. The '371 application discloses a step of removing the first resist pattern (e.g., first resist pattern 357) and then forming a second resist pattern (e.g., second resist pattern 359) on the third insulating film (e.g., second silicon dioxide film 355) and the mask pattern (e.g., mask pattern 358), the second resist pattern having openings for forming contact holes. See, e.g., EX1014 ¶[0093] ("Subsequently, as shown in Figure 16(a), the first resist pattern 357 is removed and then a second resist pattern 359 having openings for the formation of contact holes is formed on the second silicon dioxide film 355."), Fig. 16(a).

EX1014, Fig. 16(a) (annotations and coloring added to show second resist pattern 359 in green and mask pattern 358 in yellow).

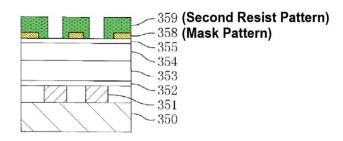

- 9. Claim 13 (step h) "dry-etching the third insulating film using the second resist pattern and the mask pattern as a mask, thereby patterning the third insulating film to have the openings for forming contact holes;"

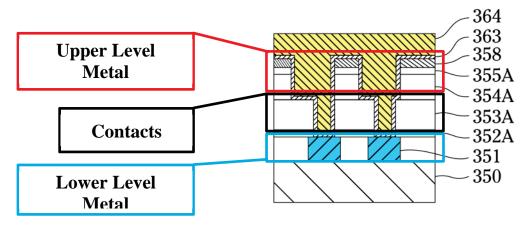

- 86. I understand that Petitioner asserts that this step is not disclosed by the '371 application. Pet. at 16, 19-21; EX1002 ¶¶122-0124, 128-136. Petitioner and Petitioner's expert Dr. Smith conclude that the variant of the third embodiment does not disclose the mask pattern 358 as a mask. Pet. at 19-21; EX1002 ¶[0133]. I disagree. Petitioner and Petitioner's expert Dr. Smith overlooks support in the passages of the '371 application that discloses a step of dry-etching the third insulating film (*e.g.*, second silicon dioxide film 355) using the second resist pattern (*e.g.*, second resist pattern 359) and the mask pattern (*e.g.*, mask pattern 358) as a mask, thereby patterning the third insulating film (*e.g.*, second silicon dioxide film 355) to have the openings for forming contact holes. *See, e.g.*, EX1014 ¶¶[0093]-[0096], Fig. 16(a)-Fig. 16(c).

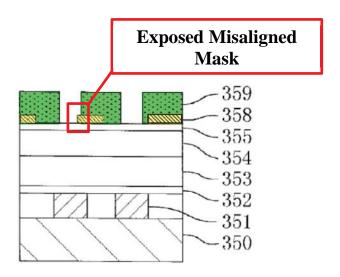

87. The '371 application's variant of the third embodiment discloses step (h) of claim 13. For example, the '371 application discloses that the second resist pattern 359 may be misaligned during fabrication. EX1014 ¶[0096]. To address this misalignment, the '371 application describes etching the underlying mask pattern 358 using the second resist pattern 359 as a mask. *Id.* As a result, edges of the second resist pattern 359 line up and become flush with the edges of the mask pattern 358. Accordingly, when the underlying third insulating film is subsequently patterned, both the second resist pattern and the mask pattern together define areas for the patterning and are both "used . . . as a mask," as recited in claim 13. Specifically, the '371 application discloses:

If there is a concern that the second resist pattern 359 has been misaligned with the first resist pattern 357, then the mask pattern 358 should be dry-etched using the second resist pattern 359 as a mask before the second silicon dioxide film 355 is dry-etched using the second resist pattern 359 as a mask. That is to say, if the mask pattern 358 is exposed to the openings of the second resist pattern 359 for the formation of contact holes because of the misalignment of the second resist pattern 359 with the first resist pattern 357, then the mask pattern 358 is dry-etched using the second resist pattern 358 as a mask. In this manner, the openings of the mask pattern 358 are expanded to include the openings for the formation of wiring grooves and contact holes.

EX1014 ¶[0096] (variant of third embodiment).

88. The series of annotated figures below illustrate this patterning in case of misalignment, according to the disclosure of the '371 application discussed above. The first annotated figure below shows the layers "if the mask pattern 358 is exposed to the openings of the second resist pattern 359 for the formation of contact holes because of the misalignment[.]" EX1014 ¶[0096].

EX1014, Fig. 16(a) (modified according to EX1014 ¶[0096] and coloring added to show second resist pattern 359 in green and exposed portion of misaligned mask pattern 358 in yellow).

89. The second annotated figure below shows the layers after "the mask pattern 358 is dry-etched using the second resist pattern 359 as a mask." EX1014 ¶[0096].

EX1014, Fig. 16(a) (modified according to EX1014 ¶[0096] and coloring added to show second resist pattern 359 in green and etched misaligned mask pattern 358 in yellow).

90. The third annotated figure below shows that, when the underlying third insulating film (355) is thereafter etched, both the second resist pattern (359) and the mask pattern (358) necessarily define the areas for etching of the third insulating film (355). As such, etching of the "third insulating film [355]" is done "using the second resist pattern [359] and the mask pattern [358] as a mask" as required by step (h) of claim 13. EX1014 ¶[0093].

EX1014, Fig. 16(a) (modified according to EX1014 ¶¶[0093], [0096] and coloring added to show second resist pattern 359 in green, etched misaligned mask pattern 358 in light green, and etched layer 355A in yellow).

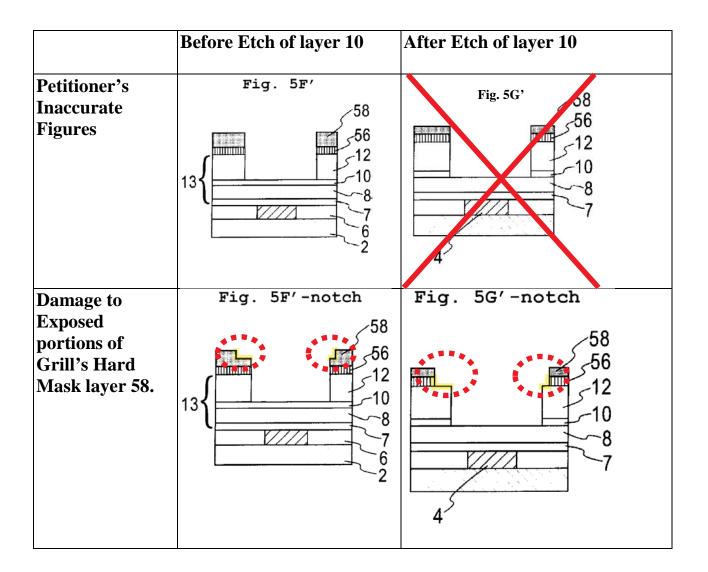

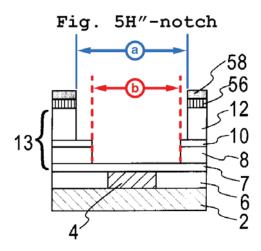

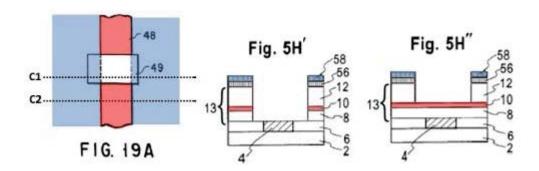

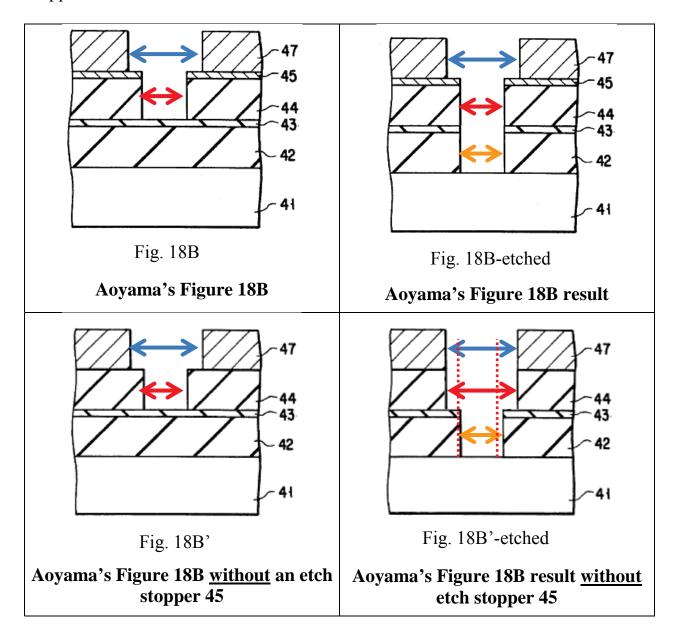

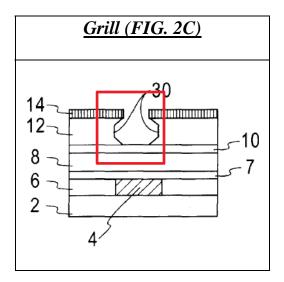

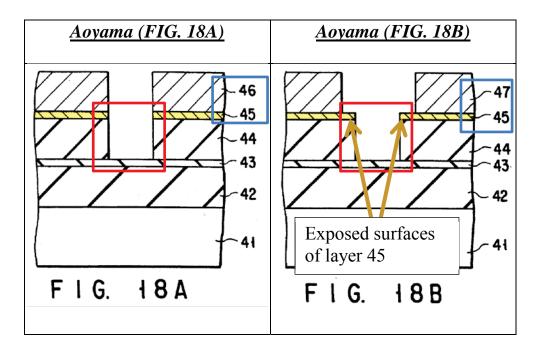

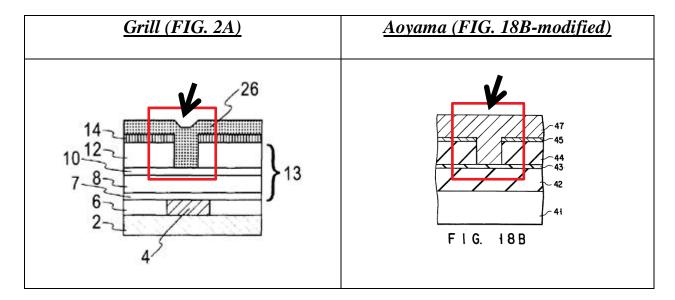

- 91. Additionally, the '371 application provides support for using two layers as a mask in a similar manner as discussed above with reference to Figures 13(b)-13(c) and 16(c)-16(d). *See* §VI.A.1. For example, Figures 13(b) and 13(c) and paragraph [0080] of the '371 application provides similar support as Figures 13(b) and 13(c) and 17:34-40 of the '696 patent. For example, Figures 16(c) and 16(d) and paragraph [0095] of the '371 application provides similar support as Figures 16(c) and 16(d) and 19:50-53 of the '696 patent.