# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD CAVIUM, INC. Petitioner v. ALACRITECH, INC. Patent Owner Case IPR. No. Unassigned U.S. Patent No. 8,805,948 Title: INTELLIGENT NETWORK INTERFACE SYSTEM AND METHOD FOR PROTOCOL PROCESSING

Petition For *Inter Partes* Review of U.S. Patent No. 8,805,948 Under 35 U.S.C. §§ 311-319 and 37 C.F.R. §§ 42.1-.80, 42.100-.123

## **Mail Stop "PATENT BOARD"**

Patent Trial and Appeal Board U.S. Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

# TABLE OF CONTENTS

|    |      |                                                              | Page |  |

|----|------|--------------------------------------------------------------|------|--|

| 1. | INTI | RODUCTION                                                    | 1    |  |

| 2. | REQ  | UIREMENTS FOR PETITION FOR INTER PARTES REVIEW.              | 1    |  |

|    | 2.1. | Grounds for Standing (37 C.F.R. § 42.104(a))                 | 1    |  |

|    | 2.2. | Notice of Lead and Backup Counsel and Service Information    | 1    |  |

|    | 2.3. | Notice of Real-Parties-in-Interest (37 C.F.R. § 42.8(b)(1))  | 2    |  |

|    | 2.4. | Notice of Related Matters (37 C.F.R. § 42.8(b)(2))           | 2    |  |

|    | 2.5. | Fee for Inter Partes Review                                  | 13   |  |

|    | 2.6. | Proof of Service                                             | 14   |  |

| 3. |      | NTIFICATION OF CLAIMS BEING CHALLENGED .104(B))              | 14   |  |

| 4. | BAC  | KGROUND OF TECHNOLOGY                                        | 14   |  |

|    | A.   | Layered Network Protocols                                    | 15   |  |

|    | B.   | TCP/IP                                                       | 16   |  |

|    | C.   | Protocol Offload and Fast-Path Processing                    | 20   |  |

|    | D.   | Direct Memory Access                                         | 22   |  |

| 5. | OVE  | YERVIEW OF THE 948 PATENT2                                   |      |  |

| 6. | 948] | PATENT PROSECUTION HISTORY                                   | 25   |  |

| 7. | CLA  | IM CONSTRUCTION                                              | 27   |  |

|    | 7.1. | Applicable Law                                               | 27   |  |

|    | 7.2. | Construction of Claim Terms                                  | 27   |  |

| 8. | PER  | SON HAVING ORDINARY SKILL IN THE ART                         | 27   |  |

| 9. | DES  | CRIPTION OF THE PRIOR ART                                    | 28   |  |

|    | 9.1. | Thia                                                         | 28   |  |

|    | 9.2. | Tanenbaum96: A. Tanenbaum, Computer Networks, 3rd ed. (1996) | 32   |  |

|    | 9.3. | Stevens2: TCP-IP Illustrated, Vol.2                          | 38   |  |

|    | 9.4. | Motivations To Combine                                       | 40   |  |

|     |       | 9.4.1.  | Thia in combination with Tanenbaum96                                                                                                                                                                                                                                          | 40 |

|-----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |       | 9.4.2.  | Thia in combination with Tanenbaum96 and Stevens2                                                                                                                                                                                                                             | 43 |

| 10. | GRO   | UND #1: |                                                                                                                                                                                                                                                                               | 44 |

|     | 10.1. | Claim 1 |                                                                                                                                                                                                                                                                               | 45 |

|     |       | 10.1.1. | [1.P] A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising.                                                                                                           | 45 |

|     |       | 10.1.2. | [1.1] running, on the host computer, a protocol processing stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, with an application layer running above the TCP layer;                                                            | 47 |

|     |       | 10.1.3. | [1.2] initializing, by the host computer, a TCP connection that is defined by source and destination IP addresses and source and destination TCP ports;                                                                                                                       | 50 |

|     |       | 10.1.4. | [1.3] receiving, by the network interface, first and second packets, wherein the first packet has a first TCP header and contains first payload data for the application, and the second packet has a second TCP header and contains second payload data for the application; | 52 |

|     |       | 10.1.5. | [1.4] checking, by the network interface, whether the packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a FIN flag set, and checking whether the packets are out of order;               | 54 |

|     |       | 10.1.6. | [1.5] if the first packet has any of the exception conditions, then protocol processing the first TCP header by the protocol processing stack;                                                                                                                                | 56 |

|     |       | 10.1.7. | [1.6] if the second packet has any of the exception conditions, then protocol processing the second TCP header by the protocol processing stack;                                                                                                                              | 56 |

|     |       | 10.1.8. | [1.7] if the packets do not have any of the exception conditions, then bypassing host protocol processing of                                                                                                                                                                  |    |

|       |         | the TCP headers and storing the first payload data and the second payload data together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the first payload data and the second payload data. | 57 |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10.2. | Claim 3 |                                                                                                                                                                                                                                                                                     | 61 |

|       | 10.2.1. | [3] The method of claim 1, wherein storing the first payload data and the second payload data together in a buffer of the host computer is performed by a direct memory access (DMA) unit of the network interface                                                                  | 61 |

| 10.3. | Claim 6 |                                                                                                                                                                                                                                                                                     | 62 |

|       | 10.3.1. | [6] The method of claim 1, including comparing, by the network interface, the IP addresses and TCP ports of the packets with the source and destination IP addresses and source and destination TCP ports that define the TCP connection.                                           | 62 |

| 10.4. | Claim 7 |                                                                                                                                                                                                                                                                                     | 64 |

|       | 10.4.1. | [7] The method of claim 1, wherein checking whether the packets have certain exception conditions includes checking whether the packets have a RST flag set                                                                                                                         | 64 |

| 10.5. | Claim 8 |                                                                                                                                                                                                                                                                                     | 64 |

|       | 10.5.1. | [8] The method of claim 1, wherein checking whether the packets have certain exception conditions includes checking whether the packets have a SYN flag set                                                                                                                         | 64 |

| 10.6. | Claim 9 |                                                                                                                                                                                                                                                                                     | 65 |

|       | 10.6.1. | [9.P] A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising:                                                                                                                 | 65 |

|       | 10.6.2. | [9.1] receiving, by the network interface, a first packet having a header including source and destination Internet Protocol (IP) addresses and source and destination Transmission Control Protocol (TCP) ports:                                                                   |    |

|       | 10.6.3.  | [9.2] protocol processing, by the host computer, the first packet, thereby initializing a TCP connection that is defined by the source and destination IP addresses and source and destination TCP ports;                                                                                                                                           | 66 |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | 10.6.4.  | [9.3] receiving, by the network interface, a second packet having a second header and payload data, wherein the second header has IP addresses and TCP ports that match the IP addresses and TCP ports of the TCP connection;                                                                                                                       | 67 |

|       | 10.6.5.  | [9.4] receiving, by the network interface, a third packet having a third header and additional payload data, wherein the third header has IP addresses and TCP ports that match the IP addresses and TCP ports of the TCP connection;                                                                                                               | 68 |

|       | 10.6.6.  | [9.5] checking, by the network interface, whether the second and third packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a FIN flag set, and checking whether the packets are out of order;                                                                    | 69 |

|       | 10.6.7.  | [9.6] if the second packet has any of the exception conditions, then protocol processing the second packet by the host computer;                                                                                                                                                                                                                    | 69 |

|       | 10.6.8.  | [9.7] if the third packet has any of the exception conditions, then protocol processing the third packet by the host computer;                                                                                                                                                                                                                      | 70 |

|       | 10.6.9.  | [9.8] if the second and third packets do not have any of the exception conditions, then storing the payload data of the second and third packets together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the payload data of the second and third packets. | 70 |

| 10.7. | Claim 11 |                                                                                                                                                                                                                                                                                                                                                     | 71 |

|       | 10.7.1.  | [11] The method of claim 9, wherein storing the payload data of the second and third packets together                                                                                                                                                                                                                                               |    |

|       |           | in a buffer of the host computer is performed by a direct memory access (DMA) unit of the network interface                                                                                                                                                                                                                                                             | 71 |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10.8. | Claim 14  | l                                                                                                                                                                                                                                                                                                                                                                       | 71 |

|       | 10.8.1.   | [14] The method of claim 9, including comparing, by the network interface, the IP addresses and TCP ports of the second and third packets with the source and destination IP addresses and source and destination TCP ports that define the TCP connection.                                                                                                             | 71 |

| 10.9. | Claim 15  | ;                                                                                                                                                                                                                                                                                                                                                                       | 72 |

|       | 10.9.1.   | [15] The method of claim 9, wherein checking whether the second and third packets have certain exception conditions includes checking whether the packets have a RST flag set                                                                                                                                                                                           | 72 |

| 10.10 | .Claim 16 | )                                                                                                                                                                                                                                                                                                                                                                       | 73 |

|       | 10.10.1.  | [16] The method of claim 9, wherein checking whether the second and third packets have certain exception conditions includes checking whether the packets have a SYN flag set.                                                                                                                                                                                          | 73 |

| 10.11 | .Claim 17 | ·                                                                                                                                                                                                                                                                                                                                                                       | 74 |

|       | 10.11.1.  | [17.P] An apparatus for network communication, the apparatus comprising:                                                                                                                                                                                                                                                                                                | 74 |

|       | 10.11.2.  | [17.1] a host computer running a protocol stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, the protocol stack adapted to establish a TCP connection for an application layer running above the TCP layer, the TCP connection being defined by source and destination IP addresses and source and destination TCP ports; | 76 |

|       | 10.11.3.  | [17.2] a network interface that is connected to the host computer by an input/output bus, the network interface adapted to parse the headers of received packets to determine whether the headers have the IP addresses and TCP ports that define the TCP connection and to check whether the packets have certain exception                                            |    |

| Co             | onditions, including whether the packets are IP          |    |

|----------------|----------------------------------------------------------|----|

| fr             | ragmented, have a FIN flag set, or are out of order, the |    |

| n              | etwork interface having logic that directs any of the    |    |

| re             | eceived packets that have the exception conditions to    |    |

|                | he protocol stack for processing, and directs the        |    |

|                | eceived packets that do not have any of the exception    |    |

|                | onditions to have their headers removed and their        |    |

|                | ayload data stored together in a buffer of the host      |    |

| -              | omputer, such that the payload data is stored in the     |    |

|                | uffer in order and without any TCP header stored         |    |

|                | etween the payload data that came from different         |    |

|                | ackets of the received packets                           | 78 |

| -              | -                                                        |    |

| 10.12.Claim 19 |                                                          | 82 |

| 10.12.1. [1    | 19] The apparatus of claim 17, wherein the network       |    |

| ir             | nterface includes a direct memory access (DMA) unit      |    |

| tł             | hat is adapted to store the payload data in the buffer   | 82 |

| 10.13.Claim 21 |                                                          | 83 |

| 10 13 1 [3     | 21] The apparatus of claim 17, wherein the exception     |    |

| -              | onditions include having a RST flag set                  | 83 |

|                |                                                          |    |

| 10.14.Claim 22 |                                                          | 84 |

| 10.14.1. [2    | 22] The apparatus of claim 17, wherein the exception     |    |

| C              | onditions include having a SYN flag set                  | 84 |

| CONCLUSION     |                                                          | 84 |

|                |                                                          |    |

11.

# **Exhibit List**

| Exhibit #                                                                                        | Description                                                                                                                                                      |  |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ex.1001                                                                                          | U.S. Patent No. 8,805,948 ("948 Patent")                                                                                                                         |  |

| Ex.1002 Excerpts from Prosecution File History of U.S. Patent No. 8,805,948 ("948 File History") |                                                                                                                                                                  |  |

| Ex.1003                                                                                          | Declaration of Robert Horst                                                                                                                                      |  |

| Ex.1004                                                                                          | Curriculum Vitae of Robert Horst                                                                                                                                 |  |

| Ex.1005                                                                                          | U.S. Patent No. 5,768,618 ("Erickson")                                                                                                                           |  |

| Ex.1006                                                                                          | Tanenbaum, Andrew S., <i>Computer Networks</i> , Prentice-Hall, Inc., New Jersey (1996). ("Tanenbaum96")                                                         |  |

| Ex.1007                                                                                          | Transmission Control Protocol, "Darpa Internet Protocol Specification", RFC: 793, Sept. 1981. ("RFC 793")                                                        |  |

| Ex.1008                                                                                          | Stevens, W. Richard, <i>TCP/IP Illustrated Volume 1: The Protocols</i> , Addison-Wesley (1994). ("Stevens1")                                                     |  |

| Ex.1009                                                                                          | Lilinkamp, J., Mandell. R. and Padlipsky, M., "Proposed Host-<br>Front End Protocol", Network Working Group Request for<br>Comments: 929, Dec. 1984. ("RFC 929") |  |

| Ex.1010 Not Used                                                                                 |                                                                                                                                                                  |  |

| Ex.1011                                                                                          | Librarian Declaration of Rice Mayors regarding Andrew S. Tanenbaum, Computer Networks (3rd ed. 1996) (Ex.1006, "Tanenbaum96")                                    |  |

| Ex.1012                                                                                          | Not Used                                                                                                                                                         |  |

| Ex.1013                                                                                          | Stevens, W. Richard and Gary R. Wright, TCP/IP Illustrated Volume 2: The Implementation, Addison-Wesley (1995). ("Stevens2")                                     |  |

| Ex.1014                                                                                          | Not Used                                                                                                                                                         |  |

| Exhibit #                                                                                                                                                                                           | Description                                                                                                                                                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ex.1015                                                                                                                                                                                             | Thia, Y.H., Woodside, C.M., "A Reduced Operation Protocol Engine (ROPE) for a Multiple-Layer Bypass Architecture", Protocols for High Speed Networks (Dordrecht), 1995. ("Thia and Woodside")                                |  |

| Ex.1016  Biersack, E. W., Rütsche E., "Demultiplexing on the ATM Adapter: Experiments with Internet Protocols in User Space", Journal on High Speed Networks, Vol. 5, No. 2, May 1996. ("Biersack") |                                                                                                                                                                                                                              |  |

| Ex.1017                                                                                                                                                                                             | Rütsche, E., Kaiserswerth, M., "TCP/IP on the Parallel Protocol Engine", Proceedings, IFIP Conference on High Performance Networking, Liege (Belgium), Dec. 1992. ("Rütsche92")                                              |  |

| Ex.1018                                                                                                                                                                                             | Rütsche, E., "The Architecture of a Gb/s Multimedia Protocol Adapter", Computer Communication Review, 1993. ("Rütsche93")                                                                                                    |  |

| Ex.1019                                                                                                                                                                                             | Padlipsky, M. A., "A Proposed Protocol for Connecting Host<br>Computers to Arpa-Like Networks Via Directly-Connected Front<br>End Processors", Network Working Group RFC #647, Nov. 1974.<br>("RFC 647")                     |  |

| Ex.1020                                                                                                                                                                                             | U.S. Patent No. 5,619,650 ("Bach")                                                                                                                                                                                           |  |

| Ex.1021                                                                                                                                                                                             | U.S. Patent No. 5,915,124 ("Morris")                                                                                                                                                                                         |  |

| Ex.1022                                                                                                                                                                                             | Cooper, E.C., et al., "Protocol Implementation on the Nectar<br>Communication Processor", School of Computer Science, Carnegie<br>Mellon University, Sept. 1990. ("Cooper")                                                  |  |

| Ex.1023                                                                                                                                                                                             | Kung, H.T., et al., "A Host Interface Architecture for High-Speed Networks", School of Computer Science, Carnegie Mellon University and Network Systems Corporation. ("Kung")                                                |  |

| Ex.1024                                                                                                                                                                                             | Exhibit D to Declaration of Dr. Gregory L. Chesson in Support of Microsoft's Opposition to Alacritech's Motion for Preliminary Injunction: "Protocol Engine Handbook", Protocol Engines Incorporated, Oct. 1990. ("Chesson") |  |

| Exhibit # | Description                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex.1025   | Kanakia, H., Cheriton, D.R., "The VMP Network Adapter Board (NAB): High-Performance Network Communication for Multiprocessors", Communications Architectures & Protocols, Stanford University, Aug. 1988. ("Kanakia") |

| Ex.1026   | Kung, H.T., Cooper, E.C., et al., "Network-Based Multicomputers:<br>An Emerging Parallel Architectures", School of Computer Science,<br>Carnegie Mellon University. ("Kung and Cooper")                               |

| Ex.1027   | Dalton, C., et al., "Afterburner: Architectural Support for High-<br>Performance Protocols", Networks & Communications<br>Laboratories, HP Laboratories Bristol, July 1993. ("Dalton")                                |

| Ex.1028   | Murphy, E., Hayes, S., Enders, M., TCP/IP Tutorial and Technical Overview Fifth Edition, Prentice-Hall, Inc. New Jersey, (1995). ("Murphy")                                                                           |

| Ex.1029   | MacLean, A.R., Barvick, S. E., "An Outboard Processor for High<br>Performance Implementation of Transport Layer Protocols", IEEE<br>Globecom '91, Phoenix, AZ, Dec. 1991. ("MacLean")                                 |

| Ex.1030   | Clark, D.D., et al., "An Analysis of TCP Processing Overhead", IEEE Communications Magazine, June 1989. ("Clark")                                                                                                     |

| Ex.1031   | Provisional Application 60-061,809 ("Alacritech 1997 Provisional Application")                                                                                                                                        |

| Ex.1032   | Culler, E.C., et al., "Parallel Computing on the Berkeley NOW",<br>Computer Science Division, University of California, Berkeley.<br>("Culler")                                                                       |

| Ex.1033   | "Gigabit Ethernet Technical Brief: Achieving End-to-End<br>Performance", Alteon Networks, Inc. First Edition, Sept. 1996.<br>("Alteon")                                                                               |

| Ex.1034   | Smith, J.A., Primmer, M., "Tachyon: A Gigabit Fibre Channel Protocol Chip", Hewlett-Packard Journal, Article 12, Oc. 1996. ("Smith")                                                                                  |

| Exhibit #        | Description                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex.1035          | Patterson, D.A., Hennessy, J.L., <i>Computer Architecture: A Quantitative Approach</i> , Morgan Kaufmann Publishers, Inc., San Mateo, CA (1990). ("Patterson")                             |

| Ex.1036          | Internet Protocol, "Darpa Internet Protocol Specification", RFC: 791, Sept. 1981. ("RFC 791")                                                                                              |

| Ex.1037 Not Used |                                                                                                                                                                                            |

| Ex.1038          | Woodside, C. M., K. Ravindran, and R. G. Franks. "The protocol bypass concept for high speed OSI data transfer." IFIP Workshop on Protocols for High Speed Networks. 1990. ("Woodside")    |

| Exs.1039-1062    | Not Used                                                                                                                                                                                   |

| Ex.1063          | Librarian Declaration of Pamela Stansbury regarding Gary R. Wright & W. Richard Stevens, TCP/IP Illustrated: The Implementation (1995) (Ex.1013, "Stevens2").                              |

| Ex.1064          | Librarian Declaration of Lisa Rowlison de Ortiz re Y.H. Thia & C.M. Woodside, A Reduced Operation Protocol Engine (ROPE) for a Multiple-layer Bypass Architecture (1995) (Ex.1015, "Thia") |

#### 1. INTRODUCTION

Pursuant to 35 U.S.C. §§ 311-319 and 37 C.F.R. §§ 42.1-.80, 42.100-.123, Cavium, Inc. ("Petitioner" or "Cavium") hereby petitions the Patent Trial and Appeal Board to institute an *inter partes* review of claims 1, 3, 6-9, 11, 14-17, 19, and 21-22 of U.S. Patent No. 8,805,948, titled "Intelligent Network Interface System and Method for Protocol Processing" (Ex.1001, the "948 Patent"), and cancel those claims as unpatentable.

#### 2. REQUIREMENTS FOR PETITION FOR INTER PARTES REVIEW

## 2.1. Grounds for Standing (37 C.F.R. § 42.104(a))

Petitioner certifies that the 948 Patent is available for *inter partes* review and that Petitioner is not barred or estopped from requesting *inter partes* review of the challenged claims of the 948 Patent on the grounds identified herein.

## 2.2. Notice of Lead and Backup Counsel and Service Information

Pursuant to 37 C.F.R. §§ 42.8(b)(3), 42.8(b)(4), and 42.10(a), Petitioner provides the following designation of Lead and Back-Up counsel.

| Lead Counsel                                                                                                                                | Back-Up Counsel                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Patrick D. McPherson                                                                                                                        | David T. Xue, Ph.D.                                                                                                              |

| Registration No. 46,255                                                                                                                     | Registration No. 54,554                                                                                                          |

| (PDMcPherson@duanemorris.com)                                                                                                               | (DTXue@duanemorris.com)                                                                                                          |

| Postal & Hand-Delivery Address: Duane Morris LLP 505 9th Street, N.W., Suite 1000 Washington, DC 20004 T: (202) 776-5214; F: (202) 776-7801 | Postal & Hand-Delivery<br>Duane Morris LLP<br>2475 Hanover St.<br>Palo Alto, CA 94304<br>T: (650) 847-4153;<br>F: (650) 444-0459 |

| Attorney for Cavium, Inc.                                                                                                                   | Attorneys for Cavium, Inc.                                                                                                       |

## 2.3. Notice of Real-Parties-in-Interest (37 C.F.R. § 42.8(b)(1))

Petitioner, Cavium, Inc. is the real-party-in-interest. No other parties exercised or could have exercised control over this Petition; no other parties funded or directed this Petition. *See* Office Patent Trial Practice Guide, 77 Fed. Reg. 48759-60.

## 2.4. Notice of Related Matters (37 C.F.R. § 42.8(b)(2))<sup>1</sup>

The following judicial or administrative matters may affect or be affected by a decision in this proceeding: *Alacritech, Inc. v. CenturyLink, Inc.*, 2:16-cv-00693-JRG-RSP (E.D. Tex.); *Alacritech, Inc. v. Wistron Corp.*, 2:16-cv-00692-JRG-RSP (E.D. Tex.); *Alacritech, Inc. v. Dell Inc.*, 2:16-cv-00695-RWS-RSP (E.D. Tex.). In

<sup>&</sup>lt;sup>1</sup> These petitions will be filed concurrently or within a few days.

addition to this Petition, Petitioner is filing petitions for U.S. Patent Nos. 7,237,036; 7,337,241; 7,673,072; 7,945,699; 8,131,880; 7,124,205; and 9,055,104.

The 948 Patent is subject to a pending request for IPR filed by Intel on May 9, 2017 (IPR-2017-01395).

Alacritech has asserted one or more of the Asserted Patents or patents related to the Asserted Patents in the following actions:

- 1. U.S. Patent Nos. 6,427,171 and 6,697,868 are asserted in *Alacritech*, *Inc. v. Microsoft Corp.*, 3-04-cv-03284, (N.D. Cal);

- 2. U.S. Patent Nos. 7,124,205; 7,237,036; 7,337,241; 7,673,072; 8,131,880; 8,805,948; and 9,055,104 are asserted in *Alacritech, Inc. v. Wistron Corp.*, 2:16-cv-00692-JRG-RSP (E.D. Tex.);

- 3. U.S. Patent Nos. 7,124,205; 7,237,036; 7,337,241; 7,673,072; 8,131,880; 8,805,948; 9,055,104; and 7,945,699 are asserted in *Alacritech, Inc. v. Dell Inc.*, 2:16-cv-00695-RWS-RSP (E.D. Tex.);

- 4. U.S. Patent Nos. 7,124,205; 7,237,036; 7,337,241; 7,673,072; 8,131,880; 8,805,948; 9,055,104; and 7,945,699 are asserted in *Alacritech, Inc. v. CenturyLink, Inc.*, 2:16-cv-00693-JRG-RSP (E.D. Tex.).

The patent family to which the 036 Patent belongs contains 19 additional U.S. patents:

1. U.S. Patent Application No. 11/821,820 (filed Jun. 25, 2007, issued

- Mar. 2, 2010 as 7,673,072 patent);

- 2. U.S. Patent Application No. 10/092,967 (filed Mar. 6, 2002, issued Jul. 8, 2003 as 6,591,302 patent);

- 3. U.S. Patent Application No. 10/023,240 (filed Dec. 17, 2001, issued Nov. 15, 2005 as 6,965,941 patent);

- 4. U.S. Patent Application No. 09/970,124 (filed Oct. 2, 2001, issued Oct. 17, 2006 as 7,124,205 patent);

- 5. U.S. Patent Application No. 09/855,979 (filed May 14, 2001, issued Nov. 7, 2006 as 7,133,940 patent);

- 6. U.S. Patent Application No. 09/802,426 (filed Mar. 9, 2001, issued May 9, 2006 as 7,042,898 patent);

- 7. U.S. Patent Application No. 09/802,550 (filed Mar. 9, 2001, issued Dec. 2, 2003 as 6,658,480 patent);

- 8. U.S. Patent Application No. 09/802,551 (filed Mar. 9, 2001, issued Jul. 11, 2006 as 7,076,568 patent);

- 9. U.S. Patent Application No. 09/801,488 (filed Mar. 7, 2001, issued Feb. 3, 2004 as 6,687,758 patent);

- 10. U.S. Patent Application No. 09/789,366 (filed Feb. 20, 2001, issued Jun. 29, 2004 as 6,757,746 patent);

- 11. U.S. Patent Application No. 09/675,700 (filed Sept. 29, 2000, issued

- Dec. 31, 2013 as 8,621,101 patent);

- 12. U.S. Patent Application No. 09/675,484 (filed Sept. 29, 2000, issued Oct. 19, 2004 as 6,807,581 patent);

- 13. U.S. Patent Application No. 09/514,425 (filed Feb. 28, 2000, issued Jul. 30, 2002 as 6,427,171 patent);

- 14. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent);

- 15. U.S. Patent Application No. 09/439,603 (filed Nov. 12, 1999, issued Jun. 12, 2001 as 6,247,060 patent);

- 16. U.S. Patent Application No. 09/416,925 (filed Oct. 13, 1999, issued Oct. 22, 2002 as 6,470,415 patent);

- 17. U.S. Patent Application No. 09/384,792 (filed Aug. 27, 1999, issued Aug. 13, 2002 as 6,434,620 patent);

- 18. U.S. Patent Application No. 09/141,713 (filed Aug. 28, 1998, issued May 14, 2002 as 6,389,479 patent);

- 19. U.S. Patent Application No. 60/098,296 (expired);

- 20. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1, 2001 as 6,226,680 patent);

- 21. U.S. Patent Application No. 60/061,809 (expired).

The patent family to which the 205 Patent belongs contains 5 additional U.S. patents:

- 1. U.S. Patent Application No. 10/092,967 (filed Mar. 6, 2002, issued Jul. 8, 2003 as 6,591,302 patent);

- 2. U.S. Patent Application No. 10/260,112 (filed Sept. 27, 2002, issued Jul. 26, 2007 as 7,237,036 patent);

- 3. U.S. Patent Application No. 10/261,051 (filed Sept. 30, 2002, issued Sept. 13, 2011 as 8,019,901 patent);

- 4. U.S. Patent Application No. 11/821,820 (filed Jun. 25, 2007, issued Mar. 2, 2010 as 7,673,072 patent);

- 5. U.S. Patent Application No. 11/582,199 (filed Oct. 16, 2006, issued Feb. 16, 2010 as 7,664,883 patent).

The patent family to which the 072 Patent belongs contains 19 additional U.S. patents:

- 1. U.S. Patent Application No. 10/260,112 (filed Sept. 27, 2002, issued Jul. 26, 2007 as 7,237,036 patent);

- 2. U.S. Patent Application No. 10/092,967 (filed Mar. 6, 2002, issued Jul. 8, 2003 as 6,591,302 patent);

- 3. U.S. Patent Application No. 10/023,240 (filed Dec. 17, 2001, issued Nov. 15, 2005 as 6,965,941 patent);

- 4. U.S. Patent Application No. 09/970,124 (filed Oct. 2, 2001, issued Oct. 17, 2006 as 7,124,205 patent);

- 5. U.S. Patent Application No. 09/855,979 (filed May 14, 2001, issued Nov. 7, 2006 as 7,133,940 patent);

- 6. U.S. Patent Application No. 09/802,426 (filed Mar. 9, 2001, issued May 9, 2006 as 7,042,898 patent);

- 7. U.S. Patent Application No. 09/802,550 (filed Mar. 9, 2001, issued Dec. 2, 2003 as 6,658,480 patent);

- 8. U.S. Patent Application No. 09/802,551 (filed Mar. 9, 2001, issued Jul. 11, 2006 as 7,076,568 patent);

- 9. U.S. Patent Application No. 09/801,488 (filed Mar. 7, 2001, issued Feb. 3, 2004 as 6,687,758 patent);

- 10. U.S. Patent Application No. 09/789,366 (filed Feb. 20, 2001, issued Jun. 29, 2004 as 6,757,746 patent);

- 11. U.S. Patent Application No. 09/675,700 (filed Sept. 29, 2000, issued Dec. 31, 2013 as 8,621,101 patent);

- 12. U.S. Patent Application No. 09/675,484 (filed Sept. 29, 2000, issued Oct. 19, 2004 as 6,807,581 patent);

- 13. U.S. Patent Application No. 09/514,425 (filed Feb. 28, 2000, issued Jul. 30, 2002 as 6,427,171 patent);

- 14. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent);

- 15. U.S. Patent Application No. 09/439,603 (filed Nov. 12, 1999, issued Jun. 12, 2001 as 6,247,060 patent);

- 16. U.S. Patent Application No. 09/416,925 (filed Oct. 13, 1999, issued Oct. 22, 2002 as 6,470,415 patent);

- 17. U.S. Patent Application No. 09/384,792 (filed Aug. 27, 1999, issued Aug. 13, 2002 as 6,434,620 patent);

- 18. U.S. Patent Application No. 09/141,713 (filed Aug. 28, 1998, issued May 14, 2002 as 6,389,479 patent);

- 19. U.S. Patent Application No. 60/098,296 (expired);

- 20. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1, 2001 as 6,226,680 patent);

- 21. U.S. Patent Application No. 60/061,809 (expired).

The patent family to which the 948 Patent belongs contains 2 additional U.S. patents:

- 1. U.S. Patent Application No. 09/692,561 (filed Oct. 18, 2000, issued Jan. 14, 2014 as 8,631,140 patent);

- 2. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1,

2001 as 6,226,680 patent);

3. U.S. Patent Application No. 60/061,809 (expired).

The patent family to which the 699 Patent belongs contains 14 additional U.S. patents:

- 1. U.S. Patent Application No. 10/881,271 (filed Jun. 29, 2004, issued Dec. 2, 2008 as 7,461,160 patent);

- 2. U.S. Patent Application No. 09/789,366 (filed Feb. 20, 2001, issued Jun. 29, 2004 as 6,757,746 patent);

- 3. U.S. Patent Application No. 09/748,936 (filed Dec. 26, 2000, issued Dec. 25, 2001 as 6,334,153 patent);

- 4. U.S. Patent Application No. 09/692,561 (filed Oct. 18, 2000, issued Jan. 14, 2014 as 8,631,140 patent);

- 5. U.S. Patent Application No. 09/675,484 (filed Sept. 29, 2000, issued Oct. 19, 2004 as 6,807,581 patent);

- 6. U.S. Patent Application No. 09/675,700 (filed Sept. 29, 2000, issued Dec. 31, 2013 as 8,621,101 patent);

- 7. U.S. Patent Application No. 09/514,425 (filed Feb. 28, 2000, issued Jul. 30, 2002 as 6,427,171 patent);

- 8. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent);

- 9. U.S. Patent Application No. 09/439,603 (filed Nov. 12, 1999, issued Jun. 12, 2001 as 6,247,060 patent);

- 10. U.S. Patent Application No. 09/416,925 (filed Oct. 13, 1999, issued Oct. 22, 2002 as 6,470,415 patent);

- 11. U.S. Patent Application No. 09/384,792 (filed Aug. 27, 1999, issued Aug. 13, 2002 as 6,434,620 patent);

- 12. U.S. Patent Application No. 09/141,713 (filed Aug. 28, 1998, issued May 14, 2002 as 6,389,479 patent);

- 13. U.S. Patent Application No. 60/098,296 (expired)

- 14. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1, 2001 as 6,226,680 patent);

- 15. U.S. Patent Application No. 60/061,809 (expired);

- 16. U.S. Patent Application No. 13/108,729 (filed May 16, 2011, issued Sept. 17, 2003 as 8,539,112 patent).

The patent family to which the 880 Patent belongs contains 6 additional U.S. patents:

- 1. U.S. Patent Application No. 10/005,536 (filed Nov. 7, 2001, issued Jan. 23, 2007 as 7,167,926 patent);

- 2. U.S. Patent Application No. 09/514,425 (filed Feb. 28, 2000, issued Jul. 30, 2002 as 6,427,171 patent);

- 3. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent);

- 4. U.S. Patent Application No. 09/384,792 (filed Aug. 27, 1999, issued Aug. 13, 2002 as 6,434,620 patent);

- 5. U.S. Patent Application No. 09/141,713 (filed Aug. 28, 1998, issued May 14, 2002 as 6,389,479 patent);

- 6. U.S. Patent Application No. 60/098,296 (expired);

- 7. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1, 2001 as 6,226,680 patent);

- 8. U.S. Patent Application No. 60/061,809 (expired).

The patent family to which the 104 Patent belongs contains 1 additional U.S. patents:

- 1. U.S. Patent Application No. 10/413,256 (filed Apr. 22, 2003, issued Jun. 2, 2009 as 7,543,087 patent);

- U.S. Patent Application No. 60/374,788 (expired).

The patent family to which the 241 Patent belongs contains 19 additional U.S. patents:

- 1. U.S. Patent Application No. 10/092,967 (filed Mar. 6, 2002, issued Jul. 8, 2003 as 6,591,302 patent);

- 2. U.S. Patent Application No. 10/023,240 (filed Dec. 17, 2001, issued

- Nov. 15, 2005 as 6,965,941 patent);

- 3. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent);

- 4. U.S. Patent Application No. 09/439,603 (filed Nov. 12, 1999, issued Jun. 12, 2001 as 6,247,060 patent);

- 5. U.S. Patent Application No. 09/067,544 (filed Apr. 27, 1998, issued May 1, 2001 as 6,226,680 patent);

- 6. U.S. Patent Application No. 60/061,809 (expired);

- 7. U.S. Patent Application No. 09/384,792 (filed Aug. 27, 1999, issued Aug. 13, 2002 as 6,434,620 patent);

- 8. U.S. Patent Application No. 09/141,713 (filed Aug. 28, 1998, issued May 14, 2002 as 6,389,479 patent);

- 9. U.S. Patent Application No. 60/098,296 (expired);

- 10. U.S. Patent Application No. 09/416,925 (filed Oct. 13, 1999, issued Oct. 22, 2002 as 6,470,415 patent);

- 11. U.S. Patent Application No. 09/514,425 (filed Feb. 28, 2000, issued Jul. 30, 2002 as 6,427,171 patent);

- 12. U.S. Patent Application No. 09/675,484 (filed Sept. 29, 2000, issued Oct. 19, 2004 as 6,807,581 patent);

- 13. U.S. Patent Application No. 09/675,700 (filed Sept. 29, 2000, issued

- Dec. 31, 2013 as 8,621,101 patent);

- 14. U.S. Patent Application No. 09/789,366 (filed Feb. 20, 2001, issued Jun. 29, 2004 as 6,757,746 patent);

- 15. U.S. Patent Application No. 09/801,488 (filed Mar. 7, 2001, issued Feb. 3, 2004 as 6,687,758 patent);

- 16. U.S. Patent Application No. 09/802,551 (filed Mar. 9, 2001, issued Jul. 11, 2006 as 7,076,568 patent);

- 17. U.S. Patent Application No. 09/802,426 (filed Mar. 9, 2001, issued May 9, 2006 as 7,042,898 patent);

- 18. U.S. Patent Application No. 09/802,550 (filed Mar. 9, 2001, issued Dec. 2, 2003 as 6,658,480 patent);

- 19. U.S. Patent Application No. 09/855,979 (filed May 14, 2001, issued Nov. 7, 2006 as 7,133,940 patent);

- 20. U.S. Patent Application No. 09/970,124 (filed Oct. 2, 2001, issued Oct. 17, 2006 as 7,124,205 patent);

- 21. U.S. Patent Application No. 09/464,283 (filed Dec. 15, 1999, issued Jul. 30, 2002 as 6,427,173 patent).

#### 2.5. Fee for Inter Partes Review

The Director is authorized to charge the fee specified by 37 C.F.R. § 42.15(a), and any other required fees, to Deposit Account No. 04-1679.

#### 2.6. Proof of Service

Proof of service of this Petition on the Patent Owner at the correspondence address of record for the 948 Patent is attached.

## 3. IDENTIFICATION OF CLAIMS BEING CHALLENGED (§42.104(B))

Ground #1: Claims 1, 3, 6-9, 11, 14-17, 19, and 21-22 of the 948 Patent are invalid under (pre-AIA) 35 U.S.C. § 103(a) on the ground that they are obvious over Y.H. Thia & C.M. Woodside, A Reduced Operation Protocol Engine (ROPE) for a Multiple-layer Bypass Architecture (1995) (Ex.1015, "Thia") in combination with Andrew S. Tanenbaum, Computer Networks (3rd ed. 1996) (Ex.1006, "Tanenbaum96") in further combination with 2 Gary R. Wright & W. Richard Stevens, TCP/IP Illustrated: The Implementation (1995) (Ex.1013, "Stevens2").

#### 4. BACKGROUND OF TECHNOLOGY

This section provides a brief background on the technology at issue, focusing on layered network protocols generally, the TCP/IP protocol, offloading protocol processing from a host to a NIC, and Direct Memory Access ("DMA"). Petitioner's declarant Dr. Horst provides a tutorial on the technology and discusses the state of the art as well. Ex.1003, ¶¶21-88.

#### A. Layered Network Protocols

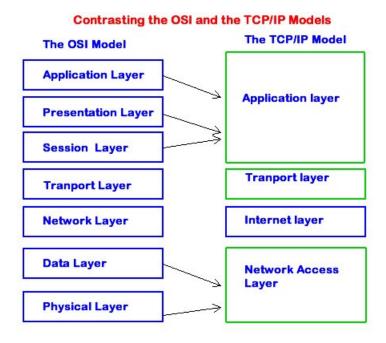

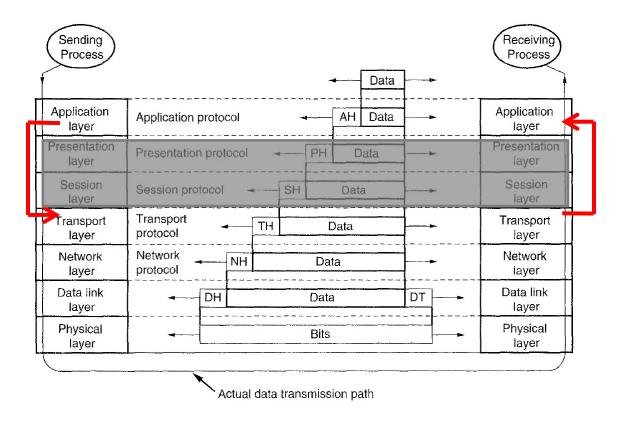

The seven-layer Open Systems Interconnect (OSI) model describes a logical network layering model including physical, data link, network, transport, session, presentation and application layers. *Id.* ¶23.

1. TCP/IP stands for Transmission Control Protocol/Internet Protocol. TCP/IP is the main protocol used for Internet communications – Web pages are served using TCP/IP. There is a well-known correspondence between TCP/IP layers and the OSI model. The following figure shows the relationship between the OSI and TCP/IP layering.

Available at http://mitigationlog.com/how-tcpip-and-reference-osi-model-works/.

Conceptually, each layer is responsible only for its respective functions. Ex.1003, ¶25. This enables, for example, hiding the complexity of the physical data

connection (that is, actually transmitting and receiving the data onto the physical wires) from the data link, network and transport layers above. *Id.* Likewise, the lowest layer must transmit and receive the data on the physical wires, but need not worry about what application the data belongs to or whether the packets are received in order. *Id.*

#### B. TCP/IP

The 948 Patent relates to an intelligent network interface card that provides a "fast path" that avoids host protocol processing for most packets in a large multipacket message. Ex.1001, Abstract. The claims are all directed to TCP/IP.

By October 14, 1996, the critical date of the 948 Patent, TCP/IP was one of the most popular networking protocols, overtaking the OSI protocols. *See* Ex.1006, .016 ("The OSI protocols have quietly vanished, and the TCP/IP protocol suite has become dominant.") TCP/IP was standardized in a series of publically available Request for Comments (RFCs) published by the Internet Engineering Task Force, including RFC 793, entitled "Transmission Control Protocol" and RFC 791, entitled "Internet Protocol." Ex.1007; Ex.1036. Free implementations of TCP/IP were widely available and widely used. Ex.1003, ¶27.

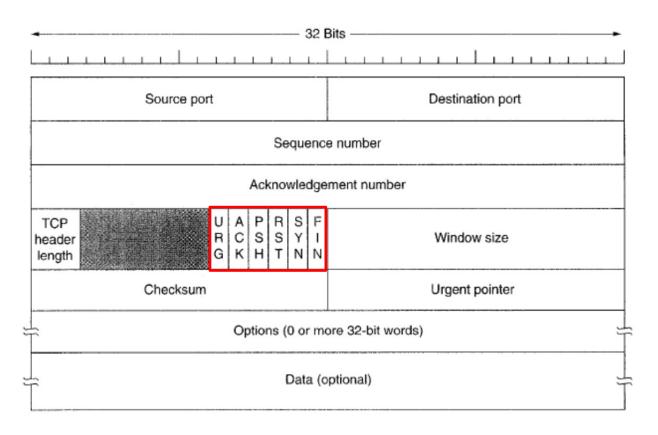

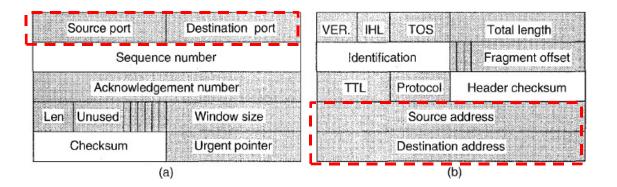

TCP/IP consists of two parts: (1) Transmission Control Protocol (TCP), which provides virtual bi-directional connections that are guaranteed in-order, error-free delivery of arbitrary amounts of data between programs running on different

computers over the Internet; and (2) Internet Protocol (IP), which provides delivery of datagrams (IP packets) to any routable Internet address, without any reliability or ordering guarantees. IP also provides for fragmentation and reassembly. Fragmentation occurs when an IP packet must be divided ("fragmented") into smaller packets en route for transmission over an intermediate network with a small packet size. TCP/IP can be transmitted over a variety of physical media, such as Ethernet. *Id.* ¶28.

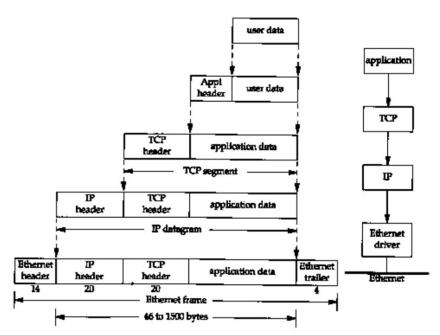

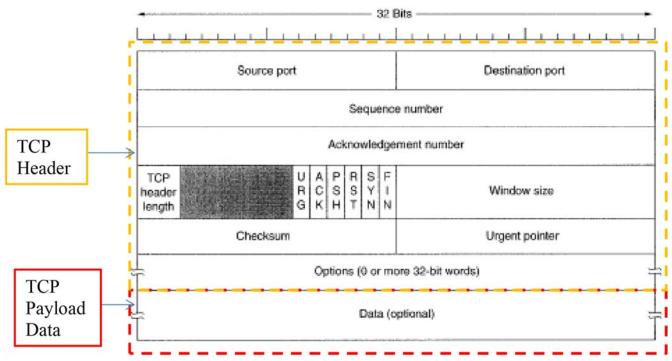

TCP runs on "top" of IP by first dividing application data to be transmitted into segments that become the data payloads of TCP packets and concatenating each payload with a TCP header to form a TCP packet, a process called TCP segmentation. TCP/IP then places the resulting TCP packet (TCP header + payload) into the data payload of an IP packet by concatenating the TCP packet (IP data payload) with an IP header. The TCP packet is thus "encapsulated" in an IP packet. For transmission on an Ethernet network, the IP packet is in turn encapsulated in an Ethernet frame by concatenating a Media Access Control (MAC) header for Ethernet with the IP packet, which becomes the payload of the Ethernet frame, and concatenating a checksum trailer at the end of the frame. *Id.* ¶29.

As shown in the figure below, in typical TCP/IP processing, the packet is built from the top down, i.e., each layer encapsulates what it receives from the above layer by concatenating an additional header associated with that layer. *Id.* ¶30. When

receiving a packet from the network, the layers work in reverse, with each layer stripping its header and providing the resulting packet to the above layer. *Id.* The user data without headers is eventually delivered to the relevant application.

Figure 1.7 Encapsulation of data as it goes down the protocol stack.

## Ex.1008, Fig. 1.7.

Starting from the lowest layer, the MAC (media access control) layer handles the actual transmission on the physical media. The header for this layer, e.g., an Ethernet header, includes a MAC address that is the address of the network interface (e.g., on a computer or router) on a local area network. Ex.1003, ¶31.

Above the MAC layer is the Internet layer (IP layer). The IP header includes source and destination IP addresses for identifying a computer at each end of the

connection. *Id.* ¶33. The IP header also has a flag that indicates whether the packet has been fragmented. *Id.*

Above the IP layer is the TCP (Transport) layer. The TCP header includes "port numbers," corresponding to the end points (e.g., client or server programs) sending and receiving data on each end of the connection. *Id.* ¶34. The TCP layer tracks the sequence of packets, ensuring assembly of packets in the proper order by using sequence numbers in its headers. *Id.* ¶35. The transport services can be performed by software or the network interface card. *Id.*

To provide guaranteed reliable, in order, delivery of arbitrary amounts of data, the TCP layer tracks and acknowledges the sequence of packets, so that the sending TCP layer can re-send lost (and therefore unacknowledged) data without the application having to manage this process. The TCP layer assembles the data from packet payloads in the proper order by using sequence numbers in the TCP packet headers. Ex.1003, ¶35.

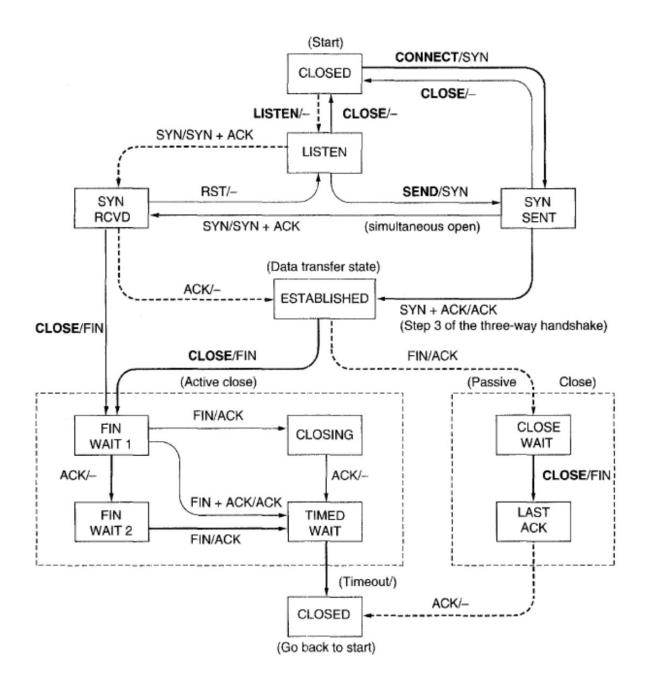

TCP maintains a finite state machine to manage the state of each connection. Connections begin in a CLOSED state. A server can move from CLOSED into a LISTEN state, which waits passively for a client to open a connection by sending a special packet called a SYN packet. After the server acknowledges the SYN packet, the connection is in the ESTABLISHED state. Either side can close the connection by sending a special packet called a FIN packet. The TCP finite state machine and

associated messages are described in detail in RFC 793. RFC 793 describes the data structure for storing the information needed to maintain a TCP connection as a Transmission Control Block (TCB). Ex.1007, .016; Ex.1003, ¶36.

In sum, sending data over a TCP/IP connection using Ethernet has always required: (1) TCP source and destination port numbers, (2) source and destination IP addresses, and (3) source and destination MAC addresses. *Id.* ¶37.

Each user application typically has one or more areas of host memory in which it can (1) place data for transmission so that the protocol stack can retrieve it, encapsulate it in packets, and transmit it, and (2) receive data from the network placed there by the protocol stack, after the protocol stack has stripped the MAC, IP and TCP headers from the packet. *Id.* ¶38.

## C. Protocol Offload and Fast-Path Processing

Protocol processing on a host computer requires that the host perform several operations on the data. To increase performance and reduce the demands on a host computer, many prior art solutions offload some (partial offload), or all (full offload), of this processing to a separate device, e.g., a network interface controller (NIC). Ex.1003, ¶40.

As early as 1974, front-end protocol offload (offloading protocol processing to a processor outside of the host) was already being considered for standardization as described in request-for-comments RFC 647, which describes a broad consensus

that front-ending (i.e. protocol offloading) was desirable. Ex.1019; Ex.1003, ¶¶41-42.

RFC 929, published in 1984, describes several motivations for offloading protocol processing to an outboard processor:

There are two fundamental motivations for doing outboard processing. One is to conserve the Hosts' resources (CPU cycles and memory) in a resource sharing intercomputer network, by offloading as much of the required networking software from the Hosts to Outboard Processing Environments (or "Network Front-Ends") as possible. The other is to facilitate procurement of implementations of the various intercomputer networking protocols for the several types of Host in play in a typical heterogeneous intercomputer network, by employing common implementations in the OPE. A third motivation, of basing a network security approach on trusted mandatory OPEs, will not be dealt with here, but is at least worthy of mention.

Ex.1009, .002; Ex.1003, ¶43. RFC 929 identifies many protocols for offloading, including TCP and UDP, and contemplates a wide range of protocol processing to be offloaded, specified by a "mediation level parameter," ranging from 9 for full offload, 8-1 for various levels of partial offloads, to 0 for no offload. Ex.1009, .015-.016; Ex.1003, ¶44.

Between the publication of RFC 929 in 1984 and the October 14, 1996 critical date for the 1997 provisional application to which the 948 patent claims priority, a

great deal of work was published in the area of protocol offloading and optimization. *See* Ex.1003, ¶¶45-80. One common implementation, called Header Prediction, examined TCP/IP packet headers to determine whether a received packet was a normal one, meaning: the connection was in the ESTABLISHED state; no TCP control flags (SYN, FIN, RST, and URG) were set; and the packet was received in order. *Id.* ¶¶58-60. These normal packets were processed on the fast path. *Id.* ¶58. Header Prediction for fast path processing on a NIC specifically teaches the alleged ideas claimed in the 948 Patent.

TCP Header Prediction was developed by Van Jacobson, who wrote the implementation of Header Prediction in the freely distributed and widely used BSD TCP/IP stack available in 1996. *Id.* ¶59. Jacobson's Header Prediction is discussed in all of three of the references relied upon in this petition.

## **D.** Direct Memory Access

Direct Memory Access (DMA) has been a well-known hardware technique that allows peripherals including network interface devices to directly access host memory without interrupting the host CPU. Ex.1003, ¶81. After received TCP/IP packets are processed on the fast path by separate hardware, the resulting data must be accessible to the application running on the host machine. *Id.* ¶82. DMA was a common and efficient way to achieve this. *Id.* Tanenbaum96 suggests the use of direct copying into the user buffer to avoid unnecessary copying. Ex.1006, .585.

The TCP/IP transport layer reassembles the original byte stream for use by the application layer after the headers are processed. *Id.* at .055-.056, .541; Ex.1003, ¶88.

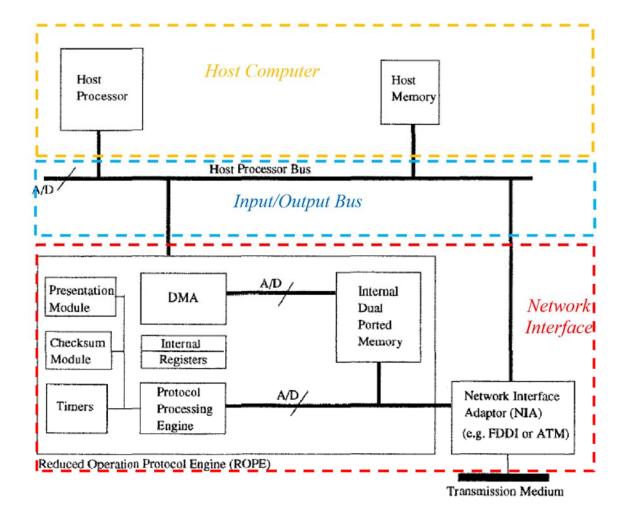

#### 5. OVERVIEW OF THE 948 PATENT

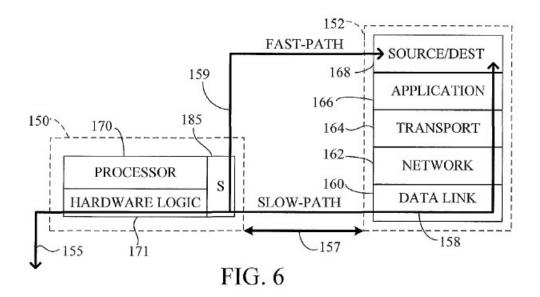

The 948 Patent relates generally to offloading TCP protocol processing for established TCP connections to a network interface card (NIC), which performs all protocol processing through the TCP layer and stores the packet payload data directly in its destination in application memory, bypassing the host protocol stack. The 948 Patent refers to the disclosed network interface card as an "intelligent network interface card (INIC)." Ex.1001, at Abstract. The INIC permits two modes of operation: a "fast path" in which protocol processing from the physical layer through the TCP layer is performed on the INIC, and a "slow path" in which network frames are handed to the host at the MAC layer and passed up through the host protocol stack conventionally. This concept is illustrated in Fig. 6, shown and described below:

A simplified intelligent network interface card (INIC) 150 is shown in FIG. 6 to provide a network interface for a host 152. Hardware logic 171 of the INIC 150 is connected to a network 155, with a peripheral bus (PCI) 157 connecting the INIC and host. The host 152 in this embodiment has a TCP/IP protocol stack, which provides a slow-path 158 for sequential software processing of message frames received from the network 155. The host 152 protocol stack includes a data link layer 160, network layer 162, a transport layer 164 and an application layer 166, which provides a source or destination 168 for the communication data in the host 152.... The INIC 150 has a network processor 170 which chooses between processing messages along a slow-path 158 that includes the protocol stack of the host, or along a fast-path 159 that bypasses the protocol stack of the host.

Ex.1001, Fig. 6; 9:11-29.

When a connection is created, the host computer creates a connection record which the 948 patent calls a "Communication Control Block (CCB)." *Id.* at 5:22-

29. Like the Transmission Control Block (TCB) described in the TCP Specification RFC 791, the CCB of the 948 Patent contains connection and state information for the connection. *Id.* at 12:32-39. When the INIC receives a packet, it looks for a CCB to determine if a connection exists, and if so, processes the packet on the fast-path, bypassing the host protocol stack:

The processor 170 chooses, for each received message packet held in storage 185, whether that packet is a candidate for the fast-path 159 and, if so, checks to see whether a fast-path has already been set up for the connection that the packet belongs to. To do this, the processor 170 first checks the header status summary to determine whether the packet headers are of a protocol defined for fast-path candidates.... For fast-path 159 candidates, the processor 170 checks to see whether the header status summary matches a CCB held by the INIC. If so, the data from the packet is sent along fast-path 159 to the destination 168 in the host. If the fast-path 159 candidate's packet summary does not match a CCB held by the INIC, the packet may be sent to the host 152 for slow-path processing to create a CCB for the message.

*Id.* at 11:57-12:10.

The claims of the 948 Patent are directed to this notion of fast-path TCP receive processing when a connection is in the ESTABLISHED state.

#### 6. 948 PATENT PROSECUTION HISTORY

The 948 Patent was filed on September 26, 2013 and issued less than 11 months later on August 12, 2014. There were no rejections or amendments.

The 948 Patent is a continuation of U.S. Patent Application No. 09/692,561, filed October 18, 2000, which is a continuation of U.S. Patent No. 6,226,680, filed April 28, 1998, which claims the benefit of U.S. Patent Application No. 60/061,809 filed October 14, 1997. Therefore, the earliest possible priority date of the 948 Patent is October 14, 1997.

On December 19, 2013, Applicant filed an Information Disclosure Statement with 383 patents, 41 applications, 13 foreign patents, and 112 non-patent literature documents, including Thia and Tanenbaum96. *See* Ex.1002, .075-.099. Neither Thia nor Tanenbaum96 were discussed during the prosecution of the application leading to the 948 Patent.

The Examiner's reasons for allowance follow:

None of the prior art of record taken singularly or in combination teaches or suggest a network interface of a host computer for checking whether received packets have certain exception conditions, including whether the packets are IP fragmented, have FIN flag set, or out of order; processing any of the received packet that have the exception conditions, and storing payload data of the received packets that do not have any of the exception conditions in a buffer of the host computer and without any TCP header stored between the payload data of the received packets.

Ex.1002, .117.

#### 7. CLAIM CONSTRUCTION

#### 7.1. Applicable Law

The "broadest reasonable construction in light of the specification of the patent in which it appears" applies to the 948 Patent. 37 C.F.R. § 42.100(b).

#### 7.2. Construction of Claim Terms

No relevant issues of claim construction are presented in the claims of the 948 Patent, and all terms should therefore simply be given their broadest reasonable construction in light of the specification as commonly understood by those of ordinary skill in the art.

#### 8. PERSON HAVING ORDINARY SKILL IN THE ART

A person having ordinary skill in the art ("POSA") with respect to the technology described in the 948 Patent would be a person with at least the equivalent of a B.S. degree in computer science, computer engineering or electrical engineering with at least five years of industry experience including experience in computer architecture, network design, network protocols, software development, and hardware development. *See* Ex.1003, ¶19.

#### 9. DESCRIPTION OF THE PRIOR ART

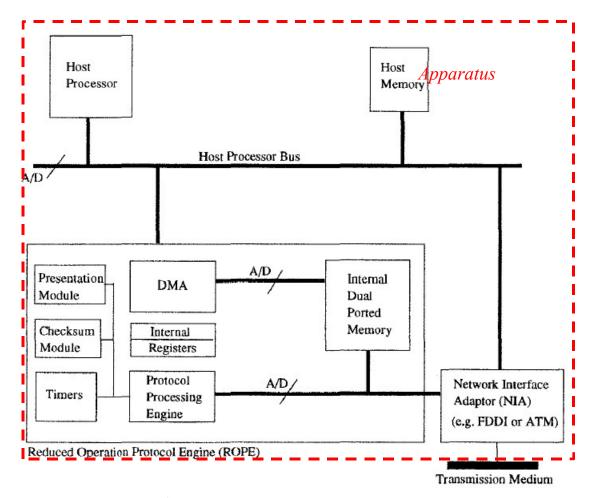

#### 9.1. Thia<sup>2</sup>

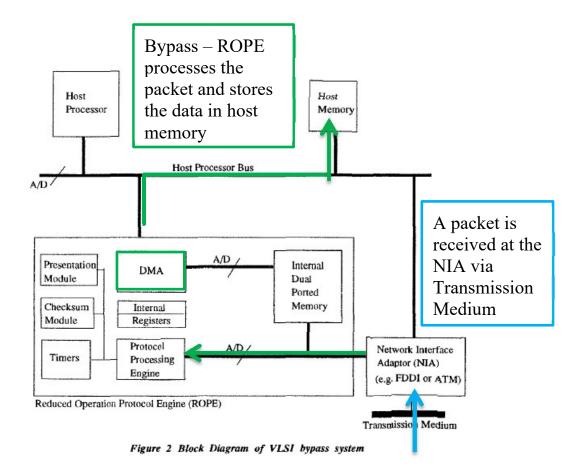

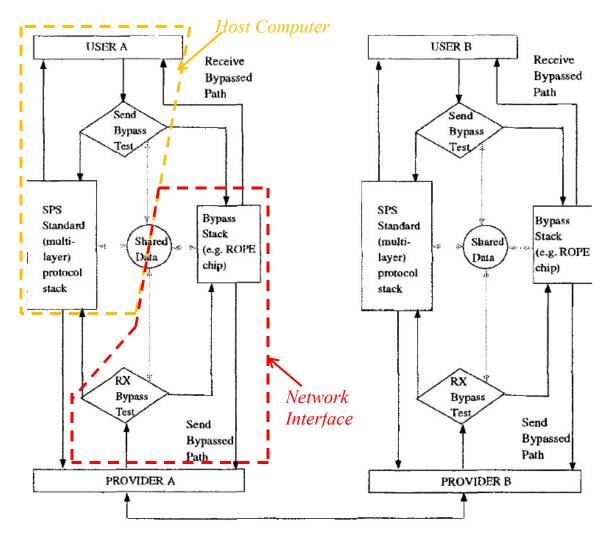

Thia teaches a hardware protocol engine for fast-path data transfer, bypassing the host protocol stack:

Abstract - The Reduced Operation Protocol Engine (ROPE) presented here offloads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer.

Ex.1015, .001. Thia is based on the Open Systems Interconnect (OSI) layered networking model.

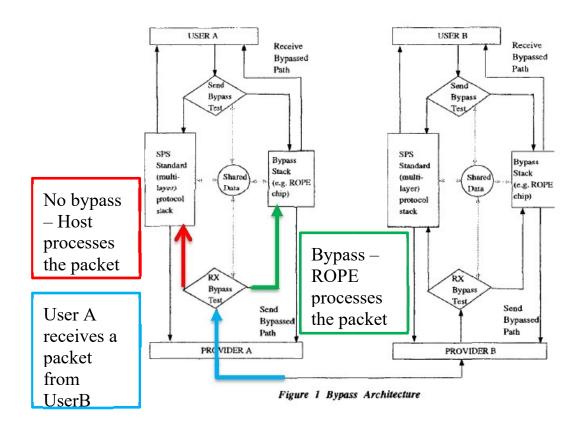

Thia describes a hardware protocol offload system that compares multiple incoming packet headers, including consecutive packets, with a template that identifies predicted bypassable headers using a receive bypass test (RX bypass test), and performs all protocol processing for packets in the "data transfer phase," bypassing the standard protocol stack (SPS) (host protocol stack):

The receive bypass test matches the incoming PDU headers with a template that identifies the predicted bypassable headers. The bypass stack performs all the relevant protocol processing in the data transfer phase.

\_

<sup>&</sup>lt;sup>2</sup> Thia was published no later than March 20, 1996 and is prior art under 102(b). *See* Ex.1064.

Ex.1015, .003. The "receive bypass test" is performed on the Network Interface Adapter. Ex.1015, .006. The hardware is referred to as a reduced operation protocol engine ("ROPE") because it only operates on a subset of packets. Ex.1003, ¶100.

#### Id. Fig. 1 (annotated).

Thia teaches that the receive bypass test ensures that the protocol bypass on the ROPE only handles normal packets – those in the data transfer phase (this is what Stevens2 referred to as the ESTABLISHED state for TCP) and that the SPS handles other phases:

A multiple-layer bypass path is a concatenation of processing procedures performed by the adjacent layers when they are simultaneously in the data transfer phase. Meanwhile, the separate

layers in the SPS [Standard Protocol Stack] path handle the other phases.

Ex.1015, .004.

In summary, the separation of the bypass path offers the following advantages:

- · The processing path of data PDUs can be optimized;

- · The number of possible PDU [Protocol Data Unit i.e. packet] formats in the bypass path is reduced to data transfer PDUs;

- The finite state machine of the protocol is now reduced to only the "OPEN" state, for as long as processing remains in the bypass path. The state of the system does not change during the entire data transfer phase and the protocol processing is reduced to ensuring reliable transfer of data across the communications network.

*Id.* at .004. Thia's receive bypass test is a generalization of Jacobson's well-known "Header Prediction Algorithm" for TCP/IP, which is also described in the Tanenbaum96 and Stevens2 references discussed below. *Id.* at .002-.04.

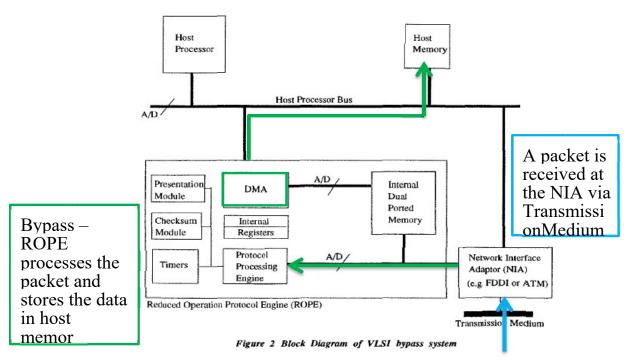

The bypass stack on the ROPE performs header decoding and can perform the checksum. *Id.*, .006.

| Layer                  | Procedure                                   | Bypass Chip                                                                   | Host | Per-Octet<br>(A) | Per-Packet<br>(B) | Per-Group-Of-Packets Aggregated to Per-Packet for bulk data transfer (B) | Remarks                                   |

|------------------------|---------------------------------------------|-------------------------------------------------------------------------------|------|------------------|-------------------|--------------------------------------------------------------------------|-------------------------------------------|

| Presentation           | Encoding                                    | х                                                                             |      | х                |                   |                                                                          |                                           |

|                        | Encryption                                  | x                                                                             |      | х                |                   |                                                                          |                                           |

|                        | Compression                                 | x                                                                             |      | х                |                   |                                                                          |                                           |

|                        | Context Alteration                          |                                                                               | х    |                  |                   | x                                                                        |                                           |

| Session                | Synchronization<br>Management               |                                                                               | x    |                  |                   | х                                                                        |                                           |

|                        | Token management                            |                                                                               | х    |                  |                   | х                                                                        |                                           |

| Transport<br>(Class 4) | Checksum (Optional)                         | х                                                                             |      | х                |                   |                                                                          |                                           |

|                        | Timer Management                            | х                                                                             |      |                  | х                 | x                                                                        | Depends on<br>Implementation              |

|                        | Generation of ACK<br>packets (Flow Control) | x                                                                             |      |                  |                   | х                                                                        |                                           |

|                        | Resequencing                                | x                                                                             |      |                  | х                 |                                                                          |                                           |

| AЦ 3 layers            | Header Construction                         | x                                                                             |      |                  | х                 |                                                                          |                                           |

|                        | Header Decode                               | х                                                                             |      |                  | x                 |                                                                          |                                           |

|                        | Buffer Management                           | х                                                                             |      |                  | х                 |                                                                          | Minimized<br>(Simple scheme)              |

|                        | Context Switching                           | х                                                                             |      |                  | х                 | х                                                                        | Moved away<br>from host OS                |

|                        | Data Copying                                | With multiple-layer<br>bypass, data Copying<br>within layers is<br>elminated. |      |                  | x                 |                                                                          | Use of dual-<br>ported memory<br>and DMA. |

Table 1 Bypassable versus Non-bypassable functions

Ex.1015, Table 1.

Thia's DMA copies the processed data from the bypass stack to Host Memory.

Id. at Fig. 2 (annotated).

As show in Table 1 above, data copying within layers is eliminated.

## 9.2. Tanenbaum 6: A. Tanenbaum, Computer Networks, 3rd ed. (1996)<sup>3</sup>

As described by the 948 Patent, Tanenbaum96 is a textbook devoted primarily to layered protocol processing. Ex.1001, 3:4-19. It is a widely-cited textbook