WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>6</sup> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      | (1                                                                             | 1) International Publication Number:         WO 99/56249                                                                                                                                                                                                                                                               |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| G06T 15/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>A1</b>                                                                                                            | (4                                                                             | <b>3) International Publication Date:</b> 4 November 1999 (04.11.99)                                                                                                                                                                                                                                                   |  |  |  |  |

| 21) International Application Number:       PCT/US9         22) International Filing Date:       23 April 1999 (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |                                                                                | (81) Designated States: CA, CN, JP, KR, European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).                                                                                                                                                                                      |  |  |  |  |

| <ul> <li>(30) Priority Data:<br/>60/083,177 27 April 1998 (27.04.98)<br/>09/291,366 14 April 1999 (14.04.99)</li> <li>(71) Applicant: INTERACTIVE SILICON, INC. [US/US<br/>201, 3737 Executive Center Drive, Austin, TX 787</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U<br>S]; Sui                                                                                                         |                                                                                | <b>Published</b><br>With international search report.<br>Before the expiration of the time limit for amending the<br>claims and to be republished in the event of the receipt og<br>amendments.                                                                                                                        |  |  |  |  |

| <ul> <li>(72) Inventor: DYE, Thomas, A.; 6621 Candle Ridge Cove<br/>TX 78731 (US).</li> <li>(74) Agent: HOOD, Jeffrey, C.; Conley, Rose &amp; Tayon, P<br/>Box 398, Austin, TX 78767–0398 (US).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e, Austi                                                                                                             | n,                                                                             |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |                                                                                |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

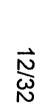

| <ul> <li>(54) Title: GRAPHICS SYSTEM AND METHOD FOR I</li> <li>(57) Abstract <ul> <li>A video/graphics controller (IMC) which includes a not for rendering and display of 3D graphical data on a disp operates to construct a 3-D Virtual display refresh list</li> <li>The IMC constructs the 3-D VDRL by first parsing the independent vertex-sorted geometric primitives (eg, trian setup on the geometric primitives. Setup includes assemblie each of the triangle vertices and determining slope values i IMC uses 3D vertex and slope information to compute hor up each triangle. The IMC then performs a Y sort of the triangle segments are generated and X sorted based on start for each segment. Span lines are horizontal line of pixels t</li> </ul> </li> </ul> | ovel spa<br>lay dev<br>(3D-V<br>geome<br>gles) a<br>ing a li<br>for the<br>izontal<br>riangle:<br>an line.<br>ting X | inni<br>vice<br>/DI<br>try<br>nd<br>st c<br>tria<br>seg<br>s fo<br>. Fo<br>pos | ing based method<br>The IMC first<br>RL) in memory.<br>data, generating<br>then performing<br>of parameters for<br>angle edges. The<br>gments that make<br>or each span line,<br>sition of triangles<br>High Level Video<br>Operations<br>Construct a 3-D Video<br>Display Refresh List in<br>the System Memory<br>302 |  |  |  |  |

| the display device, and segments are portions of the span lin<br>triangle start to stop segments. After the Y and X sorts, the<br>determination for each span line to discard or reject those seg-<br>to reject the now one-dimensional triangle segments that a<br>segments. After the Y and X sorts, and the Z rules determ<br>the segments that are visible, the IMC then constructs the<br>span line comprising pointers which reference viewed triang<br>of the 3-D VDRL, the 3-D VDRL is read and interpreted f<br>exture address, attributes and other control information to<br>pixel data includes the viewed triangle spans and may include<br>that referenced by the VDRL.                                                                                           | ne IMC<br>gments<br>re hidd<br>nination<br>e 3–D<br>gle span<br>for trian<br>o gener                                 | pe<br>tha<br>en<br>n, v<br>VD<br>s. l<br>ngle<br>ate                           | erforms a Z rules<br>at are hidden, i.e.,<br>by other triangle<br>which determines<br>PRL list for each<br>During execution<br>e parameter data,<br>pixel data. The<br>Execute the 3-D Video<br>Display Refresh List by<br>reading the 3-D VDRL<br>and generating the<br>appropriate pixel data<br>304                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |                                                                                | anfield Scientific, Inc Exhibit 1007<br>eld Scientific, Inc. v. Melanoscan, LLC<br>IPR2017-02125<br>Page 1 of 9                                                                                                                                                                                                        |  |  |  |  |

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AL | Albania                  | ES | Spain               | LS | Lesotho               | SI | Slovenia                 |

|----|--------------------------|----|---------------------|----|-----------------------|----|--------------------------|

| AM | Armenia                  | FI | Finland             | LT | Lithuania             | SK | Slovakia                 |

| AT | Austria                  | FR | France              | LU | Luxembourg            | SN | Senegal                  |

| AU | Australia                | GA | Gabon               | LV | Latvia                | SZ | Swaziland                |

| AZ | Azerbaijan               | GB | United Kingdom      | MC | Monaco                | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE | Georgia             | MD | Republic of Moldova   | TG | Togo                     |

| BB | Barbados                 | GH | Ghana               | MG | Madagascar            | ТJ | Tajikistan               |

| BE | Belgium                  | GN | Guinea              | MK | The former Yugoslav   | TM | Turkmenistan             |

| BF | Burkina Faso             | GR | Greece              |    | Republic of Macedonia | TR | Turkey                   |

| BG | Bulgaria                 | HU | Hungary             | ML | Mali                  | тт | Trinidad and Tobago      |

| 3J | Benin                    | IE | Ireland             | MN | Mongolia              | UA | Ukraine                  |

| BR | Brazil                   | IL | Israel              | MR | Mauritania            | UG | Uganda                   |

| BY | Belarus                  | IS | Iceland             | MW | Malawi                | US | United States of America |

| CA | Canada                   | IT | Italy               | MX | Mexico                | UZ | Uzbekistan               |

| CF | Central African Republic | JP | Japan               | NE | Niger                 | VN | Viet Nam                 |

| CG | Congo                    | KE | Kenya               | NL | Netherlands           | YU | Yugoslavia               |

| СН | Switzerland              | KG | Kyrgyzstan          | NO | Norway                | ZW | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP | Democratic People's | NZ | New Zealand           |    |                          |

| СМ | Cameroon                 |    | Republic of Korea   | PL | Poland                |    |                          |

| CN | China                    | KR | Republic of Korea   | PT | Portugal              |    |                          |

| CU | Cuba                     | KZ | Kazakstan           | RO | Romania               |    |                          |

| Z  | Czech Republic           | LC | Saint Lucia         | RU | Russian Federation    |    |                          |

| DE | Germany                  | LI | Liechtenstein       | SD | Sudan                 |    |                          |

| ж  | Denmark                  | LK | Sri Lanka           | SE | Sweden                |    |                          |

| EE | Estonia                  | LR | Liberia             | SG | Singapore             |    |                          |

# GRAPHICS SYSTEM AND METHOD FOR RENDERING INDEPENDENT 2D AND 3D OBJECTS

## **Field** of the Invention

The present invention relates to computer system graphics architectures, and more particularly to a graphics controller which performs pointer-based display list video operations to build and manipulate two and three dimensional objects and transfer the objects video data from a memory to a display device.

## **Description of the Related Art**

Since their introduction in 1981, the architecture of personal computer systems has remained substantially unchanged. The current state of the art in computer system architectures includes a central processing unit (CPU) which couples to a memory controller interface that in turn couples to system memory. The computer system also includes a separate graphical interface for coupling to the video display. In addition, the computer system includes input/output (I/O) control logic for various I/O devices, including a keyboard, mouse, floppy drive, hard drive, etc.

In general, the operation of a modern computer architecture is as follows. Programs and data are read from a respective I/O device such as a floppy disk or hard drive by the operating system, and the programs and data are temporarily stored in system memory. Once a user program has been transferred into the system memory, the CPU begins execution of the program by reading code and data from the system memory through the memory controller. The application code and data are presumed to produce a specified result when manipulated by the system CPU. The code and data are processed by the CPU and data is provided to one or more of the various output devices. The computer system may include several output devices, including a video display, audio (speakers), printer, etc. In most systems, the video display is the primary output device.

Graphical output data generated by the CPU is written to a graphical interface device for presentation on the display monitor. The graphical interface device may simply be a video graphics array (VGA) card, or the system may include a dedicated video processor or video acceleration card including separate video RAM (VRAM). In a computer system including a separate, dedicated video processor, the video processor includes graphics capabilities to reduce the workload of the main CPU. Modern prior art personal computer systems typically include a local bus video system based on either the peripheral component interconnect (PCI) bus or the VESA (Video Electronics Standards Association) VL bus, or perhaps a proprietary local bus standard. The video subsystem is generally positioned on a local bus near the CPU to provide increased performance.

Therefore, in summary, program code and data are first read from the hard disk to the system memory. The program code and data are then read by the CPU from system memory, the data is processed by the CPU, and graphical data is written to the video RAM in the graphical interface device for presentation on the display monitor. The CPU typically reads data from system memory across the system bus and then writes the processed data or graphical data back across the system bus to the I/O bus or local bus where the graphical interface device is situated. The graphical interface device in turn generates the appropriate video signals to drive the display monitor. It is noted that this operation requires data to make two passes across the system bus and/or the I/O

20

15

5

10

30

25

subsystem bus. In addition, the program that manipulates the data must also be transferred across the system bus from the main memory. Further, two separate memory subsystems are required, the system memory and the dedicated video memory, and video data is constantly being transferred from the system memory to the video memory frame buffer.

5

10

One recent trend in computer system architecture and design is referred to as a "shared" or "unified" memory, also referred to as a unified memory architecture (UMA). In this architecture, the main or system memory is used for operating system and applications software as well as for the video frame buffer. However, one problem with the "unified" or "shared" memory approach is the perceived need for additional bandwidth to perform video functions such as bit block transfers and video refresh, rasterization and display of three dimensional objects, as well as CPU manipulation of programs and data within the same memory subsystem.

Current 3D display system use a method called the "immediate" mode to render 3D objects. This mode draws a single triangle at a time checking a Z-buffer and reading a texture map or other source data to cover each single triangle. This prior art requires increased memory bandwidth due to triangles that are completely drawn and new triangles that overlap or hide previously drawn triangles. UMA architectures that use immediate mode 3D will be slower and lower performance due to these limitations.

Computer systems are being called upon to perform larger and more complex tasks that require increased computing power. In addition, modern software applications require computer systems with increased graphics capabilities. Modern software applications typically include graphical user interfaces (GUIs) which place increased burdens on the graphics capabilities of the computer system. Further, the increased prevalence of multimedia applications, such as digital video and 3D graphics, also demands computer systems with more powerful graphics capabilities. Therefore, a new computer system and method is desired which provides increased system performance while reducing system cost, in particular, increased video and 2D/3D graphics performance than that possible using prior art.

#### 25 Summary of the Invention

The present invention comprises a video, 2D and 3D graphics controller, also referred to as the Integrated Memory Controller (IMC), which includes a novel spanning based system and method for rendering and display of 2D and 3D graphical data on a display device or video monitor, preferably using the main system memory in a unified or shared manner. The novel object based and spanning based display refresh list system for display of 2D and 3D graphical data can also be used within a graphics adapter with it's own local memory system. The IMC performs pointer-based display list video operations for rendering of 2D and 3D video data. The graphics controller of the present invention minimizes data movement for 2D/3D and video data manipulation for video display updates and thus greatly increases system performance. The graphics system uses a list of object pointers to assemble the output display. The objects may reside in virtual locations such as memory or across LAN or WAN communication links and be of any data type (i.e. graphics, video, audio, or control) or color format. In addition, objects use a virtual addressing system for the display output which allows unrestricted movement on the display surface without actual data movement required in prior art frame buffer systems. The IMC is capable of manipulating 3D graphical data similar to streaming video sources. This makes

20

15

the invention well suited for display and manipulation of environments where 3D graphics and streaming video formats are mixed. In the preferred embodiment, the IMC transfers data between the CPU local bus and system memory and also transfers data between the system memory and the video display output. The IMC may eliminate the need for one or more of a separate 2D/3D graphics, audio, video, and telephony and core logic subsystems.

The IMC uses techniques to improve overall system performance and user response time by use of the main system memory as a virtual graphical frame buffer and program/data storage. The IMC includes a unique system level architecture that reduces data bandwidth requirements for general media input/output functions. Because the host CPU is not required to move data between main memory and the graphics, audio and/or telephony subsystems as in conventional computers, data can reside virtually in the same subsystem as the main memory. Therefore, for media output data (audio, video, telephony) the host CPU or DMA master is not limited by external available proprietary bus bandwidth, thus improving overall system throughput.

The integrated memory controller (IMC) preferably includes an advanced memory controller, 2D/3D graphics, audio, video, and optionally telephony processing capabilities. The 3D graphics capabilities of the IMC include numerous significant advances that provide greatly increased performance over prior art systems. The memory controller (IMC) of the present invention may sit on the main CPU bus, (not limited to that bus) or a high-speed system peripheral bus such as the PCI or the accelerated graphics peripheral (AGP) bus. The IMC includes one or more symmetric memory ports for connecting to system memory. The IMC also includes video outputs, (where the term "video outputs" may be used to refer to display output to drive the output display device) preferably RGB (red, green, blue) outputs as well as NTSC, HDTV or PAL video plus horizontal and vertical synchronization signal outputs. These signals directly drive the video display monitor. The IMC may also include one or more video outputs, preferably (but not limited to) industry standard RGB, YUV, NTSC, PAL, HDTV and flat panel display interfaces. The IMC also may include numerous other interfaces for video, audio, Internet and/or telephony devices, among others

The IMC includes a novel system and method for manipulating and rendering 3D graphics. The IMC first operates to construct a 3-D Virtual display refresh list (3D-VDRL) in system memory. The IMC then executes the 3-D VDRL by reading the VDRL and generating and/or accessing the appropriate pixel data from system memory to construct an image or display objects. For example, execution of the 3-D VDRL causes the generated pixel data to be stored in memory as an image.

30

35

5

10

15

20

25

After the IMC executes the 3-D VDRL, the IMC may then create a separate 2-D VDRL which references the pixel data, and then execute the 2-D VDRL to render the pixel data on the screen. In alternate embodiments the 2-D VDRL and or 3-D VDRL may be created outside the IMC by an external CPU or computing device. Alternatively, the IMC stores the pixel data generated by execution of the 3-D VDRL in a conventional frame buffer and performs a refresh of the frame buffer to render the pixel data on the screen. The IMC may also provide the pixel data directly to a rendering engine for real time display after executing the 3-D VDRL.

The IMC operates to construct the 3-D VDRL by first parsing the 3D object and generating independent vertex-sorted geometric primitives and then performing setup on the geometric primitives. Geometric primitives may comprise trapezoids, splines, triangles, lines or points, and are generically termed polygons or triangles

within this disclosure. This includes assembling a list of parameters for each of the triangle vertices and determining slope values for the triangle edges. The IMC uses 3D vertex and slope information to compute horizontal segments that make up each triangle,

The IMC then performs a Y sort of the triangles for each span line, and an X sort of triangles segments and vertices for each span line. The Y sort operates to sort triangles by minimum Y position as well as the minimum Y vertex for each triangle. For each span line, triangle segments are generated and X sorted based on starting X position of triangles for each segment. Span lines are horizontal line of pixels that run the entire length of the display device and segments are portions of the span line that represent horizontal triangle start to stop segments for a respective triangle. After the Y and X sorts, the IMC performs a Z rules determination for each span line. The Z rules determination, determines the segments that are visible, and discards those segments that are hidden, i.e., is used to reject the now one-dimensional triangle segments that are hidden by other triangle segments.

The IMC or attached CPU then constructs a 3-D VDRL list for each span line comprising pointers which reference viewed triangle spans. The 3-D VDRL comprises pointers which reference viewed triangle spans. Thus, the 3D geometry is flattened to a one dimensional set of triangle segments for a plurality of triangles and a plurality of span lines, and the information for source textures, position, and 3D attributes is stored within the 3-D VDRL.

The 3-D VDRL is then executed. More specifically, the 3-D VDRL is read and interpreted for triangle

20

5

10

15

the triangle segments for multiple triangles for an entire span line as indicated in the 3-D VDRL. During

execution of the 3-D VDRL, the 3-D VDRL is fetched for instructions and pointers to control the rasterization of the output image by the 3D engine. Execution of the 3-D VDRL may cause rasterization of the output image to the memory on to the display device.

parameter data, texture address, attributes and other control information. The 3D graphics engine then renders all

**Brief Description of the Drawings** 25

> A better understanding of the present invention can be obtained when the following detailed description of the preferred embodiment is considered in conjunction with the following drawings, in which:

Figure 1A illustrates a computer system which includes the present invention;

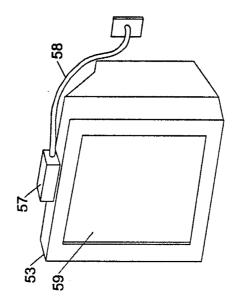

Figure 1B illustrates a television system, including a set top box, wherein one or more of the television or set top box include the present invention;

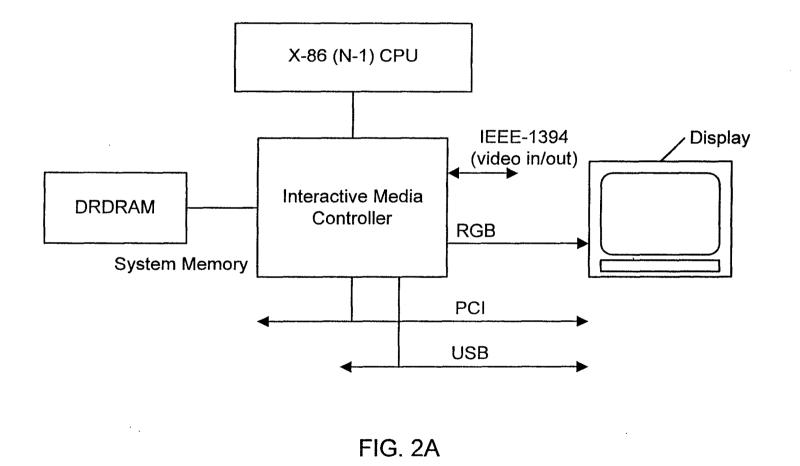

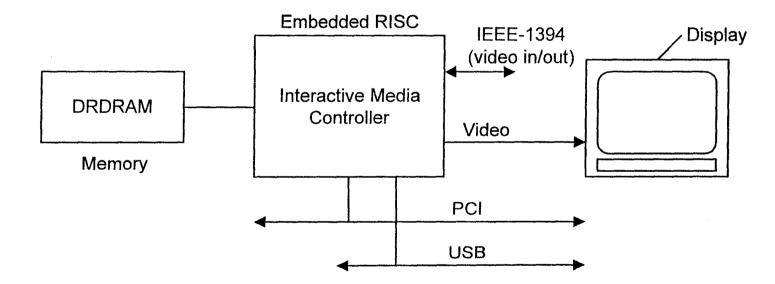

Figure 2A is a simple block diagram of a computer system including an interactive media controller (IMC) according to the present invention;

Figure 2B is a simple block diagram of a consumer appliance including an interactive media controller (IMC) according to the present invention;

35

30

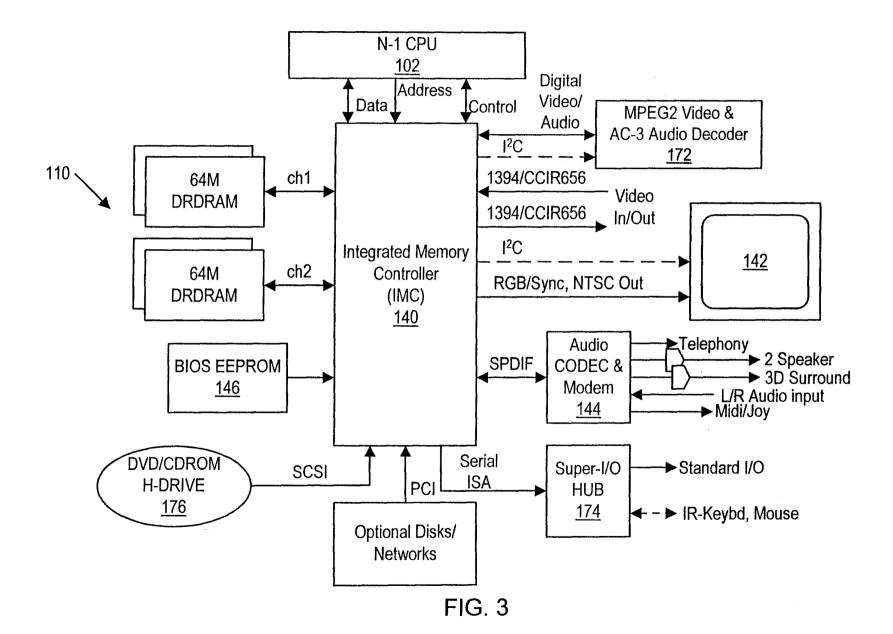

Figure 3 is a block diagram of a system including an IMC according to the present invention;

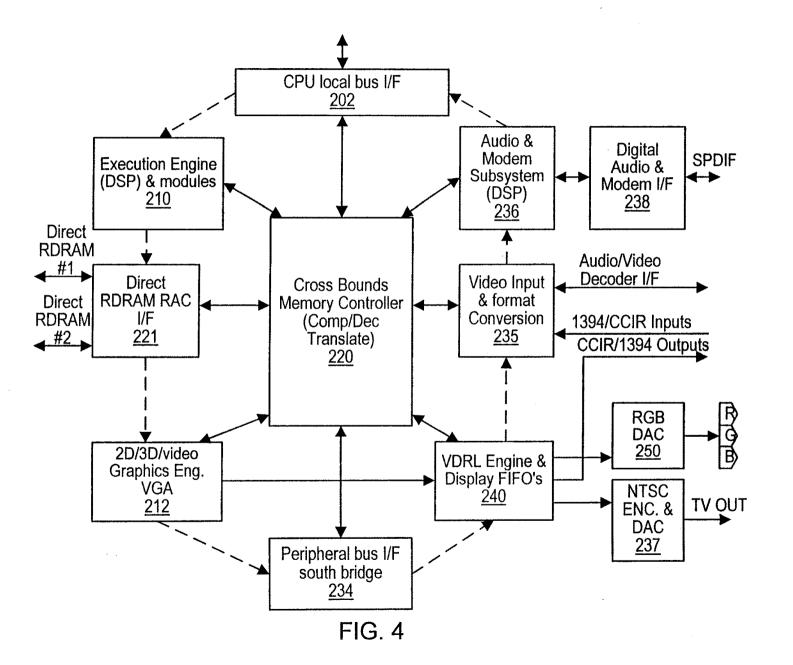

Figure 4 is a block diagram illustrating the IMC internal architecture of the present invention;

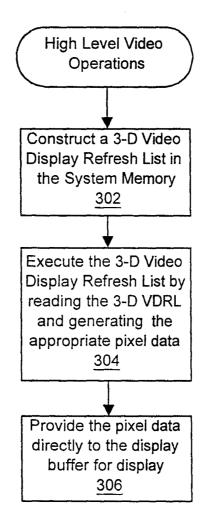

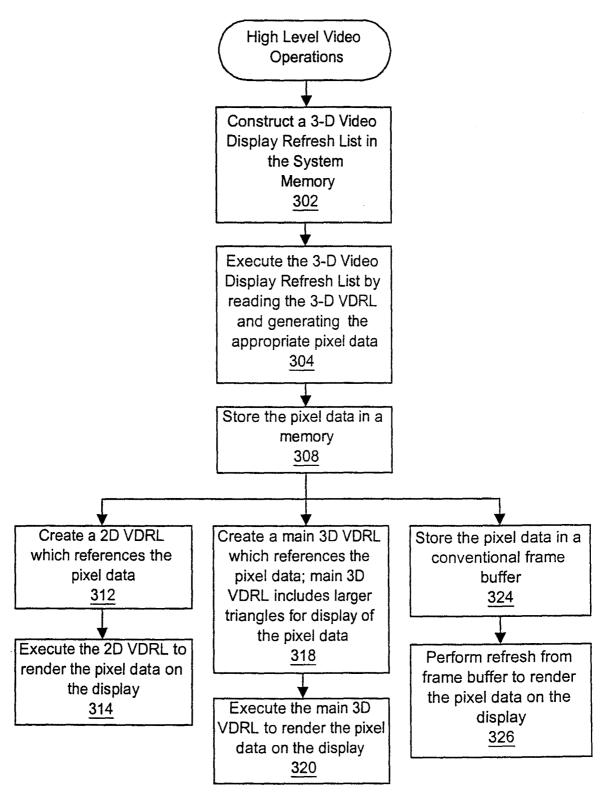

Figure 5A is a flowchart diagram illustrating operation of the IMC to construct and execute a 3-D virtual display refresh list and display the resulting pixel data;

Figure 5B is a flowchart diagram illustrating operation of the IMC to construct and execute a 3-D virtual display refresh list and store the resulting pixel data in memory for later display;

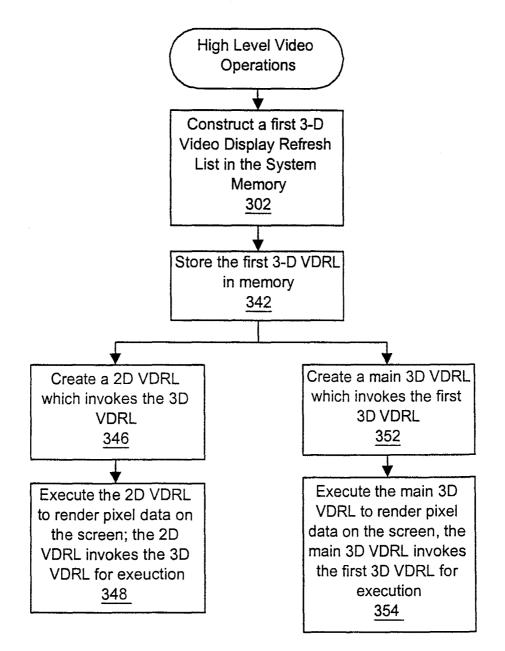

Figure 5C is a flowchart diagram illustrating operation of the IMC to construct a 3-D virtual display refresh list and store the 3-D VDRL for later execution and display;

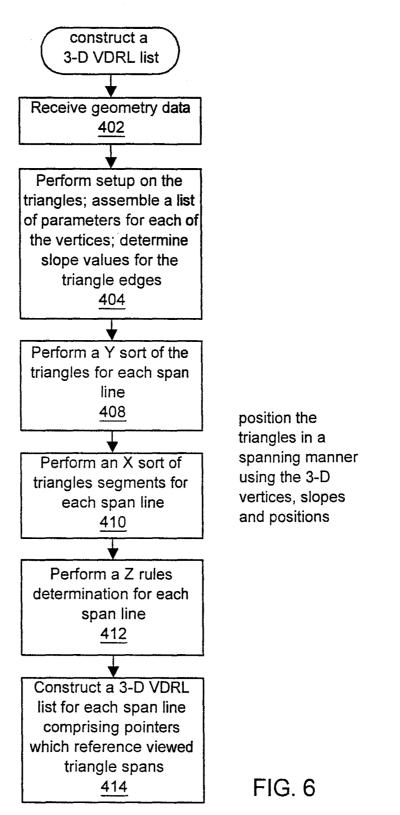

Figure 6 is a flowchart diagram illustrating operation of the IMC in constructing a 3-D VDRL;

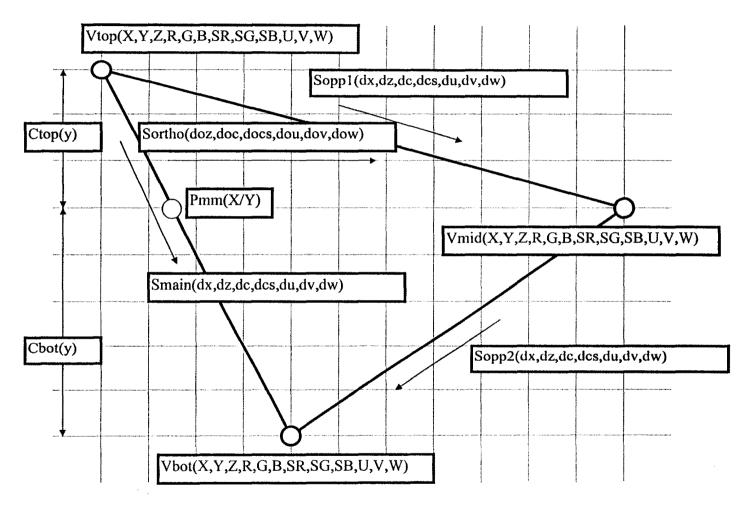

Figure 7 is a pictorial representation of a triangle parameterization process for an example triangle;

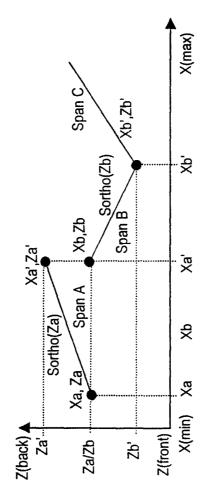

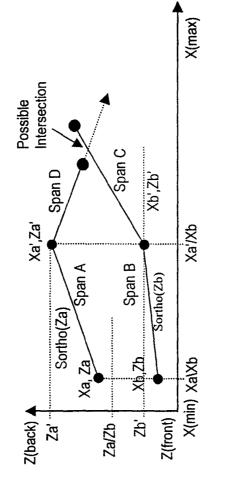

Figure 8 illustrates an example case of span line bucket sort process;

Figure 9 illustrates an example that shows a simple 8 term sort with the IMC fast-sort algorithm;

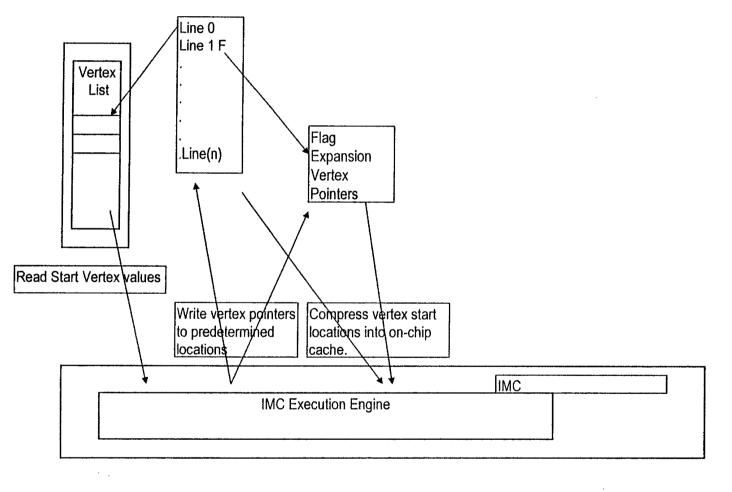

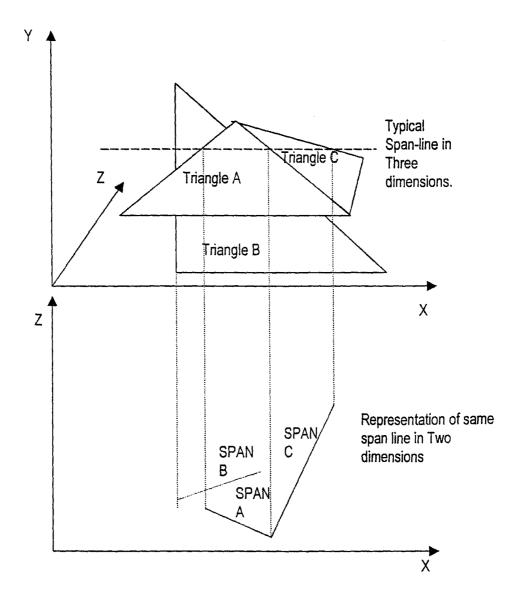

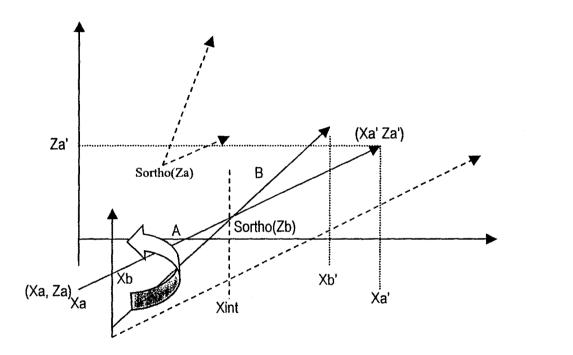

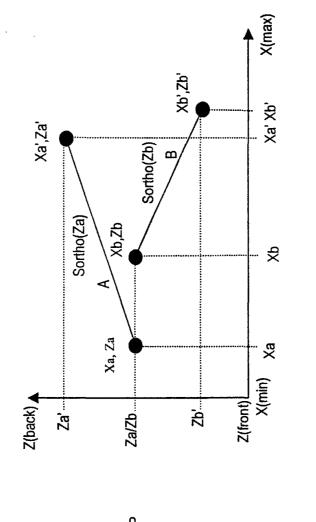

Figure 10 illustrates how triangles are converted to spans and how spans are seen from the depth space orientation;

10

15

5

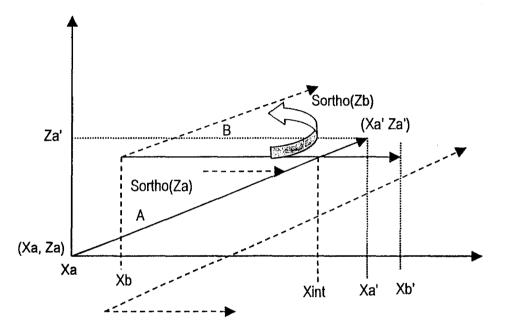

Figure 11 illustrates span reduction to a single dimension;

Figure 12 illustrates an example of visible span segments;

Figure 13 illustrates an example of totally hidden span segments;

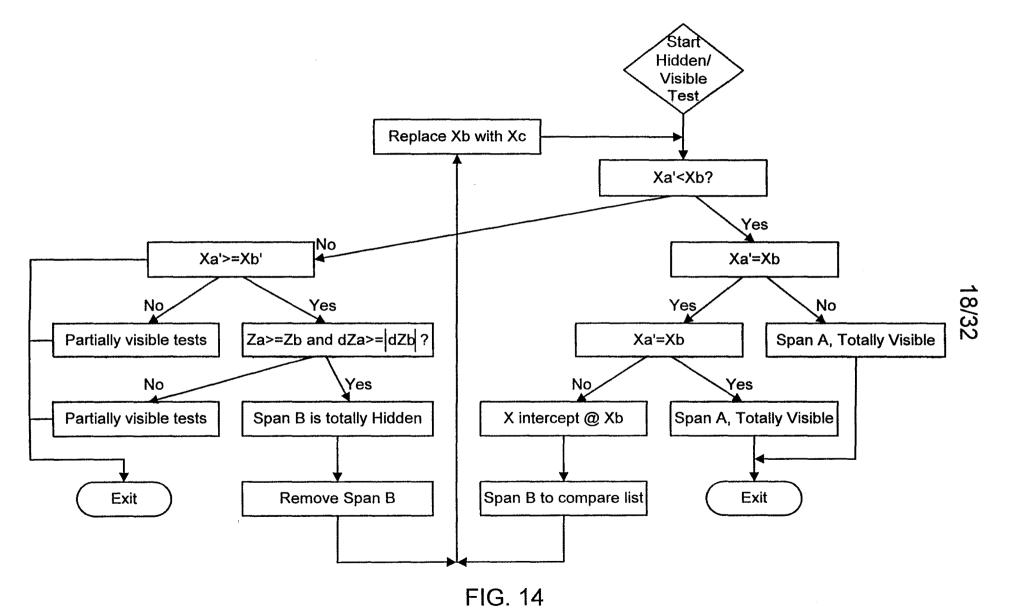

Figure 14 is a flowchart diagram illustrating determination of hidden and visible span segments;

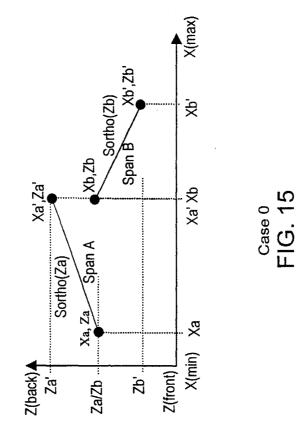

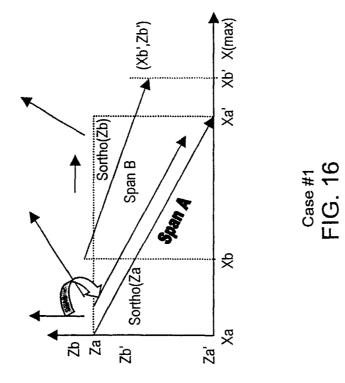

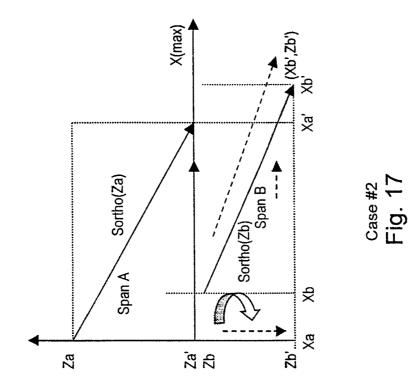

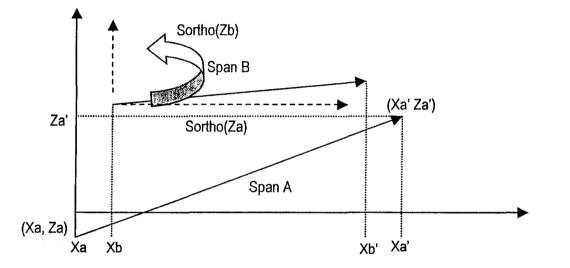

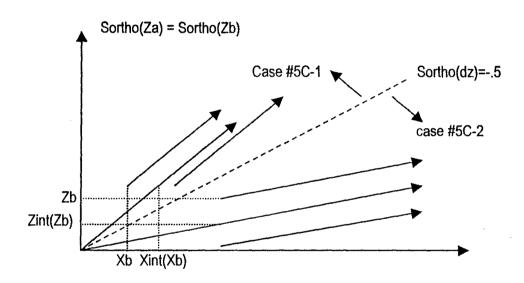

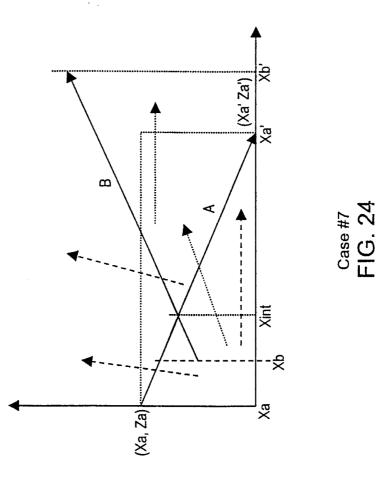

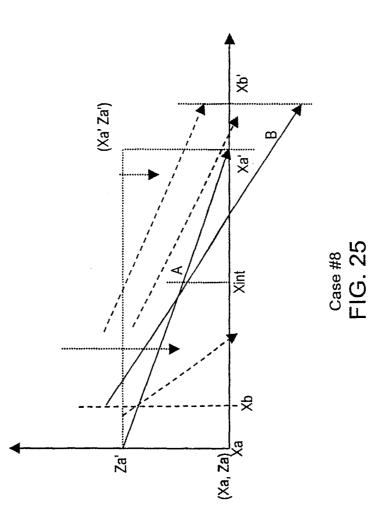

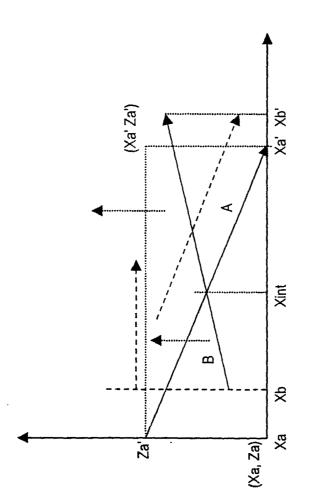

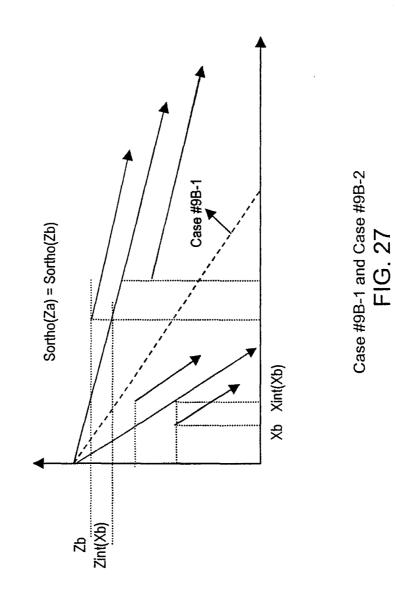

Figures 15 - 27 illustrate examples or cases of the operation of the flowchart of Figure 14; and

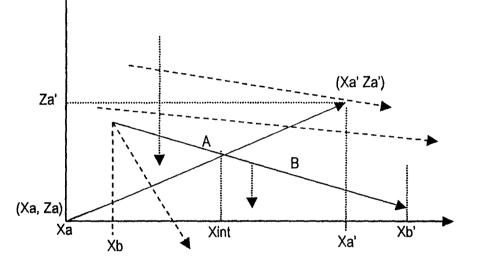

Figure 28 illustrates how a new triangle starts and continues with an intermediate triangle embedded in the middle.

20

While the invention is susceptible to various modifications and alternative forms, specific embodiments thereof are shown by way of example in the drawings and will herein be described in detail. It should be understood, however, that the drawings and detailed description thereto are not intended to limit the invention to the particular form disclosed, but on the contrary, the intention is to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the present invention as defined by the appended claims.

## **Detailed Description of the Preferred Embodiment**

25

30

35

The present invention comprises a graphic or video system and method which performs graphics/video functions with improved performance and/or more efficiency. The system and method of the present invention, referred to as the Interactive Media Controller or Integrated Memory Controller (IMC) may be used in any of various types of systems. In general, the present invention may be used in any type of system which includes a display device or display screen for displaying video images, such as analog or digital television, interactive television, computer systems which include video display monitors including computer systems which include LCD screens or flat panel screens, personal digital assistant devices (PDAs), consumer or Internet appliances, and other systems where video and/or graphics images or information are displayed to a user.

The assembly and execution of 2D VDRLs is discussed in U.S. Patent No. 5,838,334. The description that follows concentrates on the 3D portion of draw and rasterization.

# Figures 1A and 1B - Example System and Display Device Embodiments

Figure 1A illustrates a computer system 40 which includes the present invention. As shown, the computer system 40 includes a system unit comprising various standard computer components including the IMC system and method of the present invention. The system unit couples to a display device, in this case a computer system video

monitor. It is noted that the present invention may be used in other types of computer systems, including laptops, network computers, web PCs, Internet appliances, etc.

Figure 1B illustrates a television system which includes the IMC system and method of the present invention. In Figure 1B, the television system 53 includes a display screen 59. The television system also preferably includes a set top box 57 which couples through a cable, such as a fiber optic cable or coaxial cable, for receiving video images for display on the television screen 59. The IMC of the present invention may be comprised in the television system unit 53 and/or may be comprised in the set top box 57. In other words, the IMC may be comprised in the set top box 57, or the IMC of the present invention may be integrated into the television, wherein the set top box 57 is optionally not included.

The television system 53 is preferably a digital television. Alternatively, the television 53 is an analog television, wherein the set top box 57 operates to receive and/or store digital video data and provide analog video signals to the analog television. The television system 53 may also be adapted for interactive television or Internet applications, e.g., WebTV. In this case, the set top box includes a return path, such as a POTS telephone, ISDN, or DSL connection, for return data.

Therefore, the IMC of the present invention may be comprised in any of various types of systems. As used herein, the term "system" is intended to include any of various types of computer systems, including desk top computer systems, portable computer systems, network computers, web PCs, mainframes, dumb terminals, etc. The term "system" also includes any of various types of television systems, such as analog or digital television systems, set top boxes, interactive television systems, and combined computer / television systems. The term "system" further includes other types of systems which include a display screen or display device such as Internet appliances, consumer computing appliances, personal digital assistants (PDAs), and other devices which include a display screen. As used herein, the term "display device" is intended to include computer systems or display technology for displaying 2D/3D graphics, video, textual or other types of images or information.

In one embodiment, the IMC of the present invention is comprised as a set top box controller chip which may operate to provide a digital signal to a digital television, or may operate to convert digital audio and video signals to an analog output for receipt by existing television sets. The digital audio and video signals are preferably received through the cable signal or through wireless communications. This set top box controller chip enables consumers to extend the life of current television sets, while enjoying the increased functionality of digital technology, including multiple picture-in-picture, 3-D video, 3-D positional audio, and high quality pictures. The IMC set top box of this embodiment is also capable of delivering non-digital signals to digital ready television sets, thus allowing buyers the opportunity to purchase digital capable television sets to prepare for future technology without jeopardizing the entertainment value of today's programming.

In an alternate embodiment, the IMC of the present invention is comprised as an embeddable controller for being integrated within a digital or analog television set. In other words, this controller is embedded directly within a digital or analog television set, thereby producing an "IMC-TV." This operates to supplant the set top box requirement. Alternatively, the IMC controller may be comprised in a digital set top box which is used in conjunction with a digital television set. In either case, the IMC digital set top box or IMC digital TV operates to

10

5

20

15

30

25

#### WO 99/56249

provide full digital functionality including accommodations for a wide array of FCC mandated video formats. The IMC of the present invention allows a television set or a computer display to operate with a plurality of different input sources. For example, movies that were filmed at 24 frames per second in wide screen formats can be displayed simultaneously with live video at 60 frames per second on the same display device. This enables a digital TV to achieve the same display level as, or a greater display level than, current computer systems.

5

10

15

20

# Figures 2A and 2B - Example IMC Block Diagrams

Figure 2A is a block diagram illustrating a basic computer system architecture including the IMC of the present invention. Figure 2A illustrates, for example, a low cost PC reference platform. As shown, the IMC of the present invention couples to a CPU 102, preferably an X86 CPU as shown. The CPU 102 may be any of various types, including X86, RISC, PowerPC, Sparc, or others. The CPU 102 may also comprise a microcontroller, FPGA, or other programmable logic.

In one embodiment, the IMC 140 includes an internal CPU core or RISC core, and thus external CPU 102 is not required. In this embodiment, the internal CPU core or RISC core within the IMC 140 operates to execute control code and/or system level software without the need for external CPU 102. Thus the term "CPU" is intended to encompass external CPU 102 as well as a CPU core or processing core comprised in the IMC 140.

The IMC 140 also couples directly to a memory 110. The memory 110 is preferably a system memory for storing applications and data used by the CPU 102. The memory 110 also preferably stores video/pixel data, and for 3-D graphics application stores various types of 3-D graphics data.

The IMC 140 further couples to a display 142 which is a computer video monitor or other type of display device. As shown, the IMC 140 is preferably operable to receive video input/output signals such as, for example, an IEEE-1394 connection for coupling through the IEEE-1394 serial bus to one or more video devices. The IMC 140 also preferably includes one or more other I/O bus interfaces including, for example, a Peripheral Component Interconnect (PCI) bus and a Universal Serial Bus (USB) among others.

Figure 2B illustrates a simple block diagram of a consumer appliance utilizing the IMC of the present invention. Elements in Figure 2B which are similar or identical to those in Figure 2A have the same reference numerals for convenience. The consumer appliance may comprise a television, Internet appliance, set top box, or other device.

30

25

As shown, the IMC 140 couples to a memory 110, e.g., a DRDRAM. The IMC 140 also provides video to a display device 142 such as a television screen, computer video monitor, flat panel display, or other type of display device. The IMC 140 further includes a video input/output port as well as connections for coupling to a PCI bus and a USB as shown. In the embodiment of Figure 2B, the IMC 140 optionally includes an internal CPU core or RISC core, and thus external CPU 102 is not required. In this embodiment, the internal CPU core or RISC core within the IMC 140 operates to execute control code and/or system level software without the need for external CPU 102.

35

Figure 3 - IMC System Architecture

Figure 3 is a block diagram illustrating an IMC system architecture of the preferred embodiment, i.e., a system which includes the Integrated Memory Controller or Interactive Media Controller (IMC) of the present invention. Figure 3 illustrates one embodiment of a system architecture, and other system architectures may be used,

as desired. It is also noted that the IMC of the present invention may be used in various types of digital devices as described above.

As shown, the IMC 140 of the present invention preferably couples to a CPU 102. The CPU 102 is optionally coupled through a cache system (not shown) to the IMC 140. The CPU 102 may include a first level cache system and the system may also comprise a second level cache. The CPU 102 is preferably an X86 CPU, but may be any of various types of CPUs, DSPs, microcontrollers, or programmable logic, as desired. Also, as used herein, the term "CPU" is intended to include external CPU 102 as well as a CPU core or processing core, comprised in the IMC 140, that executes control code or system level software.

The IMC 140 couples to system memory 110, wherein the system memory 110 comprises one or more banks of memory. In the preferred embodiment, the system memory 110 comprises two banks of memory, and the IMC 140 preferably includes two symmetric memory ports, ch1 and ch2, for coupling to the two banks in system memory 110. In the preferred embodiment, the IMC 140 couples to the system memory 110 through a RAMBUS implementation. For more information on the RAMBUS memory architecture, please see documentation available from RAMBUS, Inc.

The IMC 140 of the present invention may couple to any of various types of memory, as desired. In the preferred embodiment, the system or main memory 110 comprises DRDRAM (Direct RAMBUS dynamic random access memory), SDRAM, DDR-SDRAM or EDO (extended data out) memory. In an alternate embodiment, the system memory 110 comprises SGRAM, VRAM, or other types of memory. As noted above, the IMC 140 of the present invention may couple to any of various types of memory, as desired.

The IMC 140 couples to a display device 142, such as a computer video monitor or television screen, among others. The IMC 140 generates appropriate video signals for driving display device 142. The IMC 140 preferably generates red, green, blue (RGB) signals as well as vertical and horizontal synchronization signals for generating images on the display 142. The IMC 140 also generates NTSC video signals, PAL video signals, or video signals for other analog or digital television / video formats. The IMC 140 may generate any of various types of signals for controlling a display device or video monitor. As shown, the IMC 140 preferably uses a serial control bus, such as the I2C serial bus, for control of the display device 142.

Therefore, the integrated memory controller 140 of the present invention integrates memory controller and video and graphics controller capabilities into a single logical unit. This greatly reduces bus traffic and increases system performance.

In the embodiment shown, the IMC 140 couples to an audio codec and/or modem 144. In one form of embodiment, the IMC 140 generates appropriate data signals, preferably SPDIF, that are provided to the audio codec and/or modem 144 for audio presentation. As shown, the audio codec and/or modem 144 is operable to generate one or more of telephony voice, data and control signals, speaker output, 3D surround audio signals, and MIDI / joystick. Alternatively, the IMC 140 integrates audio processing capabilities and provides audio signal outputs that are provided directly to speakers.

A BIOS EEPROM or boot device 146 is also coupled to the IMC 140 to configure or boot the IMC 140, as described further below.

15

10

5

20

30

25

#### WO 99/56249

The IMC 140 of the present invention also preferably couples to a video and/or audio codec 172 and in one embodiment can perform one or more of MPEG video decode standards including AC-3 audio decoding. The IMC 140 communicates digital video/audio with the decoder 172. The IMC 140 also communicates control information with the codec 172 through an I2C serial bus. The IMC 140 also may include other types of video ports, such as one or more IEEE 1394 / CCIR656 ports for video in/out.

5

10

15

20

The IMC 140 of the preferred embodiment may include other I/O interfaces. In the preferred embodiment, the IMC includes PCI interface or bridge logic for providing a PCI bus interface. The PCI bus may be used for coupling to various I/O devices, such as non-volatile storage, network interface devices, etc. The IMC 140 preferably operates as a PCI bus master on the PCI bus. The IMC 140 also may provide a serial ISA bus interface for coupling to a Super I/O hub 174 for interfacing to standard I/O devices such as a keyboard, mouse, and optionally IR devices, such as IR keyboards, mice and remote control devices. The IMC 140 also may include a SCSI (Small Computer Systems Interface) for coupling to other types of I/O devices, such as a DVD (digital video disk), CD-ROM, or non-volatile storage 176. Alternate embodiments may assume that devices are connected to other I/O interfaces to carry out the functions as indicated above.

The IMC of the present invention thus comprises a video, 2D and 3D graphics controller which includes a novel object based display refresh list system for display of 2D and 3D graphical data on a display device. The IMC 140 preferably uses the main system memory of the CPU 102 in a unified or shared memory architecture manner. The IMC graphics controller 140 minimizes data movement for 2D/3D and video data manipulation for video display updates and thus greatly increases system performance. The present invention is capable of manipulating 3D graphical data similar to streaming video sources. This makes the invention well suited for display and manipulation of environments where 2D graphics, 3D graphics and streaming video formats are mixed. The IMC 140 transfers data between the CPU local bus and system memory 110 and also transfers data between the system memory and the video display output. Therefore, the IMC 140 of the present invention may eliminate the need for a separate 2D/3D graphics, audio, video, and telephony and core logic subsystems.

25

30

35

The IMC 140 uses techniques to improve overall system performance and user response time by use of the main system memory as a virtual graphical frame buffer and program/data storage. The IMC 140 provides a unique system level architecture that reduces data bandwidth requirements for general media input/output functions. Because the host CPU 102 is not required to move data between main memory and the graphics and audio and telephony subsystems as in conventional computers, data can reside virtually in the same subsystem as the main memory. Therefore, for media output data (audio, video, telephony) the host CPU or DMA master is not limited by external available proprietary bus bandwidth, thus improving overall system throughput.

The IMC 140 of the present invention preferably comprises an advanced memory controller, 2D/3D graphics, audio, video, and optionally telephony processing capabilities. The IMC 140 performs pointer-based display list video operations for manipulation of media objects on the display, as discussed below. The 3D graphics capabilities of the IMC 140 include numerous significant advances that provide greatly increased performance over prior art systems.

The IMC 140 of the present invention preferably couples to the CPU bus, a high-speed system peripheral bus such as the PCI, or other proprietary buses such as the Accelerated Graphics Peripheral bus (AGP). In alternate

embodiments the IMC may embed any of the MPEG and audio decoder standards for a stand-alone MPEG display controller implementation.

The IMC 140 includes one or more symmetric memory ports for connecting to system memory 110. The IMC 140 also includes video outputs, preferably RGB (red, green, blue) outputs as well as NTSC or HDTV video, plus horizontal and vertical synchronization signal outputs. These signals directly drive the display device 142. The IMC 140 also may include an SPDIF digital interface for control and delivery of audio and telephony. The IMC 140 also may contain a video manipulation interface to standard video components that control equipment such as VCR's and Digital videodisks. Internal IMC circuitry may also include video and audio decompression logic for manipulation of MPEG2 (video) and AC-3 (audio) standards for the DVD and HDTV specifications. The IMC 140 also may include a telephony interface via the SPDIF digital interface for local or wide area networking. This telephony interface provides connection to other systems such as the Internet or World Wide Web. In addition the IMC 140 also may include a "local" bus interface to the CPU, peripheral bus interfaces such as PCI and ISA buses, and SCSI interface for disk drives all connected to the I/O subsystem.

The IMC 140 includes a novel system architecture which helps to eliminate system bandwidth bottlenecks 15 and removes extra operations required by the CPU 102 to move and manipulate application data. The IMC 140 includes a high level protocol for the manipulation of graphical data or video data which greatly reduces the amount of bus traffic required for video operations and thus greatly increases system performance. This high level protocol includes a display list based video refresh system and method whereby the movement of objects on the video display screen 142 does not require movement of pixel data in the system memory 110, but rather only requires the manipulation of display address pointers in a display refresh list, thus greatly increasing the performance of pixel bit block transfers, animation, and manipulation of 2D and 3D objects.

It is noted that the term "graphical data" is commonly used to refer to data written to the parallel side of VRAM or the data stored to/from the frame buffer. The term graphical data is also used to refer to graphical objects or pixel data rendered to memory. The term video data is typically used to refer to data that is provided to the RAMDAC during refresh for monitor output or to live action video data. In the present disclosure, the term video data is used to include both graphical data and video data (or pixel data). In the present disclosure, the terms video data and pixel data are often used interchangeably.

## IMC System Operation

Typical operations within a system including the IMC 140 are as follows. It is assumed that the program code and data is initially stored on a non-volatile media. Program code and data may also be received from a transmission, e.g., an interactive application transmitted with a television signal. First, the IMC 140 reads program code and data stored on the non-volatile media, or received from a transmission, using a direct memory access (DMA) and/or burst control methods, where the IMC 140 preferably acts as a master on the system bus 106. The program code and data are read by the IMC 140 and stored in the system memory 110. In an alternative embodiment, the program code and data are transferred to the IMC 140 under CPU control. The data is transferred from the non-volatile media to the system memory 110 preferably in a compressed format, and thus the data requires less disk storage and reduced system bus bandwidth. As the data is transferred from the disk 120 to the IMC 140, the

10

5

20

25

30

data is preferably decompressed by a decompression engine within the IMC 140 and stored in the system memory bank 110.

The CPU 102 begins program execution by reading the recently decompressed program code from the system memory 110. Portions of the program code contain information necessary to write data and/or instructions back to the IMC 140 using a special graphical protocol to direct the IMC 140 to control the display output on the video display 142. In many cases, the graphical data is not required to leave the system memory 110 and is not required to move to another location in system memory 110, but rather the display list-based operation and high level graphical protocol of the IMC 140 enables the CPU 102 to instruct the IMC 104 how window and other graphical data is presented on the screen. This provides a tremendous improvement over prior art systems.

The high level graphical protocol used by the IMC 140 of the present invention eliminates many of the CPU reads and writes of graphical information that are required in prior art systems. Instead, a system incorporating an IMC 140 includes a high level graphical protocol whereby the CPU 102 instructs the IMC 140 to manipulate the data stored in the system memory 110. For example, when text which appears in a window on the display screen is manipulated, the text is not required to leave the system memory 110 for processing by the CPU 102. Rather, the IMC 140 reads the text data into the system memory 110, preferably in ASCII format, and the IMC 140 processes the text data for display output. This operation is performed under the direction of the CPU 102 through the high level graphical protocol used by the IMC 140, as described further below. Another example is a back store of window information when windows are occluded or moved to the background of the display screen. In current prior art systems, this operation requires either extra cost for memory in the graphical subsystem, i.e., additional video memory or VRAM, or the CPU 102 is required to move the occluded information from the graphical subsystem back into the system memory for temporary storage. In the IMC architecture of the present invention, the data remains in the same location in system memory 110 and is easily recalled when required. No data movement or backstore of data within system memory 110 is required, but rather the only change required is an update of window assembly pointers in system memory. As another example, the movement of windows on the screen does not require any movement of video data in system memory, but rather only requires change to X and Y position pointers for the respective window.

The IMC 140 of the present invention includes a novel Window Assembler or Virtual display refresh list (VDRL) system and method which performs pointer-based window assembly for the display output during screen refresh with greater efficiency. This allows for windows and/or objects to remain in their original form and location without modification during many types of video manipulation. Note, to avoid confusion between this disclosure and related applications, "virtual display refresh list" and "video display refresh list" have the same meaning.

Therefore, pointer-based VDRL system and method of the present invention reduces the amount of data required to be moved within the system for processing, thus reducing the overall cost while improving the performance of the computer system. The high level graphical communication protocol between the CPU 102 and the IMC 140 reduces bus traffic and increases performance since the CPU 102 spends much less time moving data between the various subsystems. This frees up the CPU 102 and allows the CPU 102 greater time to work on the application program rather than moving data around the system.

10

5

20

15

25

30

35

The elements of Figure 4 may be implemented in any of various ways, including an ASIC, FPGA, programmable processing (including a CPU, DSP, etc.), discrete logic, etc., or combinations thereof. As used herein, the term "engine" or "processor" is a generic term for the elements 210, 212, 220 and 240 of Figure 4, and the term "engine" or "processor" is intended to encompass each of the above possible implementations. as well as others.

#### Figure 4 - IMC Block Diagram

5

10

15

20

25

30

Figure 4 is a block diagram of the IMC 140 of the preferred embodiment. As shown, the IMC 140 includes a memory controller, referred to as a cross bounds memory control unit 220. The cross bounds memory control unit 220 couples to a CPU local bus interface 202, an Execution Engine 210, an RDRAM interface 221, a 2D/3D/video graphics engine 212, a peripheral bus interface 234, an audio/modem/telephony engine 236, a video input and format conversion block 235 and a virtual display refresh list (VDRL) engine 240 and associated display FIFOs. As shown, the IMC 140 includes a control path for enabling programming of registers, wherein this control path couples the CPU local bus interface 202, the Execution Engine 210, the DRDRAM interface 221, the 2D/3D video graphics engine 212, the peripheral bus interface bridge 234, the VDRL engine 240, the video input and format conversion block 235, and the audio and modem subsystem block 236, which couples back to the CPU local bus interface 202.

As shown, the audio and modem subsystem block 236 couples to digital audio and modem interface block 238, which then provides SPDIF signals to the audio CODEC and modem 144 (Figure 3). As shown, the video input and format conversion block 235 provides an audio/video decoder interface and also provides an IEEE-1394 and CCIR inputs. As also shown, the VDRL engine 240 couples to an RGB DAC block 250 which in turn provides RGB signals and respective synchronization signals for driving the display device 142. The VDRL engine and display FIFOs block 240 is also operable to provide a video output to an NTSC encoding and DAC block 237, which then provides NTSC television signals for provision to a television screen. As noted above, the IMC 140 is also operable to provide video signals in other formats, such as digital television signals, e.g., HDTV, among others.

In the preferred embodiment, the Execution Engine unit 210 comprises a VLIW instruction set RISC core. Alternate embodiments may use other types of CPU or DSP cores internal to the IMC or External to accomplish the execution unit function. The Execution Engine unit 210 is responsible for the assembly of 2D and 3D Virtual display refresh lists (VDRLs). The fast sort sub-core and the Z-Rules sub-core assist building of the VDRL. The IMC 140 preferably performs memory compression and decompression operations, video data manipulation, as well as three dimensional graphical object manipulations and the assembly of 2D and 3D virtual display refresh lists. The Execution Engine 210 in combination with the fast data sorting, Z-rule and 2D/3D display list cores control and manipulate graphics objects for display position within three dimensions, X, Y, and Z. Although not limited to run without a Z-buffer, for 3D graphical object manipulation no conventional Z buffer is required.

In one embodiment, the Execution Engine 210 includes a CPU core, RISC core, or other processing core for executing control code and/or system level software. In this embodiment, external CPU 102 is optionally not required.

35

Preferably, the media DSP core 236 comprises at least one digital signal processor (DSP) which controls audio, modem, and telephony data, as well as other communication standards, such as Digital Subscriber Line (DSL).

The Execution Engine 210 in turn couples to a graphics engine 212 for control of 2D/3D and video data. The graphics engine 212 connects to the display refresh block 240 which synchronizes and serializes display data

#### WO 99/56249

into the internal video DAC 250. The above internal units couple through FIFO buffers to the Cross-bounds memory control unit 220 responsible for the compression and decompression of system memory data.

For 3D graphics the compression and decompression operation is very desirable. In alternate embodiments, the compression and decompression can be enabled or disabled for of certain 3D data types, and/or during various stages of the process. For a retained mode of operation, the 3-D VDRL and the static triangle data may be compressed with a fast parallel lossless compression technique. Textures and video input source information may be compressed with a lossy compression technique. In addition, the output data that is held as off-screen data (3DDL and rendered surfaces) may also be compressed with either the lossy or lossless compression engine. For 3D applications that require immediate mode of operation, the Z data may also be compressed in lossless format by the compression engines. As indicated, all compressed memory and addressing formats assume that compressed data is stored in the external system or attached memory. Data that is read in compressed format is decompressed by the IMC's internal decompression engines prior to usage as described in the present disclosure.

The cross-bounds memory controller unit 220 contains a non-conventional cross-bar switch and memory translation logic for virtualization of the system memory into the various IMC cores. The Graphics Engine 212 includes point, line, quadrilateral and triangle rasterization operations as well as all API-required raster operations for 3D data manipulation. The IMC graphics engine 212 differs from conventional devices in that it also manipulates video and graphical data under control and direction of the 2D and 3D virtual display refresh list engines 240.

20

5\_

10

15

The output of the graphics engine can compress the final 3D image or scene data during a write operation. When the 2-D VDRL subsequently reads the 3D image(s) for refresh, a decompression process is used to restore the original format of the data. During the Refresh to the display, under control of the 2-D VDRL, the 3D data can be written back to off-screen memory as span-line compressed. The data can also be written back as compressed 3D windows or objects in a span line compressed format. Compressed 3D windows or objects are defined as areas where the 3-D VDRL has previously written image data. Once compressed in window or object span lines, the refresh operation to the display decompresses the data prior to refresh of such data via the graphics engine. It should also be noted that in the preferred embodiment, the same engine that operates on the 2D, Video, and 3D data is also operating the refresh of data to the display.

# IMC Operation - Figures 5A - 5C

Figures 5A - 5C are flowchart diagrams illustrating examples of the operation of the IMC. As shown, the IMC includes a novel system and method for manipulating and rendering 3D graphics. Steps in Figures 5A -5C may be executed concurrently or in different orders.

# Figure 5A - Execution of the 3D VDRL in Real Time for Display

As shown in Figure 5A, in step 302 the IMC first operates to construct a 3-D Virtual display refresh list (VDRL) in system memory. The IMC constructs the 3-D VDRL in response to received geometry data. The 3-D VDRL comprises a list of commands which are executable to render pixel data comprising one or more 3-D objects. The 3-D VDRL may be constructed on a per object basis, or for the entire display. Further, the 3-D VDRL may be constructed for objects which are currently desired to be displayed as well as objects which are not currently desired to be displayed, e.g., off-screen objects. Thus, synchronization and manipulation of such objects

30

is possible under control of a set of object or window display rules by execution of constructed 3-D VDRLs. Construction of the 3-D VDRL is discussed in detail with reference to the flowchart of Figure 6 and Figures 7 onward.

In step 304 the IMC then executes the 3-D VDRL by reading the VDRL and generating the appropriate pixel data to construct an image. Execution of the 3-D VDRL operates to generate or render pixel data in response to, or based on, received geometry data. Execution of the 3-D VDRL may involve accessing texture maps from a memory in creating the pixel data. Execution of the 3-D VDRL operates to generate or render pixel data, which then may be stored in system memory for later use or may be rendered to the display in real time.

In step 306 the IMC provides the pixel data generated in step 304 directly to the display device for display. For example, the pixel data generated in step 304 may be directly provided to a display buffer for immediate output to the display.

In Figure 5A, the construction of the 3-D VDRL in step 302 preferably occurs prior to the display refresh where the pixel data is displayed. However, the embodiment of Figure 5A also contemplates construction and execution of the 3-D VDRL in real time during display refresh

In the embodiment of Figure 5A, the 3-D VDRL is executed during display refresh, wherein the pixel data generated in step 304 is provided in real time to the display during display refresh. Thus the embodiment of Figure 5A presumes a large amount of processing power to enable execution of the 3-D VDRL in real time during display refresh.

Thus Figure 5A illustrates an embodiment where execution of the 3-D VDRL operates to generate or render pixel data which is provided directly and immediately for display on the display device. In other words, the pixel data generated in step 304 is not temporarily stored in the system memory for later display, but rather the pixel data is immediately provided to the display buffer for display in step 306. Thus, in this embodiment the IMC provides the pixel data directly for display in response to executing the 3-D VDRL. This embodiment generally requires more processing power than the embodiments of Figures 5B and 5C.

25 Figure 5B - Execution of the 3D VDRL and Storage of the Pixel Data for Later Display

Figure 5B illustrates an alternate embodiment of the operation of the IMC. In Figure 5B, it is presumed that there is not sufficient processing power to enable execution of the 3-D VDRL in real time during display refresh. Note that this method may also be used even when sufficient processing power is present. Steps in Figure 5B which are similar or identical to those in Figure 5A have the same reference numerals for convenience.

As shown in Figure 5B, in step 302 the IMC first operates to construct a 3-D Virtual display refresh list (VDRL) in system memory.

In step 304 the IMC then executes the 3-D VDRL by reading the VDRL and generating the appropriate pixel data to construct an image, i.e., to generate pixel data corresponding to the image.

In step 308 the IMC stores the pixel data in a memory in response to execution of the 3-D VDRL in step 304.

Here the IMC executes the 3-D VDRL in step 304 and stores the resultant pixel data in a memory in step 308, rather than providing the resultant pixel data directly to the display in Figure 5A. This occurs, for example, because the IMC lacks sufficient processing power to execute the 3-D VDRL in real time during display refresh.

20

15

5

10

30

The rendered pixel data stored in the memory in step 308 is displayed at a later time using either a 2-D VDRL, a 3-D VDRL, or a conventional frame buffer.

In one embodiment where the IMC utilizes a 2D VDRL to display the pixel data, in step 312 the IMC preferably creates a 2-D VDRL which references the pixel data. The 2-D VDRL comprises pointers and commands which reference pixel data stored in the memory for display, including at least a portion of the pixel data rendered in the system memory in response to execution of the 3-D VDRL. In step 314 the IMC then executes the 2-D VDRL to render the pixel data on the screen. Creation and execution of a 2-D VDRL is described in U.S. Patent No. 5,838,334, incorporated by reference above.

In another embodiment where the IMC utilizes a 3D VDRL to display the pixel data, in step 318 the IMC preferably creates a second different 3-D VDRL, referred to as the main 3-D VDRL, which references the pixel data for display. The main 3-D VDRL comprises pointers and commands which reference triangles generated in response to other geometry data, as well as the pixel data rendered into the system memory due to execution of the 3-D VDRL in step 304 and storage of the pixel data in step 308. The main 3-D VDRL comprises pointers and commands which reference viewed triangle spans, e.g., information describing the start and end of triangles on respective scan lines. These viewed triangle spans possibly include triangle spans rendered from other geometry data, as well as triangle spans comprising the pixel data generated in step 304.

In the preferred embodiment, the main 3-D VDRL is preferably constructed to include one or more large triangles (3DDL) which reference the pixel data rendered into the system memory due to steps 304 and 308. In this case, the pixel data rendered into the system memory in steps 304 and 308 is treated much like a texture map. Since the 3-D VDRL preferably only references triangle spans, the pixel data rendered in step 304 is preferably referenced using one or more larger triangles (Note that, instead of a triangle span, the fundamental primitive for a 3D-VDRL that is in a hierarchical form (3DDL) alternatively may be a trapezoid or other polygon with horizontal top and bottom. Although triangles are much more commonly used, the main 3DDL may be a single trapezoid or rectangle type, referred to as a Triangle primitive type in this disclosure).

In step 320 the IMC then executes the main 3-D VDRL to render the pixel data on the display. Execution of the main 3-D VDRL includes accessing the pixel data from the memory during rendering of the triangle spans corresponding to the one or more large triangles which reference the pixel data. In this case, the pixel data is accessed much like a texture map. Creation and execution of a 3-D VDRL is described below.

The use of larger triangles to represent pixel data rendered from another 3-D VDRL allows a combination of a plurality of 3D objects into a single object, e.g., a texture map, for reduced bandwidth requirements. Stated another way, this method operates to combine or condense a large plurality of triangles from a first 3D VDRL into a few (one or more) much larger triangles in a main 3D VDRL, thereby enabling more efficient execution of the main 3D VDRL.

Alternatively, in step 324 the IMC stores the rendered pixel data in a conventional frame buffer. In step 326 the IMC performs a refresh of the frame buffer to render the pixel data on the screen. In the embodiment of steps 324 and 326, construction and execution of one or more 3-D VDRLs is required to be performed for the entire display area, since a conventional frame buffer is used. The term "frame buffer" is used to indicate an off-screen storage location. Execution of the 3-D VDRL may result in a plurality of objects stored in virtual memory

20

15

5

10

30

areas for assembly to the display surface by the main 2-D VDRL. Thus, the frame buffer nomenclature in this disclosure may not be the area from which the display data is refreshed, but a memory area for 3D object or window storage.

# Figure 5C - Store 3D VDRL in Memory for Later Execution

Figure 5C illustrates an alternate embodiment, where the IMC stores the 3-D VDRL in memory for later execution. Note that the 3-D VDRL may be stored in compressed format to save memory bandwidth and memory space. In this embodiment, in step 302 the IMC first constructs the 3-D VDRL in system memory. In step 342 the IMC stores the 3-D VDRL in memory in response to construction of the 3-D VDRL in step 302.

Steps 346 - 348 illustrate an embodiment where a 2D VDRL is used to invoke the 3D VDRL created and stored in steps 302 and 342. Steps 352 - 354 illustrate an embodiment where a main 3D VDRL is used to invoke the 3D VDRL created and stored in steps 302 and 342.

As shown in the embodiment of Figures 346 - 348, in step 346 the IMC preferably creates a 2-D VDRL which calls or invokes the stored 3-D VDRL for execution during execution of the 2-D VDRL. The 2-D VDRL comprises pointers and commands which reference pixel data stored in the memory for display, as well as commands which invoke one or more 3-D VDRLs for execution. The 2-D VDRL references pixel data which may have been previously created or rendered by the graphics engine, or by prior execution of a 3-D VDRL as described in Figure 5B.

In step 348 the IMC then executes the 2-D VDRL to render the pixel data on the screen. During execution of the 2-D VDRL, the 2-D VDRL operates to invoke the 3-D VDRL, which is then executed. Thus the 3-D VDRL is called and executed during execution of the 2-D VDRL. Creation and execution of a 2-D VDRL is described in U.S. Patent No. 5,838,334, incorporated by reference above.

As shown in the embodiment of Figures 352 - 354, in step 352 the IMC preferably creates a main 3-D VDRL which calls or invokes the stored 3-D VDRL for execution during execution of the main 3-D VDRL. The main 3-D VDRL comprises pointers and commands which are read by the IMC and interpreted for output to the memory for display, as well as commands which invoke one or more 3-D VDRLs for execution. The main 3-D VDRL may also reference pixel data which may have been previously created or rendered by the graphics engine, or by prior execution of a 3-D VDRL as described in step 318 of Figure 5B.

In step 354 the IMC then executes the main 3-D VDRL to render the pixel data on the screen. During execution of the main 3-D VDRL, the main 3-D VDRL operates to invoke the stored 3-D VDRL, which is then executed. Thus the stored 3-D VDRL is called and executed during execution of the main 3-D VDRL.

Figure 6 – Construction of the 3-D VDRL

Figure 6 is a flowchart diagram illustrating operation of the IMC in constructing a 3-D VDRL. Various of the steps in Figure 6 may occur concurrently or in different orders. The preferred embodiment of the IMC uses a VLIW RISC based execution engine, or alternatively a custom hard-wired engine to parameterize the vertex data into triangles with main edge slopes and orthogonal slopes used for scan conversion to the display surface.

In step 402 the IMC receives geometry data. The geometry data preferably comprises vertex information specifying information regarding a plurality of vertices. The plurality of vertices are useable to form a plurality of polygons, also called polygon primitives. The vertex information comprises, for each vertex, information such

16

5

15

20

25

30

as position, diffuse color, and/or normal information, as well as specular color, lighting, and/or shading information, and optionally texture coordinate, transparency, fog factor and perspective scaling, among others. The geometry data thus comprises data representing or identifying polygons, wherein the polygons are useable to form more complex shapes or objects, including 2-D and 3-D objects. The geometry data or polygons are preferably triangles, but may also comprise points, lines, triangles, trapezoids, quad meshes, strip meshes, fan meshes, star meshes, quadrilaterals, splines, or other types of polygons, or combinations thereof. In the preferred embodiment, the polygons comprise triangles or triangle meshes, and the description below is described presuming the polygons comprise triangles. In one embodiment, the geometry data is received in a compressed format, and is decompressed upon receipt by the IMC.

In the preferred embodiment, an alternate method is used for rasterization of very small triangles. This method establishes a procedure for determination of the approximate number of pixels per triangle or other primitive during the triangle set-up calculations. If the number of pixels per triangle or primitive is less than a threshold value, the triangle is rasterized differently than indicated in this disclosure. First, because the vertex information in a small triangle does not span a large delta (change in attribute values per change of X, Y or Z), a simple bi-linear average of the main edge and opposite edge values is determined. In addition, the orthogonal (ortho) values use a simple interpolation as well to determine points that fill in the center of the small triangle or primitive object. Secondly, the point values are assembled into the standard 3-D VDRL list as point and/or line primitives with all the necessary attributes and source address required for full rasterization by the 3D engine. Thus, when the 3D-VDRL list is parsed by the VDRL refresh engine, the point and line primitives fill and render the triangle in a equivalent manner to the preferred embodiment indicated by this disclosure.