# **Fundamentals** of MOS Digital Integrated Circuits

## JOHN P. UYEMURA

#### ADDISON-WESLEY PUBLISHING COMPANY

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam • Bonn Sydney • Singapore • Tokyo • Madrid • Bogotá Santiago • San Juan

This book is in the Addison-Wesley Series in Electrical and Computer Engineering

Library of Congress Cataloging-in-Publication Data

Uyemura, John P. (John Paul), 1952-Fundamentals of MOS digital integrated circuits.

Includes index.

1. Digital integrated circuits. 2. Metal oxide semiconductors. I. Title TK7874.U94 1988 621.381'73 87-11458 ISBN 0-201-13318-0

TK1874 TK194 J988

Copyright © 1988 by Addison-Wesley Publishing Company

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

ABCDEFGHIJ-HA-898

## Contents

| Preface Note on Program Listings                                                                                                                                                                                          | vii<br>xiii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CHAPTER 1: MOSFETs                                                                                                                                                                                                        |             |

| 1.1 Introduction to the MOS System 1 1.2 MOSFET Structure and Operation 12 1.3 The Gradual Channel Approximation 18 1.4 MOSFET Circuit Equations 22 1.5 The Complete MOSFET GCA Analysis 30 1.6 Depletion-Mode MOSFETs 35 |             |

| CHAPTER 2: Small-Geometry MOSFETs for VLSI                                                                                                                                                                                | 48          |

| 2.1 MOSFET Scaling Theory 49 2.1.1 Full Scaling 51 2.1.2 Constant-Voltage Scaling 54 2.1.3 Practical Limitations on the Use of Scaling Theory                                                                             | 55          |

|                                                                                                                                                                                                                           | χý          |

The state of the second second

5.2.3 Etching 258 5.3 Isolation Techniques

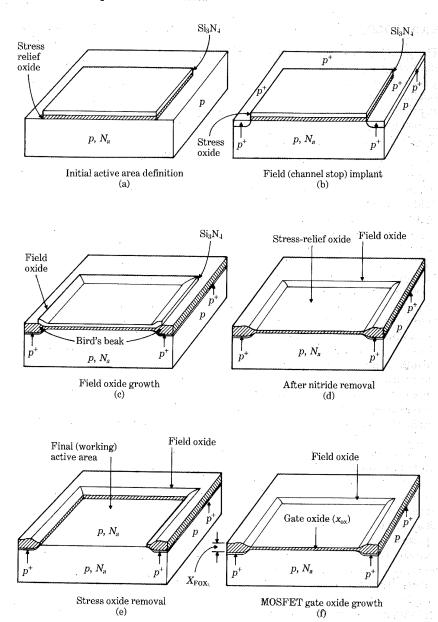

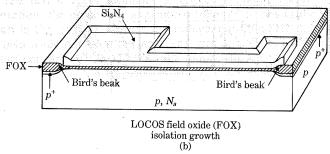

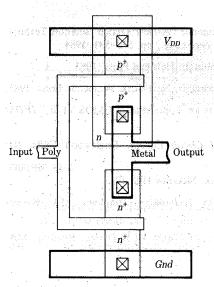

**5.3.2 LOCOS**

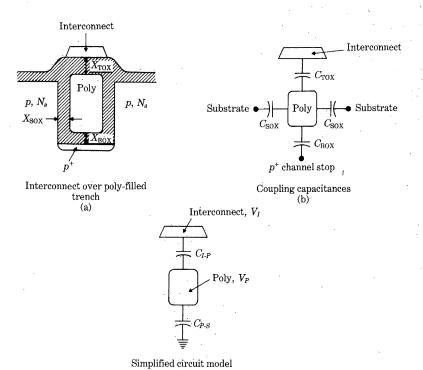

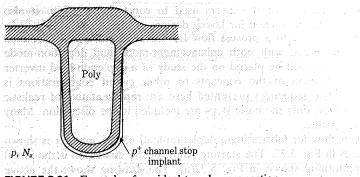

5.3.3 Trench Isolation

263

5.3.1 Etched Field Oxide Isolation

267

5.5

5.6

5.7

5.8

5.9

6.1 6.2

6.3

6.4

6.5

6.6

6.7

6.8

CHAPT

7.1

7.2

7.3

7.4

7.5

7,6

CHAPT

8.1

CHAPT

|                                                                                                                | Oghojie William                                                                                           |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Γs 57                                                                                                          | 5.4 nMOS LOCOS Process Flow 273 5.5 Threshold Voltage Adjustment 282 5.4 nMOS Design Rules and Layout 284 |

|                                                                                                                | 5.6 nMOS Design Rules and Layout 284 5.6.1 Physical Basis of Design Rules 284 5.6.2 Mask Drawings 288     |

|                                                                                                                | 5 6 2 Decign Rule Sets 289                                                                                |

|                                                                                                                | 5 CA Comports on I avout 291                                                                              |

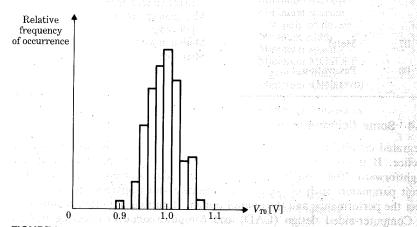

| 79                                                                                                             | 5.7 Processing Variations 292                                                                             |

|                                                                                                                | 5.7.1 Generalized Modeling 292 5.7.2 Analysis of Device Parameters 294                                    |

|                                                                                                                | 5.7.2 Analysis of Device Farameters 5.7.3 Circuit Design Criteria 296                                     |

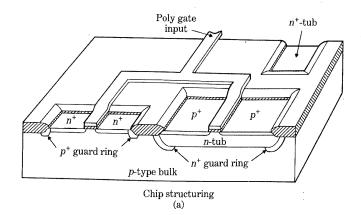

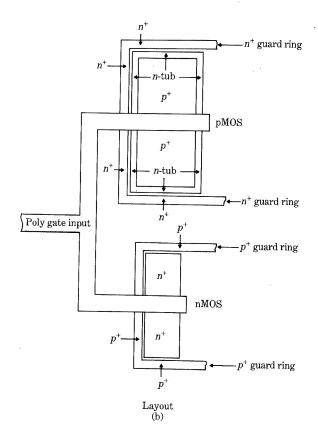

|                                                                                                                | 5.8 CMOS Technologies 296                                                                                 |

|                                                                                                                | 5.9 CMOS Design Rules 304                                                                                 |

| ds 113                                                                                                         |                                                                                                           |

|                                                                                                                | CHAPTER 6: Combinational MOS Logic Circuits 311                                                           |

|                                                                                                                | 6.1 nMOS NOR Gate 311 6.2 nMOS NAND Gate 317 6.3 Complex Static nMOS Logic 325                            |

| 158                                                                                                            | 6.4 nMOS XOR, XNOR, and Associated Circuits 551                                                           |

|                                                                                                                | 6.5 CMOS NAND and NOR Gates 344                                                                           |

|                                                                                                                | 6.5.1 2-Input NAND Analysis 346 6.5.2 2-Input NOR Analysis 352                                            |

|                                                                                                                | 6.5.3 Comparison of CMOS NAND and NOR Gates 357                                                           |

|                                                                                                                | 6.6 Complex CMOS Logic 358                                                                                |

|                                                                                                                | Transmission Cate CMUN LOGIC 229                                                                          |

| •                                                                                                              | TAL CMOC Transmission (intel Characteristics                                                              |

| and the second second                                                                                          | 6.7.1 CMOS Transmission Cute Charles 6.7.2 TG Logic Implementation 366 6.8 Nonstandard CMOS Gates 371     |

|                                                                                                                | 6.8 Nonstandard CMOS Gales 371                                                                            |

| 228                                                                                                            |                                                                                                           |

|                                                                                                                | CHAPTER 7: Bistable Logic Elements 386                                                                    |

| 29                                                                                                             | 7.1 nMOS SR Flip-Flop 386                                                                                 |

|                                                                                                                | 7.2 Clocked Flip-Flops 392 7.3 The Schmitt Trigger 398                                                    |

|                                                                                                                | 7,5 The Semmer 266                                                                                        |

|                                                                                                                | 7.4 CMOS SR Flip-Flops 408 7.5 Clocked CMOS Flip-Flops 413                                                |

|                                                                                                                | 7.5 Clocked Chief Taper 7.6 CMOS Schmitt Trigger 420                                                      |

|                                                                                                                |                                                                                                           |

| 3                                                                                                              | CHAPTER 8: Synchronous nMOS Logic 428                                                                     |

|                                                                                                                |                                                                                                           |

|                                                                                                                | 8.1 nMOS Pass Transistors 428 8.1.1 Charging Analysis: Logic 1 Transfer 431                               |

| Maria de la companya | 8.1.1 Charging Analysis: Logic 0 Transfer 8.1.2 Discharging Analysis: Logic 0 Transfer 435                |

| nativity (                                                                                                     | 8.1.2 Distriating Finally Soft Nodes 438                                                                  |

|                                                                                                                |                                                                                                           |

|                                                                                                                |                                                                                                           |

| 9                                                                                                              |                                                                                                           |

**INDEX**

619

### **CHAPTER**

### MOS Integrated Circuit Fabrication

A VLSI processing facility constitutes the major financial commitment for integrated circuit production. Vast amounts of money and engineering time are invested in an effort to advance and refine the state of the art. Higher throughput, circuit densities, and yields are all important to the economic stability of the industry.

Circuit design is structured by the processing. The interplay between chip fabrication and circuit design cannot be separated. Rather, they merge to become a single discipline. Process engineers must understand circuit design, and circuit designers must have a knowledge of fabrication if they are to be effective.

The fundamentals of silicon chip fabrication are discussed in this chapter, with an emphasis on MOS-based processes, as suggested by the chapter title. The level is introductory and is not meant to replace a detailed course in the subject. Instead, the objective is to bring out important points relevant to circuit design.

Persons with experience in the subject matter may choose to simply glance through most of the chapter in a first reading. The mathematics can generally

be omitted without loss of continuity in later chapters. Note, however, that some of the drawings are worth attention.

#### 5.1 Overview of Basic Silicon Processing Steps

stales and come a fight of the form frequency in a con-

This section will center around a brief examination of the basic wafer processing steps used to fabricate silicon integrated circuits. The discussion is intended only as an overview. A reader desiring a more in-depth treatment should consult one of the texts referenced at the end of the chapter.

#### 5.1.1 Thermal Oxidation

Thermal oxidation is the process used to create a "native" silicon dioxide (SiO<sub>2</sub>) layer on a silicon surface. The SiO<sub>2</sub> grown by this process is used in different ways. For example, it serves as the insulator in the MOS system, is needed to perform patterning during the lithography, and allows for the technique of LOCOS (local oxidation of silicon) device isolation.

A silicon dioxide layer may be grown by passing an oxygen-rich gas over a silicon surface. Pure oxygen can be used as described by the reaction

$$Si + O_2 \rightarrow SiO_2$$

.

nent for

time are

Higher conomic

en chip terge to design,

re to be

chapter, ler title.

e in the

vant to

y glance

enerally

Steam is also used to grow oxide layers. The reaction is

$$Si + 2H_2O \rightarrow SiO_2 + 2H_2$$

where it is seen that free hydrogen is left as a by-product. Both reactions use heat as a catalyst, thus giving rise to the term "thermal" oxidation. Oxide growth using  $O_2$  is called a "dry" process to distinguish it from "wet" oxidation in steam.

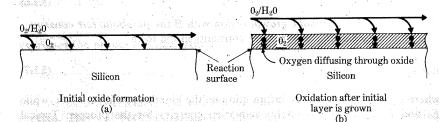

The kinetics of the oxide growth process can be understood by referring to Fig. 5.1. Figure 5.1(a) shows that the oxygen can react directly with the surface

FIGURE 5.1 Thermal oxidation process.

INTEL - 1110 Page 8 of 89

$$x_{\text{ox}}^{2}(t) + Ax_{\text{ox}}(t) = B(t + t_{0}),$$

(5.1-1)

where A and B are quantities characterizing the growth variables, such as temperature and pressure, and  $t_0$  is included to account for any existing oxide at time t = 0. Denoting this initial oxide thickness by  $x_{ox}(0)$ ,  $t_0$  is computed from

$$t_0 = \frac{1}{B} [x_{\text{ox}}^2(0) + Ax_{\text{ox}}(0)].$$

(5.1-2)

The solution to the oxide growth equation is

$$x_{\text{ox}}(t) = \frac{A}{2} \left[ \sqrt{1 + \frac{4B}{A^2}(t + t_0)} - 1 \right],$$

(5.1-3)

which allows for the growth rate  $(dx_{ox}/dt)$  to be calculated.

To study the oxidation process, assume that  $x_{ox}(0) = 0$  so that  $t_0 = 0$  for simplicity. Then eqn. (5.1-3) reduces to

$$x_{\text{ox}}(t) = \frac{A}{2} \left[ \sqrt{1 + \frac{4Bt}{A^2}} - 1 \right]. \tag{5.1-4}$$

For small values of t corresponding to the initial oxidation, the square-root term may be expanded in a Taylor series to give

$$x_{\rm ox}(t) \simeq \frac{B}{A}t. \tag{5.1-5}$$

Since the oxide thickness is proportional to the oxidation time t, this is called the *linear growth region* with (B/A) the *linear rate constant*. As the oxidation time is increased,  $(4Bt/A^2)$  dominates the square-root term, so for large values of t,

$$x_{\rm ox}(t) \simeq \sqrt{Bt}. \tag{5.1-6}$$

This describes the parabolic growth region with B the parabolic rate constant.

It is possible to express the rate constants in the form

$$B = C_1 e^{-E_1/kT},$$

$$(B/A) = C_2 e^{-E_2/kT},$$

(5.1-7)

where  $C_1$  and  $C_2$  contain the information on the kinetic growth variables, while  $E_1$  and  $E_2$  are (approximately) activation energies for the process. Typical values for (111) and (100) silicon surfaces are given in Table 5.1 for both dry

rate. After an iO<sub>2</sub> (as shown atly, the oxide eactant fluxes that the oxide ratic equation

bles, such as existing oxide is computed

$$(5.1-2)$$

(5.1-3)

hat  $t_0 = 0$  for

(5.1-4)

e square-root

(5.1-5)

this is called the oxidation or large values

(5.1-6)

ate constant.

(5.1-7)

riables, while ocess. Typical for both dry

**TABLE 5.1** Oxide Growth Rate Constants\*

| Ar väge hava           | Parabolic Rate Constant: $B$<br>Linear Rate Constant: $(B/A)$                          | $= C_1 e^{-E_1/kT}$ $= C_2 e^{-E_2/kT}$             |

|------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|

| Source                 | (111) Silicon                                                                          | (100) Silicon                                       |

| Dry O <sub>2</sub>     | $C_1 = 7.72 \times C_2 = 6.23 \times 10^6 [\mu \text{m/hr}]$ $E_1 = 1.$ $E_2 = 1.$     | $C_2 = 3.71 \times 10^6 [\mu \text{m/hr}]$          |

| Steam<br>(@ 640 torr.) | $C_1 = 3.86 \times $ $C_2 = 1.63 \times 10^8  [\mu \text{m/hr}]$ $E_1 = 0.$ $E_2 = 2.$ | $C_2 = 0.97 \times 10^8 [\mu \text{m/hr}]$ .78 [eV] |

<sup>\*</sup> From S. K. Ghandhi, VLSI Fabrication Principles, New York: Wiley, © 1983. Reprinted with permission from John Wiley & Sons, Inc.

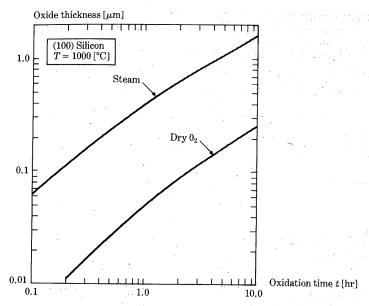

and wet oxide growth rates. At a given temperature T, steam oxidation is much faster than that obtained by dry  $O_2$ . This faster growth rate is offset by the fact that the presence of excess  $H_2O$  found in the steam-grown oxide leads to inferior  $SiO_2$  properties. Critical  $SiO_2$  layers such as those required for MOSFET gate oxides are usually grown in dry oxygen. Examples of oxide thickness as a function of growth time are shown in Fig. 5.2. Increased pressure enhances the oxide growth rate, so *high-pressure* oxidation is commonly used when large  $x_{ox}$  values are needed in the chip design. Heavy doping in the silicon also increases the growth rate of an oxide layer.

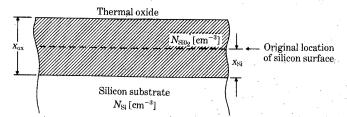

Thermal oxidation uses silicon atoms at the Si-SiO<sub>2</sub> interface to create molecules of silicon dioxide. The location of the silicon surface will thus be different after the oxide growth is completed. This is illustrated in Fig. 5.3. The thickness  $x_{Si}$  of the silicon lost to the oxide growth can be related to the oxide thickness  $x_{ox}$  using simple arguments. First, recall that  $N_{Si} = 5 \times 10^{22}$  [Si atoms/cm<sup>3</sup>] are in the crystal. The silicon dioxide has approximately  $N_{SiO_2} = 2.3 \times 10^{22}$  [molecules/cm<sup>3</sup>]. Since it takes one atom of silicon to create one molecule of SiO<sub>2</sub>,

$$N_{\rm Si}x_{\rm Si} = N_{\rm SiO_2}x_{\rm ox} \tag{5.1-8}$$

expresses the proper balance. Thus,

$$x_{\rm Si} = \frac{N_{\rm SiO_2}}{N_{\rm Si}} x_{\rm ox} \simeq 0.46 x_{\rm ox}$$

(5.1-9)

may be used to calculate the amount of silicon consumed in the oxidation process. This will become particularly important when the LOCOS isolation technique is discussed.

FIGURE 5.2 Example of thermal oxide growth.

It has been found that stray ionic charges, most notably alkali ions such as  $\mathrm{Na}^+$ , are trapped in thermally grown oxide layers. This leads to problems in MOS threshold voltage variations through the flatband voltage  $V_{FB}$ . The amount of ionic charge can be reduced by performing the oxidation in a chlorinated atmosphere, such as that obtained by adding HCl or chlorine gas. The addition of chlorine to the recipe allows for trapping of  $\mathrm{Na}^+$  ions into neutral subsystems. This reduces charge at the  $\mathrm{Si}\text{-}\mathrm{SiO}_2$  interface to levels where acceptable MOSFET performance can be attained. Phosphosilicate glass (PSG) may also be used as a method to attract mobile ions to a region of the oxide where they can be neutralized or removed.

FIGURE 5.3 Geometry for calculation of silicon consumed in the thermal oxidation process.

#### **EXAMPLE 5.1-1**

An oxide layer is grown on (111) silicon using steam. The oxidation is performed at 1000 [°C] and lasts for 1 hour. Calculate  $x_{ox}$ .

#### Solution

First find the growth rate constants. For (111) silicon in steam,

$$B = 3.86 \times 10^{2} e^{-0.78/(8.62 \times 10^{-5})(1273)} \approx 0.316 \, [\mu \text{m}^{2}/\text{hr}],$$

while

$$(B/A) = 1.63 \times 10^8 e^{-2.05/(8.62 \times 10^{-5})(1273)} \approx 1.244 \, [\mu \text{m/hr}].$$

Dividing,

$$A = \frac{B}{(B/A)} \approx 0.252 \, [\mu \text{m}].$$

Using eqn. (5.1-4) then gives

$$x_{\text{ox}} \simeq \frac{(0.252)}{2} \left[ \sqrt{1 + \frac{4(0.316)(1)}{(0.252)^2}} - 1 \right],$$

so

$$x_{ox} \simeq 4500 \, [\text{Å}].$$

fhel

Ilkali ions such as Is to problems in oltage  $V_{FB}$ . The e oxidation in a 1 or chlorine gas. of Na<sup>+</sup> ions into to levels where sphosilicate glass o a region of the

o jaleribi SiO.

korkram deks Petrophysikir

jadorliči sejšnologi,

thermal oxidation

#### 5.1.2 Impurity Diffusion

The diffusion of impurity atoms into silicon crystal has been used since the beginnings of the semiconductor industry. This doping technique is based on the fact that dopant atoms gain thermal kinetic energy at elevated temperatures. When this motion is combined with a gradient in the doping density N(x), a net flux of particles  $F[\text{cm}^2\text{-sec}]^{-1}$  is created such that the particles tend to move away from regions of high concentration. Mathematically this motion is described by Fick's law in the (one-dimensional) form

$$F = -D\frac{\partial N(x)}{\partial x},\tag{5.1-10}$$

where D [cm<sup>2</sup>/sec] is the diffusion coefficient. D depends on the temperature, the dopant species, and the concentration of dopants in the diffusion path. Diffusions are typically performed in the temperature range 900-1100 [°C].

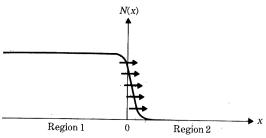

The general properties of diffusive motion are obtained by writing a balance equation for particle densities. Consider the situation shown in Fig. 5.4 where a concentration gradient causes particles to diffuse from region 1 to region 2. Since the number of particles lost from region 1 is (dN/dt), the flow

FIGURE 5.4 Particle flow established by a concentration gradient.

is described by

$$\frac{\partial N(x,t)}{\partial t} = -\frac{\partial F(x)}{\partial x}.$$

(5.1-11)

Classical diffusion theory assumes that D is not a function of position x. Thus, substituting the flux from eqn. (5.1-10) gives the diffusion equation

$$\frac{\partial N(x,t)}{\partial t} = D \frac{\partial^2 N(x,t)}{\partial x^2}.$$

(5.1-12)

This partial differential equation can be solved subject to appropriate boundary conditions to determine the impurity profile diffused into the silicon. The diffusion coefficient D in this equation is interpreted as an average value and varies with dopant species and diffusion temperature T [°K]. It may be computed using the formula

$$D = D_0 e^{-E_{\rm av}/kT},\tag{5.1-13}$$

in which  $E_{\rm av}$  is an average activation energy corresponding to the dopant "jumping" from site to site. Approximate values of  $D_0$  and  $E_{\rm av}$  are provided in Table 5.2 for B, P, and As.

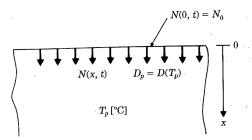

Dopant profiles are controlled by the manner in which the dopants diffuse into the silicon. Two types of profiles are of particular interest. The first is obtained using a *constant surface concentration* (or *predeposit*) process in which the surface dopant density  $N_{\rm S}=N(0)$  is maintained at a value  $N_0$  [cm<sup>-3</sup>].  $N_0$  is

th

#### T. B. BURMAXS

za roysi obino saA j 4040 sa bererebrer

Solution Fig. find the ignor

> ursa gyddiad

nt.

(5.1-11)

of position x. Thus, equation

(5.1-12)

ject to appropriate used into the silicon. as an average value T [°K]. It may be

(5.1-13)

iding to the dopant  $I E_{av}$  are provided in

1 the dopants diffuse interest. The first is (sit) process in which alue  $N_0$  [cm<sup>-3</sup>].  $N_0$  is

**TABLE 5.2** Average Diffusion Coefficients for Common Silicon Dopants

| $D = D_0 e^{-E_{\text{av}}kT} [\text{cm}^2/\text{sec}]$ |                              |                       |  |  |

|---------------------------------------------------------|------------------------------|-----------------------|--|--|

| Dopant                                                  | $D_0$ [cm <sup>2</sup> /sec] | $E_{ m av} [{ m eV}]$ |  |  |

| Boron                                                   | 5.853                        | 3.62                  |  |  |

| Phosphorus                                              | 5.853                        | 3.62                  |  |  |

| Arsenic                                                 | 0.091                        | 3.37                  |  |  |

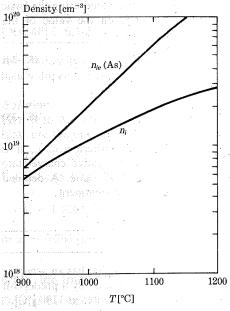

known as the solid solubility limit and represents the maximum dopant density that can be "dissolved" in the silicon.  $N_0$  depends on the dopant species and temperature as illustrated by the graph of Fig. 5.5. This type of diffusion problem is shown in Fig. 5.6(a). Assuming that the diffusion cycle lasts a time  $t_p$  and is carried out at a temperature  $T_p$ , the final impurity profile is found to be

$$N(x) = N_0 \operatorname{erfc}\left(\frac{x}{2\sqrt{D_p t_p}}\right), \tag{5.1-14}$$

FIGURE 5.5 Solid solubility limits for boron, arsenic, and phosphorus.

Basic diffusion problem

FIGURE 5.6 Constant surface concentration diffusion.

where  $D_p = D(T_p)$ . The complementary error function erfc (y) is given by

$$\operatorname{erfc}(y) = 1 - \operatorname{erf}(y),$$

(5.1-15)

where erf (y) is the error function defined by the integral representation

$$\operatorname{erf}(y) = \frac{2}{\sqrt{\pi}} \int_0^y e^{-u^2} du.$$

(5.1-16)

A plot of the erfc profile is shown in Fig. 5.6(b). The total number of dopant atoms Q introduced into the wafer during this step is

$$Q = A \int_0^\infty N(x) \, dx = 2N_0 A \sqrt{\frac{D_p t_p}{\pi}}, \tag{5.1-17}$$

with A being the surface area. This type of diffusion is used for shallow doping profiles and also as a first step in deep diffusions.

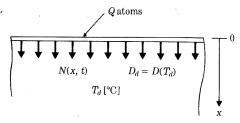

The second type of diffusion problem is one where the dopants have been introduced into the wafer by a predeposit step and are then subjected to a higher-temperature drive-in diffusion at temperature  $T_d$  for time  $t_d$ . This is shown in Fig. 5.7(a) and is also known as a *limited source* diffusion. Assuming that Q atoms have been left by the predeposit, solving eqn. (5.1-12) gives the Gaussian profile

$$N(x) = \frac{Q}{A\sqrt{\pi D_d t_d}} e^{-x^2/4D_d t_d},$$

(5.1-18)

with  $D_d = D(T_d)$ . Using Q from eqn. (5.1-17) finally yields the result of this 2-step process as

$$N(x) = \frac{2N_0}{\pi} \sqrt{\frac{D_p t_p}{D_d t_d}} e^{-x^2/4D_d t_d}.$$

(5.1-19)

This profile is illustrated in Fig. 5.7(b) and is valid as long as  $(D_d t_d) \gg (D_p t_p)$  is satisfied. Usually the wafer will be subjected to additional heat treatment steps, which will cause the dopants to diffuse deeper into the silicon. This may be accounted for by replacing the factor  $(D_d t_d)$  in eqn. (5.1-19) by an effective value

$$\overline{Dt} = D_d t_d + D_1 t_1 + D_2 t_2 + \cdots, {(5.1-20)}$$

where each term  $D_j t_j$  in the sum represents the effect of a separate heating step in the wafer processing.

The doping profiles in eqns. (5.1-14) and (5.1-19) are reasonable approximations as long as the doping levels are low enough to ignore the dependence of D on the carrier densities. High-concentration diffusions used in certain VLSI processes do not result in erfc or Gaussian profiles, and the analysis must be modified to describe these situations. The most general

Basic diffusion process (a)

FIGURE 5.7 Limited source diffusion.

TABLE 5.3 Concentration-Dependent Diffusion

Coefficient Quantities\*

| W. S. W. W. S. |               | 33770 1338 |                  |                       |                                      | 1.5 |

|----------------------------------------------------|---------------|------------|------------------|-----------------------|--------------------------------------|-----|

| 4941.80                                            | Г             | . //       | Ν                | $/n$ \ <sup>2</sup>   | $+ D_i^+ \left(\frac{p}{n_i}\right)$ | 1   |

| n-L                                                | ו יים         | n-14       | 1 1 1 <i>1</i>   | )=1 <u></u> 1 .       | + D+( <u>-</u> \                     | 100 |

| D-n                                                | $D_i$ T       | $D_i$      | / ' <del>-</del> | 1 \ in                | \ \ n \                              | 1   |

|                                                    | <b>L</b> a co | $\sim M$   | il               | $\langle n_i \rangle$ |                                      | ٠.  |

|                                                    |               |            |                  |                       |                                      |     |

$D_i^x = D_0^x e^{-E_a^x/kT}$

| Dopant          | Boron                                            | Phosphorus  | Arsenic      |

|-----------------|--------------------------------------------------|-------------|--------------|

| $D_0^o$ $E_a^o$ | 0.091<br>3.36                                    | 3.85        | 0.38<br>3.58 |

| $D_0^-$         |                                                  | 4.44<br>4.0 | 22.9         |

|                 | -<br>Hotel <del>is</del> ikus<br>Var gastrijnski | 4 65        | <u>-</u>     |

|                 | 166.3<br>4.08                                    |             |              |

$D_0^x$  in [cm<sup>2</sup>/sec],  $E_a^x$  in [eV]

Sandw ,

situation is described by writing the diffusion coefficient in the form

$$D = h \left[ D_i^o + D_i^- \left( \frac{n}{n_i} \right) + D_i^- \left( \frac{n}{n_i} \right)^2 + D_i^+ \left( \frac{p}{n_i} \right) \right], \tag{5.1-21}$$

where h is called the *field enhancement factor*. It accounts for *field-aided* diffusion under the influence of a built-in electric field that is created by the separation of electrons from their host dopant atoms. h has a value between 1 and 2. n and p are the carrier densities, while  $n_i$  is the intrinsic concentration at the diffusion temperature. The quantity  $D_i$  is the intrinsic diffusion coefficient for the x charge-state vacancy. Intrinsic values are computed from

$$D_i^x = D_0^x e^{-E_a^x/kT}, (5.1-22)$$

where  $E_a$  is the activation energy for the state. Table 5.3 provides values of  $D_0$  and  $E_a$  for B, P, and As. Note that only certain terms in eqn. (5.1-21) contribute to D for a given dopant.

Boron is a p-type (acceptor) dopant that exhibits neutral and positive charge-state vacancy interactions. The diffusion coefficient has the form

$$D \simeq D_i^o + D_i^+ \left(\frac{\underline{p}}{n_i}\right), \tag{5.1-23}$$

<sup>\*</sup>From R. A. Colclaser, Microelectronics Processing and Device Design, New York: Wiley, © 1980. Reprinted with permission from John Wiley & Sons, Inc.

where the field enhancement factor has been set to unity. It is convenient to define an average intrinsic diffusion coefficient by

$$D_i = D_i^o + D_i^+. {(5.1-24)}$$

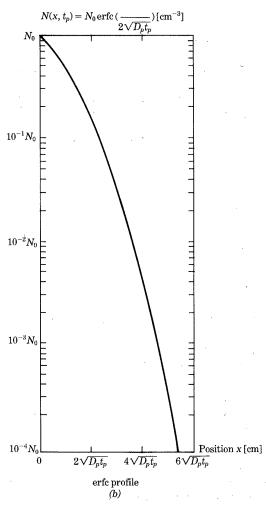

A constant surface concentration boron diffusion is then found to be described by the profile

$$N(x, t_p) \simeq N_0(1 - Y^{2/3}),$$

(5.1-25)

where

$$Y = \left(\frac{n_i x^2}{6N_0 D_i t_p}\right)^{3/2}.$$

(5.1-26)

This type of diffusion result is shown in Fig. 5.8 where it is compared to the

FIGURE 5.8 High-density constant surface concentration diffusion profile comparison.

t to

-24) bed

.-25)

L-**26**)

the

erfc distribution. The diffusion edge is much sharper than that predicted by the classical theory. When this type of boron diffusion is performed into an n-type background, a pn junction is formed. The sharpness of the curve allows the location  $x_j$  of the junction to be found by setting  $N(x_j, t_p) = 0$ , i.e., Y = 1. Thus,

$$x_j = 2.45\sqrt{D_i t_p} \sqrt{\frac{N_0}{n_i}}$$

(5.1-27)

allows for an estimate of the diffusion depth.

High-density arsenic (n-type) diffusions are characterized by

$$D = h \left[ D_i^o + D_i^- \left( \frac{n}{n_{ie}} \right) \right], \tag{5.1-28}$$

showing interactions with neutral and single-negative charge-state vacancies. The effective intrinsic carrier density  $n_{ie}$  is introduced to account for bandgap narrowing from the high doping levels. The effective density is computed from

$$n_{ie}^2 = n_i^2 e^{\Delta E_g/kT} > n_i^2 {(5.1-29)}$$

with  $\Delta E_g$  the reduction in the energy gap. Figure 5.9 shows  $n_i$  and  $n_{ie}$  over the standard range of diffusion temperatures.

It is found that the field enhancement factor for As is approximately

**FIGURE 5.9**  $n_i$  and  $n_{ie}$  as functions of temperature.

rison.

h=2. Using this with the assumption that  $(n/n_{te})\gg 1$  reduces the diffusion coefficient to

$$D\simeq 2D_i^-\Big(rac{n}{n_{ie}}\Big).$$

A constant surface concentration diffusion lasting a time  $t_p$  results in a doping profile that is approximated by

$$N(x, t_p) = N_0(1 - 0.87Y - 0.45Y^2),$$

(5.1-31)

with Y the dimensionless variable

$$Y = \sqrt{\frac{n_{ie}x^2}{8N_0D_i^{-}t_p}}. (5.1-32)$$

This type of distribution is also plotted in Fig. 5.8. When As is diffused into a lightly doped p-type sample, the pn junction depth may be calculated by setting  $N(x_j, t_p) = 0$ . Solving the quadratic results in

$$x_j \simeq 1.616 \sqrt{2D_i^- t_p \left(\frac{N_0}{n_{ip}}\right)},$$

(5.1-33)

which provides a good estimate of the diffusion depth.

The diffusive behavior of high-density phosphorus diffusions is quite complicated and is termed *anomalous* as it cannot be explained using the basic theory. The form of the diffusion coefficient depends on the value of the electron concentration with respect to a reference density

$$n_e \simeq 4.65 \times 10^{21} e^{-0.39/kT}$$

(5.1-34)

In regions near the surface where  $n > n_e$ ,

$$D = h \left[ D_i^o + D_i^= \left( \frac{n}{n_{ie}} \right)^2 \right]$$

(5.1-35)

is valid. However, in the deeper regions of the crystal where  $n < n_e$ , it is found that phosphorus has neutral and complex single-negative charge-state interactions. This changes D to what is termed the "tail" value. A detailed discussion of this topic is beyond the scope of the present treatment.

#### **EXAMPLE 5.1-2**

A 2-step phosphorus diffusion is made into a p-type wafer that has an acceptor doping density of  $N_a = 10^{15}$  [cm<sup>-3</sup>]. The diffusion is described by a predeposit for 30 minutes at 900 [°C] followed by a drive-in for 60 minutes at 1100 [°C].

Calculate the depth  $x_i$  of the pn junction formed by this process.

#### Solution

First read  $N_0 = 6 \times 10^{20}$  [cm<sup>-3</sup>] for the solid solubility. Next compute the diffusion coefficients at the two temperatures:

$$D_p = 5.853e^{-3.62/(8.62 \times 10^{-5})(1173)} \simeq 1.66 \times 10^{-15} \text{ [cm}^2/\text{sec]},$$

$$D_d = 5.853e^{-3.62/(8.62 \times 10^{-5})(1373)} \approx 3.15 \times 10^{-13} \text{ [cm}^2/\text{sec]}.$$

Then use eqn. (5.1-19) to find the doping profile:

$$N(x) = \frac{2(6 \times 10^{20})}{\pi} \sqrt{\frac{(1.66 \times 10^{-15})(30)}{(3.15 \times 10^{-13})(60)}} e^{-x^2/4(3.15 \times 10^{-13})(60)(60)}.$$

This gives

L)

2)

у

3)

te ic 1e

4)

15)

is ite

ed

tor

sit

$$N(x) \simeq 1.97 \times 10^{19} e^{-x^2/0.454} [\text{cm}^{-3}],$$

where x is in units of  $[\mu m]$ .

To calculate the junction depth, just look for the point where the donor doping exactly equals the p-type acceptor level  $N_a$ , i.e.,

$$N(x_i) = N_a$$

Solving,

ving,

$$x_j = \sqrt{0.454 \ln \left(\frac{1.97 \times 10^{19}}{10^{15}}\right)} \approx 2.12 \, [\mu \text{m}].$$

#### **EXAMPLE 5.1-3**

A high-density arsenic diffusion is performed at 1000 [°C] for 30 minutes into a lightly doped p-type wafer. Calculate the junction depth  $x_j$ .

#### Solution

First read  $N_0 = 6.5 \times 10^{20} \, [\mathrm{cm}^{-3}]$  and  $n_{ie} = 2 \times 10^{19} \, [\mathrm{cm}^{-3}]$  from the charts. Next use the data in Table 5.3 to calculate

$$D_i^- = 22.9e^{-4.1/(8.62 \times 10^{-5})(1273)} \simeq 1.36 \times 10^{-15} \text{ [cm}^2/\text{sec]}.$$

Equation (5.1-33) then gives

(Palipinianaik Nordiniak binpankiny/en/cay)

$$x_j \approx 1.616 \sqrt{2(1.36 \times 10^{-15})(30)(60) \frac{6.5 \times 10^{20}}{2 \times 10^{19}}},$$

or

$$x_i \approx 0.204 \, [\mu \, \text{m}].$$

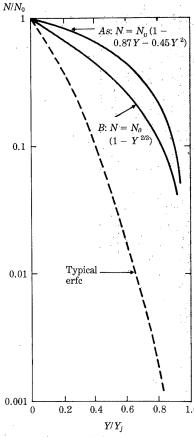

#### 5.1.3 Ion Implantation

Doping by ion implantation has already been mentioned in Section 1.1 for setting MOSFET threshold voltages. An ion implanter is an apparatus that first

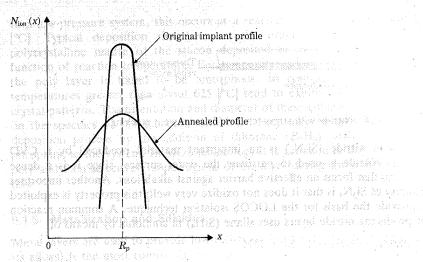

FIGURE 5.10 Gaussian approximation for ion implant profile.

ionizes a dopant source and then accelerates the ions to high energies. The ions form a beam that is focused to scan over the wafer. The dopant ions are literally smashed into the substrate. This results in a doping profile that is approximated to first order by the Gaussian

$$N_{\text{ion}}(x) = \frac{D_I}{\sqrt{2\pi}(\Delta R_p)} e^{-(1/2)[(x-R_p)/\Delta R_p]^2}.$$

(5.1-36)

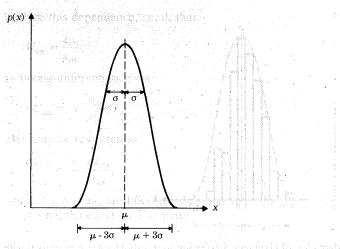

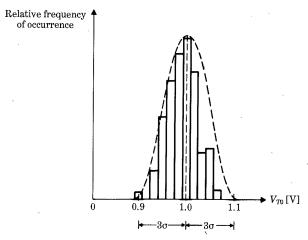

The projected range  $R_p$  represents the average penetration depth of the implanted ions.  $R_p$  increases with increasing energies and is also a function of the dopant mass. The straggle  $(\Delta R_p)$  is the standard deviation associated with the implanted depth and depends on both the incident ion energy and the ion mass relative to the silicon atomic mass. The general shape of the Gaussian approximation is illustrated in Fig. 5.10, where it is compared to a more realistic implant profile.

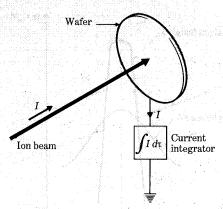

The number of ions implanted into a wafer is specified by using the dose  $D_I$  [cm<sup>-2</sup>] defined as

$$D_I = \int_{-\infty}^{+\infty} N_{\text{ion}}(x) dx = N_p(\Delta R_p) \sqrt{2\pi},$$

(5.1-37)

where  $N_p$  represents the peak concentration (at  $x = R_p$ ) in units of [cm<sup>-3</sup>]. The dose is a carefully controlled quantity and can be measured using the current integrator technique shown in Fig. 5.11. This approach to dosimetry measures the current supplied to the wafer to offset the charge imbalance created by the ion beam. To understand the system, let I represent the beam

FIGURE 5.11 Current integrator dosimetry arrangement.

made at their versions por their versions distribution statement in their current so that

he

are

is

36)

he

of

ith

on

an

re

ose

37)

he

try

ice

am

$$\Delta Q_o = \int_0^{t_i} I(\tau) d\tau \tag{5.1-38}$$

is the total charge delivered to the wafer during an implant time  $t_I$ . The charge on an individual ion can be written as  $(\pm sq)$ , where s=1 or 2 depending on whether the ions are singly or doubly charged. The total number of ions implanted into the wafer is thus given by  $(\Delta Q_o/sq)$ . Denoting the implanted area by A yields the dose expression

$$D_{I} = \frac{1}{sqA} \int_{0}^{q} I(\tau) d\tau,$$

(5.1-39)

This shows that the implant dose can be computed directly from knowledge of the beam current. Dose measurements typically exhibit less than 1% error, which serves to make ion implantation one of the most carefully controlled processes available in silicon wafer fabrication technology.

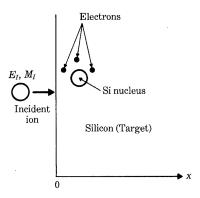

Ion implant profiles result from the statistical nature of the *ion-stopping process*. An incident ion is assumed to have a mass  $M_I$  and energy  $E_I$ , as shown in Fig. 5.12. The ion loses energy to the crystal by collisions with electrons and silicon nuclei. The maximum energy  $E_T$  transferred to a *target* mass  $M_T$  (and hence lost by the ion) is found to be

$$E_T = 4 \frac{M_I M_T}{(M_I + M_T)^2} E_I, {(5.1-40)}$$

where  $M_T$  is either the electron mass m or the nuclear mass  $M_{Si}$ , depending on the event. Coulombic forces also contribute to the ion energy loss. The overall effects are contained in the *stopping power* S [eV/cm] such that

$$S = S_n(E_I) + S_e(E_I)$$

(5.1-41)

FIGURE 5.12 Basic ion-stopping problem.

gives the nuclear and electronic contributions. The ion energy loss is then described by

$$-\frac{dE_I}{dx} = N_{Si}[S_n(E_I) + S_e(E_I)].$$

(5.1-42)

This may be used to find the implanted distance R for an ion by integrating in the form

$$R = \int_0^R dx = -\int_{E_I}^0 \frac{dE_I}{N_{Si}[S_n(E_I) + S_e(E_I)]}.$$

(5.1-43)

The limits on the energy integral correspond to having an incident ion energy  $E_I$  at x=0 and to an ion at rest (E=0) at x=R. The projected range  $R_p$  is the average value of R for all of the ions. The straggle  $\Delta R_p$  represents the statistical variations in the ion penetration distances.

The preceding brief description of the ion-stopping process illustrates two important problems introduced by the implant. First, the collisions with the targets will tend to knock Si atoms out of their equilibrium lattice sites, which causes cracks and defects in the crystal. Second, the ions will be randomly distributed in the lattice and cannot act as substitutional impurities until the implant is activated. This requires that the dopants find positions corresponding to normal lattice sites in the crystal. To solve these two problems, the wafer is subjected to an annealing step that simultaneously repairs the damage and activates the implant.

Thermal annealing consists of heating the wafer for a short time to allow for diffusion of both the dopants and the silicon atoms. Assuming that this is performed at a temperature  $T_A$  for a time  $t_A$ , the thermal anneal has the effect of changing the straggle to

$$(\Delta R_p) \to \sqrt{(\Delta R_p)^2 + 2D_A t_A},\tag{5.1-44}$$

FIGURE 5.13 Effects of implant thermal annealing.

where  $D_A = D(T_A)$  for the implanted species. A typical anneal cycle might be 30 minutes at 1000 [°C]. Using this in eqn. (5.1-36) gives the final implant form

$$N_{\text{ion}}(x) = \frac{D_I}{\sqrt{2\pi}\sqrt{(\Delta R_p)^2 + 2D_A t_A}} \exp\left[-\frac{1}{2}\left(\frac{x - R_p}{\sqrt{(\Delta R_p)^2 + 2D_A t_A}}\right)^2\right].$$

(5.1-45)

As shown by the plots in Fig. 5.13, the thermal anneal causes the dopants to diffuse away from the projected range point  $R_p$ . This spreads the distribution and reduces the peak concentration. A more accurate analysis would account for reflections and out-diffusions at the silicon surface.

Rapid anneal techniques have recently become of interest. This approach involves heating the wafer to high temperatures for very short time periods. An example of a rapid anneal technique is laser annealing, which employs a pulsed high-energy laser beam focused to scan the wafer. This induces localized melting and recrystallization. The primary advantage of this approach is that the annealed profile is very close to the original implant distribution, i.e., the spread described by eqn. (5.1-44) is not found for this type of annealing. The main disadvantage is that the wafer throughput (the number of wafers processed per hour) is greatly reduced.

#### 5.1.4 Chemical Vapor Deposition

Chemical vapor deposition (CVD) is used to obtain layers of various materials in silicon wafer fabrication. As implied by its name, CVD produces layers by using chemical reactions that deposit the desired material onto the substrate. The reaction kinetics involved in this type of process depend on the temperature, the pressure, and the reactant species.

loss is then

(5.1-42)

tegrating in

(5.1-43)

t ion energy range  $R_p$  is presents the

ustrates two ns with the sites, which e randomly ies until the correspondoblems, the the damage

me to allow; that this is as the effect

(5.1-44)

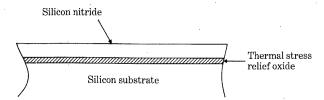

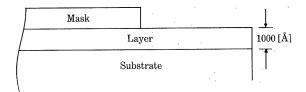

FIGURE 5.14 Nitride with stress-relief oxide to prevent cracking.

Silicon nitride  $(Si_3N_4)$  is an important material produced by a CVD process. Nitride is used to *passivate* the wafer surface, since it is a dense dielectric that forms an effective barrier against alkali ions. Another important property of  $Si_3N_4$  is that it does not oxidize very well; this property is exploited to provide the basis for the LOCOS isolation technique. A common reaction for producing nitride layers uses silane  $(SiH_4)$  in ammonia by means of

$$3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12H_2$$

.

The reaction temperature for this process is on the order of 700 [°C]. One problem that arises is that nitride layers exhibit very high tensile stress, which can lead to cracks when the nitride is deposited directly onto a silicon surface. To avoid this situation, a thin oxide layer is usually grown on a silicon surface prior to the nitride deposition, as shown in Fig. 5.14. This stress relief oxide tends to relieve some of the surface tension and allows for reliable coverage by the nitride.

CVD oxide layers are required whenever a silicon surface is not available for a thermal oxide growth. One of the more common reactions used for this purpose is the pyrolysis of silane in oxygen as described by

$$SiH_4 + 2O_2 \rightarrow SiO_2 + 2H_2O \qquad (600-1000 \ [^{\circ}C]),$$

or

$$SiH_4 + O_2 \rightarrow SiO_2 + 2H_2 \qquad (300-500 \ [^{\circ}C]).$$

The lower-temperature reaction produces hydrogen as a by-product and results in higher-quality films than those obtained using the high-temperature water-producing process. Phosphosilicate glass (PSG) can be deposited by simultaneous pyrolysis of silane and phosphine (PH<sub>3</sub>). Phosphine reacts with oxygen according to

$$2PH_3 + 4O_2 \rightarrow P_2O_5 + 3H_2O$$

.

The P<sub>2</sub>O<sub>5</sub> is then incorporated into the silica during the deposition process. PSG has a lower tensile stress than pure silica, which tends to make PSG more reliable when many thermal cycles are required in the process flow.

Polycrystalline silicon (poly) may be deposited using the direct pyrolysis of silane

$$SiH_4 \rightarrow Si + 2H_2$$

.

In a low-pressure system, this occurs at a reaction temperature of about 600 [°C]. Typical deposition rates are on the order of 200 [Å/min]. The polycrystalline nature of the silicon deposited in this manner is a strong function of reaction temperature. For temperatures less than about 575 [°C], the poly layer is found to be amorphous. In contrast, layers grown at temperatures greater than about 625 [°C] tend to exhibit localized columnar crystal patterns. The orientation and diameter of these columns are dependent on the specifics of the reaction conditions. Poly may be doped during the deposition process by the addition of diborane (B<sub>2</sub>H<sub>6</sub>), arsine (AsH<sub>3</sub>), or phosphine to the system. In MOS technology it is common to deposit intrinsic poly and then selectively dope regions of the layer during the normal process flow his to unitable requires this yield to tryot reach acts exceed to

to are perticularly useful because they emisted and resulting and of

### 5.1.5 Metallization and Silicides

Metal layers are used to provide low-resistance interconnects. Aluminum (and its alloys) is the most commonly used metal for this application, with a room temperature resistivity of about 2.7 [m $\Omega$ -cm]. Gold is also useful for certain applications. Metallic layers of this type are obtained by first melting and then evaporating the metal in a closed vacuum system. The solid samples are heated using standard resistance wiring, electron beams, or rf-induction heating techniques. Placing the wafers into the evaporant flux allows for a complete and (almost) uniform coverage of the surface. Condensation of the metal onto the wafer is attained by keeping the temperature of the wafer lower than that

of the evaporant.

Refractory (high-temperature) metals are finding increased use in VLSI structures. The main advantage of using a refractory metal is that lowresistance patterned interconnect levels can be formed at any time in the chip process flow. The high melting point associated with these metals keeps the pattern intact even if the wafer is subjected to additional heat treatments. (Al has a low melting point—660 [°C]—and can be used only after all the high-temperature cycles are completed.) This property allows for multiplelevel interconnects to be created, which aids in the layout of complex chips. Refractory metals of current interest include titanium (Ti), platinum (Pt), molybdenum (Mo), and tungsten (W). These may be evaporated using electron-beam heating or may be sputtered onto the wafer. In sputtering, an inert gas such as Ar is ionized and used to bombard an electrode that is coated with the desired substance. The collisions knock the atoms off the electrode. creating a particle flux directed toward the wafer.

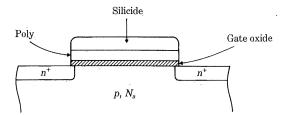

Silicides are compounds formed using silicon and a refractory metal. These have been introduced for the same reason as the elemental refractory metals, i.e., to create high-conductivity paths that can withstand high-temperature processes without melting. Some of the better-studied silicides are TiSi2, PtSi2, TaSi, and WSi<sub>2</sub>. In this group, titanium disilicide (TiSi<sub>2</sub>) has shown the lowest resistivity, with about  $\rho = 2.5 \, [\text{m}\Omega\text{-cm}]$  for cosputtered samples.

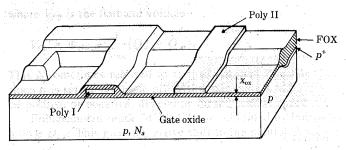

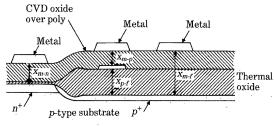

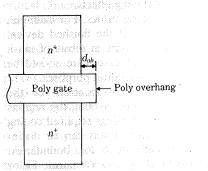

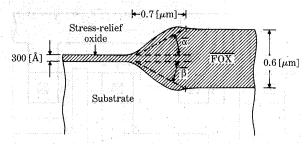

FIGURE 5.15 A polycide gate MOSFET.

Polycides are simply combinations of polysilicon and silicides. A typical polycide consists of a lower level of poly with an upper coating of silicide. These are particularly useful because they exhibit the best features of both polysilicon and silicides, including good stability, adherence, and coverage (from the poly) and a high conductivity path (from the silicide). A MOSFET fabricated with a polycide gate is shown in Fig. 5.15. It should be noted that the threshold voltage of this device is dependent on the specifics of the layering used for the gate. If a thick poly layer (>1500 [Å]) is used, then the gate threshold voltage will be the same as if only poly were used. However, if the poly layer is thin, a shift in the gate-substrate work function  $\Phi_{GS}$  will occur because of the silicide. This must be accounted for in the threshold voltage adjustment implant.

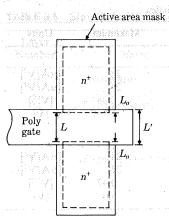

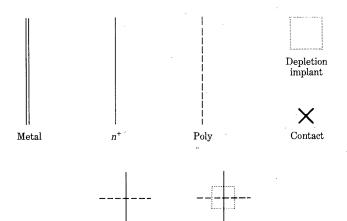

#### 5.2 Lithography

An integrated circuit may be viewed as a set of patterned layers. Each layer is a material with specific electrical properties. For example,  $n^+$  regions, silicon dioxide, and aluminum form layers of doped semiconductor, insulator, and metal, respectively. In general, a layer must be patterned before the next layer of material is applied. A device such as a MOSFET is a subset of the patterned chip layers. Device characteristics result from the 3-dimensional structure created by both the layering order and the geometric pattern on each layer.

The process used to transfer a pattern to a layer of an integrated circuit is called *lithography*. Since each layer has its own distinct patterning requirements, the lithographic sequence must be repeated for every layer used to build the chip. The main requirements for a lithographic process are (a) a mask or reticle that is a "master copy" of the desired pattern; (b) an exposure or printing system that allows the transfer of the pattern to the wafer; and (c) a resist material that coats the wafer and is itself patterned by the printing system as the first step in creating the patterned layer.

#### 5.2.1 Basic Pattern Transfer

The easiest way to illustrate the important aspects of a lithographic process is through a specific example. The one chosen here is basic optical lithography

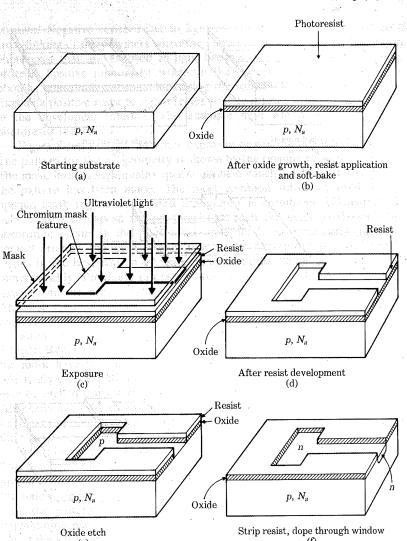

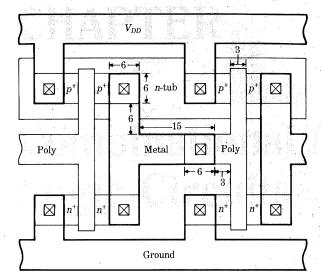

FIGURE 5.16 Example process for optical lithography.

with contact/proximity printing. The process will be discussed in conjunction with the wafer fabrication steps in Fig. 5.16. This set of drawings will show how a patterned  $n^+$  region is created in a p-type substrate such that the  $n^+$  well is accessed by a metal interconnect layer.

The starting point for the example is the section of p-type wafer with constant doping  $N_a$  shown in Fig. 5.16(a). The wafer is first subjected to a

Figure 5.16 (contd.)

thermal oxide growth and is then coated with a layer of *photoresist*. At this point, the wafer has the layering of Fig. 5.16(b). Photoresist is a light-sensitive organic polymer (generally a type of plastic) that is initially in a liquid state when it is applied to the wafer. The wafer is spun to allow for an even coating of resist, and it is then subjected to a *soft-bake* heating step that solidifies the resist enough for handling. Photoresist is available in two types, negative and

positive. Negative resists react to light by absorbing photons, which creates cross-linking of the polymers when the resist is developed. Regions of negative photoresist that are exposed to light become hardened after the developing process. Positive photoresist works in the opposite manner, with absorbed photons contributing toward increasing the solubility of the resist base resin. Exposing positive resist to light creates soluble regions that are dissolved away in the developing solution. The example here will assume that negative photoresist is used.

Figure 5.16(c) shows the actual exposure step in the first lithographic cycle. The pattern for the  $n^+$  geometry is shown by the opaque regions on the mask. The mask itself is high-quality quartz glass on which a 1-to-1 (or  $1 \times$ ) copy of the pattern has been made. The most common substance used to create opaque mask regions for optical lithography is chromium. Ultraviolet (UV) light is used to expose the photoresist through the mask as shown. Photon absorption occurs in the photoresist underneath the clear mask regions. In contact printing, the mask actually touches the surface of the resist layer. This results in the best pattern transfer resolution but tends to wear out the mask rather quickly. Proximity printing solves this problem by maintaining a small spacing (on the order of 20-40 [ $\mu$ m]) between the mask and wafer surface. Although the mask does not degrade as rapidly, the resolution of the image is reduced from that obtained by contact printing due to diffraction.

After exposure, the resist is developed to obtain the patterning as in Fig. 5.16(d). Regions of negative resist that were exposed to the UV light through the mask have become hardened. This allows for the silicon dioxide to be selectively etched into the pattern, illustrated by Fig. 5.16(e). The silica layer may be etched using a wet chemical bath of buffered hydrofluoric (HF) acid. Alternatively, a dry etch process based on a gaseous plasma may be used. It is important to note that this step has opened a patterned oxide window down to the bare p-type silicon substrate.

The next step in the processing is to strip the photoresist off the wafer. This is required because resist generally has a low melting temperature, which prohibits leaving it on during high-temperature cycles. The pattern provided by the oxide window is then used to selectively dope the wafer with donors to form the patterned n-type well in the p-type substrate. Either diffusion or implantation may be used since the oxide acts as a mask to keep the dopants out of the silicon regardless of the doping technique employed. The oxide itself becomes doped during this process but is assumed to be thick enough to keep the dopants from reaching the silicon surface. The resulting n-type well that is created in this step is shown in Fig. 5.16(f).

After the initial doping is completed, the wafer is heated for either a drive-in (for a diffusion) or an anneal (with an ion implant). The atmosphere is assumed to be nitrogen and oxygen, so an oxide layer is grown over the entire surface. This is drawn in Fig. 5.16(g). The oxide is introduced at this point as an insulator between the semiconductor and the metal layer.

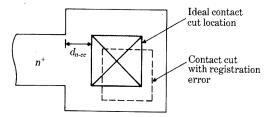

Access to the  $n^+$  well is obtained by another lithography step, which

It this nsitive I state oating es the re and

results in the oxide contact window shown in Fig. 5.16(h). Aluminum is then evaporated over the entire surface of the wafer, and the desired metal pattern is formed on the resist layer with the next lithography sequence. The wafer at this point in the processing appears as illustrated by Fig. 5.16(i). Etching the aluminum leaves the patterned layers shown in Fig. 5.16(j). The last step in this example is to strip the resist, which leaves the final structure shown in Fig. 5.16(k).

This example demonstrates that the masking process is repeated for every layer that needs patterning. In particular, masks were used to pattern the  $n^+$  doping, the oxide contact cut, and the metal geometry. Owing to the importance of obtaining patterned layers that are accurate images of the mask, good lithography is crucial for making integrated circuits. Many variations in the lithography sequence are possible. Although space prohibits a detailed discussion of the subject, some of the possibilities are discussed.

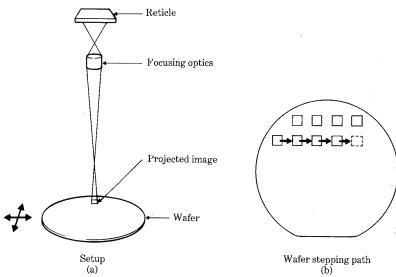

The first to be examined is an exposure technique known as projection printing. In this approach, the mask is kept some distance away from the wafer, and the pattern transfer is effected by optically projecting the image through a lens system. One example of this type of printing system is the wafer stepper shown in Fig. 5.17(a). The layer patterning is contained on the reticle, which is typically a  $5\times$  or  $10\times$  enlargement of a single die area. Pattern transfer is accomplished by optically reducing the image to the correct dimensions while simultaneously focusing it onto a specified region of the wafer. After the portion of the wafer is exposed, the system "steps" the image

FIGURE 5.17 Wafer stepper projection printing system.

s then attern ifer at ig the tep in n Fig.

he n<sup>+</sup>

the of the

Many

bits a

ection

n the image wafer eticle, attern orrect of the image

(2.87) niceç o ser umair. sigrar b cec

nupro Kilos Hvitto Cultur to the next die site, as schematically illustrated by Fig. 5.17(b). This stepping process is continued until the wafer is completely exposed.

The direct wafer stepping technique is useful because it allows for wafer surface variations due to warping. This is particularly important as wafer diameters increase. The use of a 5× or 10× reticle pattern allows for larger tolerances in the pattern definition, making it more accurate than that possible with a 1× system. Of course, diffraction effects compensate for some of this because of the nature of the projection system. Another advantage of this technique is that the pattern transfer is not greatly affected by dust particles because the rectile is shielded with a sheath of clear nitrocellulose (or similar material) called a *pellicle*. The system is arranged so that any dust accumulation is restricted to the pellicle surface. Image control is maintained by ensuring that the distance between the reticle and the pellicle is sufficient to keep the dust particles out of the focusing range of the lens system. Consequently, the dust particles do not image onto the wafer. The main disadvantage of the wafer stepper is that the wafer throughput is low compared with that of a single-exposure process.

Negative photoresists are based on light-sensitive organic polymeric resins to which photosensitizing agents have been added to aid in the photon absorption process. Typical negative-working resins are polyvinyl cinnamate and cyclized polyisoprene. The resin itself must have the basic properties that it can adhere to the desired surface and can be developed into a hardened film that is resistant to the basic layer etchants. The specific sensitizer used to create a working negative resist depends on the resin system since the two must be compatible. Negative photoresist can be made very sensitive to light, allowing for rapid exposure. This makes negative photoresists useful for high wafer throughput. However, they have the undesirable property of swelling during the development process because the developing agent is absorbed by the polymer. Owing to the distortion introduced by the swelling, negative photoresists tend to be limited to minimum linewidths on the order of 2  $[\mu m]$ .

Positive photoresists do not absorb the developing solution and are therefore the prime candidates for fine-line optical VLSI lithography. The polymeric chemistry associated with positive photoresists is quite different from that described above for negative-working resists. Resins used in positive photoresists are not generally sensitive to light but are chosen for their basic characteristics, such as solubility and adherence. The exposure properties of positive resists arise from the reaction of the added light sensitizers with the base resin chains. Positive photoresists tend to require longer exposure times than those needed for negative resists. Consequently, improved resolution capabilities are gained at the expense of reduced wafer throughput.

X-ray lithography is similar to the optical UV technique described above except that X-rays are used as the exposure source. This approach is of interest because the shorter wavelengths of X-rays allow for finer resolution in the pattern transfer process while still maintaining high wafer throughput rates.

The most difficult aspect of X-ray lithography is mask making. The requirements are somewhat different from those used in optical lithography in that the opaque regions of an X-ray mask are made to absorb (rather than reflect) the radiation. Gold is typically used as an absorber for this type of mask. The walls for the gold must be maintained perpendicular to the mask surface to ensure good resolution.

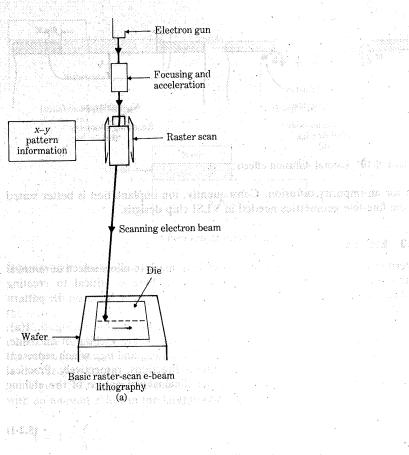

Electron-beam lithography offers the highest-resolution pattern formation by directly writing onto the wafer. The electron beam is columnated to form the desired spot size, and the beam is then used to scan the wafer surface, as shown in Fig. 5.18(a). The pattern information is contained in the e-beam scan control system, which selectively turns the beam on and off depending on the wafer coordinates of the beam as it scans the surface. Since beam diameters as small as  $0.01~[\mu m]$  are possible, direct e-beam writing allows for extremely fine-line patterning. The major drawback of this technique is that the wafer throughput is low because of the time required to scan the wafer at a rate slow enough to expose the resist. The throughput can be increased by enlarging the spot size, but this obviously reduces the resolution. A typical production line system providing a minimum linewidth of  $2~[\mu m]$  might use an e-beam as large as  $0.5~[\mu m]$ . Other problems are that the circular beam shape makes it difficult to form right-angle (90°) turns in the pattern and that electron backscattering, illustrated in Fig. 5.18(b), tends to widen the actual exposure track.

#### 5.2.2 Lateral Doping Effects

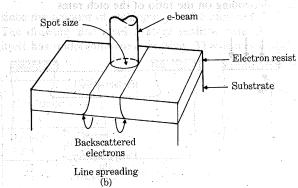

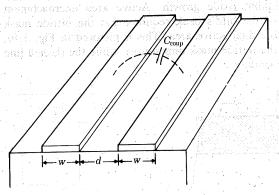

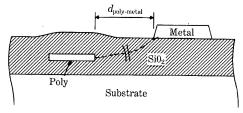

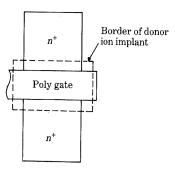

Doping through an oxide window results in a doped region that is larger than the window itself. This occurs because of *lateral doping* effects in which there is a "spreading" of the dopants outward from the window edge in directions parallel to the silicon surface. Both diffused and implanted patterns exhibit lateral spreading. The MOSFET overlap capacitances  $C_{ols}$  and  $C_{old}$  discussed in Section 4.6, are direct consequences of this phenomenon.

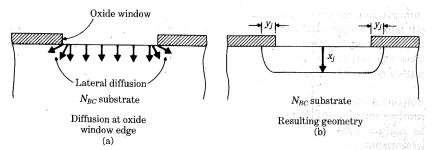

1 \* The logicality descent description

Lateral diffusion is illustrated in Fig. 5.19(a). It is seen that the oxide window serves as a mask for the patterning but that dopants at the edge of the oxide window diffuse outward. This results in the diffused well geometry shown in Fig. 5.19(b). The amount of lateral spreading is usually characterized by the lateral junction distance  $y_j$ . This can be quite large, with  $(y_j/x_j) = 0.8$  a typical order of magnitude for a deep 2-step Gaussian profile. The actual value of  $y_j$  is dependent on the background doping  $N_{BC}$  of the substrate and the specifics of the diffusion cycle.

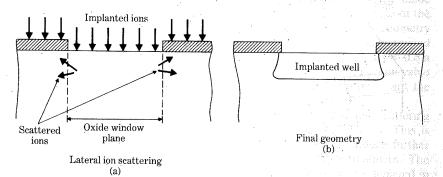

Lateral doping in ion implantation initially results from ion scattering outside the oxide "window plane" during the ion-stopping process. This is shown in Fig. 5.20(a). Thermal annealing of the implant will induce further spreading because of lateral diffusive motion during the heat treatment. The final width of the implant is thus larger than the oxide window, as depicted in Fig. 5.20(b). Lateral doping from an ion implant is generally much less than

FIGURE 5.18 Electron-beam lithography.

FIGURE 5.19 Lateral diffusion effects.

that for an impurity diffusion. Consequently, ion implantation is better suited for the fine-line geometries needed in VLSI chip designs.

## 5.2.3 Etching

Pattern transfer uses a resist layer as a etchant mask to allow selective removal of the underlying material. The process of etching is critical to creating fine-line features on integrated circuits as it establishes the limits on the pattern resolution.

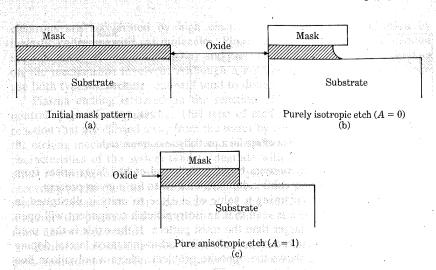

The basic problem in etching is illustrated by the example in Fig. 5.21(a), where a mask (resist) layer has been patterned to allow etching of an oxide. The etch process is characterized by the etch rates  $v_{\rm ver}$  and  $v_{\rm lat}$ , which represent the rate of etching in the vertical and lateral directions, respectively. Practical units for etch rates are [Å/min]. The two-dimensional nature of the etching process is specified by the degree of anisotropy

$$A = 1 - \frac{v_{\text{lat}}}{v_{\text{ver}}}, \tag{5.2-1}$$

where A varies from 0 to 1 depending on the ratio of the etch rates.

FIGURE 5.20 Lateral doping effects in an ion implantation.

FIGURE 5.21 Basic etching problem.

Purely isotropic etching occurs when  $v_{\rm lat} = v_{\rm ver}$ , i.e., A = 0. This results in the structure shown in Fig. 5.21(b), where the oxide etch undercuts the resist mask. A totally anisotropic etch is defined by  $v_{\rm lat} = 0$ , giving A = 1. In this case, only vertical etching is present so that the oxide wall is perpendicular to the substrate surface as shown in Fig. 5.21(c). Anisotropic etching thus results in the ideal structure.

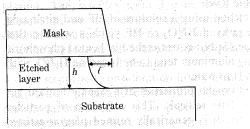

Figure 5.22 shows the general case where a film of thickness h is etched with an amount  $\ell$  lost in the lateral undercut. This is described by

$$A=1$$

,  $h$  , which is the first three particles of  $h$  . (5.2-2)

since the amount of etching is just the etch rate multiplied by the etch time  $t_e$ . The drawing also gives a more realistic case in which the masking material itself has undergone some etching. This leaves a slight tilt in the mask edge.

FIGURE 5.22 Geometry for a partially anisotropic etch.

FIGURE 5.23 Window and line effects in a partially anisotropic etch.

The difference in etched contours for the mask and etched layer arises from the fact that two materials exhibit different etch rates for a given process.

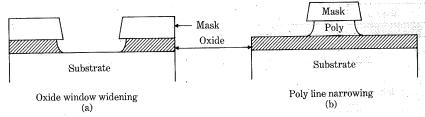

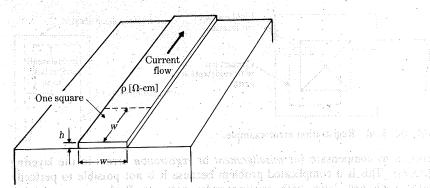

The importance of achieving a value of A close to unity is illustrated in Fig. 5.23. In Fig. 5.23(a) it is seen that an isotropic etch component will open an oxide window that is larger than the resist pattern. If the oxide is then used as a dopant mask, the curved oxide walls will lead to increased lateral doping spreads. Figure 5.23(b) shows the opposite problem, where a polysilicon line feature is defined by a resist pattern. The isotropic portion of the polysetch from  $v_{\text{lat}}$  gives a linewidth smaller than the resist pattern as shown by the cantilever resist structure. This decreases the cross-sectional area of the current flow, which increases the sheet resistance of the line. In addition, the undercutting requires that the mask pattern be larger than the final chip feature.

Etching techniques are generally classified as being either wet or dry. Wet etching, as implied by its name, employs aqueous solutions of acids (or caustics) to etch the desired layers. The wafers are immersed directly in the solution, which allows the chemical reaction to take place over the exposed surface regions. Wet etches tend to be isotropic when used on amorphous or polycrystalline material. This then limits the use of wet etching to lithographic features larger than about 3  $[\mu m]$ .

Silicon dioxide may be wet-etched in a buffered hydrofluoric acid solution containing HF, NH<sub>4</sub>F, and H<sub>2</sub>O. The HF readily attacks the SiO<sub>2</sub> layer but does not etch bare silicon. This property of *selectivity* makes it useful for etching oxide windows down to a silicon substrate since the vertical etch rate goes to zero when the substrate is reached. The HF solution is buffered to slow down the etch rate to a controllable level.

Phosphosilicate glass can be etched using a solution of HF and nitric acid (HNO<sub>3</sub>) in water. Increasing the ratio of HNO<sub>3</sub> to HF yields a solution that will etch polysilicon. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) is wet-etched in heated phosphoric acid (H<sub>3</sub>PO<sub>4</sub>). Solutions for etching aluminum tend to be based on H<sub>3</sub>PO<sub>4</sub> with HNO<sub>3</sub> and CH<sub>3</sub>COOH (acetic acid) in water.

Dry etching systems are based on the properties of a weakly ionized gas consisting of electrons, ions, and free radicals. This collection of particles constitutes a plasma, so this approach is generically termed plasma-assisted etching. The plasma is usually produced by an rf glow discharge in which

electrons are accelerated by high electric fields and induce ionization by inelastic collisions with gas molecules. Plasma-assisted etching can be divided into two categories, plasma etching and reactive ion etching (RIE), depending on the mechanisms involved. Although a realistic dry etch arrangement will use both types of etching, one will tend to dominate the overall process.

Plasma etching is based on the reaction of the surface material with a neutral species in the plasma. This type of etch produces by-products of the reaction that are carried away from the wafer by controlling the gas flow. Since the etching mechanism requires the neutral species in the reaction, the etching characteristics of the system tend to degrade with increased wafer area. This effect is termed loading and requires an adjustment of the system parameters according to the number of wafers being processed. Straight plasma etches are isotropic because of the dependence of the surface reaction. In practice, however, the presence of directed ions in the plasma can enhance  $v_{\rm ver}$  to give a more anisotropic profile.

Reactive ion etching uses a directed ion flux that etches the material by both momentum transfer (i.e., sputtering or ion milling) and a reactive etch mechanism. RIE systems are generally designed so that the ions impact the wafer vertically to ensure that  $v_{\rm ver} \gg v_{\rm lat}$ . This directionality allows for a minimization of the lateral etching, so that highly anisotropic etch contours are possible. RIE is thus a good choice for fine-line VLSI structures.

The gases used to create the plasma determine both the etch rates and profiles for a given layer. Polysilicon and silicon compounds (SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, PSG, etc.) can be etched using carbon tetrafluoride (CF<sub>4</sub>). The basic plasma forming reaction is  $CF_4 + e^- \rightarrow CF_3^+ + F^* + 2e^-,$

$$CF_4 + e^- \rightarrow CF_3^+ + F^* + 2e^-$$

which shows how an electron (e<sup>-</sup>) impacts with a CF<sub>4</sub> molecule to produce the CF<sub>3</sub><sup>+</sup> ion and the F\* free radical. The F\* radical is the active species for reactively etching silicon by forming SiF4, which is stable and can be removed from the wafer surface. A similar situation holds for silicon nitride etching. Silicon dioxide relies on the CF3+ ion for intermediate reduction to SiO, which then reacts to form SiF<sub>4</sub>. It is found that addition of oxygen (and other gases) can greatly affect the etching characteristics of the plasma for certain materials.

The refractory metals Mo, W, Ti, and Ta can be etched using a CF<sub>4</sub> plasma. The silicides formed with these metals also exhibit this property. Aluminum, on the other hand, cannot be etched with CF4. Rather, a chlorine-containing gas such as carbon tetrachloride (CCl<sub>4</sub>) is used to induce a reaction that forms AlCl<sub>3</sub> as a stable by-product. Polysilicon can also be etched using a chlorine-based plasma.

An important consideration in dry etching centers around the selectivity of the plasma. As mentioned above, selectivity refers to the ability to etch only certain materials in a given process. This is particularly crucial in etching multilayer patterns since each layer reacts differently to the etch mechanisms. In wet etching, selectivity is attained by using acids that attack only a single

from

ed in open used oping 1 line etch y the rrent , the chip

. Wet s (or n the posed us or aphic

ution r but il for 1 rate slow

: acid 1 that horic , with

d gas rticles sisted which

#### 262 MOS Integrated Circuit Fabrication

Substrate

Partial anisotropic etch with different lateral etch rates

FIGURE 5.24 Etch selectivity problem for a polycide MOSFET gate.

layer of material at a time. This can be partially achieved in a purely reactive dry etch by varying the gas composition to preferentially etch a given layer at a faster rate. Note, however, that a plasma made with CF<sub>4</sub> can potentially etch any silicon-containing layer, so that high selectivity is difficult to obtain. Another problem in dry etching is that ion bombardment of the wafer sputters off material at a rate that is relatively insensitive to the composition. Consequently, there are no built-in mechanisms to stop the process after the layer is etched. This must be controlled externally by monitoring the etching time to prevent over-etching the wafer.

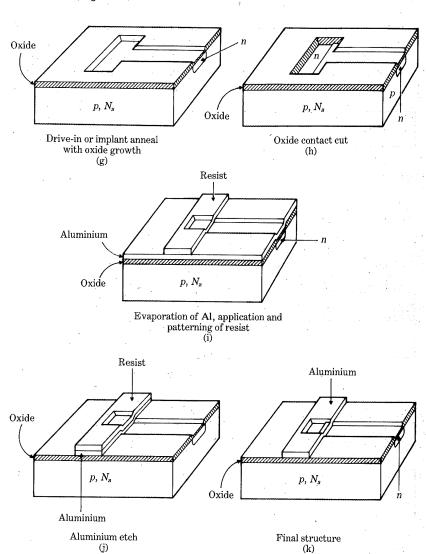

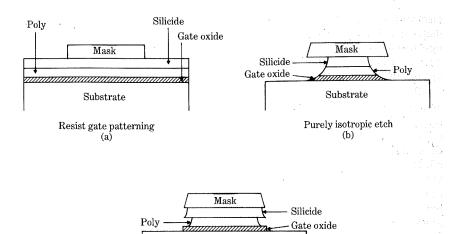

An interesting example of the multilayer dry etching problem is provided by the polycide-gate MOSFET in Fig. 5.15 of the previous section. Patterning of the gate requires etching through the silicide, the polysilicon, and the gate oxide. Figure 5.24(a) shows the initial layering with the gate etch mask. If a purely isotropic plasma etch is used, the gate will have the structure shown in Fig. 5.24(b). Although this gives a smooth transition at the layer interfaces, there is significant undercutting of the silicide underneath the mask. This results in increased sheet resistances, which act against the basic reason for introducing the silicide layer in the first place. Figure 5.24(c) shows the structure obtained using an RIE in which the lateral etch rate for the poly layer is greater than that for the silicide. This produces an undesirable silicide cantilever in the MOSFET. Problems of this type illustrate the importance of characterizing the etching process used in the wafer fabrication.

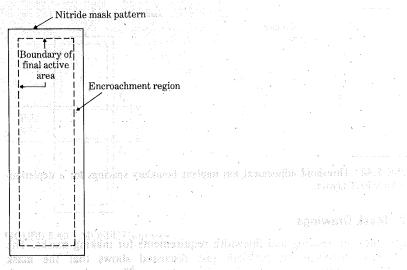

## 5.3 Isolation Techniques

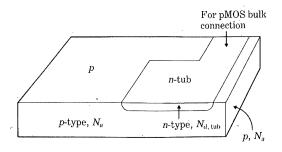

Isolation in an integrated circuit deals with the need to electrically isolate neighboring devices on the chip. MOSFETs are fabricated on planar portions of the silicon known as active areas. Active areas are surrounded by field regions, which are included for the isolation. Interconnects are patterned conducting layers for "wiring" the devices together according to the circuit design. Isolation sets the characteristics of the field regions to prevent unwanted conduction paths between active areas. This, of course, is required to ensure that the circuit operates properly.

A MOS technology is partially self-isolating in that the MOSFETs have pn junctions that are usually reverse-biased. For example, an n-channel MOSFET consists of  $n^+$  drain and source wells in a p-type substrate. Since only leakage current flows across the reverse biased junctions, some isolation is automatically provided when the transistors are placed into the chip environment.

The main complicating factor in MOS isolation is that unwanted inversion layers may form under the interconnect lines that are patterned in the field regions. If the field silicon surface becomes inverted, a conduction path may be established between MOSFETs in adjacent active areas. Isolation techniques are usually directed toward dealing with this problem.

The basic requirements for an isolation scheme are that (a) the technique should eliminate the possibility of forming unwanted field inversion layers and (b) the initial active area regions must be flat for fabricating the MOSFETs. Another desirable feature is that the overall chip process yield planar surface topologies after each major step. There are different approaches used for isolation in MOS integrated circuits. Three are presented below.

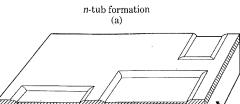

#### 5.3.1 Etched Field Oxide Isolation

surpe déphi with dithata diffu

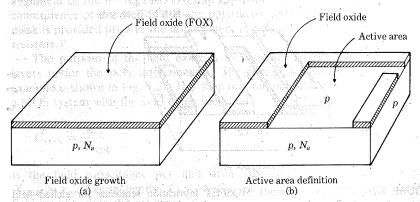

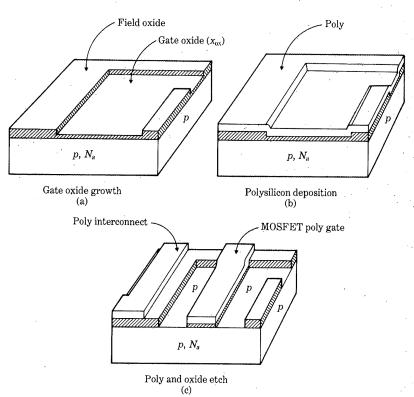

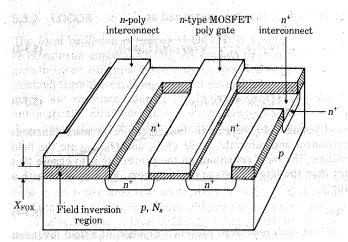

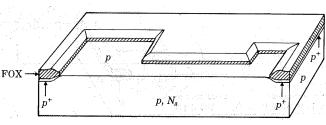

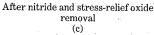

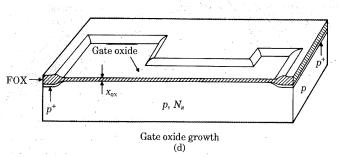

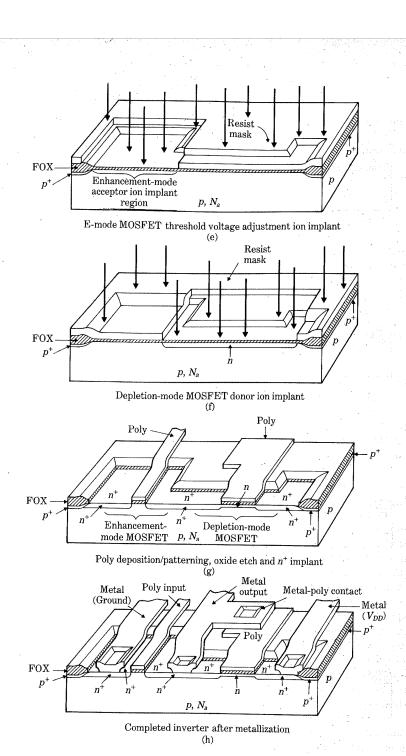

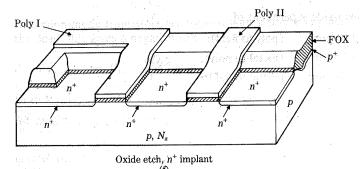

This basic MOS isolation approach uses the sequence shown in Fig. 5.25 to define and isolate active areas. The starting point is a lightly doped p-type

FIGURE 5.25 Etched field oxide isolation.