## **CERTIFICATION**

Items translated: Japanese Unexamined Patent Application Bulletin No. JP-2001-053184-A

This is to certify that the above-stated items were translated by Martin Cross from Japanese into English, and that they represent accurate and faithful renditions of the original text to the best of my knowledge and belief.

By:

November 27, 2017

(19) Japanese Patent Office (JP)

# (12) PUBLICATION OF UNEXAMINED PATENT APPLICATION (A)

(11) Patent Application Publication No.: 2001-53184 (P2001-53184A)

(43) Date of Publication: February 23, 2001

| (51) <b>Int. CI.</b> <sup>7</sup><br>H01L 23/12                        | Identification Code<br>Examina | FI<br>H01L 23/12<br>ation Request: not yet r | Theme Code (Ref.) L made Number of Claims: 12 OL (Total 10 pages)                   |

|------------------------------------------------------------------------|--------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|

| <ul><li>(21) Application No.:</li><li>(22) Application Date:</li></ul> | 11-224490<br>August 6, 1999    | (71) Applicant:                              | 000003193<br>Toppan Printing Co., Ltd.<br>1-5-1 Taitou, Taitou-ku, Tokyo-to         |

|                                                                        |                                | (72) Inventor:                               | FURUYA, Akihiko<br>Toppan Printing Co., Ltd.<br>1-5-1 Taitou, Taitou-ku, Tokyo-to   |

|                                                                        |                                | (72) Inventor:                               | KITAMURA, Satoshi<br>Toppan Printing Co., Ltd.<br>1-5-1 Taitou, Taitou-ku, Tokyo-to |

|                                                                        |                                | (72) Inventor:                               | FUKUYOSHI, Kenzo<br>Toppan Printing Co., Ltd.<br>1-5-1 Taitou, Taitou-ku, Tokyo-to  |

#### (54) [Title of the Invention] Semiconductor Device and Method of Manufacturing Same

#### (57) [Abstract]

[Problem to Be Solved] Provided is a highly reliable chipsize package type semiconductor device in which the connection strength between a metal post and a wiring pattern is high and the reliability of the electrical connection with the outside is high, and in which the wiring pattern will not break even if gas is generated in the insulating layer, and a method for manufacturing the same.

[Means for Solving the Problem] A semiconductor device characterized in that a first insulating layer having substantially the same shape as a passivation film is formed on the passivation film, which has been formed on a semiconductor element, with an electrode, which has been formed on the semiconductor element, exposed; a wiring pattern, which is connected with the electrode of the semiconductor element, is formed on the first insulating layer; a metal post for external connection is formed on the wiring pattern; a second insulating layer, which is in close contact with the wiring pattern, is formed in a manner so as to cover a side face of the metal post excluding the tip of the metal post; and after sealing resin has been [applied] in a manner so as to expose the tip of the metal post, an external connection terminal is provided at the tip of the metal post.

#### [Claims]

[Claim 1] A semiconductor device characterized in that a first insulating layer having substantially the same shape as a passivation film is formed on the passivation film, which has been formed on a semiconductor element, with an electrode, which has been formed on the semiconductor element, exposed; a wiring pattern, which is connected with the electrode of the semiconductor element, is formed on the first insulating layer; a metal post for external connection is formed on the wiring pattern; a second insulating layer, which is in close contact with the wiring pattern, is formed in a manner so as to cover a side face of the metal post excluding a tip surface of the metal post; resin sealing is performed with sealing resin in a manner so as to expose the tip surface of the metal post; and an external connection terminal is provided at the tip surface of the metal post.

**[Claim 2]** The semiconductor device according to claim 1, characterized in that the height of the surface of the second insulating layer excluding the region of the side face of the metal post is established at a position lower than the tip surface of the metal post.

[Claim 3] The semiconductor device according to claim 1 or 2, characterized in that the external connection terminal is configured with an electroconductive material provided on a surface of a support having a hollow part which is opened to the outside.

**[Claim 4]** The semiconductor device according to claim 3, characterized in that the support has a cylindrical shape having a hollow part opened to the outside.

**[Claim 5]** The semiconductor device according to claim 1 or 2, characterized in that the external connection terminal is configured with an electroconductive material is provided on a surface of a cylindrical support having no hollow part.

[Claim 6] The semiconductor device according to claim 3, 4 or 5, characterized in that an engineering plastic comprising a resin selected from polyimide, polyamide imide, polyether imide, thermoplastic polyimide, polyamide, polyacetal, polybutylene terephthalate, polyethylene terephthalate, polystyrene, syndiotactic polystyrene, polyphenylene sulfide, polyether ketone, liquid crystal polymer, polyether nitrile, fluororesin, polycarbonate, modified polyphenylene ether, polysulfone, polyethersulfone, and polyarylate is used for the support comprised by the external connection terminal.

**[Claim 7]** The semiconductor device according to claim 3, 4, 5 or 6, characterized in that the electroconductive material comprised by the external connection terminal is selected from among the following (1) to (3):

- (1) a dispersion of graphite, carbon or metal fine particles;

- (2) gold, silver, copper, aluminum or nickel alone, or an alloy containing two or more of said metals; and

- (3) a low melting point alloy having tin or lead as a principal component.

[Claim 8] A method for manufacturing the semiconductor device according to claim 1, 2, 3, 4, 5, 6 or 7, characterized by having, at least: a step of forming a first insulating layer on a passivation film, which has been formed on a semiconductor element in such a manner as to expose an electrode formed on the semiconductor element, in such a manner as to expose the electrode; a step of forming a wiring pattern, which is connected with the electrode, on the first insulating layer; a step of forming a metal post for external connection at a predetermined height. in a predetermined position on the wiring pattern; a step of forming a second insulating layer in which, after applying an insulating resin in a manner so as to include the metal post, the insulating resin is removed from the region of the tip surface of the metal post that connects with the outside; a step of performing resin sealing with sealing resin in a manner so as to expose the tip surface of the metal post; and a step of providing an external connection terminal at the tip surface of the metal post.

**[Claim 9]** The method for manufacturing a semiconductor device according to claim 8, characterized in that photolithography is used as a means for removing the insulating resin from the region of tip surface of the metal post that connects with the outside.

**[Claim 10]** The method for manufacturing a semiconductor device according to claim 8 or 9, characterized in that spin coating is used as a means for applying an insulating resin serving as the second insulating layer.

[Claim 11] The method for manufacturing a semiconductor device according to claim 8, 9 or 10, characterized in that, after the semiconductor element on which the second insulating layer has been formed has been affixed to a cooling heatsink, resin sealing is performed on the semiconductor element in a manner so as to expose the tip surface of the metal post and the face of the cooling heatsink on the side opposite to the face to which the semiconductor element was affixed, whereafter, the external connection terminal is mounted on the tip surface of the metal post.

**[Claim 12]** The method for manufacturing a semiconductor device according to claim 11 characterized in that, after batch forming a plurality of laid-out semiconductor elements, up to the formation of the second insulating layer, these are separated into individual semiconductor elements by dicing, and subsequently affixed to cooling heatsinks.

# [Detailed Description of the Invention] [0001]

**[Technical Field of the Invention]** The present invention relates to a semiconductor devices, which are known as a chip size packages (CSPs), in which a wiring layer is formed on a semiconductor element, and to a method for manufacturing the same.

#### [0002]

[Prior Art] In recent years, with miniaturization of electronic devices, semiconductor devices that are incorporated (mounted) in electronic devices are being mounted at high densities, and in conjunction with this, there is a demand for semiconductor devices to be made even smaller. Chip size packages (hereinafter, referred to as CSPs), BGAs (ball grid arrays) and the like have been proposed as technologies that respond to this demand. CSPs can be made substantially the same size as a semiconductor element (IC chip), and can be said to be an effective means for miniaturizing a semiconductor device. Various CSP structures and formats have been proposed, but a general format for a CSP will be described hereafter based on a drawing schematically illustrating the structure of a CSP.

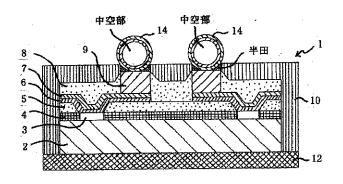

**[0003]** FIG. 6 is a cross-sectional explanatory view, schematically illustrating an example of a conventional semiconductor device 61 (CSP).

**[0004]** As shown in FIG. 6, a passivation film 64 is formed on a semiconductor element 62, on which electrodes 63 (connection pads) made of aluminum or the like have been

formed, in a manner so as to expose the electrodes 63. Next, a first insulating layer 65 made of an insulating resin or the like is formed on the passivation film 64 in a manner so as to expose the electrodes 63. Furthermore, a wiring pattern 67 (wiring layer), which is connected to the electrodes 63, is formed on the first insulating layer 65, and metal posts 69 made of copper or the like are provided on the wiring pattern 67. Note that, in the example in FIG. 6, a metal barrier layer 66 is formed below the wiring pattern 67. Next, a second insulating layer 68 is formed above the wiring pattern 67 and the first insulating layer 65, in a manner so as to expose the metal posts 69. Furthermore, resin sealing is performed with a sealing resin 70 in a manner so as to expose the metal posts 69.

[0005] Note that, in cases where a plurality of semiconductor elements 62 are formed laid out on one Si (silicon) wafer, if [operations] up to the formation of the second insulating layer 68 are performed on the Si wafer, and then the Si wafer is diced so as to be cut into individual semiconductor elements 62, semiconductor devices 61 (CSP) having substantially the same size as the individual semiconductor elements 62 can be obtained.

**[0006]** The metal posts 69 are electrically connected to the electrodes 63 by way of the wiring pattern 67, and electrical connections between the semiconductor device 61 and the outside, for example, electrical connections with a mounting board on which the semiconductor device 61 is mounted, are made by way of the metal posts 69. Note that, if necessary, as shown in FIG. 6, a solder ball 71 or the like is sometimes formed as an external connection terminal 74 on the top face of the metal post 69.

**[0007]** In many cases, the connection between the metal post 69 and the outside (for example, the mounting board) is made by thermocompression bonding using solder, but at this time, if high temperatures of, for example,  $180^{\circ}\text{C}$  to  $250^{\circ}\text{C}$  are reached, some of the metal post 69 will dissolve and dissipate in the solder. In consideration for this dissolution and dissipation, the height of the metal post 69 is generally approximately 3 µm to 50 µm.

**[0008]** However, in a semiconductor device having such a structure, the connection strength between the metal post 69 and the wiring pattern 67 was insufficient, and thus the reliability of the semiconductor device was low. Specifically, when the semiconductor device is mounted on the mounting board, stress is applied to the semiconductor device due to the difference in thermal expansion coefficients between the semiconductor device and the mounting board, and cracks, wire breakage and the like occur in the semiconductor device.

**[0009]** It is of note that, when the present inventors performed a temperature cycling test (a test in which a change in temperature from -40°C to +125°C is considered one cycle, and this change in temperature is repeated multiple times) on a board on which a conventionally used semiconductor device had been mounted, the wiring pattern 67 peeled and disconnected from the metal post 69 at approximately 50 to 200 cycles.

[0010] Furthermore, considering the manufacturing cost of the semiconductor device, it is desirable that the film thickness of the first insulating layer 65 and the second insulating layer 68 are each approximately 10 µm, or less than. If an insulating layer is formed with such a film thickness and, after forming a solder ball 71 on the metal post 69, a connection is made to the outside, stress such as thermal stress concentrates at the solder ball 71, which is the external connection terminal 74 of the semiconductor device 61, and cracks will form in the insulating layer in the vicinity of the solder ball 71, such that wire breakage will occur in the vicinity of the solder ball.

**[0011]** There have been attempts to solve such problems by forming the second insulating layer 68 at a thickness of, for example, approximately  $100 \mu m$ , and giving the metal post 69 a

height of 100  $\mu$ m. Specifically, this is intended to mitigate the stress applied to the semiconductor device due to the difference in the thermal expansion coefficient with respect to the mounting board by increasing the height of the metal post 69.

[0012] However, making a semiconductor device with such a structure results new problems. That is to say, plating methods are generally used for forming the metal post 69, and forming a metal post 69 with a height of 100  $\mu m$  by a plating method raises the manufacturing cost of the semiconductor device, and lowers manufacturing yield. Furthermore, it cannot be said that it is desirable, from the viewpoint of manufacturing costs, to form the second insulating layer 68 with a thickness of approximately 100  $\mu m$ , for example.

[0013] Furthermore, when forming the metal post 69 with a plating method, the second insulating layer 68 is used as a plating mask, and the metal post 69 is formed in an opening in the second insulating layer 68. Therefore, if an attempt is made to form the metal post 69 higher than the thickness of the second insulating layer 68 for which the film thickness has been increased, there will be variations in the height of the metal post 69 and the quality of the metal post 69 will tend to be reduced. For this reason, when electrical connection with the outside is made, local connection failures occur, which is a cause of decreased reliability in the electrical connections. Note that, the decrease in the quality of the metal post discussed above refers to voids (holes) occurring locally in the metal post, which leads to electrical defects such as disconnections. In addition, if the height of the metal post 69 varies, and if the size and shape of the solder ball 71 are nonuniform, there will also a problem in that there will be differences in the pressure applied to the solder or the solder ball when thermocompression bonding the semiconductor device and the mounting board, such that connection failures and damage to the semiconductor device will occur.

**[0014]** Furthermore, if resin is used as the insulating layer, the first insulating layer 65, on which the wiring pattern 67 is formed, is covered with the second insulating layer 68 whereafter this is cured (baked) so as to harden the second insulating layer 68. During the heating that is performed in the step of forming the second insulating layer 68, gas is generated in the first insulating layer 65, and the insulating layer expands due to bubbles resulting from the gas, which leads to wire breakage in the wiring pattern 67.

[0015]

[Problems to Be Solved by the Invention] The present invention was made in light of the problems described above, and thus is directed to providing a highly reliable chip-size package type semiconductor device in which the connection strength between the metal post and the wiring pattern is high and the reliability of the electrical connection with the outside is high, and in which the wiring pattern will not break even if gas is generated in the insulating layer, and a method for

manufacturing the same.

[0016]

[Means for Solving the Problems] In order to achieve the aforementioned object, the present inventors undertook earnest study and arrived at the present invention. That is to say, in claim 1, the semiconductor device is characterized in that a first insulating layer having substantially the same shape as a passivation film is formed on the passivation film, which has been formed on a semiconductor element, with an electrode. which has been formed on the semiconductor element. exposed; a wiring pattern, which is connected with the electrode of the semiconductor element, is formed on the first insulating layer; a metal post for external connection is formed on the wiring pattern; a second insulating layer, which is in close contact with the wiring pattern, is formed in a manner so as to cover a side face of the metal post excluding a tip surface of the metal post; resin sealing is performed with sealing resin in a manner so as to expose the tip surface of the metal post; and an external connection terminal is provided at the tip surface of the metal post.

**[0017]** Furthermore, in claim 2, the semiconductor device according to claim 1 is characterized in that the height of the surface of the second insulating layer excluding the region of the side face of the metal post is established at a position lower than the tip surface of the metal post.

**[0018]** Furthermore, in claim 3, the semiconductor device according to claim 1 or 2 is characterized in that the external connection terminal is configured with an electroconductive material provided on a surface of a support having a hollow part which is opened to the outside.

**[0019]** Furthermore, in claim 4, the semiconductor device according to claim 3 is characterized in that the support has a cylindrical shape having a hollow part opened to the outside.

**[0020]** Furthermore, in claim 5, the semiconductor device according to claim 1 or 2 is characterized in that the external connection terminal is configured with an electroconductive material provided on a surface of a cylindrical support having no hollow part.

[0021] Furthermore, in claim 6, the semiconductor device according to claim 3, 4 or 5 is characterized in that an engineering plastic comprising a resin selected from polyimide, polyamide imide, polyether imide, thermoplastic polyimide, polyamide, polyacetal, polybutylene terephthalate, polyethylene polystyrene, terephthalate, syndiotactic polystyrene, polyphenylene sulfide, polyether ketone, liquid crystal polymer, fluororesin, polyether nitrile, polycarbonate, polyphenylene ether, polysulfone, polyethersulfone, and polyarylate is used for the support comprised by the external connection terminal.

**[0022]** Furthermore, in claim 7, the semiconductor device according to claim 3, 4, 5 or 6 is characterized in that the electroconductive material comprised by the external connection terminal is selected from among the following (1) to (3):

- (1) a dispersion of graphite, carbon or metal fine particles;

- (2) gold, silver, copper, aluminum or nickel alone, or an alloy containing two or more of said metals; and

- (3) a low melting point alloy having tin or lead as a principal component.

**[0023]** Further, in claim 8, a method for manufacturing the semiconductor device according to claim 1, 2, 3, 4, 5, 6 or 7 is characterized by having, at least: a step of forming a first insulating layer on a passivation film, which has been formed on a semiconductor element in such a manner as to expose an electrode formed on the semiconductor element, in such a manner as to expose the electrode; a step of forming a wiring pattern, which is connected with the electrode, on the first insulating layer; a step of forming a metal post for external

connection at a predetermined height, in a predetermined position on the wiring pattern; a step of forming a second insulating layer in which, after applying an insulating resin in a manner so as to include the metal post, the insulating resin is removed from the region of the tip surface of the metal post that connects with the outside; a step of performing resin sealing with sealing resin in a manner so as to expose the tip surface of the metal post; and a step of providing an external connection terminal at the tip surface of the metal post.

**[0024]** Furthermore, in claim 9, the method for manufacturing a semiconductor device according to claim 8 is characterized in that photolithography is used as a means for removing the insulating resin from the region of tip surface of the metal post that connects with the outside; and in claim 10, the method for manufacturing a semiconductor device according to claim 8 or 9 is characterized in that spin coating is used as a means for applying an insulating resin serving as the second insulating layer.

**[0025]** Furthermore, in claim 11, the method for manufacturing a semiconductor device according to claim 8, 9 or 10 is characterized in that, after the semiconductor element on which the second insulating layer has been formed has been affixed to a cooling heatsink, resin sealing is performed on the semiconductor element in a manner so as to expose the tip surface of the metal post and the face of the cooling heatsink on the side opposite to the face to which the semiconductor element was affixed, whereafter, the external connection terminal is mounted on the tip surface of the metal post.

**[0026]** Furthermore, in claim 12, the method for manufacturing a semiconductor device according to claim 11 is characterized in that, after batch forming a plurality of laid-out semiconductor elements, up to the formation of the second insulating layer, these are separated into individual semiconductor elements by dicing, and subsequently affixed to cooling heatsinks.

[0027]

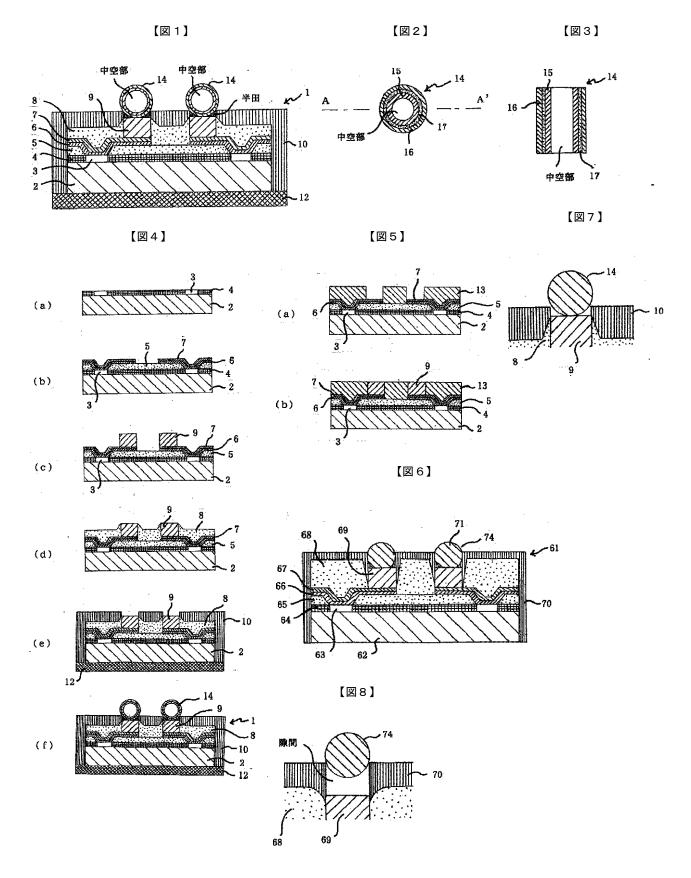

[Modes of Embodiment of the Invention] Hereafter, modes of embodiment of the present invention are described based on the drawings. In the semiconductor device 1 (CSP) of the present invention, as shown in FIG. 1, a first insulating layer 5, which has substantially the same shape as a passivation film 4, is formed on the passivation film 4, in a manner so as to expose electrodes 3, which have been formed on a semiconductor element 2. Then, a wiring pattern 7 (wiring layer) that is connected with the electrodes 3 is formed on the first insulating layer 5, and metal posts 9 for external connection, having a height of approximately 3  $\mu m$  to 50  $\mu m$ , are formed at predetermined positions on the wiring pattern 7. Next, a second insulating layer 8 is formed, which is in close contact with the wiring pattern 7 and the first insulating layer 5, and which

covers the side face of the metal post 9 excluding the tip surface of the metal post 9. Next, the semiconductor element is resinsealed with sealing resin 10 in a manner so as to expose the tip surface of the metal post 9, and an external connection terminal 14 is provided on the metal post 9.

**[0028]** The structure of the semiconductor device 1 of the present invention is such as to prioritize adhesion between the second insulating layer 8 and the metal post 9 in the part of the metal post 9 that is lower than the tip end (closer to the semiconductor element). That is to say, the second insulating layer 8 is formed in a manner so as to cover the side face of the metal post 9 excluding the tip end part. As a result, the adhesion between the second insulating layer 8 and the metal post 9 is reinforced and, in conjunction therewith, the connection strength between the metal post 9 and the wiring pattern 7 is also improved, such that disconnection between the metal post 9 and the wiring pattern 7 can be prevented.

**[0029]** Furthermore, as set forth in the foregoing claim 2, the surface of the second insulating layer 8 is formed in a manner so as be at a position lower than the tip surface of the metal post 9, so as not to present an obstacle when mounting the external connection terminal 14 to the outside (for example, on a mounting board).

[0030] In semiconductor devices such as CSPs and BGAs, it is necessary to resin-seal the main components, including the semiconductor element, for the purpose of improving the reliability and ensuring the mechanical strength of the package. As shown in FIG. 6, in an ordinary semiconductor device, a metal post 69 having a height of, for example, approximately 3 μm to 50 μm is formed, and an external connection terminal 74 is provided on the metal post 69; thus, considering the thickness of the insulating layer 68 as well, the thickness of the semiconductor device 61 after resin sealing will be unnecessarily large. Furthermore, if the surface of the sealing resin 70 is formed at a position that is higher than the tip surface of the metal post 69, problems will arise when providing the external connection terminal 74 by way of thermocompression bonding (for example, soldering) or the like. Further, because the second insulating layer 68 is made of a relatively expensive material, forming the second insulating layer 68 thickly increases the manufacturing cost of the semiconductor device and can be said to be uneconomical. The present inventors propose to optimize the height of the second insulating layer and the metal post, for the purpose of improving the work characteristics in the thermocompression bonding to the external connection terminal and the like.

[0031] That is to say, as shown in FIG. 1, it is proposed that the second insulating layer 8 be formed so that the height of the second insulating layer 8, excluding the location where this covers the side face of the metal post 9, is at a position lower than the height of the tip surface of the metal post 9. This matter will be explained below. As shown in FIG. 8 which is a partial enlarged view of a conventional semiconductor device, if the surface of the second insulating layer 68 is equal to or higher than the height of the tip surface of the metal post 69, the height of the surface of the sealing resin 70 that is formed on the second insulating layer 68 will be higher than the tip surface of the metal post 69. Therefore, even if one were to attempt to provide the external connection terminal 74 (for example, a solder ball) on the tip surface of the metal post 69, which is exposed by way of the opening in the sealing resin 70, the sealing resin 70 would get in the way, and gap would be formed between the tip surface of the metal post 69 and the external connection terminal 74 and the like, such that electrical connection failures would occur between the metal post 69 and the external connection terminal 74.

[0032] However, as shown in FIG. 7, which is a partial enlarged view of the semiconductor device of the present

invention, if the height of the second insulating layer 8, excluding the location where this covers the side face of the metal post 9, is lower than the height of the tip surface of the metal post 9, it is possible to bring the surface of the sealing resin 10 and the tip surface of the metal post 9 close to each other, such that the sealing resin 10 does not get in the way, and thus, when providing the external connection terminal 14, a gap will not be formed between the tip surface of metal post 9 and the external connection terminal 14, so that electrical connection failures between the metal post 9 and the external connection terminal 14 can be prevented.

[0033] Here, there is no particular limitation on the material used for the first insulating layer 5, so long as it has good heat resistance and adhesion, and has no influence on the semiconductor element 2, but as this touches the semiconductor element 2, it is preferable that this be of a high purity. Furthermore, a material with a low dielectric constant is preferable, and polyimide can be said to be preferable from the viewpoint of obtaining high purity, while from the point of view of manufacturing, a photosensitive polyimide material or a photosensitive polyimide siloxane composition or the like is suitable. Furthermore, a lower coefficient of thermal expansion is better, and those having a coefficient of thermal expansion of approximately 60 ppm (60 × 10 exp-6 in/in/°C) or less are desirable in practical terms.

**[0034]** Next, because the material of the second insulating layer 8 does not directly touch the semiconductor element 2, a resin having lower purity than that used for the first insulating layer 5 may be used for the second insulating layer 8. For example, in addition to the above-mentioned polyimides, an epoxy resin, an acrylic resin, a silicone modified product of these resins, or the like can be used.

**[0035]** Next, the material for the wiring pattern 7 is desirably a material with good conductivity and, for example, copper, silver, aluminum, alloys thereof, other metals that are good conductors or the like can be used. If copper, silver, or the like is used as the material for the wiring pattern 7, prior to the formation of the wiring pattern 7, it is preferable to form a metal barrier layer 6 made of a TiW alloy, TiN, TaN, W, Cr or the like as an undercoat layer, and then form the wiring pattern 7 on the metal barrier layer 6.

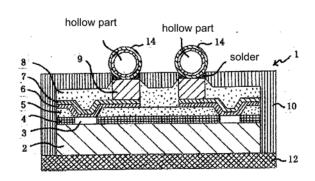

[0036] Next, a characteristic of the semiconductor device 1 of the present invention, as shown in FIG. 1, is that an external connection terminal 14 that makes an external electrical connection (for example, to a mounting board) is placed at the tip end of the metal post 9, the external connection terminal 14 being configured with an electroconductive material provided on the surface of a support having a hollow part opened to the outside. That is to say, this is characterized in that stress applied to the semiconductor device due to the difference in the thermal expansion coefficients between the mounting board and the semiconductor device after mounting is mitigated by the external connection terminal 14, in which the electroconductive material 16 is provided on the surface of the support 15 having the hollow part opened to the outside, as shown in FIGS. 1, 2 and 3. Note that FIG. 2 is a view, seen from the side, of one example of the external connection terminal 14 according to the present invention, and FIG. 3 is a sectional view in which a section at the line A-A' in FIG. 2 is seen from above (for example, seen from the mounting board side).

[0037] The matters set forth above will be explained. As

described above, when the semiconductor device 1 is mounted on the mounting board, stress is caused in the semiconductor device 1 as a result of the difference in the thermal expansion coefficients between the semiconductor element 2, which is formed of silicon or the like (for example, having a thermal expansion coefficient of approximately 3 ppm) and the mounting board (for example, a printed circuit board made of epoxy resin, having a thermal expansion coefficient of approximately 40 to 200 ppm and exceeding 200 ppm at or above the Tg point). Conventionally, when mounting a semiconductor device such as a CSP, BGA or the like on a mounting board such as a printed board, is was easy to form a solder ball having a diameter of, for example, approximately 200 to 400 µm, as an external connection terminal on a metal post, and bond this by thermocompression to the mounting board, and this was in fact performed.

**[0038]** However, stress produced by the difference in thermal expansion coefficients acted on the solder ball, and cracks in semiconductor device or the resin board, such as a printed board, formed as a result of the stress, which was transmitted by way of the solder ball, such that there was a tendency for wires to break relatively easily within the semiconductor device.

[0039] The present inventors conducted earnest study directed to preventing this and, as a result, discovered that, if the external connection terminal 14 is provided with a stress mitigating function, the stress produced by the difference the thermal expansion coefficients can be mitigated by the external connection terminal 14, whereby it is possible to prevent cracks and wire breakage from occurring in the semiconductor device 1. That is to say, in order to provide a stress mitigating function, the external connection terminal 14 according to the present invention has an electroconductive material 16 formed on the surface of a hollow support 15. Because the hollow support 15 has a flexible structure, even if the mounting board that is connected to the external connection terminal 14 repeatedly thermally expands and contracts by a considerable amount, the stress generated can be absorbed and thus mitigated. Consequently, it is possible to prevent cracks from occurring, and to prevent wire breakage due to cracks in the insulating layer at the interface between and the sealing resin and the external connection terminal 14.

[0040] Furthermore, it is preferable that the hollow part of the support 15 is opened to the external atmosphere, and that the air of the external atmosphere can freely enter and exit the hollow part. This matter will be explained. As will be discussed below, it is preferable to form the support 15 from a resin, but resins readily absorb moisture, and resins containing water tend to hydrolyze and be degraded. However, if the hollow part of the support 15 is open to the external atmosphere and the air of the external atmosphere can freely enter and exit the hollow part, the water contained in the support 15 will be released to the external atmosphere such that deterioration of the resin can be prevented. Furthermore, if the hollow part of the support 15 is opened to the external atmosphere, the water vapor resulting from water in the support 15 evaporating, and the expanded air, will be released to the external atmosphere when this is heated during mounting, such that rupture of the support 15 can be prevented. Further, even if heat is applied to the semiconductor device after mounting, water in the support 15 will be released to the external atmosphere, such that rupture and deterioration of the support 15 can be prevented.

**[0041]** Here, the outer shape of the support may be a cylindrical shape, a quadrangular prism shape, a hexagonal prism shape, an octagonal prism shape, an abacus bead shape, or the like, but if it is cylindrical, a self-alignment effect can be expected due to the surface tension of the solder when the solder is melted during soldering, and further considering the

ready availability of materials, it can be said that a cylindrical shape, such as shown in FIGS. 2 and 3, is preferable. Furthermore, if the environment in which the semiconductor device 1 is used has little thermal variation and the stress generated between the semiconductor device 1 and the mounting board is small, the shape of the support 15 may be a cylinder that does not have a hollow part.

[0042] Generally, when these are mounted and electrically connected to the outside (for example, to a mounting board), semiconductor devices such as CSPs and BGAs are mounted by thermocompression bonding with solder, a low melting point alloy, an anisotropic conductive film or the like. For this reason, the material for the support 15 comprised by the external connection terminal 14 according to the present invention is preferably a heat resistant engineering plastic. Here, engineering plastic refers to plastic that is heat resistant at 100°C or more, has a strength of 49 MPa or more, and has a flexural modulus of 2.4 Gpa or more. Materials satisfying the aforementioned conditions include polyimide, polyamide imide, polyether imide, thermoplastic polyimide, polyamide, polyacetal, polybutylene terephthalate, polyethylene terephthalate, polystyrene, syndiotactic polystyrene, polyphenylene sulfide, polyether ketone, liquid crystal polymer, polyether nitrile, fluororesin, polycarbonate, modified polyphenylene ether, polysulfone, polyethersulfone, and polyarylate. Furthermore, this may also be a polymer alloy of an engineering plastic.

**[0043]** Next, the semiconductor device 1 of the present invention performs fixation and electrical connection with the outside (for example, to a mounting board) by way of the external connection terminal 14, and an electroconductive material 16 is provided on the surface of the support 15 comprised by the external connection terminal 14. The electroconductive material 16 must perform fixation with the outside and allow for electrical connection with the outside. Conductive materials 16 that satisfy such conditions are preferably selected from among the following (1) to (3):

- (1) a dispersion of graphite, carbon or metal fine particles;

- (2) gold, silver, copper, aluminum or nickel alone, or an alloy containing two or more of said metals; and

- (3) a low melting point alloy having tin or lead as a principal component.

**[0044]** Note that the low melting point alloys mentioned above include those employing metals such as mercury, gallium, or indium, but a solder alloy having tin or lead as a main component is preferable from the viewpoint of manufacturing costs and the like. Eutectic solder or high-melting point solder with an increased lead ratio can suitably be used as the solder alloy, and if necessary bismuth, cadmium, antimony, zinc, manganese, indium, tin, silver and the like may be added. Note that, in order to improve the adhesion between the support 15 and the electroconductive material 16, as shown in FIG. 2 and FIG. 3, a bonding layer 17 may be formed on the surface of

the support 15, prior to providing the conductive material 16 thereon.

[0045] As an example of the external connection terminal 14 according to the present invention, an example may be cited in which a cylindrical polyimide having a hollow part and having an outer diameter of 100 µm to 1000 µm is used as the support 15, and a solder alloy having a thickness of several microns to several tens of microns is bonded on the surface of the support 15 as an electroconductive material 16, so as to form the external connection terminal 14. Prior to bonding the electroconductive material 16 thereon, a bonding metal layer may be formed on the surface of the tube, as a bonding layer 17. Furthermore, the thickness of the electroconductive material 16 may be increased as necessary, and the length and diameter of the support 15 may be appropriately established to suit the specifications of the semiconductor device 1 and the like.

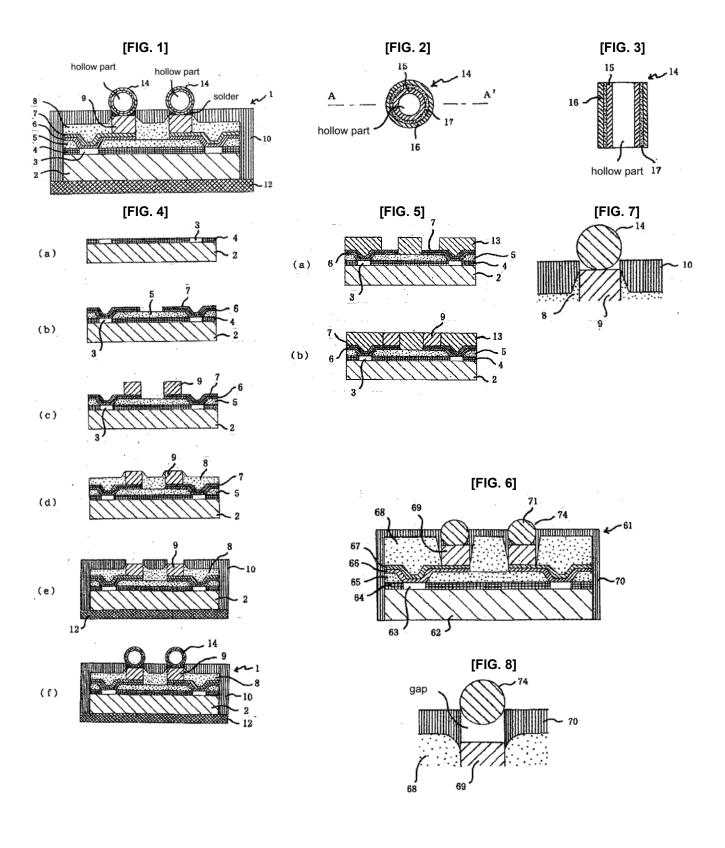

[0046] Next, in the claim 8 set forth above, a method for manufacturing the semiconductor device 1 of the present invention is proposed. That is to say, this is a method of manufacturing a semiconductor device in which electrodes 3, which provide electrical connections with the outside, and are produced by way of a conventionally known manufacturing method, are formed as shown in FIG. 4 (a), and which has at least: a step of forming a first insulating layer 5, which has substantially the same shape as a passivation film 4, on a semiconductor element 2, on the surface of which the passivation film 4 has been formed, in a manner so as to expose the electrodes 3, and then forming a wiring pattern 7 having a predetermined shape, which is connected with the electrodes 3, on the first insulating layer 5, so as to produce state in FIG. 4 (b); a step of forming a metal post 9 for external connection, in a predetermined position of the wiring pattern 7, at a predetermined height (approximately 3 µm to 50 µm), so as to produce FIG. 4 (c); a step of applying an insulating resin on the first insulating layer 5 including the metal post 9, and then removing the insulating resin from the tip region of the metal post 9 for connecting to the outside, so as to make the second insulating layer 8 and produce the state in FIG. 4 (d); a step of resin sealing with the sealing resin 10 so as to produce FIG. 4 (e); and a step of placing the external connection terminal 14 so as to produce FIG. 4 (f). Note that, in the example in FIG. 4, prior to forming the wiring pattern 7, the metal barrier layer 6 is formed as an undercoat layer.

**[0047]** As described above, after the metal post 9 is formed, the second insulating layer 8 is formed, using the insulating resin that has been applied and formed, and at this time, this is formed so that the height of the second insulating layer 8, excluding the side face of the metal post 9, is such as to be a position that is lower than the height of the tip surface of the metal post 9. For this purpose, it is preferable to use a photolithography method, in which a photosensitive insulating resin is used, and application, pattern exposure, development and the like are performed so as to remove the insulating resin in unnecessary parts.

**[0048]** A known application means such as spin coating, curtain coating, screen printing or slit-and-spin coating may be used for applying the insulating resin that serves as the second insulating layer 8. However, with a view to forming the height of the second insulating layer 8 at a position that is lower than the height of the tip surface of the metal post 9, excluding the side face of the metal post 9, spin coating is preferable. That is to say, if the insulating resin is applied by spin coating, after forming the metal post 9, excess insulating resin will be removed to the outside of the semiconductor element. Thus, by appropriately setting the application conditions, it is possible to apply the insulating resin with a film thickness that is less than the height of the tip surface of the metal post 9 in regions excluding the location of side-face of the metal post 9, and it is also possible

to apply the insulating resin to the side face of the metal post 9. Note that, with regard to the removal of the insulating resin remaining on the tip surface of the metal post 9, in addition to the photolithography method described above, this may be selectively removed by laser, dry etching, reverse sputtering or the like.

[0049] Next, a semiconductor device 1 having a cooling heatsink 12 for cooling the semiconductor element 2 is sometimes required. The invention according to claim 11 proposes a manufacturing method for a semiconductor device having a cooling heatsink 12. Specifically, after affixing the cooling heatsink 12 to the semiconductor element 2, which has been formed up to the second insulating layer 8 shown in FIG. 4 (d), this is sealed with the sealing resin 10 in a manner so as to expose the tip surface of the metal post 9 and the surface of the cooling heatsink 12 on the face opposite to the face that is affixed to the semiconductor element 2, so as to produce the state of FIG. 4 (e). The method for manufacturing a semiconductor device is characterized in that the external connection terminal 14 is subsequently mounted on the tip surface of the metal post 9, so as to produce the semiconductor device 1 shown in FIG. 1 and FIG. 4 (f).

**[0050]** Next, in many cases, a plurality of semiconductor elements 2 are formed laid out on a single planar silicon wafer. The invention according to claim 12 proposes a manufacturing method for producing individual semiconductor devices 1 from a silicon wafer on which a plurality of semiconductor elements 2 have been formed laid out. That is to say, the method for manufacturing a semiconductor device is characterized in that, after batch forming the above-described second insulating layer 8 on a silicon wafer having a plurality of laid out semiconductor elements 2, these are separated into individual semiconductor elements 2 by dicing, whereafter a cooling heatsink 12 is affixed to each of the separated individual semiconductor elements 2.

#### [0051]

**[Embodiments]** Hereafter, embodiments of the present invention will be described with reference to the drawings.

**<Embodiments>** FIG. 4 (a) is a semiconductor element 2 produced by conventionally known means, which is incorporated in a semiconductor device 1 of the present invention. Electrodes 3 made of aluminum are formed on the semiconductor element 2 with a silicon wafer as a substrate, and a passivation film 4 is formed on the semiconductor element 2 in a manner so as to expose the electrodes 3. Note that, in the present embodiment, a plurality of semiconductor elements 2 are laid out on a single silicon wafer, but for convenience of description, one semiconductor element 2 from among these is shown.

[0052] Next, a photosensitive polyimide (trade name "Pimel", made by Asahi Kasei Corp.) was applied to the semiconductor element 2, whereafter a known photoetching method was used to perform pattern exposure, development and the like, and a first insulating layer 5 having a film thickness of approximately 10 µm was formed, which exposed the electrodes 3. Next, a 2000 Å thick TiN layer and a 5000 Å thick Cu layer were

sequentially laminated on the first insulating layer 5 by sputtering. Next, a patterning process was performed on the TiN layer and the Cu layer, using a known photoetching method, to produce a wiring pattern 7, which is electrically connected to the electrode 3 (FIG. 4 (b)). Note that the TiN layer between the first insulating layer 5 and the wiring pattern 7 is formed as a barrier metal layer 6

[0053] Next, as shown in FIG. 4(c), a metal post 9 was formed on the wiring pattern 7, whereafter photosensitive polyimide (trade name "Pimel", made by Asahi Kasei Corp.) was applied on the first insulating layer 5 by spin coating, whereafter the excess polyimide was removed by photoetching, excluding the top face [sic] and side face portions of the metal post 9, to produce a second insulating layer 8 (FIG. 4(d)). As shown in FIG. 4(d), the second insulating layer 8 exposed the top face of the metal post 9 and covered the side face of the metal post 9, and at other locations the second insulating layer 8 was given a film thickness of 10 µm, so as to be lower than the top face of the metal post 9. Note that a mask plating method is used for forming the metal post 9, and the steps for the mask plating method are described below. Specifically, after producing FIG. 4 (b), a photosensitive resist layer having a film thickness of 20 µm was formed on the first insulating layer 5 and the wiring pattern 7, whereafter, using a known photoetching method, a plating mask 13 was formed, in which the wiring pattern 7 was exposed at the location where the metal posts were to be formed (FIG. 5 (a)). Next, metal posts 9 made of copper (height 15 μm) were formed on the wiring pattern 7, which was exposed by the plating mask 13, using an electrolytic plating method (FIG. 5 (d) [sic]). Next, the plating mask 13 was peeled off producing that in FIG. 4 (c).

[0054] Next, after producing 4(d), dicing was performed on the silicon wafer on which the semiconductor elements 2 were laid out, so as to divide this into individual semiconductor elements 2, whereafter a heatsink 12 made of a Cu sheet was affixed to the back face of the semiconductor element 2 (the side opposite the face on which the semiconductor integrated circuit has been formed). Next, resin molding was performed with the sealing resin 10 in a manner so as to expose the top face of the metal post 9 and the heatsink 12 (FIG. 4 (e)).

[0055] Next, the external connection terminal 14 was provided on the metal post 9 to produce the semiconductor device 1 (FIG. 4(f)). As shown in FIG. 2, the external connection terminal 14 used in the present embodiment is one in which eutectic solder is formed as the electroconductive material 16 on the surface of the hollow support 15, which is made of thermoplastic polyimide and is produced by the steps described below. First, a hollow thermoplastic polyimide tube having an inner diameter of 0.15 mm and a thickness of 50 µm was purchased in a long format. Next, metallic chromium and copper were sequentially laminated so as to form films on the tube surface (outside surface). Metallic chromium and copper serve as a bonding layer 17 when laminating the electroconductive material, and the films were formed by spluttering so as to produce a metallic chromium film thickness of 0.2 µm, and a copper film thickness of 0.4 µm. After forming the bonding layer 17, a plating was formed with eutectic solder having a film thickness of approximately 20 µm, as the electroconductive material 16. Next, after forming the eutectic solder, the long thermoplastic polyimide tube was cut to individual lengths of approximately 0.3 mm to produce the external connection terminals 14 shown in FIG. 2 and FIG. 3.

[0056] The semiconductor device 1 produced in the present embodiment was mounted on a printed board. The mounting was performed by heated pressure bonding (soldering) at 220°C for 8 seconds. At the time of this heated pressure bonding, the external connection terminal 14 having the hollow support 15 described above absorbed the pressure applied during the

heated pressure bonding, so that it could be mounted and connected with less pressure than conventionally required. It is of note that, in the semiconductor device 1 according to the present embodiment, it was possible to mount and connect this at a pressure that was approximately half of the pressure required conventionally, this being approximately 5 grams at each external connection terminal 14. Furthermore, even in cases where there was variation in the thickness of the printed board and the height of the metal post 9 such that these were not uniform, because the hollow support 15 was easily deformed during mounting, this lack of uniformity was absorbed, such that mounting could be performed without connection failure between the semiconductor device 1 and the printed board.

[0057] The printed board on which the semiconductor device 1 according to the present embodiment was mounted was subjected to a temperature cycle test of -45°C to +125°C to evaluate reliability, and no disconnections occurred even after a 1000 cycle test was performed.

**[0058]** Although embodiments of the present invention have been described above, needless to say, the modes of embodiment of the present invention are not limited to the drawings and descriptions set forth above, and various modifications may be made, based on the gist of the present invention.

**[0059]** For example, in the description set forth above, an example was illustrated in which the external connection terminal according to the present invention is used for a CSP, but the external connection terminal according to the present invention may be formed in a semiconductor device such as a BGA. Furthermore, sputtering was used to form the wiring pattern 7 in the description set forth above, but vacuum deposition, ion plating, CVD, sol-gel or the like can suitably be used for the film formation method, and a suitable film formation method may be selected depending on the configuration. Further, the material and film thickness of the insulating layer, the material and thickness of the electroconductive material, and the material, diameter, length and the like of the support may be appropriately selected according to the specifications of the semiconductor device and the like.

**[0060]** Further, instead of chromium, a metal oxide, a metal nitride, aluminum, or the like may be used for the bonding layer formed between the support and the electroconductive material, and instead of vacuum film formation such as sputtering, as the means for forming the adhesive layer, activation treatment with palladium, electroless plating of copper or nickel, electrolytic plating or the like may be used. Still furthermore, the surface of the support may be subjected to a surface treatment before forming the film on the support, and as means therefor, etching means such as plasma etching, ion etching or wet etching, or alternatively sand blasting may be used.

#### [0061]

**[Effects of the Invention]** As set forth above, in the present invention, the side face of the metal post 9 for external connection is reinforced with the second insulating layer 8, which improves the mechanical strength of the metal post 9, and the second insulating layer 8 is formed only in necessary parts. Therefore, the semiconductor device of the present invention is

capable of reducing electrical connection failures caused by thermal deformation and stress deformation. That is to say, by virtue of the present invention, it is possible to produce a highly reliable semiconductor device (CSP). Because the metal posts 9 comprised by the semiconductor device 1 of the present invention are reinforced by the second insulating layer 8, they have excellent mechanical strength and can also suitably be used in flip-chip type semiconductor devices, build-up type multilayer wiring boards and the like.

[0062] Further, when the second insulating layer 8 is formed, spin coating is used, and for removal of unnecessary resin. including at the upper parts of the metal posts 9, photoetching is used. This makes it possible to form the surface of the second insulating layer lower than the top face of the metal post, excluding the side faces of the metal posts 9. This allows the thickness of the semiconductor device 1 to be reduced, and allows electrical connection failure between the external connection terminal and the metal post caused by contact with the sealing resin to be prevented.

[0063] Furthermore, the second insulating layer 8 is formed in a manner so as to cover the wiring pattern 7 and to form a region lower than the tip surfaces of the metal posts 9, excluding the side faces of the metal posts 9. Thereby, when curing so as to form the second insulating layer 8 (for example, when heating is performed at 400°C for 1 hour in a high temperature oven), even if residual gas is generated in the resin that constitutes the first insulating layer 5, the residual gas will escape by way of the location in the second insulating layer 8 where the film thickness is low (region on the wiring pattern 7). Therefore, it is possible to prevent wire breakage in the wiring pattern 7 due to the resin part swelling because of bubbles caused by the residual gas.

[0064] Furthermore, if the heatsink 12 is attached to the back face of the semiconductor element 2 after the second insulating layer 8 is formed and [the wafer] is diced into individual pieces, a semiconductor device 1 having excellent heat dissipation properties can be obtained. Furthermore, since the resin sealing is performed excluding the tip surface of the metal post 9, a semiconductor device can be obtained in which the top face and the side faces are protected by the sealing resin, which has excellent airtightness and excellent reliability, and has no package cracks or the like due to moisture absorption.

[0065] Further, in the semiconductor device 1 of the present invention, the external connection terminal 14 comprises the hollow support 15. That is to say, in the present invention, a stress mitigating function is given to the external connection terminal 14, which has a simple structure and is produced by a simple manufacturing process. As a result, when the semiconductor device 1 is mounted on the mounting board, stress that is applied to the semiconductor device 1, due to the difference in thermal expansion coefficients between the semiconductor device 1 and the mounting board, is absorbed by the external connection terminal 14 having the stress mitigating function, allowing wire breakage and the like to be prevented, such that it will be possible to provide a highly reliable semiconductor device. With a conventional BGA, a stress mitigating means known as an interposer or the like was provided to mitigate the external forces applied to the device, but this stress mitigating means was large, and thus there was a limit on reductions in the size of the device. However, with the semiconductor device 1 of the present invention, because stress can be mitigated by the external connection terminal 14 having a simple structure, it is possible to reduce the size of the device. Furthermore, even in cases where the thickness of the printed board and the height of the metal post 9 vary such that these are not uniform, the external connection terminal 14 having the stress mitigating function can be easily deformed during mounting such that this lack of uniformity can be absorbed, and thus it is possible to prevent connection failures due to variation

and lack of uniformity in the thickness of the printed circuit board and the height of the metal post.

[0066] Furthermore, by giving the support 15 comprised by the external connection terminal 14, for example, a cylindrical shape, having a hollow part opened to the outside, it is possible to improve the reliability of electrical connection when mounting the semiconductor device 1. That is to say, when moisture is present in the support 15, this is released from the support 14 when heated during mounting, this moisture being a cause of problems such as electrical connection failures. Further, moisture in the support 15 leads to deterioration of the support 15. However, since the support 15 is hollow, moisture escapes from the hollow part into the external atmosphere when heated, such that it is possible to prevent electrical connection failures or the like during mounting, and moisture in the support 15 is released to the external atmosphere such that deterioration of the support 15 can be prevented.

#### [0067]

#### [Brief Description of Drawings]

[FIG. 1] This is a sectional explanatory view, schematically illustrating one embodiment of a semiconductor device of the present invention.

[FIG. 2] This is an explanatory view illustrating one example of an external connection terminal according to the present invention.

[FIG. 3] This is a sectional explanatory view illustrating one example of an external connection terminal according to the present invention.

[FIG. 4] (a) to (f) are sectional explanatory views illustrating one example of a method of manufacturing a semiconductor device of the present invention in the order of the steps.

[FIG. 5] (a) to (b) are sectional explanatory views illustrating one example of a method of forming the metal post in the order of the steps.

[FIG. 6] This is a sectional explanatory view, schematically illustrating one example of a conventional semiconductor device.

**IFIG. 71** This is an enlarged explanatory view, schematically illustrating one example of main components of a semiconductor device of the present invention.

[FIG. 8] This is an enlarged explanatory view showing an example of connection failure in a conventional semiconductor device.

#### [Explanation of the Symbols]

- semiconductor device 1, 61

- 2.62 semiconductor element

- 3.63 electrode

- 4.64 passivation film

- 5, 65 first insulating layer

- 6, 66 barrier layer

- 7, 67 wiring pattern

- 8.68

- second insulating layer

- 9.69 metal post

- 10, 70 sealing resin 11, 71 solder ball

- 12 heatsink

- 13 plating mask

- 14, 74 external connection terminal

- 15 support

#### (19)日本国特許庁(JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号 特開2001-53184 (P2001-53184A)

(43)公開日 平成13年2月23日(2001.2.23)

(51) Int.Cl.7

識別記号

FΙ

テーマコード(参考)

H01L 23/12

H01L 23/12

L

審査請求 未請求 請求項の数12 OL (全 10 頁)

(21)出願番号 特願平11-224490

(22)出願日 平成11年8月6日(1999.8.6)

(71)出願人 000003193

凸版印刷株式会社

東京都台東区台東1丁目5番1号

(72)発明者 古屋 明彦

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

(72)発明者 北村 智史

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

(72)発明者 福吉 健蔵

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

#### (54) 【発明の名称】 半導体装置及びその製造方法

#### (57) 【要約】

【課題】メタルポストと配線パターンの接続強度が高く、外部との電気的接続の信頼性が高く、さらに絶縁層からガスが発生しても配線パターンの断線の生じない、信頼性の高いチップサイズパッケージタイプの半導体装置及びその製造方法を提供する。

【解決手段】電極を露出して半導体素子上に形成されたパッシベーション膜上にパッシベーション膜と略同一形状の第1の絶縁層が形成され、第1の絶縁層上に半導体素子の電極と接続する配線パターンが形成され、配線パターン上に外部接続用のメタルポストが形成され、メタルポスト先端を除いたメタルポストの側面を被覆するよう、配線パターンに密着する第2の絶縁層が形成され、かつ、メタルポスト先端を露出するよう封止樹脂した後メタルポスト先端に外部接続端子を配設していることを特徴とする半導体装置。

#### 【特許請求の範囲】

【請求項1】半導体素子に形成された電極を露出して半導体素子上に形成されたパッシベーション膜上に前記パッシベーション膜と略同一形状の第1の絶縁層が形成され、前記第1の絶縁層上に半導体素子の電極と接続する配線パターンが形成され、前記配線パターン上に外部接続用のメタルポストが形成され、前記メタルポスト先端面を除いたメタルポストの側面を被覆するよう、配線パターンに密着する第2の絶縁層が形成され、前記メタルポスト先端面を露出するよう封止樹脂にて樹脂封止され、かつ、前記メタルポスト先端面に外部接続端子が配設されていることを特徴とする半導体装置。

【請求項2】メタルポスト側面領域を除いた第2の絶縁層の表面の高さを、メタルポスト先端面より低い位置に設定したことを特徴とする請求項1に記載の半導体装置。

【請求項3】前記外部接続端子を、外部に開放された中空部を有する保持体の表面に導電性材料を配設した構成としたことを特徴とする請求項1または2に記載の半導体装置。

【請求項4】保持体を、外部に開放された中空部を有するシリンダー状としたことを特徴とする請求項3に記載の半導体装置。

【請求項5】前記外部接続端子を、中空部を有しない円筒状とした保持体の表面に導電性材料を配設した構成としたことを特徴とする請求項1または2に記載の半導体装置。

【請求項6】外部接続端子を構成する保持体を、ポリイミド、ポリアミドイミド、ポリエーテルイミド、熱可塑性ポリイミド、ポリアミド、ポリアセタール、ポリブチレンテレフタレート、ポリエチレンテレフタレート、ポリスチレン、シンジオタクチックポリスチレン、ポリフェニレンサルファイド、ポリエーテルケトン、液晶ポリマー、ポリエーテルニトリル、フッ素樹脂、ポリカーボネート、変成ポリフェニレンエーテル、ポリサルフォン、ポリエーテルサルホン、およびポリアリレートより選択された樹脂からなるエンジニアプラスチックとしたことを特徴とする請求項3、4または5に記載の半導体装置。

【請求項7】外部接続端子を構成する導電性材料を、 ①グラファイト、カーボンもしくは金属微粒子分散体、 ②金、銀、銅、アルミニウム、もしくはニッケルの単 体、または前記金属を二種類以上含む合金、

③錫もしくは鉛を主成分とする低融点合金、

上記①~③のうちから選択したことを特徴とする請求項 3、4、5または6に記載の半導体装置。

【請求項8】半導体素子に形成された電極を露出するよう形成したパッシベーション膜上に前記電極を露出するよう第1の絶縁層を形成する工程と、前記第1の絶縁層上に前記電極と接続する配線パターンを形成する工程

と、前記配線パターンの所定の位置に外部接続用のメタルポストを所定の高さにて形成する工程と、前記メタルポストを含むよう絶縁性樹脂を塗布した後、外部と接続するメタルポストの先端面領域から絶縁性樹脂を除去し第2の絶縁層とする工程と、メタルポストの先端面を露出するよう封止樹脂にて樹脂封止する工程と、メタルポストの先端面に外部接続端子を配設する工程とを少なくとも有することを特徴とする請求項1、2、3、4、5、6または7に記載の半導体装置の製造方法。

【請求項9】外部と接続するメタルポストの先端面領域から絶縁性樹脂を除去する手段をフォトリソグラフィ法とすることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】第二の絶縁層とする絶縁性樹脂の塗布手段をスピンコート法としたことを特徴とする請求項8または9に記載の半導体装置の製造方法。

【請求項11】第2の絶縁層を形成した半導体素子を冷却用ヒートシンクに貼りつけた後、メタルポスト先端面および、半導体素子を貼りつけた面と反対面側の冷却用ヒートシンク面を露出するよう樹脂封止し、しかる後、メタルポスト先端面に外部接続端子を搭載することを特徴とする請求項8、9または10に記載の半導体装置の製造方法。

【請求項12】面付けされた複数の半導体素子に一括して第2の絶縁層の形成まで行った後、ダイシングにより個々の半導体素子に分離し、しかる後、冷却用ヒートシンクへの貼りつけを行うことを特徴とする請求項11に記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は、半導体素子上に配線層を形成したチップサイズパッケージ(CSP)と呼称される半導体装置及びその製造方法に係わる。

#### [0002]

【従来の技術】近年、電子装置の小型化により、電子装置に組み込まれる(実装される)半導体装置は高密度での実装が行われるようになっており、それにともなって、半導体装置はより一層小型とすることが要求されている。この要求に答える技術として、チップサイズパッケージ(Chip SizePackage、以下CSPと記す)、BGA(ボールグリッドアレイ)等が提案されている。CSPは半導体素子(ICチップ)と略同等のサイズとすることができ、半導体装置の小型化にとって有効な手段といえる。CSPの構造、形態は種々のものが提案されているが、以下にCSPの構造を模式的に示す図面に基づき、一般的なCSPの形態につき説明を行う。

【0003】図6は従来の半導体装置61(CSP)の例を模式的に示す断面説明図である。

【0004】図6に示すように、アルミ等からなる電極

63 (接続用パッド)を形成した半導体素子62上には電極63を露出するようパッシベーション膜64が形成されている。次いで、パッシベーション膜64上に電極63を露出するよう絶縁性樹脂等からなる第一の絶縁層65が形成される。また、第一の絶縁層65上には電極63と接続した配線パターン67(配線層)が形成されており、配線パターン67上に銅等からなるメタルポスト69を配設している。なお、図6の例では、配線パターン67の下にメタルバリア層66を形成している。次いで、配線パターン67および第一の絶縁層65上にはメタルポスト69を露出するよう第二の絶縁層68が形成されている。また、メタルポスト69を露出するよう封止樹脂70にて樹脂封止が行われている。

【0005】なお、1枚のSi(シリコン)ウェファー上に半導体素子62を面付けして複数個形成している場合、Siウェファー上に上記第二の絶縁層68の形成まで行い、その後、Siウェファーにダイシングを行い個々の半導体素子62に断裁すれば、個々の半導体素子62と略同一のサイズとなった半導体装置61(CSP)を得ることができる。

【0006】メタルポスト69は配線パターン67を介して電極63と電気的に接続しているもので、半導体装置61と外部との電気的接続、例えば半導体装置61が搭載される実装基板との電気的接続はメタルポスト69を介して行われる。なお、必要により図6に示すようにメタルポスト69上面に外部接続端子74としてハンダ(半田)ボール71等を形成する場合もある。

【 0 0 0 7 】メタルポスト69と外部(例えば実装基板)との接続はハンダを用い熱圧着にて行う場合が多いが、その際に例えば180℃~250℃程度と高温になるとメタルポスト69の一部がハンダに溶解消失することになる。この溶解消失を考慮してメタルポスト69の高さは3μm~50μm程度とすることが一般的となっている。【 0 0 0 8 】しかし、かかる構造とした半導体装置においてはメタルポスト69と配線パターン67との接続強度が不足し、半導体装置の信頼性が低いものとなっていた。すなわち、半導体装置を実装基板に搭載した際に半導体装置と実装基板との熱膨張率の差により半導体装置に応力が加わり、クラック、断線等が半導体装置に生じるものである。

【0009】ちなみに、本発明者らが従来より用いられていた半導体装置を実装した基板に温度サイクル試験(-40℃から+125℃まで温度を変化させて1サイクルとし、この温度変化を複数回繰り返す試験)を行ったところ、50~200サイクル程度でメタルポスト69と配線パターン67が剥がれ断線が生じたものである。

【 0010】また、半導体装置の製造コストを考慮した場合、第一の絶縁層65および第二の絶縁層68の膜厚は各々  $10\mu$ m前後もしくはそれ以下とすることが望ましい。かかる膜厚にて絶縁層を形成し、また、メタルポスト69にハンダボール71を形成した上で外部との接続を行

うと、熱応力等のストレスが経時的に半導体装置61の外部接続端子74であるハンダボール71に集中し、ハンダボール71近傍の絶縁層にクラックが入り、また、ハンダボール近傍で断線が生じることになる。

【0011】このような問題を解決するため、第二の絶縁層68を例えば100μm程度に厚く形成し、かつ、メタルポスト69の高さを100μmとすることが試みられている。すなわち、メタルポスト69の高さを高くすることで、実装基板との熱膨張率の差により半導体装置に加わる応力を緩和させようとするものである。

【0012】しかし、かかる構成とした半導体装置とすることは新たな問題を生じることになる。すなわち、メタルポスト69の形成にあたっては、メッキ法を用いることが一般的となっており、そのためメッキ法にて100  $\mu$  mの高さのメタルポスト69を形成することは半導体装置の製造コストを引き上げ、また、製造収率を下げることになる。また、第二の絶縁層68を例えば100  $\mu$  m程度と厚く形成することも製造コスト上望ましいとはいえない。

【0013】さらに、メッキ法によるメタルポスト69の 形成では、第二の絶縁層68をメッキマスクとし、第二の 絶縁層68の開口部にメタルポスト69を形成している。こ のため、膜厚を厚くした第二の絶縁層68の膜厚より高い メタルポスト69を形成しようとする場合、メタルポスト 69の高さにバラツキを生じ、また、メタルポスト69の質 を低下させやすい。このため外部との電気的接続を行う と部分的に接続不良が生じる等、電気的接続の信頼性を 低下させる要因となるものである。なお、上述したメタ ルポストの質の低下とは、断線等の電気的欠陥に結びつ くボイド(空孔)が部分的にメタルポスト内に生じるこ とを意味する。さらに加えて、メタルポスト69の高さが バラツキ、また、ハンダボール71の大きさや形状が不均 ーとなった場合、半導体装置と実装基板との熱圧着時に ハンダもしくはハンダボールに加わる圧力に差を生じ、 接続不良や半導体装置の破損を生じるという問題もあ

【 O O 1 4 】また、絶縁層として樹脂を用いた場合、配線パターン67を形成した第一の絶縁層65上を第二の絶縁層68で被覆した後、キュア(焼きかため)にて第二の絶縁層68の硬化を行う。この第二の絶縁層68の形成工程で行われる加熱の際、第一の絶縁層65よりガスが発生し、ガスによる気泡で絶縁層が膨れ配線パターン67の断線を引き起こすことになる。

## [0015]

【発明が解決しようとする課題】本発明は以上の問題に鑑みなされたもので、メタルポストと配線パターンの接続強度が高く、外部との電気的接続の信頼性が高く、さらに絶縁層からガスが発生しても配線パターンの断線の生じない、信頼性の高いチップサイズパッケージタイプの半導体装置及びその製造方法を提供しようとするもの

である。

#### [0016]

【課題を解決するための手段】本発明者らは、上記の課題を達成するために鋭意検討を行い本発明に至ったものである。すなわち請求項1においては、半導体素子に形成された電極を露出して半導体素子上に形成されたパッシベーション膜上に前記パッシベーション膜と略同一形状の第1の絶縁層が形成され、前記第1の絶縁層上に半導体素子の電極と接続する配線パターンが形成され、前記メタルポスト先端面を除いたメタルポストの側面を被覆するよう、配線パターンに密着する第2の絶縁層が形成され、前記メタルポスト先端面を露出するよう封止樹脂にて樹脂封止され、かつ、前記メタルポスト先端面に外部接続端子が配設されていることを特徴とする半導体装置としたものである。

【0017】また請求項2においては、メタルポスト側面領域を除いた第2の絶縁層の表面の高さを、メタルポスト先端面より低い位置に設定したことを特徴とする請求項1に記載の半導体装置としたものである。

【0018】また請求項3においては、前記外部接続端子を、外部に開放された中空部を有する保持体の表面に導電性材料を配設した構成としたことを特徴とする請求項1または2に記載の半導体装置としたものである。

【0019】また請求項4においては、保持体を、外部に開放された中空部を有するシリンダー状としたことを特徴とする請求項3に記載の半導体装置としたものである。

【0020】また請求項5においては、前記外部接続端子を、中空部を有しない円筒状の保持体の表面に導電性材料を配設した構成としたことを特徴とする請求項1または2に記載の半導体装置としたものである。

【0021】また請求項6においては、外部接続端子を構成する保持体を、ポリイミド、ポリアミドイミド、ポリアニアルイミド、熱可塑性ポリイミド、ポリアミド、ポリアセタール、ポリブチレンテレフタレート、ポリスチレン、シンジオタクチックポリスチレン、ポリフェニレンサルファイド、ポリエーテルケトン、液晶ポリマー、ポリエーテルニトリル、フッ素樹脂、ポリカーボネート、変成ポリフェニレンエーテル、ポリサルフォン、ポリエーテルサルホン、およびポリアリレートより選択された樹脂からなるエンジニアプラスチックとしたことを特徴とする請求項3、4または5に記載の半導体装置としたものである。

【 O O 2 2 】また請求項7においては、外部接続端子を 構成する導電性材料を、

- ①グラファイト、カーボンもしくは金属微粒子分散体、②金、銀、銅、アルミニウム、もしくはニッケルの単体、または前記金属を二種類以上含む合金、

- ③錫もしくは鉛を主成分とする低融点合金、

上記①~③のうちから選択したことを特徴とする請求項3、4、5または6に記載の半導体装置としたものである。

【0023】さらに請求項8においては、半導体素子に 形成された電極を露出するよう形成したパッシベーション膜上に前記電極を露出するよう第1の絶縁層を形成する工程と、前記第1の絶縁層上に前記電極と接続する配線パターンを形成する工程と、前記配線パターンの所定の位置に外部接続用のメタルポストを含むよう絶縁性樹脂を塗布した後、外部と接続するメタルポストの先端面を露出するよう封止樹脂にて樹脂 域から絶縁性樹脂を除去し第2の絶縁層とする工程とは 域から絶縁性樹脂を除去し第2の絶縁層とする工程とは メタルポストの先端面を露出するよう封止樹脂にて樹脂 対上する工程と、メタルポストの先端面に外部接続端子を配設する工程とを少なくとも有することを特徴とする 請求項1、2、3、4、5、6または7に記載の半導体 装置の製造方法としたものである。

【 0 0 2 4 】また請求項9においては、外部と接続するメタルポストの先端面領域から絶縁性樹脂を除去する手段をフォトリソグラフィ法とすることを特徴とする請求項8に記載の半導体装置の製造方法としたものであり、請求項10においては、第二の絶縁層とする絶縁性樹脂の塗布手段をスピンコート法としたことを特徴とする請求項8または9に記載の半導体装置の製造方法としたものである。

【 0 0 2 5 】また請求項 1 1 においては、第 2 の絶縁層を形成した半導体素子を冷却用ヒートシンクに貼りつけた後、メタルポスト先端面および、半導体素子を貼りつけた面と反対面側の冷却用ヒートシンク面を露出するよう樹脂封止し、しかる後、メタルポスト先端面に外部接続端子を搭載することを特徴とする請求項 8 、 9 または 1 0 に記載の半導体装置の製造方法としたものである。

【0026】また請求項12においては、面付けされた 複数の半導体素子に一括して第2の絶縁層の形成まで行った後、ダイシングにより個々の半導体素子に分離し、 しかる後、冷却用ヒートシンクへの貼りつけを行うこと を特徴とする請求項11に記載の半導体装置の製造方法 としたものである。

#### [0027]

【発明の実施の形態】以下に、本発明の実施形態につき図面に基づき説明する。本発明の半導体装置 1 (CSP)においては、図 1 に示すように、半導体素子 2 に形成された電極 3 を露出するよう形成されたパッシベーション膜 4 上に、電極 3 を露出するようパッシベーション膜 4 と略同一形状とした第一の絶縁層 5 を形成している。ついで、第 1 の絶縁層 5 上に電極 3 と接続する配線パターン 7 (配線層)を形成しており、配線パターン 7 上の所定の位置に外部接続用の 3  $\mu$  m ~ 5 0  $\mu$  m 程度の高さとしたメタルポスト9を形成している。次いで、メタルポスト9の先端面を除いてメタルポスト9の側面を

被覆する、配線パターン7及び第1の絶縁層5に密着した第2の絶縁層8を形成している。次いで、メタルポスト9の先端面を露出するよう半導体素子を封止樹脂10にて樹脂封止しており、また、メタルポスト9上に外部接続端子14を配設している。

【0028】本発明の半導体装置1においては、メタルポスト9先端より下部(半導体素子方向)においては第二の絶縁層8とメタルポスト9との密着性を優先させる構造としている。すなわち、先端部を除いたメタルポスト9の側面を被覆するよう第二の絶縁層8を形成している。これにより、第二の絶縁層8とメタルポスト9との密着性が補強され、それにともない、メタルポスト9と配線パターン7との接続強度も向上しメタルポスト9と配線パターン7との断線が防止できる。

【0029】また、外部接続端子14と外部(例えば実装基板)との実装の際に支障をきたさないよう、上述した請求項2に記したように、第2の絶縁層8の表面を、メタルポスト9先端面より低い位置となるように形成している。

【0030】CSP、BGA等の半導体装置において は、パッケージの信頼性向上や機械的強度の保持等を目 的として半導体素子を含めた主要部を樹脂封止すること が必要である。図6に示すように、通常の半導体装置に おいては、例えば3 µm~50 µm程度の高さのメタル ポスト69を形成し、メタルポスト69上に外部接続端子74 を配設するものであり、第二の絶縁層68の厚みをも考慮 すると樹脂封止後の半導体装置61の厚みは必要以上に厚 いものとなる。また、封止樹脂70の表面がメタルポスト 69の先端面より比較的高い位置に形成された場合、外部 接続端子74の熱圧着 (例えばハンダ付け) 等による配設 の際に支障が生じるものである。さらに、第二の絶縁層 68は比較的高価な材質のものを使用するため、第二の絶 縁層68を厚く形成することは半導体装置の製造コストを 上げることになり不経済といえる。本発明者らは外部接 続端子の熱圧着の作業性向上等を目的として、第二の絶 縁層とメタルポストとの高さを最適化することを提案す るものである。

【0031】すなわち、図1に示すように、メタルポスト9の側面を被覆する部位を除く第二の絶縁層8の高さがメタルポスト9先端面の高さより低い位置になるよう第二の絶縁層8を形成することを提案するものである。この点につき以下に説明を行う。従来の半導体装置の一部拡大図である図8に示すように、第二の絶縁層68の表面がメタルポスト69先端面の高さと同等もしくは高い場合、第二の絶縁層68上に形成される封止樹脂70の表面の高さはメタルポスト69先端面より高いものとなる。このため、封止樹脂70の開口部より露出したメタルポスト69先端面上に外部接続端子74(例えばハンダボール)を配設しようとしても封止樹脂70で邪魔をされ、メタルポスト69先端面と外部接続端子74との間に隙間が生じる等、

メタルポスト69と外部接続端子74との電気的接続不良が生じる。

【 0 0 3 2 】しかるに本発明の半導体装置の一部拡大図である図7に示すように、メタルポスト9の側面を被覆する部位を除く第二の絶縁層8の高さをメタルポスト9先端面の高さより低くすれば、封止樹脂10表面とメタルポスト9先端面とを近くすることが出来、封止樹脂10が邪魔をしないため、外部接続端子14を配設する際にメタルポスト9先端面と外部接続端子14との間に隙間が生じず、メタルポスト9と外部接続端子14との電気的接続不良を防止できる。

【 0 0 3 4 】次いで、第二の絶縁層 8 の材料は、第二の 絶縁層 8 が半導体素子 2 と直接に触れないため第一の絶 縁層 5 に使用するものより純度の低い樹脂を使用しても 構わない。例えば、前述したポリイミドの他、エポキシ 樹脂、アクリル樹脂、あるいはこれらの樹脂をシリコー ン変成させたもの等が使用できる。

【0035】次いで、配線パターン7の材料は導電性の良いものが望ましく、例えば、銅、銀、アルミニウム、これらの合金、あるいは他の良導体金属等が使用できる。なお、銅や銀等を配線パターン7の材料として用いる場合には、配線パターン7の形成に先立ち、下引き層としてTiW合金、TiN、TaN、W、Cr等からなるメタルバリヤ層6を形成し、しかる後、メタルバリヤ層6上に配線パターン7を形成することが望ましい。

【0036】次いで、本発明の半導体装置1の特徴として図1に示すように、外部に開放された中空部を有する保持体の表面に導電性材料を配設した形状とした、外部(例えば実装基板)との電気的接続を行う外部接続端子14をメタルポスト9先端に配設している。すなわち、実装した後に実装基板と半導体装置との熱膨張率の差により半導体装置にかかる応力を、図1、図2および図3に示すように、外部に開放された中空部を有する保持体15の表面に導電性材料16を配設した外部接続端子14で緩和させることを特徴としている。なお、図2は本発明に係わる外部接続端子14の一例を側面から見た図であり、図3は図2のA-A、線における断面を上方から見た(例えば実装基板側から見た)図である。

【0037】上述した点につき説明を行う。前述したよ

うに、半導体装置1を実装基板に実装すると、シリコン等で形成される半導体素子2(例えば、熱膨張率が約3ppm程度)と実装基板(例えば、エポキシ系樹脂からなるプリント基板:熱膨張率40~200ppm程度、但しTg点以上では200ppmを超える)との熱膨張率の差で生じるストレス(応力)が半導体装置1にかかる。従来より、CSP、BGA等の半導体装置をプリント基板等の実装基板に実装するには、例えば200~400μm径程度のハンダボールを外部接続端子としてメタルポスト上に形成し、ハンダボールを介して実装基板に熱圧着することが簡便であり、また実際に行われていた。

【0038】しかし、熱膨張率の差で生じるストレス (応力)がハンダボールにかかり、ハンダボールを介し て伝わるストレス(応力)により半導体装置もしくはプ リント基板等の樹脂基板にクラックが発生し、また半導 体装置内では比較的簡単に断線する傾向があった。

【0039】これを防止するため本発明者らは鋭意検討を行ったものであり、その結果、外部接続端子14に応力緩和機能を持たせれば、熱膨張率の差で生じるストレス(応力)は外部接続端子14で緩和され、半導体装置1にクラックや断線が発生することを防止できることを見いだした。すなわち、本発明に係わる外部接続端子14は応力緩和機能を持たせるため、中空とした保持体15の表面に導電性材料16を形成したものである。中空とした保持体15は柔構造のため、外部接続端子14と接続した実装基板が相当量の熱伸縮を繰り返しても、発生したストレス(応力)を吸収し応力を緩和することができる。これにより、絶縁層および封止樹脂と外部接続端子14との界面でのクラックの発生、および、クラックによる断線を防止できる。

【0040】また、保持体15の中空部は外部雰囲気に開 放され、外部雰囲気の空気が自由に中空部に出入り可能 な状態としておくことが望ましい。この点につき説明す る。後述するように保持体15は樹脂で形成することが望 ましいが、樹脂は水分を吸収しやすく、水分を含んだ樹 脂は加水分解を生じ劣化しやすい。しかし、保持体15の 中空部を外部雰囲気に開放したものとし、外部雰囲気の 空気(エアー)が自由に中空部に出入り可能な状態にし ておけば、保持体15に含まれた水分が外部雰囲気に放出 され樹脂の劣化が防止できる。また、保持体15の中空部 が外部雰囲気に開放されていれば、実装時に加熱された 際に、保持体15中の水分が蒸発した水蒸気や膨張した空 気は外部雰囲気に放出され、保持体15に破裂が生じるこ とを防止できる。さらに、実装後に半導体装置に熱が加 わても、保持体15中の水分が外部雰囲気に放出されるこ とになり、保持体15の破裂や劣化を防止できる。

【0041】ここで、保持体の外形形状は円筒状、四角柱状、六角柱状、もしくは八角柱状、算盤玉状等であっても構わないが、円筒状であればハンダ付け時にハンダ

が溶解した際、ハンダの表面張力によりセルフアライメント効果が期待でき、さらに材料の入手の容易性をも考慮すると図2、図3に示すようなシリンダー状(円筒状)が望ましいといえる。また、半導体装置1の使用される環境が熱変化の少ないものであり、半導体装置1と実装基板との間で生じる応力が小さいものであれば、保持体15の形状は中空部を有しない円筒状として構わない

【0042】CSP、BGA等の半導体装置は外部(例 えば実装基板) への実装、電気的接続の際、ハンダ、低 融点合金、異方性導電膜等による熱圧着実装を行うこと が一般的である。このため、本発明に係わる外部接続端 子14を構成する保持体15の材質は、耐熱性を有するエン ジニアプラスチックが好ましい。ここでエンジニアプラ スチックとは、耐熱性が100℃以上、強度が49MP a以上、曲げ弾性率が2. 4 G p a 以上のプラスチック のことをいうものである。上記条件を満たす材質とし て、ポリイミド、ポリアミドイミド、ポリエーテルイミ ド、熱可塑性ポリイミド、ポリアミド、ポリアセター ル、ポリブチレンテレフタレート、ポリエチレンテレフ タレート、ポリスチレン、シンジオタクチックポリスチ レン、ポリフェニレンサルファイド、ポリエーテルケト ン、液晶ポリマー、ポリエーテルニトリル、フッ素樹 脂、ポリカーボネート、変成ポリフェニレンエーテル、 ポリサルフォン、ポリエーテルサルホン、およびポリア リレート等の樹脂が挙げられる。また、上記エンジニア プラスチックのポリマーアロイであっても構わない。

【 O O 4 3 】次いで、本発明の半導体装置 1 は外部接続端子14を介して外部(例えば実装基板)との固定および電気的接続を行うもので、外部接続端子14を構成する保持体15の表面には導電性材料16を配設する。導電性材料16は、外部と固定を行い、かつ、電気的接続が可能でなければならない。このような条件を満たす導電性材料16としては

- ①グラファイト、カーボンもしくは金属微粒子分散体、②金、銀、銅、アルミニウム、もしくはニッケルの単体、または前記金属を二種類以上含む合金、

- ③錫もしくは鉛を主成分とする低融点合金、が挙げられ、

上記①~③のうちから選択することが望ましい。

【 O O 4 4 】なお、上述した低融点合金としては、水銀、ガリウム、またはインジウム等の金属を用いたものが挙げられるが、製造コスト等の観点から、錫もしくは鉛を主成分としたハンダ(半田)合金が好ましい。ハンダ合金としては、共晶ハンダや鉛の比率を高めた高融点ハンダが適用でき、また必要に応じてビスマス、カドミウム、アンチモン、亜鉛、マンガン、インジウム、錫、銀等を添加しても構わない。なお、図2および図3の例に示すように、保持体15と導電性材料16との接着性を向上させるために導電性材料16の配設に先立ち、保持体15

の表面に接着層17を形成しても構わない。

【0045】本発明に係わる外部接続端子140例として、例えば中空部を有する $100\mu$ m~ $1000\mu$ m外径の円筒状のポリイミドを保持体15とし、保持体15の表面に導電性材料16として数 $\mu$ m~数 $10\mu$ m厚のハンダ合金を被着し外部接続端子14とすることが挙げられる。なお、導電性材料16の被着に先立ち、チューブの表面に接着層17として接着金属層を形成しても構わない。また、導電性材料16の厚みは必要に応じてもっと厚くしても構わず、さらに保持体15の長さおよび径は半導体装置10位様等に合わせて適宜設定して構わない。

【0046】次いで、前述した請求項8においては本発 明の半導体装置1の製造方法を提案している。 すなわ ち、図4(a)に示す、従来公知の製造方法により得ら れた、外部との電気的接続を行う電極3が形成され、か つ、電極3を露出するパッシベーション膜4が表面に形 成された半導体素子2に、電極3を露出するようパッシ ベーション膜4と略同一形状とした第1の絶縁層5を形 成した後、第1の絶縁層5上に電極3と接続する所定の 形状とした配線パターンフを形成し図4(b)の状態と する工程と、配線パターンフの所定の位置に外部接続用 のメタルポスト9を所定の高さ(3 $\mu$ m~50 $\mu$ m程 度)にて形成し図4(c)とする工程と、メタルポスト 9を含めた第1の絶縁層5上に絶縁性樹脂を塗布した 後、外部と接続するメタルポスト9の先端領域から絶縁 性樹脂を除去し第2の絶縁層8とし図4(d)の状態と する工程と、封止樹脂10にて樹脂封止を行い図4 (e) とする工程と、外部接続端子14を配設し図4(f)とす る工程とを少なくとも有する半導体装置の製造方法とし たものである。なお、図4の例においては、配線パター ン7の形成に先立ち、下引き層としてメタルバリヤ層6 を形成している。

【0047】上述したように、メタルポスト9を形成後、塗布形成した絶縁性樹脂にて第2の絶縁層8を形成するが、その際、メタルポスト9の側面を除く第二の絶縁層8の高さをメタルポスト9先端面の高さより低い位置になるように形成する。そのため、絶縁性樹脂を感光性のものとし、塗布、パターン露光、現像等を行い不要部の絶縁性樹脂の除去を行うフォトリソグラフィー法を用いることが望ましい。

【0048】第2の絶縁層8とする絶縁性樹脂の塗布には、スピンコート法、カーテンコート法、スクリーン印刷法、スリットアンドスピンコート法等の公知の塗布手段を用いることで構わない。しかし、メタルポスト9の側面を除く第二の絶縁層8の高さをメタルポスト9先端面の高さより低い位置になるように形成することを考慮した場合、スピンコート法が望ましい。すなわち、メタルポスト9の形成後にスピンコート法にて絶縁性樹脂の塗布を行えば、余分な絶縁性樹脂は半導体素子の外へ除去される。このため塗布条件を適宜設定することで、メ

タルポスト9の側面部位を除いた領域ではメタルポスト9先端面の高さより薄い膜厚にて絶縁性樹脂を塗布でき、かつ、メタルポスト9の側面にも絶縁性樹脂を塗布できることになる。なお、メタルポスト9先端面に残った絶縁性樹脂の除去は、前述したフォトリソグラフィー法の他に、レーザー、ドライエッチング、逆スパッタ等で選択的に除去することであっても構わない。

【0049】次いで、半導体装置1として、半導体素子2の冷却のために冷却用ヒートシンク12を有するものが要求される場合がある。請求項11に係わる発明は、冷却用ヒートシンク12を有する半導体装置の製造方法を提案するものである。すなわち、図4(d)に示す第2の絶縁層8まで形成した半導体素子2に、冷却用ヒートシンク12を貼りつけた後、メタルポスト9先端面および、半導体素子2を貼りつけた面と反対面側の冷却用ヒートシンク12面を露出するよう封止樹脂10にて樹脂封止し図4(e)の状態とする。しかる後、メタルポスト9先端面に外部接続端子14を搭載し、図1および図4(f)の半導体装置1を得ることを特徴とする半導体装置の製造方法としたものである。

【0050】次いで、半導体素子2は、板状の一枚のシリコンウェファーに複数個面付けされた状態で形成される場合が多い。請求項12に係わる発明は、面付けして複数個形成された半導体素子2を有するシリコンウェファーから個々の半導体装置1を得る製造方法を提案するものである。すなわち、面付けされた複数個の半導体素子2を有するシリコンウェファー上に一括して前述した第2の絶縁層8の形成まで行った後にダイシングにより個々の半導体素子2に分離し、しかる後、分離された個々の半導体素子2に各々冷却用ヒートシンク12の貼りつけを行うことを特徴とする半導体装置の製造方法としたものである。

# [0051]

【実施例】以下に、本発明の実施例につき図面に基づき 説明する。

く実施例>図4 (a) は本発明の半導体装置1に組み込む、従来公知の手段により得られた半導体素子2である。半導体素子2はシリコンウェファーを基材としてアルミからなる電極3が形成されており、また、半導体素子2上には電極3を露出するようパッシベーション膜4が形成されている。なお、本実施例においては半導体素子2は一枚のシリコンウェファー上に複数個面付けされているが、説明の都合上、その内の1個の半導体素子2を図示している。

【0052】次いで、半導体素子2上に感光性ポリイミド(旭化成工業(株)製、商品名「パイメル」)を塗布した後、パターン露光、現像等を行う公知のフォトエッチング法を用い、電極3を露出する膜厚約10 $\mu$ mの第一の絶縁層5を形成した。次いでスパッタリング法にて膜厚2000ÅのTiN層および膜厚5000ÅのCu

層を順次第一の絶縁層 5上に積層した。次いで、公知のフォトエッチング法を用いて i N層および C u 層をパターニング処理し、電極 3 と電気的に接続した配線パターン7を得た(図4(b))。なお、第一の絶縁層 5 と配線パターン7 との間の T i N層はバリアメタル層 6 として形成したものである。

【0053】次いで、図4(c)に示すように、配線パ ターン7上にメタルポスト9を形成した後、第一の絶縁 層 5 上に感光性ポリイミド(旭化成工業(株)製、商品 名「パイメル」)をスピンコート法にて塗布した後、フ オトエッチング法にてメタルポスト9上面および側面部 を除く余分なポリイミドを取り除き第二の絶縁層8を得 た(図4(d))。図4(d)に示すように、第二の絶 縁層8はメタルポスト9上面を露出し、かつ、メタルポ スト9側面を被覆させ、その他の部位ではメタルポスト 9上面より低くなるよう膜厚10μmとした。なお、メ タルポスト9の形成にあたってはマスクメッキ法を用い たものであり、以下にマスクメッキ法の工程を記す。す なわち、図4(b)を得た後、第一の絶縁層5および配 線パターン7上に膜厚20μmの感光性レジスト層を形 成した後、公知のフォトエッチング法を用いメタルポス ト形成部位の配線パターンフを露出させたメッキマスク 13を形成した(図5(a))。次いで、電解メッキ法を 用い、メッキマスク13より露出した配線パターンフ上に 銅からなるメタルポスト9 (高さ  $15\mu$ m)を形成した (図5 (d))。次いで、メッキマスク13を剥膜し図4 (c) としたものである。

【0054】次いで、図4(d)とした後、半導体素子2が面付けされたシリコンウェファーにダイシングを行い、半導体素子2を個片化した後、半導体素子2の裏面(半導体集積回路が形成された面と反対面側)にCu板からなるヒートシンク12を貼りつけた。次いで、メタルポスト9の上面およびヒートシンク12が露出するよう封止樹脂10にて樹脂モールドを行った(図4(e))。

【0055】次いで、メタルポスト9上に外部接続端子 14を載置し、半導体装置1を得た(図4(f))。本実 施例で用いた外部接続端子14は、図2に示すように熱可 塑性ポリイミドからなる中空の保持体15の表面に導電性 材料16として共晶ハンダを形成したもので、以下に記す 工程で得た。すなわちまず、内径0.15mm、肉厚5 Ο μ mの中空の熱可塑性ポリイミドチューブを長尺状で 購入した。次いで、チューブ表面(外側面)に金属クロ ムと銅を順次積層成膜した。金属クロムおよび銅は導電 性材料を積層する際に接着層17としての役目を持たせた もので、金属クロムの膜厚を Ο. 2μm、銅の膜厚を 0. 4 μ m となるようスパッタリングにより成膜した。 接着層17を形成した後、導電性材料16として膜厚約20 μmの共晶ハンダをメッキ形成した。次いで、共晶ハン ダの形成後、長尺状の熱可塑性ポリイミドチューブを各 々長さ約0.3mmにカッティングし、図2および図3

に示す、外部接続端子14とした。

【0056】本実施例で得た半導体装置1をプリント基板に実装した。実装は220℃、8秒間の加熱圧着(ハンダ付け)で行った。その加熱圧着の際、上述した中空の保持体15を有する外部接続端子14が加熱圧着時にかかる圧力を吸収するため、従来必要とされていた圧力より軽い圧力で実装接続できた。ちなみに本実施例に係わる半導体装置1では1か所の外部接続端子14当たり5グラム程度と、従来必要とされていた圧力の半分程度の圧力で実装接続できた。また、プリント基板の厚みやメタルポスト9の高さにバラツキが有り不均一となった場合でも、実装の際に中空の保持体15が容易に変形したためこの不均一を吸収したものであり、半導体装置1とプリント基板との接続不良を生じること無く実装できた。

【0057】本実施例に係わる半導体装置 1 を実装したプリント基板に-45  $^{\circ}$ C  $^{\circ}$ C  $^{\circ}$ C  $^{\circ}$ C の温度サイクル試験を行い信頼性の評価を行ったが、1000 回のサイクルテストを行った後も断線が生じなかった。

【0058】以上、本発明の実施例につき説明したが、本発明の実施の形態は上述した図面および記述に限定されるものではなく、本発明の趣旨に基づき種々の変形を行っても構わないことはいうまでもない。

【 O O 5 9 】例えば、上述した説明では本発明に係わる外部接続端子をCSPに用いた例を示したが、本発明に係わる外部接続端子はBGA等の半導体装置に形成しても構わない。また、上述した説明では配線パターン7の成膜にスパッタリング法を用いたが、成膜方法は真空蒸着法、イオンプレーティング法、CVD法、もしくはゾルゲル法等が適用可能であり形態に応じて適宜成膜法を選択して構わない。さらに、絶縁層の材質および膜厚、導電性材料の材質、膜厚、または、保持体の材質、径および長さ等も半導体装置の仕様等に応じて適宜選択して構わない。

【 O O 6 O 】 さらに、保持体と導電性材料との間に形成する接着層として、クロムの代わりに、金属酸化物や金属窒化物、あるいはアルミニウム等を用いても良く、接着層の成膜手段はスパッタ法のような真空成膜に変えて、パラジウムによる活性化処理、銅やニッケルの無電解メッキ、電解メッキ等を用いても構わない。さらにまた、保持体への成膜を行う前に保持体表面を表面処理することであっても構わず、その手段として、プラズマエッチング、イオンエッチング、あるいはウェットエッチング等のエッチング手段、もしくはサンドブラストを用いても構わない。

#### [0061]

【発明の効果】上述したように、本発明においては、外部接続用のメタルポスト9の側面を第二の絶縁層8で補強しメタルポスト9の機械的強度を向上させており、また、第二の絶縁層8を必要部のみに形成している。このため、本発明の半導体装置は、熱歪み、応力歪みに起因

する電気的接続不良を減少させることが可能である。すなわち、本発明により高信頼性の半導体装置(CSP)を得ることが可能となる。また、本発明の半導体装置1を構成するメタルポスト9は第二の絶縁層8で補強されているため機械的強度に優れており、フリップチップタイプの半導体装置やビルドアップ型多層配線板等に形成するメタルポストにも適用することが可能である。