I, Michael Fletcher, declare:

1. I am well versed in both the Japanese and English languages and have over 14 years of experience translating Japanese technical documents into English.

2. The following translation of the patent document WO0055910A1 to English is accurate and complete to the best of my knowledge.

I declare under penalty of perjury under the laws of the United States of America that the foregoing is true and accurate.

Executed this 10th day of January, 2018, at Parowan, UT

Michael fletcher

Michael Fletcher

PC T

World Intellectual Property Organization

International Office

International Application based on Patent Cooperation Treaty

| (51) International Patent Classification 7 A<br>H01L 23/12 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>(11) International Application No.<br/>WO00/55910</li> <li>(43) International Publication Date</li> </ul>                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) International Application No.       PCT/JP00/01550         (22) International Application Date       March 14, 2000         (30) Priority Rights Data       March 15, 1999 (15.03.99) JP         (71) Applicant (all designated countries except the US)         Hitachi, Ltd. [JP/JP]         6, 4-chome, Kandasurugadai, Chiyoda-ku, Tokyo 101-8010         Tokyo, (JP)         (72) Inventor; Same         (75) Inventor/Applicant (Only for US)         YAGUCHI, Akihiro [JP/JP]         MIURA, Hideo [JP/JP]         KAZAMA, Atsushi [JP/JP]         c/o Hitachi, Ltd Machinery Research Center, 502 Kandatsu-         machi, Tsuchiura-shi, Ibaraki-ken 300-0013         NISHIMURA, Asao         c/o Hitachi, Ltd. Semiconductor Business HQ Tokyo (JP) 20-         1, 5-chome, Josuihon-cho, Kodaira-shi, Tokyo         (54) Title: Semiconductor Device and Semiconductor Module | September 21, 2000         (74) Agent         ASAMURA, Kiyoshi et al.         Shin-Otemachi Bld 331, 2-1, 2-chome, Otemachi,         Chiyoda-ku, Tokyo 100-0004 Tokyo (JP)         (81) Designated Countries         CN, KR, SG, US         Attached Publication         International Search Report |

| $\begin{cases} 1 \\ 1 \\ 1 \\ 3 \\ 8 \\ 6a \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7a $7a$ $2$ $7a$ $5$                                                                                                                                                                                                                                                                                 |

## Abstract

A small semiconductor device with an external terminal on the semiconductor element as well as a semiconductor structure equipped with a small semiconductor device, wherein, disconnection of the external terminal is prevented if temperature change is applied with the semiconductor device mounted on a printed wiring board.

## **Resolution Means**

A protrusion is formed on the land of the external terminal connector of the semiconductor device and the protruding part of the protrusion is connected to the external terminal. Also, a protective film intervening part made up of a resin material if formed between the land and the semiconductor terminal.

| 1  | Specification                                                                                       |

|----|-----------------------------------------------------------------------------------------------------|

| 2  |                                                                                                     |

| 3  | Semiconductor device and structure with semiconductor mounted                                       |

| 4  | Technical Field                                                                                     |

| 5  | The present invention is related to a small semiconductor device having external terminals on a     |

| 6  | semiconductor element, and more specifically, to a small semiconductor device having a              |

| 7  | semiconductor element with various functions manufactured using wafer processes and to a            |

| 8  | semiconductor module having a semiconductor device with external terminals mounted on a printed     |

| 9  | wiring board.                                                                                       |

| 10 |                                                                                                     |

| 11 | BACKGROUND TECHNOLOGY                                                                               |

| 12 | Flip chip mounting has been conventionally used as high packing density mount technology for        |

| 13 | mounting a semiconductor element on a printed wiring board or the like without packaging it. With   |

| 14 | this flip chip mounting, external terminals are formed on pads of a semiconductor element, and the  |

| 15 | pads of the semiconductor element and bonding pads on a printed wiring board are electrically and   |

| 16 | mechanically connected via the external terminals.                                                  |

| 17 |                                                                                                     |

| 18 | With flip chip mounting, however, the layout and size of external terminals are restricted by the   |

| 19 | layout and size of pads of the semiconductor element. The pad size of a semiconductor element is    |

| 20 | about 50 $\mu m$ at a maximum and the pad spacing is about 100 $\mu m$                              |

| 21 | In general, a printed wiring board using resin material as the base material thereof, the size of a |

| 22 | bonding pad is roughly 200 $\mu m$ at a minimum and the bonding pad spacing is roughly 500 $\mu m$  |

| 23 | Therefore, using flip chip mount technology, it is difficult to mount a semiconductor element on a  |

| 24 | printed wiring board that uses resin material as its base material.                                 |

| 25 | In order to solve the above-described problem associated with flip chip mounting technology,        |

| 26 | the tendency for the size of the semiconductor device to get close to the size of the semiconductor |

| 27 | element is remarkable. A package of such a semiconductor device is generally called a CSP           |

| 28 | (abbreviation of chip size package or chip scale package). Examples of CSP are described in JP-A-6- |

| 29 | 504408, Technical Report of the Institute of Electronics, Information and Communication Engineers   |

| 30 | "Development of Tape BGA type CSP", CPM96-121, ICD96-160 (December 1996) and the like.              |

| 31 |                                                                                                     |

1 DISCLOSURE OF THE INVENTION 2 In semiconductor device package based on this type of conventional technology, a sheet-shaped member made of a film base material formed with conductive wire lines and lands is attached to the 3 4 surface of a semiconductor element with an adhesive member, and external terminals are formed in 5 the plane of projection of the principal surface of the semiconductor element. Therefore, the 6 package size is approximately the same size as the semiconductor element. 7 With conventional CSP techniques in which external terminals described above are arranged in 8 the plane of projection of the principal surface of a semiconductor element, metal bumps such as 9 solder bumps are used as the external terminals and are connected to a printed wiring board. A 10 problem associated with CSP having such a structure is a connection reliability of solder bumps. 11 A coefficient of linear thermal expansion of a semiconductor element (silicon (Si)) is roughly 3 x 12  $10^{-6}$ /°C and a coefficient of linear thermal expansion of the most common printed circuit board (FR-4 13 or the like) made of glass epoxy resin group is about 17 x  $10^{-6}$ /°C. If there is a large difference 14 between the two coefficients of linear thermal expansion and the semiconductor device is subjected 15 to a temperature change, thermal strain is generated in the external terminals which are the solder 16 bumps. 17 Strain generated in the bump is concentrated close to the bonding area between the bump and 18 the land of a semiconductor device or the bonding pad of the printed wiring board. If such a 19 temperature change is repeated, it can cause a crack in the bonding area. The crack formed in the 20 bonding area of the bump gradually grows leading to a disruption in the bonding area of the bump. 21 As the bump that is the external terminal is disrupted, electrical connection between the 22 semiconductor device and an external device via the external terminal cannot be maintained; 23 therefore, reliability of the semiconductor device is lowered considerably. 24 25 A CSP type semiconductor device with consideration for solder bump fatigue failure thought to have high reliability is the semiconductor device disclosed in Japanese Unexamined Patent 26 27 Application H06-504408. 28 In this semiconductor device, a sheet-shaped member is attached to the principal surface of a 29 semiconductor element with an adhesive member with low elasticity made of a flexible material 30 (e.g., elastomer resin: polymer substance having a rubber-like elasticity at an ordinary temperature) 31 Material having an elastic modulus approximately equal to that of the adhesive member is used as a 32 sealing member. Therefore, a coefficient of linear thermal expansion difference between a 33 semiconductor element and a printed wiring board can be absorbed by the adhesive member which 34 is made of flexible elastomer resin. As a result, thermal strain applied to a solder bump can be 35 reduced.

1 However, this semiconductor device requires specific techniques for respective processes for 2 forming flexible material, a process of connecting internal wire lines using leads, and a process of sealing with sealing member. Therefore, if this package is to be manufactured with conventional 3 4 wafer processes for semiconductor elements, new manufacture equipment is required posing a 5 problem of an increase of the number of processes and manufacturing cost. 6 Furthermore, the peripheral area of leads for this conventional semiconductor is covered with a 7 flexible sealing member so that a large deformation acts on the leads due to thermal deformation of 8 the flexible adhesive member and this may lead to disconnection of the lead. 9 An example of a CSP type semiconductor device manufactured by wafer manufacturing 10 processes to improve the solder bump reliability and reduce manufacturing cost has been proposed 11 in "Advent of Low Cost Method for CSP Expected as Main Candidate for Chip Size Mount", Nikkei 12 Micro Devices, April 1998 (pg. 164 to 167). 13 With this conventional semiconductor device, additional wire lines are formed on the 14 semiconductor element, a column-like member called a via post made of metal is formed on the 15 additional wire lines, and the peripheral area of the via post is sealed with resin. A solder bump is 16 bonded via a barrier metal layer to the upper surface of the via post exposed through the sealing 17 resin. 18 With this semiconductor device, deformation of the solder bump near the bonding area on the 19 semiconductor device side is suppressed by the via post which has a large rigidity, so that strain 20 generated in this area can be reduced effectively. However, the strain generated in the bonding area

21 on the printed wiring board side due to the linear expansion coefficient difference between the

22 semiconductor element and the printed wiring board increases by the amount that strain in the

23 bonding area of the semiconductor device side is reduced.

24 It is, therefore, difficult to improve the reliability of the semiconductor device as a whole.

Similar to CSP, flip chip mounting techniques are also associated with the problem of a

connection reliability of a solder bump which is an external terminal.

Countermeasure techniques for improving the reliability of solder connections based on flip

chip mounting techniques are described in Japanese Unexamined Patent Application H07-211722, in

which a bump electrode for an external terminal formed by a first metal layer and a second metal

layer formed on a semiconductor element pad via a metal thin film is connected to the bonding pad

of a printed wiring board.

With this conventional technique, the first metal layer protruding from the pad increases the

With this conventional technique, the first metal layer protruding from the pad increases the

height of the bump electrode enabling reducing the thermal strain generated in the bump electrode.

34

1 However, as a semiconductor element is mounted on a printed wiring board made of resin 2 material as its base material based on flip chip mounting techniques, differences in the size of the semiconductor element and the printed wiring board connections lead to thermal strain 3 4 concentrations at the connection on the semiconductor element side where the size of the 5 connection is small so sufficient strain reduction can not be achieved. 6 Further, since the layout of bump electrodes as the external terminals is dependent upon the 7 layout of bonding pads of the semiconductor element, the wire design of the printed wiring board 8 cannot be performed freely, and this is factor that hinders standardization of printed wiring boards. 9 An object of the present invention is to overcome the problems described above and provide a 10 semiconductor device and a semiconductor module having high reliability capable of 11 preventing/suppressing disconnection of, in particular, the external terminal. 12 The problems described above can be resolved through use of the following structures for 13 suppressing and reducing strain generated in the external terminal due to differences in the 14 coefficient of linear thermal expansion between a printed wiring board and a semiconductor device 15 for a semiconductor device comprising a semiconductor element, a passivation film, a conductive 16 wire line connected to the pad of the semiconductor element, a land contiguous with the conductive 17 wire line, an insulating protective film, and an external terminal. 18 (1) Having a protrusion formed on the land to which the external terminal is bonded, this 19 protrusion being bonded to the external terminal made of solder material or the like, and a 20 protective film being formed between the passivation film and the land. 21 The protrusion is preferably bonded to the external terminal so that the protrusion protrudes 22 into the inside of the external terminal. 23 The land of the semiconductor device is formed out of metal material such as copper (Cu). This 24 material has a higher rigidity than that of solder used as the material for the external terminal and 25 that of the protective film that covers the semiconductor element surface. As the protrusion and 26 external terminal are bonded together in the manner described above, deformation of the external 27 terminal near the bond part on the semiconductor device side is constrained by the protrusion. 28 Thus, the thermal distortion that occurs on the external terminal near the bond on the 29 semiconductor device side can be reduced. 30 Furthermore, the protective film is interposed between the land and the passivation film on the 31 semiconductor element surface. The protective film is made of resin material which has a smaller 32 elastic modulus than those of the materials normally used for the land and external terminal. 33

1 Since the protective film with a smaller elastic modulus is interposed between the land to be 2 bonded to the external terminal and the passivation film on the semiconductor element surface, deformation that occurs in the external terminal due to a difference in the linear expansion 3 4 coefficient between the semiconductor device and the printed wiring board can be mitigated based 5 on deformation of the protective film. It is, therefore, possible to reduce strain that occurs in the 6 bond parts on both the semiconductor device and printed wiring board. 7 (2) Further, the conductive wire line comprises a first conductive wire line connected to the pad 8 of a semiconductor element and a second conductive wire line connected to the first conductive

9 wire line and land. The protective film comprises a first protective film connected to the first

10 conductive wire line and second conductive wire line and a second protective film having an exposed

11 surface on the side where the external terminal is formed. It is preferable that the first protective

12 film is interposed just under the land.

13 It is also preferable that a protrusion is formed on the land, and the external terminal andprotrusion are bonded together.

Furthermore, It is preferable that in the semiconductor device with the structure described above, the first conductive wire line and second conductive wire line are connected somewhere other than just under the land.

With the structure described above, the first conductive wire line and second conductive wire line are arranged in a lamination structure in the thickness direction of the semiconductor device so that the protective film can be interposed between the land contiguous with the second conductive wire line and the semiconductor element. It is, therefore, possible to reduce strain that occurs in the bond parts on both the semiconductor device and printed wiring board.

23 Since the conductive wire line is made of metal material such as copper (Cu) or the like with a 24 rigidity greater than that of the protective film, if the connection between the first conductive wire 25 line and second conductive wire line is in plane of projection of the land, the strain mitigation effects 26 of the protective film are lost. Therefore, the first conductive wire line and second conductive wire 27 line are preferably connected in an area somewhere other than the plane of projection of the land. 28 In addition, it is preferable that the second protective film is formed out of material with a larger 29 elastic modulus than that of the first protective film. Therefore, it is possible to prevent 30 disconnection as the amount of deformation of the second conductive wire line can be reduced. 31 (3) Furthermore, the insulative protective film is made up of a first protective film connected to 32 the land and resides between the semiconductor element and the land and a second protective film

- 33 with an exposed surface on the side on which the external terminal is formed.

- 34

1 As described above, the first protective film is provided so as to connect to the land. The first 2 protective film is formed out of resin material such as polyimide with an elastic modulus smaller 3 than that of the material normally used for the land and external terminal. Since the protective film 4 with a smaller elastic modulus is interposed between the land to be bonded to the external terminal 5 and the passivation film on the semiconductor element surface, deformation that occurs in the 6 external terminal due to a difference in the linear expansion coefficient between the semiconductor 7 device and the printed wiring board can be mitigated based on deformation of the protective film. It 8 is, therefore, possible to reduce strain that occurs in the bond parts on both the semiconductor 9 device and printed wiring board. The second protective film is formed with an exposed surface on 10 the side where the external terminal is formed so as to connect to the conductive wire line and the 11 surface of the land on the side the external terminal is formed on, to thereby protect the conductive 12 wire line and land. 13 In addition, it is preferable that the second protective film is formed out of material with a larger 14 elastic modulus than that of the first protective film. Therefore, it is possible to prevent disconnection as the amount of deformation of the conductive wire line can be reduced. 15 16 (4) Furthermore, with the semiconductor device described above, the protrusion resides in the 17 plane of projection of the land and the end of the land is positioned outside of the edge of the 18 protrusion. 19 As described above, although thermal strain generated in the external terminal due to 20 temperature change can be reduced through restraint of the deformation of the external terminal 21 by the protrusion having a large rigidity, deformation generated by the difference in the coefficients 22 of linear thermal expansion between the semiconductor device and printed wiring board acts upon 23 the protrusion itself. This deformation of the protrusion generates stress at the boundary between 24 the land formed with a protrusion and the protective film. The stress is concentrated upon 25 particularly the end of the land, and a crack of the protective film may be formed starting from this 26 area. In order to prevent this crack of the protective film, the land end is arranged outside of the 27 protrusion edge. Therefore, the contact area between the land and protective film increases so that 28 the stress generated at the boundary therebetween can be distributed over a broad surface area 29 and the stress concentrated at the end of the land end can be mitigated. 30 (5) Furthermore, it is preferable that the protrusion and external terminal of the semiconductor 31 device are bonded together via a metal thin film provided on the surface of the protrusion. 32 As the metal thin film such as gold (Au) or nickel (Ni) is formed in the bond part of the protrusion 33 bonded to the external terminal, connection reliability can be improved. 34 (6) A semiconductor module with the semiconductor device described above mounted on a 35 printed wiring board via an external terminal, constructed so that the external terminal arrangement direction bond area between the bonding pad of the printed wiring board and the external terminal 36

- 37 is larger than the external terminal arrangement direction bond area of the protrusion and external

- 38 terminal.

- 39

(7) Furthermore, a semiconductor module with the semiconductor device described above

mounted on a printed wiring board via external terminals constructed so the peripheral area of the

bond part between the bonding pad of the printed circuit board and the external terminal is covered

with resin.

5 In a comparison of the strains generated in each of the bond parts on the semiconductor device 6 and printed wiring board, the strain generated in the bond part on the printed wiring board side are 7 larger from a relative perspective than those generated in the bond parts on the semiconductor 8 device side adjacent to the first protective film with low elasticity that is formed on the 9 semiconductor device and upon which the protrusion is formed. With the present invention, in order 10 to reduce the strain generated in the bond part of the printed wiring board, the external terminal 11 arrangement direction bond area between the bonding pad of the printed wiring board and the 12 external terminal is set larger than the external terminal arrangement direction bond area of the 13 protrusion and external terminal The strain generated in the bond part of the external terminal is 14 reduced as the bond part surface area becomes broader. This is because if the size of the land of the 15 semiconductor device or the size of the bonding pad of the printed circuit board is increased in size 16 increase the bond part surface area, the rigidity of the bond part increases causing the amount of 17 deformation in the solder to be reduced. As described above, as the bond part on the printed circuit 18 board side is made broader than that on the semiconductor device side, the strain to be generated 19 in the bond part on the printed circuit side can be reduced so that a difference from the strain on 20 the package side can be made small. It is, therefore, possible to improve the reliability of the 21 semiconductor module as a whole. 22 The peripheral area of the bond part between the bonding pad of the printed wiring board and 23 the external terminal is covered with resin. The strain generated in the bond part described above is 24 distributed into the boundary between the external terminal and resin so that the strain generated 25 in the bond part between the external terminal and bonding pad is reduced. It is, therefore, possible 26 to reduce the difference between the strain generated in the bond part on the package side and the 27 bond part on the printed circuit board side and therefore to improve the reliability of the 28 semiconductor module as a whole.

29 [Brief Description of the Drawings]

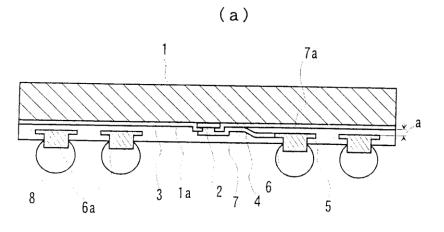

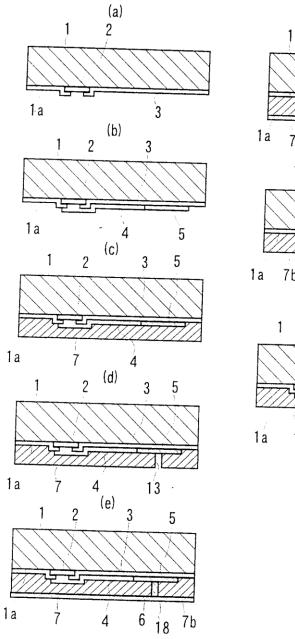

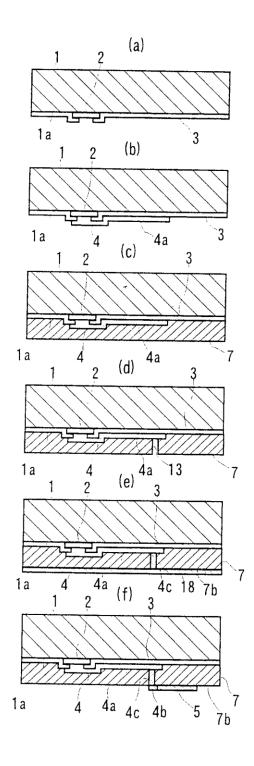

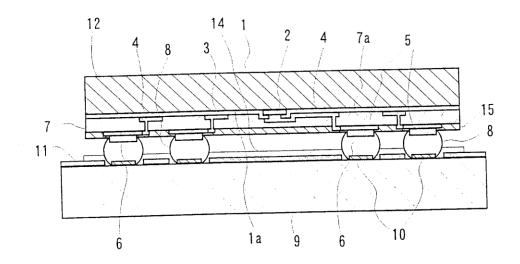

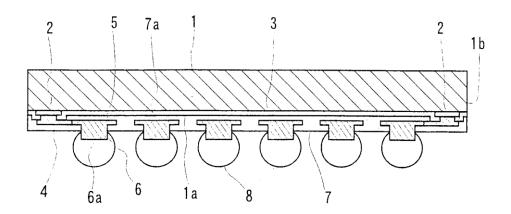

30 FIG. 1(a) is a cross-sectional view of a semiconductor device according to a first embodiment of

31 the present invention and plan view with a portion of its protective film removed.

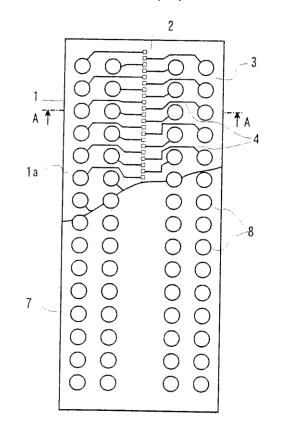

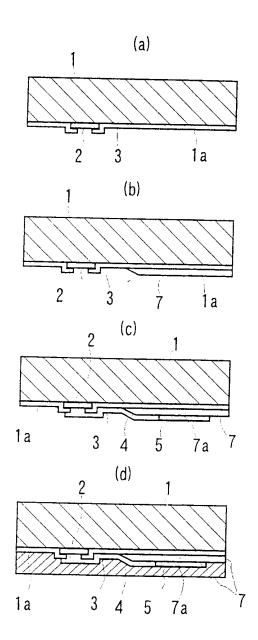

32 FIG. 2 is a partial cross-sectional drawing that describes the manufacturing method of the

33 semiconductor device based on embodiment 1 shown in FIG. 1.

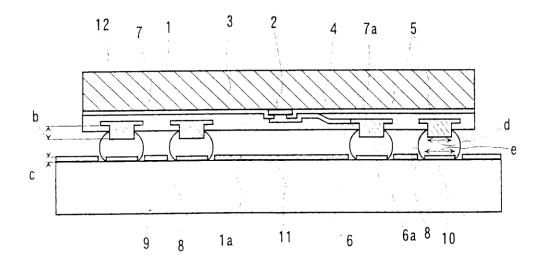

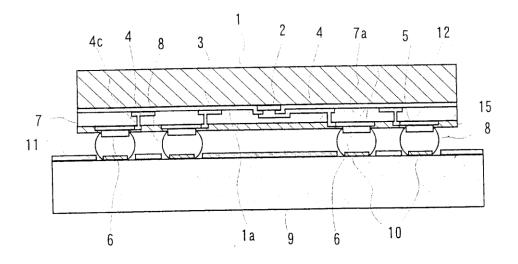

| 1  | FIG. 3 is a cross-sectional view of a semiconductor module having the semiconductor device of   |

|----|-------------------------------------------------------------------------------------------------|

| 2  | embodiment 1 shown in FIG. 1 mounted on a printed wiring board.                                 |

| 3  | FIG. 4 is a cross-sectional view of another example of a semiconductor module having the        |

| 4  | semiconductor device of embodiment 1 shown in FIG. 1 mounted on a printed wiring board.         |

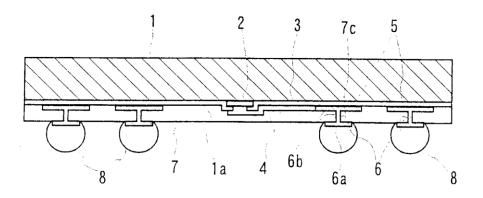

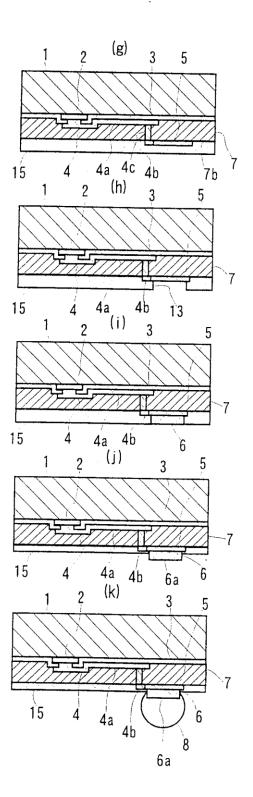

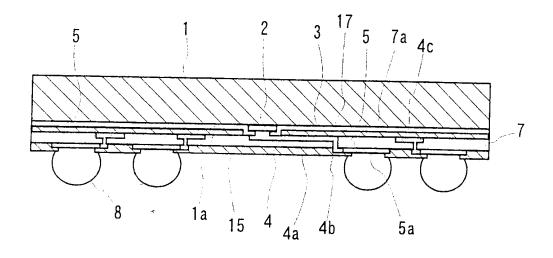

| 5  | FIG. 5 is a cross-sectional drawing that shows embodiment 2 of the semiconductor device of the  |

| 6  | present invention.                                                                              |

| 7  | FIG. 6 is a partial cross-sectional drawing that describes the manufacturing method of the      |

| 8  | semiconductor device based on embodiment 2 shown in FIG. 5.                                     |

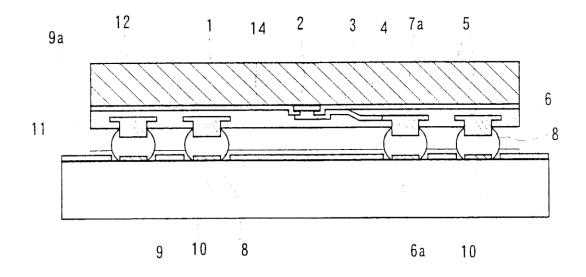

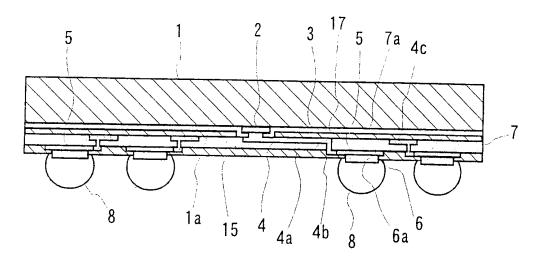

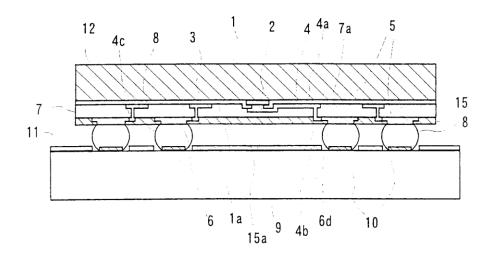

| 9  | FIG. 7 is a cross-sectional drawing that shows embodiment 3 of the semiconductor device of the  |

| 10 | present invention.                                                                              |

| 11 | FIG. 8 is a cross-sectional view of a semiconductor module having the semiconductor device of   |

| 12 | embodiment 3 shown in FIG. 7 mounted on a printed wiring board.                                 |

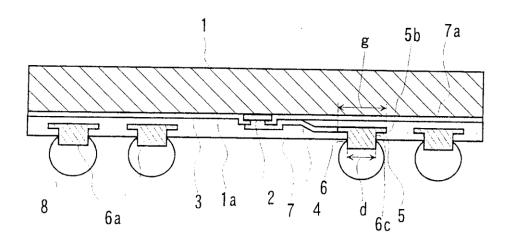

| 13 | FIG. 9 is a cross-sectional drawing that shows embodiment 4 of the semiconductor device of the  |

| 14 | present invention.                                                                              |

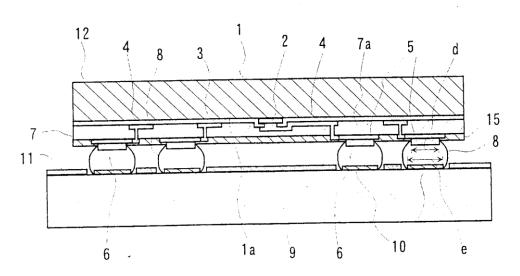

| 15 | FIG. 10 is a cross-sectional view of a semiconductor module having the semiconductor device of  |

| 16 | embodiment 4 shown in FIG. 9 mounted on a printed wiring board.                                 |

| 17 | FIG. 11 is a partial cross-sectional drawing that describes the manufacturing method of the     |

| 18 | semiconductor device based on embodiment 4 shown in FIG. 9.                                     |

| 19 | FIG. 12 is a cross-sectional view of another example of a semiconductor module having the       |

| 20 | semiconductor device of embodiment 4 shown in FIG. 9 mounted on a printed circuit board.        |

| 21 | FIG. 13 is a cross-sectional view showing still another example.                                |

| 22 | FIG. 14 is a cross-sectional drawing showing another example of the semiconductor device of the |

| 23 | present invention shown in FIG. 9.                                                              |

| 24 | FIG. 15 is a cross-sectional view of a semiconductor device according to the present invention  |

| 25 | that explains the relationship between land size and projection size.                           |

| 26 |                                                                                                 |

| 27 | FIG. 16 is a cross-sectional view describing an example of a semiconductor device formed with a |

| 28 | pad near the end of a semiconductor element.                                                    |

| 29 | FIG. 17 is a cross-sectional view showing another example of a semiconductor device based on    |

| 30 | embodiment 4 shown in FIG. 9.                                                                   |

| 31 |                                                                                                 |

| 32 |                                                                                                 |

| 33 | PREFERRED EMBODIMENT OF THE INVENTION                                                           |

| 34 | The present invention will be described in detail in accordance with the drawings attached.     |

| 35 | FIG. 1 is a cross-sectional drawing that shows embodiment 1 of the semiconductor device of the  |

| 36 | present invention.                                                                              |

In addition, FIG. 2 is a plan view of the semiconductor shown in FIG. 1 with a part of the

protective film removed. Note, the cross section drawing of FIG. 1 shows the cross section of the A-A

cross section position shown in FIG. 2.

4 5

As shown in FIG. 1 and FIG. 2

6 the semiconductor device of embodiment 1 of the present invention comprises a

7 semiconductor element 1, a passivation film 3 formed so the surface of a pad 2 on the

8 semiconductor device surface 1a is exposed, a conductive wire line 4 connected to the pad 2, a land

9 5 connected to the conductive wire line 4, a protective film 7, a protrusion 6 provided on the land 5,

10 and an external terminal 8.

The pad 2 is arranged vertically in the center of the semiconductor element surface and the 11 12 conductive wire line 4 connected to the pad 2 extends to the land 5 on which the protrusion 6 is 13 formed on the semiconductor element surface 1a. The protective film 7 covers a part of the 14 passivation film 3, conductive wire line 4, land 5, and protrusion 6 on the semiconductor element 15 surface 1a and is also provided between the land 5 and passivation film 3 and forms the intervening 16 portion 7a of the protective film. A part of the protrusion 6 protrudes through the protective film 7 17 and this protruding part 6a is bonded to the external terminal 8. The pad 2 of the semiconductor 18 element 1 and external terminal 8 are electrically connected via the conductive wire line 4, land 5, 19 and protrusion 6. 20 The conductive wire line 4 is made up of a single or alloy of a plurality of materials out of copper 21 (Cu), aluminum (Al), gold (Au), or silver (Ag) or the like. In addition, there are also cases where a 22 plating of nickel (Ni) or chromium (Cr) is applied to the surface. The land 5 connected to the 23 conductive wire line 4 is also formed of the same material as the conductive wire described above. 24 Solder material (for example Pb-Sn system eutectic solder or sn-Ag-Cu system solder) or the like 25 is used where a spherical shaped piece of material or paste type solder material is placed on 26 protruding part of the protrusion where it is melted and bonded to the land. Examples of materials 27 that can be used for the protective film 7 include liquid or film type polyamide resin, polyether imide 28 resin, acrylic denatured epoxy resin, epoxy resin mixed with rubber, or silicon resin or the like. 29 The elastic modulus of the material used for the conductive wire line 4 and land 5 is, for 30 example, roughly 110 GPa for copper (Cu).

The elastic modulus of the material used for the protective film, for example polyimide resin at

room temperature is roughly 1 to 9 GPa so the elastic modulus of the material that forms the

protective film 7 is smaller than that for the land 5. Note, the elastic modulus of the protective film

can be further reduced depending on the material selected.

5 According to the semiconductor device of the first embodiment described above, the external 6 terminal 8 is bonded to the protruded part 6a of the protrusion 6 formed on the land 5. Therefore, if 7 there is a temperature change applied while the semiconductor device is mounted to a printed 8 wiring board, the deformation of the external terminal 8 in the bond area of the protrusion 6 and 9 external terminal 8 on the semiconductor device side is restrained by the protrusion 6 enabling 10 reducing the amount of deformation. Thus, the thermal distortion that occurs on the external 11 terminal 8 near the bond on the semiconductor device side can be reduced.

12

13 Further, the intervening portion 7a of the protective film 7 is provided between the land 5 and 14 the passivation film 3 on the semiconductor element surface 1a. Therefore, the deformation 15 generated on the external terminal 8 by the difference between the coefficient of linear expansion 16 between the semiconductor device and printed wiring board trace can be mitigated by deformation 17 of the intervening member 7a of the protective film that is less elastic than the material that makes 18 up the land 5. Furthermore, the strain generated in the semiconductor device and printed wiring 19 board bond parts can be reduced. Thus, even if there is a temperature change in the condition the 20 semiconductor device is mounted on a printed wiring board, disconnection defects that occur in the 21 bond part of the external terminal can be prevented, enabling realization of a semiconductor device 22 and a semiconductor module with high reliability. Still further, with the semiconductor device of 23 embodiment 1 of the present invention, the conductive wire line 4 is formed on the semiconductor 24 element surface 1a and the projection 6 and external terminal 8 are connected on the land 5 25 provided at a location separated from pad 2 enabling elongation of the distance from the external 26 terminal 8 to the pad 2. Therefore, even if there is intrusion of water inside the semiconductor 27 device from the bonding area of the external terminal 8, this can be prevented from intruding into 28 the pad 2 enabling suppression of electrical conduction defects due to corrosion of the pad. Also, 29 since the land 5 bonded to the external terminal 8 is formed in a location separated from the top of 30 pad 2, the size of the land 5 can be made larger than that of the pad 2 enabling enlarging the 31 bonding area between the external terminal 8 and land 5 or in other words the protrusion 6 shown 32 in this embodiment. As the bonding surface area is increased, strain generated in the external 33 terminal bond part due to a difference in the coefficients of linear thermal expansion between the 34 semiconductor device and printed wiring board acts on a large bonding surface area effectively reducing the strain at the edge of bond part where forming of a crack would start. 35 36

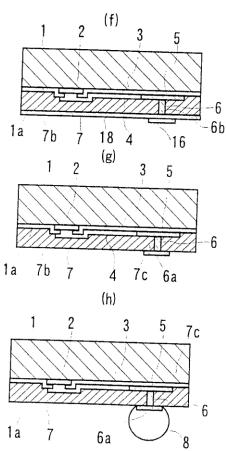

1 Bonding between the external terminal 8 and the protruding part 6a of the protrusion 6 formed 2 on the land 5 is performed by melting solder material used as the material for the external terminal 8. In order to improve bonding between the protrusion 6 and external terminal 8, a metal thin film 3 4 can be plated on the protruding part 6a in the bond location of the protrusion 6. The material used 5 for the metal thin film can be gold (Au) or nickel (Ni) or the like. 6 FIG. 2 is a cross-sectional drawing that describes the manufacturing method of the 7 semiconductor device of embodiment 1 of the present invention shown in FIG. 1. 8 The protective film 7 of polyamide resin or the like is formed on the pad 2 and the surface 1a (a) 9 of the semiconductor element 1 formed with a passivation film 3 formed covering the 10 semiconductor element surface 1a with a part of the pad 2 exposed using a potting method, printing 11 method, or pasting of a film type material (b) or the like. The conductive wire line 3 [sic] is formed 12 through the surface of the protective film 7 while in addition, the land 5 is provided on the surface of 13 the protective film 7 (c). The conductive wire lines 3 [sic] are formed using a plating method or 14 sputtering method. The protective film 7 provided on top of the semiconductor element surface 1a 15 is between the land 5 and semiconductor element surface 1a becoming the intervening part 7a of 16 the protective film. Furthermore, the protective film 7 is formed so as to cover the conductive wire 17 line 4 and land 5 on the surface of the semiconductor element 1a (d). An opening 13 is formed on 18 the surface 7b of the protective film 7 exposing the surface of the land 5 (e). The opening 13 is 19 formed by masking the area where the opening is not formed, forming the opening using an etching 20 method, and then removing the mask or using a hole forming method using a laser. 21 The opening 13 is filled with a metal material such as copper (Cu) using a sputter method or 22 plating method to form a protrusion 6 on the land 5 (f). The protective film 7 is removed from the 23 surface 7b using etching, the protruding part 6a is formed such that a part of the protrusion 6 is 24 caused to protrude from the surface 7a of the protective film 7 (9). The protruding part 6a of the 25 protrusion 6 is bonded to the external terminal 8 made up of solder material (h). This is cut to 26 prescribed size to obtain the semiconductor device shown in embodiment 1 of the present 27 invention. 28 The manufacturing method of the semiconductor device for the invention shown in FIG. 2 is the 29 same manufacturing method used to manufacture the semiconductor element as a wafer. 30 Note, materials described above with elastic modulus are selected depending on the size of the 31 semiconductor element and number of terminal devices and terminals of the external terminals; 32 however, to improve the mitigation effect of strain generated in bonds due to deformation of the 33 intervening portion 7a of the protective film, a material with a small elastic modulus, preferably in 34 the range of 0.5 to 3 GPa should be used.

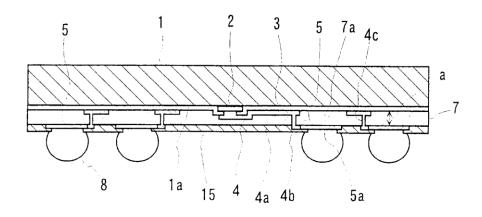

1 Furthermore, it preferably should have the elastic modulus at low temperatures (roughly -50 °C). 2 In addition, achieving the strain reduction effect requires ensuring of a certain level of thickness a of the intervening portion 7a shown in FIG. 1 (a). The thickness of the intervening portion 7a of the 3 4 protective film interposed between the land 5 and passivation film is preferably changed depending 5 on the elastic modulus of the material used for the protective film 7 where the thickness of the 6 intervening portion 7a needs to be increased as the elastic modulus of the protective film 7 gets 7 larger. For example, if polyamide resin described above is used as the protective film 7, a material 8 with an elastic modulus of roughly 1 GPa to 3 GPa is preferably selected from among the polyamide 9 resins and in this case, the thickness of the intervening portion 7a is preferably set to 20 µm or 10 more. 11 The protective film 7 may be made of single material or may have a lamination structure made 12 of a plurality of materials. In this case, the elastic modulus value is preferably still within the range 13 described above (0.5 GPa to 3 GPa) for the overall protective film. 14 FIG. 3 is a cross-sectional view that shows embodiment 1 of the semiconductor module

according to the present invention with the semiconductor device in embodiment 1 shown in FIG. 1mounted on a printed wiring board.

17 The semiconductor device 12 shown in FIG. 3 is connected to the bonding pad 10 and external 18 terminal 8 provided on the surface of the printed wiring board 9 with the flat surface side on which 19 the external terminal 8 is provided facing the printed wiring board 9 and is thus mechanically and 20 electrically connected to the printed wiring board. On parts of the surface of the printed wiring 21 board 9 where bonding pads 10 are not formed, a resist film 11 is formed in order to protect internal 22 wiring (not shown) of the printed wiring board 9. 23 The printed wiring board 9 is typically a glass/epoxy board (e.g., FR-4) made of epoxy resin as a 24 base material mixed with glass cloth and boards that use BT resin or aramid resin and the like in 25 place of epoxy resin are also used. 26 With the height of the protruding part 6a connected to the external terminal 8 of the protrusion

27 6 provided on the land 5 shown in FIG. 3 as b and the height of the bonding pad 10 of the printed

wiring board 9 bonded to the external terminal 8 as C, it is preferable for  $b \ge C$  for the

29 semiconductor device of embodiment 1.

As with the semiconductor device of the embodiment 1 of the present invention, a part of the protrusion 6 provided on the land 5 protrudes into the external terminal 8 and is bonded enabling reduction of strain generated in this part. Similarly, the bonding pad 10 in the bonding area of the printed wiring board 9 side protrudes into and is bonded in the external terminal 8 enabling reduction of strain generated in the bond.

6 In the case that a semiconductor device without a protrusion 6 or protective film formed on the 7 land 5 shown in FIG. 1 is mounted on a printed wiring board, since the linear expansion coefficient of 8 the printed wiring board is close to the linear expansion coefficient of the solder material used for 9 the external terminal 8 and the printed wiring board has lower elasticity semiconductor device 10 primarily occupied by the semiconductor element 1, the strain generated in the bond of the external 11 terminal of the printed wiring board is less than the strain generated on the semiconductor device 12 side. In the semiconductor device of embodiment 1 described above, the protrusion 6 formed on the 13 land 5 is bonded to the external terminal 8 raising the rigidity in the bond part and enabling reducing 14 strain generated in the bond part of the semiconductor device side. In addition, the difference 15 between strains generated at the bonds of both of the semiconductor device and printed wiring 16 board can be reduced. However, in the bond part of the printed wiring board side, if the height c of 17 the bonding pad 10 bonded inside the external terminal 8 is enlarged, the strain in the bond part of 18 the printed wiring board side is reduced but strain in the bond part on the semiconductor device 19 side increases correspondingly Therefore, if the height b of the protruding part 6a is set equal to or 20 larger than the height c of the bonding pad 10 of the printed wiring board 9 bonded to the external 21 terminal 8, the difference in strains generated in both the bond parts can be reduced, and reliability 22 can be improved overall. 23 Furthermore, in embodiment 1 of the semiconductor module according to the present 24 invention, the bond surface area between the bonding pad 10 of the printed wiring board 9 and the 25 external terminal 8 in the horizontal direction, in other words the external terminal arrangement 26 direction, is preferably set larger than the bond surface area between the protruding part 6a of the 27 protrusion 6 provided on the land 5 of the semiconductor device 12 bonded to the external terminal 28 8. In this embodiment, the plan view shape of the protrusion 6 and bonding pad 10 is circular. In 29 order to increase the size of bond surface area on the printed wiring board side beyond that on the 30 semiconductor device side, with the protruding part 6a of the protrusion 6 as d and the diameter of 31 the bonding pad of the printed wiring board 9 as e, the relation e>d needs to be true.

1 By setting the bond surface area on the printed wiring board side broader than on the 2 semiconductor device side, the rigidity of the bonding pad 10 increases so that it is possible to reduce the strain generated in the bond part of the external terminal on the printed wiring board 3 4 side. It is also possible to reduce the difference between the strain generated in the bond part of the 5 external terminal on the printed wiring board side and the strain generated in the external terminal 6 bonding part of the semiconductor device side reduced through the bonding with the protruding 7 part 6a of the protrusion 6. Thus, even if a temperature change is applied, disconnection defects 8 generated in the bond parts of the external terminal on both sides of the semiconductor device and 9 printed wiring board can be prevented, and a semiconductor module having a high reliability as a 10 whole can be realized. 11 FIG. 4 is a cross-sectional view of another example of a semiconductor module having the 12 semiconductor device shown in FIG. 1 mounted on a printed wiring board. 13 With the semiconductor module shown in FIG. 4, on a semiconductor device mount surface 9a 14 of a printed wiring board 9, a reinforcement resin 14 is provided covering at least the periphery of 15 the bond part of the external terminal 8 and bonding pad 10. 16 The reinforcement resin 14 may be made of epoxy resin, epoxy resin filled with silica particles, or 17 the like. The reinforcement resin 14 is formed by mounting a semiconductor device 12 on the 18 printed wiring board 9, thereafter flowing liquid resin on the printed wiring board surface 9a, and 19 heating and hardening it. By covering the bond part between the bonding pad 10 of the printed 20 wiring board 9 and the external terminal 8 with reinforcement resin 14, strain generated in the bond 21 part of the external terminal on the printed wiring board side can be mitigated. As strain in the bond 22 part of the external terminal on the printed wiring board side is reduced, the difference between the 23 strain generated in the bond part between the protruding part 6a of the protrusion 6 and the 24 external terminal 8 and the strain generated in the external terminal bond of the semiconductor 25 device reduced by the forming of an intervening part 7a of the protective film is eliminated making it 26 possible to reduce strain generated in the external terminal bond part of the semiconductor device 27 as a whole. 28 FIG. 5 is a cross-sectional drawing that shows embodiment 2 of the semiconductor device of the 29 present invention. 30 The fundamental structure of the semiconductor device embodiment 2 of the present invention 31 shown in FIG. 5 is similar to the embodiment 1 shown in FIG. 1. A point of difference from the 32 embodiment 1 is that a part 6b of the protrusion 6 surrounded by protective film 7 is narrower than the protruding part 6a bonded to the external terminal 8 so that an intervening part 7c of the 33 34 protective film 7 is formed in the plane of projection of the protruding part 6a of the protrusion 6.

1 With the semiconductor device of embodiment 2 of the present invention, an intervening 2 portion 7c of the protective film 7 is provided on the plane of projection of the protruding part 6a. Therefore, the deformation generated on the external terminal 8 by the difference between the 3 4 coefficient of linear expansion between the semiconductor device and printed wiring board trace 5 can be mitigated by deformation of the intervening member 7c of the protective film 7 that is less 6 elastic than the material that makes up the land 5. Furthermore, the strain generated in both the 7 semiconductor device and printed wiring board bond parts can be reduced. 8 FIG. 6 is a cross-sectional drawing that describes the manufacturing method of the 9 semiconductor device of embodiment 2 of the present invention shown in FIG. 5. 10 A conductive wire line 4 is formed on the pad 2 and on the semiconductor element 1 surface 1a 11 on which a passivation film 3 is formed covering the semiconductor element surface 1a partially 12 exposing the pad 2 from the pad 2 to the surface of the protective film 7 (a) using a plating method 13 or sputtering method and the land 5 is provided on the surface of the protective film 7 at the same 14 time (b). A protective film 7 is formed covering the conductive wire line 4, land 5 and passivation film 15 3 using a potting method, a printing method or an attachment method (c). Furthermore, an opening 16 13 is formed in the surface 7b of the protective film 7 exposing the surface of the land 5 using a laser 17 beam or etching or the like (d). Metal material 18 such as copper (Cu) is formed in the opening 13 18 and on the surface 7b of the protective film 7 using a sputtering method or a plating method (e) and 19 the metal material in the opening 13 makes up the protrusion 6. A resist film 16 is formed on the 20 surface 7b of the protective film 7 (f) and unnecessary metal material 18 is removed to form a 21 protruding part 6a of the protrusion 6 (g). The protruding part 6a is formed larger in the horizontal 22 direction than the protruding part 6b covered with the protective film 7, so that an intervening 23 portion 7c of the protective film is formed between the protruding part 6a and the semiconductor 24 element surface 1a. The protruding part 6a of the protrusion 6 is bonded to an external terminal 8 25 (h) and then cut to a prescribed size to form the semiconductor device shown as embodiment 2 of 26 the present invention. 27 The manufacturing method of the semiconductor device for the invention shown in FIG. 6 is the 28 same manufacturing method used to manufacture the semiconductor element as a wafer. 29 FIG. 7 is a cross-sectional view showing a semiconductor device according to embodiment 3 of

30 the present invention.

31

SAMSUNG EXHIBIT 1011 Samsung v. Tessera

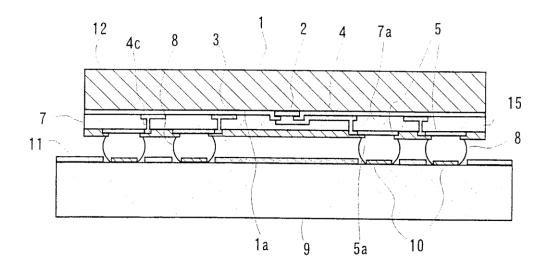

1 As shown in FIG. 7, the semiconductor device of embodiment 3 of the present invention 2 comprises a semiconductor element 1, a passivation film 3 formed so the surface of a pad 2 on the semiconductor device surface 1a is exposed, a conductive wire line 4 connected to the pad 2, a land 3 4 5 contiguous with the conductive wire line 4, a first protective film 7, a second protective film 15, 5 and an external terminal 8. 6 The pad 2 is arranged in the central part of the semiconductor element surface 1a and the 7 conductive wire line 4 is connected to the pad 2. The conductive wire line 4 connected to the pad 2 8 comprises a first conductive wire line 4a arranged on the semiconductor element surface 1a and a 9 second conductive wire line 4b connected to the land 5. The first protective film 7 is provided on the 10 semiconductor element surface 1a, covering the passivation film 3, the first conductive wire line 4a, 11 and a part of the second conductive wire line 4b. The second protective film 15 covers the second 12 conductive wire line 4b and the land 5 except the external terminal bond surface 5a. The first 13 conductive wire line 4a and second conductive wire line 4b are arranged in a lamination structure via 14 the first protective film 7. An intervening part 7a of the first protective film is formed between the 15 land 5 contiguous with the second conductive wire line and the passivation film 3. The external 16 terminal 8 is connected to the external terminal bond surface 5a of the land. 17 The pad 2 of the semiconductor element 1 and external terminal 8 are electrically connected via 18 the conductive wire line 4 and land 5. The first conductive wire line 4a and second conductive wire 19 line 4b are electrically connected by a vertical wire line 4c which is part of the second conductive 20 wire line 4b and is formed extending in the thickness direction of the first protective film 7. 21 Examples of materials that can be used for the first protective film 7 include liquid or film type 22 polyamide resin, polyether imide resin, acrylic denatured epoxy resin, epoxy resin mixed with 23 rubber, or silicon resin or the like. 24 The material of the second protective film 15 can be a liquid or film type polyimide resin, epoxy 25 resin, or epoxy resin mixed with filler such as glass, or the like. 26 The elastic modulus of the material used for the conductive wire line 4 and land 5 is, for 27 example, roughly 110 GPa for copper (Cu). The elastic modulus of the material used for the first 28 protective film 7, for example polyimide resin at room temperature is roughly 1 to 9 GPa so the 29 elastic modulus of the material that forms the first protective film 7 is smaller than that for the land 30 5. The elastic modulus of the first protective film 7 may be set even smaller depending on selection

- 31 of material.

- 32

| 1  | FIG. 8 is a cross-sectional view of a semiconductor module having the semiconductor device of           |

|----|---------------------------------------------------------------------------------------------------------|

| 2  | embodiment 3 shown in FIG. 7 mounted on a printed wiring board.                                         |

| 3  | The semiconductor device 12 shown in FIG. 7 is connected to the bonding pad 10 and external             |

| 4  | terminal 8 provided on the surface of the printed wiring board 9 with the flat surface side on which    |

| 5  | the external terminal 8 is provided facing the printed wiring board 9 and is thus mechanically and      |

| 6  | electrically connected to the printed wiring board.                                                     |

| 7  | As described above, with the semiconductor device of embodiment 3 of the present invention,             |

| 8  | the first conductive wire line 4a and second conductive wire line 4b are arranged in a lamination       |

| 9  | structure so that the intervening portion 7a of the first protective film 7 can be formed between the   |

| 10 | land 5 and the passivation film 3 on the semiconductor element surface 1a. Therefore, the               |

| 11 | deformation generated on the external terminal 8 due to the difference between the coefficient of       |

| 12 | linear expansion between the semiconductor device and printed wiring board trace can be mitigated       |

| 13 | by deformation of the intervening member 7a of the protective film that is less elastic than the        |

| 14 | material that makes up the land 5. Furthermore, the strain generated in the semiconductor device        |

| 15 | and printed wiring board bond parts can be reduced.                                                     |

| 16 | Thus, even if there is a temperature change in the condition the semiconductor device is                |

| 17 | mounted on a printed wiring board, disconnection defects that occur in the bond part of the             |

| 18 | external terminal can be prevented, enabling realization of a semiconductor device and a                |

| 19 | semiconductor module with high reliability.                                                             |

| 20 | In order to reduce thermal strain generated in the external terminal 8, material having a               |

| 21 | relatively low elastic modulus is selected from the materials described above as the material of the    |

| 22 | first protective film 7. On the other hand, it is preferable that the second protective film 15 is made |

| 23 | of a material having an elastic modulus higher than that of the material that makes up the first        |

| 24 | protective film 7.                                                                                      |

| 25 | There is a general tendency that the coefficient of linear expansion of resin material increases as     |

| 26 | the elastic modulus decreases. As the semiconductor device shown in FIG. 7 is subjected to a            |

| 27 | temperature change, deformation of the first protective film 7 having a lower elastic modulus occurs    |

| 28 | through contraction and expansion. Due to this deformation, deformation may also occur in the           |

| 29 | conductive wire line 4 in contact with the first protective film 7 and disconnection may occur at the   |

| 30 | bond of the conductive wire line 4 and pad 2 and at a flexure point of the conductive wire line 4. If   |

| 31 | the second protective film 15 in contact with the upper part of the conductive wire line 4 is made of   |

| 32 | material having an elastic modulus higher than that of the material of the first protective film 7,     |

| 33 | restraining of deformation of the conductive wire line 4 due to the second protective film 15           |

| 34 | increases so that the amount of deformation of the conductive wire line 4 can be reduced and            |

| 35 | disconnection can be prevented.                                                                         |

| 20 |                                                                                                         |

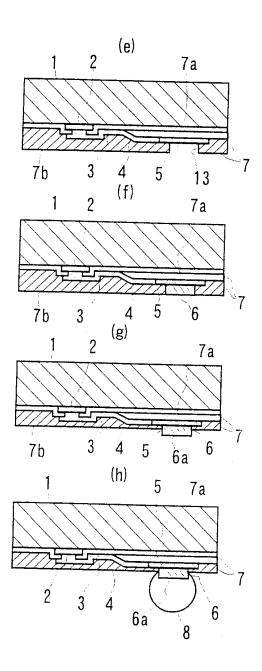

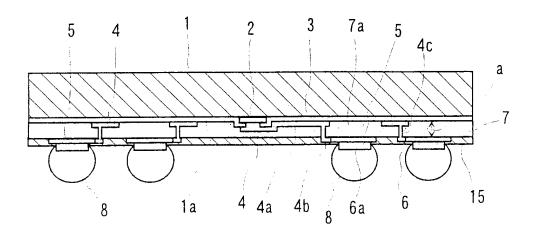

1 FIG. 9 is a cross-sectional drawing that shows embodiment 4 of the semiconductor device of the 2 present invention. In FIG. 9, the structure of the semiconductor device is basically the same as the semiconductor 3 4 device of embodiment 3 shown in FIG. 7 and a point of difference is that a protrusion 6 is formed on 5 a land 5 and a protrusion part 6a protruding from the second protective film 15 is bonded to the 6 external terminal 8. 7 FIG. 10 is a cross-sectional view of a semiconductor module having the semiconductor device of 8 embodiment 4 shown in FIG. 9 mounted on a printed wiring board. 9 The semiconductor device 12 shown in FIG. 10 is connected to the bonding pad 10 and external 10 terminal 8 provided on the surface of the printed wiring board 9 with the flat surface side on which 11 the external terminal 8 is provided facing the printed wiring board 9 and is thus mechanically and 12 electrically connected to the printed wiring board. 13 As described above, the external terminal 8 is bonded to the protruded part 6a of the protrusion 14 6 formed on the land 5. Therefore, if there is a temperature change applied while the semiconductor 15 device is mounted to a printed wiring board, the deformation of the external terminal 8 near the 16 bond area of the protrusion 6 and external terminal 8 on the semiconductor device side is restrained 17 by the protrusion 6 enabling reducing the amount of deformation. Thus, the thermal distortion that 18 occurs on the external terminal 8 near the bond on the semiconductor device side can be reduced. 19 FIG. 11 is a cross-sectional drawing that describes the manufacturing method of the 20 semiconductor device of embodiment 4 of the present invention shown in FIG. 9. Note, the 21 semiconductor device of embodiment 3 of the present invention, shown in FIG. 7, can also be 22 manufactured using the method shown in FIG. 11 by omitting the process of forming the protrusion 23 6. 24 A first conductive wire line 4a connected to pad 2 is formed on the pad 2 and on the 25 semiconductor element 1 surface 1a on which a passivation film 3 is formed covering the 26 semiconductor element surface 1a partially exposing the pad 2 (a) using a plating method or 27 sputtering method (b). A first protective film 7 is formed covering the first conductive wire line 4a 28 and passivation film 3 by a potting method, a printing method or a attachment method (c). An 29 opening 13 is formed from the surface 7b of the first protective film 7 to the surface of the first 30 conductive wire line 4a by using a laser beam or by etching (d). Metal material 18 such as copper 31 (Cu) is formed in the opening 13 and on the surface 7b of the first protective film 7 by a sputtering 32 method or a plating method (e). The metal material in the opening 13 forms a vertical wire line 4c.

1 The unnecessary part of the metal material 18 formed on the surface 7b of the first protective 2 film 7 is removed by etching or the like to form a second conductive wire line 4b and a land 5 (f). A second protective film 15 is formed on the surface 7b of the first protective film 7, covering the 3 4 second conductive wire line 4b and land 5 (g), and an opening 13' is formed in the second protective 5 film 15 to expose an external terminal bond surface 5a of the land 5 (h). Copper (Cu) or the like is 6 filled in this opening 13 to form a protrusion 6 (i), and the surface of the second protective film 15 is 7 shaved by etching or the like to form a protruding part 6a of the protrusion 6 (j). The protruding part 8 6a of the protrusion 6 is bonded to an external terminal 8 (k) and then cutting is performed to a 9 prescribed size to form the semiconductor device of embodiment 4 of the present invention. The 10 semiconductor device manufacture method of this invention described with reference to FIG. 11 is 11 similar to a general method of manufacturing semiconductor devices from a wafer. 12 Note, materials described above with elastic modulus selected for the first protective film 7 13 depending on the size of the semiconductor element and terminal arrangement and number of 14 terminals for the external terminal; however, to improve the mitigation effect of strain generated in 15 bonds due to deformation of the intervening portion 7a of the first protective film 7, a material with 16 a small elastic modulus, preferably in the range of 0.5 to 3 GPa should be used. Furthermore, it preferably should have the elastic modulus at low temperatures (roughly -50 °C). Furthermore, 17 18 achieving the strain reduction effect requires ensuring of a certain level of thickness a of the 19 intervening portion 7a shown in FIG. 7 and FIG. 9. The thickness of the intervening portion 7a of the 20 first protective film interposed between the land 5 and passivation film is preferably changed depending on the elastic modulus of the material used for the first protective film 7 where the 21 22 thickness of the intervening portion 7a needs to be increased as the elastic modulus of the first 23 protective film 7 gets larger. For example, if polyamide resin described above is used as the first 24 protective film 7, a material with an elastic modulus of roughly 1 GPa to 3 GPa is preferably selected 25 from among the polyamide resins and in this case, the thickness of the intervening portion 7a is preferably set to 20  $\mu$ m or more. The first protective film 7 may be made of single material or may 26 27 have a lamination structure made of a plurality of materials. In this case, the elastic modulus value is 28 preferably still within the range described above (0.5 GPa to 3 GPa) for the overall protective film. 29 FIG. 12 is a cross-sectional view of a semiconductor module having the semiconductor device of 30 embodiment 4 of the present invention shown in FIG. 9 mounted on a printed wiring board. The 31 bond surface area between a bonding pad 10 of a printed wiring board 9 and an external terminal 8 32 in the horizontal direction, in other words in the external terminal arrangement direction, is set 33 larger than the bond surface area between a protruding part 6a of a protrusion 6 on a land 5 of a 34 semiconductor device 12 and the external terminal 8.

35

Page 22 of 44

1 In FIG. 12, the plan view shape of the protrusion 6 and bonding pad 10 is circular. In order to 2 increase the size of bond surface area on the printed wiring board side beyond that on the semiconductor device side, with the protruding part 6a of the protrusion 6 as d and the diameter of 3 4 the bonding pad of the printed wiring board 9 as e, the relation e>d needs to be true. 5 As described above, by setting the bond surface area on the printed wiring board side broader 6 than on the semiconductor device side, the rigidity of the bonding pad 10 increases so that it is 7 possible to reduce the strain generated in the bond part of the external terminal on the printed 8 wiring board side. It is also possible to reduce the difference between the strain generated in the 9 bond part of the external terminal on the printed wiring board side and the strain generated in the 10 external terminal bonding part of the semiconductor device side reduced through the bonding with 11 the protruding part 6a of the protrusion 6. Thus, even if a temperature change is applied, 12 disconnection defects generated in the bond parts of the external terminal on both sides of the 13 semiconductor device and printed wiring board can be prevented, and a semiconductor module 14 having a high reliability as a whole can be realized. 15 FIG. 13 is a cross-sectional view of a semiconductor module having the semiconductor device of 16 embodiment 4 of the present invention shown in FIG. 9 mounted on a printed wiring board. 17 Reinforcement resin 14 is provided on the semiconductor device mounting surface 9a of the printed 18 wiring board 9 covering at least the area around the bond parts of the external terminal 8 and bond 19 pad 10. 20 The reinforcement resin 14 may be made of epoxy resin, epoxy resin filled with silica particles, or 21 the like. The reinforcement resin 14 is formed by mounting a semiconductor device 12 on the 22 printed wiring board 9, and thereafter flowing liquid resin on the printed wiring board surface 9a, 23 followed by heating and hardening it. 24 25 By covering the bond part between the bonding pad 10 of the printed wiring board 9 and the 26 external terminal 8 with the reinforcement resin 14, strain generated in the bond part of the 27 external terminal on the printed wiring board side can be mitigated by the reinforcement resin, thus 28 reducing strain that is generated. 29 As strain in the bond part of the external terminal on the printed wiring board side is reduced, 30 the difference between the strain generated in the bond part between the protruding part 6a of the 31 protrusion 6 and the external terminal 8 and the strain generated in the external terminal bond of 32 the semiconductor device reduced by the forming of an intervening part 7a of the first protective 33 film is eliminated making it possible to reduce strain generated in the external terminal bond part of 34 the semiconductor device as a whole. 35

1 Thus, even if there is a temperature change in the condition the semiconductor device is 2 mounted on a printed wiring board, disconnection defects that occur in the bond part of the 3 external terminal can be prevented, enabling realization of a semiconductor device and a 4 semiconductor module with high reliability.

FIG. 14 is a cross-sectional drawing showing another example of the semiconductor device of the

present invention shown in FIG. 7 and FIG. 9.

The fundamental structure of the semiconductor device shown in FIG. 14 (a) is the same as the

semiconductor device shown in FIG. 7, and the fundamental structure of the semiconductor device

shown in FIG. 14 (b) is the same as the semiconductor device shown in FIG. 9. A point of difference

10 resides in that a third protective film 17 is provided between the passivation film 3 on the

11 semiconductor element surface 1a and the first conductive wire line 4a. The material of the third

12 protective film 17 may be polyimide resin, particularly photosensitive polyimide resin, polyether

13 imide resin, epoxy resin, acrylic denatured epoxy resin, epoxy resin mixed with rubber, silicone resin

14 or the like, of a liquid type or a film type. The third protective film 17 is formed by printing, potting,

15 spin coating, or attachment of a film or the like of the resin material described above.

As shown in FIG. 14, forming the third protective film 17 between the passivation film 3 and first

conductive wire line, enables preventing noise generated by electric capacitance between circuit

18 wire lines not shown in the semiconductor element 1 and the first conductive wire line 4a.

The third protective film 17 is preferably formed thick between the circuit wire line in the semiconductor element 1 and the first conductive wire line 4a in order to reduce electric capacitance. Although it is necessary to determine the thickness of the third protective film 17 based upon the performance of the semiconductor element and the layout of inner circuit wire lines, a thickness of about 10 µm needs to be ensured.

As shown in FIG. 15, with the semiconductor device of the present invention having the land 5 formed on the protrusion 6, if the size g of the land 5 in the horizontal direction is larger than the size d of the protrusion 6, the end 5b of the land 5 is preferably formed protruding outside of the side edge 6c of the protrusion 6.

Although thermal strain generated in the external terminal 8 due to temperature change can be reduced through restraint of the deformation of the external terminal by the protrusion having a large rigidity, deformation generated due to the difference in the coefficients of linear thermal expansion between the semiconductor device and printed wiring board acts upon the protrusion itself. This deformation of the protrusion generates stress at the boundary between the land 5 formed with the protrusion 6 and the protective film 7.

1 The stress is concentrated on particularly the end 5b of the land 5, and a crack in the protective 2 film 7 may start in this area. In order to prevent cracking of the protective film 7, the land end 5b is positioned outside of the protrusion side edge 6c. Therefore, the contact surface area between the 3 4 land 5 and protective film 7 increases so that the stress generated at the boundary therebetween 5 can be distributed over a broad surface area and the stress concentrated at the land end 5b can be 6 mitigated. 7 With the semiconductor devices according to the present invention shown above, embodiments 8 where the pad 2 of the semiconductor element 1 is arranged at the center part of the 9 semiconductor element 1 were shown as examples. The arrangement of the pad 2 of the 10 semiconductor element 1 is not limited to the central area of the semiconductor element 1, but as 11 shown in FIG. 16, they may be arranged near the edges 1b of the semiconductor element. With the 12 semiconductor element shown in FIG. 16, a conductive wire line 4 extends from a pad 2 arranged 13 near the end 1b of the semiconductor element 1 toward the inside of the semiconductor element. A 14 protective film 7 is formed covering the pad 2, passivation film 3 and land 5 contiguous with the 15 conductive wire line 4. A protrusion 6 is formed on the land 5, and an external terminal 8 is bonded 16 to the protruding part 6a of the protrusion 6. 17 The structure in which the pads are provided near the edge 1b of the semiconductor element 1 18 is suitable for the case that the semiconductor device uses a semiconductor element 1 with a 19 relatively large number of input signals. 20 FIG. 17 is a cross-sectional view showing another example of the semiconductor device of 21 embodiment 4 of the present invention shown in FIG. 9, as mounted on a printed wiring board. 22 The fundamental structure of the semiconductor device shown in FIG. 17 is the same as that of 23 the semiconductor device shown in FIG. 9. A point of difference is that the surface 6d of the 24 protrusion 6 formed on the land 5 is flush with the surface 15a of the second protective film 15, and 25 an external terminal 8 is bonded to the surface 6d of the protrusion 6. 26 Also with the structure shown in FIG. 17, even if there is a temperature change under the 27 conditions that the semiconductor device is mounted on a printed wiring board, deformation of the 28 external terminal 8 near the bond part of the external terminal 8 and protrusion 6 on the 29 semiconductor device side is restrained by the protrusion 6 having a large rigidity so that the 30 amount of deformation of the external terminal 8 can be reduced. Thus, the thermal distortion that 31 occurs on the external terminal 8 near the bond on the semiconductor device side can be reduced. 32

1 In order to confirm the thermal strain reduction effects when the external terminal 8 is bonded

2 to the protruding part 6a of the protrusion 6 formed on the land 5 of the semiconductor device,

3 thermal strain was analyzed using a finite element method. The thickness of the protective film 6

4 between the land 5 and semiconductor element surface 1a was set to 5  $\mu$ m, the diameter of the

5 protruding part 6a and the diameter of the bonding pad were set to 250  $\mu$ m, the material of the

6 printed wiring board was epoxy resin (equivalent of FR-4) mixed with glass cloth, and the

7 temperature was changed from 125 °C to -55 °C. As shown in Table 1, the thermal strain generated

8 in the external terminal 8 was reduced to 2.7% by forming the protrusion 6, whereas the thermal

9 strain was 3.4% for the case the protrusion 6 was not formed.

10

11

| Table 1 | L |

|---------|---|

|---------|---|

|                | Maximum strain generated     |  |

|----------------|------------------------------|--|

|                | in the external terminal (%) |  |

| Protrusion     | 2.7                          |  |

| present        | 2.7                          |  |

| Protrusion not | 3.4                          |  |

| present        |                              |  |

12

13 Thermal strain was analyzed using a finite element method by setting the bonding pad size of

14 the printed wiring board for bonding the external terminal 8 larger than the size of the bond part (or

protruding part 6a) on the semiconductor device side for bonding the external terminal 8. The

results are shown in Table 2. If the diameter e of the bonding pad and the diameter d of the bond

17 part on the semiconductor device side are the same and no protrusion 6 is formed, the difference

18 between the strain generated on the printed wiring board side and the strain generated on the

19 semiconductor device side becomes large. If the protrusion 6 is formed and bonded to the external

20 terminal 8 and the diameter e of the bonding pad is set larger than the diameter d of the protrusion

21 part 6a, a difference between the strain generated on the sides of both the printed wiring board and

22 semiconductor device can be reduced.

23

| т | ab | le  | 2 |

|---|----|-----|---|

|   | ab | LC. | ~ |

| Protrusion | Bond pad diameter            | Printed wiring board side   |  |

|------------|------------------------------|-----------------------------|--|

|            | e/semiconductor connecting   | strain/semiconductor device |  |

|            | part (protrusion) diameter d | strain                      |  |

| Not        | 1                            | 0. 72                       |  |

| Present    | 1                            | 1.11                        |  |

| (b = 0.02  | -                            | 1.11                        |  |

| Present    | 1.14                         | 1.02                        |  |

| (b = 0.02  | 1.14                         |                             |  |

24

25

- As described above, according to the semiconductor device and semiconductor module of the present invention, strain generated in the external terminal due to the difference in coefficients of linear thermal expansion between a printed wiring board and the semiconductor device mounted on the printed wiring board can be reduced and disconnection of the external terminal can be prevented. The invention is effective in preventing disconnection of the external terminal of a semiconductor device, particularly, a semiconductor device of a chip size to be manufactured by wafer processes. A small semiconductor device and a semiconductor module having a high reliability

- 8 can therefore be provided.

- 9

1 Claims:

2

1. A semiconductor device comprising a semiconductor substrate on which a pad is formed, a

passivation film formed on the surface of the semiconductor substrate on the side the pad is formed

on, and a land formed on the semiconductor substrate on the side opposite the passivation film via

an insulative film for connecting to external terminals, wherein the pad and land are connected by