# FUNDAMENTALS OF DIGITAL LOGIC WITH VERILOG DESIGN

# **Stephen Brown and Zvonko Vranesic**

Department of Electrical and Computer Engineering University of Toronto

Boston Burr Ridge, IL Dubuque, IA Madison, WI New York San Francisco St. Louis Bangkok Bogotá Caracas Kuala Lumpur Lisbon London Madrid Mexico City Milan Montreal New Delhi Santiago Seoul Singapore Sydney Taipei Toronto

# McGraw-Hill Higher Education 👷

A Division of The McGraw-Hill Companies

### FUNDAMENTALS OF DIGITAL LOGIC WITH VERILOG DESIGN

Published by McGraw-Hill, a business unit of The McGraw-Hill Companies, Inc., 1221 Avenue of the Americas, New York, NY 10020. Copyright © 2003 by The McGraw-Hill Companies, Inc. All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written consent of The McGraw-Hill Companies, Inc., including, but not limited to, in any network or other electronic storage or transmission, or broadcast for distance learning.

Some ancillaries, including electronic and print components, may not be available to customers outside the United States.

This book is printed on acid-free paper.

International

1 2 3 4 5 6 7 8 9 0 QPF/QPF 0 9 8 7 6 5 4 3 2

Domestic

1 2 3 4 5 6 7 8 9 0 QPF/QPF 0 9 8 7 6 5 4 3 2

ISBN 0-07-282315-1 ISBN 0-07-121322-8 (ISE)

Publisher: Elizabeth A. Jones Senior sponsoring editor: Carlise Paulson Administrative assistant: Michaela M. Graham Executive marketing manager: John Wannemacher Senior project manager: Jill R. Peter Production supervisor: Kara Kudronowicz Lead media project manager: Judi David Senior media technology producer: Phillip Meek Coordinator of freelance design: Michelle D. Whitaker Cover designer: Rokusek Design Cover image: Stephen Brown and Zvonko Vranesic Senior photo research coordinator: Lori Hancock Compositor: Techsetters, Inc. Typeface: 10/12 Times Roman Printer: Quebecor World Fairfield, PA

#### Library of Congress Cataloging-in-Publication Data

#### Brown, Stephen D.

Fundamentals of digital logic with Verilog design / Stephen D. Brown, Zvonko G. Vranesic.—1st ed. p. cm. (McGraw-Hill Series in electrical and computer engineering)

Includes index.

ISBN 0-07-282315-1

1. Logic circuits—Design and construction—Data processing. 2. Verilog (Computer hardware description language). 3. Computer-aided design. I. Vranesic, Zvonko G. II. Title. III. Series.

TK7868.L6 B76 2003 621.39′2—dc21

2002071439 CIP

### INTERNATIONAL EDITION ISBN 0-07-121322-8

Copyright © 2003. Exclusive rights by The McGraw-Hill Companies, Inc., for manufacture and export. This book cannot be re-exported from the country to which is is sold by McGraw-Hill. The International Edition is not available in North America.

www.mhhe.com

To Susan and Anne

# **ABOUT THE AUTHORS**

**Stephen Brown** received his B.A.Sc. degree in Electrical Engineering from the University of New Brunswick, Canada, and the M.A.Sc. and Ph.D. degrees in Electrical Engineering from the University of Toronto. He joined the University of Toronto faculty in 1992, where he is now an Associate Professor in the Department of Electrical & Computer Engineering. He is also Director of Software Development at the Altera Toronto Technology Center.

His research interests include field-programmable VLSI technology and computer architecture. He won the Canadian Natural Sciences and Engineering Research Council's 1992 Doctoral Prize for the best Ph.D. thesis in Canada.

He has won four awards for excellence in teaching electrical engineering, computer engineering, and computer science courses. He is a coauthor of two other books: *Fundamentals of Digital Logic with VHDL Design* and *Field-Programmable Gate Arrays*.

**Zvonko Vranesic** received his B.A.Sc., M.A.Sc., and Ph.D. degrees, all in Electrical Engineering, from the University of Toronto. From 1963–1965, he worked as a design engineer with the Northern Electric Co. Ltd. in Bramalea, Ontario. In 1968 he joined the University of Toronto, where he is now a Professor in the Departments of Electrical & Computer Engineering and Computer Science. During the 1978–79 academic year, he was a Senior Visitor at the University of Cambridge, England, and during 1984–85 he was at the University of Paris, 6. From 1995 to 2000 he served as Chair of the Division of Engineering Science at the University of Toronto. He is also involved in research and development at the Altera Toronto Technology Center.

His current research interests include computer architecture, field-programmable VLSI technology, and multiple-valued logic systems.

He is a coauthor of four other books: *Computer Organization*, 5th ed.; *Fundamentals of Digital Logic with VHDL Design; Microcomputer Structures*; and *Field-Programmable Gate Arrays*. In 1990, he received the Wighton Fellowship for "innovative and distinctive contributions to undergraduate laboratory instruction."

He has represented Canada in numerous chess competitions. He holds the title of International Master.

## 6.2 DECODERS

311

$$f = \overline{w}_2 f_{\overline{w}_2} + w_2 f_{w_2}$$

=  $\overline{w}_2 (w_3 + w_1 \overline{w}_4) + w_2 (\overline{w}_1 \overline{w}_3 + \overline{w}_3 w_4)$

Observe that  $f_{\overline{w}_2} = f_{w_2}$ ; hence only two 3-LUTs are needed, as illustrated in Figure 6.14*b*. The LUT on the right implements the two-variable function  $\overline{w}_2 f_{\overline{w}_2} + w_2 \overline{f}_{\overline{w}_2}$ .

Since it is possible to implement any logic function using multiplexers, general-purpose chips exist that contain multiplexers as their basic logic resources. Both Actel Corporation [2] and QuickLogic Corporation [3] offer FPGAs in which the logic block comprises an arrangement of multiplexers. Texas Instruments offers gate array chips that have multiplexerbased logic blocks [4].

# **6.2** Decoders

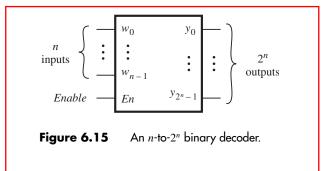

Decoder circuits are used to decode encoded information. A binary decoder, depicted in Figure 6.15, is a logic circuit with *n* inputs and  $2^n$  outputs. Only one output is asserted at a time, and each output corresponds to one valuation of the inputs. The decoder also has an enable input, *En*, that is used to disable the outputs; if En = 0, then none of the decoder outputs is asserted. If En = 1, the valuation of  $w_{n-1} \cdots w_1 w_0$  determines which of the outputs is asserted. An *n*-bit binary code in which exactly one of the bits is set to 1 at a time is referred to as *one-hot encoded*, meaning that the single bit that is set to 1 is deemed to be "hot." The outputs of a binary decoder are one-hot encoded.

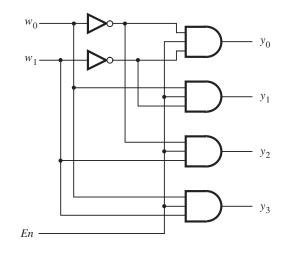

A 2-to-4 decoder is given in Figure 6.16. The two data inputs are  $w_1$  and  $w_0$ . They represent a two-bit number that causes the decoder to assert one of the outputs  $y_0, \ldots, y_3$ . Although a decoder can be designed to have either active-high or active-low outputs, in Figure 6.16 active-high outputs are assumed. Setting the inputs  $w_1w_0$  to 00, 01, 10, or 11 causes the output  $y_0$ ,  $y_1$ ,  $y_2$ , or  $y_3$  to be set to 1, respectively. A graphical symbol for the decoder is given in part (*b*) of the figure, and a logic circuit is shown in part (*c*).

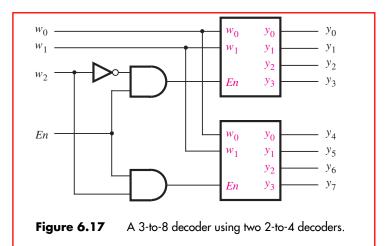

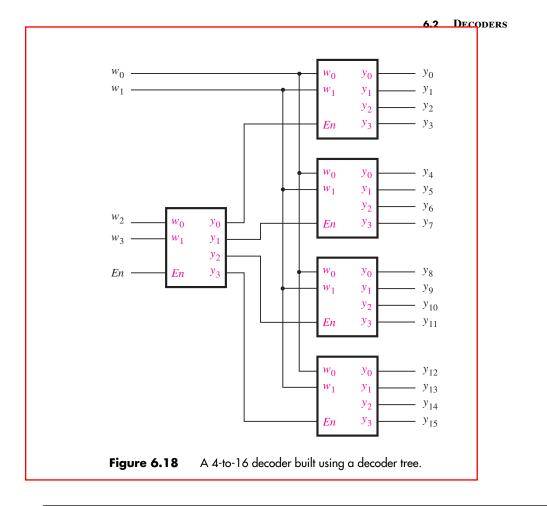

Larger decoders can be built using the sum-of-products structure in Figure 6.16*c*, or else they can be constructed from smaller decoders. Figure 6.17 shows how a 3-to-8 decoder is built with two 2-to-4 decoders. The  $w_2$  input drives the enable inputs of the two decoders. The top decoder is enabled if  $w_2 = 0$ , and the bottom decoder is enabled if  $w_2 = 1$ . This concept can be applied for decoders of any size. Figure 6.18 shows how five 2-to-4 decoders can be used to construct a 4-to-16 decoder. Because of its treelike structure, this type of circuit is often referred to as a *decoder tree*.

#### 312 **COMBINATIONAL-CIRCUIT BUILDING BLOCKS** CHAPTER 6 ٠

| En | $w_1$ | $w_0$ | <i>y</i> <sub>0</sub> | $y_1$ | $y_2$ | $y_3$ |  |                                            |                       |

|----|-------|-------|-----------------------|-------|-------|-------|--|--------------------------------------------|-----------------------|

|    |       |       | 1<br>0<br>0<br>0<br>0 |       |       |       |  | <br>w <sub>0</sub><br>w <sub>1</sub><br>En | $y_0$                 |

| I  | 0     | 0     | 1                     | 0     | 0     | 0     |  | 142                                        | v                     |

| 1  | 0     | 1     | 0                     | 1     | 0     | 0     |  | <i>w</i> 1                                 | <i>y</i> <sub>1</sub> |

| 1  | 1     | 0     | 0                     | 0     | 1     | 0     |  |                                            | $y_2$                 |

| 1  | 1     | 0     | 0                     | 0     | 1     | 0     |  | -                                          |                       |

| 1  | 1     | 1     | 0                     | 0     | 0     | 1     |  | <br>En                                     | <i>y</i> <sub>3</sub> |

| 0  | x     | x     | 0                     | 0     | 0     | 0     |  |                                            |                       |

| 0  | А     |       | Ŭ                     | 0     | 0     | 0     |  |                                            |                       |

|    |       |       |                       |       |       |       |  |                                            |                       |

(c) Logic circuit

Figure 6.16 A 2-to-4 decoder.

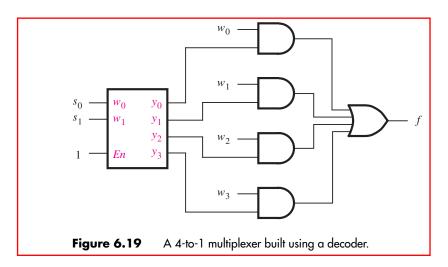

**D**ecoders are useful for many practical purposes. In Figure 6.2*c* we showed the sum-ofproducts implementation of the 4-to-1 multiplexer, which requires AND gates to distinguish the four different valuations of the select inputs  $s_1$  and  $s_0$ . Since a decoder evaluates the values on its inputs, it can be used to build a multiplexer as illustrated in Figure 6.19. The enable input of the decoder is not needed in this case, and it is set to 1. The four outputs of the decoder represent the four valuations of the select inputs.

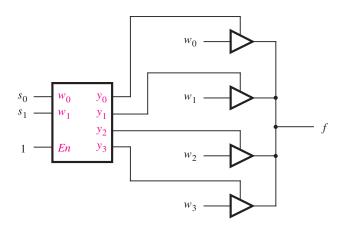

In Figure 3.59 we showed how a 2-to-1 multiplexer can be constructed using two tri-state buffers. This concept can be applied to any size of multiplexer, with the addition of a decoder. An example is shown in Figure 6.20. The decoder enables one of the tri-state buffers for each valuation of the select lines, and that tri-state buffer drives the output, f, with the selected data input. We have now seen that multiplexers can be implemented in various ways. The choice of whether to employ the sum-of-products form, transmission gates, or tri-state buffers depends on the resources available in the chip being used. For

313

# 314 CHAPTER 6 • COMBINATIONAL-CIRCUIT BUILDING BLOCKS

instance, most FPGAs that use lookup tables for their logic blocks do not contain tri-state buffers. Hence multiplexers must be implemented in the sum-of-products form using the lookup tables (see problem 6.15).

# **6.2.1 DEMULTIPLEXERS**

We showed in section 6.1 that a multiplexer has one output, *n* data inputs, and  $\lceil \log_2 n \rceil$  select inputs. The purpose of the multiplexer circuit is to *multiplex* the *n* data inputs onto the single data output under control of the select inputs. A circuit that performs the opposite function, namely, placing the value of a single data input onto multiple data outputs, is

A 4-to-1 multiplexer built using a decoder and tri-state buffers.

#### DECODERS 6.2

called a *demultiplexer*. The demultiplexer can be implemented using a decoder circuit. For example, the 2-to-4 decoder in Figure 6.16 can be used as a 1-to-4 demultiplexer. In this case the En input serves as the data input for the demultiplexer, and the  $y_0$  to  $y_3$  outputs are the data outputs. The valuation of  $w_1w_0$  determines which of the outputs is set to the value of En. To see how the circuit works, consider the truth table in Figure 6.16a. When En = 0, all the outputs are set to 0, including the one selected by the valuation of  $w_1w_0$ . When En = 1, the valuation of  $w_1w_0$  sets the appropriate output to 1.

In general, an *n*-to-2<sup>*n*</sup> decoder circuit can be used as a 1-to-*n* demultiplexer. However, in practice decoder circuits are used much more often as decoders rather than as demultiplexers. In many applications the decoder's En input is not actually needed; hence it can be omitted. In this case the decoder always asserts one of its data outputs,  $y_0, \ldots, y_{2^n-1}$ , according to the valuation of the data inputs,  $w_{n-1} \dots w_0$ . Example 6.11 uses a decoder that does not have the En input.

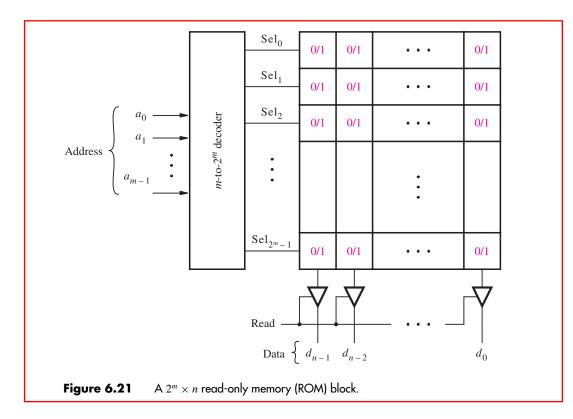

One of the most important applications of decoders is in memory blocks, which are used to store information. Such memory blocks are included in digital systems, such as computers, where there is a need to store large amounts of information electronically. One type of memory block is called a read-only memory (ROM). A ROM consists of a collection of storage cells, where each cell permanently stores a single logic value, either 0 or 1. Figure 6.21 shows an example of a ROM block. The storage cells are arranged in  $2^m$  rows with n

Example 6.11

## 316 CHAPTER 6 • COMBINATIONAL-CIRCUIT BUILDING BLOCKS

cells per row. Thus each row stores *n* bits of information. The location of each row in the ROM is identified by its *address*. In the figure the row at the top of the ROM has address 0, and the row at the bottom has address  $2^m - 1$ . The information stored in the rows can be accessed by asserting the select lines, Sel<sub>0</sub> to Sel<sub>2<sup>m</sup>-1</sub>. As shown in the figure, a decoder with *m* inputs and  $2^m$  outputs is used to generate the signals on the select lines. Since the inputs to the decoder choose the particular address (row) selected, they are called the *address* lines. The information stored in the row appears on the data outputs of the ROM,  $d_{n-1}, \ldots, d_0$ , which are called the *data* lines. Figure 6.21 shows that each data line has an associated tri-state buffer that is enabled by the ROM input named *Read*. To access, or *read*, data from the ROM, the address of the desired row is placed on the address lines and *Read* is set to 1.

Many different types of memory blocks exist. In a ROM the stored information can be read out of the storage cells, but it cannot be changed (see problem 6.31). Another type of ROM allows information to be both read out of the storage cells and stored, or *written*, into them. Reading its contents is the normal operation, whereas writing requires a special procedure. Such a memory block is called a programmable ROM (PROM). The storage cells in a PROM are usually implemented using EEPROM transistors. We discussed EEPROM transistors in section 3.10 to show how they are used in PLDs. Other types of memory blocks are discussed in section 10.1.

# **6.3** Encoders

An encoder performs the opposite function of a decoder. It encodes given information into a more compact form.

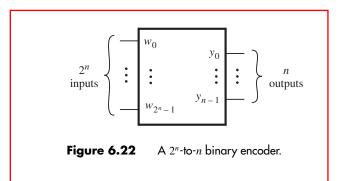

# **6.3.1** BINARY ENCODERS

A *binary encoder* encodes information from  $2^n$  inputs into an *n*-bit code, as indicated in Figure 6.22. Exactly one of the input signals should have a value of 1, and the outputs present the binary number that identifies which input is equal to 1. The truth table for a 4-to-2 encoder is provided in Figure 6.23*a*. Observe that the output  $y_0$  is 1 when either input  $w_1$  or  $w_3$  is 1, and output  $y_1$  is 1 when input  $w_2$  or  $w_3$  is 1. Hence these outputs can be generated by the circuit in Figure 6.23*b*. Note that we assume that the inputs are one-hot