Paper 30 Date: January 9, 2020

# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD INTEL CORPORATION, Petitioner, v. QUALCOMM, INC, Patent Owner. IPR2018-01261¹ Patent 9,535,490 B2

Before DANIEL N. FISHMAN, DANIEL J. GALLIGAN, and AARON W. MOORE, *Administrative Patent Judges*.

FISHMAN, Administrative Patent Judge.

JUDGMENT

Final Written Decision

Determining All Challenged Claims Unpatentable

35 U.S.C. § 318(a)

<sup>&</sup>lt;sup>1</sup> IPR2018-01293, IPR2018-01295, IPR2018-01344, and IPR2018-01346, each directed to claims of this same patent, have been consolidated with the instant proceeding in accord with 37 C.F.R. § 42.122(a).

### I. INTRODUCTION

# A. Background and Summary

Intel Corporation ("Petitioner") requests *inter partes* review of claim 31 of U.S. Patent No. 9,535,490 B2 (the "490 patent," Ex. 1001) pursuant to 35 U.S.C. § 311 *et seq*. Paper 3 ("Petition," "Pet.," or "1261PET"). Qualcomm, Inc. ("Patent Owner") filed a Preliminary Response. Paper 7 ("Prelim. Resp."). On January 15, 2019, based on the record before us at that time, we instituted an *inter partes* review of claim 31 on the sole ground of unpatentability asserted in the Petition. Paper 8 ("Decision on Institution" or "Dec. on Inst.").

Concurrently with the filing of this Petition, Petitioner filed four additional petitions in each of IPR2018-01293, IPR2018-01295, IPR2018-01344, and IPR2018-01346. Each of those four petitions challenge other claims of the '490 patent.<sup>2</sup> Patent Owner filed a Preliminary Response in each of these additional cases presenting similar arguments to those presented in the Preliminary Response in the instant case. The grounds asserted, the references relied upon for those grounds, and the arguments presented, in each of these four additional petitions are similar to those of the instant matter. In each of these four additional, concurrently filed petitions, based on the record before us and for reasons similar to those in the instant case, we instituted review on all asserted grounds for the claims challenged in each petition. In an Order entered January 29, 2019, we consolidated cases IPR2018-01293, IPR2018-01295, IPR2018-01344, and

\_

<sup>&</sup>lt;sup>2</sup> Where all five petitions are substantively the same, we cite only to the petition in the instant case (IPR2018-01261). In like manner, where each of our five Decisions on Institution reaches the same conclusion, we cite only to our Decision on Institution for the instant case (IPR2018-01261).

IPR2018-01346 into the instant case. Paper 10. Having instituted all challenged claims in each of the petitions on all grounds, the consolidated proceeding involves *inter partes* review of claims 1–6, 8, 9, 11–13, 16, 17, 20, 22–24, 26–28, 30, and 31 (the "challenged claims").

In this consolidated proceeding, Patent Owner filed a Patent Owner's Response (Paper 21, "PO Resp."),<sup>3</sup> Petitioner filed a Reply (Paper 20, "Reply"), and Patent Owner filed a Sur-Reply (Paper 23, "Sur-Reply").

Oral argument was held on October 9, 2019 and a transcript of that hearing is in the record. Paper 29 ("Tr.").

Upon consideration of the complete record, we determine by a preponderance of the evidence that claims 1–6, 8, 9, 11–13, 16, 17, 20, 22–24, 26–28, 30, and 31 (all challenged claims) are unpatentable.

### B. Consolidated Papers and Exhibits

The petitions filed in each of the consolidated cases are entered in the record of this case (IPR2018-01261) as exhibits, namely the petition in IPR2018-01293 ("1293PET," Ex. 1028), the petition in IPR2018-01295 ("1295PET," Ex. 1029), the petition in IPR2018-01344 ("1344PET," Ex. 1030), and the petition in IPR2018-01346 ("1346PET," Ex. 1031).

Several exhibits in each of the consolidated cases are identical but are numbered differently in each of the consolidated cases. The parties jointly filed a paper describing the correspondence of the substantively identical exhibits. Paper 13. For example, Exhibit 1001 in this proceeding (IPR2018-

\_

<sup>&</sup>lt;sup>3</sup> Patent Owner filed an earlier Response as Paper 17, which lacked proper page numbering. Patent Owner later filed an authorized, corrected version of its Response as Paper 21 (PO Resp.) with page numbers added and no substantive changes to the arguments. We address Patent Owner's arguments as presented in that corrected Patent Owner Response.

01261), the '490 patent, is identified as Exhibit 1101 in 1293PET, as Exhibit 1201 in 1295PET, as Exhibit 1301 in 1344PET, and as Exhibit 1401 in 1346PET. Paper 13, 1. For all such substantively identical exhibits, despite each consolidated petition referring to its unique exhibit numbers, we refer to the exhibit numbers used in IPR2018-01261 (this proceeding).

Of particular note, Petitioner's expert, Dr. Bill Lin, provides a declaration in each of the five consolidated petitions (Ex. 1002 in IPR2016-01261, Ex. 1102 in IPR2018-01293, Ex. 1202 in IPR2018-01295, Ex. 1302 in IPR2018-01344, and Ex. 1402 in IPR2018-01346). Although much of Dr. Lin's analysis is similar or identical in the five cases, the declarations are not substantively identical (some arguments apply to claims only challenged in the corresponding petition) nor syntactically identical (even for similar arguments, page and paragraph numbers are different). Exhibits 1102, 1202, 1302, and 1402 from these four consolidated proceedings are entered in the record of this consolidated case (IPR2018-01261) as Exhibits 1018, 1019, 1020, and 1021, respectively.

### C. Real Parties in Interest

Petitioner identifies both Intel Corporation and Apple Inc. as real parties in interest. Pet. 1. Patent Owner identifies itself (Qualcomm, Inc.) as the sole real party in interest for Patent Owner. Paper 5, 2.

### D. Related Matters

The parties informed us that the '490 patent is presently asserted against Petitioner in the litigation *Qualcomm Inc. v. Apple Inc.*, Case No. 3:17-cv-01375-DMS-MDD (S.D. Cal.), and against Apple in a proceeding before the International Trade Commission ("ITC") captioned *In the Matter of Certain Mobile Electronic Devices and Radio Frequency Components*Thereof, Inv. No. 337-TA-1065. Pet. 1–2; Paper 5, 2. The ITC investigation

addressed claim 31 of the '490 patent and we find the Commission's final Commission Opinion informative in this Decision. *See* Ex. 1022.

The parties further informed us that the '490 patent is at issue in the above-identified, concurrently filed petitions for *inter partes* review of claims of the '490 patent (i.e., cases IPR2018-01293, IPR2018-01295, IPR2018-01344, and IPR2018-01346). *See* Pet. 2; Paper 5, 2. As noted above, these four related proceedings before the Board have been consolidated into this proceeding.

### E. The '490 Patent

The '490 patent is generally directed to power saving techniques in computing devices. Ex. 1001, code (54), code (57). According to the '490 patent, although stationary desktop computers and servers are generally immune to power consumption issues, "mobile devices constantly struggle to find a proper balance between available functions and battery life." *Id.* at 1:28–31. The '490 patent further indicates that mobile devices utilize internal bus structures to connect components within the mobile device and that increased performance demands have led to use of faster, higher-power-consuming interconnect bus structures within mobile devices (e.g., Peripheral Component Interconnect Express "PCIe" and Universal Serial Bus "USB" 3.0). *Id.* at 1:36–60.

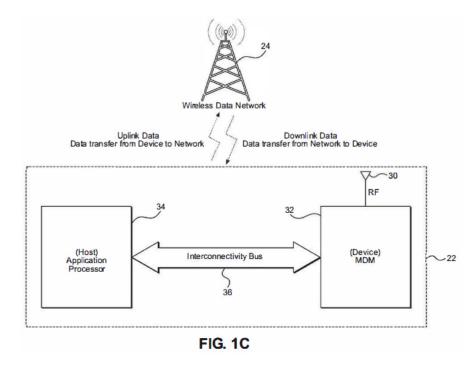

Figure 1C of the '490 patent is reproduced below.

Figure 1C is a block diagram of mobile terminal 22 with interconnectivity bus 36 coupling application processor 34 and modem processor 32. In one embodiment disclosed by the '490 patent, bus 36 may be a PCIe bus. *Id.* at 8:6–9. According to the '490 patent, "[w]hile placing the interconnectivity bus 36 in a sleep mode generally saves power, such sleep modes do have a drawback in that they consume relatively large amounts of power as they transition out of the sleep mode." *Id.* at 8:9–12.

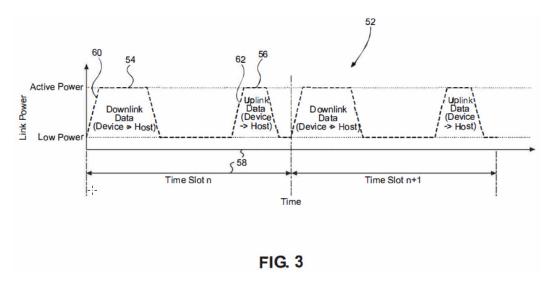

According to the '490 patent, the PCIe bus can be transitioned from a low power state (e.g., saving battery life) to an active state in which information may be exchanged. *Id.* at 8:23–26. Figure 3 of the '490 patent is reproduced below.

Figure 3 depicts graph 52, without the purported improvement of the '490 patent, presenting time on the X-axis versus the power state of a PCIe link on the Y-axis. "Downlink data" refers to data received by the device (i.e., from a connected network) destined for the host/application processor of the device, and "uplink data" refers to data to be sent from the device (i.e., from the host/application processor) to the device (i.e., for transmission to a network). Time is shown as a sequence of time slots 58 (n, n+1, etc.). *Id.* at 8:20–40, Fig. 3. The '490 patent asserts that, as practiced prior to its purported invention, within a given time slot 58, exchange of downlink data 54 requires first transition 60 from a low power state to an active power state and back to a low power state, followed by a similar second transition 62 for exchange of uplink data 54. *Id.* at 8:21–34. According to the '490 patent, where the time slot duration is one millisecond, as is common, there may be thousands of such transitions (60, 62) per second. *Id.* at 8:34–38. Thousands of such transitions per second consume a significant amount of power in a battery powered mobile terminal. *Id.* at 8:38–40.

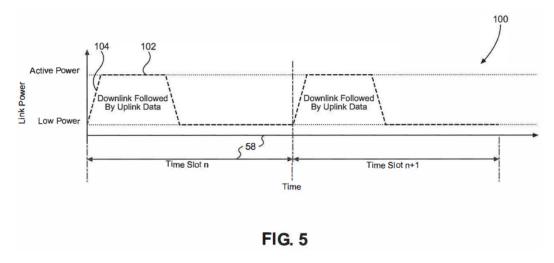

The '490 patent purports to improve battery life by reducing the number of such transitions. *See, e.g., id.* at 5:32–35. Figure 5 of the '490 patent is reproduced below.

Figure 5 depicts graph 100, as purportedly improved by the '490 patent, presenting time on the X-axis versus the power state of a PCIe link on the Y-axis. According to the '490 patent, combining transmission of downlink data and uplink data during a single active power state period 102 requires only one transition 104 from a low power state to an active power state during a time slot 58. *Id.* at 10:36–40. According to the '490 patent, reducing the number of transitions increases the duration of the low power state in each time slot, thus conserving battery power in a mobile terminal. *Id.* at 10:40–45.

The '490 patent proposes a number of structures and techniques within a mobile terminal for combining uplink and downlink transmissions to reduce the number of low power to active power transitions.

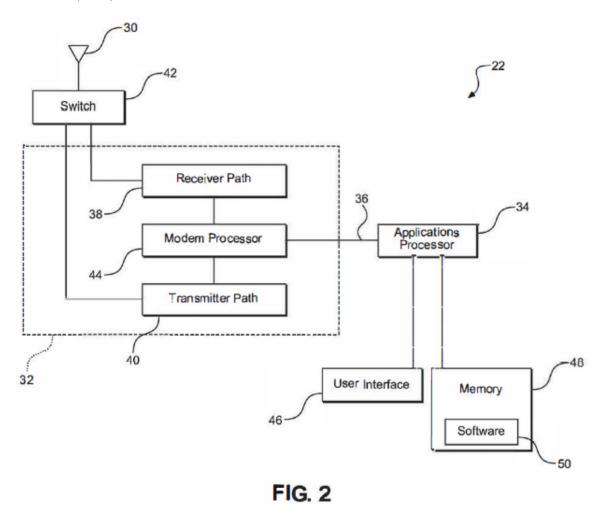

Figure 2 of the '490 patent is reproduced below.

Figure 2 is a block diagram of exemplary mobile terminal 22. Mobile terminal 22 comprises application processor 34 and modem 32. Ex. 1001, 6:58–63, 7:4–12. Modem 32 further comprises modem processor 44, receiver path 38, and transmitter path 40. *Id.* at 6:58–63, 7:7–10. Modem processor 44 and application processor 34 are coupled by interconnectivity bus 36. *Id.* In one embodiment, bus 36 may be a PCIe compliant bus. *Id.* at 6:66–67, 7:14–15. Mobile terminal 22 further comprises a modem timer (not shown). *Id.* at 4:30–31.

In one disclosed embodiment of the '490 patent, the modem processor is configured to hold data it has received that is ready to send to the application processor ("downlink" data) until a programmed time period of

the modem timer expires. *Id.* at 4:32–34. The application processor is configured to hold data it has ready to send to the modem processor ("uplink" data) until the modem processor pulls any held data from the application processor. *Id.* at 4:38–42.

In another disclosed embodiment of the '490 patent, the application processor is configured to hold data it has ready to send to the modem processor ("uplink" data) until downlink data is received at the application processor from the modem processor, which triggers the application processor to send its held data to the modem processor. *Id.* at 2:56–62.

In yet another disclosed embodiment of the '490 patent, the application processor is configured to hold data it has ready to send to the modem processor ("uplink" data) until downlink data is received at the application processor from the modem processor or until a programmed time period of an uplink timer expires, which triggers the application processor to send its held data to the modem processor. *Id.* at 3:2–6.

In other disclosed embodiments of the '490 patent, a variety of threshold measures may be used to override the wait for a timer to expire including, for example, a byte count threshold, a packet size threshold, a packet number threshold, etc. *Id.* at 2:23–34.

### F. Illustrative Claims

Independent claims 1 and 31 are illustrative of the claimed subject matter and are reproduced below.

- 1. A mobile terminal comprising:

- a modem timer;

- a modem processor, the modem processor configured to hold modem processor to application processor data until expiration of the modem timer;

an application processor;

IPR2018-01261 Patent 9,535,490 B2

an interconnectivity bus communicatively coupling the application processor to the modem processor; and

the application processor configured to hold application processor to modem processor data until triggered by receipt of the modem processor to application processor data from the modem processor through the interconnectivity bus after which the application processor to modem processor data is sent to the modem processor through the interconnectivity bus responsive to the receipt of the modem processor to application processor data from the modem processor through the interconnectivity bus.

Ex. 1001, 17:55–18:5.

# 31. A mobile terminal comprising:

a modem timer;

a modem processor, the modem processor configured to hold modem processor to application processor data until expiration of the modem timer;

an application processor;

an interconnectivity bus communicatively coupling the application processor to the modem processor; and

the application processor configured to hold application processor to modem processor data until the modem processor pulls data from the application processor after transmission of the modem processor to application processor data,

wherein the modem processor is further configured pull data from the application processor after transmission of the modem processor to application processor data and before the interconnectivity bus transitions from an active power state to a low power state.

*Id.* at 21:4–21.

### G. Prior Art and Asserted Grounds

Petitioner asserts that claims 1–6, 8, 9, 11–13, 16, 17, 20, 22–24, 26–28, 30, and 31 are unpatentable on the following grounds:

| Claims Challenged                                       | 35 U.S.C. § | References                                          |

|---------------------------------------------------------|-------------|-----------------------------------------------------|

| 1, 4–6, 8, 9, 11–13,<br>16, 20, 22–24, 26–28,<br>30, 31 | 1034        | Heinrich, <sup>5</sup> Balasubramanian <sup>6</sup> |

| 2, 3, 17                                                | 103         | Heinrich, Balasubramanian, Tsai <sup>7</sup>        |

Petitioner relies on the declarations of Bill Lin, Ph.D. (Exs. 1002, 1018–1021, 1023) in support of its assertions. Patent Owner relies on the declaration of R. Jacob Baker, Ph.D. (Ex. 2007).

### II. ANALYSIS

# A. Legal Standards

### 1. Obviousness

A patent claim is unpatentable under 35 U.S.C. § 103 if the differences between the claimed subject matter and the prior art are "such that the subject matter[,] as a whole[,] would have been obvious at the time the invention was made to a person having ordinary skill in the art to which

<sup>&</sup>lt;sup>4</sup> The Leahy-Smith America Invents Act ("AIA") amended 35 U.S.C. § 103. *See* Pub. L. No. 112-29, 125 Stat. 284, 287–88 (2011). Because the application that resulted in the '490 patent was filed after the effective date of the post-AIA amendment, the post-AIA version of § 103 applies. For the same reasons, the post-AIA version of § 102 applies in determining whether the applied references qualify as prior art.

<sup>&</sup>lt;sup>5</sup> Heinrich, US 9,329,671 B2, issued May 3, 2016 (Ex. 1004).

<sup>&</sup>lt;sup>6</sup> Balasubramanian, US 8,160,000 B2, issued Apr. 17, 2012 (Ex. 1005).

<sup>&</sup>lt;sup>7</sup> Tsai, US 8,112,646 B2, issued Feb. 7, 2012 (Ex. 1017).

<sup>&</sup>lt;sup>8</sup> Exhibit 1018 herein is referred to as Exhibit 1002 in 1293PET. Exhibit 1019 herein is referred to as Exhibit 1002 in 1295PET. Exhibit 1020 herein is referred to as Exhibit 1002 in 1344PET. Exhibit 1021 herein is referred to as Exhibit 1002 in 1346PET.

<sup>&</sup>lt;sup>9</sup> Patent Owner filed two exhibits with the exhibit number 2007—Dr. Baker's declaration and a transcript of a hearing before the International Trade Commission ("ITC"). In this decision, we refer to Dr. Baker's declaration as "Ex. 2007" and we do not need to refer to the ITC transcript.

said subject matter pertains." *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 406 (2007). The question of obviousness is resolved based on underlying factual determinations, including (1) the scope and content of the prior art; (2) any differences between the claimed subject matter and the prior art; (3) the level of skill in the art; and (4) objective evidence of non-obviousness, i.e., secondary considerations. *Graham v. John Deere Co.*, 383 U.S. 1, 17–18 (1966).

### B. Level of Ordinary Skill in the Art

Petitioner argues a person of ordinary skill in the art related to the '490 patent would have a Master's degree in electrical engineering, computer engineering, or computer science, and would also have at least two years of experience in "mobile device architecture and multiprocessor systems." Pet. 20. In the alternative, Petitioner argues the ordinarily skilled artisan would have a Bachelor's degree in one of the above-identified programs and at least four years of experience in the above-identified fields. *Id.*

Patent Owner agrees with Petitioner's definition of the level of skill, emphasizing that "relevant experience' in the context of the '490 Patent refers to experience with mobile device architecture and multiprocessor systems." PO Resp. 19.

In our Decision on Institution, we adopted Petitioner's definition of the level of ordinary skill in the art, with the exception of the language "at least," and determined that a person of ordinary skill in the art at the time of the invention of the '490 patent would have had a Master's degree in

<sup>&</sup>lt;sup>10</sup> Patent Owner does not present arguments or evidence of such secondary considerations in its briefs. Therefore, secondary considerations do not enter into our analysis.

electrical engineering, computer engineering, or computer science, and two years of experience in mobile device architecture and multiprocessor systems or, in the alternative, a Bachelor's degree in one of the above-identified programs and four years of experience in the above-identified fields. Dec. on Inst. 9–10. On the complete record, we discern no reason to modify our determination regarding the level of ordinary skill.

### C. Claim Construction

In an *inter partes* review for a Petition filed before November 13, 2018, a claim in an unexpired patent shall be given its broadest reasonable construction in light of the specification of the patent in which it appears. 37 C.F.R. § 42.100(b) (2017); see also Cuozzo Speed Techs., LLC v. Lee, 136 S. Ct. 2131, 2142–46 (2016) (upholding the use of the broadest reasonable interpretation standard ("BRI standard")). Under the BRI standard, claim terms generally are given their ordinary and customary meaning, as would be understood by one of ordinary skill in the art in the context of the entire disclosure. In re Translogic Tech., Inc., 504 F.3d 1249, 1257 (Fed. Cir. 2007). "[A] claim construction analysis must begin and remain centered on the claim language itself . . . . " Innova/Pure Water, Inc. v. Safari Water Filtration Sys., Inc., 381 F.3d 1111, 1116 (Fed. Cir. 2004). "Though understanding the claim language may be aided by the explanations contained in the written description, it is important not to import into a claim limitations that are not a part of the claim." SuperGuide Corp. v. DirecTV Enters., Inc., 358 F.3d 870, 875 (Fed. Cir. 2004).

By contrast, for an expired patent or an unexpired patent challenged in a petition filed on or after November 13, 2018, we apply the principles set forth in *Phillips v. AWH Corp.*, 415 F.3d 1303, 1312–17 (Fed. Cir. 2005) (en

banc) ("Phillips standard"). See 37 C.F.R. § 42.100(b) (2019); Wasica Fin. GmbH v. Cont'l Auto. Sys., Inc., 853 F.3d 1272, 1279 (Fed. Cir. 2017).

Under either standard for claim construction in our proceedings, there is no presumption of validity, and Petitioner's burden of proof is still by a preponderance of the evidence. Moreover, a "claim term will not receive its ordinary meaning if the patentee acted as his own lexicographer and clearly set forth a definition of the disputed claim term in either the specification or prosecution history." *CCS Fitness, Inc. v. Brunswick Corp.*, 288 F.3d 1359, 1366 (Fed. Cir. 2002). Any special definition for a claim term must be set forth in the specification with reasonable clarity, deliberateness, and precision. *In re Paulsen*, 30 F.3d 1475, 1480 (Fed. Cir. 1994). In the absence of such a special definition or other consideration, "limitations are not to be read into the claims from the specification." *In re Van Geuns*, 988 F.2d 1181, 1184 (Fed. Cir. 1993).

Petitioner applies the *Phillips* standard for interpreting terms of the '490 patent but argues "Petitioner is not aware of any difference in how the claims would be construed under the BRI standard." Pet. 19. Patent Owner notes that Petitioner failed to timely file a motion requesting use of the *Phillips* standard for claim construction (under 37 C.F.R. § 42.100(b)) but waives any objection to that deficiency. PO Resp. 27. Patent Owner agrees with Petitioner that "there is no difference in how the claims would be construed under the BRI standard." *Id*.

The '490 patent is not expired, will not likely expire prior to entry of this final written decision, neither party has made a request in compliance with our rules that the *Phillips* standard be applied, and the Petition was filed prior to the change of our rules regarding claim construction effective for petitions filed on or after November 13, 2018. Therefore, as we did in our

Decision on Institution (*see* Dec. on Inst. 11–12), we apply the broadest reasonable interpretation for any needed claim construction.

Although the broadest reasonable interpretation standard is broad, the Board cannot interpret the words of a claim without regard for the full claim language and the written description. See TriVascular, Inc. v. Samuels, 812 F.3d 1056, 1062 (Fed. Cir. 2016); Microsoft Corp. v. Proxyconn, Inc., 789 F.3d 1292, 1298 (Fed. Cir. 2015). Our reviewing court has emphasized the importance of a patent's specification as intrinsic evidence for construing claim terms. See Phillips, 415 F.3d at 1315–17. Specifically, the Court has explained that "the specification . . . is the single best guide to the meaning of a disputed claim term." Id. at 1314 (quoting Vitronics Corp. v. Conceptronic, Inc., 90 F.3d 1576, 1582 (Fed. Cir. 1996)). "In determining the meaning of the disputed claim limitation, we look principally to the intrinsic evidence of record, examining the claim language itself, the written description, and the prosecution history, if in evidence." DePuy Spine, Inc. v. Medtronic Sofamor Danek, Inc., 469 F.3d 1005, 1014 (Fed. Cir. 2006) (citing *Phillips*, 415 F.3d at 1312–17). The court in *Phillips* stated that extrinsic evidence, such as dictionary definitions, may be useful, but is unlikely to result in a reliable interpretation of claim scope unless considered in the context of the intrinsic evidence. See Phillips, 415 F.3d at 1319.

Furthermore, only terms that are in controversy need to be construed and only to the extent necessary to resolve the controversy. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017) ("[W]e need only construe terms 'that are in controversy, and only to the extent necessary to resolve the controversy' . . . ." (quoting *Vivid Techs., Inc. v. Am. Sci. & Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999))).

Other than the terms interpreted below, we discern no reason to expressly construe any other claim terms.

### 1. "Pull"

Claim 31 includes the recitation, "wherein the modem processor is further configured pull data from the application processor." <sup>11</sup>

### a) The Parties' Interpretations

Petitioner contends "pull," in the context of the '490 patent would have been understood to mean "receiving data in response to a request for the data." Pet. 20. Petitioner argues "[i]n a pull data transfer, the data is transferred in response to a request for data by the intended recipient of the data." Pet. 21 (citing Ex. 1002 ¶ 68). Petitioner further argues the '490 patent Specification is consistent with this interpretation in that, although not expressly defining the term "pull," the Specification discloses pulling data with no mention of a required address/location, refers to both pulling and pushing of data as distinct modes of transfer, and discloses that both techniques may be implemented "based on polling, setting doorbell registers, or other techniques." Pet. 20–21 (citing Ex. 1001, 9:61–10:1, 16:34–37). Petitioner cites extrinsic evidence in support of its proffered construction. Pet. 21 (citing Exs. 1008 (an electrical engineering technical dictionary defining "pull technology" to mean "[d]ata distribution, such as that over the Internet, in which users receive information by requesting it"), 1009 (a computer and Internet technical dictionary defining "pull" to mean "the

<sup>&</sup>lt;sup>11</sup> Claim 14 includes a similar recitation that the modem processor is configured to pull data from the application processor. Claim 14 is not challenged in this consolidated proceeding. However, we may consider use of the term "pull" in the context of claim 14 to the extent it aids in our construction of the term.

process whereby the user retrieves information from a network at the user's request, as in traditional web browsing"), 1010 (an academic paper discussing push and pull data transmission techniques and stating: "In the receiver-pull model, it is the receiver who initiates the message transfer by explicitly contacting the sender. The sender passively waits for the receiver and delivers the entire content upon receiving a request.")).

Patent Owner argues that, in the context of the '490 patent, a pull operation requires that the requesting recipient provide location information to the sender to locate the data to be sent in response to the pull. *See* PO Resp. 27–28 ("With knowledge of where in a shared memory the application-processor-held data, the modem processor is able to reach out and access the data from the shared memory based on that specified address (*i.e.*, pull the data)." (citing Ex. 2007 ¶ 61)). Patent Owner cites the same two portions of the '490 patent Specification as cited by Petitioner but adds that surrounding disclosure of each citation allegedly clarifies that a pointer (i.e., an address or location) is provided by the application processor for the modem processor to know where data to be transferred is stored. *Id.* at 29 (citing Ex. 1001, 9:41–10:10, 15:61–16:37).

In support of its proffered construction, Patent Owner points to deposition testimony of Petitioner's expert in the parallel ITC proceeding, Dr. Yalamanchili, who testifies, *inter alia*, that, in a pull operation, "[t]he location of the data has to be known in order to effect any transfer, so the data can be accessed," that, in a pull operation, supplying an address of the data "would be typical," and that some identifier or information related to where the data is located would be part of the initiation of the pull. PO Resp. 28–29 (quoting excerpts of Ex. 2008). Patent Owner further argues Petitioner's expert in this proceeding (Dr. Lin) agrees that an exemplary pull

operation in the '490 patent "uses doorbell registers and *address-indicating pointers*" in performing a pull operation. *Id.* at 29 (citing Ex. 2010, 27:5–7). Furthermore, Patent Owner argues the extrinsic evidence proffered by Petitioner (Exs. 1008–1010) in support of its interpretation of "pull" supports Patent Owner's position because they refer to typical Internet access such as web browsing in which a user supplies an address or hyperlink that specifies the location of the data to be pulled. PO Resp. 29–30.

Moreover, Patent Owner asserts Petitioner's proffered construction, as supported by Dr. Lin's testimony, is contrary to positions articulated by Petitioner's expert (Dr. Yalamanchili) in the related ITC proceeding and, thus, Dr. Lin's testimony interpreting "pull" should be given little weight. PO Resp. 29; *see also* Sur-Reply 2–6.

Accordingly, Patent Owner argues "pull" should be interpreted to mean "accessing data based on a specified location of that data." PO Resp. 32 (citing Ex.  $2007 \, \P \, 66$ ).

Petitioner replies that Patent Owner's narrower construction requiring that a "pull" operation include a "specified location of the data" to be pulled is inconsistent with the intrinsic and extrinsic evidence. Reply 4. In particular, Petitioner argues Patent Owner relies on an exemplary embodiment in the '490 patent that uses a direct memory access ("DMA") read transaction on a PCIe bus, which includes specifying an address in memory for the data to be pulled from the application processor. Reply 5 (citing PO Resp. 29, 55 ("DMA read request includes the address in memory of the data to be pulled")). Petitioner contends the '490 patent Specification does not "suggest any intent to limit the 'pull' of claim 31 to PCIe and/or DMA-based transfers," but, instead, repeatedly refers to pulling data without

reference to DMA or PCIe exemplary embodiments. *Id.* (citing Ex. 1001, 4:40–41, 9:66–10:2, 16:35–37). Petitioner further contends that the '490 patent Specification makes clear that a PCIe implementation is intended merely as exemplary and discloses other interconnectivity busses and techniques that may be employed. Reply 7 (citing Ex. 1001, 6:66–7:3).

### b) Analysis

Both parties' proffered interpretations are consistent with the Specification of the '490 patent. However, we are persuaded that the broadest reasonable interpretation of "pull," consistent with the Specification and the plain meaning, at least encompasses Petitioner's proffered interpretation, which is broader than Patent Owner's proffered interpretation because it does not require that a "pull" specify a location from which the data is to be pulled.

As our reviewing court held, we focus on the intrinsic evidence (claims, Specification, prosecution history) to construe the terms in the claims. *DePuy*, 469 F.3d at 1014. Here, the intrinsic evidence provides scant aid in interpreting the term "pull." There is no express definition of "pull" in the intrinsic evidence. Claim 14 (not challenged here) recites, in essence, that the modem processor pulls uplink data from the application processor in response to receipt of downlink data or the expiration of information. Claim 31 recites, in essence, that the application processor holds (e.g., buffers) uplink data until the modem processor pulls the held data and the modem processor *pulls* the held uplink data from the application processor after transmitting downlink data to the application processor and before the interconnectivity bus transitions to a low power state. Although both proffered interpretations are consistent with these

claims, we discern nothing in these claims that limits the claims requiring a "pull" to specify an address or location of the data to be pulled.

Like the claims, we find the '490 patent Specification provides little aid in interpreting the term "pull." Both parties point to portions of the Specification in columns 9–10 and 15–16. Pet. 20 (citing Ex. 1001, 9:61– 10:1, 16:34–37); PO Resp. 29 (citing Ex. 1001, 9:41–10:10, 15:61–16:37); see also PO Resp. 55. We are unpersuaded that the cited portions of the Specification limit the interpretation of "pull" to require an address be specified. These and other portions of the Specification merely discuss an exemplary embodiment in which the processors are coupled by a PCIe bus using the MHI protocols. See, e.g., Ex. 1001, 9:42-46 ("For example, on a fusion device using MHI over PCIe, the modem processor 44 may poll (read) the MHI channel Context Write Pointer to determine data buffers where downlink packets can be transferred." (emphasis added)). In like manner, the '490 patent Specification at columns 15 and 16 refers to the same "write pointers" of the PCIe/MHI exemplary embodiment. Although this is the only exemplary embodiment discussed in any detail in the '490 patent Specification, we remain disinclined to import such a narrow limitation from an exemplary embodiment of the Specification into the claims. See SuperGuide, 358 F.3d at 875. Patent Owner acknowledges that its claims are not limited to this disclosed PCIe-based embodiment:

And you have to read the claims in the context of the specification of which they are a[] part. The only examples given in the patent of a pull both used a DMA process over a PCIe bus. And, yes, Dr. Baker said that the claims aren't limited to that, but to interpret the claims, you have to read in the specification, and the specification makes it clear that these Patentees meant a pull to be more than just simply receiving data passively.

Tr. 66:2–9. We agree that the claims are not limited by the Specification's disclosure of an exemplary PCIe bus embodiment, but we disagree that "the specification makes it clear that these Patentees meant a pull to be more than just simply receiving data passively." To the contrary, although the Specification at column 15, line 61 through column 16, line 30 discloses a method depicted in Figure 12 that, inter alia, updates a write pointer in the application processor for the modem processor to "pull" data, the next paragraph states, "once a timer has expired, data can be pulled or pushed across the interconnectivity bus 36 based on polling, setting doorbell registers, or other technique[s]." Ex. 1001, 16:34–37 (emphasis added). The phrasing "pulled or pushed . . . based on . . . other technique[s]," clearly suggests that techniques for pulling data, other than those that require a "write pointer," are within the meaning of "pull." In like manner, disclosure of "a fusion device using MHI over PCIe" is clearly disclosed as a nonlimiting, exemplary embodiment. *Id.* at 9:40–60. Lastly, the Specification includes a typical "savings clause" that clearly discloses that the exemplary embodiments are not intended to limit the scope of the claims—including the scope of claimed "pull" operations. *Id.* at 17:44–53. As above, although both proffered interpretations are consistent with the '490 patent Specification, we discern nothing in Specification that limits the claims requiring a "pull" to specify an address or location of the data to be pulled.

Neither party identifies relevant prosecution history (Ex. 1003) to be considered in interpreting "pull."

Accordingly, the intrinsic evidence supports Petitioner's broader interpretation. Although we find the intrinsic evidence sufficient to interpret "pull" in accord with Petitioner's broader interpretation, we turn next to consideration of the extrinsic evidence. Patent Owner argues the dictionary

definitions proffered by Petitioner in support of its broader interpretation actually support Patent Owner's narrower interpretation of "pull" because each dictionary points to Internet access as an example of a pull request and argues that each such exemplary Internet use includes a receiver of the pulled data specifying an address or location of the data to be retrieved. PO Resp. 29–30. We are unpersuaded by Patent Owner's argument. A first technical dictionary defines "pull" as "[d]ata distribution, such as that over the Internet, in which users receive information by requesting it" and then provides a specific example of requesting data by providing an address. Ex. 1008, 3. Another technical dictionary defines "pull" to mean "the process whereby the user retrieves information from a network at the user's request" and, like the first dictionary, then follows with an example such as web browsing on the Internet. Ex. 1009, 3. These dictionaries are consistent with Petitioner's broader interpretation, consistent with the '490 patent Specification, and merely provide common examples of pull operations in the context of Internet accesses where the request includes an address. Such examples are common in the Internet context but do not limit the ordinary meaning of "pull" to require specification of a location in all contexts. In particular, in the context of the '490 patent claims, the "pull" operation is unrelated to typical Internet access but, instead, relates to a more generic pull operation of data between two processors.

Furthermore, we credit Dr. Lin's testimony that, unlike the PCIe exemplary embodiments of the '490 patent Specification, at least one other known interconnectivity bus does not require an address or location to be

<sup>1′</sup>

<sup>&</sup>lt;sup>12</sup> More precisely, Exhibit 1008 defines "pull" as substantively the same as "pull technology" and then defines "pull technology" as stated.

specified for a pull operation. Ex. 1023 ¶ 9 (citing Ex. 1027 describing the I<sup>2</sup>C interconnectivity bus standard, which utilizes only a single bit to request a pull of data from another device). Dr. Lin's deposition testimony describes such a single bit that may be used to initiate a "pull" operation without any express specification of an address or location. Ex. 2010, 32:10–38:5. Rather, so long as the sender and receiver know what data is to be transmitted, the "pull" operation need not specify the location of the data to be pulled but merely sends the request to the processor that has the data to be sent.

- Q. So a pull request does not need to include an address?

- A. Well, so if I want to pull data from you, I have to send a request to you. I can't just send a request to -- out in the air or out to nobody. So, in a sense, I'm specifying location where the request is going, to you.

- Q. Do you need to tell me what data you're requesting?

- A. Well, if I'm requesting a particular data, the data that's in your packet queue, I'm asking you for the data that's in the packet queue, and you are sending that data back to me in response to that request.

. . .

- Q. So if I just asked you to send me what data you have queued, is that a pull request?

- A. Yes, because you're identifying what data you want.

- Q. So if I ask you to send me the data you have, is that a pull request?

A. Yes.

Ex. 2010, 30:2–14, 32:10–16. In other words, if a first processor wishes to pull data that is queued by a second processor, queued (held) specifically for transmission to the first processor as is the case in the '490 patent, a "pull"

request need only be directed from the first processor to the second processor because the second processor already knows the request from the first processor is for the data queued (held) for such transmission. The '490 patent's non-limiting, exemplary embodiment happens to use the MHI protocol over a PCIe bus such that a "pull" request in that context may need to specify an address for the data to be pulled in accord with the MHI/PCIe standards. Therefore, we credit Dr. Lin's testimony that there were, at the time of the '490 patent, known techniques to "pull" data, such as the I<sup>2</sup>C protocol standards, that do not require specifying an address to request pulled data and, therefore, the ordinary meaning of "pull" at the time of the '490 patent does not require a pull request to specify an address of the data to be pulled.

We are also unpersuaded by Patent Owner's argument that Dr. Lin's testimony should be accorded less weight because it allegedly conflicts with Dr. Yalamanchili's testimony on behalf of the Petitioner in the related ITC matter and, thus, Dr. Lin is not credible. Sur-Reply 2–3, 6 (citing *Ultratec*, *Inc. v. CaptionCall, LLC*, 872 F.3d 1267, 1273 (Fed. Cir. 2017) and *Nissan North America, Inc. v. Board of Regents, the University of Texas System*, IPR2012-00035, Paper 30 at 7 (PTAB 2013)). Initially, we note that in both *Ultratec* and *Nissan*, the *same* expert offered allegedly conflicting testimony. By contrast, here, Dr. Yalamanchili did not testify in this matter but testified

<sup>&</sup>lt;sup>13</sup> Neither party positively asserts that DMA techniques are disclosed in the '490 patent but both parties discuss DMA techniques as they would be expected to be used in the context of the '490 patent. Although the '490 patent makes no mention of DMA techniques for such MHI transfers over the PCIe bus, such an embodiment may indeed require the "pull" request to specify an address for the DMA controller to access in the application processor's memory.

before the ITC—a different expert witness, testifying in a different proceeding, in a different forum that applies different claim construction standards and standards of proof. Thus, Patent Owner's reliance on *Nissan* and *Ultratec* in arguing we should accord less weight to Dr. Lin's testimony is inapposite.

Moreover, we are not persuaded Dr. Lin's testimony conflicts with Dr. Yalamanchili's testimony. Dr. Yalamanchili testified that it is "typical" that a pull operation requires some identification of the location of data to be pulled. Ex. 2008, 187:24–188:3, 188:17–18, 190:23–24, 191:3. However, Dr. Yalamanchili also testified, "the pull of data is a situation where the destination is responsible for the transfer of data from the source, as opposed to a push, where the source controls the transfer of data to a destination," and "the flow of data to the destination under the control of the destination would be considered a pull." Ex. 2008, 187:12–20, 188:12–14. Lastly, Dr. Yalamanchili's testimony in our record consists of only a brief excerpt of the transcript of his deposition in the ITC proceeding. Such a scant record of a witness (testifying in another proceeding in another forum applying different claim construction standards) is deserving of less weight in this proceeding as compared to Dr. Lin's full testimony (including two declarations and two complete deposition transcripts).

Still further, we note that the ITC Commission Opinion finds, "[a] 'pull' means the receiving processor (the modem processor in claim 31) requests or initiates the transfer of data from a remote source (the application processor). This understanding is consistent with the plain meaning of 'pull' and its usage in the '490 patent." Ex. 1022, 42 (citation omitted). Although we are not bound by the claim construction of another forum (particularly a forum that applies a different claim construction standard), it is noteworthy

that the Commission, applying the potentially narrower *Phillips* standard for claim construction, arrives at essentially the same construction we adopt—namely, Petitioner's broader construction.

Lastly, we acknowledge Patent Owner's argument that Petitioner's Exhibit 1027 was filed late and should be accorded no weight in interpreting the term "pull." Sur-Reply 32–33. As seen above in our analysis to interpret "pull," we do not rely on Exhibit 1027 as providing a definition of "pull" but, instead, refer to it only as evidence that the ordinarily skilled artisan, at the time of the '490 patent, would have known of interconnectivity busses and corresponding protocols that, unlike the PCIe exemplary embodiment of the '490 patent, do not require any address or location indicia be specified to perform a "pull" consistent with our interpretation of the term. Even assuming, arguendo, that Exhibit 1027 was improperly filed, Patent Owner did not timely object to the new evidence and, accordingly, cannot file a motion to exclude. See 37 C.F.R. § 42.64. We accord Exhibit 1027 some weight as supporting Dr. Lin's arguments that there were known interconnectivity busses at the time of the '490 patent that used pull operations that did not specify an address or location with the pull operation. Furthermore, we agree with Dr. Lin that Exhibits 1008 through 1010 provide sufficient extrinsic evidence in support of his positions. See Sur-Reply 32–33 (quoting Ex. 2012, 21:16–25, 22:5–15, 23:7–9).

Weighing all intrinsic and extrinsic evidence of record, we determine that, although both proffered interpretations of "pull" are reasonable and consistent with the evidence, Petitioner's proffered interpretation is the broader reasonable interpretation. Accordingly, we interpret "pull" to mean "receiving data in response to a request for the data."

# 2. "Triggered By" and "Triggers"

Challenged independent claims 1, 16, 26–28, and 30, as well as their respective challenged dependent claims, recite that transmission of held data in one direction is "triggered by" or "triggers" transmission of data in the other direction between the application and modem processors of the '490 patent. Petitioner argues the term "triggered by" means "initiated in response to." 1293PET 19. Petitioner further argues the '490 patent Specification does not expressly define the term but the Specification, prosecution history, and the claims impliedly support its proffered construction. *Id.* at 19–20 (citing Ex. 1001, 2:3–6, 11:15–18, 11:39–46; Ex. 1003, 45<sup>14</sup>). Petitioner cites extrinsic evidence (three dictionaries defining "trigger") in support of its proffered construction of "triggers" and "triggered by." *Id.* at. 20 (citing Exs. 1012, 1013, 1014).

Patent Owner does not expressly address construction of this term. *See* PO Resp. 26–32.

We find Petitioner's argument for its proffered construction of "triggered by" persuasive. Specifically, claim 1 sufficiently defines the condition that triggers the defined response—i.e., data is held by a first processor until receipt of data from a second processor, after which the first processor sends its held data to the second processor. The receipt of data is

\_

<sup>&</sup>lt;sup>14</sup> Petitioner cited "[8/24/2016 Response], 14" in this exhibit of prosecution history. Although Petitioner correctly numbered pages of the exhibit sequentially starting at page "1," in the lower right corner of each page, Petitioner cites to page "14" of the original, underlying documents that comprise the prosecution history. We find the cited page "14" at page 45 of the exhibit (Ex. 1003 in this consolidated proceeding) and request that all parties, in all proceedings before the Board, number exhibits with sequential page numbers starting at "1" and use those sequential page numbers in all citations in papers and other exhibits.

the event that triggers further action (transmission of the held data from the first processor to the second processor) following the event. In like manner, the other independent claims that refer to an event that "triggers" a next event (i.e., receipt of some data that triggers transmission of other data), sufficiently define the relevant conditions that trigger the next action. Petitioner's interpretation is consistent with the claims in that a recited next action/event is *initiated in response to* some other recited action/event.

Therefore, we adopt the Petitioner's definition and find that an action "triggered by" a recited condition means the action is "*initiated in response to*" the condition. In like manner, we interpret "triggers" in the context of a condition that "triggers" some action to mean that the action is "*initiated in response to*" the specified condition.

# D. Obviousness Over Heinrich and Balasubramanian

In this consolidated proceeding, Petitioner relies on the combined disclosures of Heinrich and Balasubramanian in contending certain claims are unpatentable as obvious under 35 U.S.C. § 103 (post-AIA) as follows: claim 31 (Pet. 30–56); claims 1, 4–6, and 8 (1293PET 29–63); claims 16 and 22–24 (1295PET 29–67); claims 20, 28, and 30 (1344PET 56–72) and claims 9, 11–13, 26, and 27 (1346PET 55–69).

# 1. Overview of Heinrich (Ex. 1004)

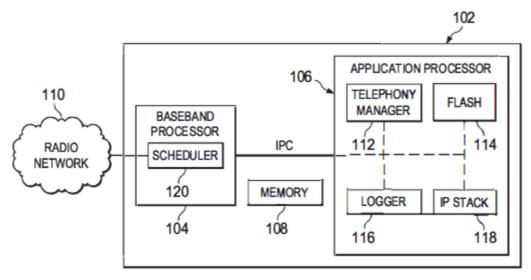

Heinrich is directed to problems of power efficiency in inter-processor communications ("IPC") among multiple processors of a system. Ex. 1004, 1:6–2:8. In battery-powered systems in particular, power consumption is a critical issue. *Id.* at 1:18–23. Figure 1 of Heinrich is reproduced below.

FIG. 1

Heinrich's Figure 1 is a schematic illustration of a communication system including mobile device 102. *Id.* at 3:19–20, 4:18–19. Mobile device 102 may be a mobile phone or tablet connected to radio network 110. *Id.* at 4:19–21. Mobile device 102 comprises baseband processor 104 and application processor 106. *Id.* at 4:26–29. Baseband processor 104 acts as a radio frequency ("RF") modem to modulate and demodulate data exchanged between mobile device 102 and network 110. *Id.* at 4:30–33. Physical interface (labeled IPC in Figure 1) communicatively couples baseband processor 104 and application processor 106. *Id.* at 4:44–46. The physical interface to the IPC may be, for example, a USB interface. *Id.* at 4:46–48.

Each processor of mobile device 102 may operate in one of a plurality of modes, including an "awake" mode ready to process data and a "sleep" mode not ready to process data but saving power. *See id.* at 1:54–62. According to Heinrich, in the prior art, each time baseband processor 104 receives any quantum of data to be sent to application processor 106, application processor 106 would have to already be in the awake mode or would have to be transitioned from the sleep mode to the awake mode. *See*

*id.* at 1:65–2:2. Frequent transitions out of sleep mode consume additional power in mobile device 102. *See id.* at 2:2–8.

To reduce power consumption of mobile device 102, Heinrich discloses that baseband processor 104 includes scheduler 120. Id. at 7:8–10. Scheduler 120 may be configured to reduce power consumption by reducing the number of times a processor is awakened from its sleep mode. Id. at 7:16–19. Scheduler 120 may be configured to schedule communication in either direction between baseband processor 104 and application processor 106. Id. at 7:19–21. Alternatively, scheduler 120 may schedule only communication from baseband processor 104 to application processor 106, and another scheduler (not shown) implemented within application processor 106 may schedule communication in the opposite direction. *Id.* at 7:21–27. In general, scheduler 120 is operable to identify communications awaiting transmission from one processor to the other processor that are not real-time critical so that they may be delayed until a later time to avoid causing another sleep-to-awake mode transition of the other processor. Id. at 7:65–8:1. By grouping the non-real-time sensitive exchanges together and scheduling them for communicating to the other processor during a period in which the other processor is continuously in the awake mode, the number of times that the other processor enters and exits the sleep mode is reduced. *Id.* at 4:6–11.

Heinrich's Figure 3 is reproduced below.

FIG. 3

Figure 3 is a flowchart describing operation of a scheduler. At step S302, scheduler 120 determines which pending communications awaiting transmission to the other processor are not real-time sensitive. *Id.* at 8:10–16. Non-real-time data is that which may be delayed, and, conversely, real-time data is that which must be transmitted without delay (e.g., voice communications). *Id.* at 8:14–20. Step S304 groups the identified non-real-time data for delayed transmissions and schedules them for transmission during a single awake mode of the other processor. *Id.* at 8:21–32. Step S306 transmits the grouped, delayed, non-real-time data to the other processor during a single awake mode—i.e., during a period of time in which the other processor is continuously awake. *Id.* at 8:33–49.

# 2. Overview of Balasubramanian (Ex. 1005)

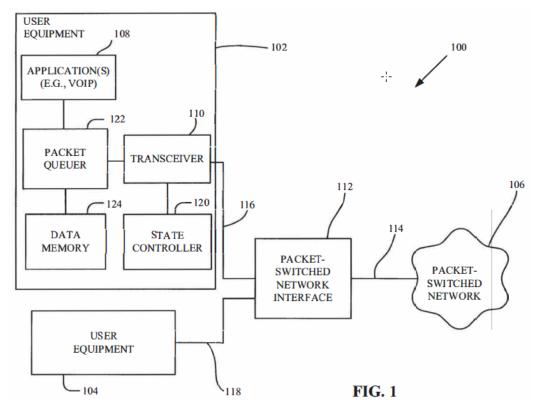

Balasubramanian is directed to grouping packets of data to be exchanged by buffering packets destined for a device that is presently in a low power mode. Ex. 1005, 1:16–45. Balasubramanian's Figure 1 is reproduced below.

Figure 1 depicts a system adapted to transmit and receive groups of packets. *Id.* at 3:15–17. System 100 includes user equipment 102 and 104 coupled to packet-switched network 106 to group packets for transmission and, thereby, reduce power consumption. *Id.* at 4:1–5. User equipment 102 and 104 may each be, for example, a mobile phone, a laptop computer, a wireless device or modem, or other types of communication devices wishing to connect with another user equipment or with packet-switched network 106. *Id.* at 4:24–29. User equipment 102 includes transceiver 110 to provide a physical layer interface for transmissions to and from user equipment 102. *Id.* at 4:37–42. User equipment 102 and 104 communicate with packet-switched network 106 through packet-switched network interface 112 (via communication links 116, 118, and 114). *Id.* at 4:43–57.

Transceiver 110 in user equipment 102 may be switched between an active state (ready to send or receive data) and a suspended state (saving

IPR2018-01261 Patent 9,535,490 B2

power but not ready to send or receive data). *Id.* at 5:30–46. To conserve power, while transceiver 110 is in a suspended state, user equipment 102 and interface 112 may queue packets to be sent through transceiver 110. *Id.* at 5:47–51.

Here, power may be conserved by not transitioning the transceiver 110 from the suspended state to the active state every time a packet has been generated for transmission by the user equipment 102 or every time it is expected that the user equipment 102 will receive a packet. Accordingly, power savings may be achieved by rescheduling the packet traffic into groups of traffic.

*Id.* at 5:55–61. To enable this power saving, "user equipment **102** and/or the network interface **112** may be adapted to queue packets while the transceiver **110** is in the suspended state." *Id.* at 5:47–51.

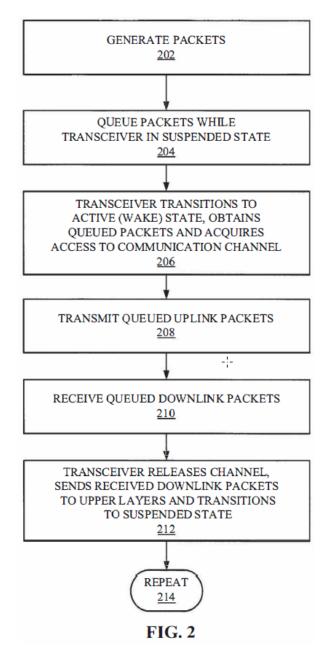

Figure 2 of Balasubramanian is reproduced below.

Figure 2 is a flowchart of operations to send or receive a group of packets. *Id.* at 3:18–20. At step 202, user equipment 102 generates data as packets to be sent to packet-switched network 106. *Id.* at 6:29–31. At step 204, user equipment 102 queues the generated packets while transceiver 110 is in a suspended state. *Id.* at 6:40–43. At step 206, transceiver 110 awakens from its suspended state and obtains queued packets for transmission to packet-switched network 106. *Id.* at 6:55–62. At step 208, transceiver 110

transmits the queued packets over path 116—all queued packets may be retrieved and transmitted during the present single awake state of transceiver 110. *Id.* at 6:63–67. In addition, during the same single awake state at step 210, network interface 112 may "use the receipt of an uplink packet as a trigger to transmit any downlink packets in its queue" to transceiver 110. *Id.* at 7:4–8. Alternatively, transceiver 110 may send a message to interface 112 requesting transmission of any queued downlink packets up to transceiver 110. *Id.* at 7:8–13.

### 3. Motivation to Combine Heinrich and Balasubramanian

Petitioner argues the ordinarily skilled artisan would have been motivated to combine Balasubramanian's disclosed pulling of data with Heinrich's disclosed inter-processor communication scheduling for the following reasons.

### a) Analogous Art

Whether a reference in the prior art is "analogous" is a factual question. *In re Clay*, 966 F.2d 656, 658–659 (Fed. Cir. 1992) (citing *Panduit Corp. v. Dennison Mfg.*, 810 F.2d 1561, 1568 n.9 (Fed. Cir. 1987)). Two criteria have evolved for determining whether prior art is analogous: (1) whether the art is from the same field of endeavor, regardless of the problem addressed, and (2) if the reference is not within the field of the inventor's endeavor, whether the reference still is reasonably pertinent to the particular problem with which the inventor is involved. *Id.* (citing *In re Deminski*, 796 F.2d 436, 442 (Fed. Cir. 1986); *In re Wood*, 599 F.2d 1032, 1036 (CCPA 1979)).

# (1) Same Field of Endeavor

Petitioner argues Balasubramanian and Heinrich are in the same field of endeavor addressing the same issues of reducing power consumption when transitioning from low power to high power states. Pet. 47–48. In particular, Petitioner argues Heinrich and Balasubramanian disclose "similar architectures that include two processing nodes coupled by a bus, buffering data on both sides of the bus to allow for power savings states, and the use of a timer in one or both processing nodes to determine when to send queued data to the other processing node." *Id.* (citing Ex. 1004, 4:6–11; Ex. 1005, 5:55–61; Ex. 1002 ¶ 100). Second, Petitioner argues both references "solve the power consumption problem in the same way: minimizing the number of transitions from low power-to-high power states." Pet. 48 (citing Ex. 1002 ¶ 101).

Patent Owner argues Petitioner's analysis depends on an overly broad characterization of the relevant field of endeavor and the teachings of Balasubramanian because the claims of the '490 patent are directed to a mobile terminal comprising multiple processors but Petitioner broadens that field to encompass Balasubramanian's two separate processing nodes coupled by a network. PO Resp. 62-63. Patent Owner contends that framing the field so broadly "conceivably encompasses any two electronic devices, as long as they are connected over a network." Id. at 63. Patent Owner asserts that the proper field of endeavor is "power saving in a single mobile terminal and intra-device communication." Sur-Reply 38. In other words, Patent Owner argues the field is defined as power savings where the two devices connected by the interconnectivity bus must physically reside within the same single mobile terminal. By contrast, Patent Owner argues, "Balasubramanian, on the other hand, relates to communications between different devices" and "devices connected over a network have a different set of power consumption objectives and different power management

IPR2018-01261 Patent 9,535,490 B2

schemes than IPC activities on a single user device." *Id.* at 38–39 (citing Ex.  $2007 \, \P \, 123-127$ ).

We are persuaded that Heinrich and Balasubramanian are in the same field of endeavor as the '490 patent. Initially, we observe the '490 patent broadly characterizes its field of endeavor as "power saving techniques in computing devices." Ex. 1001, 1:20–21. Heinrich appears on its face to be in the same field in that it is directed to saving power in a computing system. See, e.g., Ex. 1004, code (54) ("POWER-EFFICIENT INTER PROCESSOR COMMUNICATION SCHEDULING"), 1:16–17 ("[I]t is important to keep the power consumption of the computer system at a low level."), 4:6–11 ("By grouping the non real-time sensitive IPC activities together and scheduling them for communicating to the second processor during a period in which the second processor is continuously in the first mode, the number of times that the second processor enters and exits the second mode (e.g. sleep mode) is reduced. This reduces the power consumed by the computer system in handling the IPC activities."). In like manner, Balasubramanian appears on its face to be in the same field. See, e.g., Ex. 1005, code (54) ("ACHIEVING POWER SAVINGS THROUGH PACKET GROUPING"), code (57) ("Power savings may be achieved in a packet-switched system by grouping packets."), 1:52–53 ("In some aspects power savings are achieved in an apparatus by grouping packets."), 5:55–61 ("Here, power may be conserved by not transitioning the transceiver 110 from the suspended state to the active state every time a packet has been generated for transmission by the user equipment 102 or every time it is expected that the user equipment 102 will receive a packet. Accordingly, power savings may be achieved by rescheduling the packet traffic into groups of traffic."). Furthermore, both Heinrich and Balasubramanian disclose these problems and solutions arise in the context of mobile devices. Ex. 1004, 1:14–17 ("However, for computer systems implemented on user devices, such as mobile smart phones and tablets, it is important to keep the power consumption of the computer system at a low level"), Ex. 1005, 1:30–34 ("Also, mobile devices traditionally operate on battery power. In this case, reducing the power consumed by the mobile device effectively increases the talk time of the device between recharges of the battery."). Still further, both Heinrich and Balasubramanian disclose a solution to the problem by grouping transmissions between two processors to save power by reducing the number of transitions of a processor into a sleep mode. Pet. 47 (citing Ex. 1004, 4:6–11, Ex. 1005, 5:55–61).

Both references expressly disclose the same advantage, reducing power consumption, by essentially the same techniques, grouping transmissions between processors to reduce power state transitions of the processors. Thus, we are persuaded the references are in the same field of endeavor—reducing power consumption in mobile devices—as the '490 patent.

We are not persuaded by Patent Owner's argument that the field of endeavor is narrowed to "power saving in a single mobile terminal and intradevice communication." Sur-Reply 38. Patent Owner argues that the agreed upon level of skill in the art requires experience in "mobile device architecture and multiprocessor systems" and, apparently believes such a skilled person would not consider Balasubramanian because the identified processors (110 and 112) are not both within the user equipment 102 (the mobile device). *Id.* at 38–40. Patent Owner's analysis is premised on its suggested narrow field of endeavor—a field essentially limited to that of the

IPR2018-01261 Patent 9,535,490 B2

claims of the '490 patent. We decline to so narrow the field of endeavor of the references.

(2) References Solve a Reasonably Pertinent Problem

Patent Owner argues Balasubramanian is "not pertinent to the problems and solutions of the '490 patent" because,

Balasubramanian is concerned only with managing processor wake states, not activity states of any interconnectivity bus. In contrast, the '490 Patent is directed towards the more granular technique of minimizing the active state and the state transitions of the *interconnectivity bus*. Accordingly, Petitioner fails to present any persuasive reason why a POSITA would look to Balasubramanian to address the problems solved by the '490 Patent.

### Sur-reply 40.

For essentially the same reasons as above regarding the field of the invention, we are not persuaded by Patent Owner's argument that, again, narrowly focuses on the problems addressed by the claimed invention. We are persuaded both Heinrich and Balasubramanian address a problem reasonably pertinent to the particular problem addressed in the '490 patent. As discussed *supra* in the invention's field of endeavor, we understand the problem addressed by the '490 patent more broadly as reducing power consumption of a computing device by reducing power state transitions within the device. *See*, *e.g.*, Ex. 1001, 1:20–21 ("[t]he technology of the disclosure relates generally to power saving techniques in computing devices"). The '490 patent specifically addresses this problem by synchronizing transmissions in both directions between processors, thereby reducing the number of low to high (active) power state transitions of an interconnectivity bus between processors. *See*, *e.g.*, *id.* at 2:12–15 ("By holding or accumulating the data at a source processor in this fashion,

unnecessary transitions between low power states and active states on the PCIe bus are reduced and power is conserved."), 5:33–35 ("By holding or accumulating the data at a source processor in this fashion, unnecessary transitions between low power states and active states on the PCIe bus are reduced and power is conserved."), 8:41–48 ("[e]xemplary aspects of the present disclosure reduce the number of transitions (i.e., 60, 62) from low power to active power by synchronizing packet transmission from the modem processor 44 and the application processor 34").

However, as noted *supra*, Patent Owner acknowledges that the '490 patent is not limited to the exemplary embodiments disclosed therein. Thus, we find the problem addressed more generally to be reducing power consumption of a computing device by reducing power state transitions within the device. Whether the transitions are those of processors within the device or an interconnectivity bus within the device, the broader problem being addressed is the same—reduce power consuming power state transitions.

Furthermore, Patent Owner acknowledges that a "bus," per se, is merely a collection of wires/conductors—a passive entity over which interface circuits exchange information. *See* Tr. 40:17–42:14. In other words, a PCIe or USB bus is merely a passive collection of wires that has no power states itself but becomes a PCIe bus, having various power states, by virtue of being coupled to a PCIe interface circuit—i.e., coupled to a processor/circuit that senses and applies signals to the wires in accord with the PCIe standards. Thus, a bus, per se, does not have any associated power states but, rather, the interface circuits coupled to the conductors/wires of the bus may transition between power states as data is transferred over the bus in accord with the specific protocol employed.

Based on our determination of the problem addressed by the '490 patent, Heinrich resolves a similar problem, which would be reasonably pertinent to the ordinarily skilled artisan, by holding data until a more opportune time to send data from one processor to another to eliminate some low to high power transitions within the computing device. See, e.g., Ex. 1004, 4:6–15 ("By grouping the non real-time sensitive IPC activities together and scheduling them for communicating to the second processor during a period in which the second processor is continuously in the first mode, the number of times that the second processor enters and exits the second mode (e.g. sleep mode) is reduced. This reduces the power consumed by the computer system in handling the IPC activities."), 10:44– 47 ("delaying some of the IPC activities to thereby group them together . . . results in fewer transitions between the sleep and awake modes on the application processor 106"). Balasubramanian also resolves a similar problem, which would be reasonably pertinent to the ordinarily skilled artisan, by holding data until a more opportune time to send data from one processor to another to eliminate some low-to-high power transitions within the computing device. See, e.g., Ex. 1005, 1:52–53 ("In some aspects power savings are achieved in an apparatus by grouping packets."), 5:55–61 ("Here, power may be conserved by not transitioning the transceiver 110 from the suspended state to the active state every time a packet has been generated for transmission by the user equipment 102 or every time it is expected that the user equipment 102 will receive a packet. Accordingly, power savings may be achieved by rescheduling the packet traffic into groups of traffic."), 14:56–59 ("By 'waking' less often to transmit and/or receive packets, the number of transitions between active and suspended states (e.g., turning the transceiver on and off) will be reduced.").

(3) Heinrich and Balasubramanian are Analogous Art

Accordingly, we are persuaded by Petitioner's arguments that Heinrich and Balasubramanian are analogous art to the '490 patent both because they are in the same field of endeavor and because they address a problem that is reasonably pertinent to the particular problem with which the '490 patent inventor is involved. However, that finding alone is insufficient to establish a reason why the ordinarily skilled artisan would have combined the references.

b) Balasubramanian's Pulling Fits in Heinrich's Scheduling of a "Good Time"

As discussed further below, Petitioner relies on Balasubramanian primarily for its disclosure of one device pulling data from another device (as the term "pull" has been construed) (see Pet. 51–56) and for its disclosure of an event being "triggered by" another event (as the term "triggered by" has been construed) (see 1293PET 39–45). Petitioner argues Balasubramanian's disclosure of sending data from a first node to a second node and then, following the transmission, pulling data from the second node to the first node, fits well in the scheduler architecture of Heinrich. Pet. 48. In particular, Petitioner argues "Heinrich teaches that a 'good time' to schedule communications over the IPC link is when the application processor is in the awake state, and one way to know that a processor is in an awake state is when data is being transmitted to it." Id. at 48–49 (citing Ex. 1004, 7:19–21, 9:13–21; Ex. 1002 ¶ 102); see also 1293PET 53–54. Petitioner further argues Balasubramanian's approach of combining transmission and receipt of packets into a single active power state of its transceiver saves power and contends the ordinarily skilled artisan "would realize that the same advantages taught by Balasubramanian would be

gained by applying the same approach to the system in Heinrich." Pet. 49–50 (citing Ex. 1005, 1:52–62, 5:55–61, 14:49–63; Ex. 1002 ¶ 103); see also 1293PET 53–54. Petitioner contends, "Applying the power-saving approach in Balasubramanian to Heinrich would result in a system in which the application processor buffers its data until it is pulled by the modem processor, which occurs after the modem processor transmits data to the application processor and during the same active state of the apparatus." Pet. 50 (citing Ex. 1002 ¶ 103). Still further, Petitioner contends,

Because Heinrich similarly discloses a bus with low and high power states and performing a data transfer between two processors during a single wake state of a bus, a person of ordinary skill in the art would have been motivated to apply Balasubramanian's teaching of performing push and pull transactions during a single wake state of communication link 116, to the system of Heinrich, to create a system in which a modem processor pushes data to, and pulls data from, an application processor during a single active state of the communication link between the modem processor and application processor.

Pet. 53 (citing Ex. 1002 ¶ 109).

Patent Owner argues there is no motivation to combine Balasubramanian with Heinrich because "[n]either reference recognizes the problem addressed by the '490 Patent" and "[t]hus there is no motivation to combine the references in the manner claimed to solve this unrecognized problem." PO Resp. 58 (citing Ex. 2007 ¶ 114); *see also id.* at 61 ("[T]here is certainly no motivation to combine the references in the manner claimed to address a problem that no prior art of record recognizes as even being a problem" (citing Ex. 2007 ¶ 120)); *id.* at 65 (arguing that a "POSITA would not have been motivated to combine Heinrich and Balasubramanian in the

manner proposed by Petitioner to address a problem unrecognized by the prior art evidence of record"); Sur-Reply 36–38.

We are not persuaded by Patent Owner's argument because it is premised on Patent Owner's narrower understanding of the field of endeavor and the corresponding problem addressed by the '490 patent and the references. As discussed *supra*, we are persuaded by Petitioner that the references are in the same field of endeavor and address a problem reasonably pertinent to the inventor of the '490 patent.

In support of its position, Patent Owner further argues that the Federal Circuit has held that one small design change can cause unpredictable results. PO Resp. 61–62 (citing *Nichia Corp. v. Everlight Americas, Inc.*, 855 F.3d 1328, 1339 (Fed. Cir. 2017)).

We are unpersuaded by this argument. Initially, it is unclear to us what one small design change Patent Owner is referring to in the proposed combination. Regardless, as Petitioner correctly observes, the Court in *Nichia* found that the prior art reference at issue disclosed "different structures, resolve[d] dissimilar problems, and propose[d] dissimilar solutions." Reply 38 (quoting *Nichia*, 855 F.3d at 1339). Here, as discussed *supra*, we have determined that the references disclose similar structures (a mobile device with two processors coupled by a bus), resolve similar problems (reduce power consumption by reducing power state transitions within the mobile device), and propose similar solutions (pull data from the first processor when the second processor has sent data to the first processor or triggering transmission of held data following receipt of data—i.e., during a single power state).

Patent Owner also contends Heinrich and Balasubramanian solve the power consumption problem in different ways that are "in conflict" and,

thus, there would be no motivation to combine the references. PO Resp. 64. Specifically, Patent Owner argues Balasubramanian's approach "contemplates that the intra-device processes and processing components must remain active in order to queue packets for transmission," which conflicts with Heinrich's goal to "minimize the time the application processor or baseband processor spends in an active state." *Id.* at 64–65 (citing Ex. 1005, 5:20–22, 27–29; Ex. 2007 ¶ 126).

We remain unpersuaded by Patent Owner's argument. We discern no conflict in the references that negates Petitioner's proposed motivation for the ordinarily skilled artisan to have considered combining the references.

c) Reasonable Expectation of Success in the Combination

Petitioner argues the ordinarily skilled artisan would have had a reasonable expectation of success in combining Balasubramanian's data pull technique with Heinrich because both push and pull techniques for transferring data were well-known and the combination would not have required alterations to the bus protocols coupling Heinrich's processors but, instead, "would merely have involved routine scheduling, which would also have been considered trivial to a person of skill in the art." Pet. 50–51 (citing Ex. 1002 ¶ 104); see also 1293PET 54–57.

Patent Owner does not expressly direct any of its arguments toward these assertions of Petitioner.

On this record, we are persuaded by Petitioner's arguments that the ordinarily skilled artisan would have had a reasonable expectation of success in adding Balasubramanian's disclosure of pulling data to Heinrich's disclosures to achieve the benefits of Balasubramanian and thereby arrive at the claimed invention.

# d) Conclusion Regarding Motivation to Combine Heinrich and Balasubramanian

In view of the above discussion, we are persuaded by Petitioner's arguments that the ordinarily skilled artisan would have been motivated to add Balasubramanian's disclosure of pulling data or triggering a transmission of data to Heinrich's disclosures to achieve the express benefits of Balasubramanian and thereby arrive at the claimed invention. Thus, Petitioner has articulated reasons the ordinarily skilled artisan would have combined the references based on rational underpinnings with a reasonable expectation of success.

#### 4. Claims 1 and 31

Petitioner identifies each structural element of claims 1 and 31 in Heinrich and the various functions of the recited elements in the combined teachings of Heinrich and Balasubramanian. Specifically, the "mobile terminal" recited in the preamble of each claim is identified as Heinrich's "user device 102." Pet. 30 (citing Ex. 1001, 6:37–41; Ex. 1004, 4:21–23, Fig. 1); 1293PET 29 (citing Ex. 1001, 6:37–41; Ex. 1004, 4:21–23, Fig. 1). The recited "modem timer" of claim 31 is identified as the "lazy timer" of Heinrich, one or more of which are used by scheduler 120 to control IPC activities in both directions of data exchange. Pet. 30–31 (citing Ex. 1004, 7:8–21, 9:2–6; Ex. 1002 ¶ 76); 1293PET 29–30 (citing Ex. 1004, 7:8–21, 9:2–6; Ex. 1018 ¶ 78).

The recited "modem processer" is identified as Heinrich's "baseband processor 104." Pet. 31–32 (citing Ex. 1004, 4:30–36, Fig. 1; Ex. 1002 ¶ 77); 1293PET 30–31 (citing Ex. 1004, 4:30–36, Fig. 1; Ex. 1018 ¶ 79). Claims 1 and 31 recite that the modem processor is "configured to hold modem processor to application processor data until expiration of the

modem timer." In other words, the modem processor holds received downlink data from a network until the modem timer expires. Petitioner argues Heinrich discloses this function because "Heinrich teaches that baseband processor 104 delays sending certain data to the application processor 106 over the IPC interface, and transmits such data upon expiration of the modern timer." Pet. 32–33; 1293PET 31–32. Specifically, Petitioner argues Heinrich discloses that IPC activities (i.e., data to be transferred between processor) that are not real-time sensitive "can be delayed until it is deemed profitable to run them." Pet. 33 (citing Ex. 1004, 7:65–8:1); 1293PET 32 (citing Ex. 1004, 7:65–8:1). Heinrich associates a "lazy timer" with each such delayed IPC activity and when any one of the timers expires, all the delayed IPC activities are aggregated and transmitted at the same time. Pet. 33 (citing Ex. 1004, 9:5–13); 1293PET 32 (citing Ex. 1004, 9:5–13). Heinrich further discloses that buffering, delaying, and aggregating such IPC activities results in fewer sleep mode to awake mode transitions of the applications processor and, thus, reduces power consumption of the user device. Pet. 33–34 (citing Ex. 1004, 10:44–51, 11:57–58; Ex. 1002 ¶ 78); 1293PET 32 (citing Ex. 1004, 10:44–51, 11:57– 58; Ex. 1018 ¶ 80).

The Petition identifies the recited "application processor" of claim 31 as Heinrich's "application processor 106." Pet. 37 (citing Ex. 1004, 4:36–42, Fig. 1; Ex. 1002  $\P$  84); 1293PET 35 (citing Ex. 1004, 4:36–42, Fig. 1; Ex. 1018  $\P$  86). We address the recited function of the application processor in both claims below.