# SEMICONDUCTOR WAFER BONDING: SCIENCE AND TECHNOLOGY

# Q.-Y. TONG

Duke University Durham, North Carolina, USA

Max-Planck-Institute of Microstructure Physics Halle, Germany

Southeast University Nanjing, China

# U. GÖSELE

Max-Planck-Institute of Microstructure Physics Halle, Germany

Duke University Durham, North Carolina, USA

Sponsored by THE ELECTROCHEMICAL SOCIETY, INC. Pennington, New Jersey

A WILEY-INTERSCIENCE PUBLICATION JOHN WILEY & SONS, INC.

NEW YORK / CHICHESTER / WEINHEIM / BRISBANE / SINGAPORE / TORONTO

This book is printed on acid-free paper. ©

Copyright ©1999 by John Wiley & Sons, Inc. All rights reserved.

Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ@WILEY.COM.

#### Library of Congress Cataloging in Publication Data:

Tong, Q.-Y., 1938-Semiconductor

Semiconductor wafer bonding / by Q.-Y. Tong and U. Gösele

p. cm. Includes index.

ISBN 0-471-57481-3 (cloth: alk. paper)

1. Semiconductors--Bonding. 2. Semiconductor wafers.

I. Gösele, U. 1949-. II. Title.

TK7871.85.S4685 1999

621.3815'2--dc21

98-24397

CIP

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

# **CONTENTS**

| Se | ries l     | Preface                                                                         |                                                                                               | XI   |

|----|------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|

| Pi | eface      |                                                                                 |                                                                                               | xiii |

| 36 | ries l     | Page                                                                            |                                                                                               | xv   |

| Se | lecte      | d List o                                                                        | of Symbols                                                                                    | xvii |

| L. | Intro      | oductio                                                                         | n ·                                                                                           | 1    |

|    | 1.2<br>1.3 | Histor                                                                          | is "Wafer Bonding"?, 1 rical Background, 1 r Bonding: Advantages and Opportunities, 7 , 13    |      |

| 2  | Basi       | cs of I                                                                         | nteractions Between Flat Surfaces                                                             | 17   |

|    |            | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Surface<br>Measu<br>2.2.1<br>2.2.2<br>2.2.3 | Related Methods, 25 Bond Strength Measurement: Fracture Strength Method, 28                   |      |

|    | Refe       | erences                                                                         | , 30                                                                                          |      |

| 3  | Influ      | ience o                                                                         | f Particles, Surface Steps, and Cavities                                                      | 33   |

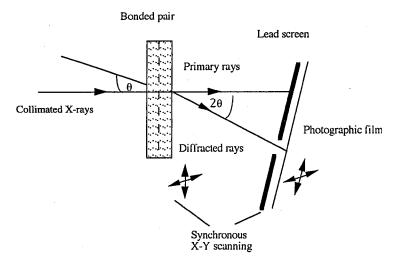

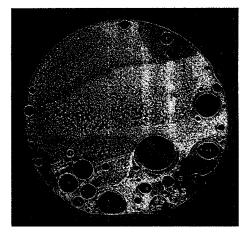

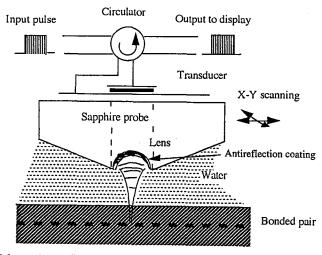

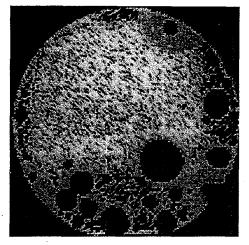

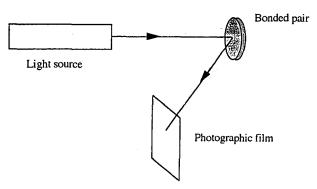

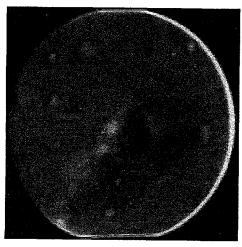

|    | 3.1        | 3.1.1<br>3.1.2<br>3.1.3                                                         | Optical Transmission, 33 X-ray Topography, 36 Acoustic Microscopy, 38 Magic Mirror Method, 40 |      |

# vi CONTENTS

|     | 3.1.5                                                     | Interface Etching, 41 Transmission Electron Microscopy, 41                              |    |  |

|-----|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|----|--|

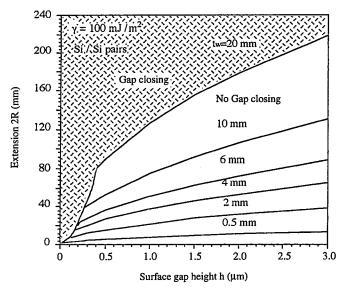

| 3.2 |                                                           | le Diameter as a Function of Particle Size, 42                                          |    |  |

|     | .3 Influence of Surface Flatness, Steps, and Cavities, 44 |                                                                                         |    |  |

|     |                                                           |                                                                                         |    |  |

| Kel | erences                                                   | 5, 47                                                                                   |    |  |

|     |                                                           |                                                                                         |    |  |

| Sur | face Pr                                                   | eparation and Room-Temperature Wafer Bonding                                            | 49 |  |

| 4.1 | Polish                                                    | ning of Wafer Surfaces, 49                                                              |    |  |

| 4.2 | Wafe                                                      | r Surface Cleaning, 51                                                                  |    |  |

|     | 4.2.1                                                     | Cleaning Principle of Hydrogen-Peroxide-Based                                           |    |  |

|     |                                                           | RCA Solutions, 51                                                                       |    |  |

|     | 4.2.2<br>4.2.3                                            | Microroughening and Modified RCA1 Solution, 53<br>Alternative Cleaning Technologies, 54 |    |  |

|     |                                                           | 4.2.3.1 Sulfuric- and HF-Based Solutions, 54                                            |    |  |

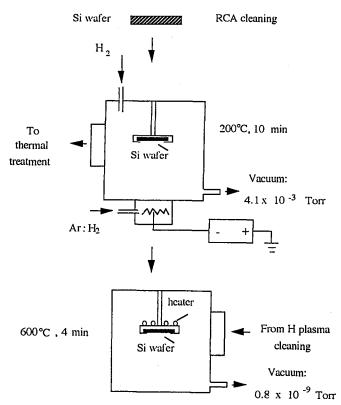

|     |                                                           | 4.2.3.2 Hydrogen Plasma Cleaning and Thermal                                            |    |  |

| 4.0 |                                                           | Treatment in UHV, 55                                                                    |    |  |

| 4.3 |                                                           | ation of Wafer Surface, 57                                                              |    |  |

|     | 4.3.1<br>4.3.2                                            |                                                                                         |    |  |

|     | 4.5.2                                                     | Wet Chemical Activation of Si or SiO <sub>2</sub> Surface, 59                           |    |  |

|     |                                                           | 4.3.2.1 Wet Chemical Hydrophilization of SiO <sub>2</sub><br>Surface, 59                |    |  |

|     |                                                           | 4.3.2.2 Wet Chemical Electrophilization of Si                                           |    |  |

|     |                                                           | Surface, 63                                                                             |    |  |

|     | 4.3.3                                                     | ·                                                                                       |    |  |

|     |                                                           | 4.3.3.1 Plasma Activation via Formation of Surface                                      |    |  |

|     |                                                           | Bond Defects, 65                                                                        |    |  |

|     |                                                           | 4.3.3.2 Plasma Activation via Removal of Surface Layers, 67                             |    |  |

|     |                                                           | Surface Activation by UHV Annealing, 67                                                 |    |  |

| 4.4 |                                                           | n-Temperature Bonding in a Conventional                                                 |    |  |

|     |                                                           | room, 67                                                                                |    |  |

|     | 4.4.1                                                     | <b>-----</b>                                                                            |    |  |

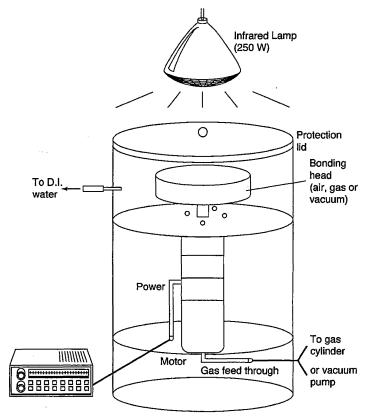

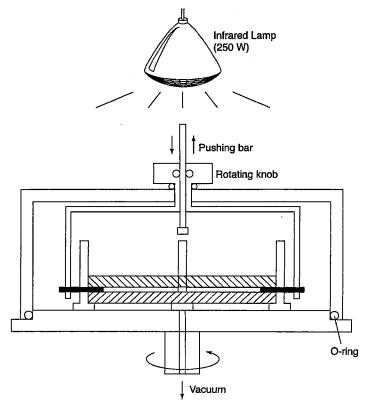

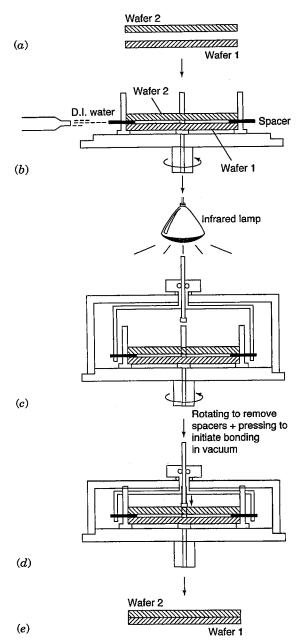

| 4 = |                                                           | Bonding Fixtures and Machines, 69                                                       |    |  |

| 4.5 | Setup                                                     | 1-Temperature Bonding with Micro-Cleanroom                                              |    |  |

| 4.6 | -                                                         | tion and Propagation of Bonding Front, 77                                               |    |  |

| 4.7 |                                                           | ace of Room-Temperature Bonded Si Pairs, 80                                             |    |  |

|     | 4.7.1                                                     | Interface of Room-Temperature Bonded Hydrophilic                                        |    |  |

|     |                                                           | Si Pairs, 80                                                                            |    |  |

|     | 4.7.2                                                     | Interface of Room-Temperature Bonded Hydrophobic                                        |    |  |

|     |                                                           | Si Pairs 87                                                                             |    |  |

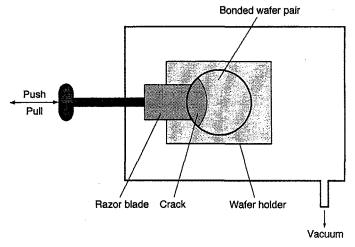

|                | 4.9.2            | Physics Background and Modeling, 90<br>One-Wafer Bent Concept, 91<br>Water-Enhanced Crack Opening, 92   |     |

|----------------|------------------|---------------------------------------------------------------------------------------------------------|-----|

| Refe           | rences           |                                                                                                         |     |

| Ther           | mal Tı           | reatment of Bonded Wafer Pairs                                                                          | 103 |

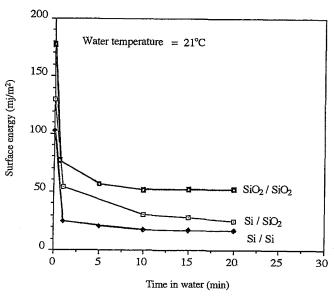

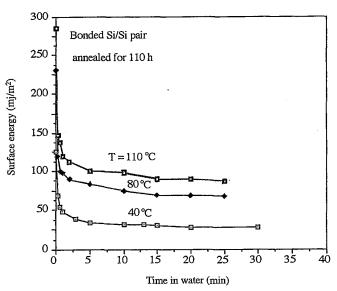

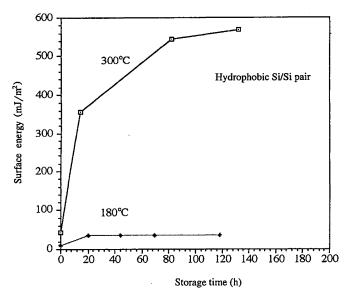

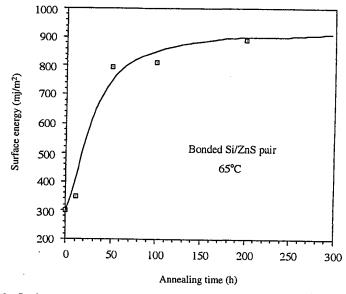

| 5.1            | Bondi            | ng Energy as a Function of Time, 103                                                                    |     |

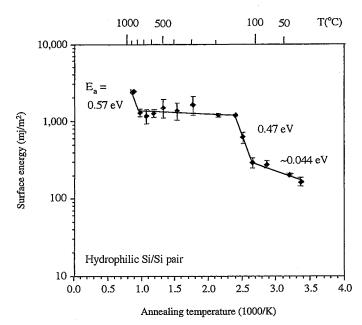

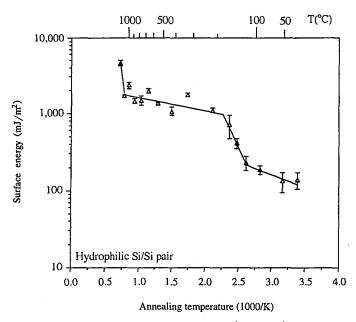

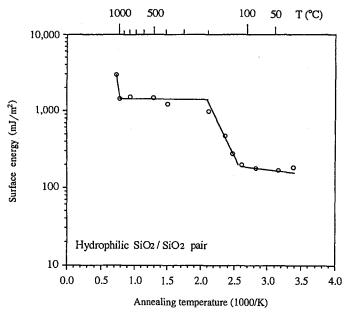

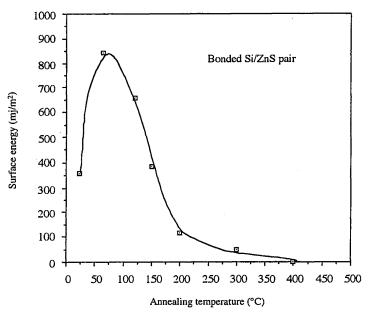

| 5.2            | Bondi            | ng Energy as a Function of Temperature, 106                                                             |     |

|                | 5.2.1            | SiO <sub>2</sub> /SiO <sub>2</sub> Pairs, 106                                                           |     |

|                | 5.2.2            | Bonding Energy of Hydrophobic Si/Si Pairs, 117                                                          |     |

| 5.3            |                  | Cemperature Wafer Bonding, 122                                                                          |     |

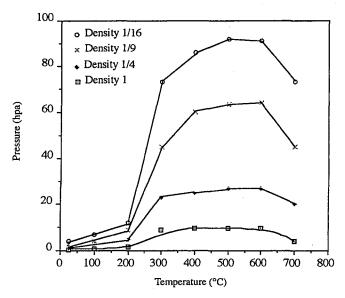

| 5.4            | Temp             | erature-Dependent Interface Bubbles, 123                                                                |     |

|                | 5.4.1            | Causes of Temperature-Dependent Interface<br>Bubbles, 123                                               |     |

|                | 5.4.2            | Prevention of Temperature-Dependent Interface<br>Bubbles, 127                                           |     |

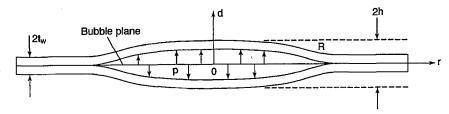

|                | 5.4.3            | A Simple Model of Bubble Formation, 127                                                                 |     |

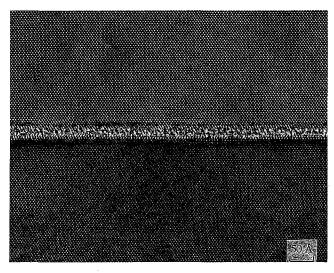

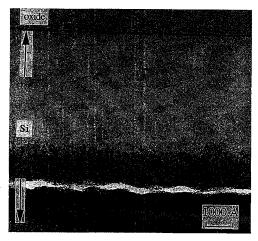

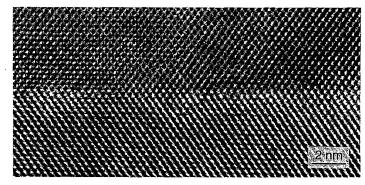

| 5.5            | Struct<br>Layers | ural Development of Thin Interfacial Oxide<br>s, 129                                                    |     |

|                | 5.5.1<br>5.5.2   | Influence of Rotational Wafer Misorientation, 131 Influence of Oxygen Content in Si Bonding Wafers, 132 |     |

| Refe           | erences          |                                                                                                         |     |

| Thir           | ning P           | Procedures                                                                                              | 137 |

| 6.1            | Mech             | anical Thinning, 137                                                                                    |     |

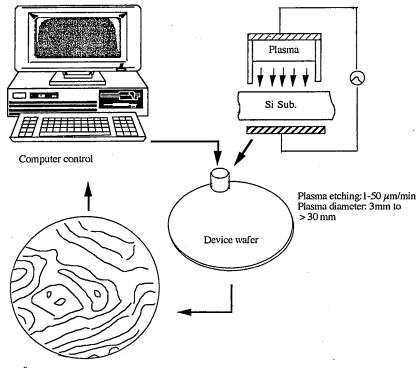

| ₹ <sup>*</sup> | 6.1.2            | Chemical-Mechanical Polishing, 137<br>Refinement by Local Thinning, 138<br>Polish-Stop Technology, 140  |     |

| 6.2            |                  | n Chemical Etching, 141                                                                                 |     |

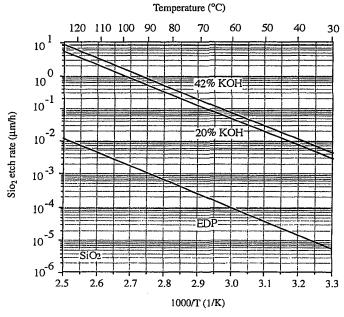

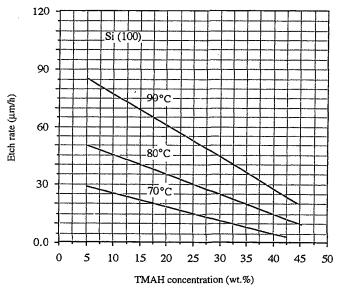

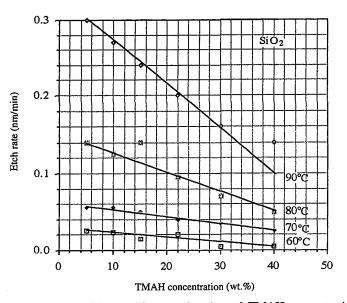

|                |                  | Aqueous Alkaline Etchants, 143                                                                          |     |

|                |                  |                                                                                                         |     |

4.8 Thick-Wafer Bonding, 88

4.9 Debonding, 89

5

6

| CONTENTS |  |

|----------|--|

|----------|--|

| :::  | CONTENTS |

|------|----------|

| VIII | CONTENTS |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

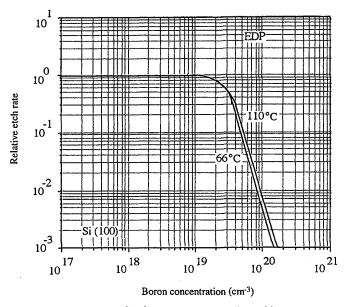

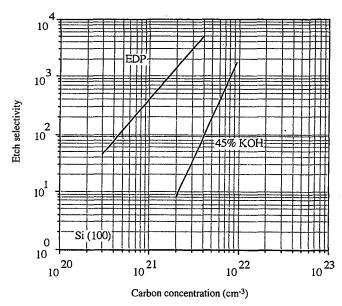

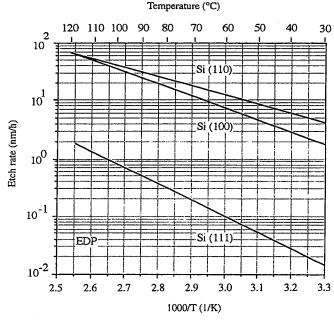

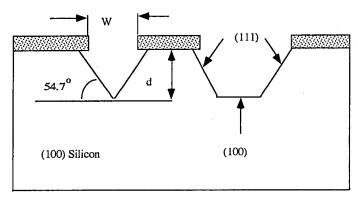

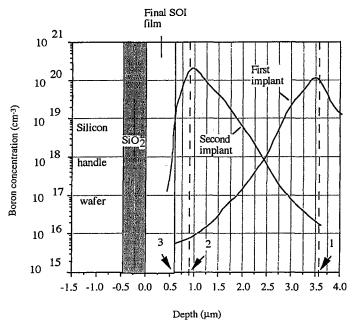

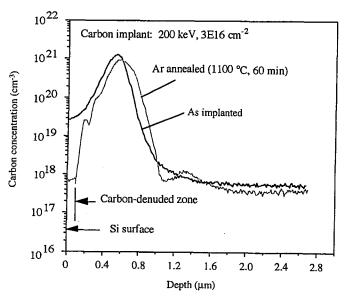

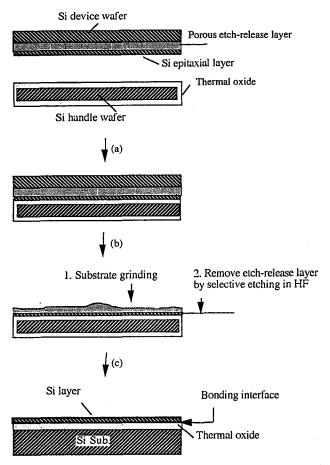

|   | 6.2.3 Silicon Anisotropic Etching, 151 6.2.4 Silicon Isotropic Etching, 153 6.3 Layer Transfer, 153 6.3.1 Layer Transfer by Bonding and Etch-Back, 154 6.3.1.1 B and B/Ge Etch-Stop, 154 6.3.1.2 Carbon-Implanted Etch-Stop, 157 6.3.1.3 Oxygen-Implanted Etch-Stop, 158 6.3.1.4 SiC Etch-Stop for Transfer of SiC Layers, 159 6.3.1.5 Porous Silicon Etch-Release Layer, 160 6.3.2 Layer Transfer by Bonding and Layer Splitting, 161 6.3.3 Layer Transfer by Bonding and Lateral Etching, 169 |                                                    | <ul> <li>9.1.3 Quartz Crystal/Si Bonding, 210</li> <li>9.1.4 Si/Quartz Glass Bonding, 210</li> <li>9.1.5 Si/Glass Bonding, 212</li> <li>9.1.6 Si/Sapphire Bonding, 212</li> <li>9.1.7 SiC on Insulator, 214</li> <li>9.2 Bonding Layers for Direct Bonding of Dissimilar Materials, 215</li> <li>9.2.1 CVD Silicon Oxide, 216</li> <li>9.2.2 CVD Polysilicon, 217</li> <li>9.2.3 CVD Silicon Nitride, 217</li> <li>9.2.4 CVD InP and Other Materials, 219</li> <li>References, 219</li> </ul> |     |

|   | References, 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    | 10 Bonding of Structured Wafers                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 223 |

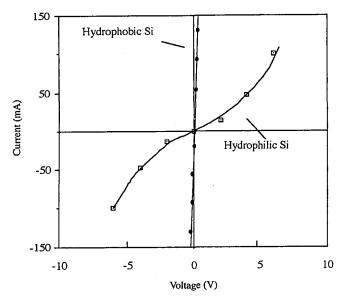

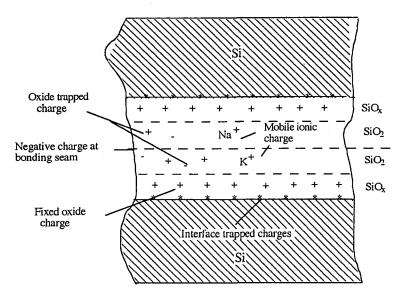

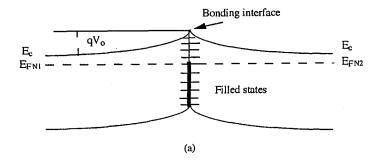

| 7 | <ul> <li>Electrical Properties of Bonding Interfaces</li> <li>7.1 Electrical Properties of Interfaces in Bonded Hydrophilic and Hydrophobic Si/Si Wafers, 175</li> <li>7.1.1 Charges in Bonded Si/Si Interface Region, 175</li> </ul>                                                                                                                                                                                                                                                           | 175                                                | <ul> <li>10.1 Design Considerations for Patterned Wafers, 223</li> <li>10.2 Bonding of Wafers with Cavities, 228</li> <li>10.3 Bonding of Partially or Fully Processed Wafers, 229</li> <li>References, 231</li> </ul>                                                                                                                                                                                                                                                                        |     |

|   | <ul><li>7.1.2 Boron Contamination at Bonding Interfaces, 179</li><li>7.1.3 Recombination Centers at Bonding Interface, 180</li></ul>                                                                                                                                                                                                                                                                                                                                                            |                                                    | 11 Mainstream Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 233 |

|   | <ul> <li>7.2 Electrical Properties of Si/SiO<sub>2</sub> and SiO<sub>2</sub>/SiO<sub>2</sub> Bonding Interfaces, 182</li> <li>7.2.1 Charges in Bonded Si/SiO<sub>2</sub> Interface Region, 181</li> <li>7.2.2 Charges in Bonded SiO<sub>2</sub>/SiO<sub>2</sub> Interface Region, 182</li> <li>7.3 Electrical Properties of Bonded Oxide, 184</li> <li>References, 185</li> </ul>                                                                                                               |                                                    | 11.1 Bonding Applications in VLSI, 233 11.1.1 Competing SOI Technologies, 233 11.1.2 Radiation-Hard SOI Devices, 234 11.1.3 DRAMs, 235 11.1.4 Low-Power, Low-Voltage CMOS, 237 11.1.5 Body Contacts of SOI MOSFETs, 239                                                                                                                                                                                                                                                                       |     |

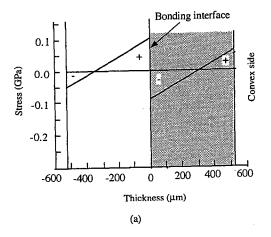

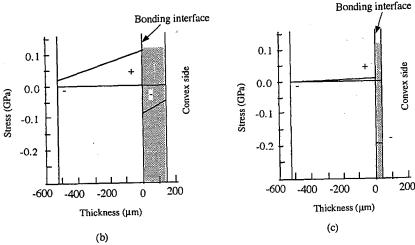

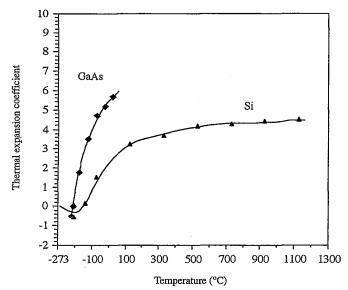

| 8 | Stresses in Bonded Wafers                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 187                                                | 11.2 Bonding Applications in High-Voltage and Power Devices, 239                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

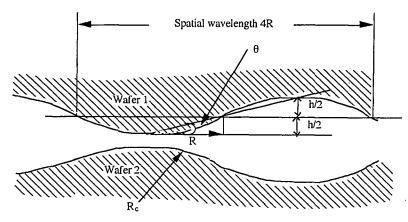

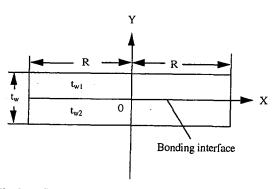

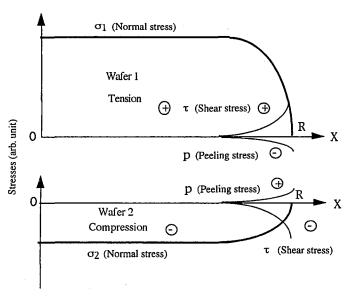

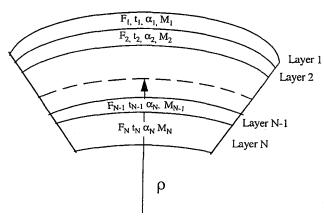

|   | <ul> <li>8.1 Stresses Caused by Surface Waviness, 187</li> <li>8.2 Stresses in Bonded Dissimilar Materials, 189 <ul> <li>8.2.1 Basic Analytic Equations, 189</li> <li>8.2.2 Stresses in Thin Films, 192</li> <li>8.2.3 Stresses in Bonded GaAs/Si Structures, 194</li> <li>8.2.4 Stresses in Bonded SOI and Multilayered Structures, 195</li> </ul> </li> <li>8.3 Bonding of Prestressed Wafers, 197 <ul> <li>References, 200</li> </ul> </li> </ul>                                            |                                                    | 11.2.1 Dielectric Isolation, 241 11.2.2 High-Voltage Devices, 245 11.2.3 High-Power Devices, 247 11.2.4 Smart-Power Circuits, 248 11.2.5 Buried Layer Structures, 250 11.3 Bonding Applications in Micromechanics, 252                                                                                                                                                                                                                                                                        |     |

| 9 | <b>Bonding of Dissimilar Materials</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 203                                                | 12 Emerging and Future Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 263 |

|   | <ul> <li>9.1 Bonding of Wafers of Dissimilar Materials, 203</li> <li>9.1.1 GaAs/Si Bonding, 204</li> <li>9.1.2 InP/Si Bonding, 207</li> </ul>                                                                                                                                                                                                                                                                                                                                                   | destriction (exployed) (stationable of experience) | 12.1 Bonding Applications in Optoelectronics, 263 12.1.1 Optoelectronic integrated circuits, 263 12.1.2 Low-Threshold, Long-Wavelength Lasers, 265                                                                                                                                                                                                                                                                                                                                            | 200 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | *                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

#### x CONTENTS

|      | 12.1.3  | Quasi-Phase-Matched Second-Harmonic                     |

|------|---------|---------------------------------------------------------|

|      |         | Generation, 265                                         |

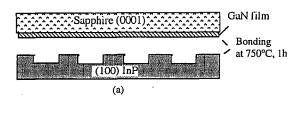

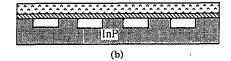

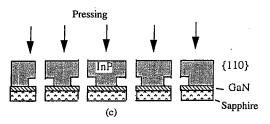

|      | 12.1.4  | Cleaved GaN Facet Mirrors on Sapphire                   |

|      |         | Substrates, 268                                         |

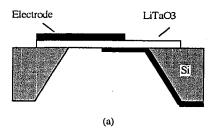

| 12.2 | Bondin  | g Applications in Electroacoustics, 269                 |

| 12.3 | Bondin  | g Applications in Electromagnetooptics, 271             |

| 12.4 | Surface | Protection of Semiconductor Wafers, 271                 |

| 12.5 | New M   | aterial Combinations, 272                               |

|      | 12.3.1  | Infrared Window Protection Using Si on ZnS Bonding, 272 |

|      | 12.3.2  |                                                         |

| 12.6 | Bondin  | g Interface as a Gettering Layer, 275                   |

| 12.7 | Researe | ch Applications, 277                                    |

|      | 12.7.1  | Room-Temperature UHV Bonding, 277                       |

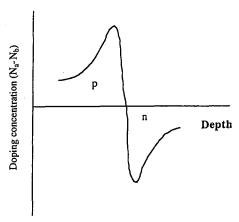

|      | 12.7.2  | Very Abrupt pn Junctions, 278                           |

|      | 12.7.3  | Self-Stressed Semiconductor Structures, 280             |

|      | 12.7.4  | Fabrication of Grain Boundary Structures, 281           |

|      | 12.7.5  | Investigation of Surface-Contamination, 282             |

|      | 12.7.6  | Determination of Surface Topology and Surface           |

|      |         | Energy, 282                                             |

|      | 12.7.7  | Formation of Uniformly Spaced Silicon                   |

|      |         | Wafers, 283                                             |

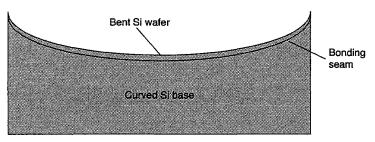

|      | 12.7.8  | Curved Single-Crystal Silicon X-Ray                     |

|      |         | Analyzer, 283                                           |

|      | 12.7.9  | Double-Gate SOI MOSFETs, 284                            |

|      | 12.7.10 | "Compliant" Substrates for High-Quality                 |

|      |         | Heteroepitaxial Growth, 285                             |

References, 286

Index 289

# **SERIES PREFACE**

The Solid-State Monograph Series of the Electrochemical Society (ECS) is aimed at providing detailed and focused expositions by recognized experts on current topics of interest in solid-state science and technology. ECS is an international, nonprofit, educational society serving over 7000 members engaged in solid-state and electrochemical science and technology (on the Web at http://www.electrochem.org). These topics are of broad interest to the various solid-state divisions of ECS, including the Electronics, the Dielectric Science and Technology, the High Temperature Materials, and the Luminescence and Display Materials divisions. The Energy Technology and the Sensor divisions also have extensive interests in solid-state topics. Each monograph is expected to include a historical discussion of the subject, an exposition of its current status, and a projection of future trends, along with appropriate scientific and technical content and literature references.

It is a pleasure to introduce the first volume in this Monograph Series, Semiconductor Wafer Bonding: Science and Technology, written by Q.-Y. Tong and U. Gösele of Duke University, North Carolina, USA and the Max-Planck-Institute for Microstructure Physics, Halle, Germany, respectively. Wafer bonding is the process that results in the joining of semiconductor wafers without the addition of an adhesive agent. It is a technique that has received extensive attention for its application in microelectronics, power electronics, microelectromechanical systems technology, and optoelectronics.

Wafer bonding has established itself as a commercial means for the production of silicon-on-insulator (SOI) wafers. Tong and Gösele are leading researchers in the field of wafer bonding, credited with inventing the Micro-CleanRoom setup for bonding, modeling the processes of hydrophobic and hydrophilic bonding, inventing the low-temperature bonding of dissimilar materials (such as Si/quartz, Si/glass, Si/SiC, Si/sapphire, Si/GaAs, and Si/InP), studying device-layer transfer of bonded and etched-back materials and circuits, inventing the Smarter-Cut process with the co-implantation of boron and hydrogen, introducing the bonding of ultrathick layers, and investigating the applications of low-vacuum bonding.

This monograph describes the role of fundamental physical and chemical mechanisms in the bonding process. It covers the practical aspects of the influence of particles, surface steps, and cavities, surface preparation techniques, the effects of thermal treatments, the electrical properties of bonded

#### xii SERIES PREFACE

interfaces, stresses in bonded wafers, and the bonding of dissimilar materials and structured wafers. This monograph then details the mainstream applications of bonding in VLSI, high-voltage and high-power devices, and micromechanics. It concludes with an assessment of emerging and future applications in optoelectronics, electroacoustics, electromagnetooptics, new materials combinations, and gettering applications.

Authors interested in contributing to this series are encouraged to contact the Chair of the Solid-State Monograph Committee or the ECS Publications Manager.

ECS Solid-State Monograph Committee Hisham Z. Massoud, Chairman Duke University massoud@ee.duke.edu ECS Publications Manager Mary E. Yess publications@electrochem.org

The Electrochemical Society, Inc. 10 South Main Street Pennington, NJ 08534-2896, USA

Tel: 1.609.737.1902 Fax: 1.609.737.2743

Web site: http://www.electrochem.org

# **PREFACE**

Wafer bonding allows one to join mirror-polished semiconductor or other wafers without the addition of any glue. Wafer bonding has been applied in microelectronics, power electronics, micromechanics, and optoelectronics to name just a few areas. Bonded silicon-on-insulators (SOI) wafers are commercially available from a number of companies. Materials that have been used for wafer bonding include not only silicon, but also III-V compounds, fused and crystalline quartz, glass, silicon carbide, sapphire, ferroelectrics and many other materials. Wafer bonding is deceivingly simple and allows one to produce a variety of materials combinations not available otherwise. Nevertheless, it appears that most researchers and engineers, when considering the use of wafer bonding technology, are initially confronted with a number of down-to earth questions and problems. The answers to these questions on wafer bonding are mostly available somewhere, but unfortunately are distributed over close to one thousand publications in a variety of journals, proceedings and book chapters. The present book tries to give in one volume the science governing wafer bonding and associated thinning processes as well as information on technology and applications of wafer bonding. The book is intended for materials scientists and electrical engineers charged or interested in taking advantage of the potential wafer bonding technology offers as well as for graduate students who would like to get familiar with this interdisciplinary field involving surface chemistry, solid state physics, materials science, and electrical engineering.

Over the past decade, we have done extensive research and consulting in the area of wafer bonding at Duke University, Durham, North Carolina, USA, at MPI of Microstructure Physics, Halle, Germany and at Southeast University in Nanjing, China. We would like to express our thanks to the many graduate students, post-docs, visiting scientists, and colleagues who made this research endeavor successful, challenging, and enjoyable. U. Gösele would like to express thanks specifically to two of the post-docs involved in the early wafer bonding research at Duke University, Reinhard Stengl and Volker Lehmann, both now at Siemens Research Laboratories, Munich, Germany. Their unconventional approaches inspired him to remain in this research area and uncover the science involved so that wafer bonding could be moved from the early stages with a touch of "black magic" to the attractive and flexible technology of today. Q.-Y. Tong is grateful for the

#### xiv PREFACE

constant support from the Microelectronics Center, Southeast University, China, where he has been enjoying a stimulating collaboration with the wafer bonding research group. He is indebted to his wife, Shi-Hui Kan and their children, Hui and Ling; without their support, understanding, and encouragement the book writing would have not been possible.

Our research over the years was supported by many companies such as Shin-Etsu-Handotai, AT & T, IBM, Texas Instruments, Siemens, Bosch, Ford, Intel, General Motors, Hughes Optical Systems, SOITEC and others, as well as by foundations and research organizations such as NREL, Argonne National Laboratory, Lord Foundation, Mobil Foundation, the German Ministry of Science and Technology, and the German Science Foundation. This support is highly appreciated. Finally, it is our pleasure to appreciate the input of Hisham Massoud from Duke University, who suggested to us to write this book many years ago and exerted gentle pressure to keep our interest in this book project alive.

Because of continuous advances in wafer bonding, the present book is far from being able to cover all aspects and developments in this area. We, nevertheless, hope that it proves to be helpful in advancing the field and that input from the readers will find its way into an extended edition in the near future.

QIN-YI TONG

Durham, North Carolina, USA

Ulrich Gösele

Halle, Germany

# THE ELECTROCHEMICAL SOCIETY SERIES

**Corrosion Handbook**

Edited by Herbert H. Uhlig

Modern Electroplating, Third Edition

Edited by Frederick A. Lowenheim

The Electron Microprobe

Edited by T. D. McKinley, K. F. J. Heinrich, and D. B. Wittry

**Chemical Physics of Ionic Solutions**

Edited by B. E. Conway and R. G. Barradas

**High-Temperature Materials and Technology**

Edited by Ivor E. Campbell and Edwin M. Sherwood

Alkaline Storage Batteries

S. Uno Falk and Alvin J. Salkind

The Primary Battery (in Two Volumes)

Volume I Edited by George W. Heise and N. Corey Cahoon Volume II Edited by N. Corey Cahoon and George W. Heise

**Zinc-Silver Oxide Batteries**

Edited by Arthur Fleischer and J. J. Lander

**Lead-Acid Batteries**

Hans Bode

Translated by R. J. Brodd and Karl V. Kordesch

Thin Films-Interdiffusion and Reactions

Edited by J. M. Poate, M. N. Tu, and J. W. Mayer

Lithium Battery Technology

Edited by H. V. Venkatasetty

Quality and Reliability Methods for Primary Batteries

P. Bro and S. C. Levy

Techniques for Characterization of Electrodes and Electrochemical Processes

Edited by Ravi Varma and J. R. Selman

Electrochemical Oxygen Technology

Kim Kinoshita

Synthetic Diamond: Emerging CVD Science and Technology Edited by Karl E. Spear and John P. Dismukes

Corrosion of Stainless Steels

A. John Sedriks

Fundamentals of Electrochemical Deposition Milan Paunovic and Mordechay Schlesinger

Semiconductor Wafer Bonding: Science and Technology Q.-Y. Tong and U. Gösele

The Electrochemical Society 10 South Main Street Pennington, NJ 08534-2896 USA http://www.electrochem.org

# SELECTED LIST OF SYMBOLS

| Symbol               | Definition                                                 |

|----------------------|------------------------------------------------------------|

| $\boldsymbol{A}$     | Area, Hamaker constant                                     |

| a                    | Lattice constant, radius of a hole                         |

| $\boldsymbol{C}$     | Concentration                                              |

| D                    | Diffusivity                                                |

| d                    | Distance between two wafers                                |

| $d_{\mathrm{OHi}}$   | Surface density of isolated silanol groups                 |

| $d_{\mathrm{OHH}}$   | Surface density of associated silanol groups               |

| $d_{\mathrm{Si-F}}$  | Surface density of Si-F bonds                              |

| $d_{\mathrm{Si-Si}}$ | Surface density of Si—Si bonds                             |

| $E_{ m total}$       | Total energy                                               |

| $E_{ m elas}$        | Elastic energy                                             |

| $E_{ m g}$           | Energy band gap                                            |

| $E_{ m hi}$          | Hydrogen bond energy of isolated silanol groups            |

| $E_{\mathtt{hH}}$    | Hydrogen bond energy of associated silanol groups          |

| $E_{\mathtt{hHF}}$   | Hydrogen bond energy of HF cluster                         |

| $E_{\rm Si-O}$       | Silanol bond energy                                        |

| $E_{\mathrm{Si-Si}}$ | Si—Si bond energy                                          |

| $E_{\mathtt{Si-F}}$  | Si—F bond energy                                           |

| $\boldsymbol{E}$     | Young's modulus, potential energy                          |

| E'                   | Biaxial modulus                                            |

| e                    | Electron charge                                            |

| $\boldsymbol{F}$     | Force                                                      |

| f                    | Misfit                                                     |

| $\boldsymbol{G}$     | Free energy                                                |

| $\sigma$             | Stress, charge density                                     |

| α                    | Thermal expansion coefficient, surface tension of a liquid |

| λ                    | Wavelength                                                 |

| γ                    | Specific surface energy                                    |

## xviii SELECTED LIST OF SYMBOLS

| $\gamma_{ m eff}^{\ m}$ | Effective specific energy in a medium         |

|-------------------------|-----------------------------------------------|

| $\gamma_{s, s}$         | Specific energy of bonded state               |

| $\gamma_{ m m,  s}$     | Specific energy of debonded state in a medium |

| $\boldsymbol{\theta}$   | Angle                                         |

| $	heta_{ m ws}$         | Contact angle                                 |

| ν                       | Poisson ratio, frequency                      |

| $\mu$                   | Mobility                                      |

| au                      | Shearing stress                               |

| H                       | Height of a gap                               |

| h                       | Height of a dip, Planck constant              |

| I                       | Moment of inertial                            |

| $\boldsymbol{k}$        | Reaction constant                             |

| $k, k_{\mathrm{B}}$     | Boltsman constant                             |

| l                       | Distance from a center                        |

| L                       | Crack length                                  |

| ε                       | Electric constant                             |

| N                       | Number of fringers                            |

| $\boldsymbol{P}$        | Pressure, power, peeling stress               |

| $\Delta P$              | Pressure difference                           |

| $P_{ m w}^{ m eff}$     | Effective water vapor pressure                |

| $P_{ m w}^{ m sat}$     | Saturated water vapor pressure                |

| ρ                       | Radius of curvature                           |

| R                       | Gap extension, radius                         |

| RT                      | Room temperature                              |

| S                       | Etching selectivity                           |

| TTV                     | Total thickness variation                     |

| $t, t_{\rm w}$          | Wafer thickness                               |

| $t_{ m f}$              | Film thickness                                |

| $t_{\rm b}$             | Razor blade thickness                         |

| $t_{\rm s}$             | Critical thickness of separator               |

| u                       | Small displacement                            |

| V                       | Molar volume                                  |

| W                       | Work                                          |

| $W_{\rm c}$             | Interaction energy                            |

| x                       | Distance from center                          |

|                         |                                               |

# SEMICONDUCTOR WAFER BONDING

# 1 Introduction

## 1.1 WHAT IS "WAFER BONDING"?

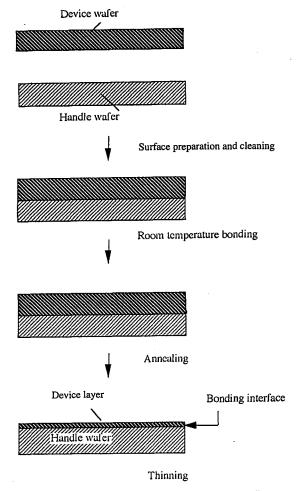

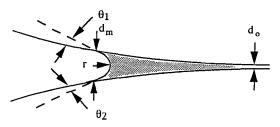

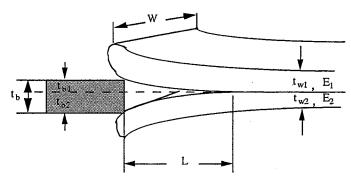

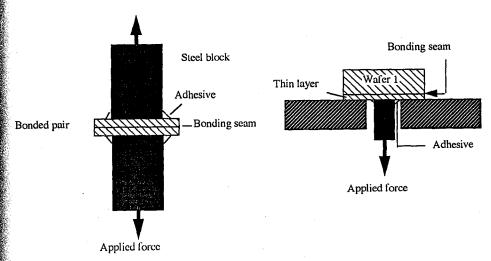

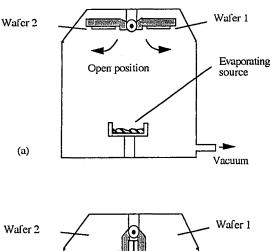

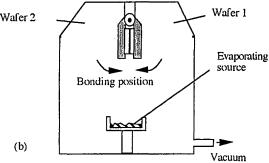

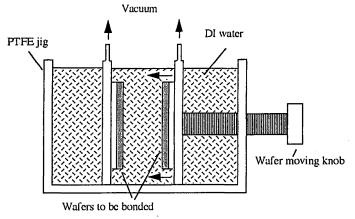

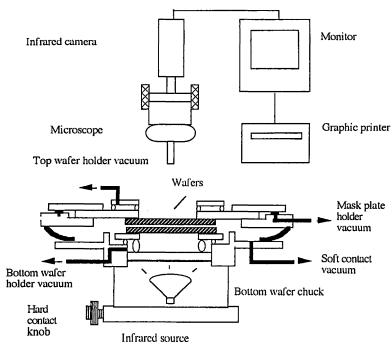

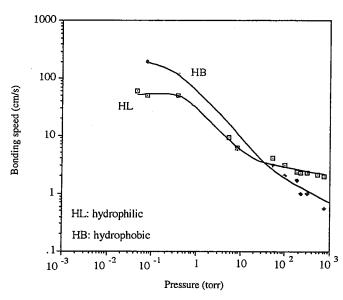

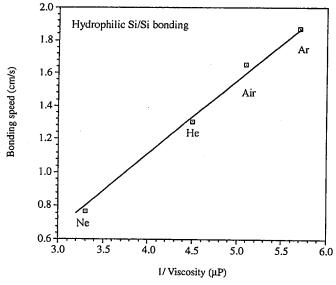

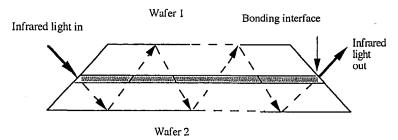

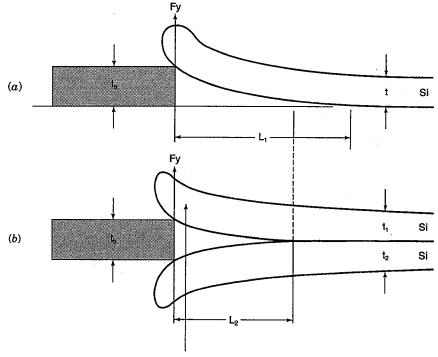

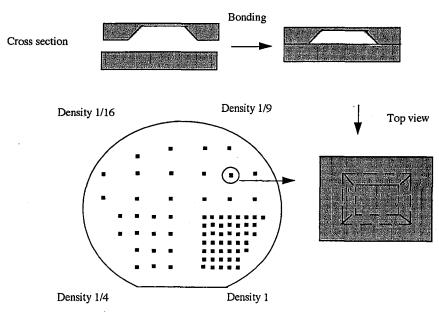

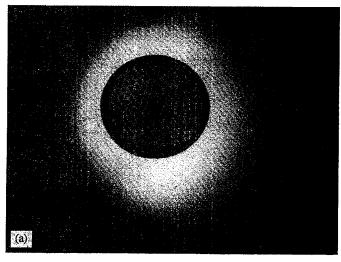

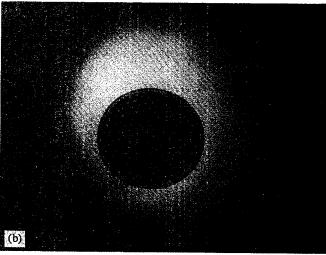

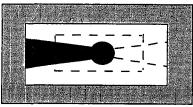

Wafer bonding" generally refers to a process by which two mirror-polished wafers adhere to each other at room temperature without the application of any macroscopic gluing layer or outside force. Wafer bonding is alternatively known as "direct bonding" and "fusion bonding" or more colloquially as "gluing without glue."/Although by no means required, in most cases the wafers involved in actual applications are typical semiconductor wafers consisting of single-crystalline material used in micro- or optoelectronics such as silicon or gallium arsenide. After starting the bonding process by locally applying a slight pressure to adjacent wafers, the bonded area spreads laterally over the whole wafer area, typically in a few seconds, as shown in Fig. 1.1. The bonding achieved at room temperature is usually relatively weak compared to the bonding within metallically, covalently, or ionically bonded solids. Therefore, for many applications, the room temperature bonded wafers have to undergo a heat treatment to strengthen the bonds across the interface. Frequently, one of the two wafers is then thinned to a thickness that depends on the specific application and may be in the range of many microns down to a couple of nanometers. This generic process flow is schematically shown in Fig. 1.2. Modifications of this process flow are quite common for specific applications, (for example, no heating or thinning step may be involved, or the heating and bonding steps may be combined).

This book deals with the underlying science of wafer bonding in many of its variants as well as technological and application questions. In this chapter, a short historical background and an explanation of the growing interest in wafer bonding during the past decade are given. Typical problems and solutions involved in wafer bonding are also mentioned in a general way. Detailed discussions of various topics are contained in the chapters that follow.

#### 1.2 HISTORICAL BACKGROUND

The adhesion of solids to each other has been observed for centuries. In 1792 Desagulier showed that two spheres of lead, when pressed together, strongly

SAMSUNG EXHIBIT 1008 Samsung v. Invensas Bonding

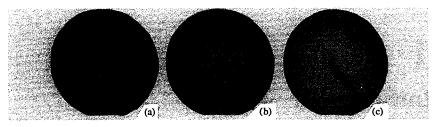

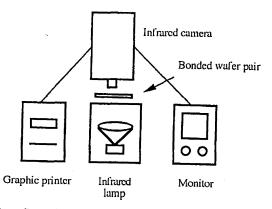

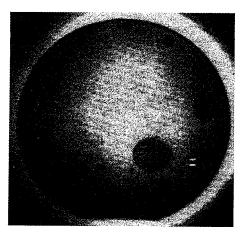

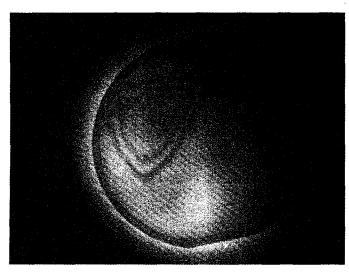

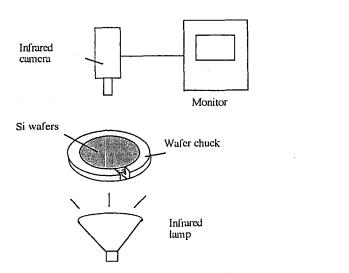

Fig. 1.1 Infrared picture of initiation and propagation of a bonding wave in wafer bonding of 4-in. silicon wafers. (a) Local starting of the contact wave, (b) extension after about 2 sec, and (c) complete bonding after about 5 sec. The radial dark line comes from the tong used to initiate the bonding.

adhere to each other (1). In this case strong plastic deformation is involved, which is not a desirable option for typical, highly brittle semiconductor wafers. The phenomenon that optically polished bulk pieces of metals, used for precision length measurements, stick to each other was observed about a century ago by German craftsmen and termed "Ansprengen" or "jumping into contact." The analogous phenomenon was found also for optically polished glasses such as precision prisms. This effect was and still is used to precisely position optical elements with respect to each other without leaving an optically undesirable space between the elements. The first systematic investigation of room temperature adhesion between two optically polished glass plates was performed in 1936 by Lord Rayleigh (2) who was the first to determine that the interaction energy per area was on the order of 100 mJ/m². For a long time, this adhesion phenomena did not have any noticeable technological impact except in the well-known traditional area of optics, and now and then for some isolated specific applications.

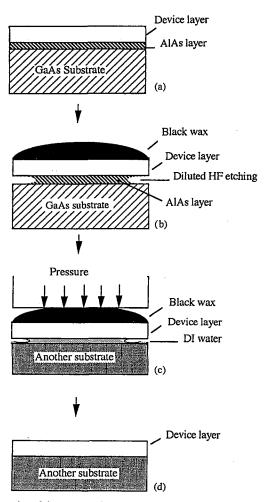

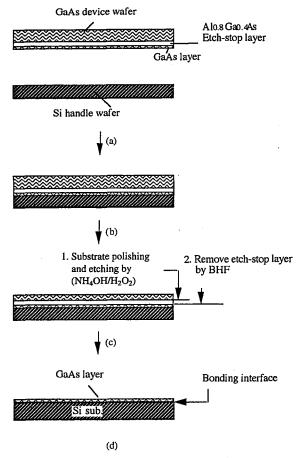

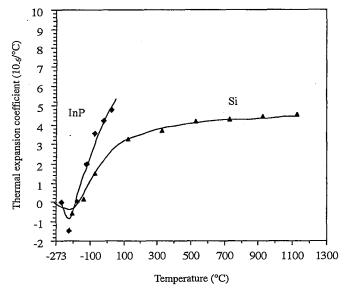

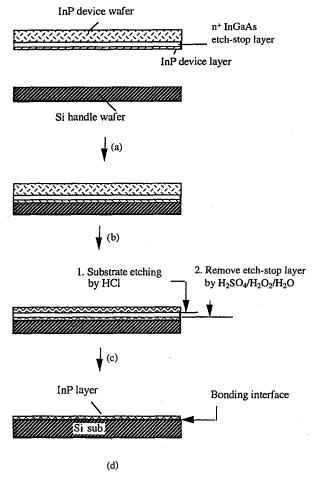

The bonding of silicon wafers to sodium-containing glass wafers at elevated temperatures (around 500°C) under the influence of an applied electric field was pioneered by Wallis and Pommerantz in 1969 (3). Ever since it has been used in the area of encapsulation of sensors. This type of bonding, termed "anodic bonding," is restricted to electrically conducting glasses with a thermal expansion coefficient close to that of the semiconductor wafer to be bonded and the presence of mobile ions, such as sodium, which is not desirable for most advanced microelectronic devices. We will, therefore, hardly touch on the subject of anodic bonding, although there are a number of similarities to the direct bonding described in this book. For an overview of anodic bonding, the reader is referred to a review by Obermeier (4). The transfer of a thin gallium arsenide layer to a glass substrate was first performed by "wafer fusion" at elevated temperatures by Antypas and Edgecumbe in 1975. They used an epitaxial, aluminum-rich AlGaAs etch-stop layer to etch off the GaAs substrate but leave a thin GaAs layer to be transferred. This etch-stop concept became essential for many wafer bonding applications (5)

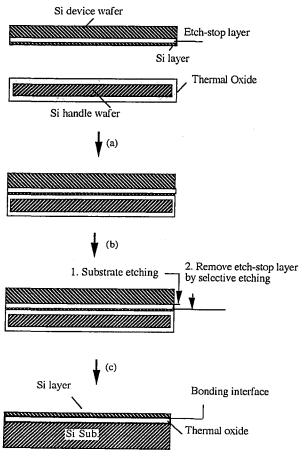

Fig. 1.2 Schematic of wafer-bonding process flow.

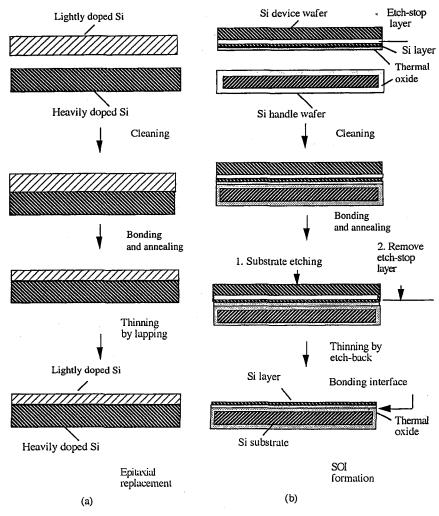

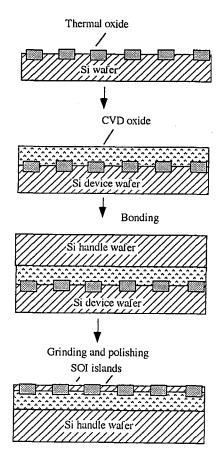

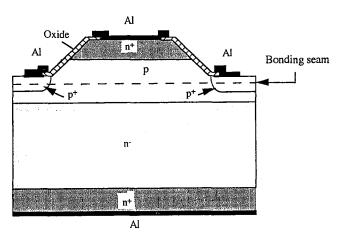

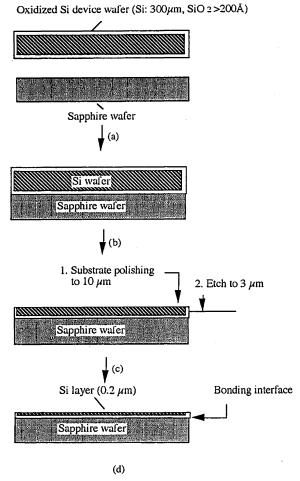

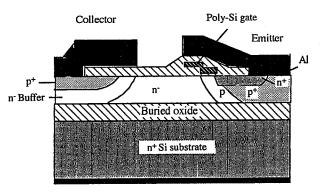

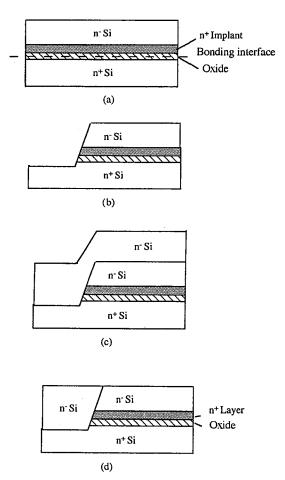

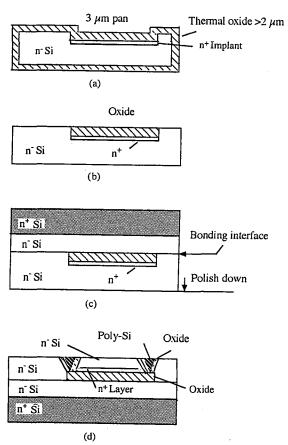

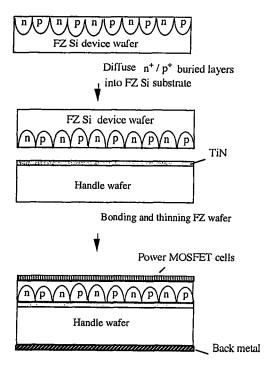

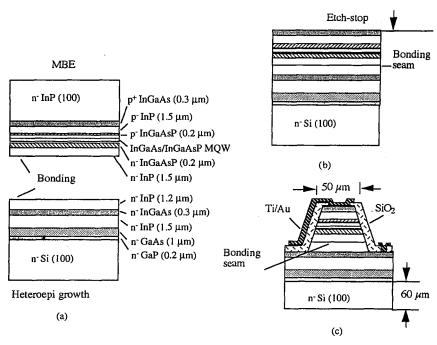

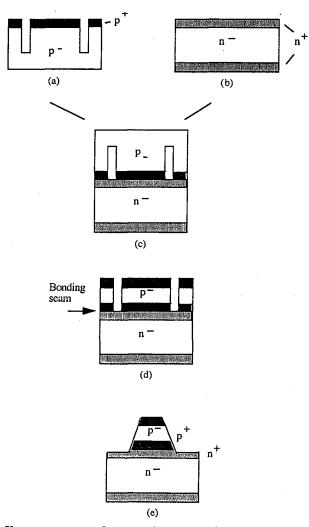

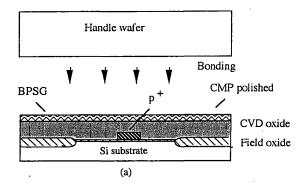

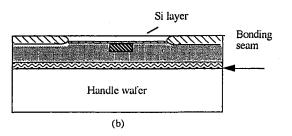

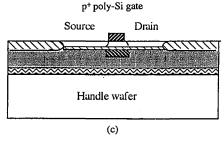

Widespread interest in modern wafer bonding techniques was generated by reports on silicon-silicon wafer bonding by two groups (6-8) in 1985-1986 in which the initial bonding of the two wafers at room temperature was followed by a high-temperature bond-strengthening heat treatment. Shimbo and co-workers from Toshiba (6) investigated the bonding of silicon wafers without any thermal oxide between the wafers. Wafer bonding served as a substitute process for the growth of thick epitaxial layers of single-crystalline silicon on silicon for potential applications in power devices (Fig.1.3a). In contrast, Lasky from IBM (7,8) bonded two silicon wafers, with one or both of the wafers being covered by a thermally grown, electrically insulating, silicon dioxide layer (Fig.1.3b). One of the silicon wafers was thinned to

#### INTRODUCTION

Fig. 1.3 Schematic of bonded and thinned silicon wafers (a) for replacement of an epitaxial layer and (b) for silicon-on-insulator (SOI) structure.

a few microns, leaving a thin single-crystalline silicon layer on top of an insulator layer (the thermally grown oxide layer), which is on top of a silicon handle wafer. The silicon handle wafer acts mainly as a mechanical support for the thin-layer structure. This silicon-on-insulator (SOI) structure is desirable because of its high resistance against the undesirable side effects of radiation-induced electron-hole pair generation encountered in outer-space experiments or for military purposes. This "radiation hardness," which had originally driven the development of SOI materials including silicon-on-

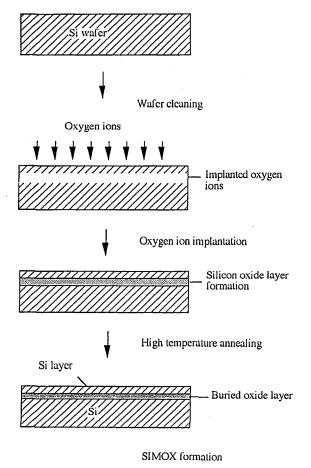

Fig. 1.4 Schematic of SIMOX approach.

sapphire (SOS) and others, is however of minor importance compared to commercial applications based on the ability of SOI materials to allow operation at lower voltages (e.g., for hand-held devices) and a higher packing density of devices as well as the simultaneous use of low- and high-voltage devices on one chip (9). At the time of Lasky's fabrication of SOI material by silicon wafer bonding and thinning, the main approach to generate equivalent silicon structures was based on high-energy, high-dose implantation of oxygen ions into silicon. At temperatures close to the melting point of silicon, the implanted oxygen agglomerates in the form of a continuous buried layer of silicon dioxide. This so-called Separation by IMplanted OXygen (SIMOX) (10, 11) approach (Fig. 1.4) left a high density of implantation-induced dislocations in the silicon layer and, in addition, was very expensive. At the

time it was hoped that silicon wafer bonding and thinning would constitute a less expensive and technologically much simpler approach to fabricate SOI layers with the added advantage that the silicon layer would be as good as the bulk silicon material since no implantation damage was involved.

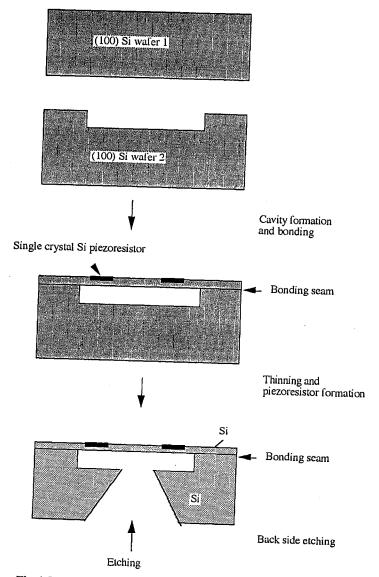

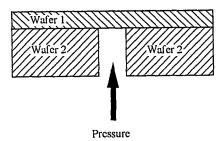

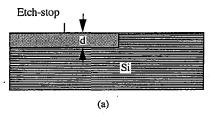

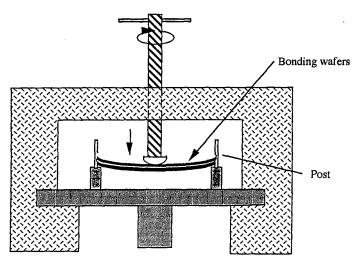

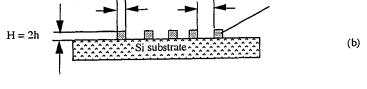

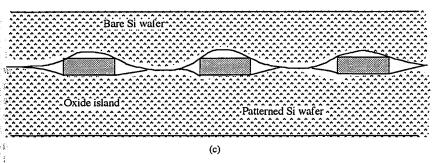

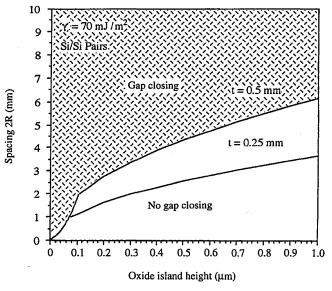

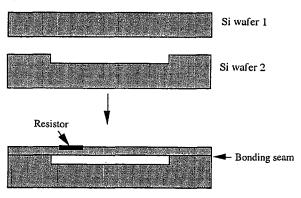

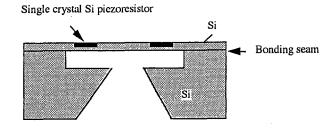

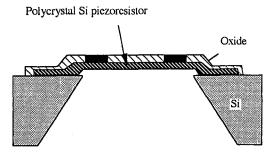

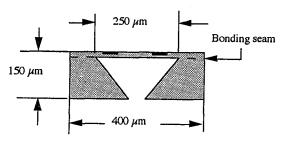

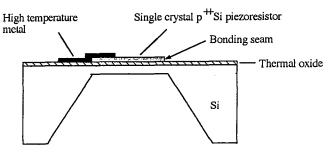

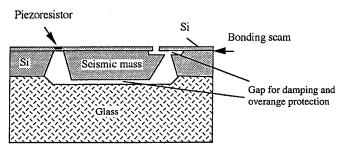

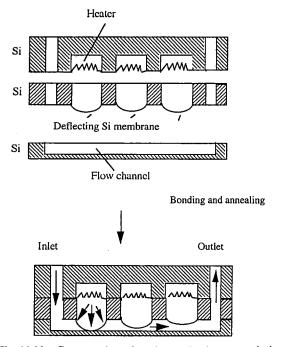

Parallel to the electronics-related work on silicon wafer bonding at Toshiba and IBM, in 1988 Petersen and Barth (12) pioneered the use of silicon wafer bonding for pressure sensors, in which at least one of the silicon wafers was structured containing holes or cavities (Fig. 1.5). The process was termed "fusion bonding" and actually went into production.

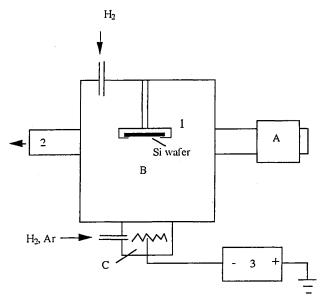

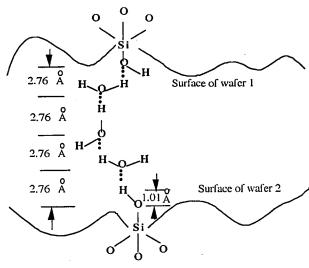

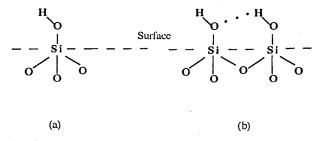

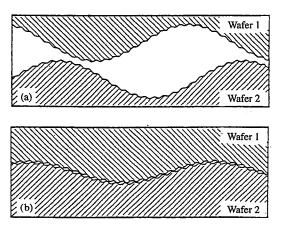

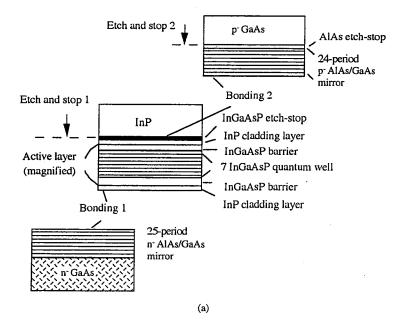

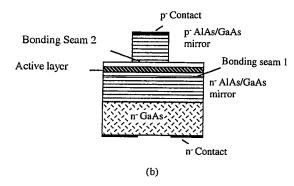

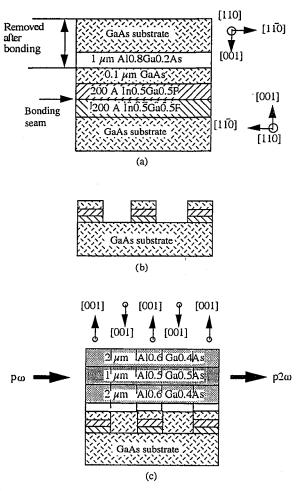

Although the work of Shimbo et al. (6) and Lasky (7, 8) generated a lot of interest and follow-up research, it did not immediately lead to viable products in the area of microelectronics, because the difficulties associated with wafer bonding were also noticed quickly. The success of bonding depends critically on surface properties, chemical cleaning and conditioning of the surfaces, and to a certain extent on the atmosphere (air, humidity, vacuum) in which the initial bonding is performed/Particles that remain attached to the surfaces to be bonded locally prevent bonding and lead to unbonded areas (termed "interface bubbles" or "voids") with lateral extensions of many millimeters for particles in the micron range. Frequently, interface bubbles are even generated during the heat-treatment step and are not related to particles. Uniform thinning of one of the wafers was a major obstacle. Based on these difficulties, wafer bonding was characterized as "black magic" and as a technology that is not easily manufacturable. Fortunately, during the last decade, the science behind wafer bonding has been investigated thoroughly and most of the difficulties associated with silicon wafer bonding have been ironed out, so that little if any black magic remains, as documented in many review articles (13-22), the proceedings of various wafer bonding conferences (23-26), and a special journal issue on wafer bonding (27). The recent announcement (August 1988) by IBM of a new microchip breakthrough using the SOI technology to boost the performance of computers and communication systems by 35% clearly demonstrates that SOI is becoming the mainstream technology for the next generation of VLSI industry. Not only are bonded SOI wafers now commercially available from a variety of vendors, but a range of other possible applications has opened up, for example, in micromechanics (14, 16, 21) and in optoelectronics (28-30) involving the bonding of III-V compound wafers at elevated temperatures in hydrogen. This book presents not only the science behind wafer bonding technology, but also information on the more mundane aspects of wafer bonding such as cleaning, etching, and thinning procedures. The book touches upon some mainstream applications as well as some approaches that are presently in the research stage or are rather esoteric in nature. In the following section, a short overview of why wafer bonding is such an interesting approach for materials combinations in general and what basic opportunities wafer bonding offers is given.

Fig. 1.5 Schematic of pressure sensor fabricated by wafer bonding.

# 1.3 WAFER BONDING: ADVANTAGES AND OPPORTUNITIES

After the discussion of the early difficulties associated with wafer bonding in the previous section, a question arises as to the benefits of applying wafer bonding as compared to other methods of joining solids or depositing or growing thin layers on appropriate substrates. Obviously, wafer bonding requires mirror-polished surfaces, whereas most other methods of joining bulk materials, such as gluing, soldering, or welding, can tolerate fairly rough surfaces. For most of the technical applications of wafer bonding, the requirement of mirror-polished surfaces is not a major obstacle, basically for three reasons:

- 1. As long as comparatively thin wafers are used (in the range below about a millimeter in thickness), the wafers can relatively easily conform to each other and adapt a possible small bow by elastic deformation during bonding. Therefore, in contrast to the expensive "optical polishing" necessary for bonding of bulk pieces (which requires a flatness over the entire surface within a quarter of an optical wavelength, which would limit surface variations to about 100 nm over the whole surface), only "mirror polishing" with much less stringent requirements is required (as described in detail in Chapter 3).

- 2. Most of the wafers used, such as silicon or gallium arsenide wafers, come in mirror-polished form for reasons not associated with bonding, so that frequently no additional polishing step is required for the wafer-bonding process.

- If the wafer surfaces contain an unfavorable surface topography from previous processing steps, so that polishing is required, this is not a major obstacle because of the wide availability of chemomechanical-polishing (CMP) equipment in any modern microelectronics facility (owing to the steadily increasing need of planarization processes in device fabrication).

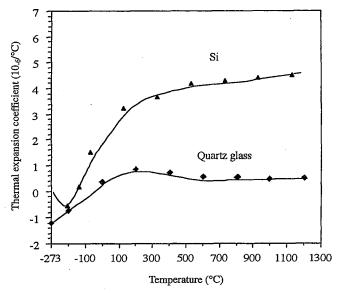

Obviously, wafer bonding, if performed properly, is a convenient joining technology which involves no macroscopical gluing or soldering layer and, consequently, no harmful contamination. It allows the joined wafers (if not prohibited by large differences in thermal expansion coefficients of the bonded wafers) to be heated to temperatures well above the thermal stability of conventional organic glues. It works not only for silicon but for many different materials provided they can be polished properly, as demonstrated for room-temperature bonding by Haisma et al. (20) and shown in Table 1.1. Typical wafer-bonding procedures are also fully compatible with microelectronics processing technologies and can thus easily be integrated using equipment already available for microelectronic or micromechanic device manufacturing.

Joining of whole blank or structured wafers is just one of the more mundane applications. The more exciting possibility, which wafer bonding

TABLE 1.1 Experimental Results of Bondability of Various Material Combinations (Bonding Material A to Material B) $^a$

|                                                    | Mate            | erial B        |                         |  |

|----------------------------------------------------|-----------------|----------------|-------------------------|--|

| Material A                                         | Quartz Glass    | Hydrophilic Si | Material B = Material A |  |

| Metal                                              |                 |                |                         |  |

| Ta (poly* layer on Si)                             | ++              | ++             |                         |  |

| Ti (poly* layer on Si)                             | ok              | ok             | ++                      |  |

| W (poly* layer on Si)                              | Local weak bond |                | _                       |  |

|                                                    | under pressure  | under pressure | _                       |  |

| Cu poly                                            | +               | +              | 27.74                   |  |

| Semimetal                                          | +               | +              | N/A                     |  |

| Bi poly                                            |                 | Τ              | N/A                     |  |

| Semiconductor                                      | ++              | 1.1            |                         |  |

| Si                                                 | 1.1.            | ++             | ++                      |  |

| Ge                                                 | ++              |                |                         |  |

| B (poly* layer on Si)                              | +               | ++             | ++                      |  |

| GaAs                                               |                 | +              | +                       |  |

| InP                                                | ++<br>++        | ++             | ++                      |  |

| Superconductor                                     | ++              | ++             | ++                      |  |

| YBa <sub>2</sub> Cu <sub>3</sub> O <sub>7-8</sub>  | <del>1-</del>   | +              | _                       |  |

| (polycrystalline)                                  |                 |                |                         |  |

| Oxide                                              |                 |                |                         |  |

| SrTiO <sub>3</sub>                                 |                 |                |                         |  |

| $ZrO_2Y_2O_3$                                      | ++              | ++             | +                       |  |

| Ferroelectric                                      | ++              | ++             | +                       |  |

| BaTiO <sub>3</sub> (poly*)                         |                 |                |                         |  |

| LiNbO <sub>3</sub>                                 | +               | +              | +                       |  |

| Fluoride                                           | +               | +              | +                       |  |

| BaF <sub>2</sub>                                   |                 |                |                         |  |

|                                                    | ++              | +              | +                       |  |

| CeF <sub>3</sub> (on glass)<br>Nitride             | +               | +              | +                       |  |

|                                                    |                 |                |                         |  |

| Si <sub>3</sub> N <sub>4</sub> (poly* layer on Si) | +               | +              | _                       |  |

| AlN (polycrystalline) Carbide                      | +               | +              | <del></del>             |  |

| =                                                  |                 |                |                         |  |

| B <sub>4</sub> C (polycrystalline)                 | +               | +              | N/A                     |  |

| Diamond                                            | +               | +              | Very weak               |  |

| Insulator                                          |                 | ,              | , or weak               |  |

| ZnSe (polycrystalline)                             | ++              | ++             | ++                      |  |

<sup>&</sup>lt;sup>a\*</sup>: Polycrystalline; ++: very good; +: good; -: no bond; N/A: not investigated.

offers, is the fabrication of single crystalline layers of material A on almost any kind of appropriately polished substrate B, even if the substrate is amorphous, polycrystalline, or single crystalline but of a very different lattice constant or crystallographic orientation. Usually, a single crystalline layer can be grown only on top of a single crystalline substrate of the same material (i.e., homoepitaxial growth, silicon on silicon) or a different material which

has a lattice constant closely matching that of the desired layer to be grown (i.e., heteroepitaxial growth, AlAs on GaAs). If the lattice constants of layer and substrate material differ by a percent or more, the layer will first grow elastically strained, and then, after exceeding a critical thickness, will introduce so-called misfit dislocations at the interface. Because these dislocations generally nucleate at the surface and glide to the interface, these films will contain a high density of dislocations threading through the grown film, thus rendering the film unsuitable for many electronic or optoelectronic applications.

Based on this knowledge of epitaxial growth of single crystalline layers, materials scientists, solid state physicists, and electrical engineers developing solid-state devices have been trained to accept that single crystalline layers generally cannot be fabricated on amorphous, polycrystalline, or single crystalline material that is grossly lattice-mismatched or on the same crystalline material but with an unrelated lattice orientation. Wafer bonding, as described in this book, in many cases allows one to overcome these restrictions, but not in the form of layer growth but rather by transferring a thin single crystalline layer from a first substrate to a second substrate (amorphous, polycrystalline, or nonfitting crystalline). Thus, wafer bonding opens up the possibility of preparing combinations involving single crystalline materials excluded previously because of the lack of a proper crystallographic relationship. Such possible applications are astonishingly diverse and apparently limited more by our lack of imagination than by technological constraints. Two recent developments involving wafer bonding demonstrate this versatility.

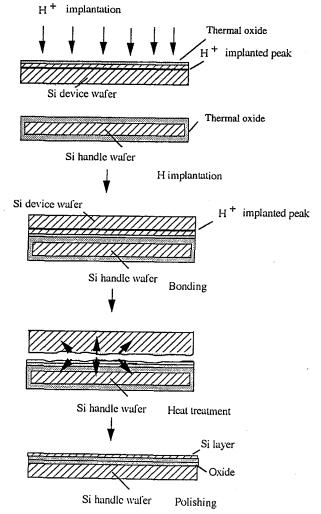

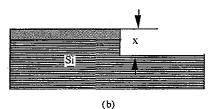

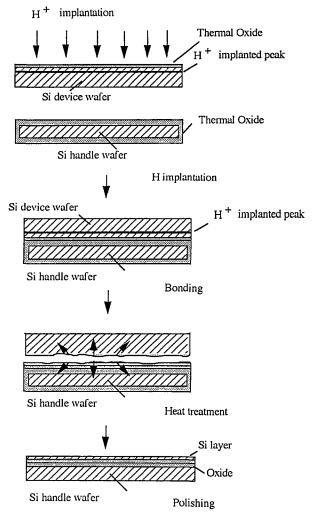

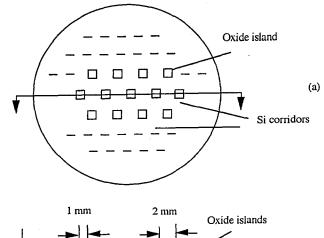

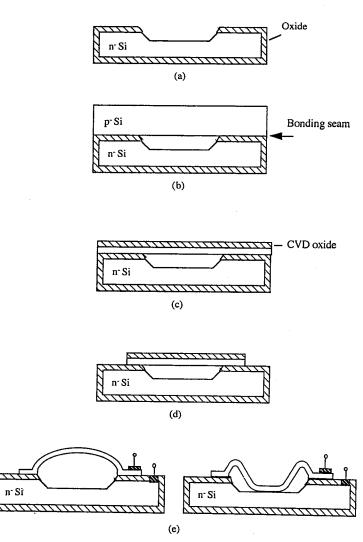

The first development concerns the thinning technology utilized after wafer bonding occurs. It had been commonly assumed that thinning of one of the wafers would be associated with the loss of most of this wafer by grinding, lapping, polishing, or etching away everything except the layer to be transferred. The "smart-cut" process recently developed by Bruel (31, 32) has demonstrated that this assumption is not necessarily true. The process flow is schematically shown in Fig. 1.6. In this process, hydrogen ions are implanted before bonding into one of the wafers from which a thin layer should be transferred. Then the wafers are bonded and heated (in the case of silicon to about 500°C), which leads to the development and growth of hydrogeninduced microcracks parallel to the bonding interface. Finally, by growth of the microcracks, the splitting of a thin layer away from the implanted substrate occurs. The transferred layer shows an excellent thickness uniformity. Only slight touch polishing is required to achieve a surface equivalent to typical silicon surfaces. The split-off wafer has typically lost only a layer on the order of 1  $\mu$ m from a thickness of 500-1000  $\mu$ m and can thus be used further after repolishing. Repeated application of this process might well lead to major advances in the fabrication of three-dimensionally stacked electronic devices. Presently the process only works for silicon, germanium, diamond, gallium arsenide (33), and silicon carbide (34, 35); it is quite

Fig. 1.6 Schematic of different steps in the "smart-cut" process.

possible that further research might enable the splitting of other materials such as ferroelectrics and oxides.

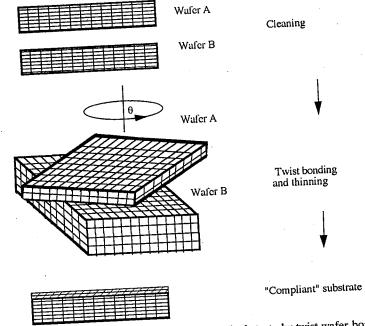

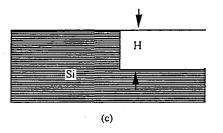

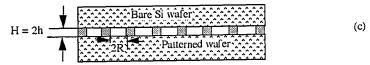

The second astounding development concerns the application of twist wafer bonding to generate a so-called "compliant" substrate. A compliant substrate allows the heteroepitaxial growth of materials with a large misfit in their lattice constants with a drastically reduced density of threading dislocations, even if the heteroepitaxial layer exceeds many times the critical

Fig. 1.7 Schematic of fabrication of "compliant" substrate by twist-wafer bonding.

thickness (36) for the generation of misfit dislocations. The basic idea is that misfit dislocation formation could be prevented if the heteroepitaxial growth occurred on a basically free-standing thin film which is below its critical thickness (37, 38). Although the validity of this concept has been shown experimentally (39), it is not practical to work with free-standing films of a thickness on the order of a few nanometers. Rather, it would be desirable to connect this film to a substrate in such a way that it can easily shift laterally with respect to the substrate. One approach to fabricate such a "compliant" substrate involves wafer bonding. The idea here is to generate a weakly bonded zone by the interface between two wafers bonded under a large twist angle such as 10-30° (40, 41). The resulting structure is schematically shown in Fig. 1.7. The system investigated first was that of a (100) GaAs layer twist bonded on a (100) GaAs substrate. The etch-stop method used was that suggested by Antypas and Edgecumbe in 1975 (5) involving a thin etch-stop layer of GaAlAs with a sufficiently high Al concentration grown epitaxially on a GaAs substrate, followed by a second 3- to 10-nm thick epitaxial layer of GaAs to be transferred. The bonding was performed under high mechanical compression and hydrogen flow at temperatures over 500°C. Heteroepitaxial growth of different materials ranging from In<sub>0.35</sub>Ga<sub>0.65</sub>P (40) to InSb (41) (with misfits ranging from about 1 to 15%, respectively) well above their respective critical thickness did not show any threading dislocations in cross-sectional electron micrographs. It is not yet understood how "compliant" substrates really work (42). Nevertheless, if actually reproducible, this approach of twist wafer bonding could be extended to Si/Si bonding or any combination of appropriate materials and allow heteroepitaxial growth of misfitting material without the usual drawback of threading dislocations which are detrimental in many electronic or optoelectronic applications.

In the rest of the book, various aspects of wafer bonding are considered in some detail. Chapter 2 gives a fairly general discussion of interactions between surfaces; Chapter 3 addresses the influence of particles and surface steps; and Chapters 4 and 5 thoroughly discuss surface preparation, room-temperature bonding procedures, and thermal treatments. Chapter 6 is devoted to presently available thinning procedures and Chapter 7 to the electrical properties of bonding interfaces. Chapter 8 deals with stresses in bonded wafers in general and Chapter 9 with bonding of dissimilar materials for which the occurrence of mechanical stresses due to different thermal expansion coefficients is of major concern. Chapter 10 concentrates on the bonding of structured wafers as important mostly for micromechanical applications. Chapters 11 and 12 deal with mainstream and emerging applications, respectively.

### REFERENCES

- 1. D. Dawson, History of Tribology, Longman, London, 1979.

- Lord Rayleigh, "A study of glass surfaces in optical contact," Proc. Phys. Soc., A156, 326 (1936).

- G. Wallis and D. I. Pommerantz, "Field assisted glass-metal sealing," J. App. Phys. 40, 3946 (1969).

- 4. E. Obermeier, "Anodic wafer bonding," Proceedings of the 3rd International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, Vol. 95-7, The Electrochemical Society, Pennington, NJ, 1995, p. 212.

- 5. G. A. Antypas and J. Edgecumbe, "Glass-sealed GaAs-AlGaAs transmission photocathode," *Appl. Phys. Lett.* **26**, 371 (1975).

- M. Shimbo, K. Furukawa, K. Fukuda, and K. Tanzawa, "Silicon-to-silicon direct bonding method," J. Appl. Phys. 60, 2987 (1986).

- 7. J. B. Lasky, S. R. Stiffler, F. R. White, and J. R. Abernathy, "Silicon-on-insulator (SOI) by bonding and etch-back," *Proceedings of the IEEE International Electronic Device Meeting*, IEEE, Piscataway, NJ, 1985, p. 684.

- 8. J. B. Lasky, "Wafer bonding for silicon-on-insulator technologies," Appl. Phys. Lett. 48, 78 (1986).

- J. P. Colinge, Silicon-on-Insulator Technology: Materials to VLSI, 2nd ed., Kluwer Academic, Boston, 1997.

- K. Izumi, M. Doken, and H. Ariyoshi, "CMOS devices fabricated on buried SiO<sub>2</sub> layers formed by oxygen implantation into silicon," *Electron Lett.* 14, 593 (1978).

- 11. S. Cristoloveanu and S. S. Li, Electrical Characterization of Silicon-On-Insulator Materials and Devices, Kluwer Academic, Boston, 1995.

- 12. K. Petersen, P. W. Barth, J. Poydock, J. Brown, J. Mallon, and J. Bryzek, "Silicon fusion bonding for pressure sensors," *Proceedings of the IEEE Solid State Sensor and Actuator Workshop*, Hilton Head, SC, 1988, p. 144.

- J. Haisma, B. A. C. M. Spierings, U. K. P. Biermann, and J. A. Pals, "Silicon-on-insulator wafer bonding—Wafer thinning technological evaluations," *Jpn. J. Appl. Phys.* 28, 1426 (1989).

- P. W. Barth, "Silicon fusion bonding for fabrication of sensors, actuators and microstructures," Sensors and Actuators A21-A23, 919 (1990).

- 15. W. P. Maszara, "Silicon-on-insulator by wafer bonding: A review," J. Electrochem. Soc., 138, 341 (1991).

- 16. C. Harendt, H. G. Graf, B. Höfflinger, and E. Penteker, "Review: Silicon fusion bonding and its characterization," J. Micromech. Microeng. 2, 113 (1992).

- 17. K. Mitani and U. Gösele, "Wafer bonding technology for silicon-on-insulator applications: A review," J. Electron. Mater. 21, 669 (1992).

- 18. S. Bengtsson, "Semiconductor wafer bonding: A review of interfacial properties and applications," J. Electron. Mater. 21, 669 (1992).

- 19. J. Haisma, B. A. C. M. Spierings, U. K. P. Biermann, and A. A. v. Gorkum, "Diversity and feasibility of direct bonding: A survey of a dedicated optical technology," *Appl. Opt.* 33, 1154 (1994).

- 20. Q.-Y. Tong and U. Gösele, "Semiconductor wafer bonding: Recent developments," *Mater. Chem. Phys.*, 37, 101 (1994).

- 21. F. S. d'Aragona and L. Ristic, Sensor Technology and Devices, L. Ristic, (Ed.), Artech House, Boston, 1994, p. 157.

- U. Gösele, H. Stenzel, M. Reiche, T. Martini, H. Steinkirchner, and Q.-Y. Tong, "History and future of semiconductor wafer bonding," Solid State Phenomena, 47/48, 33 (1996).

- 23. U. Gösele, J. Haisma, M. Schmidt, and T. Abe, (Eds.), Proceedings of the 1st International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, Vol. 92-7, The Electrochemical Society, Pennington, NJ, 1992.

- 24. H. Baumgart, C. Hunt, M. Schmidt, and T. Abe (Eds.), Proceedings of the 2nd International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, Vol, 93-29, The Electrochemical Society, Pennington, NJ, 1993.

- 25. H. Baumgart, C. Hunt, S. Iyer, U. Gösele, and T. Abe, (Eds.), Proceedings of the 3rd International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, Vol. 95-7, The Electrochemical Society, Pennington, NJ, 1995.

- U. Gösele, H. Baumgart, T. Abe, C. Hunt, and S. Iyer, (Eds.), Proceedings of the 4th International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, Vol. 97-36, The Electrochemical Society, Pennington, NJ, 1998.

- 27. Special Issue on Direct Bonding, Philips J. Res., 49, 1-182 (1995).

- 28. Z. L. Liau and D. E. Mull, "Wafer fusion: A novel technique for optoelectronic device fabrication and monolithic integration," Appl. Phys. Lett., 56, 737 (1990).

- 29. F. A. Kish, "High-brightness AlGaInP light light diodes," Proc. IEEE, 85, 1752 (1997).

- Z.H. Zhu, F. E. Ejeckam, Y. Qian, J. Zhang, Z. Zhang, G. L. Christenson, and Y. H. Lo, "Wafer bonding technology and its applications in optoelectronic devices and materials," *IEEE Sel. Top. Quantum Electron.*, 3, 927, (1997).

- 31. M. Bruel, "Silicon on insulator material technology," Electron. Lett., 31, 1201 (1995).

- 32. M. Bruel, B. Aspar, and A. J. Auberton-Herve, "Smart-cut: A new silicon on insulator material technology based on hydrogen implantation and wafer bonding," *Jpn. J. Appl. Phys.*, 36, 1636 (1997).

- E. Jalaguier, B. Aspar, S. Pocas, J. F. Michaud, M. Zussy, A. M. Papon, and M. Bruel, "Transfer of three-inch GaAs Film on silicon substrate by proton implantation process," *Electron. Lett.*, 34, 408 (1998).

- 34. Q.-Y. Tong, K. Gutjahr, S. Hopfe, U. Gösele, and T. H. Lee, "Layer splitting process in hydrogen-implanted Si, Ge, SiC, and diamond substrates," *Appl. Phys. Lett.*, **70**, 1390 (1997).

- 35. L. Di Cioccio, Y. Le Tiec, F. Letertre, C. Jaussaud, and M. Bruel, "Silicon carbide on insulator formation using the Smart Cut process," *Electron. Lett.*, 32, 1144 (1996).

- 36. J. W. Matthews and A. E. Blakeslee, "Defects in epitaxial multilayers," J. Cryst. Growth, 26, 118 (1974).

- 37. J. Woltersdorf and E. Pippel, "Substrate deformation and thin film growth," *Thin Solid Films*, **116**, 77 (1984).

- 38. L. B. Freund and W. D. Nix, "A critical thickness condition for a strained compliant substrates/epitaxial film system," Appl. Phys. Lett. 69, 173 (1996).

- 39. D. Teng and Y. H. Lo, "Dynamic model for pseudomorphic structures grown on compliant substrates: An approach to extend the critical thickness," Appl. Phys. Lett., 62, 43 (1993).

- F. E. Ejeckam, Y. H. Lo, S. Subramanian, H. Q. Hou, and B. E. Hammon, "Lattice engineered compliant substrate for defect-free heteroepitaxial growth," Appl. Phys. Lett., 70, 1685 (1997).

- 41. F. E. Ejeckam, M. Seaford, Z. H. Zhu, J. Zhang, Y. H. Lo, Q. Hou, and B. E. Hammons, "Dislocation-free InSb on GaAs compliant universal substrates," *Appl. Phys. Lett.*, 71, 776 (1997).

- 42. T. Y. Tan and U. Gösele," Twist wafer bonded 'fixed-film' versus 'compliant' substrates: Correlated misfit dislocation generation and contaminant gettering," Appl. Phys. A, 64, 631 (1997).

# 2

# **Basics of Interactions Between Flat Surfaces**

#### 2.1 INTERACTION FORCES BETWEEN SURFACES

The first step in the wafer direct bonding process is bonding (contacting) at room temperature. Since there is no adhesive or external electrical field involved in the wafer bonding process, surface forces between the wafers determine the adhesion. Therefore, a knowledge of surface forces and the resulting interaction between mating wafers is necessary to understand the direct bonding process.

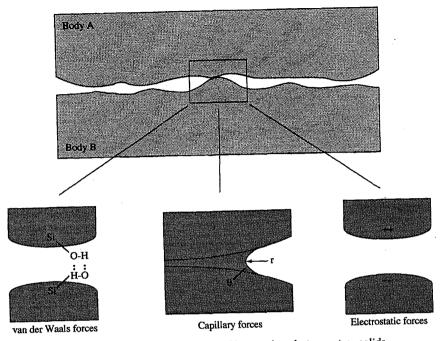

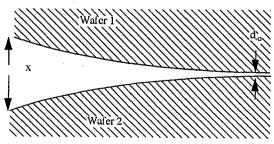

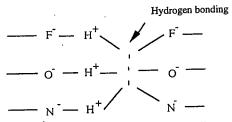

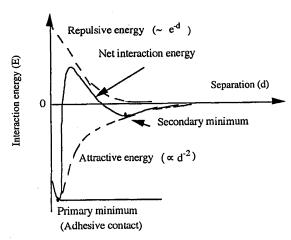

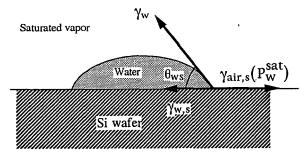

A number of interactions occur between two surfaces. Depending on the environmental conditions (e.g., vacuum, vapors, liquids), different forces may be dominating. Let us consider the interfaces of identical or dissimilar extended solids which are close together in vacuum, in the presence of water vapor, or in water. There are mainly three types of surface forces acting between two solids in sufficient proximity: (1) van der Waals attraction forces, (2) electrostatic Coulombic forces, and (3) capillary forces. Figure 2.1 shows schematically these three types of interactions.

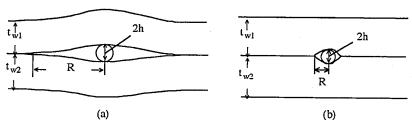

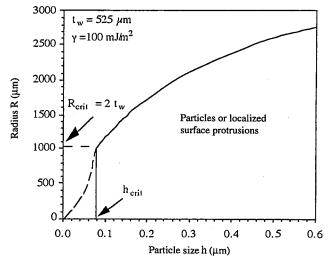

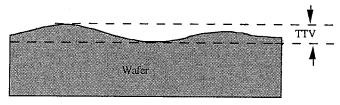

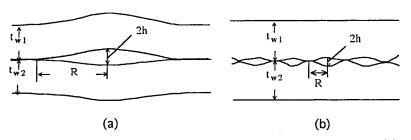

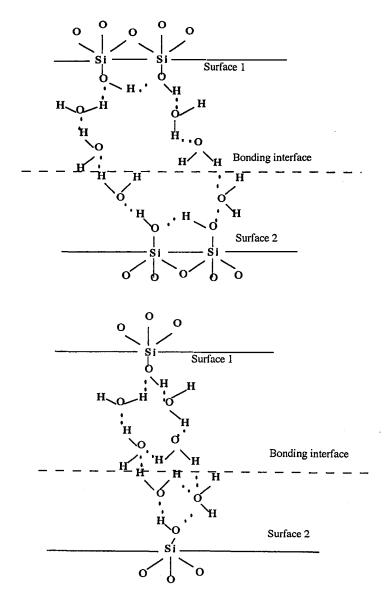

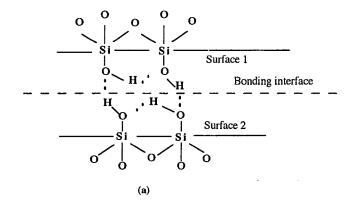

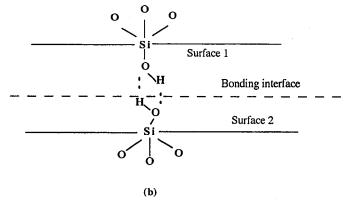

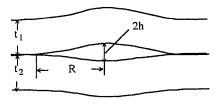

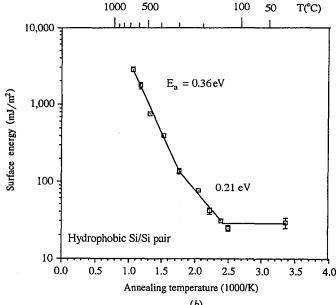

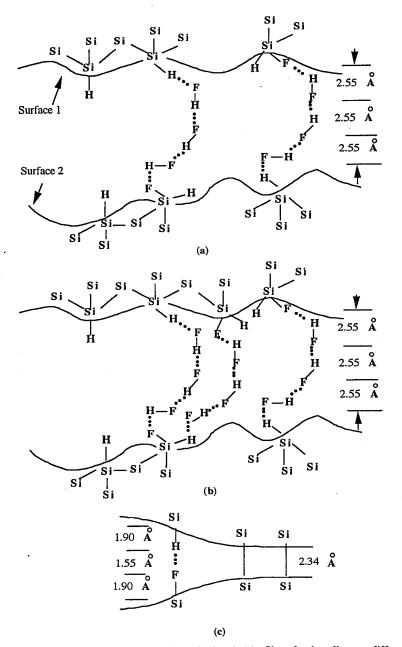

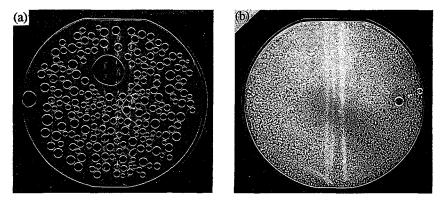

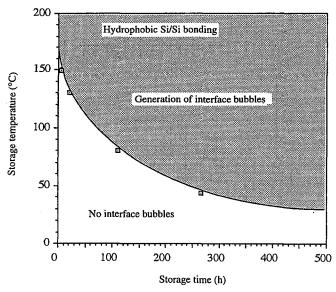

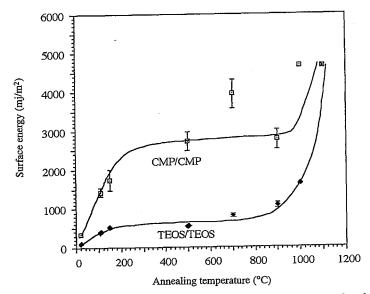

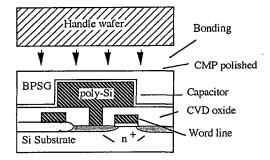

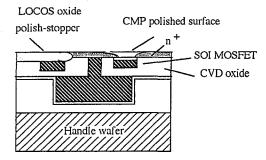

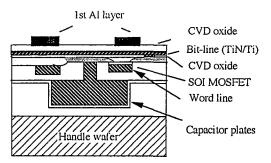

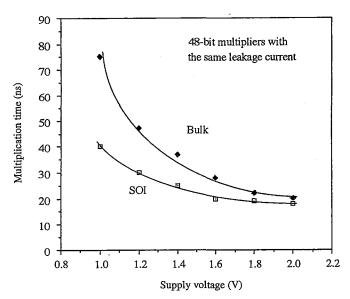

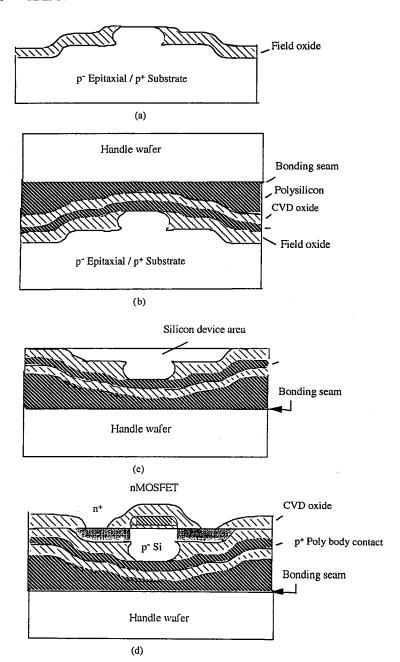

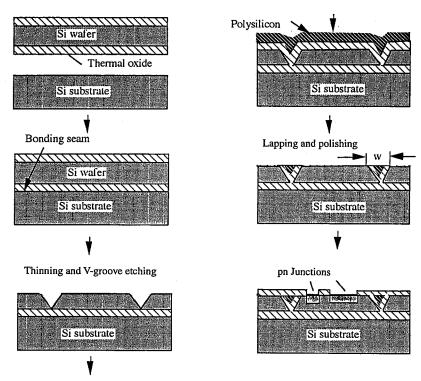

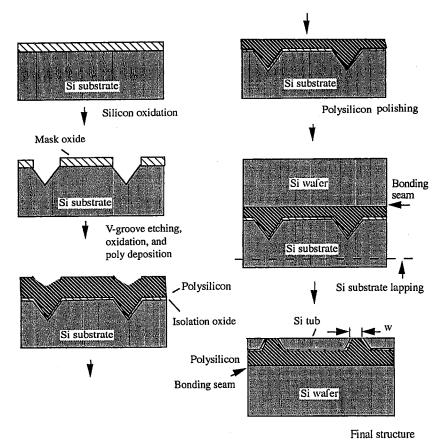

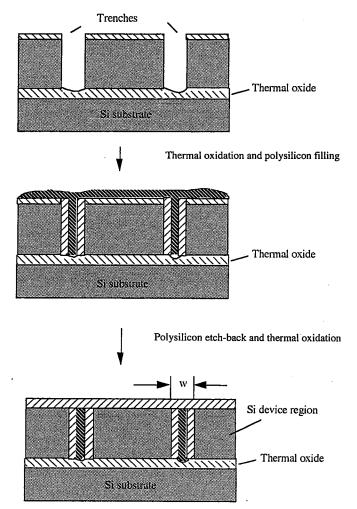

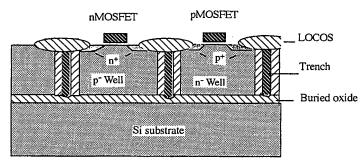

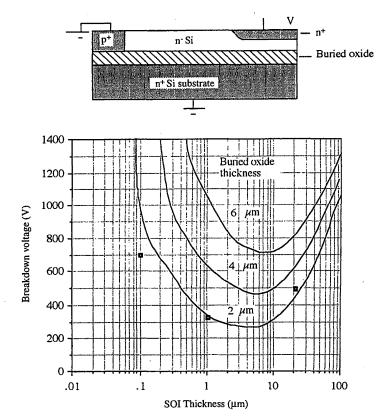

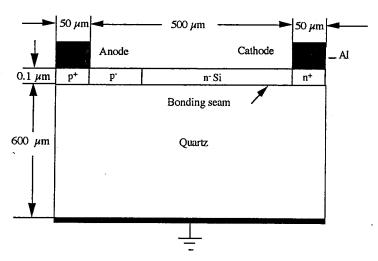

## 2.1.1 Van der Waals Interactions