INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand corner and continuing from left to

right in equal sections with small overlaps. Each original is also photographed in

one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

$\mathbf{UMI}^{^{\mathtt{n}}}$

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

800-521-0600

Page 1 of 115

# Systematic Low Temperature Bonding And Its Application To The Hydrogen Ion Cut Process And Three-Dimensional Structures

By

### YANG LI

#### **Dissertation**

Submitted in partial satisfaction of the requirements for the degree of

### **Doctor of Philosophy**

in

**Electrical Engineering**

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**Davis**

Approved:

Committee in Charge

1999

UMI Number: 9940109

UMI Microform 9940109 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

#### Abstract

A systematic low temperature process is demonstrated in this work. This process is improved from the earlier wafer bonding technology. It can be reproduced consistently therefore it can be implemented in the modern semiconductor industry to produce threedimensional structures. A brief review of the revolution of modern semiconductor device, especially metal-oxide-semiconductor (MOS) device, is given. Threedimensional electronic devices are considered the next generation in the IC industry. Low temperature bonding technology is a necessary approach to produce this multi-layer, multi-function electronic device. To stack the electronic devices, as well as vertical integration of different other microstructures, such as III-V based photo-electro devices. microwave devices and Micro-Electro-Mechanical-Structure (MEMS), into one single silicon based IC chip, to achieve so-called system-on-chip structure, is critical for the further development of the ultra-large-scale-integration (ULSI) technology. necessary approaches, such as systematic low temperature wafer bonding, reversible bonding, layer splitting and thin film transferring, copper to copper low temperature direct bonding, etc. are demonstrated, in order to make it possible for the vertical integration. Low temperature direct bonding together with reversible bonding, are the key steps to stack different pre-fabricated active device layer into one single chip. Ioncut technology, also referred as Smart-cut<sup>®</sup> technology, demonstrated a excellent way to form thin films that can be further processed in the conventional IC microfabrication laboratory. The development of this technology, especially using boron and hydrogen co-implantation instead of using hydrogen implantation only, as of the conventional Smart-cut® technology, reduced both the implantation dose and the cutting temperature to

an acceptable level for the active device layer. Copper (Cu), considered as the key candidate of the interconnection metal for the next generation of ultra-large-scale-integrated circuit (ULSI) and giga-scale-integrated circuit (GSI), is receiving more and more attention. Cu to Cu low temperature direct bonding technology may be critical in some of the ULSI applications, not only due to its mechanical properties (e.g., high thermal conductivity for heat dissipation), but also due to the possibility of vertical integration of the multi-layer microelectronics structures for the next generation of faster ULSI and GSI devices. An easy way of Cu-Cu low temperature bonding is demonstrated in this work. Following the summary, some further work also critical for the vertical integration is discussed, such as the thin film transfer, or so-called low temperature modular lift-off technology, the possibility of implementing B-H co-implantation layer splitting in partially or fully processed device layers, etc.

**Dedicated to My Parents - Qingchang and Weihe**

### **Acknowledgment**

I wish to express my deepest gratitude to my research advisor, Professor Robert W. Bower. I greatly appreciate his guidance, instruction, encouragement, patience, support, understanding and friendship, it has always been, and will, a great pleasure to work with him. I surely do not remember how many times Professor Bower and I were working late till midnight running some experiment in the cleanroom, only two of us left in the whole building. However, I can never forget the experiment we did on December 24, 1997, the one we did not stop until 8:30 in the evening, when everything worked out so nicely we could not believe with our own eyes. I guess it was the holly God watching over us and grant us such excellent results.

I want to express my special thanks to Dr. Michael Nastasi, my supervisor at Los Alamos National Laboratory, who, together with Professor Bower, supported my research work in the last eight months of my graduate studies. I want to thank for his patience, understanding, guidance and friendship. Working with Dr. Nastasi, as well as Kevin Walter, Tobias Hoechbauer, Kent Scarborough, Joe Tesmer, Calib Evans, Mark Hollander, Carl Magriore, Xiao-Ming He, Doek-Hyung Lee, Serge Fayeulle, Zoran Falkenstein, Neil Baker and many others at Los Alamos National Laboratory, is forever a valuable experience.

I also extend great appreciation to Professor Olav Solgaard in the Department of Electrical and Computer Engineering, who served as the chairman on my committee in the qualifying examination. Professor Subuuh Risbud in the Department of Chemical Engineering and Material Science and Professor Vojin Oklobdzija in the Department of

-V-

Electrical and Computer Engineering are also acknowledged, for their help and kindness in serving on my qualifying exam as well as their valuable suggestions, comments, discussions and advice.

I am especially indebted to Mr. Angus McFadden, first with the Implant Center and then switched to nTEK Inc., for his tireless help on providing the implant wafers.

I would like to express thanks to all the students in Professor Bower's research group at different times while I am staying at UC Davis - Victor Watt, Winnie Chan, Linh Hong, Frank Y.-J. Chin, Jennifer Lee, Louis LeBoeuf, Wade Xiong, Jason Wu, Jimmy Kuei, Bryan Frane and Ray Verda, their presence, friendship and assistance have created the working environment exciting and rewarding.

I want to thank many other fellow graduate students at UC Davis, Tao Pi, Xiaodong Wang, Kris Vossough, Bonnie Gray, Carlos Gonzales, Dave Pedersen, Paul Hagelin and others, for their friendship, company and valuable discussions.

Finally, I want to acknowledge University of California MICRO program,

Material Science and Technology Division-8 at Los Alamos National Laboratory,

Hughes Aircraft Inc., Santa Barbara Research Center, Fairchiled Semiconductor

Corporation, for their cooperation, equipment, facilities and financial support.

# **CONTENTS**

# CHARTER 1

| Introduction                                                    | 1 |

|-----------------------------------------------------------------|---|

| 1.1 VLSI Technology in the Past 25 Years                        |   |

| 1.2 Three-dimensional Microelectronics                          |   |

| 1.3 Vertical Integration Multi-layer Microstructure             |   |

| References                                                      |   |

|                                                                 |   |

| CHARTER 2                                                       |   |

| Low Temperature Direct Bonding                                  | 8 |

| 2.1 Brief History of Wafer Bonding                              |   |

| 2.2 Aligned Wafer Bonding                                       |   |

| 2.3 Mechanical Considerations of Wafer Bonding                  |   |

| 2.4 RCA Clean                                                   |   |

| 2.5 Optimization of Plasma Activation Process                   |   |

| 2.6 Plasma Treatment and Surface Activation Energy              |   |

| 2.7 Three-step Systematic Low Temperature Wafer Bonding Process |   |

|                                                                 |   |

#### References

References

# CHARTER 3

| Reversible Bonding                                                   | 39 |

|----------------------------------------------------------------------|----|

| 3.1 Importance of the Reworkability in Three-dimensional Integration |    |

| 3.2 Possible Ways to Reverse the Bond                                |    |

| 3.3 Analysis of the Reversible Bonding for Two Typical Cases         |    |

| References                                                           |    |

|                                                                      |    |

|                                                                      |    |

| CHARTER 4                                                            |    |

|                                                                      |    |

| Layer Splitting and Thin Film Transfer                               | 51 |

| 4.1 A Brief Review of Smart-cut® Technology                          |    |

| 4.2 Hydrogen-Silicon System and Basic Mechanism of Smart-cut®        |    |

| 4.3 Low Temperature and Smoother Thin Film Transference              |    |

| 4.4 Lower Hydrogen Dose and Lower Temperature Layer Splitting        |    |

# CHARTER 5

| Low Temperature Copper Direct Bonding 82                                      |    |

|-------------------------------------------------------------------------------|----|

| 5.1 Comparison of Possible Interconnect Metal                                 |    |

| 5.2 Low Temperature Copper to Copper Low Temperature Direct Bonding           |    |

| 5.3 Bond Strength Test                                                        |    |

| 5.4 Specific Contact Resistance Measurement                                   |    |

| References                                                                    |    |

| CHARTER 6                                                                     |    |

| Summary and Future Work                                                       | 92 |

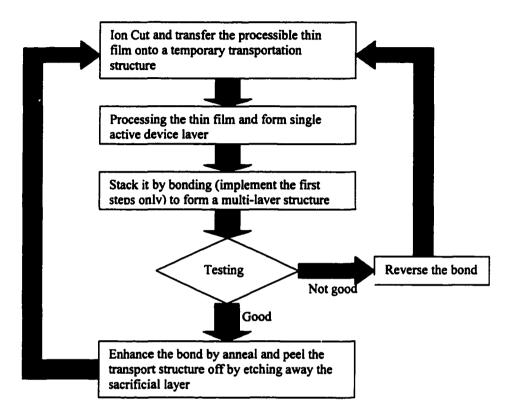

| 6.1.Overall Scheme for the Vertical Integration of Multi-layer Microstructure |    |

| 6.2.Future Work                                                               |    |

| References                                                                    |    |

|                                                                               |    |

| Appendix                                                                      |    |

| Bonding Classification 97                                                     |    |

### **List of Tables**

| Table 1.1 | A few major changes for MOSFET in the past 25 years                     | 7      |             |

|-----------|-------------------------------------------------------------------------|--------|-------------|

| Table 2.1 | Optimized recipes for different plasma activation process in            | the    | low         |

|           | temperature direct bonding                                              | 27     |             |

| Table 2.2 | Experimental evidence of the effects for different plasma activation p  | roces  | s in        |

|           | low temperature direct bonding                                          | 27     |             |

| Table 2.3 | Initial bonding results with pressure only                              | 27     |             |

| Table 2.4 | Bonding samples after pressure and temperature                          | 28     |             |

| Table 2.5 | Bond types before and after the third (200 °C anneal) step with or with | thout  | the         |

|           | intermediate step (second step with both temperature and pressure)      | 28     |             |

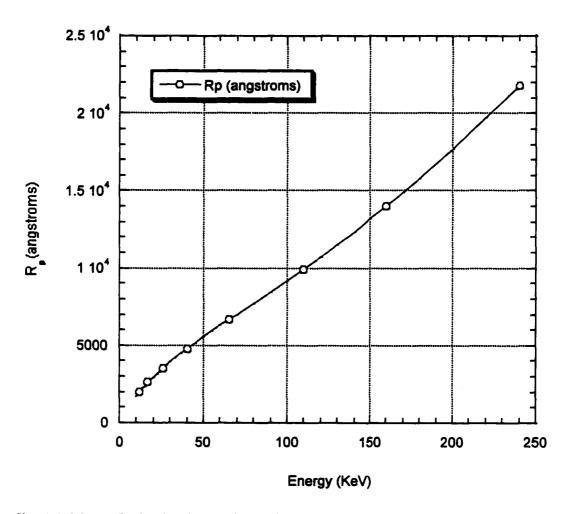

| Table 4.1 | Monte Carlo simulation results for hydrogen implants into silicon by S  | SRIM   | <b>1 68</b> |

| Table 4.2 | Implant boron as the catalyst material may greatly reduce both the h    | ıydro  | gen         |

|           | implantation dose and the splitting temperature.                        | 69     |             |

| Table 5.1 | Comparison of properties of possible interlayer metals (ref. 3 and 4)   | 88     |             |

| Table 5.2 | Contact resistance measurement for Cu-Cu direct bonding, the contact    | et are | a is        |

|           | 18 mm <sup>2</sup> for this sample                                      | 88     |             |

| Table A.1 | Bond classification, only type 4 or 5 bonds shown in IR can produc      | e str  | ong         |

|           | bonding where the bond strength is measured >1,000 ergs/cm <sup>2</sup> | 99     |             |

# **List of Figures**

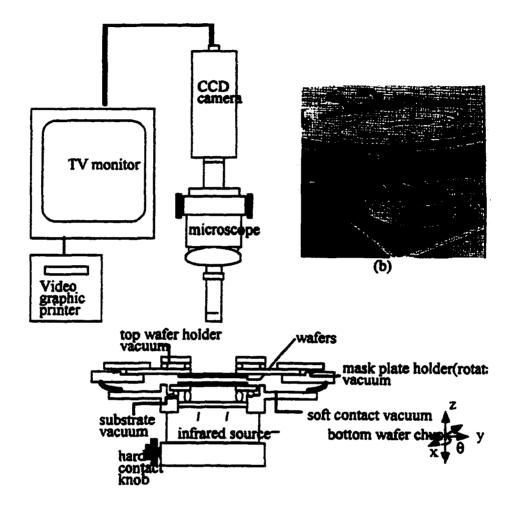

| Figure 2.1  | The experimental setup for aligned wafer bonding (after Bower et al., 1   | 1991  | )29   |

|-------------|---------------------------------------------------------------------------|-------|-------|

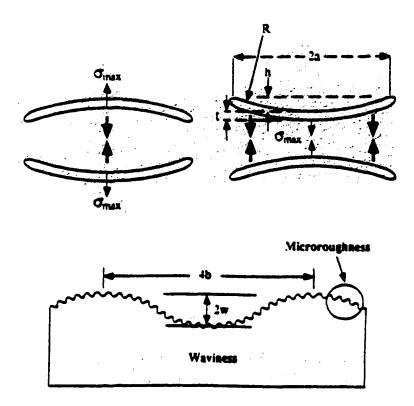

| Figure 2.2  | Some mechanical considerations for the wafer bonding - radius of cu       | rvat  | ure,  |

|             | waviness and microroughness (after Bower et al., 1995)                    | 30    |       |

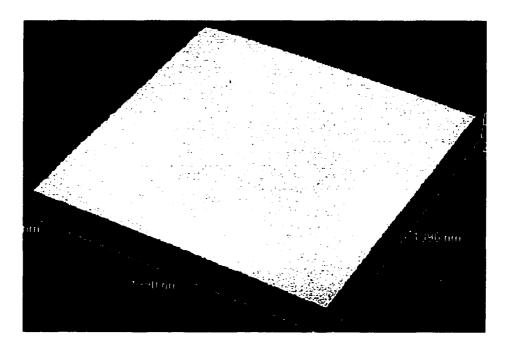

| Figure 2.3  | AFM surface measurement shows, for commercial (100) silicon wa            | ıfer, | the   |

|             | microroughness is much below the mechanical criteria for achie            | eving | g a   |

|             | successful wafer bonding                                                  | 31    |       |

| Figure 2.4  | Cross sectional SEM image of aligned bonded commercial SRAM               | ls (a | ıfter |

|             | Bower et at., 1993)                                                       | 32    |       |

| Figure 2.5  | Reduction of the surface activation energy $(E_a)$ by applying the        | plas  | sma   |

|             | treatment to the attempted bonded samples                                 | 33    |       |

| Figure 2.6  | Pressure fixture built for applying the pressure in three-step low temp   | рега  | ture  |

|             | direct bonding process                                                    | 34    |       |

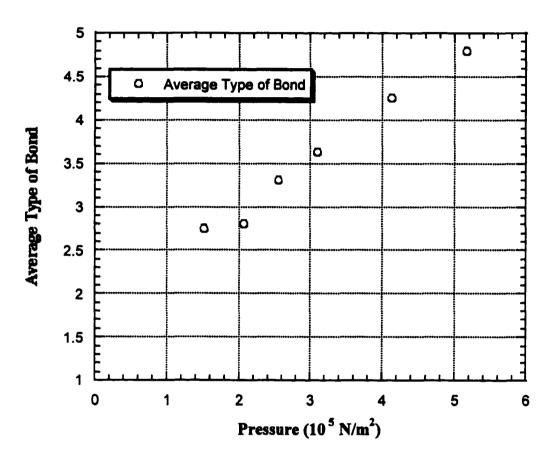

| Figure 2.7  | Average initial type of bond with pressure only                           | 35    |       |

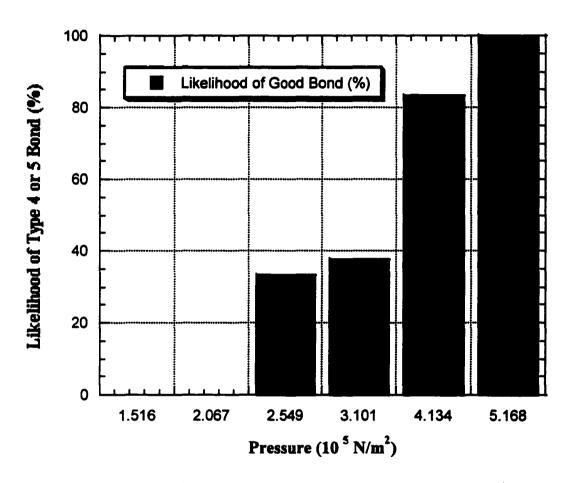

| Figure 2.8  | Likelihood of Good Bond with Pressure only                                | 36    |       |

| Figure 2.9  | Average type of bond after pressure and temperature treatment             | 37    |       |

| Figure 2.10 | Likelihood of Good Bond after Pressure and Temperature Treatment          | nt    | 38    |

| Figure 3.1  | Cross section of wafers or chips stacked in a three-dimension array       | with  | an    |

|             | offset when aligned bonded, so that a force can be applied along the ed   | ge    | 49    |

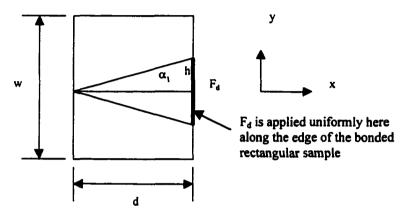

| Figure 3.2  | Rectangular chip of dimensions $d$ by $w$ , with line force $F_d$ applied | 49    |       |

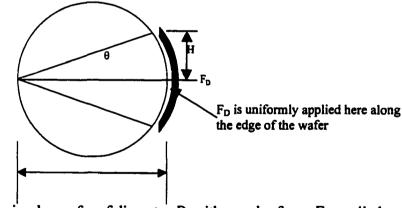

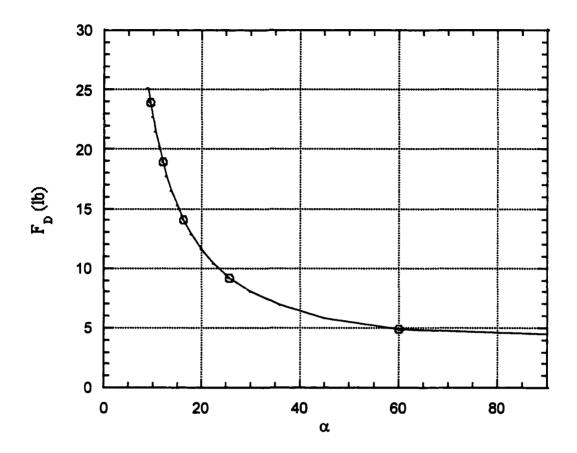

| Figure 3.3  | Circular wafer of diameter $D$ , with angular force $F_D$ applied         | 49    |       |

| Figure 3.4 | Force needed to debond a 100mm circuit bonded sample, from the                             | calibration                         |

|------------|--------------------------------------------------------------------------------------------|-------------------------------------|

|            | measurement of a 2cm × 2cm square bonded sample, where 0.5                                 | lb force is                         |

|            | applied on the side (Note $\alpha = 2\theta$ , can change from 0 to 90°, they re-          | epresent the                        |

|            | total length of the arc at the edge that a force is applied).                              | 50                                  |

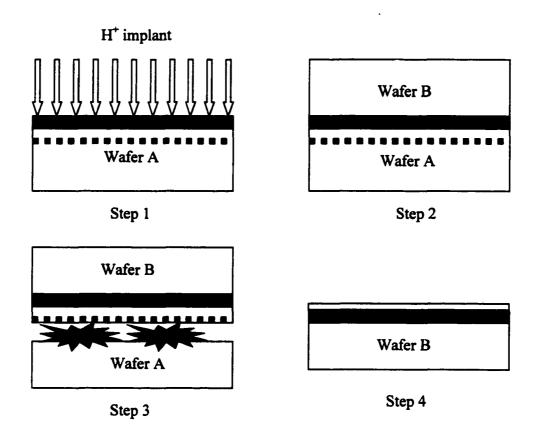

| Figure 4.1 | Smart-cut® technology to produce silicon-on-insulator material                             | 70                                  |

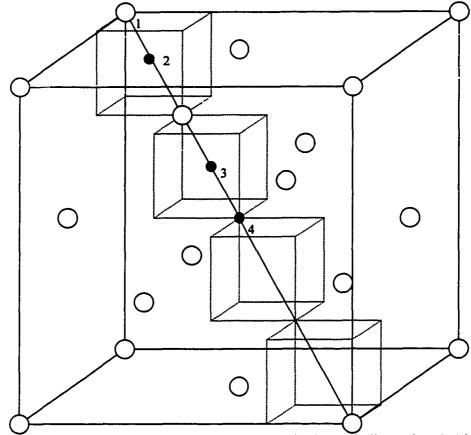

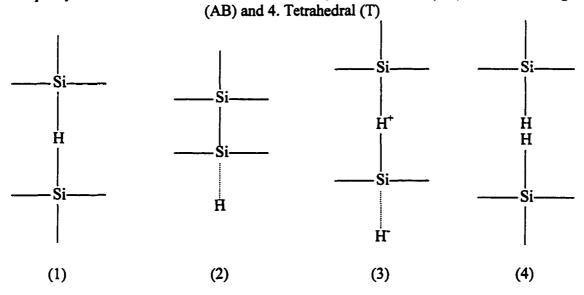

| Figure 4.2 | Four possible hydrogen configurations in silicon (1) bond - centered                       | ed (BC); (2)                        |

|            | antibonding (AB); (3) H <sub>2</sub> *; (4) silanic                                        | 71                                  |

| Figure 4.3 | Blisters at the silicon surfaces after hydrogen ion implantation.(a)                       | 4.5×10 <sup>16</sup> H <sup>+</sup> |

|            | into (100) Si, 40 KeV, 425 °C, 6 hours; (b) 4.9×10 <sup>16</sup> H <sup>+</sup> into (100) | Si, 40 KeV,                         |

|            | 425 °C, 2 hours; (c) 5.3×10 <sup>16</sup> H <sup>+</sup> into (100) Si, 40 KeV, 425 °C,    | 25 minutes;                         |

|            | (d) 5.7×10 <sup>16</sup> H <sup>+</sup> into (100) Si, 40 KeV, 425 °C, 20 minutes          | 72-75                               |

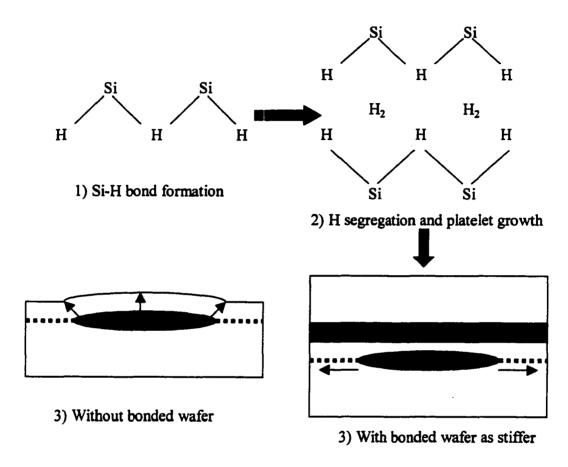

| Figure 4.4 | Proposed basic mechanism of Smart Cut® process                                             | 76                                  |

| Figure 4.5 | Monte Carlo TRIM-95 simulation for H <sup>+</sup> implantation into silicon                | 77                                  |

| Figure 4.6 | A 10cm diameter SOI wafer produced with a hydrogen ion cut at 4                            | 20 °C after                         |

|            | low temperature wet SRD direct bonding                                                     | 78                                  |

| Figure 4.7 | The surface roughness of smart-cut <sup>®</sup> layers created with a normal               | direct bond                         |

|            | after an Atomic Force Microscopic (AFM) picture published in a re                          | cent article                        |

|            | (after M. Bruel et al)                                                                     | 79                                  |

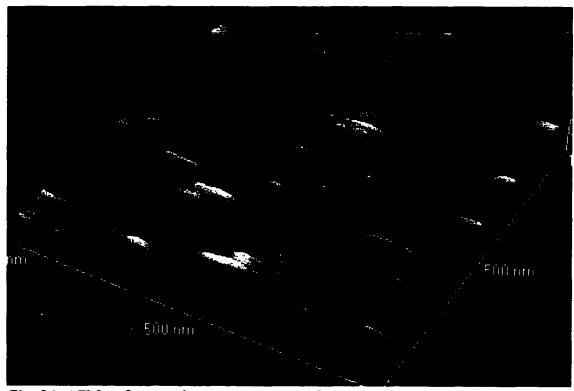

| Figure 4.8 | AFM of the surface roughness low temperature bonded hydrogen                               | n cut wafer                         |

|            | (vertical scale is 0 - 12.49 nm)                                                           | 80                                  |

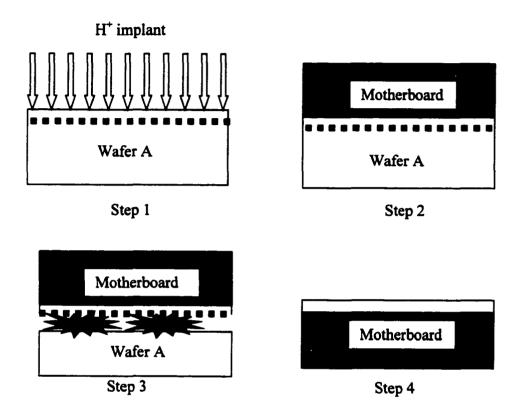

| Figure 4.9 | Process of layer splitting and thin film transfer 81                                       |                                     |

| Figure 5.1 | AFM surface roughness measurement. Scan range is 1 $\mu m$ $\times$                        | 1 μm; the                           |

|            | vertical scale is 0 to 11 nm                                                               | 89                                  |

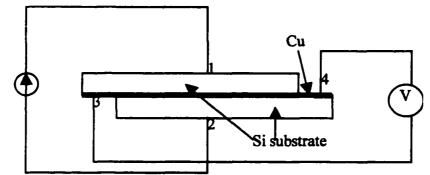

| Figure 5.2 | Specific contact resistance measurement experimental setup       |          | 90      |

|------------|------------------------------------------------------------------|----------|---------|

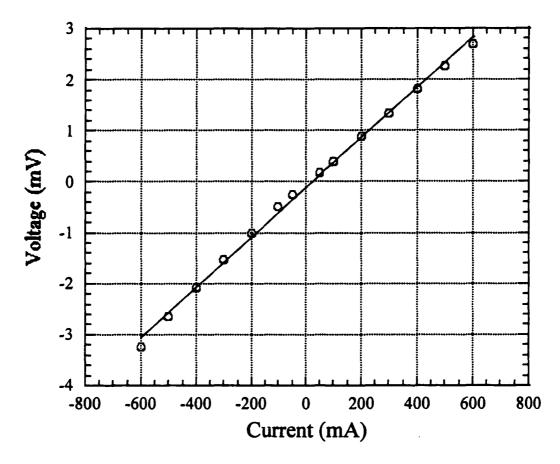

| Figure 5.3 | I-V measurement shows very good linear relation indicates n      | o extra  | contact |

|            | barrier exists for this Cu-Cu direct bond                        | 91       |         |

| Figure 6.1 | Overall process flow for the vertical integration of multi-layer | nicrostr | ucture  |

|            |                                                                  | 96       |         |

| Figure A.1 | Type1 bond                                                       | 97       |         |

| Figure A.2 | Type2 bond                                                       | 97       |         |

| Figure A.3 | Type3 bond                                                       | 98       |         |

| Figure A.4 | Type4 bond                                                       | 98       |         |

| Figure A.5 | Type5 bond                                                       | 99       |         |

#### i

### CHAPTER 1

### Introduction

#### 1.1.VLSI Technology in the Past 25 Years

The electronics industry has being experienced phenomenal growth in the past few decades. It is now become the largest industry in the world with global sales over one trillion (10<sup>12</sup>) dollars! It never has such an impact to the people in their day-to-day life. Low power, fast speed, high packaging density, high yield and low cost are always the key driven forces in the evolution of this industry. The most important device for ultra-large-scale-integration (ULSI) may be the enhancement mode metal-oxide-semiconductor field-effect transistor (MOSFET). Although reported as early as in the early 1960's (by Kahng and Atalla [1], Bower and Dill [2], etc.), it could not be fabricated properly and reliably until the early 1970's. However, since then, lots of changes happened to this simple device, Table 1.1 just listed a few major ones.

R. W. Bower summarizes one simple relation between the manufacturing fabrication cost and the device feature size in the early 1990's as following:

# Fabrication Cost $\propto 1/(Feature \ size)^2$

It is not surprising that the manufacturing fabrication cost is in the range of two billions nowadays when the device feature size reaches one-quarter micron. One can further easily predict that the fabrication cost will be in the range of 10-13 billion dollars when the feature size decreases to 0.1 micron in the very near future.

However, the feature size is no longer the pre-dominant parameter for the speed, performance and packaging density in the ULSI and giga-scale-integration (GSI) technology. As S. J. Hilenius stated in *Modern Semiconductor Device Physics* (Wiley-Interscience, 1998), "... we have seen various technologies become more integrated into a single chip and more and more functionality incorporated into these 'system on a chip' architectures. The future of these systems will be in the increased integration of these different structures with an ever-increasing dependence on the **three-dimensional** nature of these devices..." [3].

Should we keep on squeezing the near-saturated devices in two-dimensional as we did in the past 25 years, or should we move to the three-dimensional scheme for the next generation of ULSI and GSI? What are the advantages for the three-dimensional integration? What are the necessary approaches to achieve the vertical integration? These are the questions to be answered in this work.

#### 1.2. Three-dimensional Microelectronics

The aluminum based two-dimensional networks has been found inadequate in ULSI and GSI technology, because of the unacceptable high values of the interconnection delay (or so-called RC delay) [4, 5]. One can reduce the RC delay either by reducing C associated with the dielectric or by reducing R, while only the latter will be considered in this work. According to the simple relationship of  $R = \rho L/A$ , R can be reduced by reducing the resistivity  $\rho$  and the length L of the interconnection metal or by increasing the cross-sectional area of the interconnections, with geometry factors also affecting C. Increasing the interconnection area has little appeal, since (a) the area occupied by interconnection lines is already an extremely large fraction of the chip area

and (b) the fabrication requirements limit the thickness of the metal (in the matter of fact, however, using other interconnect metal with higher electromigration resistance, such as copper, to replace aluminum, may be also possible to reduce the cross sectional area A, this issue will be addressed briefly in Chapter 5 of this work). Therefore, a vertical structure integrating the multi-layer is proposed in this work, the lowering of L in such schemes is achieved by using vertical interconnections that span shorter horizontal distances on selected planar levels.

The industrial standard integrated circuits (ICs) are usually two-dimensional. However, huge gain can be achieved when expand the device into three-dimensional. Take static random-access-memory (SRAM) as a simple example. Although the device dimension is kept on shrinking in the last few years, the most significant structural change is the accomplishment of extensive usage of the thin-film transistors (TFT) to allow the *p*-channel load transistor to be put on top of the *n*-channel transistor to produce a cell stacked in the third dimension. Dynamic random-access-memory (DRAM), as another example, the incredible volume increase comes from the expanding the device properly in the third dimension also, either using a deep-trench capacitor deep under the MOS transistor or using a crown type of capacitor structure above the MOS transistor.

Besides modifying the processing technology and producing the single device in three-dimensional directly, the post-single-device-fabrication three-dimensional packaging is also proposed. Packaging the conventional two-dimensional IC into three-dimensional microelectronics is always a challenging issue in the semiconductor field. The gain is huge, e.g., a two-dimensional conventional IC is about 500 µm thick (for 10cm wafer), the active layer of this IC is only about 1 to 2 µm thick. Thus, three-

dimensional stacked aligned bonded chips would have a density of 250 to 500 times denser than conventional chips. Moreover, the conventional IC is also mounted in a package that increases its thickness to the order of  $\geq 2$  mm. Thus, ideally speaking, the density ratio of three-dimensional to two-dimensional chips is as great as 1000 to 1!

Overall, three-dimensional microelectronics devices, comparing to their two-dimensional counterparts, have faster speed at a given feature size, much higher packaging density at a given feature size. Therefore, the cost per function is reduced and the performance is increased. Smaller manufacturing capital cost can then eventually be accomplished.

#### 1.3. Vertical Integration Multi-layer Microstructures

Silicon based integrated circuit technology has been a major factor for the semiconductor industry evolution in the past few decades. Some other important developments are those of micro-electro-mechanical structure (MEMS), III-V based photonic devices and microwave devices, etc. The integration of these technologies is a goal whose impact will be far reaching. Unfortunately, different processing lines are required for fabricating different type of devices. Thus, packaging the processed devices into one chip turns out to be the main approach for this issue.

Wafer bonding is considered the major approach for stacking different active device layer into one single chip. A systematic low temperature silicon/SiO<sub>2</sub> wafer bonding technology is developed in this work [6, 7]. The re-workability of this wafer bonding technology is also discussed and a reasonable re-work method is proposed and analyzed [8, 9]. Ion-cut technology for layer splitting and thin film transferring is developed [10], the basic mechanism of Smart-cut<sup>®</sup> is discussed [11]. A brand new

boron/hydrogen co-implantation compared with low temperature direct wafer bonding ion-cut technology, allowing a lower implantation dose and more importantly, at much lower cutting temperature, is developed [12]. Finally, copper metallization is discussed and a copper to copper low temperature direct bonding process is demonstrated [13].

#### References

- 1. D. Kahng and M.M. Atalla, "Silicon-silicon dioxide surface device", in IRE Device Research Conference, Pittsburgh, 1960.

- R. W. Bower and H. G. Dill "INSULATED GATE FIELD EFFECT TRANSISTORS

FABRICATED USING THE GATE AS SOURCE-DRAIN MASK", Paper 16.6

International Electron Device Meeting, Washington, D.C., 1966.

- 3. "Modern Semiconductor Device Physics", Edited by S. M. Sze, published by Wiley-Interscience, 1998.

- 4. S. P. Murarka, R. J. Gutmann, A. E. Kaloyeros and W. A. Lanford, "Advanced multilayer metallization schemes with copper as interconnection metal", Thin Solid Films, 236 (1993) 257-266.

- Ronald J. Gutmann, T. Paul Chow, William N. Gill, Alain E. Kaloyeros, William A. Lanford and Shyam P. Murarka, "COPPER METALLIZATION MANUFACTURING ISSUES FOR FUTURE ICs", Mat. Res. Sco. Symp. Proc. Vol. 337, 1994.

- 6. Y. Albert Li and Robert W. Bower, "Low temperature direct bonding using pressure and temperature", Proceedings of SPIE, Vol. 3184, June 1997, 124-128.

- Y. Albert Li and Robert W. Bower, "Systematic Low Temperature Silicon Bonding using Pressure and Temperature", Japanese Journal of Applied Physics, Vol. 37, No. 3, 737-741 (March), 1998.

- Robert, W. Bower and Y. Albert Li, "Reversible low temperature direct bonds for fabrication of three-dimensional microelectronic structures", Proceedings of SPIE, Vol. 3184, June 1997, 120-123.

- Robert W. Bower and Y. Albert Li, "Analysis of Rectangular Chip and Circular Wafer Debonding Applied to Reversible Low Temperature Bonding", to be published, 1998.

- 10. Robert W. Bower, Y. Albert Li and Frank Y-J Chin, "The hydrogen ion cut technology combined with low temperature direct bonding", Proceedings of SPIE, Vol. 3184, June 1997, 2-4.

- 11. Y. Albert Li and Robert W. Bower, "Surface Conditions and Morphology of Hydrogen Ion Cut Low Temperature Bonded Thin Film Layers", submitted to Journal of Applied Physics, August 1998.

- 12. Robert W. Bower, Louis LeBoeuf, and Y. Albert Li, "Transposed Splitting of Silicon Implanted With Spatially Offset Distributions of Hydrogen and Boron", IL NUOVO CIMENTO, Vol. 19, D, N. 12, 1871-1879, December 1997.

- 13. Y. Albert Li Robert W. Bower and Izak Bencuya, "Low Temperature Copper to copper Direct Bonding", Jpn. J. Appl. Phys. Vol.37(1998) pp.L1068-L1069, Part 2, No. 9A/B, 15 September 1998.

| Issue                  | From  | То                  | By        | Why                         |

|------------------------|-------|---------------------|-----------|-----------------------------|

| Feature Size           | 10 μm | < 0.25 μm           | Hard Work | Speed and Packaging Density |

| Wafer Size             | 10 mm | > 200 mm            | Growing   | Yield                       |

| Devices per<br>Chip    | 25    | > 2×10 <sup>7</sup> | Scaling   | Speed and Packaging Density |

| Fab Cost<br>(in US \$) | 10°   | 2×10 <sup>9</sup>   | Money     | Money                       |

Table 1.1. A few major changes for MOSFET in the past 25 years.

## CHAPTER 2

# **Low Temperature Direct Bonding**

#### 2.1 Brief History of Wafer Bonding

Wafer bonding, in order to create novel structures, is not a new technology. As early as in 1969, Wallis and Pomerantz first introduced their work on anodic bonding of glass to metal or silicon to quartz, which is also known as field-assisted bonding [1]. This process is based on electrostatic forces pulling materials together and is applicable only when at least one of the materials is insulating or covered with an insulator. The materials brought into mechanical contact are heated to an elevated temperature and an electric field is applied across the boundary. This method is used extensively in fabricating sensors and actuators especially for creating a hermetic sealed cavity. However, this method is limited to the materials, at least one of the wafers must be insulator as mentioned above. In addition to the material limitations, anodic bonding requires high voltage (200 - 2000 Volts) which is generally detrimental for use with prefabricated electronics devices.

Gluing is another natural, simple bonding method. Two attempted pairs are joined together with a thin adhesive "glue" layer, which usually is low temperature melting glass such as boron glass, BPSG glass, or spin-on-glass, polymer (PMMA, e.g.) glue, sometimes even low melting point metal for conductive bonding [2-7]. The intermediate layer gives good adherence between two wafers after an annealing step. Applications of gluing include an epitaxial film transfer technique for producing single

crystal silicon film on an insulating substrate [8]. The drawbacks are that the adhesive may produce a layer of unnecessary material with temperature restrictions that may impose unnecessary limitations on the composite structures.

Direct bonding, which does not require any adhesive or electrostatic field, was first performed by two independent groups in the mid 1980's. Lasky et al. reported the bonding of silicon dioxide and silicon dioxide to silicon dioxide, and Shimbo et al. reported the silicon to silicon direct bonding in 1985 and 1986 respectively [9, 10]. Direct bonding usually consists of room temperature bonding of clean and particle free, mirror-polished, flat wafer surface (either hydrophilic or hydrophobic). The initial weak room temperature bond is followed by an anneal cycle to create a permanent strong bond. The temperature of the thermal anneal cycle dictates the type of direct bonding. An anneal cycle above 700°C is usually required for this category of direct bonding, which is also called fusion bonding, thermal bonding or high temperature direct bonding [11-13].

Plasma activated low temperature direct bonding was first introduced by Bower et al in the early 1990's [14-17]. Where the attempted samples were first received a plasma treatment prelude the room temperature initial contact, following a thermal anneal at a temperature of only 90-300°C. As a well known fact, that silicon has a 0.5-1 percent solid solubility in aluminum at a temperature of 450-500°C, therefore, during heat treatment, Si will diffuse into Al, forming Al spikes in the Si. These spikes may destroy the operation of the transistor. This phenomenon is particularly severe in the LSI scheme and beyond since the junction is designed shallower and shallower. To bond preprocessed electronics device with metal line already in place, a low temperature process is required. Since the year of 1993, independent research groups developed different

methods of low temperature wafer bonding, either by sufficiently long time subsequent low temperature anneal (~ 200 hours is required at anneal temperature of 150 °C), or by ultrahigh vacuum (~ 3×10<sup>-9</sup> Torr) room temperature bonding, or by all means of plasma treatment for low temperature direct bonding [18-32]. In our research group at UC Davis, ammonia, oxygen and argon plasmas were used for the surface activation, different materials such as bare silicon, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, TiN, etc. were successfully bonded [15-17, 33-36]. Our recent experimental data (1996-97) shows that oxygen plasma activated Si/SiO<sub>2</sub> wafers have the best bonding results (uniformity and strength), the bond strength of a uniform bonded sample usually in the range of greater than 1,000 ergs/cm<sup>2</sup>, which is as strong as that of high temperature direct bonding.

#### 2.2 Aligned Wafer Bonding

It is critical to have an aligned wafer bonding process in making the three-dimensional microstructures. Bower et al. described a mechanical fixture to implement the aligned wafer bonding process (Fig. 2.1) in 1991, where the wafer alignment of an accuracy of 5 µm was obtained [14]. This fixture consisted basically of an infrared (IR) wafer-mask aligner system, where the two vacuum chucks hold the two attempted wafers in place, face-to-face and parallel respect of each. An infrared source generated the infrared beam shinning on the etched grooves, which were used to obtain the contrast for the alignment. The monitoring system consisted of a microscope, a CCD camera and TV monitor. By monitoring the transmitted IR image, one could adjust the positions of the two wafer holders and achieve a good alignment.

#### 2.3 Mechanical Considerations of Wafer Bonding

To achieve a successful wafer bonding, the wafers have to be 1) clean and free of particles, 2) flat, where the radius of curvature should be at least 60 meters, 3) smooth, where the waviness should be less than  $10^{-6}$  and the microroughness should be less than 1nm. Several articles presented the investigations of the surface variations, and the above criteria are concluded by Bower et al. in 1995 [37]. The definitions of the radius of curvature, waviness and microroughness are shown in Fig. 2.2.

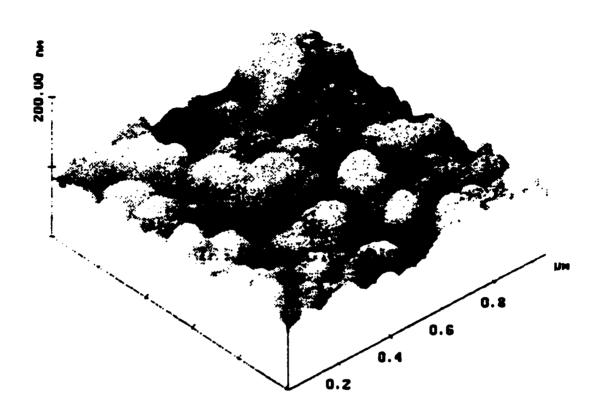

For a commercial (100) silicon wafer, an atomic force microscopy (AFM) was used to measure the surface variations [38]. The results indicate that the surface roughness  $R_a = 0.2383$  nm and the root-mean-square (RMS) = 0.3035 nm, both of them are much below the mechanical criteria for a successful wafer bonding (Fig. 2.3). The flatness and the waviness can be measured by a DekTak 3030 Profilometer, usually the radius of curvature is > 100 m, and the waviness is <  $10^{-6}$ . Both of them are within the range for a good bonding.

A question will be immediately raised, which is "Is the fully processed IC chip with circuits good enough to do a wafer bonding?" Fortunately, the multi-layer interconnection metallization scheme in the modern IC industry (5 layers for 0.25-µm feature size device, e.g.) requires smoother and smoother surfaces of the device after each layer in order to add the next layer and complete the whole structure. Fig. 2.4 shows a cross sectional scanning electron microscopy (SEM) image for aligned bonded two commercial SRAMs (donated by Advanced Micro Device Inc.). This picture indicates clearly that 1) the industry standard devices are flat and smooth enough for direct wafer bonding, without any extra post-planarization, and 2) only the low temperature direct

bonding process can in used in bonding the pre-fabricated devices with the metal line already in place.

#### 2.4 RCA Clean

Considering the strict mechanical criteria for the direct wafer bonding, all of experiment in this work was completed in the cleanroom environment (Class-100) at UC Davis. RCA clean is required before any plasma activation in the low temperature direct bonding process (to all the semiconductor surfaces). The standard RCA process consists of:

- 1. Base bath  $(NH_4OH:H_2O_2:H_2O = 1:1:6)$  at 75°C for 10 minutes

- 2. De-ionized (DI) water rinse

- 3. Acid bath (HCl: $H_2O_2$ : $H_2O = 1:1:7$ ) at 75°C for 10 minutes

- 4. DI water rinse

- 5. Buffered-oxide-etcher (BOE) dip for 1 minute

- 6. DI water rinse

- 7. Spin dry

The organic contaminants can be removed in the base bath, where the acid bath can get rid of the metallic contaminants on the surface of the wafer. DI water rinse not only can rinse off the activation residues but may also be useful in getting rid of the loose particles. BOE dip is usually used for stripping off the native oxide layer. This may convert the wafer surface from hydrophilic into hydrophobic. However it was found that the native oxide layer did not necessarily affect the bonding results in this work, our plasma activated low temperature process can be applied to both hydrophilic and hydrophobic surfaces. This is because after the plasma activation process, the wafers are

always converted to hydrophilic in spite of its original state. Therefore, BOE dip may be skipped in this work. The fact of the equivalent effect of this low temperature bonding process to both hydrophilic and hydrophobic materials plays very important role in the ion-cut technology, the detailed results will be given in Chapter 4.

#### 2.5 Optimization of Plasma Activation Process

Following the RCA clean, as mentioned before, different plasmas, such as NH<sub>3</sub>, O and Ar, were used for the surface activation process prelude the low temperature direct bonding. Either a Technics PECVD 900 series chamber for generating NH<sub>3</sub> plasma or a Technics RIE 800 series chamber for generating O or Ar plasma was used in this work. While all the plasmas succeeded somewhat, however, one has to adjust the operation parameters such as the gas flow rate, the chamber pressure (output mass flow controller, for RIE 800 only), the power of plasma, and the activation time, to obtain the best combination in order to accomplish the best activation effect for the bonding. Table 2.1 lists the optimized activation recipes for all the three kinds of plasmas used in this work.

#### 2.6 Plasma Treatment and Surface Activation Energy

Plasma activation process changes the kinetics of strong bond formation. Possible effects of the plasma activation process to the surface includes 1) chemical reaction of the plasma and the surface material, 2) electronic charge deposition onto the surface, 3) plasma induced surface damage, which may further cause re-arrangement of the atoms on the wafer surface, and the combinations of the above three items. A set of experiment is completed, with a) both reactive plasma gases (NH<sub>3</sub> and O) and inert plasma gas (Ar), b) initiate the bonding immediately after the plasma treatment and apply another wet surface clean (DI water rinse, in order to remove the possibly deposited charge). Table 2.2 shows

the experimental evidence of different treatment. The surface damage is obviously the common effect for all processes. It is believed that the diffusion coefficient (D) at the bonded interface is increased by the plasma induced surface damage, which can further increase the surface activation energy  $(E_a)$ . However, although Ar gas may not directly react with Si (comparing with O and NH<sub>3</sub>, they may chemically react with Si to form a thin layer of  $SiO_x$  or  $Si_xN_y$ ), it is possible that Ar ions remove chemisorbed water from the surface, rearrange the dangling bonds on the surface, and/or remove other contaminants on the surface, hence to introduce some sort of a chemical change to the bonding material. It is still an open question whether the physical damage or the chemical change to the surface is most critical for bonding mechanism, more experimental evidence is required before any explicit conclusion is drawn.

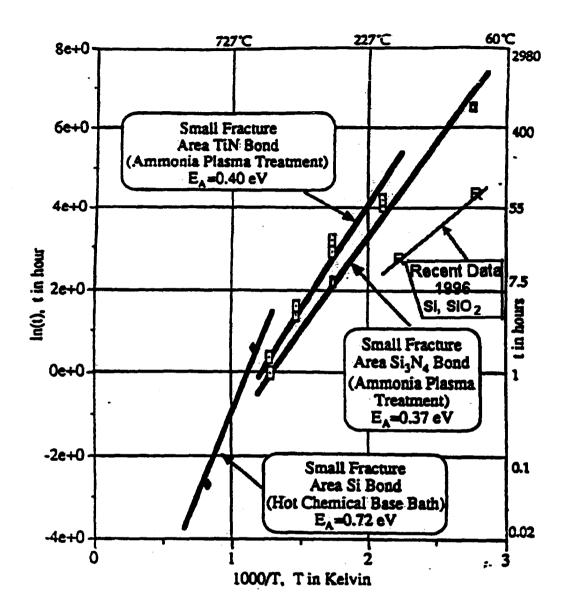

Figure 2.5 shows the reduction of the surface activation energy by using plasma treatment for the attempted bonded samples. It is found the bonded area of the plasma activated direct bond after initial contact of the two substrates appears to slowly grow, till the bond strength to be saturated at a certain value, e.g.  $\sim 1,000 \text{ ergs/cm}^2$ . The rate of the growth of the bonded area is linearly related to anneal time and temperature. To produce a bond strength at the saturation value, one can either fix the anneal temperature and increase the anneal time, or fix the anneal time but use a higher anneal temperature. It is found that the anneal time follows straight lines when plotted on a semilogrithimic scale versus reciprocal anneal temperature. This type of behavior is similar to many other natural systems (e.g., diffusion rate versus temperature) and can be referred to Arrhenius expression to the relationship. Therefore, the following model is used to describe this behavior:  $ln(t)=E_d/(kT)+C$ , where k is Boltzman's constant and C is an arbitrary

constant. Experimental data set are presented in Figure 2.5. At each data point, the bond strength is measured to be  $\sim 1,000 \text{ ergs/cm}^2$ . The horizontal axis represents 1000 over anneal temperature T (in Kelvin), while the vertical axis shows anneal time t (in hours). A simple relationship between t and T is then presented as:

$$t = t_0 \, Exp(-E_a/kT) \tag{2.1}$$

One can easily obtain the surface activation energy  $(E_a)$  by calculating the slope of the 1000/T vs. t curve. The experimental data indicates that, in the earlier high temperature direct bonding,  $E_a$  is about 0.72 eV, it is reduced gradually in different plasma activation process for treating different bonded surfaces, and the latest results (1996-97) show that  $E_a$  is only  $\sim 0.3$  eV for oxygen plasma activated Si/SiO<sub>2</sub> surfaces.

Conclusively, the surface activation energy is greatly reduced by plasma activation the bonded surfaces, much less energy is required to enhance the strong bond formation, therefore, the final thermal anneal temperature can be also greatly reduced.

#### 2.7 Three-Step Systematic Low Temperature Wafer Bonding Process

To implement a technology into the semiconductor industry, it has to be (1) able to fabricate reproducibly with a consistent high yield, and (2) reliable after long enough period of time after the fabrication. Earlier work of direct wafer bonding is always initiated by a pair of tweezers, and it was very dependent of a good deal of artistic talent of the operators and hard to reproduce consistently. Furthermore, it is hard to imagine that this tweezers-initiation can be applied in making a mass production in the IC industry. Therefore, a systematic method must be developed in order to make it possible to adopt this low temperature direct bonding technology into the daily routine IC fabrication [35, 36].

A systematic three-step process to low temperature direct bond silicon and/or SiO<sub>2</sub> surfaces was developed. The process activates the surface with ammonia, argon or oxygen plasma. While these activation processes allow a very strong low temperature bond to be created, they require techniques distinctly different from those found in previous work for reproducible results. The plasma processes do not result in a bond that propagates as a wave resulting from a point source initiation. A substantial pressure is required to initiate the bond. It is found that a three-step process using pressure and temperature results in very strong, reproducible bonds.

As mentioned above, the processes used to create strong, direct bonds differ considerably by various researchers. Work that is reported in several articles describes a process where a wafer bond with H<sub>2</sub>O precursor is initiated from pressure applied at a point source that propagates across the surface, as if a wave spreads out from the initial contact point across the entire surface. This point source initiation is also reported to produce void free bonds for sodium silicate bonded surfaces. It has also been the experience in our research group that bonds formed with an H<sub>2</sub>O precursor can be effectively initiated at a point that generates a wave that propagates across the surface. However, a number of papers that describe direct bonds to silicon make no reference to propagation of a surface wave propagating from a point. The bonds reported in these articles, however, do not result from an initial water bond. No reference to contact waves is found in the initiation of bonds that form after plasma activation. Plasma activated low temperature bonds have been described in earlier publications, without the initial bond forming from a wave propagating across the surface. While plasma activated low temperature bonds do not propagate as a wave, this technique does require the application

of considerable pressure applied over a substantial portion of the surface. In past plasma activated low temperature bonding work this pressure has been applied with tweezers and involved a good deal of artistic talent to generate successful bonds. Here, a systematic procedure has been developed that results in reproducible strong bonds after a low temperature anneal.

The bond is initiated by the application of a uniform pressure to the samples being bonded. It is known from earlier work that the initial plasma activated low temperature bonds are weak and require substantial pressure to initiate. In fact, the initial bond produced in the plasma activated low temperature bonding process is much weaker than generally found in a conventional process with water bonds. As a result of this weak initial bond the pair has often debonded due to the shear forces during the thermal shock of the final anneal step before a strong bond can develop. Therefore, a systematic three-step process was developed using plasma activation to avoid:

- 1) The artistic nature of the tweezers pressure application.

- 2) The debonding of the initial plasma activated pair due to thermal shear fracture of the weak bond.

In order to accomplish:

- 1) Possible mass production with consistent high yield in the IC industry.

- 2) Good reliability for a long period of time.

The following three-step systematic process has been developed for oxygen plasma activated low temperature bonding. It is found that the application of pressure in the first two steps of this process is essential for the generation of a uniform strong bond on clean semiconductor surfaces. The three-step process consists of:

- 1. Pressure. A pressure of greater than  $2.1 \times 10^5$  N/m<sup>2</sup> applied for 10 minutes was found to be necessary for a high likelihood of a uniform bond.

- 2. Pressure with temperature. The application of a pressure of greater than 4 × 10<sup>5</sup> N/m<sup>2</sup> at a temperature of 200 °C, for a period of 30 minutes was found to overcome the tendency of the pieces to debond during a final anneal process. It was found that while this intermediate pressure and temperature step did not produce a strong bond, it was strong enough avoid debonding when followed by a final anneal.

- 3. Temperature. While the intermediate (step 2) pressure and temperature anneal produced a high likelihood of a uniform bond, the strength of this bond was weak. A final anneal of 200 °C for 10 hours increased the bond strength greater than that of a normal high temperature direct bond or >1,000 ergs/cm<sup>2</sup>.

Similar three-step process has also been found appropriate for both ammonia and argon plasma activated low temperature bonding, with variations in the required pressures for step 1 and 2.

The following process is completed in a class-100 cleanroom of UC Davis to reduce the particle count to the lowest level. 100-mm commercial Czochralski (CZ) (100) silicon wafers are used in this work. The wafers are n-type with a resistivity of 1-2 ohmom and thickness of 500-550  $\mu$ m. The wafers are then cut into 2cm  $\times$  2cm square samples. All attempted bonding samples receive a regular RCA clean, as described in the previous section (2.4). BOE dip produces no observable difference in bonding results, which implies that this process works for both bare silicon and SiO<sub>2</sub> surfaces. The samples are dried in a N<sub>2</sub> gun after the finial DI water rinse. A Technics 800 series Micro Reactive Ion Etcher (RIE) is used for the surface plasma activation process. The

samples, which are handled by vacuum tweezers only during the whole process (this prevents any unnecessary damage on the wafer surface), are put into the chamber, bonding face up. The chamber is pumped to 6 mTorr, backfilled by oxygen at a flow rate of 10 sccm, the mass flow controller is adjusted till the pressure is at 135 mTorr. The activation proceeds at the power of 100 watts for a period of 10 minutes.

After the plasma surfaces treatment, a pair of samples is placed face-to-face into a pressure fixture shown in Fig. 2.6, where the spring is well calibrated and well controlled by turning the two knobs. The pair to be bonded is held between two perfectly flat gauge blocks, where there is a little hole in the center of each, and the pressure is applied through a stainless still ball which sits on the hole of the top gauge block. This plate is thus gimbaled by the still ball to keep the plates parallel during the application of pressure. A uniform pressure is therefore applied to the whole surface of the bonded pair.

The experimental results in Tables 2.3 through 2.5 for oxygen plasma activated samples classify the results by the nature of the infrared interference patterns seen in the bonded pairs at various stages of the three-step process. The bond type classification system rates the bond quality on a scale of 1 to 5, with the type 5 most likely to form a high quality strong bond after the final anneal (step 3) and a type 1 the least likely to form such a bond. Details of the bond type classification scheme are given in the Appendix.

Experimental results are shown in Tables 2.3, 2.4 and 2.5, they represents the results of step 1, 2, and 3 respectively in this three-step process. The raw bond type is given for each applied pressure, the average types of bond and the likelihood of producing uniform (type 4 or 5) bonds are calculated. Statistical descriptions appropriate

for the small sample sizes and the discrete, subjective bond classification system has been employed.

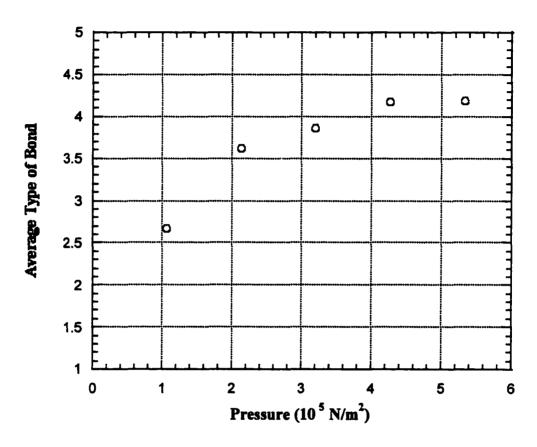

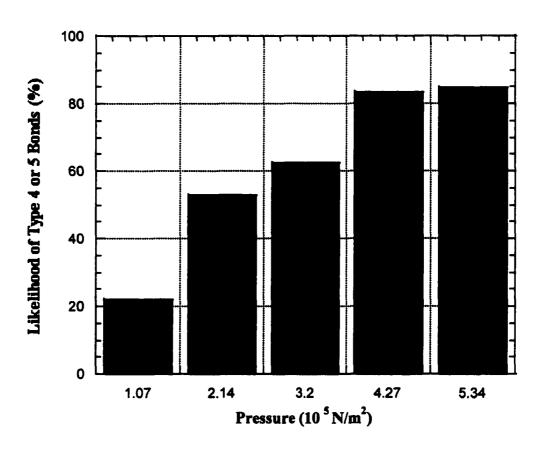

Table 2.3 represents the bond rating for the initial bond found as a function of pressures ranging from  $1.1 \times 10^5$  N/m<sup>2</sup> to  $5.3 \times 10^5$  N/m<sup>2</sup>. Column (I) gives the applied pressure, column (II) shows the classification types of bond corresponding to that pressure for each sample analyzed. The average type of bonds is calculated in column (III), and column (IV) gives the likelihood of forming a type 4 or 5 bonds, where the likelihood defined as the ratio of type 4 or 5 bonds produced compared with the total number attempted. Figure 2.7 shows a graph of these data where the bond classification improves only slightly for pressures greater than  $3.5 \times 10^5$  N/m<sup>2</sup>. Figure 2.8 plots the likelihood of producing a type 4 or 5 bond and shows that a pressure of  $2.1 \times 10^5$  N/m<sup>2</sup> is a pressure that has a likelihood of greater than 50% of producing a type 4 or 5 bond, while pressures greater than  $4.3 \times 10^5$  N/m<sup>2</sup> have a likelihood of 80% of producing a type 4 or 5 bond.

Table 2.4 depicts the experimental data describing the intermediate step where both pressure and temperature are applied to strengthen the bond without shearing the pair. Column (I) through (IV) in Table 2.4 have the same parameters as in Table 2.3. The average type of bond corresponding to different pressure is also plotted in Figure 2.9. In this case the average bond type improves approximately linearly with pressure requiring greater than  $4 \times 10^5$  N/m<sup>2</sup> for bonds better than type 4. Figure 2.10 then plots the likelihood of producing a type 4 or 5 bond with various pressures. These data illustrate that a dramatic improvement in this likelihood occurs for pressures greater than  $4 \times 10^5$  N/m<sup>2</sup>.

Table 2.5 shows the type of bond produced at various points with variations in the three-step process described in this paper. Column A) is the normal process, while column C) shows the data where the second step is removed. The pairs of numbers in each column indicate the type of bond before and after the third step anneal. The final bonds in columns A) are of good quality when the bond at the intermediate step was good. Final results in column C) are uniformly poor indicating that step 2 (pressure and temperature) is of critical importance.

A systematic low silicon and/or SiO<sub>2</sub> direct bonding process using pressure and temperature is developed. Oxygen, Argon or Ammonia plasma activation was used to initiate the process. For the case of an oxygen plasma activation it was found that a pressure greater than 2.1 × 10<sup>5</sup> N/m<sup>2</sup> is needed for step 1. A pressure greater than 4 × 10<sup>5</sup> N/m<sup>2</sup> at 200 °C, 30 minutes was found necessary for step 2. After appropriate pressures and temperatures in steps 1 and 2 an anneal of 200 °C for 10 hours is required for the final anneal. After the plasma activates the wafer surface, the first two steps create uniform bonds, while the third step will increase the bond strength to > 1,000 ergs/cm<sup>2</sup>, which is as strong as in the high temperature direct bond. The results of this investigation clearly indicate that the tweezers push can be replaced with a well-defined application of uniform pressure, provided a combination of pressure and temperature is subsequently applied. The standard three-step process follows the pressure and temperature step with a standard anneal; this is found to produce an acceptable process. However, the three-step process may be collapsed into two-step process where a relatively long anneal under pressure is found to produce an excellent bond. The bond strength was measured after a

long period storage time in air (> 6 months), no difference was found from the as-bonded samples.

As a conclusion of this chapter, the three-step process can be used in mass production with a consistent high yield (~ 80%), and the bonds are reliable after only 10 hours of 200 °C thermal anneal.

#### References

- George Wallis and Daniel T. Pomerantz, "Field Assisted Glass-Metal Sealing", Journal of Applied Physics, Vol. 40, No. 10, September 1969, 3946-3949

- M. Kimura, K. Egami, M. Kanamori and T. Hamaguchi, "Epitaxial film transfer technique for producing ingle crystal Si film on an insulating substrate", Appl. Phys. Lett. 43 (3), August 1983, 263-265

- Leslie A. Field and Richard S. Muller, "Fusing Silicon Wafers with Low Melting Temperature Class", Sensors and Actuators A21-23 (1990) 935-938

- A. Yamada, T. Kawasaki and M. Kawashima, "SOI BY WAFER BONDING WITH SPIN-ON-CLASS AS ADHESIVE", Electronics Letters, 2<sup>nd</sup> January 1987, Vol. 23, No. 1, 39-40

- A. Yamada, T. Kawasaki and M. Kawashima, "BONDING SILICON WAFER TO SILICON NITRID WITH SPIN-ON CLASS AS ADHESIVE", Electronics Letters, 2<sup>nd</sup> January 1987, Vol. 23, No. 1, 314-315

- 6. W. P. Eaton, S. H. Risbud, R. L. Smith, "Wafer bonding by low tmperature melting glass", Proceedings of the First International Symposium on Semiconductor Wafer Bonding: Science, Technology and Applications, 13-18, 1991, p. 146-52

- W. P. Eaton, S. H. Risbud, R. L. Smith, "Silicon wafer-to-wafer bonding at T<200°C with polymethylmethacrylate", Applied Physics Letters, Vol. 65, Iss. 4, p. 439-41, 25</li>

July 1994

- Jayant K. Bhagat and David B. Hicks, Bonding of silicon by solid-phase epitaxy", J.

Appl. Phys. 61 (8), 15 April 1987, 3118-20

- Goran S. Matijasevic, Chen Y. Wang and Chin C. Lee, "Void Free Bonding of Large Silicon Dice Using Gold-Tin Alloys", IEEE Transactions on Compinents, Hybrids, and Manufacturing Technology, Vol. 13, No. 4, December 1990, 1128-33

- 10. J. B. Lasky, "Wafer bonding for silicon-on-insulator technologies", Appl. Phys. Lett.,48 (1), 6 January 1986, 78-80

- 11. Stefan Bengtsson, "Semiconductor Wafer Bonding: A Review of Interfacial Properties and Applications", Journal of Electronic Materials, Vol. 21, No. 8, 1992, pp841 862

- 12. W. P. Maszara, G. Goetz, A. Caviglia and J. B. McKitterick, "Bonding of silicon wafers for silicon-on-insulator", J. Appl. Phys. 64, 4943 (1988)

- 13. Takao Abe, Tokio Takei, Atsuo Uchiyama, Katsuo Yoshizawa and Yasuaki Nakazato, Japanese Journal of Applied Physics, "Silicon Wafer Bonding Mechanism for Silicon-on-Insulator Structures", Vol. 29, No. 12, December, 1990, pp. L 2311-L 2314

- 14. R. W. Bower, M. S. Ismail, and S. N. Farrens, "Aligned Wafer Bonding: A Key to Three Dimensional Microstructures", Journal of Electronic Materials, Vol. 20, No. 5, 1991

- R. W. Bower and M. S. Ismail, "Nitrogen Based Low Temperature Direct Bonding",

US patent No. 5,503,704, filed June 23, 1992, issued April, 1996.

- 16. Robert W. Bower, Mohd S. Ismail and Brian E. Roberds, "Low temperature Si<sub>3</sub>N<sub>4</sub> direct bonding", Appl. Phys. Lett. **62** (26), 28 June, 1993, 3485-87

- 17. V. H. C. Watt, R. W. Bower, "Low temperature direct bonding of nonhydrophilic surfaces", Electronics Letters, Vol. 30 (9), p. 693-5, 29 April 1994

- 18. Gudrun Kissinger and Wolfgang Kissinger, "Void-free silicon-wafer-bond strengthening in the 200-400 °C range", Sensors and Actuators A, 36 (1993) 149-156

- 19. Qin-Yi Tong, G. Cha, R. Gafiteanu, U. Gosele, "Low temperature wafer direct bonding", Journal of Microelectromechanical Systems, Vol. 3 (1), p. 29-35, March 1994

- 20. Q.-Y. Tong, U. Gosele, "Process design of low temperature wafer bonding", Proceedings of the Third International Symposium on Semiconductor Wafer Bonding: Physics and Applications, P. 78-95, 1995

- 21. Q.-Y. Tong, U. Gosele, "A model of low-temperature wafer bonding and its applications", Journal of the Electrochemical Society, Vol. 143 (5), p. 1773-9, May 1996

- 22. U. Gosele, H. Stenzel, T. Martini, J. Steinkirchner, D. Conrad, and K. Scheerschmidt, "Self-propagting room-temperature silicon wafer bonding in ultrahigh vacuum", Appl. Phys. Lett. 67 (24), 11 December 1995, 3614-16

- 23. H. Takagi, K. Kikuchi, R. Maeda, T.R. Chung, T. Suga, "Silicon wafer direct bonding at room temperature in a vacuum", Journal of Mechanical Engineering Laboratory, Vol. 50 (3), p. 53-8, May 1996

- 24. James a. Folta, Charles E. Hunt and Shari N. Farrens, "Low-Temperature Wafer Bonding of Surfaces Using a Reactive Sputtered Oxide", J. Electrochem. Soc., Vol. 141, No. 8, August 1994

- 25. Shari N. Farrens, James R. Dekker, Jason K. Smith, and Brian E. Roberds, "Chemical Free Room Temperature Wafer To Wafer Direct Bonding", J. Electrochem. Soc., Vol. 142, No. 11, November 1995, 3949-55

- 26. B. Roberds and S. Farrens, "An AFM study on the roughness of silicon wafers correlated with direct wafer bonding", Proceedings of the Third International Symposium on Semiconductor Wafer Bonding: Physics and Applications, p. 326-41, 21-26 May 1995

- 27. B. Roberds and S. Farrens, "An atomic force microscopy study on the roughness of silicon wafers correlated with direct wafer bonding", Journal of Electrochemical Society, Vol. 143 (7), p. 2365-71, July 1996

- 28. R. Stengl, K.-Y. Ahn and U. Gosele, "Bubble-free silicon wafer bonding in a noncleanroom environment", Jpn. J. Appl. Phys. 27, L2364 (1988)

- 29. H. J. Quenzer and W. Benecke, "Low-temperature silicon wafer bonding", Sensors and Actuators A, 32 (1992) 340-344

- 30. Takao Abe, Tokio Takei, Atsuo Uchiyama, Katsuo Yoshizawa and Yasuaki Nakazato, "Surface Impurities Encapsulated by Silicon Wafer Bonding", Japanese Journal of Applied Physics, Vol. 29, No. 12, December, 1990, pp. L 2315-L 2318

- 31. Stefan Bengtsson and Olof Engstrom, "Interface charge control of directly bonded silicon structures", J. Appl. Phys. 66(3), 1 August 1989, 1231-1239

- 32. H. Takagi, K. Kikuchi, and Maeda, "Surface activated bonding of silicon wafers at room temperature", Appl. Phys. Lett. 68(16), 15 April 1996, 2222-2224

- 33. R.W. Bower, W.Chan, L.Hong, L. LeBoeuf, Y.A. Li, and J. Lee, "Optimization of Low Temperature NH3 Plasma Activated Direct Bonding", Technical Digest Solid-State Sensor and Actuator Workshop, Hilton Head, SC, June 1996

- 34. Robert W. Bower and Frank Y.-J. Chin, "Low Temperature Direct Silicon Wafer Bonding Using Argon Activation", Jpn. J. Appl. Phys. Vol. 36 (1997) Pt. 2, No. 5A, L527-L528

- 35. Y. Albert Li and Robert W. Bower, "Low temperature direct bonding using pressure and temperature", Proceedings of SPIE, Vol. 3184, June 1997, 124-128

- 36. Y. Albert Li and Robert W. Bower, "Systematic Low Temperature Silicon Bonding using Pressure and Temperature", Japanese Journal of Applied Physics, Vol. 37, No. 3, 737-741 (March), 1998

- 37. R. W. Bower, W. Chan, L. Hong, V. H. C. Watt, "Mechanical considerations for direct bonding of semiconductor materials", Proceedings of the Third International Symposium on Semiconductor Wafer Bonding: Physics and Applications, p. 107-14, 21-26 May 1995

- 38. V. H. C. Watt, M. Moinpour, R. Bower, and R. Sundararaman, "Atomic force microscopy: a key to direct wafer bonding technology", Journal of Materials Science Letters, Vol. 14 (2), p. 96-8, 15 Jan. 1995

| Gas             | Power | Time   | Flow Rate | Pressure | Activation<br>Chamber |

|-----------------|-------|--------|-----------|----------|-----------------------|

| NH <sub>3</sub> | 50 W  | 5 min  | 75 sccm   | 430 mT   | Technics<br>PECVD 900 |

| 0               | 200 W | 10 min | 10 sccm   | 135 mT   | Technics RIE<br>800   |

| Ar              | 100 W | 10 min | 10 sccm   | 150 mT   | Technics RIE<br>800   |

Table 2.1 Optimized recipes for different plasma activation process in the low temperature direct bonding.

| Plasma          | Surface                    | Chemical | Charge | Damage |

|-----------------|----------------------------|----------|--------|--------|

| NH <sub>3</sub> | Dry                        | ×        | ×      | ×      |

| NH <sub>3</sub> | Wet clean after activation | ×        |        | ×      |

| 0               | Dry                        | ×        | ×      | ×      |

| Ar              | Dry                        | ?        | ×      | ×      |

| Conclusion      |                            | ?        | No     | Yes    |

Table 2.2. Experimental evidence of the effects for different plasma activation process in low temperature direct bonding

| Pressure                      | Bond Type Data                                                 | Average Type of | Likelihood of a 4 or |

|-------------------------------|----------------------------------------------------------------|-----------------|----------------------|

| $(\times 10^5 \text{ N/m}^2)$ | (II)                                                           | Bond            | 5 bonds (%)          |

| (I)                           |                                                                | (III)           | (IV)                 |

| 1.1                           | 1, 3, 3, 1, 4, 4, 3,<br>2, 3                                   | 2.67            | 22.2                 |

| 2.1                           | 5, 5, 4, 5, 4, 5, 4,<br>4, 4, 2.5, 1, 3, 2,<br>2.5, 3.5, 4, 3, | 3.62            | 52.9                 |

| 3.2                           | 5, 5, 5, 3, 5, 4, 2,<br>2,                                     | 3.86            | 62.5                 |

| 4.3                           | 5, 4, 2, 4, 5, 5                                               | 4.17            | 83.3                 |

| 5.3                           | 3, 4, 4, 4, 4.5, 4,<br>4.5, 4, 3, 4.5, 5,<br>5, 5              | 4.19            | 84.6                 |

Table 2.3. Initial bonding results with pressure only

| Pressure                      | Bond Type Data                 | Average Type | Likelihood (%) |

|-------------------------------|--------------------------------|--------------|----------------|

| $(\times 10^5 \text{ N/m}^2)$ | (II)                           | of Bond      | (IV)           |

| (I)                           |                                | (III)        |                |

| 1.516                         | 3.5, 3, 2.5, 2                 | 2.75         | 0              |

| 2.067                         | 2, 2.5, 2.5, 3.5, 2.5, 3.5, 3  | 2.8          | 0              |

| 2.549                         | 3, 2, 5                        | 3.3          | 33.3           |

| 3.101                         | 4, 3.5, 3, 3, 2.5, 5, 4.5, 3.5 | 3.63         | 37.5           |

| 4.134                         | 4, 3.5, 5, 4.5, 4.5, 5,        | 4.25         | 83.3           |

| 5.168                         | 4, 5, 5, 5, 5, 5, 5, 4.5, 4.5  | 4.8          | 100            |

Table 2.4 Bonding samples after pressure and temperature

| Anneal results w/ step 2 (before/after) (A)                                                                                                                                                                   | Anneal results w/o step 2 (before/after) (B)                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2/3, 4/5, 2/2.5, 5/5, 5/5, 4/5, 2/2, 3/5, 5/5, 3/3, 2/3, 5/5, 2/2.5, 5/5, 4/4.5, 3/3, 5/5, 5/5, 3/4, 5/5, 4/4, 5/4, 5/5, 5/5, 2/2, 4/3.5, 2/2, 4/4, 2/4, 2/2, 2/2, 3/3, 4/4, 3/3, 4/4, 5/5, 5/5, 5/5, 2.5/2.5 | 5/1, 5/1, 4/1, 5/1, 5/1, 5/1, 3/2, 3/2, 2/1, 2/1, 5/1, 4/2, 4/3, 3/2, 2/3, 3/1, 5/1, 4/1, 5/1, 3/1, 5/1, 3/1, 2/2, 5/1, 5/1, 3/1, 3/3 |

Table 2.5 Bond types before and after the third (200 °C anneal) step with or without the intermediate step (second step with both temperature and pressure)

Fig. 2.1. The experimental setup for aligned wafer bonding (after Bower et al., 1991)

Fig. 2.2. Some mechanical considerations for the wafer bonding - radius of curvature, waviness and microroughness (after Bower et al., where the microroughness should be less than 1nm; waviness should be less than 10<sup>-6</sup>; and radius of curvature should be greater than 100m for a successful direct bonding.

Fig. 2.3. AFM surface measurement shows, for commercial (100) silicon wafer, the microroughness is much below the mechanical criteria for achieving a successful wafer bonding

Fig. 2.4. Cross sectional SEM image of aligned bonded commercial SRAMs (after Bower et at., 1993)

Fig. 2.5. Reduction of the surface activation energy  $(E_a)$  by applying the plasma treatment to the attempted bonded samples

Fig. 2.6. Pressure fixture built for applying the pressure in three-step low temperature direct bonding process.

Fig. 2.7. Average initial type of bond with pressure only

Fig. 2.8. Likelihood of Good Bond with Pressure only

Fig. 2.9. Average type of bond after pressure and temperature treatment

Fig. 2.10. Likelihood of Good Bond after Pressure and Temperature Treatment

## CHAPTER 3

## **Reversible Bonding**

#### 3.1 Importance of the Reworkability in the Three-dimensional Integration

This chapter describes the formation and application of reversible low temperature bonds for fabrication of three-dimensional microelectronic structures. The basis of this reversible bond is that a partially formed low temperature bond is strong enough to be tested, but may be debonded without significant damage to the surface so a new bond may be subsequently formed. The three-step low temperature bonding process has provided an excellent approach to form this partial bond [1, 2]. This three-step process, as described in detail in the last chapter, consists of 1) pressure, 2) pressure and temperature, and 3) temperature. The first and second steps of this process create a uniform, void free, weak bond of strength less than 100 ergs/cm<sup>2</sup> that can be easily severed. The third step consists of a long anneal (10 hours) at 200 °C that creates a bond of strength greater than 1,000 ergs/cm<sup>2</sup>. A thin layer of silicon (or other semiconductor such as Ge, SiC or diamond, etc) is then to be used to fabricate the various structures that will comprise the three-dimensional layered structure. A planarized layer of bondable material is then formed on the surface of the structured thin silicon-on-insulator (SOI) layer. The processed thin layer is then reversibly bonded to a conformable transfer membrane. The thin layer of processed material is then released from the bulk wafer. The thin layer of processed material is then reversibly align-bonded to the threedimensional microstructure. The resulting composite structure is then tested. If the

system tests good the reversible bond is made permanent by completing the third step of the process and the process is repeated for the next layer. If the test fails, the top layer is removed at the reversible bond and reworked [3, 4].

Direct bonding of silicon and related semiconductor fabrication materials such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and TiN has been studied extensively for the past decade [5-12]. In the early 1990's, the concept of low temperature direct bonding was introduced [13-20]. Later, in the 1996-97 period, the concept of a three-step low temperature direct bonding methodology was also introduced [1, 2]. This low temperature direct bonding process, together with the evidence of a low temperature hydrogen ion cut technology for creating silicon-on-insulator (SOI) material and capable of producing transferable thin layers of a variety of bare and processed micro-electro-mechanical structure (MEMS) and optical materials is presented. In order to utilize this technology for the formation of threedimensional microstructures and multichip modules, it is extremely important to have a rework procedure that allows a bonded part that proves defective to be removed and replaced so that the entire structure is not rendered inoperable. This concept is important in three-dimensional structures and multichip modules because the value of the entire item becomes larger as each new element is added. Thus, near the end of the process it is very costly to allow the entire module to fail as a result of adding one new defective element. Thus, we developed a rework procedure in the form of a reversible low temperature bond into our process. The three-step low temperature direct bonding process lends itself perfectly to this concept since a weak, uniform bond is formed after the first and second steps of the process that can be easily severed.

### 3.2 Possible Ways to Reverse the Bond

The rework requirements using a low temperature direct bond must include the following:

- a) The reversible bond must be strong enough to hold the materials together in alignment during ordinary handling.

- b) The reversible bond must be easily severed by a standardized procedure that does not damage the surfaces, so that rebonding may be accomplished with a replacement chip.

- c) The reversible bonded sample must be able to be tested *in situ* to determine whether rework is necessary.

The following three methods of reversing a bond were studied experimentally with the following results:

#### 1) The straight pull normal to the plane of the bonded pair.

A force applied normal to the bonded pair was first investigated as a method to reverse a bond. It was found that this straight pull method of reversing a direct bond after step 1 or step 2 of the three-step process required forces ranging from 2 to 8 lbs/in<sup>2</sup>. The forces required were also found to be difficult to control by process variations. It was therefore decided that the straight pull method would not be used in this procedure.

### 2) A twisting or sliding force in the plane of the bonded pair.

The application of a sliding or twisting force in the plane of the bonded pair was found to be unacceptable because the surface damage caused by this action prevented rebonding of the materials.

#### 3) Side torque applied on the edge of the material.

The application of a side torque to the bonded parts was found to allow the surfaces to be easily and reproducibly debonded without noticeable surface damage. Fig. 3.1 shows the bonded sample with multiple layers of active devices already in place, they are bonded with an offset upon aligned bonding. Therefore, a force can be easily applied along the edge of each layer.

In summary of the experimental analysis it is found the side torque method to be an acceptable method to debond low temperature direct bonded oxygen plasma activated samples at the conclusion of step 1 or 2 of the process. It is also found that debonded samples were not damaged and could be rebonded. Finally, it is found that these reversible bonds provided suitable electrical conduction to allow in situ testing of the bonded layer.

A number of possible manufacturing methods for applying a side torque to debond a reversible pair are possible. One such method would be to generate a notch on the top or bottom edge of each wafer or chip. A simple tool could then be inserted into the notch whereby a force normal the bonded plane could be applied by a twist or pull of the tool that applies a normal force to one side of the pair perpendicular to the bonded plane.

#### 3.1 Analysis of Reversible Bonding for Two Typical Cases

The most interesting geometries for wafer bonding are circular for wafers and rectangular for chips. The force required for debonding with a side torque applied to these geometries is considered in detail.

Fig. 3.2 illustrates the geometry of a line side torque applied to a rectangular bonded chip of dimension d by w. The line force  $F_d$  (in the unit of force/length, e.g., N/m, etc.) is applied over a length 2h.

The total torque generated by force  $F_d$  can be expressed as  $2d\int_0^h F_d dy$ . By equating this integration, also note that  $h = d(\tan \alpha_1)$ , to the opposite couple of the bonded pair,  $\int_0^d w f_d x dx$ , where  $f_d$  is force generated by bonding per unit area (in the unit of force/area, e.g. N/m², etc.), then it is easily found that the line force  $F_d$  necessary in terms of the bonding force per unit area,  $f_d$ , is given by

$$F_d = \frac{wf_d}{4\tan\alpha_1} \text{ or } F_d = \frac{dwf_d}{4h}$$

(3.1)

or the total applied force is

$$F_d 2h = \frac{hwf_d}{2\tan\alpha} \text{ or } F_d 2h = \frac{dwf_d}{2}$$

(3.2)