## Low temperature Si<sub>3</sub>N<sub>4</sub> direct bonding

Robert W. Bower, Mohd S. Ismail, and Brian E. Roberds

Citation: Appl. Phys. Lett. **62**, 3485 (1993); View online: https://doi.org/10.1063/1.109002

View Table of Contents: http://aip.scitation.org/toc/apl/62/26

Published by the American Institute of Physics

## Articles you may be interested in

Wafer bonding for silicon-on-insulator technologies Applied Physics Letters **48**, 78 (1998); 10.1063/1.96768

Mechanisms for room temperature direct wafer bonding Journal of Applied Physics **113**, 094905 (2013); 10.1063/1.4794319

Bonding of silicon wafers for silicon-on-insulator Journal of Applied Physics **64**, 4943 (1998); 10.1063/1.342443

Surface activated bonding of silicon wafers at room temperature Applied Physics Letters **68**, 2222 (1998); 10.1063/1.115865

The hydrogen content of plasma-deposited silicon nitride Journal of Applied Physics **49**, 2473 (2008); 10.1063/1.325095

Silicon-to-silicon direct bonding method Journal of Applied Physics **60**, 2987 (1998); 10.1063/1.337750

## Low temperature Si<sub>3</sub>N<sub>4</sub> direct bonding

Robert W. Bower and Mohd S. Ismail

Department of Electrical and Computer Engineering, University of California, Davis, California 85616

Brian E. Roberds

Department of Mechanical, Aeronautical and Material Engineering, University of California, Davis, California 95616

(Received 16 November 1992; accepted for publication 7 April 1993)

Extremely strong bonds can be formed between smooth, clean layers of  $\mathrm{Si_3N_4}$  at temperatures ranging between 90 and 300 °C. These bonds have been formed between  $\mathrm{Si_3N_4}$  layers deposited on various substrates with deposition temperatures as low as 300 °C. The bond is initially formed at room temperature and subsequently annealed at temperatures ranging between 90 and 300 °C. Thus, the materials bonded in this manner are never exposed to temperatures higher than 300 °C. This low temperature bond greatly expands the range of applications of direct bonding which had heretofore been restricted by the temperatures of 700 to 1000 °C required by conventional wafer bonding.

Direct wafer bonding between layers of silicon and SiO<sub>2</sub> have been studied and applied successfully to a variety of applications including bond and etch back for silicon-on-insulator devices (SOI), sensors and actuators, and aligned wafer bonded structures. Although these bonding techniques have proven useful the high anneal temperature required by this technique has limited the applications. Previously, it has been reported that Si<sub>3</sub>N<sub>4</sub> is not a bondable surface, 1,7 although an oxidized surface of nitride was reported to bond at high temperatures consistent with silicon fusion bonding.8 Direct bonding of lowmetalorganic chemical-vapor deposition pressure (LPCVD) of Si<sub>3</sub>N<sub>4</sub> at temperatures greater than 800 °C has also been reported. The Si<sub>3</sub>N<sub>4</sub> bonding technique described here allows the fabrication of microstructures with materials that are able to withstand temperatures of 100 to 300 °C. The applications which are possible with this procedure include a variety of optoelectronic and high frequency devices that require materials such as GaAs and InP. This low temperature bonding technique reduces the problems of thermal mismatch in bonding dissimilar materials. Thus, materials such as GaAs and InP may be bonded to silicon to combine the power and economy of silicon integrated circuits to these high performance optoelectronic materials. Diamond heat sinks may also be bonded to a variety of materials to improve heat dissipation or mechanical durability. It also follows that combinations of III-V and II-VI materials or devices may be combined with low temperature bonding that are otherwise difficult to merge with conventional heteroepitaxial techniques. Van der Waals bonding of GaAs using epitaxial lift-off has been successfully accomplished to bond GaAs to a number of substrates. 10 The strength of this epitaxial lift-off bond has subsequently been improved by using an interfacial layer of Pd. 11 However, the cited literature does not report the capability of producing electrically conducting and insulating regions, nor can prefabricated structures be critically aligned and bonded with the epitaxial lift-off process.

Additionally, low temperature bonding can be applied to planarized surfaces of "completed" integrated circuit

chips and wafers which include the conventional Al metalization. Normally, the Al metalization would limit bonding steps to temperatures of 400 to 450 °C, which again precludes conventional high temperature bonding. Completed integrated circuits have only been bondable using organic glues or indium bumps. Both of these types of bonds have limitations compared with a clean, low temperature Si<sub>3</sub>N<sub>4</sub> bond. <sup>12,13</sup> To complete this discussion we should add that we have found a companion electrically conducting material, TiN, to complement Si<sub>3</sub>N<sub>4</sub> to provide both insulating and conducting surfaces which may be align bonded at low temperature. TiN coated silicon wafers have been activated and found to produce strong bonds at temperatures as low as 90 °C. The combination of Si<sub>2</sub>N<sub>4</sub> and TiN surfaces align bonded provide electrical, insulating, and optical connections between the joined layers for three dimensional optoelectronic elements.<sup>14</sup>

Material preparation for low temperature Si<sub>3</sub>N<sub>4</sub> bonding has many similarities to other wafer bonding. 15 Wafer flatness and surface roughness have been found to be important physical considerations in bonding other thin film deposited materials. 16 Deposition of about 500 Å thick Si<sub>3</sub>N<sub>4</sub> was achieved using plasma enhanced chemical deposition at 300 °C. The wet chemical cleaning of the nitride requires a controlled time treatment of a modified RCA clean where the NH<sub>4</sub>OH is diluted to 25% of that used in a standard RCA clean. The reduced NH4OH in the base cleaning agent offers the effectiveness of a standard RCA clean with less silicon nitride surface roughening. 17 The final step in the surface preparation includes a 10 s dip in 1% HF which renders the surfaces hydrophilic and enables bonding immediately after rinsing and spin drying. A one step process of bonding Si<sub>3</sub>N<sub>4</sub> has also been developed. A NH<sub>3</sub> plasma activation for several minutes immediately after Si<sub>3</sub>N<sub>4</sub> deposition without breaking the plasma renders the surface for direct bonding. The utilization of NH3 plasma treatment in high temperature direct bonding of silicon and silicon dioxide has been reported previously. 18

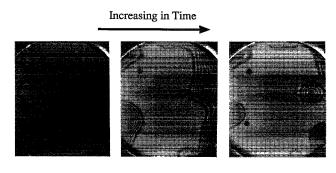

We have successfully bonded silicon to silicon, silicon to  $SiO_2$ , and Si to GaAs using  $Si_3N_4$  as the intermediate bonding layer. The bonded area of the  $Si_3N_4$  direct bond

FIG. 1. Infrared images of the spread in the bonded area of Si<sub>3</sub>N<sub>4</sub> surfaces at room temperature upon initial contact of the two substrates.

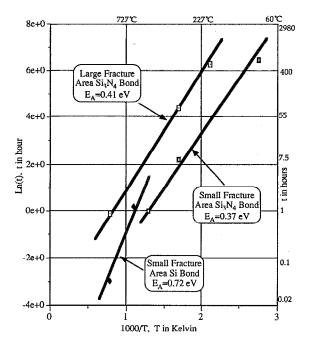

after initial contact of the two substrates appears to slowly grow as illustrated in the infrared micrograph in Fig. 1. The rate of growth of the bonded area is not as rapid as in the silicon direct bonding. The Si<sub>3</sub>N<sub>4</sub> direct bond has been found to be strong enough to result in three dimensional fracture in tensile strength tests conducted on samples annealed for various lengths of time at temperatures ranging from 90 to 300 °C. These data are presented in Fig. 2 which plots ln(t) versus 1000/T, where t is the annealing time leading to a given fracture morphology as indicated in this figure, and T is temperature in Kelvin. This figure plots data for low temperature Si<sub>3</sub>N<sub>4</sub> bonds and also for high temperature silicon bonds. <sup>19</sup> These sets of data have been analyzed and fit to the relationship  $ln(t) = E_0/K(1/T)$ +C, where C is a constant.  $E_a$  is found from this analysis to be equal to approximately 0.37 eV for Si<sub>3</sub>N<sub>4</sub> direct bonds and 0.73 eV for Si direct bonds where the time t was determined for the onset of three-dimensional fracture for a tensile pull that resulted in fracture of the bonded couple.

FIG. 2. Graph plot of  $\ln(t)$  vs 1/T, where t is the annealing time to give the indicated fracture-type and T is temperature in Kelvin. Data for  $\mathrm{Si}_3\mathrm{N}_4$  direct bond and silicon direct bond were plotted on the same graph for comparison.

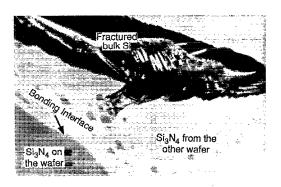

FIG. 3. A photomicrograph of one of the tensile test samples that shows an example of the three-dimensional fracture of Si<sub>3</sub>N<sub>4</sub> direct bonds. Both substrates are silicon.

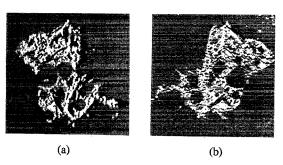

The time t required to create a large area three dimensional fracture for Si<sub>3</sub>N<sub>4</sub> direct bonds was also determined and found to fit a linear plot of ln(t) versus 1000/T over temperatures ranging from approximately 200 to 1000 °C. For the large area fracture case an approximate value of  $E_a$ =0.41 eV was determined for the  $Si_3N_4$  direct bonds. Thus, the values for  $E_a$  for the onset of fracture and large area fracture for Si<sub>3</sub>N<sub>4</sub> direct bonds are found to be within 10% of each other indicating that a common limiting process may control bond development over temperatures ranging from 90 to 1000 °C. Fracture occurs at about 2 MPa for Si<sub>3</sub>N<sub>4</sub> direct bonds. This value may be compared to the bulk silicon fracture of approximately 10 MPa. 19 The lower value for the fracture of Si<sub>3</sub>N<sub>4</sub> may be related to the fact that three-dimensional fracture may be initiated by defects in the substrate induced by internal stress caused by the deposited Si<sub>3</sub>N<sub>4</sub> film. This conjecture tends to be corroborated by the examination of the bond fracture shown in Fig. 3. It should be noted in this photomicrograph that the bonded interface between the Si<sub>3</sub>N<sub>4</sub> layers appears to be intact while fracture has occurred in the bulk of the bonded silicon substrates. Figure 4 is a photomicrograph that shows the fractured surface of Si bonded to GaAs with Si<sub>3</sub>N<sub>4</sub> as the intermediate layer. This photomicrograph reveals that fracture occurred in the relatively more brittle GaAs rather than the silicon or silicon nitride interface.

The significant difference in activation energy between the  $Si_3N_4$  direct bond and the silicon direct bond would

FIG. 4. A photomicrograph of the fractured surface of a small sample of Si bonded to GaAs via Si<sub>3</sub>N<sub>4</sub> direct bonding, where (a) is the silicon substrate and (b) is the GaAs substrate.

suggest that a considerably different surface chemistry is involved for the Si<sub>3</sub>N<sub>4</sub> direct process than that proposed by Stengl for the silicon direct bond.<sup>20</sup> The final stage of the cohesive bond in silicon direct bonding has been described in many articles including Stengl's as a covalent Si-O-Si chemical structure.20 The Si-O-Si bond is suggested to form via the interaction between two radicals of SiOH at temperatures higher than 700 °C.20 We suggest that surface free radicals of Si-N-H may be responsible for the formation of direct bonds at the Si<sub>3</sub>N<sub>4</sub>-Si<sub>3</sub>N<sub>4</sub> interface. The cohesive direct bond of the Si-(N)-Si-type has been achieved at temperatures as low as 90 °C. The activation energies of 0.37 and 0.41 eV for Si<sub>3</sub>N<sub>4</sub> direct bonding are found to be comparable with the activation energy of the permeability of H<sub>2</sub> in vitreous silica of about 0.38 eV reported by Lee et al. 21 Based on this result we speculate that a chemical reaction as follows:

$$\equiv$$

Si- $(N_xH_y)+(N_xH_y)$ -Si $\equiv \rightarrow \equiv$ Si- $(2N_x)$ -Si $\equiv +yH_2$

may be responsible where the released hydrogen diffuses from the bonding interface. The surface chemistry of treated Si<sub>3</sub>N<sub>4</sub> layers using both processes described in this letter are currently under investigation.

This letter has described the technique to achieve low temperature Si<sub>3</sub>N<sub>4</sub> direct bonding. Successful direct bonding of the coated Si<sub>3</sub>N<sub>4</sub> layer has been applied to silicon, silicon dioxide, and GaAs substrate wafers. The activation energy for Si<sub>3</sub>N<sub>4</sub> direct bonding was found to range from 0.37 to 0.41 eV which is approximately half of the value found for silicon direct bonding. This low activation energy allows bonding of optoelectronic materials and completed integrated circuits with Al metalization in place. We suggest that the surface chemistry of Si<sub>3</sub>N<sub>4</sub> bonding may differ from that found in direct silicon bonding. Two methods of a wet chemical process and a one-step plasma process for surface preparation prior to initial Si<sub>3</sub>N<sub>4</sub> direct bonding has been established.

The authors wish to thank Hughes Aircraft Company

for supplying materials, financial and technical support for this work. We also wish to thank Dr. Sherri Farrens for her helpful suggestions. The work has also been funded under UC-Micro program.

- <sup>1</sup>J. B. Lasky, Appl. Phys. Lett. 48, 78 (1986).

- <sup>2</sup> K. Peterson, P. Barth, J. Plydock, J. Brown, J. Mallon, Jr., and J. Bryzek, Solid State Sensor and Actuator Workshop Technical Digest, Hilton Head Island, South Carolina, June 1988.

- <sup>3</sup>G. S. Chung, S. Kawahito, M. Ishida, and T. Nakamura, Electron. Lett. 27, 1098 (1991).

- <sup>4</sup>R. W. Bower, M. S. Ismail, and S. N. Farrens, J. Electron. Mater. 20, 383 (1991).

- <sup>5</sup>R. W. Bower and M. S. Ismail, Technical Digest in International Conference on Solid-State Sensors and Actuators, San Francisco, California, 312–314, June 1991.

- <sup>6</sup>M. S. Ismail and R. W. Bower, J. Micromech. Microeng. 1, 231 (1991).

<sup>7</sup>A. Yamada, T. Kawasaki, and M. Kawashima, Electron. Lett. 23, 41 (1987).

- <sup>8</sup> M. S. Ismail, R. W. Bower, J. L. Veteran, and O. J. Marsh, Electron. Lett. 26, 1045 (1990).

- <sup>9</sup>C. Harendt, B. Hofflinger, H. G. Graf, and E. Penteker, Sensors and Actuators A 25-27, 87 (1991).

- <sup>10</sup> E. Yablonovitch, D. M. Hwang, T. J. Gmitter, L. T. Florez, and J. P. Harbison, Appl. Phys. Lett. **56**, 2419 (1990).

- <sup>11</sup> E. Yablonovitch, T. Sands, D. M. Hwang, I. Schnitzer, T. J. Gmitter, S. K. Shastry, D. S. Hill, and J. C. C. Fan, Appl. Phys. Lett. **59**, 3159 (1990).

- <sup>12</sup> M. Yasumoto, H. Hayama, and T. Enomoto, Technical Digest in IEEE International Electron Devices Meeting, San Francisco, 816–819, Dec. 1984.

- <sup>13</sup> K. J. Lodge and D. J. Pedder, IEEE Trans. Components Hybrids Manufacturing Technol. 13, 847 (1990).

- <sup>14</sup>R. W. Bower, M. S. Ismail, and B. E. Roberds, Patent Pending, 1993.

- <sup>15</sup>S. Bengtsson, J. Electron. Mater. 21, 841 (1992).

- <sup>16</sup>M. S. Ismail, R. W. Bower, and B. E. Roberds, Technical Digest Solid-State Sensor and Actuator Workshop, Hilton Head, South Carolina, 86–89, June 1992.

- <sup>17</sup> M. Meuris, M. M. Heyns, P. W. Mertens, S. Verhaverbeke, and A. Philipossian, Microcontamination 10, 31-69 (1992).

- <sup>18</sup> X. L. Xu and Q. Y. Tong, Electron. Lett. 25, 394 (1989).

- <sup>19</sup> S. N. Farrens, B. Roberds, M. C. Boettcher, M. S. Ismail, R. W. Bower, C. Desmond, and C. E. Hunt, Presented at Materials Research Society Meeting, Boston, Massachusetts, Dec. 1991.

- <sup>20</sup>R. Stengl, T. Tan, and U. Gosele, Jpn. J. Appl. Phys. 28, 1735 (1989).

- <sup>21</sup> R. W. Lee, R. C. Frank, and D. E. Swets, J. Chem. Phys. 36, 1062 (1962).