|            | the t                            |                             |

|------------|----------------------------------|-----------------------------|

| de         | th t                             | .3                          |

| Guide      | wi                               | s f.6                       |

| e 6        | 91-3                             | Jen                         |

| H          | Si                               | at I                        |

| r Exposure | nior                             | Kodak Anastigmat Lens f.6.3 |

| Ex         | Sei                              | asti                        |

| JOL        | dak                              | Am                          |

| Outdoor    | Ko                               | lak                         |

| On         | the                              | Ko                          |

|            | for the Kodak Senior Six-16 with |                             |

|            |                                  |                             |

| SPERD   | 1/25                                                                                                               | 1/25                                                                      | 1.25                                                                                                                  | 1,25                                                                                       | 1/25                                | 00171                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP    | Zin                                                                                                                | 7116                                                                      | <i>102</i>                                                                                                            | 1.6.3                                                                                      | f.8                                 | 7,623                                                                                                                                                                                       |

| Stateor | Nearby landscapes snowing little<br>or no sky. Nearby subjects in<br>open field, park or garden.<br>Street scenes. | Ordinary landscapes showing sly, with principal object in the foreground. | Murine and beach scenes. Distant landscapes. Snow scenes without prominent dark objects in the foreground. Mountains. | Portraits in the open shade, not under trees or the roof of a porch. Shaded nearby scenes. | Narrow and slightly shaded streets. | Moving objects.  When photographing a moving object such as a runner, train or an automobile, the subject should be moving towards or away from the camera at an angle of about 45 degrees. |

rise until one hour before sunset on days when the sun is shining. If pictures are made earlier of later, or if it is a sightly cloudy or hazy day, use a larger stop opening. This table is for Kodak Verichrome, Super Sensitive Princhromatic and Panatomic Films; if using Kodak N. C. Film, exposures can be made from 25% hours after sunrise until 25% hours before sunset. Exposures are for the hours from one hour after sun-

Kodak Super Sensitive Parchromatic Film is about lifty per cent faster with morning or afternoon light than Kodak Verichrome Film.

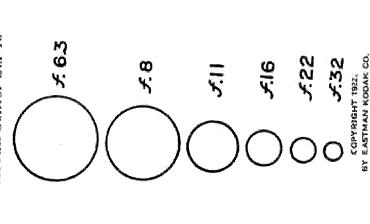

The largest stop opening is f.6.3. The higher the number the smaller the opening.

### SERVICE DEPARTMENT

ADDITIONAL ASSISTANCE FOR MAKING BETTER PICTURES A LTHOUGH we give in this manual the essential directions for using the camera it accompanies, there are amateurs who wish for further knowledge of photography.

The Service Department is at their service, your service.

Do not hesitate to call on us for information on any photographic subject.

We are at your service, write to usthere is no charge, no obligation.

Address all Communications

SERVICE DEPARTMENT

EASTMAN KODAK COMPANY ROCHESTER, N. Y.

Picture taking with the

### Kodak Senior Six-16

Kodak Anastigmat Lens f.6.3

Published by EASTMAN KODAK COMPANY ROCHESTER, N. Y. U. S. A.

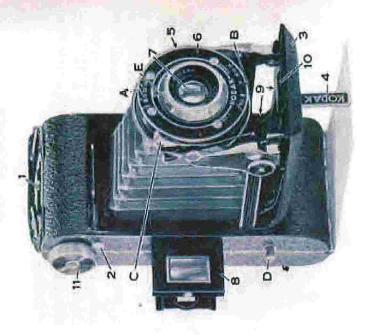

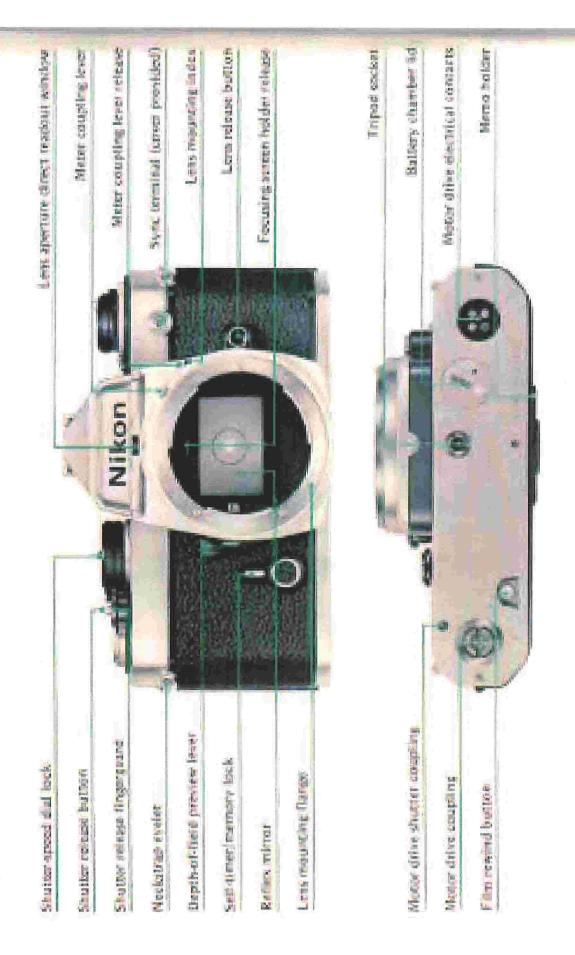

Button for Open-Lock for Back ing Front

Vertical Support Bed

Horizontal Support Shutter 8 + 16 6 14

Release for Clos-Optical Direct Tripod Socket View Finder Serews

ing Front Winding Knob

Stop Opening Lever -Exposure Button Exposure Lever Speed Indicator Focus Pointer

### IMPORTANT

DEFORE loading your Kodak with tures with it, read these instructions how to operate the shutter, see page 9. earefully. Take especial care to learn Ifilm, and before taking any pic-

While loading and unloading, be very careful to keep the protective paper wound tightly around the film can be loaded or unloaded in daylight. to prevent light striking it. The Kodak This should be done in a subdued ight, not in direct sunlight.

### TO LOAD

Use film number:

V 616, SS 616, F 616, or 616 for the Kodak Senior Six-16.

ton of the lock Push the buttowards arrow.

Open the back.

Lift up the spool holder in the recess adjoining the hinge of the back and place the roll of film

in it, springing out the flanges until the pins engage the holes in the spool. Make sure that the word "TOP" on the paper is on the side opposite the winding knob.

Kodak Senior Six-16

Remove the paper band and pass the protective paper over the two rollers. Thread the paper through the longer slit in the empty reel, as far as it will go.

Turn the winding knob once or twice to bind the paper on the reel, and be sure that the paper is started straight.

177

## Pieture taking with the

Close the back, pressing it so that the spring lock snaps into place, securely fastening the back.

Push back the slide that covers the red window on the back of the Kodak. This slide prevents fogging the film.

Turn the winding knob, watching the red window. After a few turns, a warning

After a few turns, a warning hand will appear; then turn slowly until the figure 1 is in the center of the window.

Push the slide over the red window. The window should be uncovered only when winding the film.

The film is now in position for the first exposure. After each exposure wind the film to the next number. This prevents making two pictures on the same section of film.

Nocak Kenier Six-18

## OPENING THE FRONT

Press the button2, page 2, to open the Kodak; then draw down the bed until it locks. This brings the lensand shutter into position.

### To Focus

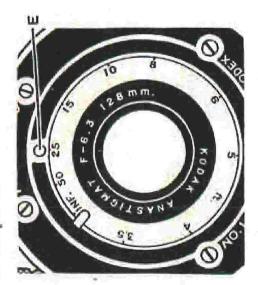

The various distances at which the Kodak may be focused are engraved on the beveled edge of the lens mount.

The scale is marked for 3.5, 4, 5, 6, 8, 10, 15, 25, 50 feet, and INF. (infinity).

To focus the Kodak, revolve the lens mount by turning it to the right or left until the figure representing the distance from the subject to lens is under the pointer E at the top of the lens, see diagram, page 8.

When facing the Kodak, turn the lens mount to the right for distant graduations on the scale, and turn to

the left when focusing on nearby or close subjects.

The distance between the subject and Kodak can be estimated without measuring, when the subject is beyond lifteen feet; for instance, if the focus is set at 25 feet (the usual distance for ordinary street scenes) the sharpest part of the picture will be the objects at that distance from the camera, but everything from about 18 to about 45 feet will be in good focus.

For ordinary street pictures the focus may be kept at 25 feet, but where the principal object is nearer or farther

Kodak Senior Six-16

away, the focus should be changed accordingly.

For dislant views turn the lens mount to INF. (infinity). Nothing nearer than  $3\frac{1}{2}$  feet can be focused without using a Kodak Portrait Attachment, see pages 31 and 32, or a small stop opening, see page 14.

### THE SHUTTER

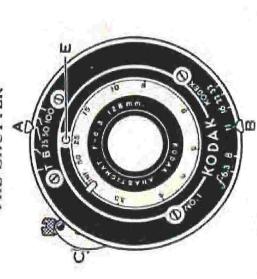

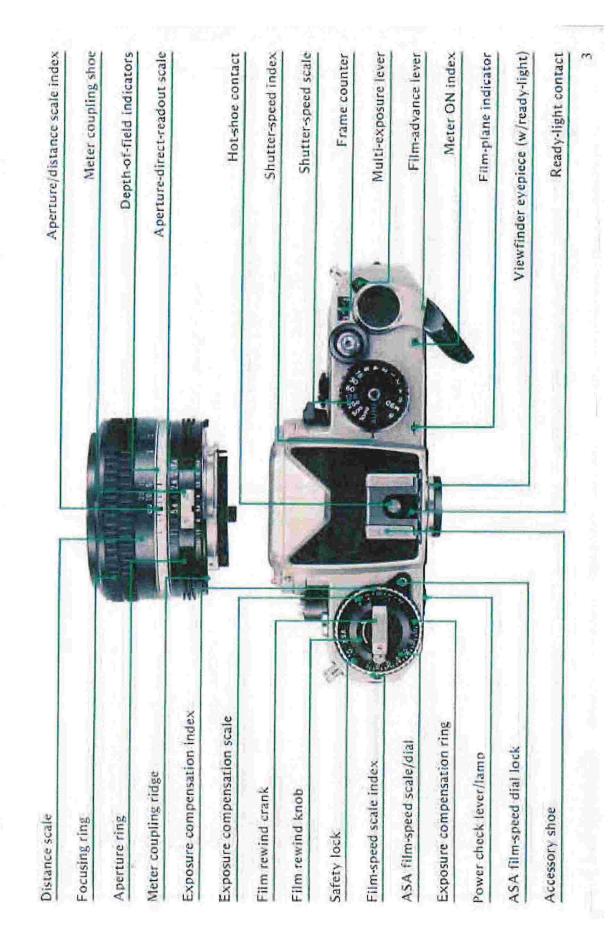

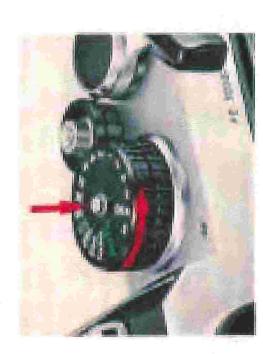

A—Speed Indicator C—Exposure Lever B—Stop Opening Lever E—Focus Pointer

## Instantaneous Exposures

Move indicator A to 25, 50, or 100 (see Exposure Guide on back cover or table on pages 12 and 13).

=

Move lever B to the correct stop opening. See Exposure Guide on back cover or table on pages 12 and 13.

Kodak. This makes the exposure. The the lever C. The use of button D. however, is recommended for snap-Press button D on the side of the exposure can also be made by pressing shots, as it assures a steadier holding of the camera.

## Time Exposures

sure and nature of the subject. See Move lever B to f.6.3, 8, 11, 16, 22, tables on pages 12, 13, 28, 29 and 34. Move indicator A to the letter "T." or 32, according to the time of expo-

Press lever C or button D. This opens the shutter. Time the exposure by a watch. Again press lever C or button D. This closes the shutter.

For short time exposures from oneualf second to ten seconds, "Bulb" Exposures are recommended.

## "Bulb" Exposures

Move indicator A to the letter "B," Move lever B to f.6.3, 8, 11, 16, 22, See tables on pages 12, 13, 28, 29 and 34.

## Kodak Senior Six-10

Press lever C or button D to open the shutter, which will remain open as long as lever C or button D is held

never be made with the Kodak held in Time and "Bulb" Exposures must the hands.

In case of accident, return the camera Important: Never oil the shutter. to your dealer or to us for repairs.

Timer for self-portraiture. The cable if it is desired to use the Kodak Self Cable Release: A cable release (No. 29) can be used with this Kodak release should be removed before closing the camera.

To attach the cable release, remove After using the cable release, detach it the screw directly behind the lever C and replace it with the cable release. and replace the screw in the opening. The screw may be loosened and tightened with a thin coin.

## STOP OPENINGS

amount of light passing through the The stop openings regulate the lens. The openings are enlarged or

reduced by moving the lever B, see page 9.

j.6.3—For rapidly moving objects in bright sunlight, use speed 100. For exposures on cloudy days and during rain in the middle of the day, use speed 25. For portraits outdoors, when the sun is shining, see page 30.

Important: When using stop f.6.3 and the distance between the subject and camera is ten feet or less, the distance must be accurately measured as the depth of focus is limited, see table on page 14.

f.8—For instantaneous exposures on slightly cloudy or hazy days, use speed 25. For scenes on narrow and slightly shaded streets, use speed 25. For moving objects in very bright sunlight, use speed 100.

f.11—For all ordinary outdoor pictures, such as nearby landscapes showing little or no sky, groups and street scenes, when the subject is in bright sunlight, use speed 25.

f.16—For open views, when the sunlight on the subject is unusually strong and there are no heavy shadows, such

Nodak Senior Six-16

as views at the seashore and on the water, use speed 50; for ordinary landscapes, in bright sunlight, with clear sky overhead, use speed 25; also for Interior Time Exposures, the time for which is given in the table on page 28.

of extremely distant landscapes, marines, snow scenes without prominent dark objects in the foreground, and clouds only, in bright sunlight, use speed 25; also for Time Exposures.

f.32—For Time Exposures Outdoors on cloudy days, see table on page 34. For Interior Time Exposures, see pages 28 and 29. Never for instantaneous exposures.

Failure will result, if stop f.32 is used for instantaneous exposures.

The smaller the stop opening the greater the depth of focus or range of sharpness, see pages 14 and 15.

1

All exposures given for outdoor subjects are for the hours from one hour after sunrise until one hour before sunset, when using Kodak Verichrome, Super Sensitive Panchromatic or Panatomic Film. If Kodak N. C. Film is

2 L 2 L Kodak Senier Six-16

used, exposures can be made from  $21_2$

hours after sunrise until 2½ hours be-

fore sunset. If earlier or later, the ex-

oosures must be longer.

For a subject in the shade, under

time exposure must be made, see page 34. When making pictures under these

conditions, the camera must be placed

on some steady, firm support

the roof of a porch, or under a tree, a

### 1

### The Depth of Focus for Different Stop Openings

By "depth of focus" is meant the distance, in front of and behind the subject focused on, within which details in the picture will be sharp and distinct.

Table for use with the Kodak Senior Six-16

| Ste gin, we dit, the                          | 31 6 01 70 1 11 11 11            | geram toger ham                                                             | ા કેદળ માદ ગાદ                 | 30 8 3) C 61 3) {E                                                   | [**] FR                          | ago - : |

|-----------------------------------------------|----------------------------------|-----------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|----------------------------------|---------|

| alt noble on                                  | 4 (4, 2 in, to 0 (4, 2 in,       | gir im to ite hin                                                           | 11 (5 or an 5 at k             | menjeanje<br>vicojeanje                                              | 117<br>119                       |         |

| 1) (1 to 31) (1<br>2) (1 to 31) (1            | 7) 8 21 7) 2<br>1) 12 (7) 13 (1) | 21 C 0 U 2 C                                                                |                                | 73 (c. to. 91 (c. 5) (c. 5) (c. 5)                                   | 1) 9<br>1) 9                     |         |

| 71 159 01 31 15<br>74 01 31 30<br>76 01 31 45 | 1)                               | 11 107 02 J1 101<br>11 105 02 J1 101<br>11 105 03 J1 101<br>11 105 03 J1 10 | 11 14 to 12 10 to 13 10 to 1   | "1) [6] (01 '1) [8<br>  "3) [6] (01 '1) [8]<br>  "1) [6] (01 '1) [8] | 10 LF<br>12 LF<br>32 LF          |         |

| jai or aj fol<br>13. te miot                  | ीता था है।<br>जुला था जुला       | ुंगा ला ना सिंह<br>अस्र ता का जा                                            | 101 of 11 155<br>101 of 11 155 | do it, to int.<br>284 it, to int.                                    | PO IT                            | - P     |

|                                               |                                  | 115                                                                         | wy.                            | E07                                                                  | Sometary<br>Descending<br>Toog 7 |         |

anosinequico y de boteminso de mas granego sida tol depte dell' 1883, tol mayin non si succil de dippe dell' anol odi morti osmeloje botimilian magnimesor—vitadati tol molinivorden odi si "Inl".

stool volt mort evarable bothmillon on gondewn—vitadul tot doitsiverdda edd si "Aal"

## DEPTH OF FOCUS

Depth of focus is the distance from the nearest to the farthest objects that will appear sharp in the negative or print. It depends upon the distance between the subject and lens, the focal length of the lens, and the size of the stop opening used. The smaller the stop opening, the greater the depth of focus. See the table on page 14.

## THE "f," SYSTEM

A lens is said to work at a certain "speed;" this means that the lens will give a sharp image from corner to corner of the film with an opening a certain proportion of its focal length.

1.0

Picture taking with the

the size of the opening in proportion to upon the size of the opening, but upon when the Kodak is focused for INF. (infinity). It should be borne clearly the foral length of the lens. The lens that will give sharp images with the argest opening is said to have the The focal length of a lens is the disance between the lens and the film n mind that this "speed" depends not greatest "speed."

of the stop opening is designated by the "f." number and is the quotient The proportional size or "value" obtained by dividing the focal length of the lens by the diameter of the Hop opening.

### How to Use Your Kodak as a Fixed Focus Camera

SET THE FOCUS AT 25 PERT. USE STOP OPENING f.16, AND SPEED 25.

fueus type, nearby subjects must be in bright sunlight, to obtain fully When using the Kodak as a fixed exposed negatives.

Kodak Seniar Six-1:

The runge of sharpness when your Kodak is adjusted as a fixed focus camera will be found on page 14.

Kodak Senior Six-16

These circles are the same size as the stop openings of the shutter on the Kodak Senior Six-16. They clearly show the relative sizes of the stop openings and how their areas differ.

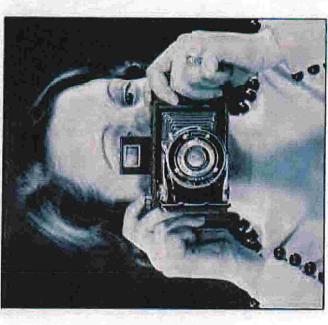

## Making a Horizontal Picture

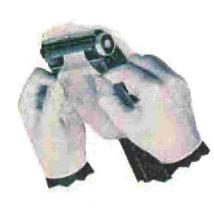

Hold camera firmly against the face.

When making instantaneous exposures or snapshots, hold the Kodak firmly against your face and press the exposure button as shown in these two illustrations. When pressing the exposure button, hold the breath for the instant. If the Kodak is moved during the exposure, the picture will be blurred.

Kodak Senior Six-16

## Making a Vertical Picture

Hold camera firmly against the face.

## THE OPTICAL DIRECT VIEW FINDER

The camera is equipped with an optical direct view finder 8, page 2, attached to the side of the Kodak. To use this finder, raise the front frame by the button and both parts of the finder will spring into position. Hold the camera with the sight or rear frame

O.

## Picture taking with the

as close to the eye as possible with the camera held firmly against the face, and frame the picture within the front frame of the finder. All vertical lines in the subject should be kept parallel with the vertical sides of this frame, when holding the camera either in the vertical or horizontal position.

## MAKING INSTANTANEOUS EXPO-SURES OR SNAPSHOTS

When ordinary instantaneous exposures or snapshots are made, the subject should be in the broad, open sunlight, but the camera must not. The sun should be behind your back or over the shoulder. If it shines directly into the lens, it will blur and fog the picture. For obtaining back- or side-lighted pictures, use a Kodak Adjustable Lens Hood No. 2.

Special instructions for making portraits are given on pages 29 to 33.

## HOLD THE KODAK LEVEL

The Kodak must be held level. If all the subject cannot be included in the finder without tilting the lens

## Kodak Senior Six-16

upwards, move backwards until it is all included with the camera held level.

Effect produced by tilling the Kodale.

If the subject is below the normal height, like a small child or a dog, the Kodak should be held down level with the center of the subject.

After an exposure has been made, turn the winding knob slowly, a few times, until No. 2 (or the next number) is in the center of the red window.

ě

## CLOSING THE KODAK

Before closing the Kodak, it should be focused for INF. (infinity); then press the plate release 10, page 2, as shown below, raise the bed and snap

it shut. The front and bellows fold automatically. If a cable release has been used, remove it before closing the camera.

## REMOVING THE FILM

After the last section of film has been exposed, turn the winding knob until the end of the paper passes the red window.

In a subdued light, open the back of the Kodak, see pages 3 and 4.

Hold the end of the paper taut, see illustration at top of page 23, and turn the knob until all the paper is on the

Kodak Senior Six-16

roll. If the sticker folds under the roll, turn the knob to bring it up.

Take hold of the ends of the paper and sticker to prevent the paper from loosening. Draw out the knob and re-

move the film. Fold under about halfan-inch of the protective paper, and fasten it with the sticker.

500

"Cinch" Marks: After removing the film from the Kodak, do not wind it tightly with a twisting motion, or the film might be scratched. Wrap up the exposed film. It is now ready for development. This may be done by a photo finisher, or by yourself. Our Service Department will be glad to send you, upon request, complete instructions for developing and printing.

Remove the empty spool and place it in the winding end of the camera. The Kodak is now ready for reloading.

## Kodak Senior Six-16

It is a good plan to reload the Kodak as soon as an exposed film has been removed, to be ready for the next pictures. For the best results, load with Kodak Film.

Important: Film should be developed as soon as possible after exposure. The quality of the image on all sensitized products is retained by prompt development after exposure.

## TIME EXPOSURES-INDOORS

For time exposures the camera must always be placed on a firm support like a tripod, Optipod, table or chair, never hold it in the hands. The Kodak has two tripod sockets for use with a tripod, an Optipod, or a Kodapod, with the Kodak either in the vertical or horizontal position. The screws in the

ÇĮ ÇJ

tripod sockets can be removed and replaced with a thin coin. Place the Kodak in such a position that the finder will include the view desired. The diagram on page 25 shows three positions for the camera. It should not be pointed at a window as the glare of light may blur the picture.

for making a vertical picture, use the If the Kodak is placed on a table, vertical support 4.

The camera must not be more than two or three inches from the edge of the table.

behind the shutter, and place the out a tripod, swing out the support 5, camera as shown below.

Adjust the shutter for a time exposure as described on page 10.

All being ready, press the exposure again press the exposure button or ime the exposure by a watch, and button or lever carefully, once to open, ever to close the shutter.

After making an exposure, turn the winding knob until the next number appears in the red window.

If no more time exposures are to be made, adjust the shutter for an instananeous exposure, see page 9.

Kodak Senior Six-16

Вхростве Тавье гон Гатевіова изіма Зточ Л.16

| , soim č<br>20 secs, | snins.             | 1 min.<br>20 sees. | to sees. | Dark colored walls and furnishings and only one window.             |

|----------------------|--------------------|--------------------|----------|---------------------------------------------------------------------|

| 2 mins.<br>40 sees.  | .nim 1<br>.soss 02 | 40 secs.           | Soos 07  | Dark colored walls and furnishings<br>and more than one window.     |

| suim £               | .nim I             | 30 secs.           | 12 secs. | Medium colored walls and furnish-<br>ings and only one window.      |

| .mim 1<br>.eoes 02   | 40 sees.           | .eoos 02           | S secs.  | Medium colored walls and furnish-<br>ings and more than one window. |

| .nim 1               | 30 zeca.           | 16 sees,           | esecs.   | White walls and only one window.                                    |

| 40 sees.             | 20 secs.           | TO secs.           | 4 secs.  | White walls and more than one win-<br>dow.                          |

| Cloudy<br>full       | Cloudy             | me yzeH            | unesdahu | ,                                                                   |

If earlier or later the exposures must be longer, sky and for hours from three hours after sunrise until three hours before sun-These exposures are for rooms where windows get the direct light from the

The table on page 28 gives suitable exposures for varying conditions of Exposure Table for Interiors light, when using stop f.16.

one-quarter;

one-half; twice;

With stop f.6.3 give one-sixth;

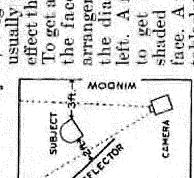

TO MAKE A PORTRAIT

The smaller the stop opening the

the exposures given in the table.

four times

sharpness, see page 14. Stop f.16 gives

the best average results for Interiors.

greater the depth of focus or range of

feet from the subject; and for a The subject should be seated in a chair partly facing the light with the The subject should look at an object level with the lens or directly at the lens. Compose the picture in the finder. For a three-quarter figurer the Kodak should be about ull-length figure, about ten feet. The background should form a contrast body furned slightly away from, and he face turned towards the Kodak which should be a little higher than an ordinary table;

8

BlackBerry Corporation Exhibit 1018, pg. 1226

usually gives a better effect than a dark one.

To get a good light on the face, follow the arrangement shown in the diagram at the left. A reflector helps to get detail in the shaded part of the face. A white towel or tablectoth held by an

tablecloth held by an assistant or thrown over a screen or other high piece of furniture will make a suitable reflector; it should be at an angle and in the position indicated.

If the above suggestion for lighting is followed, an exposure of about one second with stop f.11 will be sufficient on a bright day.

## Making Portraits Outdoors

When making portraits outdoors, with the sun shining brightly, the subject should be in the shadow of a building or a large tree, but with clear and unobstructed sky overhead—use stop f.6.3 and speed 25. By following this

## Kodak Senior Six-16

rule, unpleasant and distorting shadows on the face will be avoided. The best results are obtained with the subject fairly close to the camera and the lens adjusted accordingly. When the distance between the subject and Kodak is ten feet or less, measure the distance carefully, see table on page 14.

## Kodak Portrait Attachment

This Kodak can be focused at 3½ feet, which makes it possible to obtain excellent head and shoulder portraits without the use of the Kodak Portrait Attachment.

By using the Kodak Portrait Attachment, large images of flowers and similar "still life" subjects can be obtained. For the best results when making pictures of subjects at short distances, it is advisable to use the f.8 or a smaller stop opening.

Place the Attachment over the lens and compose the picture in the finder. When making vertical pictures, turn the Kodak just a little to the right, as the short distances at which the subject must be from the lens make it

100

## Picture taking with the

necessary to center the subject by eye instead of by the finder.

| THE FOCUSING<br>COLLAR MUST BE    | 3½ feet          | <u></u> | .23    | 77  | -1  | a   | (2) | 13 | -2  | (infinity) |

|-----------------------------------|------------------|---------|--------|-----|-----|-----|-----|----|-----|------------|

| E F                               | 85               | খ       | 10     | 4   | 30  | 10  | 15  | 25 | 200 | INE.       |

| TH TOU                            |                  | 3       | ÷      |     |     | 11  | 1   | 7  | - 6 | K          |

|                                   | 4                |         | 10-    | - 1 |     | - 2 | 4   | 10 |     | 4          |

|                                   | . 4              |         | 4      | 1   |     | - 7 | - 4 |    |     |            |

|                                   | - 1              | 7       | X      |     |     | - 1 | 1.0 |    |     | *          |

| to the                            |                  | - 1     |        |     | ů   | - 2 | - 5 |    |     |            |

| 63 7                              |                  | - 1     |        |     |     | - 6 | - 1 |    |     |            |

| DISTANCE BETWEEN SUBJECT AND LENS | I foot 11 inches | inch    | inches | 3   | 3   |     | 1   | a. |     | 4          |

| NCE BET                           | 1                | -       | 100    | 4   | 0   |     | +   | 00 |     | CI         |

| JECT                              | foot             | feet    | feet   | #   | 3   | ış. | 1   | 12 | 1   | 3          |

| 22 (2)                            | -                | CA.     | 601    | CM. | OI. | 99  | 00  | 99 | +   | +          |

| Ata                               |                  |         |        |     |     |     |     |    |     |            |

The subject must be at one of the distances from the Kodak, given in the table above. Measure the distance carefully from the lens to the subject, and revolve the lens mount until the correct figure is at the pointer E (page 8) according to the table.

The same exposure is required as without the Attachment.

Use Kodak Portrail Attachment No. 5, with the Kodak Senior Six-16, with the Kodak Anastigmat Lens f.6.3.

Kodak Senior Six-16

### Kodak Diffusion Portrait Attachment

The Kodak Diffusion Portrait Attachment is a supplementary lens used in the same manner as the regular Kodak Portrait Attachment. It produces a true, soft-focus effect.

Use Kodak Diffusion Portrait Attachment No. 5, with the Kodak Senior Six-16, with the Kodak Anastigmut Lens f.6.3.

"AT HOME WITH YOUR KODAK" is a booklet containing many diagrams and illustrations showing various lighting effects. It gives suggestions for making pictures in and around the home.

"PICTURE TAKING AT NIGHT" is a booklet that describes in detail the methods of making pictures by electric light, flush-light exposures, campfire scenes, fireworks, lightning, moonlight effects, silhouettes and other novel and unusual pictures.

These two booklets are free, and copies of them will be sent upon request to our Service Department.

30

## TIME EXPOSURES-OUTDOORS

When the smallest stop opening (f.32) is used, the light passing through the lens is so much reduced that very short time exposures may be made outdoors.

For short time exposures described below, use the "Bulb" Exposure, see page 10. With Light Clouds—From one to three seconds will be sufficient.

With Heavy Clouds—Four seconds to eight seconds will be required.

With Sunshine—Time Exposures

should not be made.

When making time exposures the Kodak must be placed on some steady, firm support, do not hold it in the hands or the picture will be blurred.

### CLEAN LENSES

Made with Dirty Lens. Made with Clean Lens.

Kodak Senior Six-16

The pictures on page 34 illustrate the difference between results with a dirty and a clean lens.

Lenses should be cleaned as follows:

Open the back of the Kodak, see pages 3 and 4; then open the front as described on page 7. Wipe the front and back of the lens with Lens Cleaning Paper or a clean handkerchief. Never unscrew the lens.

## Keep Dust Out of the Camera

Wipe the inside of the camera and bellows, occasionally, with a slightly damp cloth, especially if the camera has not been used for some time.

## EASTMAN KODAK COMPANY, ROCHESTER, N. Y.

語

### PRICE LIST

|                                                                          | Se Se             |                                                                     | <del>9</del>                                 | 010                   | 왕            | 27:                                                              |                            | 1.50          | 1.50                      |                                 |                                         |                                   | 2.75                      |        | 5.00 | 1 95                                 |                                    | 1.75                                  | 500        |                                    |            | 1.23                              | 1.25                             |                                              | NY,                    |

|--------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------|----------------------------------------------|-----------------------|--------------|------------------------------------------------------------------|----------------------------|---------------|---------------------------|---------------------------------|-----------------------------------------|-----------------------------------|---------------------------|--------|------|--------------------------------------|------------------------------------|---------------------------------------|------------|------------------------------------|------------|-----------------------------------|----------------------------------|----------------------------------------------|------------------------|

| KODAK VERICHROME FILM, V 616, for<br>the Kodak Senior Six-16, 215 x 414. | eight exposures   | DAAK SUPER SENSITIVE FANCHRO-<br>MATIC FILM, SS 616, 2½ x 4¼, eight | exposures. Koda F Panaromic Film F 616, 2% x | 414, eight exposures. |              | KODAR PORTRAIT ATTACHMENT, No. 5,<br>for the Kodak Senior Six-16 | DIFFUSION PORTRAIT ATTACH- | Annual Contra |                           | KODAR PICTORIAL DIPPUSION DISK, | 1 1 2 2 2 2 2 2 3 3 3 3 3 3 3 3 3 3 3 3 | KODAK ADJUSTABLE LENE HOOD, NO. 2 | 0                         |        |      | Oprinop, for attaching camera to the | Koparop, for attaching camera to a | tree, fence or similar rough surface. | and around | KODAK SELF TMER, fits on the cable | otographer | Konas Negarity: Album to hold 100 | ives                             | All prices subject to change without notice. | EASTMAN KODAK COMPANY, |

| ME FILM,<br>for Six-16,                                                  | 0.0 4 6 0 7 9 7 7 | 616, 235 x                                                          | C FILM. F                                    | aures                 | The House to | ATTACHME<br>Senior Six-                                          | N PORTRAI                  |               | KODAK COLOR FILTER, NO. 5 | L DIFFUS                        |                                         | LE LENB H                         | KODAK METAL TRIPOD, NO. 0 |        |      | ching cam                            | taching ca                         | nilar rough                           |            | ER, fits on                        | ing the ph | n the picti                       | 21/2 x 41/4 or smaller negatives | ect to change                                | N KODAL                |

| VERICHRO                                                                 | exposures         | FILM, SS                                                            | PANATOM                                      | ight expo             | exposures    | PORTRAIT<br>e Kodak S                                            | DIFFUSIO                   | No. 5         | COLOR FIN                 | PICTORIA                        |                                         | ADJUSTAB                          | METAL TI                  |        |      | for table                            | D. for att                         | ence or sin                           | Six-16     | SELF TIM                           | pin, enabl | NEGATIVE                          | 414 or sm                        | I prices subh                                | CASTMA                 |

| Kopak<br>the K                                                           | eight             | MODAK                                                               | Konak                                        | 4½, e                 | eight        | Kobak<br>for th                                                  | KODAK                      | MENT,         | KODAK                     | KODAK                           | No. 5                                   | KODAK.                            | Kopak                     | No. 1. | 100  | OPTITOD                              | Koparo                             | tree, f                               | Senior     | KODAK                              | f-qsnd     | Konsk                             | 21/2 x                           | F.                                           | I                      |

### IMPORTANT

This manual should be read thoroughly, before you make any pictures.

While loading and unloading the camera, be very careful to keep the protective paper wound tightly around the film to prevent light striking it.

Before making an exposure be sure that the shutter is adjusted properly, for an instantaneous or time exposure, whichever is required. Use the correct stop opening and speed. The camera must be focused and ununexposed section of film in position.

The sun must be behind your back or over the shoulder. If the sun shines directly into the lens it will blur and fog the picture.

Hold the camera level.

Hold the camera steady when making instantaneous exposures or snapshots. The camera should be held firmly against the face, and when pressing the exposure button or lever, hold the breath for the instant. If the camera is moved during the exposure, the picture will be blurred.

Turn a now section of film into position immediately after making an exposure. This prevents making two pictures on the same section of film.

Keep the lens and inside of camera clean. Never oil the shutter.

Instructions for making time exposures, indoors and outdoors, are included in this manual.

EASTMAN KODAK COMPANY, ROCHESTER, N. Y.

PRINTED IN U.S.A.

36

BlackBerry Corporation Exhibit 1018, pg. 1231

## NOMENCLATURE

BlackBerry Corporation Exhibit 1018, pg. 1232

BlackBerry Corporation Exhibit 1018, pg. 1233

### ONTENTS

| Exposure measurement, Automatic shurter spend selection Manual shurter speed selection.  Exposure control.  Metering tange.  High-contrast fighting altegrans. | Stop-diswer expisiure measurements  Exposure compensation adjustments  EV range of the currents  Multiple exposures,  Flash synchronization  Result these | Figs on careers care Mounting and removing lenses  Changing fraucing screens  Focusing street scientor gaide  Lens/screen compatibility chart  Accessining |                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Forward.  Preparation for use Installing the Galleries Checking battery power Leading for.  Prior to shooting.                                                 | Setting the film speed.  Metro holder  Charallon of camera contract.  Setting the thatter speed.  Film advance lever.                                     | Schl-time Memory, lock Unlanding the consets Shatter release operation (formation with cottle preferen                                                     | Focusing Infrared photography Furn plane Indicator. Depth of Palst. Depth of Palst. Depth of Palst. |

## FOREWORD

camera with a host of outstanding features. It offers aperture-priority automatic exposure control with shutter speeds from 1/1000 second down to 8 seconds, has flash speed setting when used in conjunction with the The Nikon FE is a compact 35mm single-lons reflex al MD-12 for motor-driven exposures up to 3.5 frames per second. In addition, the FE incorporates automatic rccessory Speedlight Unit 58-10, When the 58-10 is interchangeable focusing screens, and accepts the optionmounted on the camera's hot shoe and turned on, the whurter speed is automatically set to the proper synchronization speed of 1/90 second when the camera is set to accessory in the Nikon System—the most comprehensive fully, and practice using the controls before loading the his camera, study the instructions in this manual careminutes you spend familiarizing yourself with the "automatic," The FE will also accept virtually every ever created for photography. To get the most out of camera with film. Keep the manual on hand for ready reference until you have mistered operation. The few camera will guarantee you the best results and increase nour pleasure in taking pictures many times over.

# OPERATION OF CAMERA CONTROLS

## Setting the Shutter Speed

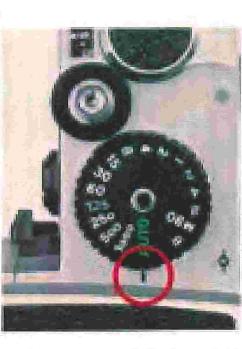

The Milkon FE is set for automatic or manual shatter speed dial positioned to the right of the finder, with vetting operation possible at any time tither before or after the shutter is wound. The dial is provided with positions for automatic [AUTO], and manual speeds from a seconds to 1/1/000 settend. To set the dial for automatic shutter speed selection, simply rotate the dial clockwise until the green AUTO (automatic) settler speed selection, simply the shutter-speed selection the base of the dial; the built-in backing mechanism ensures that the dial; the built-in backing mechanism ensures that the dial; the built-in backing mechanism ensures that the dial carrent he action the state of the dial; the shotten

To see the dist for manual shutter speed selection used during "match-reedle" exposure measurement, simply hold in the shutter-speed ded lock and rotate the distance in the shutter-speed ded lock and rotate the distance of the "AUTO" position, when the distance with white entires from 2 to 1000, the securily shutter speed is a fractional value from 1/2 securilities to 11000 second, while the remaining settings indicate the security indicates a mechanical shutter speed of 1/90 second which operates independently of butter speed of 1/90 second which operates independently of butter speed of 1/90 second the only setting lexicips. B") which can be used when

the batteries are exhausted or none are loaded in the camera. The "M90" setting also serves as a known shutter speed when shooting with electronic flash. At the "B" setting, the shutter remains open as long as the shutter release button is depressed. "B" is also a mechanical shutter speed, so there is no battery drain when shooting time exposures. To conserve battery power when making really long time exposures, use a cable release and then push the film-advance lever back in flush with the camera bady after opening the shutter. Note that the 125 setting is engraved in red, this indicates \$1/125 second, the fattest shutter speed available for synchronization with electronic flash units. (Refer to page 37 for additional information on flash photography...)

### APPENDIX BBB

BlackBerry Corporation Exhibit 1018, pg. 1238

### The Development of Digital Still Camera using I.3M-Pixel VT-CCD Image Sensor

Kazuya Oda Tiaki Ichikawa Ryuji Kawaguchi Izumi Miyake Kazuki Iwabe

Fuji Photo Film Co., Ltd. Engineering & Designing Dept. Electronic Imaging Products Div. Fuji Photo Film Co., Ltd. Products Planning & Development Dept. Electronic Imaging Products Div.

### Abstract:

We have developed a 2/3-inch 1.3M-pixel full-frame readout VT-CCD (Vacancy Transfer CCD) image sensor for digital still cameras. We have also completed a portable SLR-type digital still camera using this CCD image sensor. We can obtain as much image quality and resolution as in conventional photoprint.

### 1. Introduction

In recent years, digital cameras have gained attention as image-data input devices in the fields of commercial photography, news reporting, medicine and printing along with the advent of the age of multimedia that comprehensively handles still images, videos, audio and character information, along with the higher functionality of personal computers and networks. So to support this multimedia generation, the singlelens reflex (SLR) type digital camera DS-505/515 was developed.

The concept of the DS-505/515 was to place importance on high quality and behavior and operability by which it can be used with the same feeling as a conventional single-lens reflex type camera.

For that reason, the DS-505/515 was developed as a new image sensor (VT-CCD) that simultaneously reads all 1.3 million pixels in a 2/3 inch size as a dedicated still image to attain image quality that can be compared to LS size prints that require high-image quality2). The following is an overview of the digital camera DS-505/515 system, and a

report on the main engineering and imaging elements.

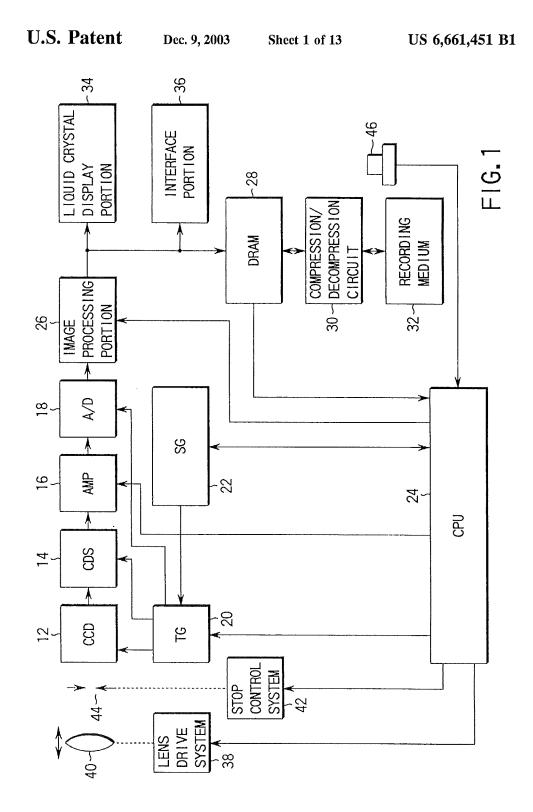

Fig. 1 DS-505/515, HG-15

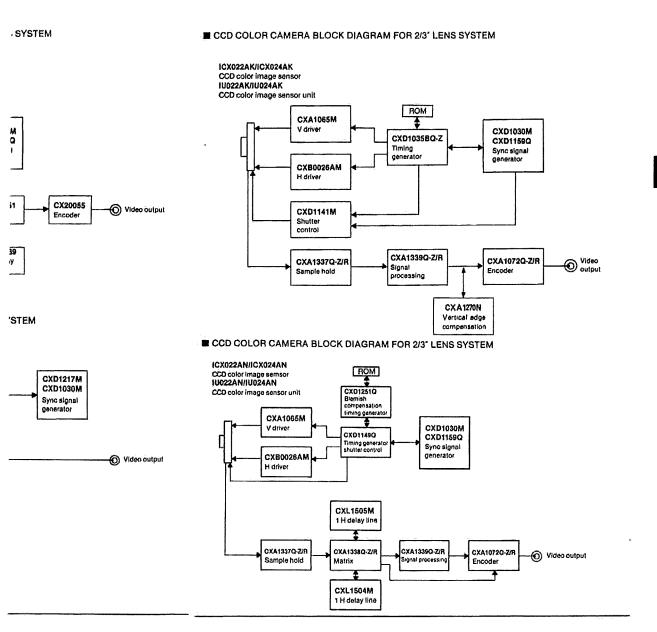

### 2. DS-505 System Configuration

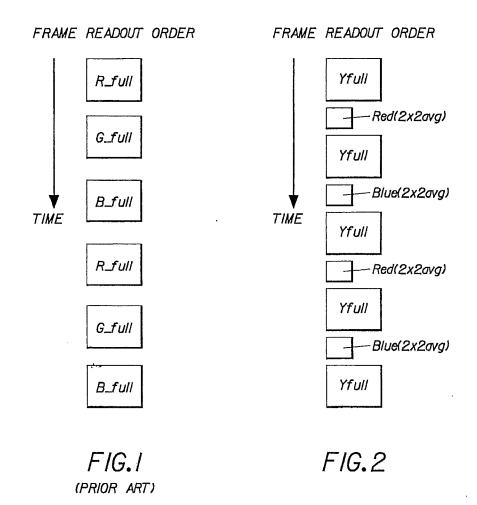

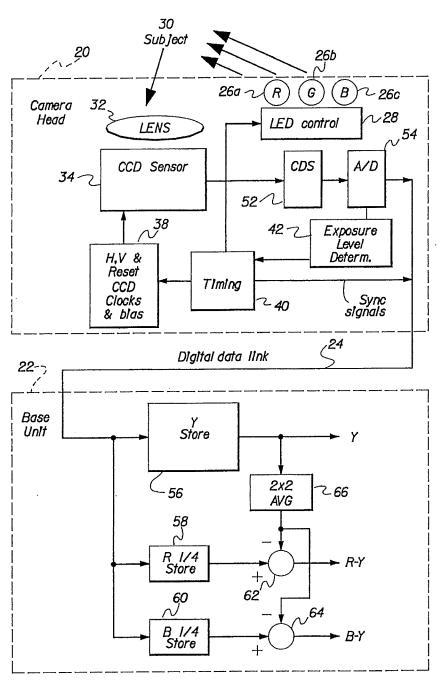

The DS-505 is a single-shot model and the DS-515 is continuous shooting model. (DS-515 is capable of continuous shooting at 3 frames/second.) The following is a description using DS-505 as an example.

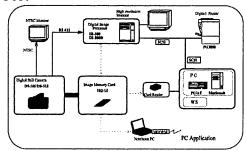

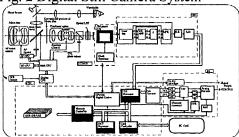

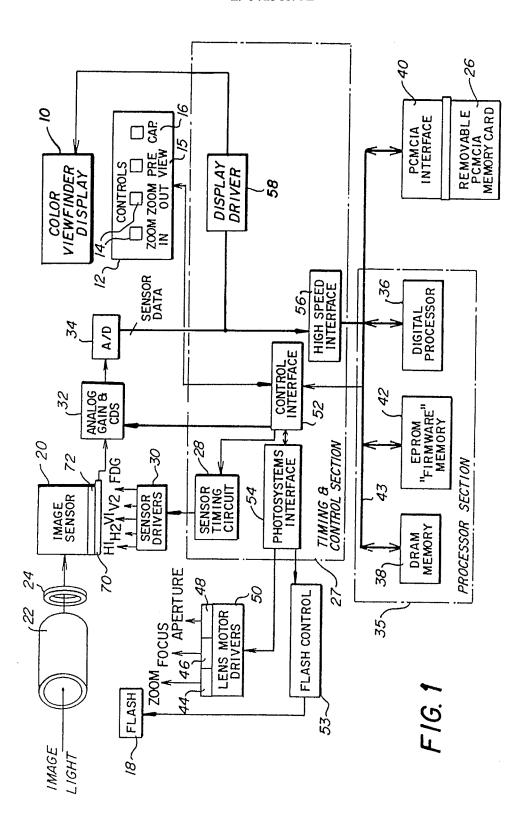

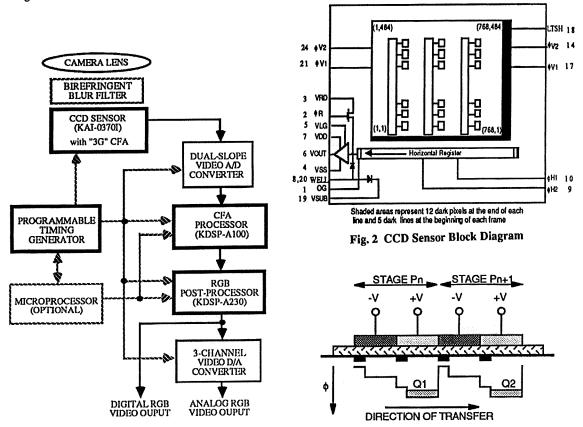

Fig. 2 shows the overall configuration of the camera system. Image data is interfaced with a personal computer using a PC card, MO device, and SCSI, as shown in the drawing.

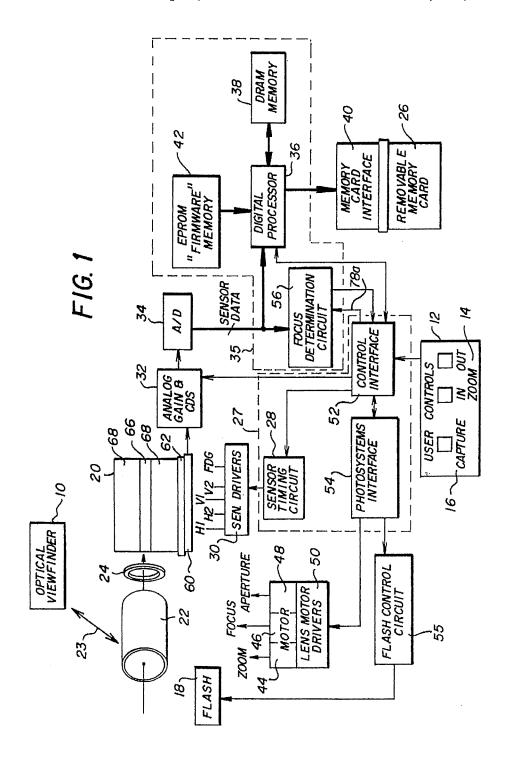

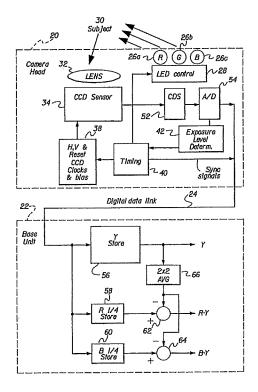

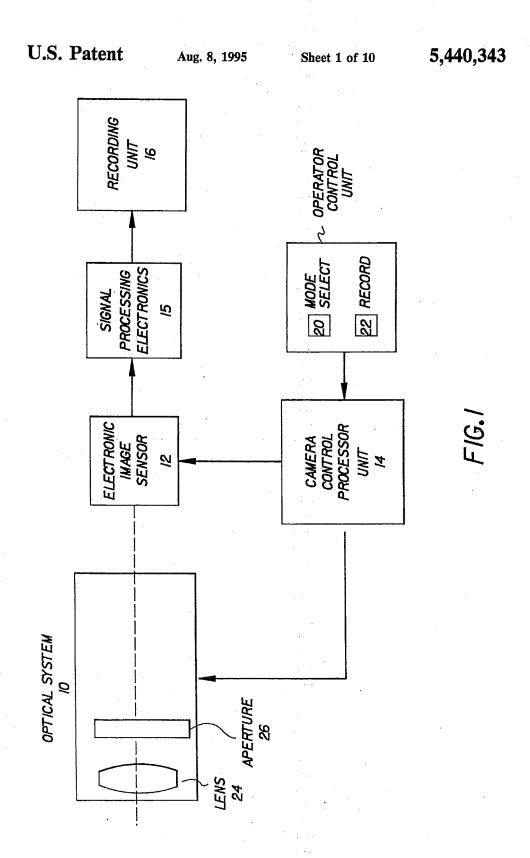

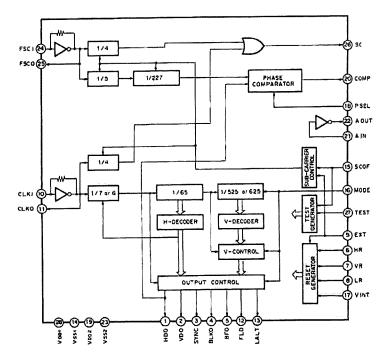

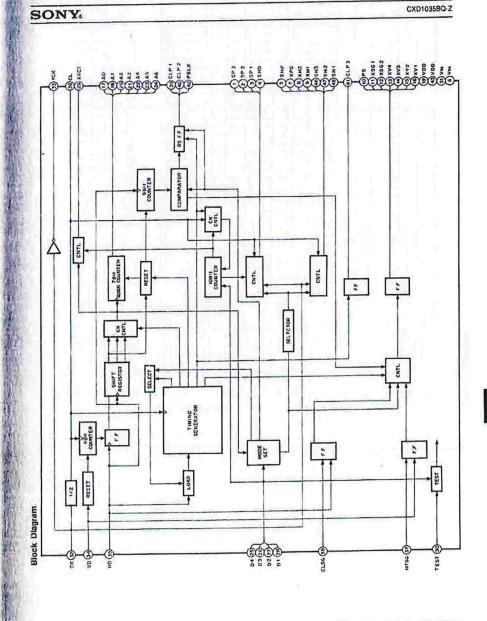

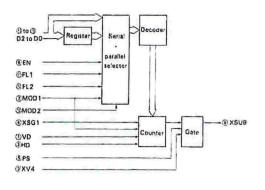

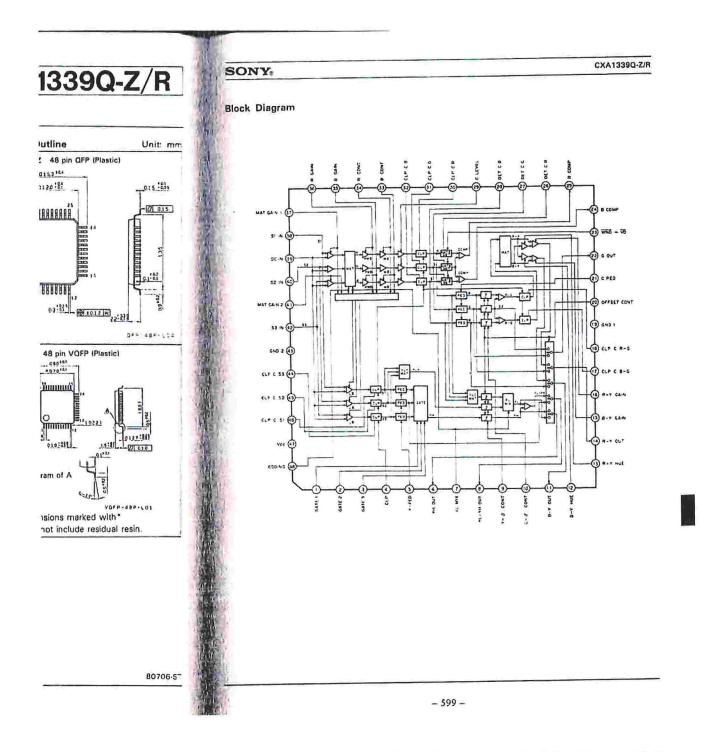

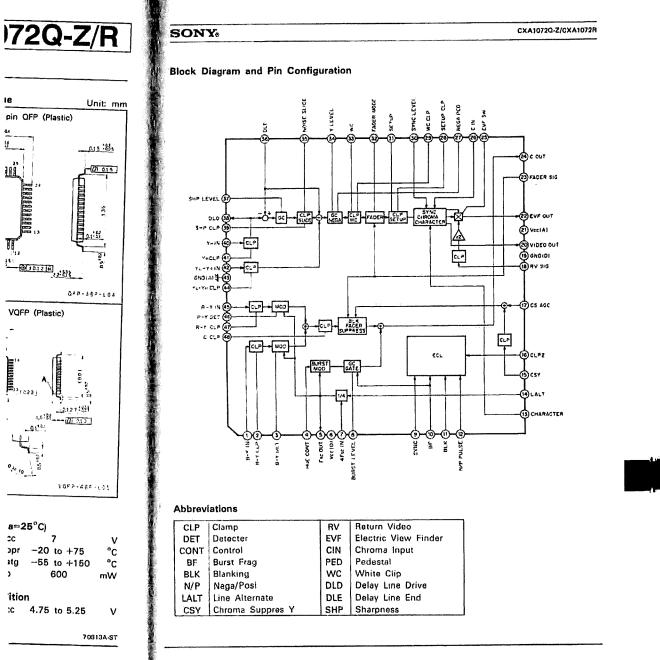

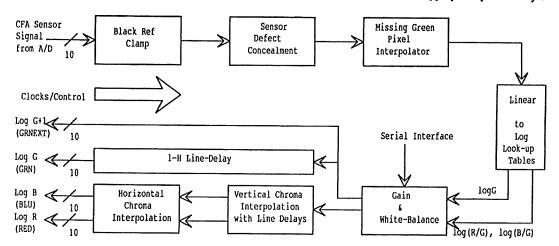

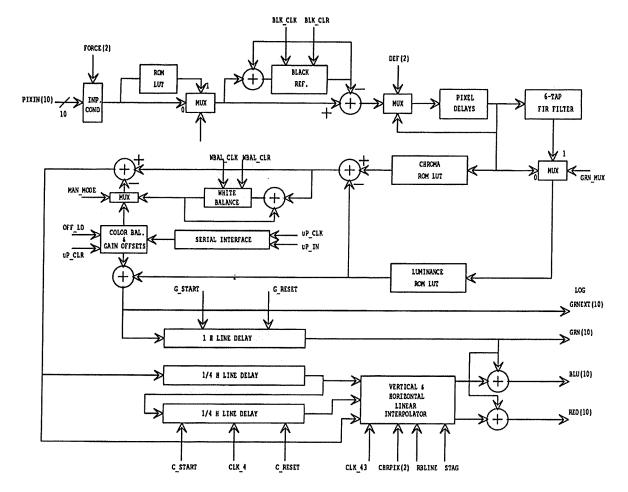

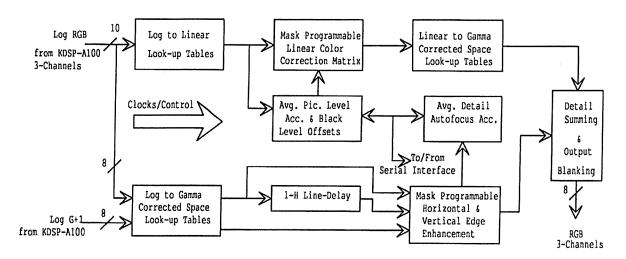

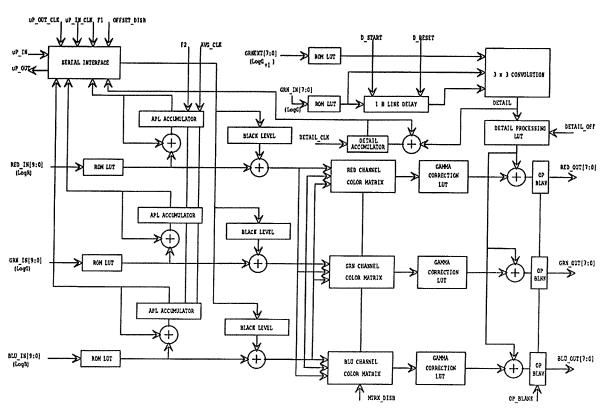

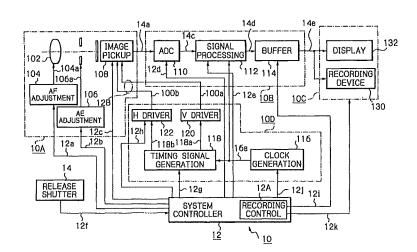

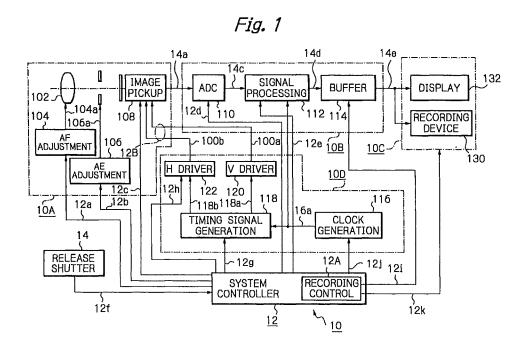

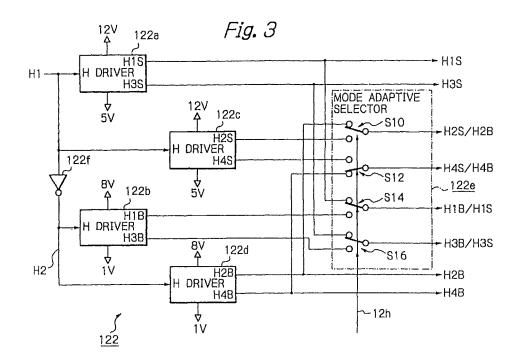

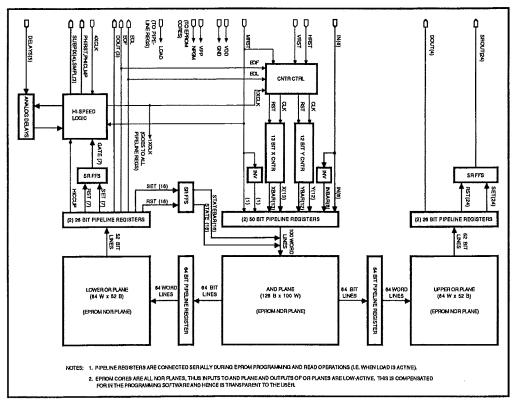

Fig. 3 is a block diagram of internal signal processes in the digital camera DS-505.

Fig. 2 Digital Still Camera System

Fig. 3 Block Diagram of DS-505

3. Main Specifications (Features)

Table 1 shows the main specifications of the DS-505.

The following will describe the features of this digital still camera.

1) Attains high-image quality and high-resolution by mounting a I.3M-Pixel VT-CCD

- 2) Used with the same feel as a singlelens reflex (SLR) camera. (Adopts an optical reduction system, replacement lens, and others)

- 3) More compact because of the development of a signal-processing LSI.

- 4) Adopts a PC card (HG-15, 15 MB) that records at high speed.

- 4) VT-CCD

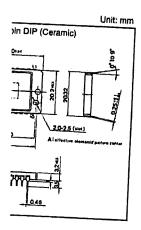

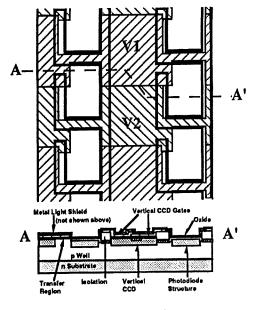

### 4-1) CCD Device

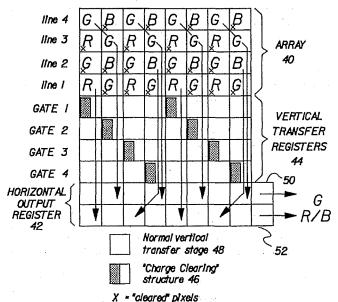

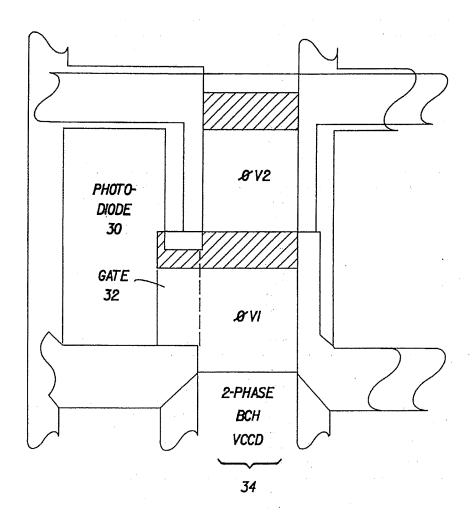

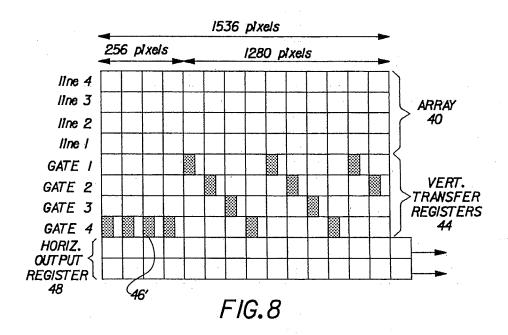

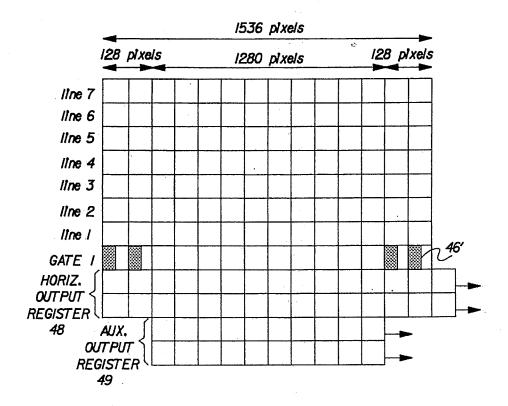

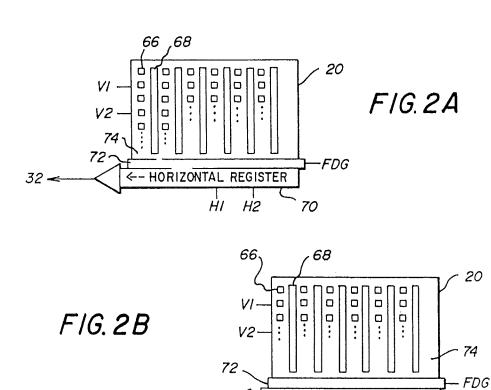

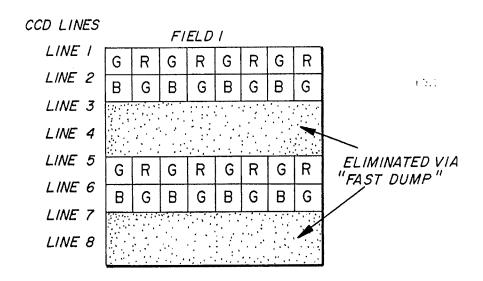

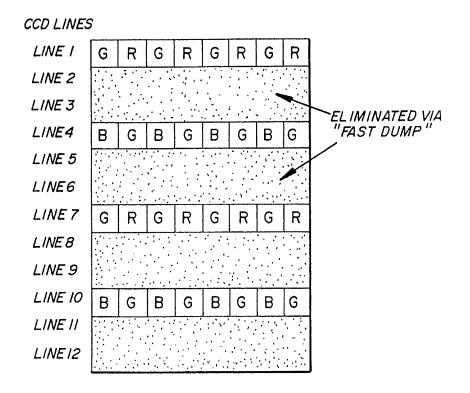

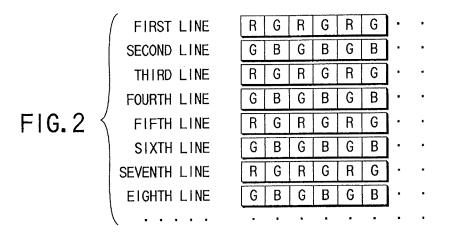

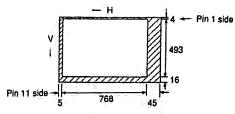

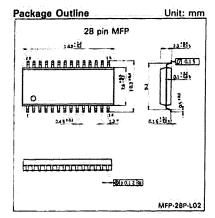

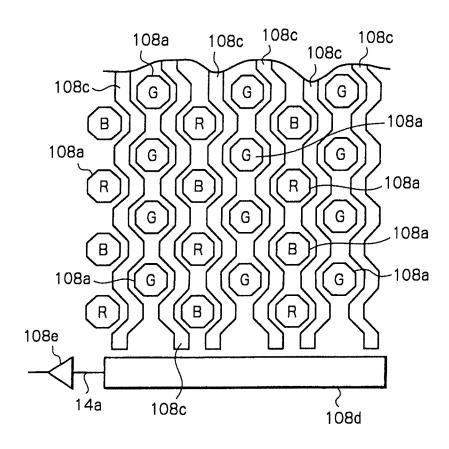

This time, a method image sensor for independently reading all 1.3 million pixels (VT method: Vacancy Transfer) in a 2/3 inch size was developed as to be dedicated to still images. This device simultaneously reads and transfers an image of a full frame that includes 1,280 (H) x 1,001 (V) effective pixels.

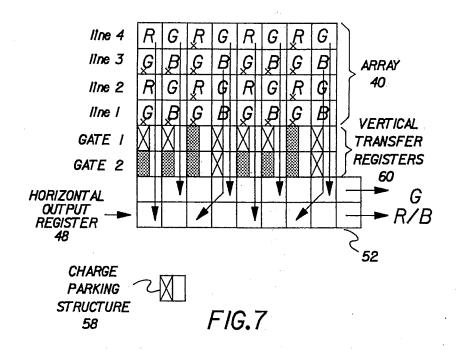

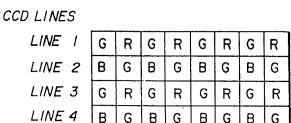

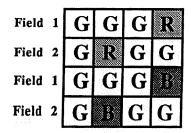

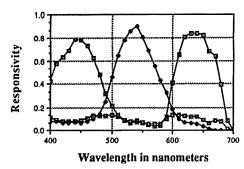

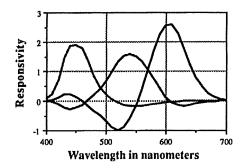

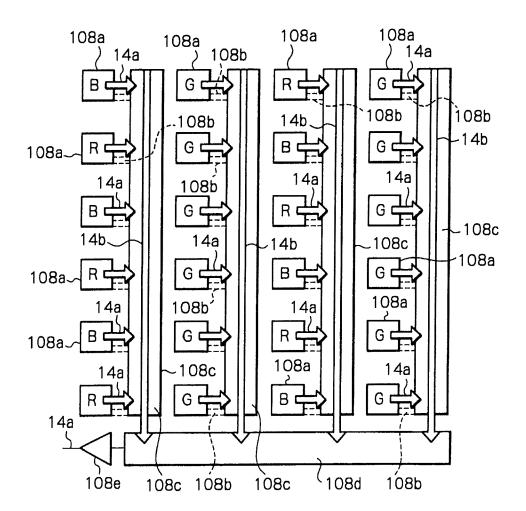

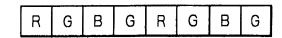

A G vertical-stripe R/B complete checkerboard method was attained as a result of simulating filter arrangements. Table 2 shows the element performance in this device.

| Transfer architecture      | Vacancy Transfer(VT)                                          |

|----------------------------|---------------------------------------------------------------|

| Optical format             | 2/3 inch                                                      |

| Number of effective pixels | 1, 240 (H) × 1, 001 (Y)                                       |

| Number of total pixels     | 1, 364 (B) ×1, 032 (Y)                                        |

| Aspect ratio               | 5:4                                                           |

| Pixel size                 | 8. 8 (H) × 6. 8 (V) µm²                                       |

| Effective pixel size       | 8. 7 (H) × 6. 96 (Y) am                                       |

| Optical black              | (H):front 4pixel rear 72pixel<br>(V):front 4pixel rear 4pixel |

| Frame rate                 | 1/5.96sec                                                     |

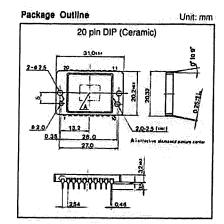

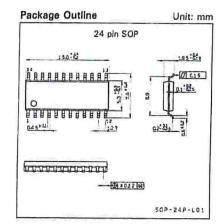

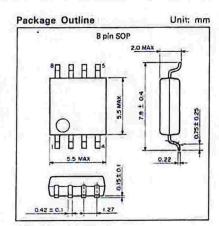

| Package                    | 28pin DIP                                                     |

| Filter                     | G line stripe<br>R/B perfect checker                          |

| Sensitivity                | 220mV<br>Green signal F5.6(1,200nt)                           |

| Saturation output voltage  | 400mV                                                         |

| Shutter speed              | 1/2 ~ 1/1,000cec                                              |

Table 2. Specification and Performance

| Formal                     | ELR Digital Sell Carpers                                                                       |                                                                                                                                                   |  |  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Less record                | Nikos P moese                                                                                  | Nikon P moest                                                                                                                                     |  |  |  |  |  |

| Forus models               | Astofostusal                                                                                   |                                                                                                                                                   |  |  |  |  |  |

| Express (costo)            | Programmel autoloperum pri<br>sharet priprig/ma                                                | ority/<br>real modes                                                                                                                              |  |  |  |  |  |

| Singular control           | Encountably controlled fortal<br>First : 1/2115 ~ 1/<br>1116 : 1/2115 ~ 1/<br>1111 1/2115 ~ 1/ | Escreenically convolud ford plane shutter  First : 1/2110 ~ 1/f sec  first : 1/2110 ~ 1/f sec  first : 1/2110 ~ 1/f sec  first : 1/2110 ~ 1/f sec |  |  |  |  |  |

| Apertura                   | 1-6 1 - 11 fet is the in                                                                       | terial Caufenper tens                                                                                                                             |  |  |  |  |  |

| Exposure compensation      | 1/411 11:1/±1ff an                                                                             |                                                                                                                                                   |  |  |  |  |  |

| Pinder                     | Optical Finder Frame coverage:<br>acts at picture area Viewing may                             | Optical FasherFrame coverage vimusby 160% of<br>actual picture area Viewing magnification 0.72X                                                   |  |  |  |  |  |

| Continuous film<br>advance | when using triage Messory Car                                                                  | 3 frame, but up to 7 frames; DS-3151, financies; (DS-305) when using bringe Memory Card HO-15                                                     |  |  |  |  |  |

| CCD                        | 1/1-ict, t, 14-pieri (j, 1)1                                                                   | × 1, 61/11/46                                                                                                                                     |  |  |  |  |  |

| Effective ISO              | 150 800/1600                                                                                   |                                                                                                                                                   |  |  |  |  |  |

| White balance              | Auto/manual/5 ateplicodes                                                                      |                                                                                                                                                   |  |  |  |  |  |

| Pile sice                  | l, titixt, tit pipely , ti-                                                                    | 114 14 47                                                                                                                                         |  |  |  |  |  |

| Storage medium             | aft troe f at #, ffact                                                                         |                                                                                                                                                   |  |  |  |  |  |

| Data compression           | 1790 packed                                                                                    |                                                                                                                                                   |  |  |  |  |  |

| Namber of fraces           | Consection mode<br>FIGUre congressed)<br>Fine<br>Normal<br>Banks                               | Number of Energy<br>3 Resons<br>21 Energy<br>43 Energy<br>84 Energy                                                                               |  |  |  |  |  |

| Octor                      | Video tuqua : NTSC/FAL Digi                                                                    | ni mapus: RS-422                                                                                                                                  |  |  |  |  |  |

| Forest stucks              | Dedicated NiOi battery / Factors                                                               | Debicated NiCol battery / Reserval power angely                                                                                                   |  |  |  |  |  |

Table I. Specification of DS-505

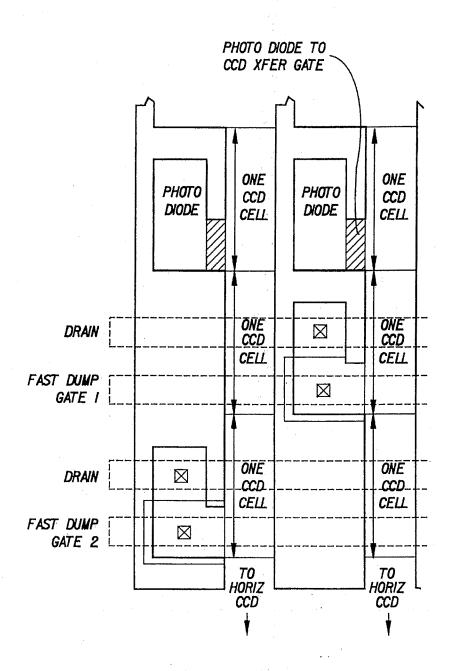

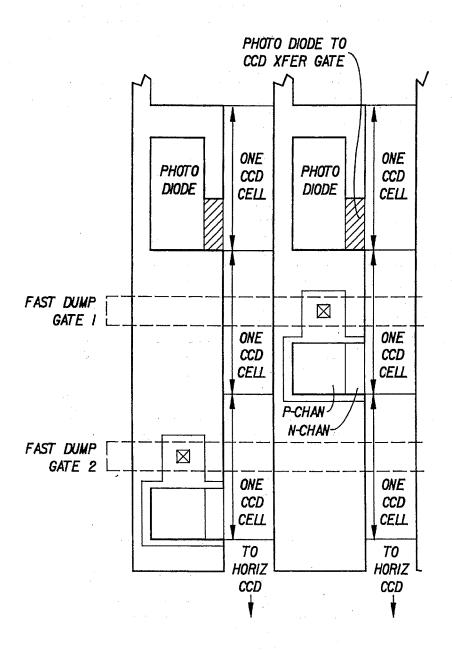

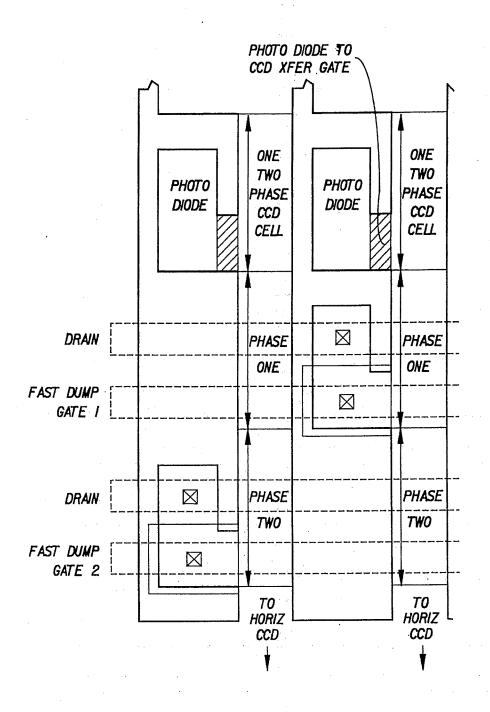

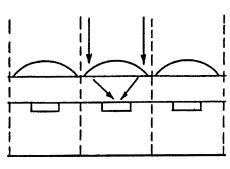

### 4-2) VT Method

Ordinary inter-line type CCDs read signal charges from all photodiodes to a vertical transfer path. It is not possible to transfer the charge without mixing.

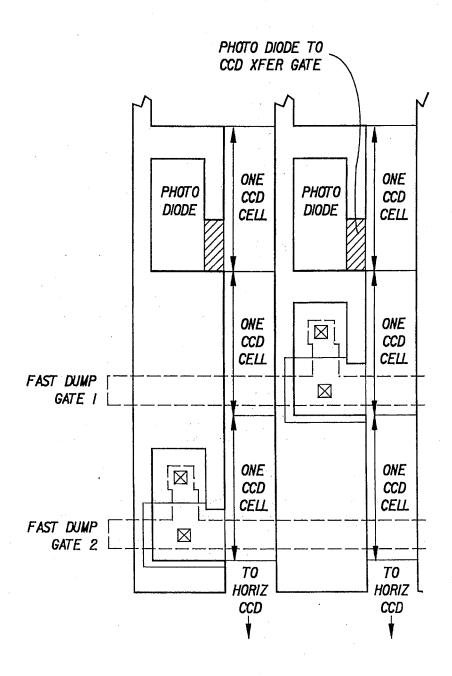

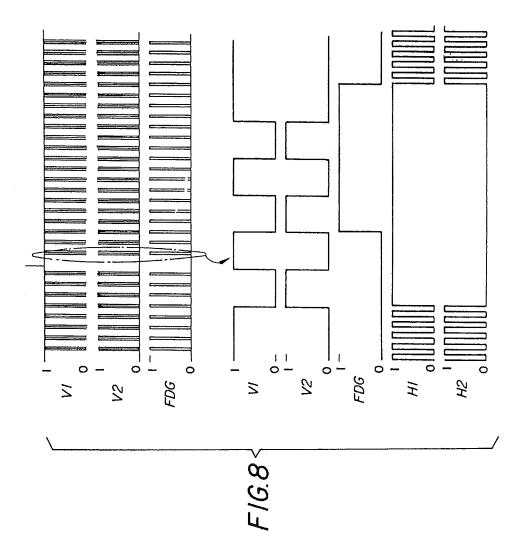

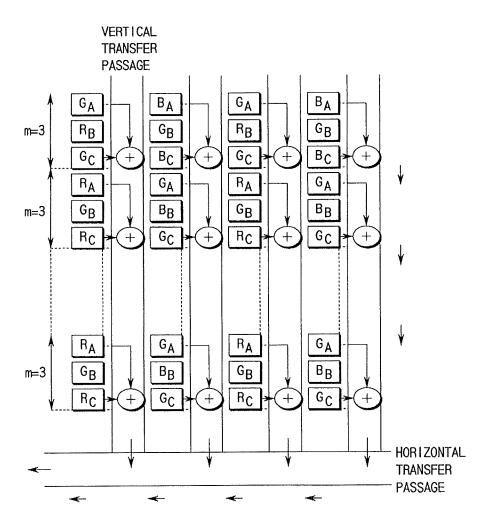

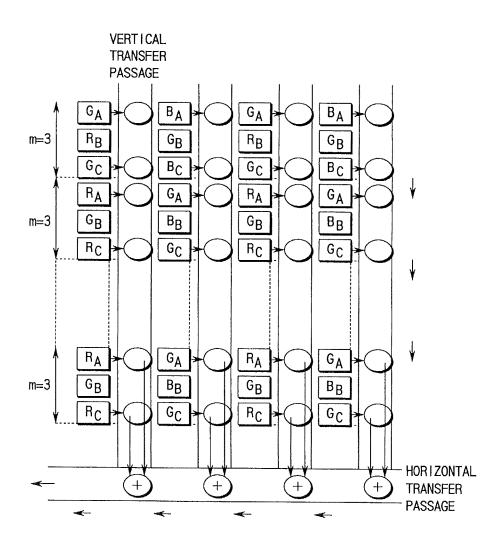

There, by injecting an empty packet generated from a horizontal charge transfer path side and moving this empty packet in a direction reverse to the vertical charge transfer path, it is possible to read all pixels at the same time.

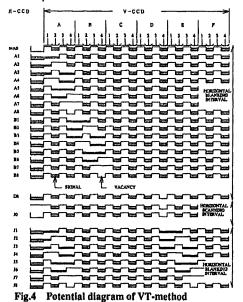

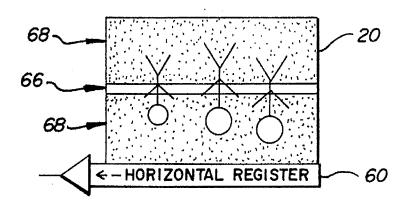

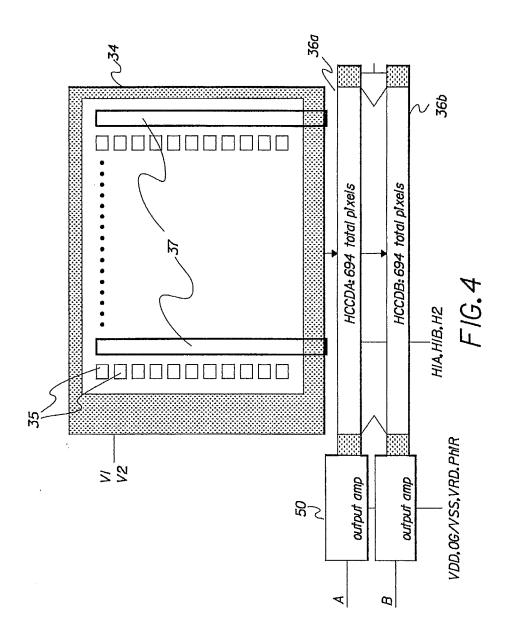

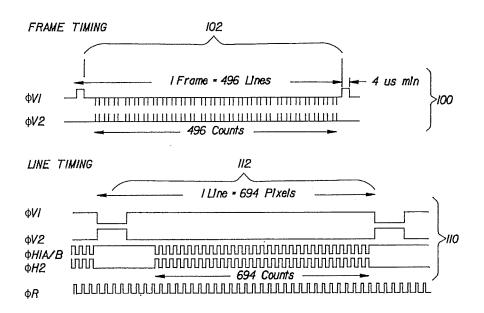

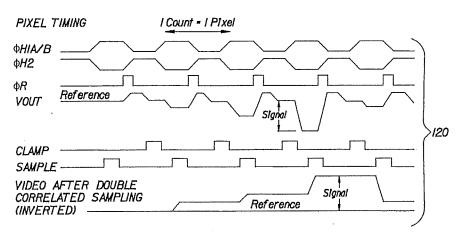

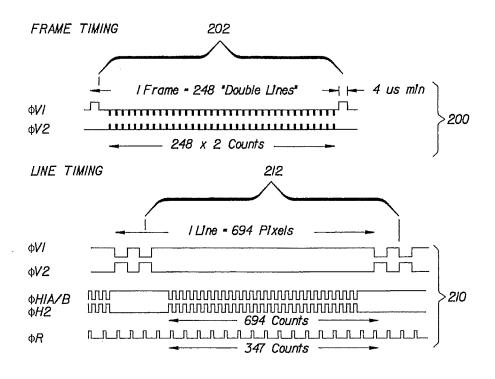

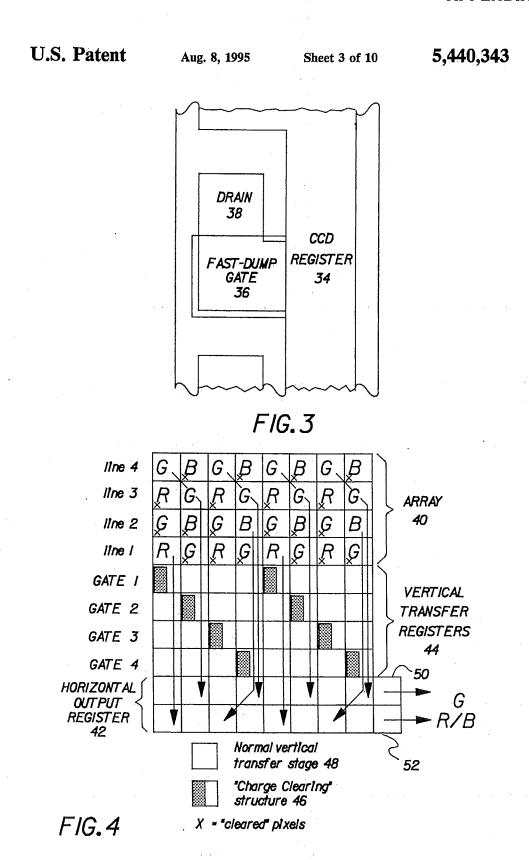

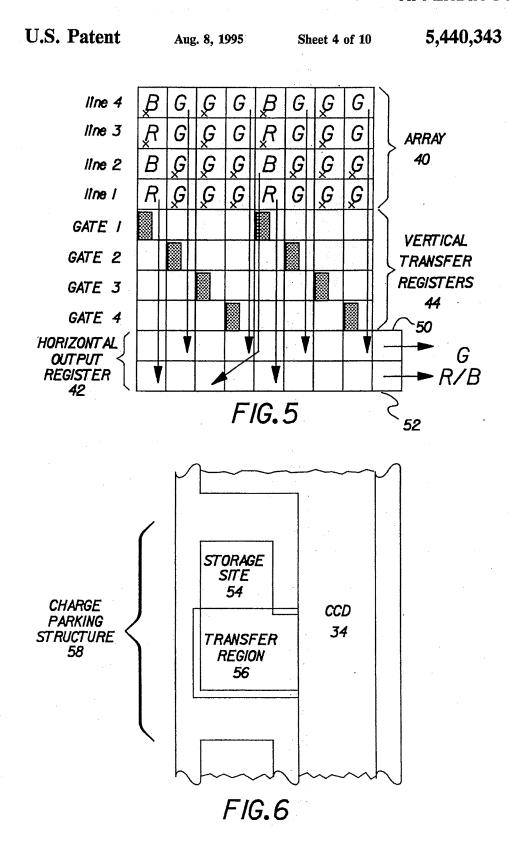

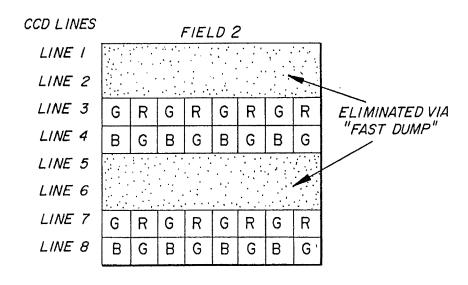

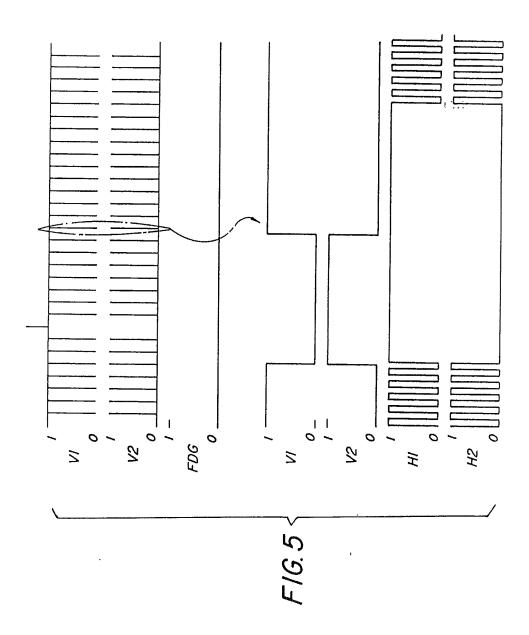

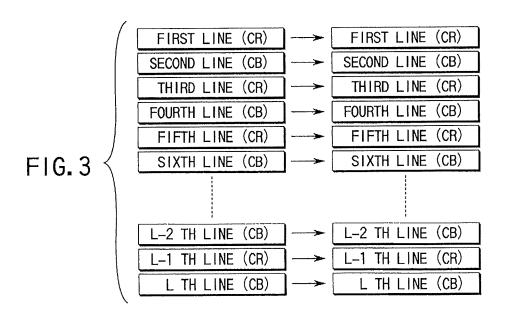

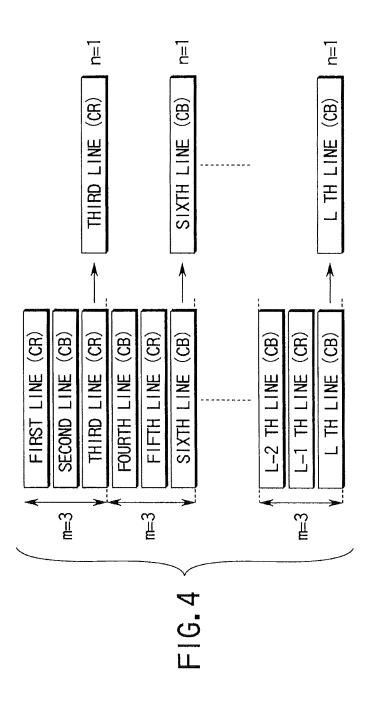

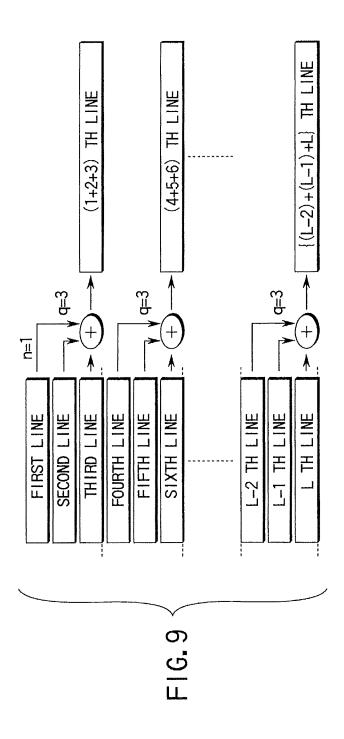

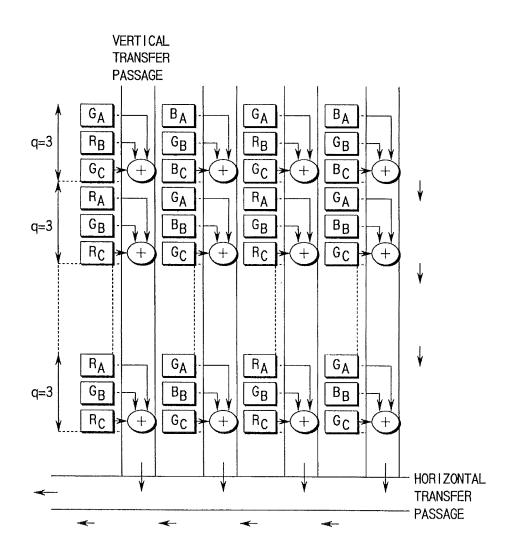

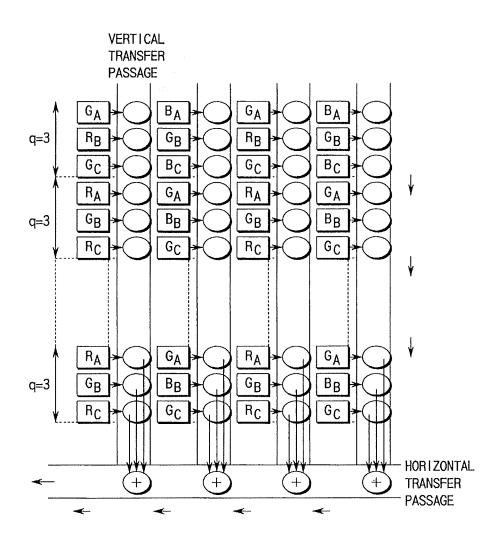

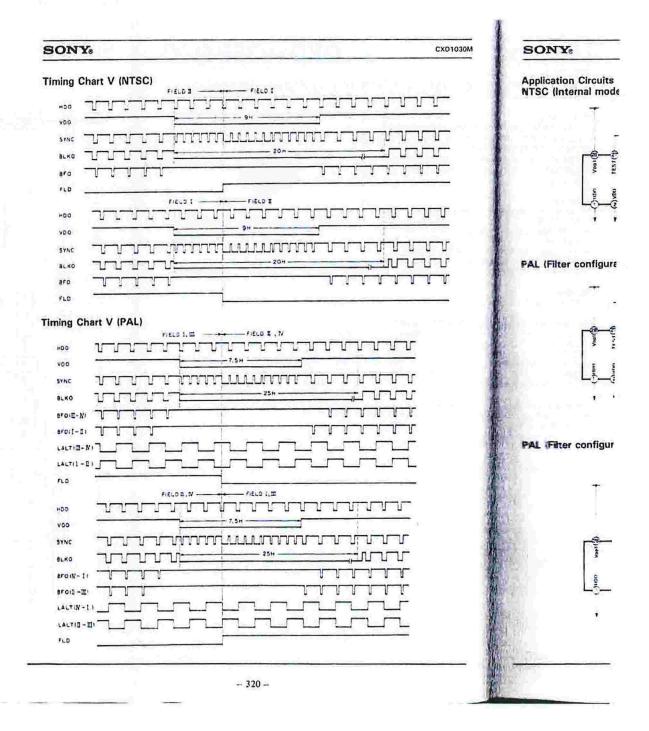

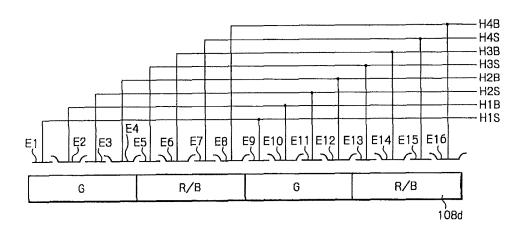

Fig. 4 is a view of the potential of a vertical transfer path that shows the drive method of the device. This shows that four transfer electrodes in order from nearest to the horizontal transfer path are one block; sequential vertical transfer pulses are charged and the empty packet moves sequentially in the reverse direction.

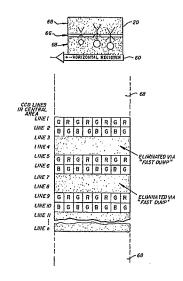

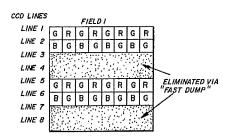

This injection operation of the empty packet is implemented in each horizontal period, and the empty packet is dispersed in 8-horizontal line increments in the vertical transfer route.

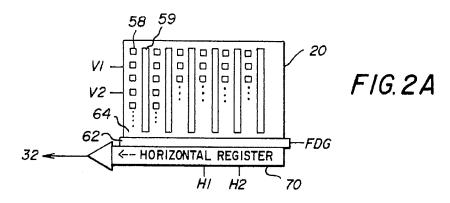

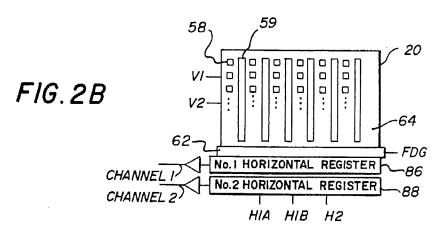

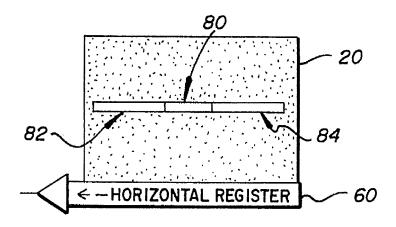

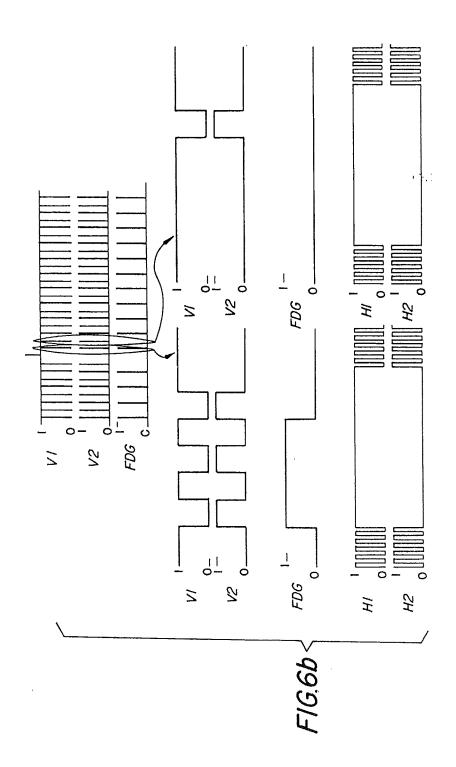

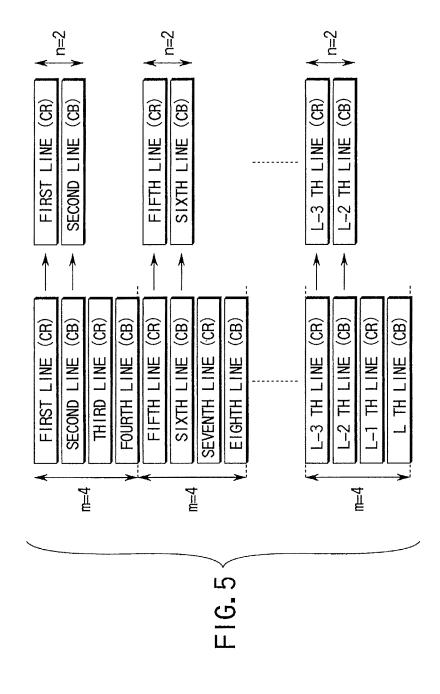

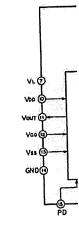

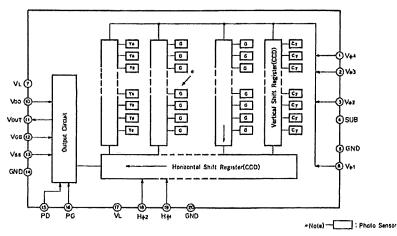

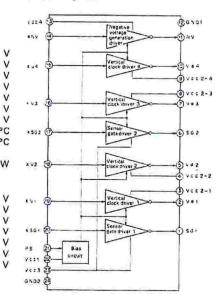

Fig. 5 shows a block diagram of the VT-CCD.

In order to attain this transfer method, a VT scanning circuit, a vertical-transfer pulse control circuit, and a charge-reading pulse charge circuit were disposed in an ordinary inter-line CCD.

The VT scanning circuit is composed of a shift register that generates a pulse for

sequentially selecting a blocked vertical transfer electrode. Output from the scanning circuit is contacted to the vertical transfer pulse control circuit, and a vertical drive pulse is charged to the selected block electrode. The chargeread-out pulse charge circuit is a circuit that controls the read-out gate to transferring the signal charge accumulated in the photodiode to the accumulated packet in the vertical transfer path. To read-out all pixels simultaneously, it is acceptable to turn on all TG pulses simultaneously.

### 4-3) Others Features

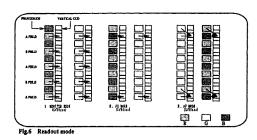

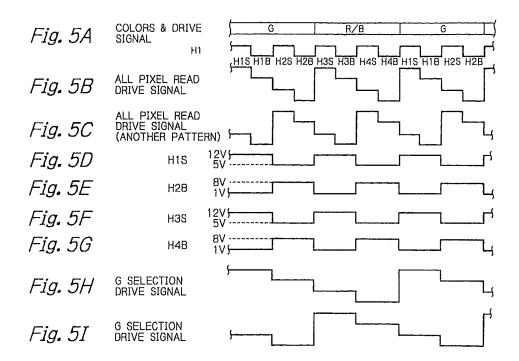

As another feature of this device, it also capable of the following drive, in addition to simultaneous read-out of all pixels, described above.

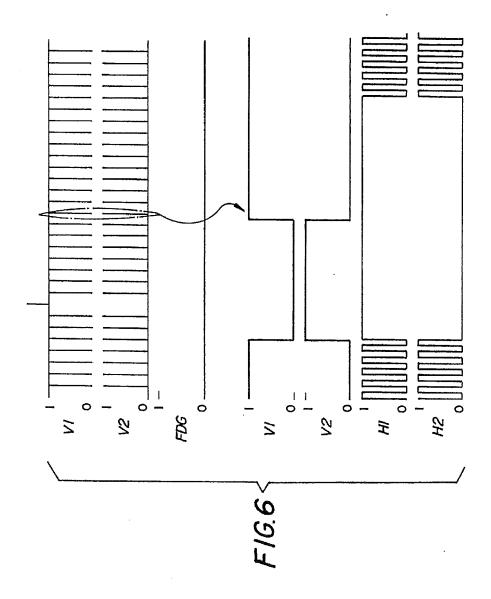

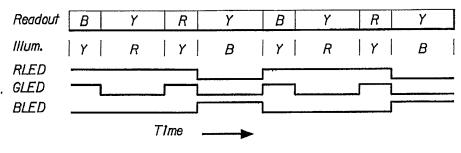

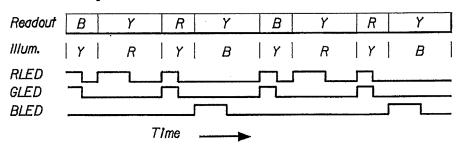

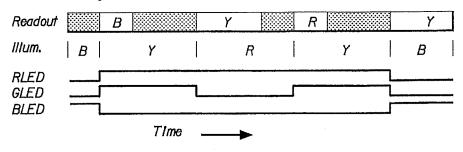

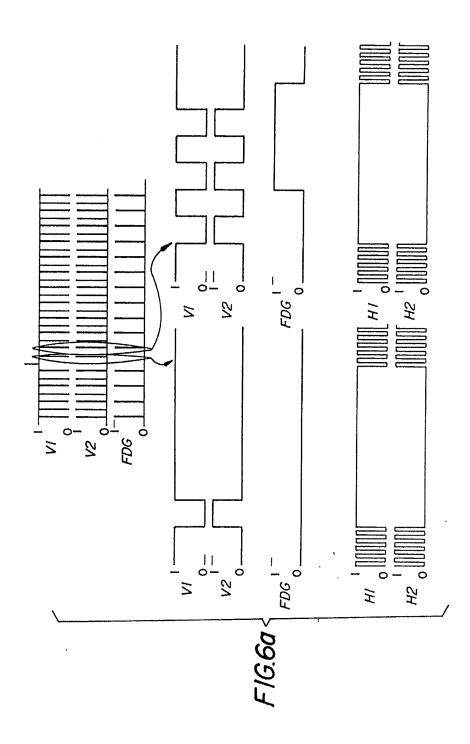

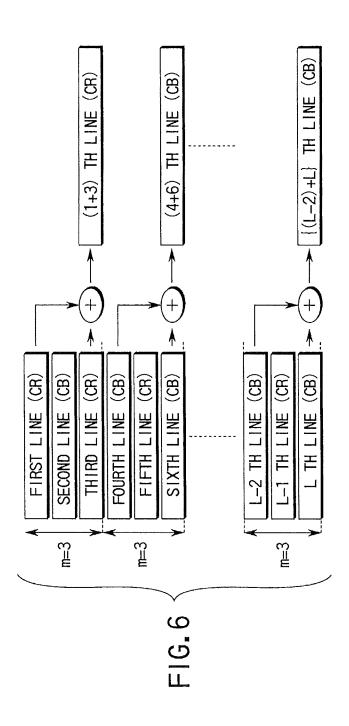

1) Movie mode (Fig. 6-1)

Includes a motor mode for reading the signal charge for each four vertical lines. Also includes a function for interlacing pixels in a 1,280 x 250 pixel field every 1/30 seconds.

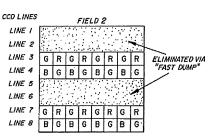

2) AE mode (Fig. 6-2)

Drive method for reading pixels in a 1,280 x 125 pixel field without mixing each color, using a drive method for reading at high speed of 1/60 seconds for each eight vertical lines.

3) AF mode (Fig. 6-3)

This is a drive method for reading pixels at the high speed of 1/60 seconds for each eight vertical lines similar to AE mode. However, to attain the information amount of the horizontal direction, this is a drive method for reading by calculating 2 pixels in the vertical direction.

It is possible to support the drive method described above so it is possible to implement pre-processes such as exporting images to an electronic

viewfinder or AE/AF and others, with the same speed as a conventional still camera.

PHOTOGOROW VERTICAL CCD

VONT

HIGHEONTAL CCD

HIGHEONTAL CCD

HIGHEONTAL CCD

SETT

Fig.5 Schematic diagram of this device

Optical Reduction System

Conventional single-lens reflex type digital still cameras could only record a portion of the image that can be seen from the finder, but with the DS-505/515, an optical reduction system was mounted to guide the image angle of the lends as it is to the CCD.

With this, the entire range in the finder visual field can be image-recorded, so imaging is possible with the same feeling as a single-lens reflex camera. 3)

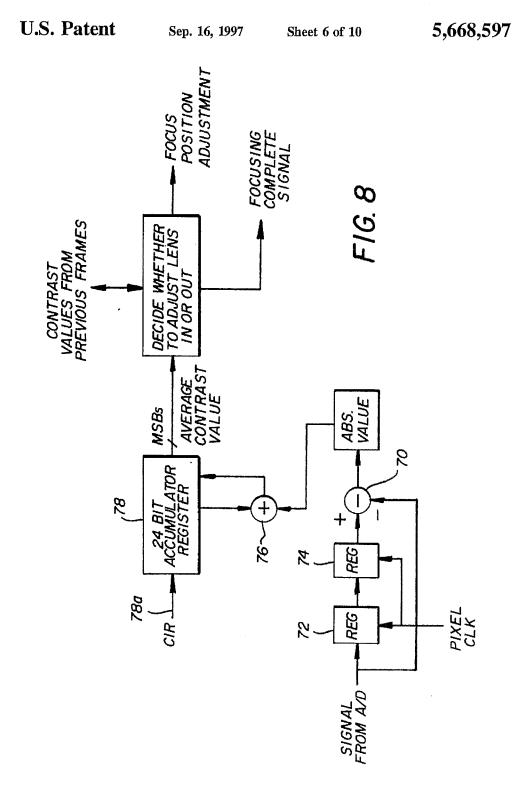

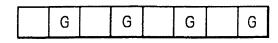

### 6. Signal-processing LSI

Four types of signal processing LSI (YC processor, memory controller, DCT processor, card controller) shown in the block diagram of Fig. 2 were developed.

Brightness/color-difference signal processing for VT-CCD signal output, JPEG-standard DCT compression and decompression, memory control, and card-interfacing of PC cards as recording media are possible with this LSI.

Also included are the low-power consumption features such as compactness, and support for 3.3 V drive and others. It is possible to constitute the most optimum circuit for the compact digital camera, and dramatically improve compatibility with PCs by adopting JPEG compression and PC card recording.

7. Recording Behavior and PC Cards

For the recording media, PC cards (ATA flash memory) which comply with PCMCIA have been adopted. When recording to ATA, compressed and uncompressed data is recorded at high speed to the card by buffering in sector units. For ATA, PC cards with a capacity of 15 M and that can record at the high speed of approximately 1 second/image is used.

### 8. Summary

It has become possible to obtain image quality comparable to L size (5 x 4 inches) prints by installing the 1.3 million-pixel VT CCD. Also, a size and weight equivalent to a single-lens reflex camera has been attained by making a majority of the electrical circuits ICs. These have gained favorable reviews in the commercial photography, and medical fields.

### Reference Literature

1)T.Soga,M.Arai,T.Matruo and K.I wabe;"Digital Card Camera DS-200F System", IS&T's 46th Annual Conference Proc.pp33-35.May.1993

2)T.Toma,A.Sakoda,A.Mikoshiba,K.Oda,R.Kawagichi and M.Inuiya;"A 2/3-Inch 1.3M-pixel Falli Frame Readout VT-CCD Image Sensor", ITE Technical Report Vol.18,No.54,pp15-18,Oct.1994

3)M.Takemae,T.Ohta,K.Higashi and K.Kawamura;"The Development of SRL-type Digital Still Camera", ITE Technical Report Vol.19,No.45,pp21-25,Sep.1995

4)O.Saito,M.Watanabe,K.Ito,K.Adachl and S.Nishi: "Signal Processing LSIs for High-Resolution Digital Card Camera DS-505/DS-515", IS&T's 48th Annual Conference Proc.pp418-421,May.1995

Fuji Photo Film Co., Ltd .Products Planning & Development Dept. Electronic Imaging Products Div. 3-11-46 Senzui, Asaka City, Saitama Prefecture, 351 TEL 048-468-2378

### **APPENDIX DDD**

### A4M-Pixel CMD Image Sensor A4M-Pixel CMD Image Sensor

Shigeru Hosokai, Tetsuo Nomoto, Toshihiko Isokawa Ryouji Hyuga, \*Shinichi Nakajima and "Toshiyuki Terada

OLYMPUS Optical Co., Ltd.

Microcomponent Engineering Dept.

Microcomponent Engineering Dept.

\*Imaging System Dept.

OLYMPUS Optical Co., Ltd.

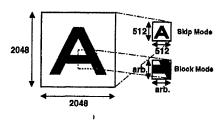

A 4M-pixel Charge Modulation Device (CMD) image sensor with pixel size of  $7.5 \times 7.5 \, \mu m^2$  has been developed. The sensor has three readout modes that are a full, a skip and a block modes. A4 M-Pixel image is obtained in the full modes, while an arbitrary window-of-interest can be read out in the block modes. The skip mode reads every  $4^{th}$  pixel in both horizontal and vertical directions. The frame rate can be raised in the skip and the block modes. The sensor also has a capability of lowering the dark current generation during the integration time.

### 1. Introduction

In recent years, the demand for higher resolutions of electronic images has become extremely high. For that reason, a breakthrough has been required in problems relating to embedding in conventional, standard television format. The biggest of these problems, relating to ease-of-use for image quality and image-inputting devices, is the frame rate.

In this paper, the authors report on a 4 million-pixel CMD imaging element that they developed, with a focus on this viewpoint.<sup>1)</sup>

Several items that use CCD as high-resolution imaging elements that exceed high-vision (2-million pixels) have been reported.<sup>2</sup> However, most of these imaging elements substantially support still images, and it can take several

seconds to load the image of one frame. For that reason, there are a variety of restrictions in the demand for industrial and consumer use. For example, using the example of a digital still camera, the fact that it is not possible to attain framing or focusing which are indispensable camera functions in real-time are major disadvantages of these kinds of cameras with high-resolution imaging elements. Also, because the frame rate is low, it takes a long time to accumulate a signal charge so there is a problem in that image quality degrades because of a dark charge that is accumulated along with the signal charge. A method has also been adopted in some to cool the elements in order to suppress the generation of the dark charge, but this introduces a new problem of

increased power consumption of the overall system.

Still further, a variety of exposure times are used in electronic still cameras which are different from TV cameras. As the exposure time increases, a dark charge for that amount is accumulated. This invites serious image degradation along with the accumulation of a dark current caused by the low frame rate.

1-1. Countermeasure for Solving the Frame-rate Problem in High-resolution Imaging Elements

The basic countermeasure for solving the problem described above which is caused by a low frame-rate is to raise the data rate of the signal. For that reason, there is a method for making the drive block itself high-speed, and a method for improving the effective data rate by using multiple signal output lines. However, in the case of the 4 million pixel imaging elements, for example, the clock frequency required to attain a frame-rate of 30 fps with the former method is 150 MHz or higher. In such a case, major difficulties are expected considering an increase in the signal band and additional processing circuits.

Also. with ordinary CCDs, temperature of the element rises because of the increased power consumption in line with the higher clock speed; there is a high danger that that will cause image degradation caused by the dark current. Conversely, the latter method for reading out using multiple lines is often used with high-speed cameras, but there is a tendency for images to degrade when processing circuits becoming more complex, and variations in each output line and processing circuit return to the low-frequency side of video signals.

For that reason, the authors developed a new scanning method that solves the bugs in functionality and performance to circumvent a situation that directly faces new problems caused by making data rates high-speed as they are. For that reason, firstly, the authors organized the problems caused by a low frame-rate, namely the three points already mentioned. They are:

- (1) Maintaining framing an overall image observation in real time;

- (2) Maintaining focusing and detailed observation in real time; and

- (3) Preventing image degradation cause by accumulation of a dark charge.

The authors undertook development with a view to solving each of these problems using the following methods.

- (1) Thinned readout: Spatial resolution degrades, but functional requirements are matched and real-time is maintained.

- (2) Any region readout: Viewability of the entire image angle is lost, but functional requirements are matched and real-time is maintained.

- (3) Low-dark current drive: Alleviates pixel bias during exposure of the read-out of all pixels and prevents image degradation by reducing the dark current. The following reports on the overall design and the results of evaluations of prototype imaging elements.

### 1-2. Design

When designing this image sensor, functions for freely switching the three read-out methods (all pixels, thinning/random range) were installed in the scanning circuit, in order to solve the problem of frame-rate. Also, a function for implementing low-dark current drive was installed to suppress the generation

of the dark charge when a charge is accumulated.

### 1-3. Sensor Configuration

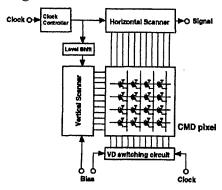

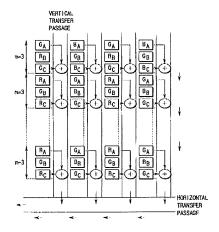

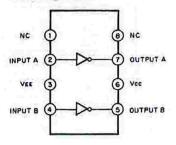

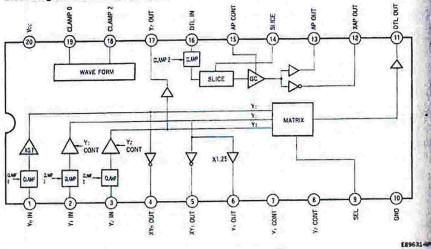

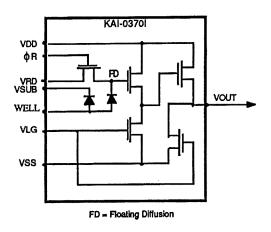

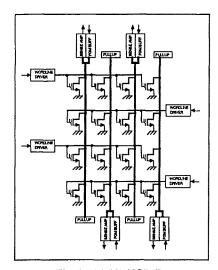

Fig. 1 is a circuit diagram for the CMD imaging elements. CMD is a 4-terminal MOS device. Three terminals other than the gate are biased to DC.

Fig. 1 Block diagram of the CMD image sensor.

CMD behavior control is implemented by changing the gate potential; the CMD source current is handled as an output signal. Each row of CMD source terminals is commonly connected to the source line in the vertical direction. This source line is connected to the output signal line via a MOS switch driven by a horizontal scan circuit. The gate for CMDs in each line is commonly connected to the horizontal direction gate line. The CMD of each line is controlled for read-out behavior and reset behavior by a pulse charged to each gate line from the vertical scan circuit.

Pixel selection of CMD imaging elements as described above is implemented by an X-Y address method.

### 2. New Development Item 1 (Each Type of Read-out Method)

Fig. 2 shows the general concepts newly developed for Full mode, Skip mode, and Block mode with these imaging elements.

Fig.2 Schematic diagram of three reason modes.

Fig.3 Configuration of the shift register.

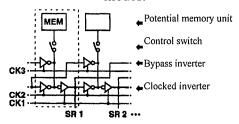

Generally, a decoder is used for read-out of any pixel. However, with a decoder, no bit is equivalent in a circuit, so there is concern that streak-like FPN will be generated. Therefore, a circuit was developed with all bits having the same configuration. Fig. 3 is a conceptual view of the scanning circuit developed this time. The shaded portion is a unit of one level of the scanning circuit. This unit is composed of a potential memory unit for a read-out position setting in block mode, a control switch for switching the clocked inverter when not using the potential memory unit, and a bypass inverter for transferring a transfer pulse when in skip mode from a next level clocked inverter to a destination. Behavior of the scanning circuit to attain each scanning mode will now be described below.

### 2-1. Full Mode

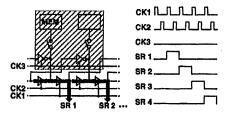

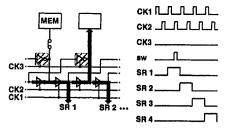

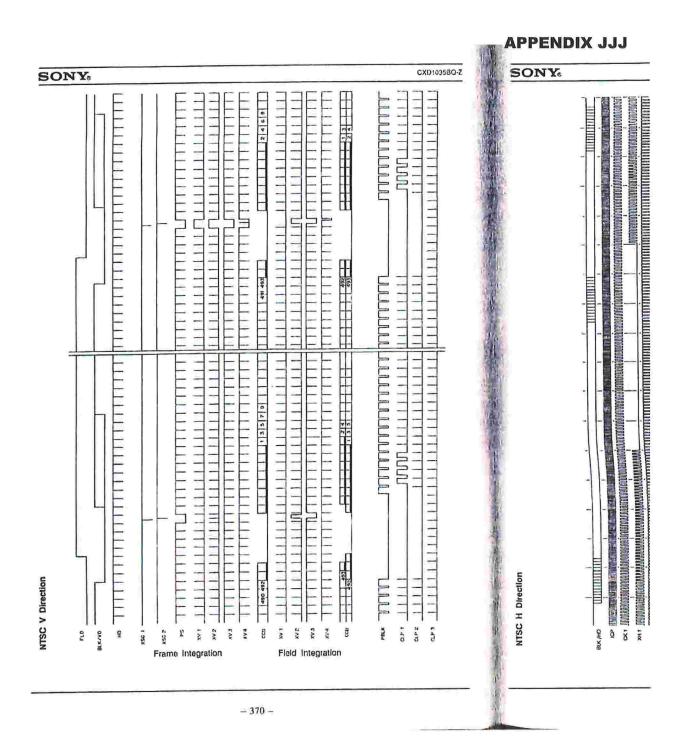

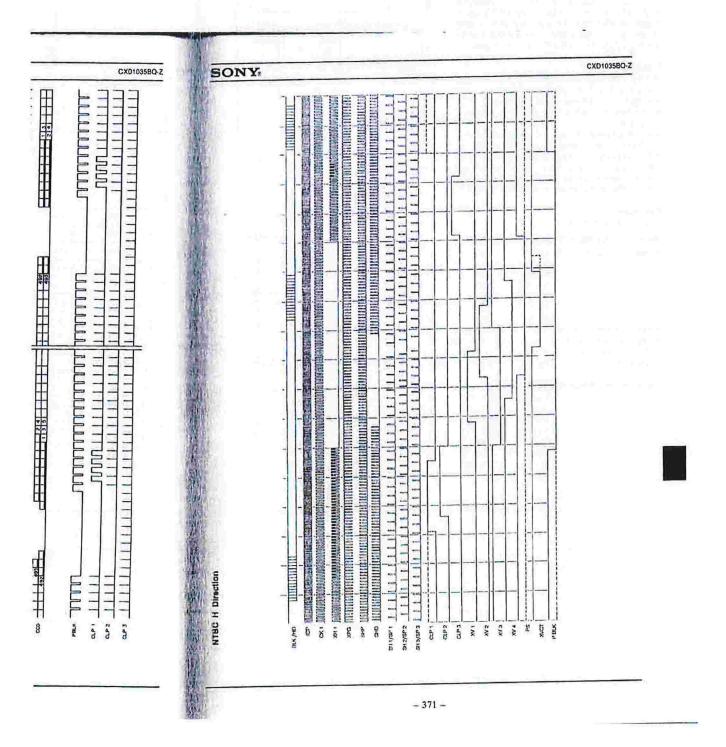

Fig. 4 is a timing chart when in full mode drive. With full mode scanning, fix CK3 in Fig. 3 to low level, and turn off the control switch at the same time to

electrically separate the potential memory unit, and the bypass inverter from the clocked inverter. For that reason, in full mode, this has the same scan circuit configuration as conventional CMD imaging elements. The result is that the start pulse is transferred sequentially by CK 1 and CK 2 inside the clocked inverter, and carried to the final stage of the shift registers. Row and line selection signals appear in sequence of SR 1, SR 2

• • •; in full mode, it is possible to attain an image with the resolution of 4 million pixels.

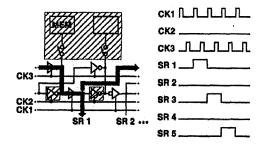

#### 2-2. Skip Mode

Fig. 5 shows the timing chart when in skip mode drive. It is possible to attain random thinning rates by changing the connection of the bypass inverter, but with these imaging elements, it was designed to thin three pixels of four pixels in both the horizontal and vertical directions. This resulted in being able to obtain all pixels obtained in the field angle of the imaging elements as a rough image thinned at 1/16. The frame-rate is 30 fps, and it is also possible to display video.

When scanning in skip mode, by tuning off the control switch, the potential memory unit is separated in the same way as in full mode. Also, fixing CK2 to low level stops operation of the initial inverter of the clocked inverters at two levels that compose single units of the shift registers. The result is that the shift pulse is transferred to the bypass inverter and the last level inverter of the clocked inverters at two levels by CK 1, and CK 3.

Fig.4 Timing diagram of the Full mode.

Fig.5 Timing diagram of the Skip mode.

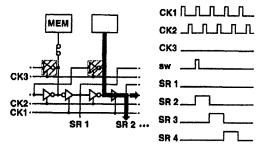

#### 2-3. Block Mode

Block mode is a scanning method for reading out all image information in an arbitrary, specified range. A two-stage process is required to implement block mode. These are a process for setting the read-starting position and a process for actually reading out an arbitrary range.

Fig. 6(a) is a timing charge for setting the read-starting position in block mode. In order to set the read-starting position, firstly, electrically separate the bypass inverter by fixing CK 3 to low level. Until the signal-reading position is set, the content of the clocked inverter that is two levels is sequentially transferred by the start pulse. When the transferred start pulse reaches the desired read-out-starting position, node information in clocked inverters at each level is transferred altogether to the potential memory unit a the corresponding position when all control switches are turned on. The result is that the low level is set for only the potential memory unit at the position to start reading.

(a) Start address set-up

(b) Signal readout Fig.6 Timing diagram of the Block mode.

Next, the scan circuit drive method for reading out signals in an arbitrary range will be described. Fig. 6(b) is a timing charge for reading gout signals in block mode. In the same way as setting the read-starting mode, electrically separate the bypass inverter by fixing CK 3 to low. Potential information that is retained in the potential memory unit is transferred into the shift registers when the control switch is turned on while driving CK 1, and CK 2. The result is that the selection signal appears at SR 2 in Fig. 3, and is sequentially transferred to a later stage by CK 1, and CK 2. The range to read can be randomly specified, but if the pixel count to read is not different from skip mode, the frame-rate will be 30 fps, and video display will be possible.

# 3. New Development Item 2 (Low-dark Current Drive)

Details of the mechanism that generates CMD dark current is being analyzed, but the authors have understood that dependency on the gate drain electrical field is one major factor<sup>3)</sup>. The low-dark current drive that was adopted for these imaging elements will be described after the conventional CMD drive is described. The low-dark current drive adopted for these imaging elements will be described after describing the conventional CMD drive below.

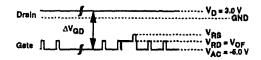

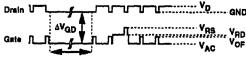

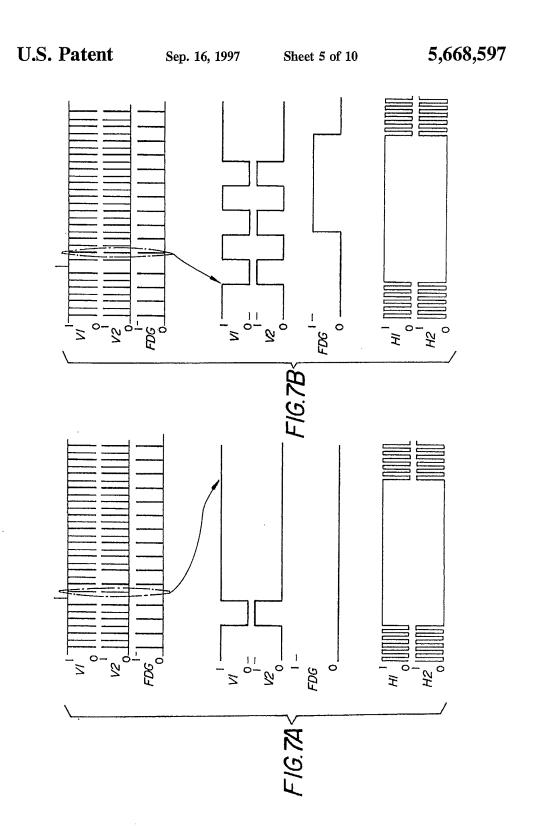

#### 3-1. Low-dark Current Drive

Fig. 7(a) is a drive method for conventional CMD imaging elements. A positive DC bias is charged to a drain electrode, and is fixed to approximately a normal 3V. In this state, CMD behavior is controlled by changing the gate voltage VG. The charge accumulation status is maintained while a voltage; VAC is charged to the CMD gate electrode to accumulate a charge. The CMD is cut-off and the source current does not flow. Here, when a potential; VRD for reading the signal is charged to the gate electrode, the source current is started to be read. Also, an overflow potential; VOF for sweeping away an excess charge is supplied to non-selected pixels during the horizontal blanking period. Normally, a voltage of approximately -6V is charged to VAC in the potential accumulation state, so the potential difference; VGD between the gate and drain is a maximum of 9V.

Fig. 7(b) is a drive method for the newly developed CMD imaging elements. By lowering the drain voltage; VD for the exposure time in full mode, generation of the dark charge is suppressed by

mitigating the electrical field between the gate and drain. For that reason, VD is supplied via a VD switch. Therefore, when the VD switch is turned on, the terminal supplying VD is switched to GND. With these imaging elements, the potential difference  $\Delta VGD$  between the gate and drain is mitigated from a maximum of 9V to 6 V.

(a) Conventional driving of the CMD image sensor

Low-dark current drive period

(b) New driving of the CMD image

#### 4. Evaluation Results

4-1. Each Read-out Method (Full/Skip/Block)

Fig. 8(a) and Fig. 8(b) show imaging examples in a resolution chart. Fig. 8(a) is an imaging example of a resolution chart for the skip mode. Here, an entire image of a target object is obtained within an angle of view that can capture with an image area of these imaging elements. Pixels are thinned to 1/16 in line with the horizontal and vertical directions. Fig. 8(b) is an imaging example of a resolution chart for the block mode. Fig. 8(b) is a view of reading a region indicated by the white frame in Fig. 8(a). The drive frequency of these imaging elements is approximately 12 MHz; these imaging examples are displayed on an

NTSC monitor. The frame-rate for both skip and block modes is 30 fps, and it is also possible to display video. Also, in full mode, resolution of 2,000 TVs is implemented for both horizontal and vertical directions.

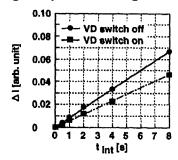

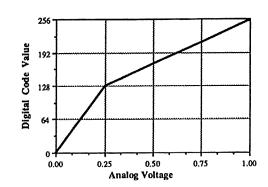

4-2. Low-dark Current Drive

Fig. 9 is a graph showing results when implementing low-dark current drive while accumulating a charge. The horizontal axis represents the time for accumulating a charge; the vertical axis represents the amount of increase of signal currents caused by accumulating a dark charge. The incline in the graph is equivalent to the rate of generation of the charge for each. As a result of implementing low-dark current drive with the prototype elements this time,

generation of a dark charge compared to the conventional method was suppressed 30%. With this, it is possible to reduce the amount accumulated during exposure of the dark-current charge accumulated in full mode.

(a) Skip mode.

(b) Block mode.

Fig.8 Reproduced images

Fig.9 Dark current generation.

# 4-3. Element Characteristics Table 1 shows the design characteristics and features of these imaging elements. Of the characteristics in the table, the saturation signal current and sensitivity were measured in skip mode (accumulation time $t_{int} = 1/60s$ ). The

saturation signal current was 24  $\mu$ A, and the sensitivity was 440 nA/lx. Power consumption was measured in block mode and had low power consumption of 90 mW. This indicates a value substantially equivalent to skip mode. The dynamic range in full mode is determined by dark-current shot noise of the pixels. In full mode, the results of signal accumulation time of 0.4 s and 70 dB were obtained.

#### 5. Summary

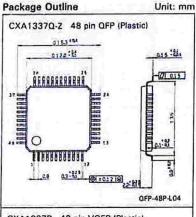

A 4 million-pixel CMD imaging element was developed. Fig. 10 shows a photo of the chip. Not only is drive frequency increased, but also a design was implemented for the purpose of solving the problems of frame rate in high-definition images without multi-line readouts. Development of imaging elements that have three read-out methods was successful. The result was that by dual use of both skip mode and block mode, the overall rough image of high-definition images and a portion of the image can be confirmed in a video.

Table I Specifications and performance of the CMD image senser.

| Pixel size                | 7.5 $\mu$ m(H)× 7.5 $\mu$ m(V) |

|---------------------------|--------------------------------|

| Number of effective pixel | 2048(H)×2048(V)                |

| Image area                | 15.36 mm(H)×15.36 mm(V)        |

| Chip size                 | 20.0 mm(H)×20.0 mm(V)          |

| Output channel            | Single                         |

| I/O pins                  | 35 pins                        |

| Readout mode              | Full/Skip/Block                |

| Saturation Signal         | 24 μ Α                         |

| Sensitivity               | 440 nA/lx (tint=1/60 s)        |

| Blooming level            | -110 dB                        |

|                           | (V/10 exposure,Block mode)     |

| Power dissipation         | 90 mW (Block/Skip)             |

| H limiting resolution     | 2000 TV lines                  |

| V limiting resolution     | 2000 TV lines                  |

| Dynamic Range             | 70 dB (Full mode)              |

| Frame rate (@12MHz)       | 2 fps (Full mode)              |

|                           | 30 fps (Skip mode)             |

|                           | variable (Block mode)          |

#### APPENDIX DDD

Fig. 10 CMD image sensor micrograph.

Also, to avoid a drop in image quality that accompanies the generation of a dark charge during exposure in full mode, a low-dark current drive was developed. By adopting this drive method, an amount of suppression of 30% of a dark charge compared to the same accumulation time was confirmed.

The functionality above was satisfied, and despite multiple pixels, low power consumption of 90 mW was attained.