| UNITED STATES PATENT AND TRADEMARK OFFICE |

|-------------------------------------------|

| BEFORE THE PATENT TRIAL AND APPEAL BOARD  |

| SAMSUNG ELECTRONICS CO., LTD. Petitioner  |

| v.                                        |

| PROMOS TECHNOLOGIES, INC. Patent Owner    |

| Patent No. 6,163,492                      |

DECLARATION OF INGRID HSIEH-YEE, PH.D. IN SUPPORT OF PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 6,163,492

# Declaration of Dr. Ingrid Hsieh-Yee U.S. Patent No. 6,163,492

## **Table of Contents**

| I.   | INTRODUCTION   |                                                      |    |

|------|----------------|------------------------------------------------------|----|

|      | EX. 1014 WESTE |                                                      |    |

|      | A.             | Library of Congress – Bibliographic and MARC Records | 9  |

|      | B.             | Library of Congress – Date Stamp                     | 13 |

|      | C.             | United States Copyright – Copyright Registration     | 14 |

|      | D.             | Actual Usage                                         | 15 |

| III. | II. CONCLUSION |                                                      |    |

| IV   | ΔΡΕ            | PENDICES                                             | 19 |

I, Ingrid Hsieh-Yee, Ph.D., declare as follows:

### I. INTRODUCTION

- 1. I have been retained as an independent expert witness on behalf of Samsung Electronics Co., Ltd. ("Samsung") in this proceeding before the United States Patent and Trademark Office ("PTO") regarding U.S. Patent No. 6,163,492.

- 2. I am being compensated for my work in this matter at my accustomed hourly rate. I am also being reimbursed for reasonable and customary expenses associated with my work and testimony in this investigation. My compensation is not contingent on the results of my study, the substance of my opinions, or the outcome of this matter.

- 3. In the preparation of this declaration, I have reviewed the documents referenced below. Each of these documents is a type of material that experts in my field (as I discuss below) would reasonably rely upon when forming their opinions. I refer to these documents by exhibit numbers that I understand are assigned to them in this proceeding before the PTO.

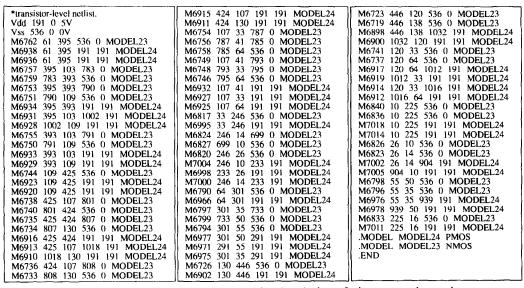

- (1) Weste, N. H. E. & Eshraghian, K. (1993). PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE ("Weste"), **Ex. 1014**;

- (2) Bibliographic record for PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE (1993) available at the Library of Congress online catalog at <a href="https://lccn.loc.gov/92016564">https://lccn.loc.gov/92016564</a>, accessed on February 26,

## 2019, Appendix C;

- MARC record for PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS

PERSPECTIVE (1993) available at the Library of Congress online

catalog

at <a href="https://catalog.loc.gov/vwebv/staffView?searchId=23680&recPoint">https://catalog.loc.gov/vwebv/staffView?searchId=23680&recPoint</a>

er=0&recCount=25&searchType=1&bibId=1559597, accessed on

February 26, 2019, **Appendix D**;

- (4) Copyright registration record for PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE (1993), available at the public catalog of the United States Copyright Office at <a href="https://cocatalog.loc.gov/cgi-bin/Pwebrecon.cgi?v1=1&ti=1,1&Search%5FArg=principles%20of%20cmos%20vlsi%20design&Search%5FCode=TALL&CNT=25&PID=Pgd2v2jBNnZG4h6jx7oX1FhZaj&SEQ=20190303114850&SID=3, accessed on February 26, 2019, **Appendix E**.

- **4.** In forming the opinions expressed within this declaration, I have considered:

- (1) The documents listed above;

- (2) The reference materials cited herein; and

- (3) My own academic background and professional experiences, as described below.

- **5.** My complete qualifications and professional experience are described in my academic curriculum vitae, a copy of which is attached as **Appendix A**. The following is a brief summary of my relevant qualifications and professional

experience.

- 6. I am currently a Professor in the Department of Library and Information Science at the Catholic University of America. I have experience working in an academic library, a medical library, and a legislative library and have been a professor for more than 25 years. I hold a Ph.D. in Library and Information Studies from the University of Wisconsin-Madison and a Masters degree in Library and Information Studies from the University of Wisconsin-Madison.

- 7. I am an expert on library cataloging and classification and have published two books on this subject, *Organizing Audiovisual and Electronic Resources for Access: A Cataloging Guide* (2000, 2006). I teach a variety of courses, including Cataloging and Classification, Internet Searches and Web Design, Advanced Cataloging and Classification, Organization of Internet Resources, Advanced Information Retrieval and Analysis Strategies, the Information Professions in Society, Information Literacy Instruction, and Digital Content Creation and Management. My research interests cover cataloging and classification, information organization, metadata, information retrieval, information architecture, digital collections, scholarly communication, user interaction with information systems, and others.

- 8. I am fully familiar with a library cataloging encoding standard known as the "Machine-Readable Cataloging" standard, also known as "MARC," which became the national standard for sharing bibliographic data in the United States by 1971 and the international standard by 1973. MARC is the primary communications protocol for the transfer and storage of bibliographic metadata in libraries. Experts in my field would reasonably rely upon MARC records when forming their opinions.

- 9. A MARC record comprises several fields, each of which contains specific data about the work. Each field is identified by a standardized, unique, three-digit code corresponding to the type of data that follows. Appendix B is a true and correct copy of Parts 7 to 10 of "Understanding MARC Bibliographic: Machine-Readable Cataloging" (http://www.loc.gov/marc/umb/) from the Library of Congress that explains commonly used MARC fields. For example, the personal author of the work is recorded in Field 100, the title is recorded in Field 245, publisher information is recorded in Field 260, and the physical volume and characteristics of a publication are recorded in Field 300, and topical subjects are recorded in the 650 fields.

- 10. Library online catalogs are based on MARC records that represent their collections and help the public understand what materials are publicly

accessible in those libraries. Most libraries with online catalogs have made their catalogs freely available on the Web. These online catalogs offer user-friendly search interfaces, often in the form of a single search box, to support searching by author, title, subject, keywords and other data elements. They also offer features for users to narrow their search results by language, year, format, and other elements. Many libraries display MARC records on their online catalogs with labels for the data elements to help the public interpret MARC records. Many libraries also offer an option to display MARC records in MARC fields. For monographs, after a MARC record is created and made searchable on a library catalog, it is customary library practice to have the physical volume processed for public access soon after, usually within a week.

11. I used authoritative information systems such as the online catalog at the Library of Congress (<a href="https://catalog.loc.gov">https://catalog.loc.gov</a>) and the public catalog of the United States Copyright Office (<a href="http://cocatalog.loc.gov/cgi-bin/Pwebrecon.cgi?DB=local&PAGE=First">http://cocatalog.loc.gov/cgi-bin/Pwebrecon.cgi?DB=local&PAGE=First</a>) to search for records. These records are identified and discussed in this declaration. Experts in the field would reasonably rely on the data described herein to form their opinions.

### **II. EX. 1014 WESTE**

- asked to prepare this declaration, I searched the Library of Congress online catalog for records because books published in the United States tend to be registered with the Copyright Office of the Library of Congress and cataloged by the Library of Congress. The search results informed me that the Library of Congress provided access to Weste. The "Item Availability" area of the library records indicates that the Library of Congress holds one copy of this book, which is "stored offsite" and can be requested in the "Jefferson or Adams Building Reading Rooms." The record I saved on February 26 shows the item status was "c.1 Charged Due (Internal Loan)," meaning it was being used at the time. I requested access to this title later and received the physical volume of copy 1 at the Science and Technology Reading Rooms in the Library of Congress Adams Building on March 1, 2019.

- 13. Ex. 1014 is a true and correct copy of portions of Weste that I made on March 1, 2019, while the book was in my possession at the Library of Congress. I obtained Ex. 1014 by personally scanning the cover, series title page, title page, copyright page, about the author page, preface, table of contents, the last numbered page of the book, back cover, and spine of this book. These pages are presented as Ex. 1014.

- 14. The cover of Ex. 1014 shows that "PRINCIPLES OF CMOS VLSI

DESIGN: A Systems Perspective" is the title, "Neil H. E. Weste" and "Kamran Eshraghian" are the authors, and the publication is the "second edition." The cover also shows a Library of Congress bar code, with the number "00001496268." The series title page of Ex. 1014 shows that the book is in the "Addison-Wesley VLSI Systems Series." The title page of Ex. 1014 shows the same title, authors, and edition number as the information presented on the cover. It also shows that "Addison-Wesley Publishing Company" of Reading, Massachusetts is the publisher. The copyright page of Ex. 1014 carries a stamp of "LIBRARY OF CONGRESS MAY 13 1993 CIP," where CIP stands for Cataloging in Publication. It also shows a block of "Library of Congress Cataloging-in-Publication Data," a hand-written call number of "TK7874 .W46 1993," a copyright date of "1993" held by AT&T. The back cover shows the title's ISBN (International Standard Book Number) is "0-201-53376-6" and the spine of the book has a label of the call number "TK 7874 .W46 1993" and a label of its location "CBN BRNCH GenColl," meaning Cabin Branch general collection.

## A. <u>Library of Congress – Bibliographic and MARC Records</u>

15. Appendix C is a true and correct copy of the Bibliographic record for Weste. I retrieved this record from the Library of Congress online catalog (<a href="https://catlog.loc.gov">https://catlog.loc.gov</a>) after searching for the book by its title, "principles of CMOS VLSI design." I personally identified and located this record, which experts

in my field would reasonably rely upon when forming their opinions.

- 16. Appendix D is a true and correct copy of the MARC record for Weste. I retrieved this record from the Library of Congress online catalog (<a href="https://catlog.loc.gov">https://catlog.loc.gov</a>) after searching for the book by its title, "principles of CMOS VLSI design" and selecting the MARC Tags display. I personally identified and located this record, which experts in my field would reasonably rely upon when forming their opinions.

- Field 245 of the MARC record (**Appendix D**) identify the book title as "Principles of CMOS VLSI design: a systems perspective" and identify "Neil H. E. Weste, Kamran Eshraghian" as the authors. The edition area of the Bibliographic record and Field 250 of the MARC record identify this publication as the "2<sup>nd</sup> ed." The published/created field of the Bibliographic record and Field 260 of the MARC record show that Weste was published by Addison-Wesley Pub. Co. of Reading, Mass. in 1993. The ISBN field of the Bibliographic record and Field 020 of the MARC record show a number of "0201533766," which matches the ISBN on the back cover of **Ex. 1014**. The description field of the Bibliographic record and Field 300 of the MARC record show the book has "xxii" introductory pages, and the last numbered page is page 713, which matches the last numbered page of **Ex. 1014**.

The title, authors, edition number, publisher, publication date, ISBN and pagination recorded in the Bibliographic and MARC records match the information contained in **Ex. 1014**. Field 991 of the MARC record shows a code of "00001496268," which matches the label on the cover of **Ex. 1014**. It also shows the book is in the "GenColl" with a number of "TK7874 .W46 1993," which matches the spine label of **Ex. 1014**.

**18.** The first six digits of Field 008 of the MARC record (**Appendix D**) inform me that the record for the book was first created on "920421" (i.e., April 21, 1992) and Field 955, a field for recording local cataloging dates, shows "CIP ver. pv07 06-16-93" (i.e., June 16, 1993). Field 040 subfield "a" shows that "DLC" is the library that created the original MARC record. According to the Directory of OCLC Members (https://www.oclc.org/en/contacts/libraries.html), "DLC" is the OCLC symbol for the Library of Congress. These data inform my opinion that the MARC record (**Appendix D**) was first created on April 21, 1992, as a Catalogingin-Publication record based on the information presented by the publisher. After the CIP record was completed, it was sent to the publisher for inclusion in the published volume. The block of "Library of Congress Cataloging-in-Publication Data" on the copyright page of Ex. 1014 reflects this practice. That block of data includes a number of "92-16564," which has the appearance of a Library of Congress control number. This number is reflected in the LCCN field of the

Bibliographic record and Field 010 of the MARC record. Following the Cataloging in Publication (CIP) Program agreement, the publisher sent the physical volume to the CIP after the volume was published. CIP catalogers then used the volume to verify the record on June 16, 1993.

- assigned a Library of Congress Classification (LCC) number, "TK7874," which is the class number for "Microelectronics. Integrated circuits." Field 082 shows the Dewey Decimal Classification (DDC) Number assigned to this publication is "621.3/95," which is the class number for "circuity." The subjects of this book are also represented by Library of Congress subject headings in two Field 650s: "Integrated circuits |x Very large scale integration |x design and construction" and "Metal oxide semiconductors, Complementary" (|x represents a topical subdivision). Because the book is in a series, the series title, "The VLSI systems series," is also recorded in Field 440 to make the series title searchable. Field 700 records the authorized form of the second author and makes this author an access point for this book.

- **20.** This MARC record (**Appendix D**) has made Weste (**Ex. 1014**) searchable in the Library of Congress online catalog. As a result, users interested in topics covered by this book can find it by the LCC number, the DDC number, the

subject headings and the series title. In addition, users can find this book by its title, authors, and ISBN.

21. Based on the information above, it is my opinion that PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE (**EX. 1014**) is a book that has been made available by the Library of Congress, meaning that anyone who was interested in the topics covered by the book would have been able to search for and access PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE.

## B. <u>Library of Congress – Date Stamp</u>

22. The copyright page of Weste in Ex. 1014 bears a stamp of "LIBRARY OF CONGRESS MAY 13 1993 CIP" that indicates the date when the Cataloging in Publication Program of the Library of Congress received the physical volume of Weste from the publisher. The stamp has the appearance and distinctive characteristics of a typical check-in date stamp utilized by libraries to indicate the date a particular publication was received by the library. The date stamp and the cataloging dates in Field 955 of the MARC record (Appendix D) inform my opinion that the MARC record was created by Library of Congress catalogers on "920421" (i.e., April 21, 1992) as a CIP record, that the physical volume was received by the CIP Program of the Library of Congress on May 13, 1993, and that CIP catalogers used the physical volume to verify the record on "06-16-1993" (i.e., June 16, 1993). In most academic libraries a newly cataloged book

would have become available for the public soon after the cataloging record is completed, usually within a week. Considering the volume of materials the Library of Congress needs to catalog and process, my conservative estimate is that Weste would have become available for public access by September 16, 1993, three months after the cataloging record was verified.

23. Based on the date stamp placed on the copyright page in Weste (Ex. 1014), which has a date stamp of May 13, 1993, the Bibliographic record (Appendix C), the MARC record (Appendix D), and my understanding of the ordinary and customary cataloging and processing practices of libraries, it is my opinion that Weste (Ex. 1014) was cataloged and became searchable as early as April 1992 when the CIP record was created, and the physical item would have become accessible to the public by September 1993, three months after the cataloging record was verified in June 1993.

## C. <u>United States Copyright – Copyright Registration</u>

24. Appendix E is a true and accurate copy of the copyright registration record obtained from the public catalog of the United States Copyright Office in the Library of Congress. I obtained Appendix E by first accessing the http://www.copyright.gov/ website, selecting the hyperlink "Search Copyright Records," and performing a search by the title on February 26, 2019, to retrieve the record for "Principles of CMOS VLSI design." I personally identified and located

this record, which experts in my field would reasonably rely upon when forming their opinions.

25. The copyright record shows that PRINCIPLES OF CMOS VLSI DESIGN: A SYSTEMS PERSPECTIVE is the title of this book and that "Neil H. E. Weste, Kamran Eshraghian" are the authors. The record identifies the book as the "2<sup>nd</sup> ed." It also shows Addison-Wesley Pub. Co., of Reading, MA as the publisher. It shows the book has a copyright date of 1993 and "AT&T Bell Telephone Laboratories, Inc." as the copyright claimant. The date of creation is "1992," the date of publication is "1993-04-26" (i.e., April 26, 1993) and the copyright registration date is "1993-08-20" (i.e., August 20, 1993). The title, authors, edition number, publisher, publication date and the copyright holder information on the copyright record match the information contained in Ex. 1014. The copyright record also shows that Weste has 713 pages, which matches the last numbered page of this book recorded in Field 300 of the MARC record (**Appendix D**) and is consistent with the page number of the last page of Weste (Ex. 1014), which I personally scanned at the Library of Congress.

## D. Actual Usage

**26.** Actual usage of a publication is reflected by the papers that make reference to it. My research on Google Scholar has identified at least three articles published from 1994 to 1996 that cited PRINCIPLES OF CMOS VLSI DESIGN : A

SYSTEMS PERSPECTIVE (1993). The earliest citing document was published in December 1994. The citations of the citing articles are listed here for easy reference, and these citing articles are attached in **Appendix F**.

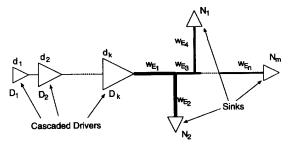

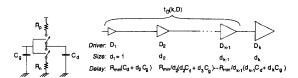

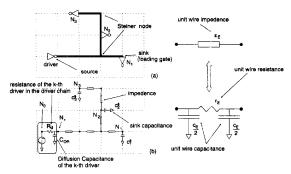

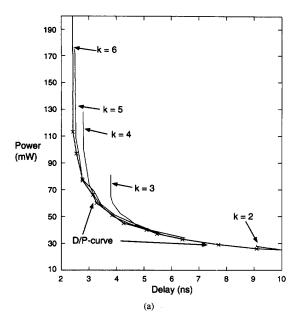

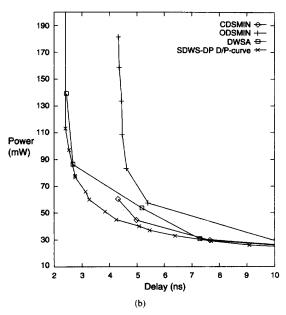

- (1) Cong, J., & Koh, C. K. (1994). Simultaneous driver and wire sizing for performance and power optimization. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2(4), 408-425.

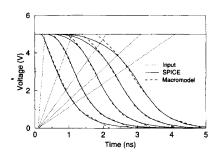

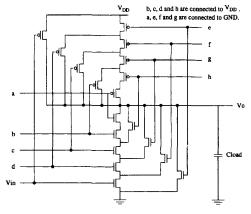

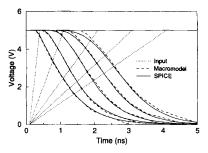

- (2) Kong, J. T., & Overhauser, D. (1995). Methods to improve digital MOS macromodel accuracy. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 14(7), 868-881.

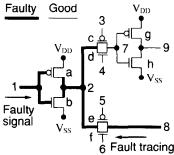

- (3) Nakamae, K., Miura, K., & Fujioka, H. (1996). VLSI testing with CAD-linked electron beam test system. *Microelectronic Engineering*, 31(1-4), 319-330.

- 27. Taken together, the "MAY 13 1993" date stamp on the copyright page of Weste (Ex. 1014), the Bibliographic record (Appendix C), the MARC record (Appendix D), the copyright record (Appendix E), and my understanding of the ordinary and customary cataloging and processing practices of libraries inform my opinion that Weste (Ex. 1014) would have been cataloged and discoverable by the public at the online catalog of the Library of Congress by April 1992 when the CIP cataloging record was created, and the physical item would have been available for public access by September 16, 1993, three months after the CIP record was verified. A person reasonably familiar with library resources and on-line searching

could have found this book through a reasonably diligent search—by title, authors, series, subject classification numbers, and subject headings—on or before that date. The earliest citing document of Weste appeared in December 1994.

#### III. **CONCLUSION**

I hereby declare that all statements made herein on my own 28. knowledge are true and that all statements made on information and belief are believed to be true, and further, that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Date: 3-4-2019 Executed: Ingrid Hsieh-Yee, Ph.D.

## IV. APPENDICES

## APPENDIX A

## **Ingrid Hsieh-Yee**

Professor

Dept. of Library and Information Science

Catholic University of America

Washington, D.C. 20064

E-mail: hsiehyee@cua.edu

Phone: (202) 319-5085 Fax: (202) 319-5574

#### **Education**

- Ph.D. Library and Information Studies, University of Wisconsin-Madison Minors: Sociology and Psychology

- M.A. Library and Information Studies, University of Wisconsin-Madison.

- M.A. Comparative Literature, University of Wisconsin-Madison.

- B.A. Foreign Languages and Literature, National Taiwan University.

## **Work Experience**

- Professor, School/Dept. of Library and Information Science, Catholic University of America, 2004- (Assistant Professor, 1990-1996; Associate Professor, 1997-2004)

- Co-Chair, Dept. of Library and Information Science, Catholic University of America, June 2015-August 2016.

- Acting Dean, School of Library and Information Science, Catholic University of America, January 2010-June 2012.

- Cataloger, Dept. of Legislative Reference Library, Annapolis, Maryland, 1989-1990.

- Lecturer, School of Library and Information Studies, University of Wisconsin-Madison, 1988.

- Teaching Assistant, School of Library and Information Studies, University of Wisconsin-Madison, 1986-1988.

Cataloger, Health Sciences Library, University of Wisconsin-Madison, 1984-1986.

## **Areas of Teaching and Research Interests**

Information Organization and Access; Metadata; Cataloging & Classification; Information Architecture; Information Retrieval; Digital Collections; Scholarly Communication; Information

#### **Grants & Honors**

- Cultural Heritage Information Management Project. IMLS grant. Amount: \$498,741. Period: Aug. 2012 to July 2015. Co-PI with Dr. Youngok Choi.

- D.C. Health Information Technology (HIT4): Building Capacity & Providing Access in Our Nation's Capital. Dept. of Labor H2B Training Grant. Grant amount: \$4,175,500. Grant period: Nov. 2011 to Dec. 2015. Partner with the Metropolitan School of Professional Studies of the Catholic University of America, Children's National Medical Center, D.C. Department of Employment Services, Holy Cross Hospital, Howard University, Center for Urban Progress, Providence Hospital, and Sibley Memorial Hospital.

- Capital Health Careers Project. Department of Labor Healthcare Sector and Other High Growth and Emerging Industries Grant. Grant amount: \$4,953,999. Grant period: March 2010 February 2013. Awarded to a group of healthcare organizations and educational institutions in Washington, D.C. Providence Health Foundation of Providence Hospital (Lead institution). Part of the grant supported the development of a Master's degree program in Information Technology with a concentration in Health Information Technology offered by the School of Library and Information Science.

- The Washington D.C. School Librarians Project. IMLS grant. Grant amount: \$412,660. Grant period: Aug. 2007 June 2011. The School partnered with the District of Columbia Public Schools (DCPS) and the District of Columbia Library Association to educate and mentor school media specialists for the DCPS system. PI, Jan. 2010 to June 2011.

SIG Member of the Year, American Society for Information Science and Technology (2009).

Most Outstanding Paper of OCLC Systems & Services (2001).

ALISE Research Grant (2001).

Most Outstanding Paper of OCLC Systems & Services (2000).

Research Grant from ERIC (1999-2000).

Best Research Paper Award; Association for Library and Information Science Education (1998).

Research Grants, Catholic University of America. 1991, 1992, 1993, 1996, 1998, 1999, 2004, 2005, 2006, 2007, 2013-14.

Cooperative Faculty Research Grant, Consortium of Universities in the Washington Metropolitan Area (1993-1994).

Cooperative Research Grant, Council on Library Resources (1993-1994).

Journal of the American Society for Information Science Best Paper Award (1993).

ASIS/ISI Information Science Doctoral Dissertation Scholarship (1989).

HEA Title IIB Fellowship (Dept. of Education) (1989)

Chinese-American Librarians Association Scholarship (1987).

Beta Phi Mu (1985).

Vilas Fellowship, University of Wisconsin-Madison. 1984

#### **Publications**

- Choi, Y., and Hsieh-Yee, I. (2010). Finding Images in an OPAC: Analysis of User Queries, Subject Headings, and Description Notes. *Canadian Journal of Information and Library Science*, 34(3): 271 295.

- Hsieh-Yee, I. (2008). Educating Cataloging Professionals in a Changing Information Environment. *Journal of Education for Library and Information Science*, 46(2): 93-106.

- Vellucci, S. L., Hsieh-Yee, I., and Moen, W.E. (2007). The Metadata Education and Research Information Commons (MERIC): A Collaborative Teaching and Research Initiative. *Education for Information*, 25(3&4): 169-178.

- NISO Framework for Guidelines for Building Good Digital Collections. 3<sup>rd</sup> ed. Baltimore, MD: National Information Standards Organization, 2007. Also available online: <a href="http://www.niso.org/framework/framework3.pdf">http://www.niso.org/framework/framework3.pdf</a> (NISO Working Group members: Priscilla Caplan (chair), Grace Agnew, Murtha Baca, Tony Gill, Carl Fleischhauer, Ingrid Hsieh-Yee, Jill Koelling, and Christie Stephenson.)

- Choi, Y., Hsieh-Yee, I., and Kules, B. (2007). Retrieval Effectiveness of TOC and LCSH. *Proceedings of the Joint Conference on Digital Libraries*, pp. 233-234.

- Vellucci, S., and Hsieh-Yee, I. (2007). They Didn't Teach Me That in Library School! Building a Digital Teaching Commons to Enhance Metadata Teaching, Learning and Research. *Proceedings of the National Conference of the Association of College and Research Libraries, Baltimore, MD*, pp. 26-31.

- Mitchell, Vanessa, and Ingrid Hsieh-Yee. (2007). Converting Ulrich's Subject Headings to FAST Headings: A Feasibility Study. *Cataloging & Classification Quarterly*, 45(1): 59-85.

- Hsieh-Yee, I., Tang, R., and Zhang, S. (2007). User Perceptions of a Federated Search System. *IEEE Technical Committee on Digital Libraries Bulletin*, Summer 3(2) (URL = http://www.ieee-tcdl.org).

- Tang, R., Hsieh-Yee, I., and Zhang, S. (2007). User Perceptions of MetaLib Combined Search: An Investigation of How Users Make Sense of Federated Searching." *Internet Reference Services Quarterly*, 12(12): 211-236.

- Hsieh-Yee, I., Tang, R., and Zhang, S. (2006). User Perceptions of a Federated Search System. *Proceedings of the Joint Conference on Digital Libraries, June 11-15, 2006, Chapel Hill*, p. 338.

- Hsieh-Yee, I. (2006). Organizing Audiovisual and Electronic Resources for Access: A Cataloging Guide. 2nd ed. Westport, Conn.: Libraries Unlimited.

- NISO A Framework of Guidance for Building Good Digital Collections. 2nd ed. Bethesda, MD: National Information Standards Organization, 2004. Framework Advisory Group: Grace Agnew, Liz Bishoff, Priscilla Caplan (Chair), Rebecca Gunther and Ingrid Hsieh-Yee.

- Hsieh-Yee, I. (2004). Cataloging and Metadata Education in North American LIS Programs. *Library Resources & Technical Services*, 48(1): 59-68.

- Hsieh-Yee, I. (2004). Cataloging and Metadata Education. In Gary E. Gorman (Ed.), International Yearbook of Library and Information Management 2003: Metadata Applications and Management, (pp.204-234). London: Facet Publishing.

- Yee, P. L., Hsieh-Yee, I., Pierce, G.R., Grome, R., and Schantz, L. (2004). Self-Evaluative Intrusive Thoughts Impede Successful Searching on the Internet. *Computers in Human Behavior*, 20(1): 85-101.

- Hsieh-Yee, I. (2003). Cataloging and Metadata Education: A Proposal for Preparing Cataloging Professionals of the 21st Century. A report submitted to the ALCTS-Education Task Force in response to Action Item 5.1 of the *Bibliographic control of Web Resources: A Library of Congress Action Plan*. Approved by the Association for Library Collections and Technical Services. Web version available since April 2003 at <a href="http://lcweb.loc.gov/catdir/bibcontrol/CatalogingandMetadataEducation.pdf">http://lcweb.loc.gov/catdir/bibcontrol/CatalogingandMetadataEducation.pdf</a>.

- Hsieh-Yee, I. (2002). Cataloging and Metadata Education: Asserting a Central Role in Information Organization. *Cataloging & Classification Quarterly* 34(½): 203-222.

- Hsieh-Yee, I., and Smith, M. (2001). The CORC Experience: Survey of Founding Libraries, Part I. *OCLC Systems & Services*, 17: 133-140. (Received "The Most Outstanding Paper of OCLC Systems & Services in 2001" award.)

- Hsieh-Yee, I., and Smith, M. (2001). The CORC Experience: Survey of Founding Libraries, Part II, Automated Tools and Usage. *OCLC Systems & Services*, 17: 166-177. (Received "The Most Outstanding Paper of OCLC Systems & Services in 2001" award.)

- Hsieh-Yee, I. (2001). ERIC User Services: Changes and Evaluation for the Future. *Government Information Quarterly*, 18: 31-42.

- Hsieh-Yee, Ingrid. (2001). Research on Web Search Behavior. *Library and Information Science Research*. 23: 167-185.

- Logan, E., and Hsieh-Yee, I. (2001). Library and Information Science Education in the Nineties. *Annual Review of Information Science and Technology*, 35: 425-477.

- Hsieh-Yee, I. (Ed.) (2001). *Library and Information Science Research*, 23 (2). A special issue in honor of the retirement of Douglas L. Zweizig.

- Hsieh-Yee, I. (2000). *ERIC User Services: Evaluation in a Decentralized Environment*. Washington, D.C.: Dept. of Education.

- Hsieh-Yee, Ingrid. (2000). Organizing Audiovisual and Electronic Resources for Access: A Cataloging Guide. Littleton, CO: Libraries Unlimited.

- Hsieh-Yee, I. (2000). Organizing Internet Resources: Teaching Cataloging Standards and Beyond. *OCLC Systems & Services*, 16: 130-143. (Received "The Most Outstanding Paper of OCLC Systems & Services in 2000" award.)

- Hsieh-Yee, I. (1998). The Retrieval Power of Selected Search Engines: How Well Do They Address General Reference Questions and Subject Questions? *Reference Librarian*, 60: 27-47.

- Hsieh-Yee, I. (1998). Search Tactics of Web Users in Searching for Texts, Graphics, Known Items and Subjects: A Search Simulation Study. *Reference Librarian*, 60: 61-85. (Received the 1997 Best ALISE Research Paper Award.)

- Hsieh-Yee, I. (1997). Access to OCLC and Internet Resources: LIS Educators' Views and Teaching Practices. *RQ*, 36: 569-86.

- Hsieh-Yee, I. (1997). Teaching Online and CD-ROM Resources: LIS Educators' Views and Practices. *Journal of Education for Library and Information Science*, 38: 14-34.

- Hsieh-Yee, I. (1996). The Cataloging Practices of Special Libraries and Their Relationship with OCLC. *Special Libraries*, 87: 10-20.

- Hsieh-Yee, I. (1996). Modifying Cataloging Practice and OCLC Infrastructure for Effective Organization of Internet Resources. In *Proceedings of the OCLC Internet Cataloging Colloquium*. [Online]. Available: http://www.oclc.org/oclc/man/colloq/hsieh.htm

- Hsieh-Yee, I. (1996). Student Use of Online Catalogs and Other Information Channels. *College & Research Libraries*, 57: 161-175.

- Hsieh-Yee, I. (1995). Ten entries in James S. C. Hu (Ed.), *Encyclopedia of Library & Information Science*, 913, 1028-29, 1036, 1037, 1145-46, 1514, 1575, 1763-64, 2216-27, 2378-79. Taipei, Taiwan: Sino-American Publishing. (Topics include "Advanced Technology/Libraries," "Information Ethics," "Instruction on Cataloging and Classification," "Instruction on Reference Services.")

- Hsieh-Yee, I. (1993). Effects of Search Experience and Subject Knowledge on Online Search Behavior: Measuring the Search Tactics of Novice and Experienced Searchers. *Journal of the American\_Society for Information Science*, 44: 161-174. (Received the 1993 Best JASIS Paper Award.)

#### **Presentations**

- Hsieh-Yee, I. and Fragan-Fly, J. (May 2018) Trends, Design & Strategies for Digital Scholarship Services. Presented at the 2018 Maryland/Delaware Library Association Conference, Cambridge, MD.

- Hsieh-Yee, I. (February, 2018) Research Data Management: What It Takes to Succeed. Presented at the 10<sup>th</sup> Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I. (February, 2017) Research Data Management: New Competencies and Opportunities for Information Professionals. Presented at the 9th Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I. and Lawton, P. (February, 2017) *Enhancing Catholic Portal Searches with User Terms and LCSH*. Presented at the 9th Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I. (2016, October) *Visualizing Data for Information*. Presented at the 2016 Virginia Library Association Conference, Hot Springs, VA.

- Hsieh-Yee, I. (2016, August) *Religious Materials Toolbox for Archivists: Solutions to Problems Facing the Profession.* Presented at Archives \* Records 2016, Atlanta, GA.

- Hsieh-Yee, I. and Lawton, P. (2016, March) *Enhancing Retrieval of Catholic Materials with LCSH Knowledge Structure*. Presented at the 2016 Catholic Library Association Conference, San Diego, CA.

- Fagan-Fry, J. and Hsieh-Yee, I. (2016, February) *Approaches to Digital Scholarship at Top Universities around the World: Scholarly Publishing in the Digital Age.* Presented at the 8th Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee and Fagan-Fry, J. (2016, January) *Innovative Services for Digital Scholarship at Top 100 Research Libraries of the World*. Poster presented at the 2016 Annual Conference of the Association for Library and Information Science Education, Boston, Mass.

- Hsieh-Yee, I. and Lawton, P. (2015, June). *Crowdsourcing terms for CRRA portal themes.* Poster presented at the third CRRA symposium and annual meeting, Bringing the created toward the Creator: Liturgical art and design since Vatican II. Catholic Theological Union, Chicago, Illinois.

- Hsieh-Yee, I. and Lawton, P. (2015, February). *Crowdsourcing terms for thematic exploration in the Catholic Portal*. Poster presented at the 7<sup>th</sup> Annual Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I., James, R., and Fagan-Fry, J. (2015, February). *Support for digital scholarship at top university libraries of the world*. Poster presented at the 7<sup>th</sup> Annual Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I., Zhang, S., Lin, K., and Cherry, S. (2015, February). *Thus said the end users:* Summon experience and support for research workflows. Poster presented at the 7<sup>th</sup> Annual Bridging the Spectrum Symposium, Washington, D.C.

- Yontz, E., Hsieh-Yee, I., & Houston, S. (2015, February). *Healthy Heroes Summer Reading Club: Developing healthy youth at public libraries*. 11th Annual Jean Mills Health Symposium, Greenville, North Carolina.

- Yontz, E., Hsieh-Yee, I., and Houston, S. (2015, January). *Healthy youth and libraries: A pilot study*. Association for Library & Information Science Education (ALISE) Annual Conference, Chicago, Illinois.

- Hsieh-Yee, I. (2014, May). *Linking CRRA resources to portal themes via authority files*. Presented at the Catholic Research Resources Alliance 2014 Membership Meeting, Marquette, WI.

- Hsieh-Yee, I. (2014, April). *Enhancing subject access to CRRA resources*. Presented at the 2014 Catholic Library Association Conference, Pittsburgh, PA.

- Hsieh-Yee, I. (2014, January). *Health Information Technology Program: Educational entrepreneurship in action*. Presented at the 2014 annual Conference of the Association for Library and Information Science Education, Philadelphia, PA

- Hsieh-Yee, I., Zhang, S., Lin, K., and Cherry, S. (2014, January). *Discovering information through Summon: An analysis of user search strategies and search success*. Paper presented at the 6th Bridging the Spectrum Symposium, Washington, D.C.

- Hsieh-Yee, I. (2012, December). *National Digital Stewardship Alliance and SLIS at CUA: An Educational Partnership.* Paper presented at Best Practices Exchange: Acquiring, Preserving, and Providing Access to Government Information in the Digital Era, Annapolis, MD

- Choi, Y. and Hsieh-Yee, I. (2010, January). *Finding Images in an OPAC: Analysis of User Queries, Subject Headings, and Description Notes.* Paper presented at 2<sup>nd</sup> Annual Bridging the Spectrum Symposium, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I. and Coogan, J. (2010, January). *Google Scholar vs. Academic Search Premier: What Libraries and Searchers Need to Know.* Paper presented at 2<sup>nd</sup> Annual Bridging the Spectrum Symposium, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I. (2009, November). *Information Science Education: An LIS School's Perspective*. Paper presented at Annual Meeting of the American Society for Information Science and Technology, Vancouver, British Columbia, Canada.

- Hsieh-Yee, I., Menard, E., Ya-Ning Chen, A., Shu-Jiun Chen, S., Kalfatovic, M. R., Wisser, K. M. (2009, November). *Information Organization in Libraries, Archives and Museums:*Converging Practices and Collaboration Opportunities. Presented at Annual Meeting of the American Society for Information Science and Technology, Vancouver, British Columbia, Canada. (Organizer and moderator of this panel.)

- Hsieh-Yee, I. and Coogan, J. (2009, July). *Catching up to Google Scholar: The Retrieval Power of Academic Search Premier and Google Scholar*. Poster presented at American Library Association Conference, Chicago, Illinois.

- Hsieh-Yee, I., with the CUA Scholarly Communications Project Team. (2009, January). *Digital Scholarship@CUA: Developing an Institutional Repository for CUA*. Poster presented at 1<sup>st</sup> Annual Bridging the Spectrum Symposium, Catholic University of America, Washington, D.C.

- Wise, M., Cylke, K., and Hsieh-Yee, I. (2009, January). *Digital Talking Books: Meeting the Needs of the Blind and the Handicapped*. Paper presented at the Bridging the Spectrum Symposium, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I. (2009, January). *User Expectations of MERIC*. Presented at the Information Organization Competencies for the 21st Century Discussion Session of the 2009 Conference of the Association for Library and Information Science Education, Denver, Colorado.

- Choi, Y., and Hsieh-Yee, I. (2008,November). *Subject Access for Images in an OPAC*. Annual Meeting of the American Society for Information Science and Technology, Columbus, Ohio. (Also co-organized a panel on Retrieving and Using Visual Resources: Challenges and Opportunities for Research and Education.)

- Hsieh-Yee, I. (2008, June). Educating Cataloging Professionals in a Changing Information Environment. National Taiwan University, Taipei, Taiwan.

- Vellucci, S. L., Moen, W.E., Hsieh-Yee, I., Marson, B., and Wisser, K. (2008, January) Building a Metadata Education and Research Community through MERIC (Metadata Education and Research Information Commons): Demo and Stakeholder Input. A panel presented at the 2008 Conference of the Association for Library and Information Science Education, Philadelphia, Pennsylvania.

- Hsieh-Yee, I., Choi, Y. and Kules, B. (2007, October). Searching for Books and Images in OPAC: Effects of LCSH, TOC and Subject Domains. A poster presented at the American Society for Information Science and Technology Annual Meeting, Milwaukee, Wisconsin.

- Hsieh-Yee, I. and Coogan, J. (2007, August) *Google Scholar vs. Academic Search Premier: A Comparative Analysis.* Presented to the Faculty and Staff of the University of the District of Columbia.

- Hsieh-Yee, I. and Coogan, J. (2007, June). *Google Scholar vs. Academic Search Premier: A Comparative Analysis*. Presented to the Washington Research Library Consortium Community, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I., Choi, Y., and Kules, B.. (2007, June). What Users Need for Subject Access: Table of Contents or Subject Headings? A poster presented at the 2007 American Library Association Annual Conference, Washington, D.C., June 2007.

- Choi, Y., Hsieh-Yee, I., and Kules, B. (2007, June). *Retrieval Effectiveness of TOC and LCSH*. A paper presented at the Joint Conference on Digital Libraries 2007, Vancouver, Canada.

- Vellucci, S. L., Hsieh-Yee, I., and Moen, W.E. (2007, May). *If We Build It, Will They Come? Building a Community of Practice for Metadata Stakeholders.* A poster presented at the Rutgers University Research Day, Bridgeton, New Jersey.

- Hsieh-Yee, I. (2007, May). Federated Searching: User Experience & Perceptions. International Conference on Information Organization & Retrieval, National Taiwan University, Taipei, Taiwan.

- Hsieh-Yee, I. (2007, May). Search Performance of Google Scholar and Academic Search Premier. International Conference on Information Organization & Retrieval, National Taiwan University, Taipei, Taiwan.

- Hsieh-Yee, I. (2007, May) *MERIC: Building a Digital Commons for Metadata Education & Research*. International Conference on Information Organization & Retrieval, National Taiwan University, Taipei, Taiwan.

- Hsieh-Yee, I., and Coogan, J. (2007, March/April). *A Comparative Analysis of Google Scholar and Academic Search Premier*. Poster presented at the Association of College & Research Libraries 13th National Conference, Baltimore, Maryland.

- Vellucci, S. L. and Hsieh-Yee, I. (2007, March/April) *They Didn't Teach Me That in Library School! Building a Digital Teaching Commons to Enhance Metadata Teaching, Learning and Research*. On-site presentation and Webcast by Elluminate. A contributed paper presented at the Association of College & Research Libraries 13th National Conference, Baltimore, Maryland. The acceptance rate for contributed paper was 20%. This paper was one of 10 conference papers chosen for live webcast during the conference.

- Moen, W., Hsieh-Yee, I. and Vellucci, S.L. (2007, January) *A DSpace Foundation for a Teaching & Research Commons: The Metadata Education and Research Information Commons.* A poster session presented at the Open Repositories Conference 2007, San Antonio, Texas.

- Tang, R., Hsieh-Yee, I., and Zhang, S. (2006, November) *User Perception of MetaLib Combined Search*. Paper presented at the Annual Meeting of the American Society for Information Science and Technology, Austin, Texas, Nov. 2006.

- Hsieh-Yee, I. (2006, November). Federated Searching: User Perceptions, System Design, and Library Instructions. Paper presented at the Annual Meeting of the American Society for Information Science and Technology, Austin, Texas. (Panel organizer, moderator, presenter).

- Hsieh-Yee, I. (2006, November). Building a Digital Teaching Commons to Enhance Teaching and Learning: The MERIC Experience and Challenges. Paper presented at the Annual Meeting of the American Society for Information Science and Technology, Austin, Texas. (Panel organizer, moderator, presenter)

- Hsieh-Yee, I. (2006, September). *Search Performance of Google Scholar and Academic Search Premier*. Paper presented at the ERIC Publishers Meeting, Washington, D.C.

- Hsieh-Yee, I., Zhang, S., and Rong Tang, R. (2006, June). *User Perceptions of a Federated Search System*. Poster presented at Joint Conference on Digital Libraries, Chapel Hill, North Carolina.

- Hsieh-Yee, I. and Zhang, S. (2006, June). *Preparing Users for Federated Search: Implications of a MetaLib User Perceptions Study*. Paper presented at the 2006 Ex Libris User Groups of North America Conference, Knoxville, Tennessee.

- Hsieh-Yee, I. (2006, January). *MERIC Organizations and Navigation*. Paper presented at the 2006 ALISE Annual Conference, San Antonio, Texas.

- Hsieh-Yee, I. (2006, January). *Metadata and Cataloging Education: Recommended Competencies*. Paper presented at the 2006 ALISE Annual Conference, San Antonio, Texas.

- Hsieh-Yee, I. (2005, November). *Digital Library Evaluation: Progress & Next Steps*.

Presentation at the Annual Meeting of the American Society for Information Science & Technology, Charlotte, North Carolina.

- Hsieh-Yee, I. (2005, August). *Providing Access to Digital Content: Issues for DL Managers*. Presentation at MDK12 Digital Library Steering Committee Meeting, Columbia, Maryland.

- Hsieh-Yee, I. (2005, April). *Enhancing Teaching and Learning: The Role of School Library Media Specialists*. Presentation at Meeting of the Baltimore County Public School System School Media Specialists, Baltimore, Maryland.

- Hsieh-Yee, I. (2005, January). Subject Access and Users: Insights & Inspirations from Marcia J. Bates. Paper presented at the Historical Perspectives SIG, 2005 Conference of the Association for Library and Information Science Education, Boston, Massachusetts.

- Hsieh-Yee, I. (2005, January). *Electronic Resource Management: Practice, Employer Expectations, & CE Interests.* Paper presented at Technical Services Education SIG, 2005 Conference of the Association for Library and Information Science Education, Boston, Massachusetts.

- Hsieh-Yee, I. (2004, October). *Library Professionals for the Digital Age: Competencies & Preparation.* Paper presented at Bibliographic Access Management Team meeting, Library of Congress, Washington, D.C.

- Hsieh-Yee, I. (2004, January). *Cataloging and metadata expertise for the digital era*. Presented at Preparing 21<sup>st</sup> Century Cataloging and Metadata Professionals: A Workshop for Educators and Trainers, San Diego and sponsored by ALCTS, ALISE, LC, and OCLC.

- Hsieh-Yee, I. (2004, January). *Educating catalogers for the digital era*. Paper presented at the Technical Services SIG, 2004 Conference of the Association for Library and Information Science Education, San Diego.

- Hsieh-Yee, I. (2003, July). *Cataloging Education for the 21<sup>st</sup> Century*. A presentation at the Library of Congress, Washington, D.C.

- Hsieh-Yee, I. (2002, January) Metadata Education and Research Priorities: A Delphi Study of

- *Metadata Experts.* Presentation at the 2002 Conference of the Association for Library and Information Science Education, New Orleans.

- Hsieh-Yee, I. (2001, November). *A Delphi Study of Metadata: Preliminary Findings*. Poster session at the 2001 Annual Meeting of the American Society for Information Science & Technology, Washington, D.C.

- Hsieh-Yee, I. (2001, June). Resources on Asian American Children: Analysis of Retrieval by Search Engines and WorldCat. Presentation at the National Conference on Asian Pacific American Librarians, San Francisco.

- Hsieh-Yee, I. (2001, January). *Delphi Study on Metadata: Project Design*. Presentation at Research Awards Session, Association for Library & Information Science Education, Washington, D.C.

- Hsieh-Yee, I. (2000, May). Web Search Behavior Research: Progress and Implications.

Presentation at the Symposium on Evaluating Library and Information Science Research,

University of Wisconsin-Madison, Madison, Wisconsin.

- Hsieh-Yee, I. (2000, March). *ERIC User Services: Evaluation in a Decentralized Environment*. Presentation at the National ERIC Joint Directors/Technical Meeting, Arlington, Virginia.

- Hsieh-Yee, I. (2000, January). *Enhancing Learning with Web Technology*. Presentation at Faculty Conversations, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I. (2000, January). From Surrogates to Objects: CUA's Approaches to Organizing Electronic Resources. Paper presentation at the Annual Conference of the Association for Library and Information Science Education, San Antonio, Texas.

- Yee, P., and Hsieh-Yee, I. (1997, November). *Individual Differences in Search Behavior on the WWW*. A poster session presented at the 38th Annual Meeting of the Psychonomic Society, Philadelphia, Pennsylvania.

- Hsieh-Yee, I. (1997, April). *Research + Marketing + Preparation = Job!* Presented at the "Workshop on Resume and Interview Techniques," Special Libraries Association, Student Chapter, Catholic University of America, Washington, D.C.

- Hsieh-Yee, I. (1997, February). *Creating CyberCatalogers: Education and Training*. Presentation at ALA's Midwinter Meeting, Washington, D.C.

- Hsieh-Yee, I. (1997, February). Search Tactics of Web Users in Searching for Texts, Graphics, Known Items and Subjects: A Search Simulation Study. Presented at the Conference of the Association for Library and Information Science Education, Washington, D.C.

- Hsieh-Yee, Ingrid. "Beginning Your Special Library/Information Center Career." Presented at SLA's "Career Day," Jan. 11, 1997, Catholic University of America.

- Hsieh-Yee, I. (1996, September). *The Roles of Library and Information Scientists in Managing Electronic Information*. Presentation at Hamilton College, Clinton, New York.

- Hsieh-Yee, I. (1996, May). *The Future of Cataloging as a Profession*. Presented at "The Cataloging Forum, Library of Congress, Washington, D.C.

- Hsieh-Yee, I. (1994, October). *The Impact of the Internet on OPACs*. Presented at the Third Workshop on User Interfaces for OPACs, Library of Congress, Washington, D.C.

## **Reports**

- Hsieh-Yee, I., with Knowledge Management Competencies and Performance Action Group of the Federal Knowledge Management Initiative. "From Knowledge Management Competencies to Improved Organizational Performance." April 9, 2009.

- Hsieh-Yee, I., with Knowledge Practices Action Group of the Federal Knowledge Management Initiative. "KM Practice in Government Agencies: Findings and Recommendations." April 9, 2009.

- Hsieh-Yee, I. "Delphi Study on Metadata." 2001. Three quarterly reports submitted to the Association for Library and Information Science Education.

- Hsieh-Yee, I. "College Students' Information Channels: Patterns of Use and Possible Factors in Channel Selection." 1995. Submitted to the Catholic University of America.

- Hsieh-Yee, I. "The Information-Seeking Patterns of Scholars and Their Use of an Online Information System." 1994. Submitted to the Council on Library Resources.

#### **Book Reviews**

- Review of *The Measurement and Evaluation of Library Services*, by Sharon L. Baker and F. Wilfrid Lancaster. *Information Processing and Management* 30 (1994): 450-52.

- Review of Subject Access to Films and Videos, by Sheila S. Intner and William E. Studwell; and Cataloging Unpublished Nonprint Materials, by Verna Urbanski with Bao Chu Chang and Bernard L. Karon. Information Processing and Management 30 (1994): 449-50.

- Review of Automated Information Retrieval in Libraries: A Management Handbook, by Vicki Anders. Journal of Library and Information Science 19 (1993): 98-100.

- Review of *Full Text Databases*, by Carol Tenopir and Jung Soon Ro. *Information Processing and Management* 28 (1992): 667-68.

- Review of Descriptive Cataloging for the AACR2R And USMARC: A How-to-Do It Workbook, by Larry Millsap and Terry Ellen Ferl. Information Processing and Management 28 (1992): 809-11.

- Review of MARC Manual: Understanding and Using MARC Records, by Deborah J. Byrne. Information Processing and Management 28 (1992): 537-38.

#### Service

#### **Professional Associations and Societies**

- Library of Congress. RDA Training Program for the Profession. Co-authored with Tim Carlton. 2013-2014.

- 2014 Digital Preservation Outreach & Education Survey. Contributed to the design of the survey, 2014.

- National Digital Stewardship Alliance. Outreach Committee. 2011-2014.

- National Digital Stewardship Residency Program. Advisory Group, 2012-2013.

- FEDLINK Health Information Technology Advisory Council, 2011-2015.

- 2012 Joint Conference on Digital Libraries. Program Planning Committee, Pre-Conference Proposals Review Committee, 2012

- Catholic Research Resources Alliance. Five-Year Strategic Plan Task Force, 2011-2012

- Institute of Museum and Library Services. Grant reviewer. 2004, 2005, 2010.

- Association for Library and Information Science Education.

- \* ALISE Bodan Wynar Research Paper Award Committee, 2015, 2016, 2017

- \* ALISE Eugene Garfield Dissertation Award Competition, Jury, 2013, 2014

- \* ALISE Research Grant Competition Committee. Chair, 2012

- \* Pratt-Severn Faculty Innovation Award. Chair, 2009, 2010

- \* ALISE Doctoral Poster Jury, 2012

- \* "Information Organization Competencies for the 21st Century" Discussion session leader. 2009 Conference of the Association for Library and Information Science Education.

- \* Assisted Technical Services SIG Convener in organizing a program, ""Building a Metadata Education and Research Community through MERIC (Metadata Education and Research Information Commons): Demo and Stakeholder Input" for the 2008 ALISE conference.

- \* Association for Library Collections and Technical Services/Association for Library and Information Science Education (ALCTS/ALISE) Metadata Education and Research Information Center (MERIC) Advisory Board, Co-Chair (with Sherry Vellucci), 2005-2007. Chair, 2008-2009 (leading the effort to build MERIC, a repository and collaborative space for metadata educators, practitioners, and researchers)

- \* Technical Services SIG, Convener, 2004-2005. Organized a program on "Electronic Resources Management: Current Practices, Employer Expectations, and Teaching Strategies" for the 2005 conference in Boston, Massachusetts.

- \* Technical Services SIG, Convener, 2003-2004. Organized a program on "Organizing Information with Metadata: Desired Competencies and Teaching Innovations" for the 2004 conference.

- \* Technical Services SIG, Convener, 1999-2000. Organized a program on "Teaching the Organization of Electronic Resources" for the 2000 conference.

- \* Curriculum SIG, Co-convener (with Sibyl Moses), 1996-97. Organized a program on "Government Information Policy" for the 1997 conference.

- American Society for Information Science & Technology.

- \* Reviewer, Conference program panel submissions and poster submissions, 2005, 2006, 2007, 2009, 2011, 2012, 2013, 2014, 2015, 2016, 2017

- \* Nomination Committee, 2009-2011

- \* Information Science Education Special Interest Group. American Society for Information Science and Technology. Chair-Elect, 2007-2008. Chair 2008-2009.

- \* Committee on Information Science Education. 1999-2006.

- \* Committee on Information Science Education. Organizing Committee for an orientation program for students at ASIS annual meetings, 1999-2001

- \* Committee on Information Science Education. Sub-committee on Student Welfare (focusing on issues related to master's education), 1998-2001

- \* SIG ED. Organizing Committee for the "Seminar on Research and Career Development" for junior researchers. 1995-96 (chair), 1997-2001

- \* ISI Doctoral Dissertation Proposal Scholarship Jury, 1997; 2001, 2002

- \* Pratt-Severn Best Student Research Paper Award Jury. Chair. 1997

- \* 1998 Midyear Meeting (referee of contributed papers), 1997

- \* Organizer and moderator of the ASIS Doctoral Forum and the Doctoral Research Seminar 1994-1995

- \* SIG Human Computer Interaction. Chair-Elect, Chair, 1993-1995

- \* Doctoral Forum Award Jury, 1995

- \* Best Student Paper Award Jury, 1995

- American Library Association.

- \* Committee on Accreditation, External Review Panelist, 2009- (site visiting team 2013-2014; site visiting team 2016-2017)

- \* Association for Library Collections and Technical Services Task Force on Competencies and Education for a Career in Cataloging, member, 2008-2009

- \* Facilitator for "What They Don't Teach in Library School: Competencies, Education and Employer Expectations for a Career in Cataloging," an Association for Library Collections and Technical Services Preconference, June 22, 2007 in Washington, D.C. Also a local liaison for bringing this program to the Catholic University of America.

- \* Facilitator for a discussion on "Effect of Electronic Resources on Technical Services" at ALA's Midwinter Meeting held in Feb. 1997 in Washington, D.C.

- \* International Relations Committee, Subcommittee Task Force for IFLA and China, 1994-1997

- Virginia Association of School Librarians. Scholarships and Awards Committee. 2010-2012

- Federal Knowledge Management Initiative, Knowledge Management Practices Action Group. Member. 2009 (leading the effort to build a knowledge management repository)

- Federal Knowledge Management Initiative, Knowledge Management Competencies & Learning Action Group. Member. 2009 (developing an action plan for helping government knowledge workers and government agencies to develop knowledge management competencies)

- National Center for Education Statistics. Technical Review Panel. 2008.

- External evaluator for a case of promotion to full professorship. University of Tennessee. 2008.

- National Information Standards Organization (NISO). Advisory Board, Revision of "IMLS Framework of Guidance for Building Good Digital Collections," 2004, 2007.

- Library of Congress, Bibliographic Control of Web Resources: A Library of Congress Action Plan. Principal Investigator of Action Item 5.1, focusing on cataloging and metadata education for students and new librarians, 2002-2003. (worked with the Association for Library Collections and Technical Services, Education Task Force)

- Chinese American Librarians Association

- \* Chinese American Librarians Association Outstanding Library Leadership Award in Memory of Dr. Margaret Chang Fung, Award Committee, 2016-2017

- \* Achievement Award Jury, 2000-2001

- \* CALA Goal 2000 Task Force, 1997

- \* Scholarship Committee, 1995, 1996-1997 (chair)

- \* Board of Directors, 1994-1997

- \* Publication Committee, 1993-1995

- \* International Relations Committee, 1993-1996

- Sailor<sup>SM</sup> Assessment Advisory Group (An impact study of Sailor, Maryland's Public Information Network), 1995

- Editorial boards

Journal of Library and Information Science. Editorial Board, 2012-

Chinese American Librarians Association, *Occasional Papers Series*. Editorial Board, 2009-2016.

Library Quarterly. Editorial Board, 2003-2008

Bulletin of the Medical Library Association, 1994-97

Newsletter editor for the Chinese American Librarians Association, 1989-92

• Referee for the following journals

Information Processing and Management

Journal of Digital Information

Journal of Education for Library and Information Science

Journal of Information Science

Journal of Library & Information Science

Journal of Library Metadata

Journal of the American Society for Information Science & Technology

Library and Information Science Research

Library Quarterly

- Expert reviewer, "Digital Library" course, Evaluation module, University of North Carolina, Chapel Hill, 2007-2008.

- Expert reviewer, "Information Organization" course, University of Michigan, Ann Arbor. 2007.

### **Catholic University of America**

- School of Arts & Sciences, Academic Senate representative, 2017-2020

- School of Arts & Sciences, Committee on Appointments and Promotions, 2015-2019

- School of Arts & Sciences, Academic Council, 2015-2016.

- School of Arts & Sciences, Ordinary Professor Group, 2013-

- Doctoral Dissertation Defense Committee, Chair, Dept. of Psychology, 2016, 2017, 2018

- Doctoral Dissertation Defense Committee, Chair, Dept. of Education, 2014, 2015, 2017

- President's Administrative Council, 2010-2012

- Deans' Council, 2010-2012

- Academic Leadership Group, 2010-2012

- Academic Senate, 2003-2012

- Academic Senate, Committee on Committees and Rules, 2009-2012

- Academic Senate, Committee on Appointments and Promotions, 2005-2008

- Graduate Board, 2010-2012

- CUA Scholarly Communication Project Team, Member (2007), Chair, 2008-2009

- Academic Senate Library Committee, Interim Chair (2007), Member, 2008-2012

- Doctoral Dissertation Defense Committee, Chair, School of Nursing, 2006, 2008

- Dean Search Committee, 1992-1994, 1998-1999, 2002-2003, 2006-2007

- Fulbright Review Panel, 2006

- Academic Senate Committee on Computing, 1995-2003

- CUA Service Learning Advisory Board, 2001-2002

- CUA Faculty Conversations on Enhancing Teaching and Learning through Technology, Planning Group, 1999-2001

- CUA Initiative on Technology and Teaching, 1998-2001

### **Dept. of Library and Information Science**

• Symposium and Colloquium Committee, fall 2016-May 2018, Chair, May 2018-

- Admissions Committee, 2007-2009, Chair 2010-2012, Member 2013-2015, Member 2018-

- Accreditation presentation, Chair, June 2015-August 2016

- Interim Co-Chair, June 2015-August 2016.

- Appointments and Promotions Committee, 1991-

- Blended/OWL Learning Committee, spring 2016-2018

- Scholarship and Awards Committee, fall 2016-

- Technology Committee, fall 2016-2017

- Comprehensive examination editor, 2016-2017, reader (every year since 1990)

- LIS Advisory Board, 2015-2016 (chair); fall 2016- May 2018 (member)

- Committee on Planning and Assessment, 2015-2016 (chair)

- Senior Faculty Committee, 2014-2016.

- Accreditation Steering Committee, 2014-2016 (Chair, 2015-2016)

- Accreditation Students Standard Committee, co-chair, 2014-2016

- Accreditation Mission, Goals, and Objectives Standard Committee, co-chair, 2014-2016

- Accreditation Curriculum Standard, member 2014-2-16

- Accreditation Administration and Finance Standard, member 2014-2016

- Cultural Heritage Information Management Project (IMLS-funded), Co-PI, 2012-2015

- Cultural Heritage Information Management Forum (scheduled for June 2015), Co-Organizer, 2013-2015

- Health Information Technology Interim Review Committee, 2015 (chair)

- Health Sciences Librarianship Advisory Group, 2015- (chair)

- Comprehensive examination editors, 2013-2014, 2016-2017

- National Digital Stewardship Alliance liaison, 2011-2014

- Advisory Board, Chair 2010-2012

- Academic Honesty Committee, Chair, 2008-2012

- Blended Learning Committee, 2010-2012

- Colloquium Committee, 2010-2012

- Comprehensive Examination Administration, 2010-2012

- Cultural Heritage Information Management Advisory Committee, 2010-2012 (chair), 2013-

- Curriculum Committee, 1991-2003, 2007-2009, Chair 2010-2012, member 2013-

- Curriculum Subcommittee on Comprehensive Examination, Chair 2009-2012

- Health Information Technology Advisory Board, Chair 2010-2012. Member 2013-

- Health Sciences Advisory Committee, 2009, Chair 2010-2012. Member 2013-

- HIT Expert Forum, Chair 2012. Member 2013-

- Health Information Technology Student Group Advisor, 2011-2012

- State Council for Higher Education of Virginia, SLIS Representative, 2010-2012

- Symposium Planning Committee, 2010-2012

- Website Management Team, Chair, 2010-2012

- Urban School Librarianship Project (IMLS-Funded), PI, 2007-2011 (chair, 2010-11)

- Failing Grades Committee, 1995-1997 (chair), 2000-2001 (chair), 2004-2005 (chair), 2007 (chair)-2011

- Faculty Search Committee, 1994-1998, 2002-2004, 2006 (chair), Fall 2007-2009, Chair fall 2009-2012

- Recruitment Committee, Chair 2010-2012

- Strategic Planning Committee, Chair 2010-2012

- Technology Committee, 2010-2012

- Accreditation Advisory Committee, 2007-2009

- Accreditation Coordinating Committee, 2007-2009

- Accreditation Steering Committee, 2007-2009

- SLIS Advisory Group, 2007-2009

- Accreditation Curriculum Standard Committee, Co-chair, 2007-2009

- Accreditation Faculty Standard Committee, Co-chair, 2007-2009

- LSC 551 Information Organization Review Team, Co-chair, 2008-2009, 2015-2016.

- Curriculum Subcommittee on Portfolios, 2009

- LSC 555 Information Systems in Libraries and Information Centers Review Team, contributor, 2008-2009

- Redesign of LSC 730 Use and Users of Libraries and Information. 2009-

- Development of a metadata institute that was taught as LSC 715 Organization of Internet Resources in 2008. The institute is being revised and will be offered in 2010 under a new course title.

- Development of lesson plans, assignments, and evaluation rubrics for LSC 606, Cataloging and Classification, for the School's NCATE accreditation. 2008

- Howard and Mathilde Rovelstad Scholarship Committee, Chair, 2004-2007

- Assistant Dean Search Committee, Chair, Fall 2007

- Liaison to the Association for Library Collections and Technical Services to bring its preconference program, Cataloging Education and Employer Expectations, to CUA during the 2007 American Library Association Annual Meeting in Washington, D.C.

- Organizer of the colloquium presentation and reception for Tamar Sadeh of Ex Libris on PRIMO June 2007

- Practicum review and design (work with potential supervisors, such as the American Indian Museum internship description revision) 2006-

- Comprehensive examinations (edits, proctoring, and grading), 1990-

- SLIS Web site redesign: Comments and suggestions. Fall 2007

- Conducted surveys of current students and alumni in preparation for the 2005 reaccreditation, 2004-2005

- Student advisement, 1990-

- Technology Committee, 1992-1999 (chair, 1996-1998), 2002-2003 (member)

- Colloquia Committee 1997-1999, 2002-2003.

- Advisor of the CUA Student Chapter of the American Society for Information Science and Technology, 2002-2003

- Visiting Professor Search Committee, 1999, 2000, 2001

- Leader, Participation in the CORC experiment, 1999-2000

- Advisor of the Special Libraries Association Student Chapter, 1993-1999; the group was recognized for outstanding leadership by SLA in 1999.

- COA planning Committee, Task Force on Electronic Presentation of SLIS Reports (team leader) 1997-1998

- COA Planning Committee, Subcommittee on Technology 1996-1998

- NLM practicum coordinator, 1997-1998

- Computer Literacy Workshops: Assisted with the development and evaluation of the workshops, 1996-1998

- Leader, Participation in the InterCat project, 1995-1997

## APPENDIX B

### <u>Library of Congress</u> >> <u>MARC</u> >> <u>Understanding MARC</u>

### **MARC 21 Reference Materials**

Part VII: A Summary of Commonly Used MARC 21 Fields

Part VIII: A List of Other Fields Often Seen in MARC Records

Part IX: The Leader

Part X: Field 008 for Books

### Part VII:

## A Summary of Commonly Used MARC 21 Fields

This is a summary of the MARC 21 tags used most frequently by libraries in entering their own bibliographic records. For full listings of all MARC 21 tags, indicators, and subfield codes, see *MARC 21 Format for Bibliographic Data*.

In the explanations on these pages:

**Tags** -- The tags (3-digit numbers) are followed by the names of the fields they represent. In this summary, and in the *MARC 21 Format for Bibliographic Data*, if a tag can appear more than once in one bibliographic record, it is labeled repeatable (R). If it can only be used once, it is labeled non-repeatable (NR). For example, a catalog record can have several subjects, so the tags for subject added entries (6XX) are labeled repeatable (R).

**Indicators** -- The use of indicators is explained in fields where they are used. Indicators are one-digit numbers. Beginning with the 010 field, in every field -- following the tag -- are two character positions, one for Indicator 1 and one for Indicator 2. The indicators are not actually defined in all fields, however. And it is possible that a 2nd indicator will be used, while the 1st indicator remains undefined (or vice versa). When an indicator is undefined, the character position will be represented by the character # (for blank space).

**Subfield codes** -- All the data in each field (beginning with the 010 field) is divided into subfields, each of which is preceded by a delimiter-subfield code combination. The most common subfield codes used with each tag are shown. Each subfield code is preceded by the character \$, signifying a delimiter. The name of the subfield follows the code.

In general, every field MUST have a subfield 'a' (\$a). One exception that is often seen is in Field 020 (ISBN), when the ISBN information (subfield \$a) is unavailable but the price (subfield \$c) is known. Some subfields are repeatable. In this summary, repeatability is noted for only the more common repeatable subfields.

**Examples:** Examples follow the explanation for each field. For clarity, one space has been placed between the tag and the first indicator, one space has been placed between the

second indicator and the first delimiter- subfield code, and one space has been inserted between the delimiter-subfield code and the subfield data.

### 010 Library of Congress Control Number -- (LCCN)

(NR, or Not Repeatable

Indicators undefined.

Subfield used most often:

\$a -- Library of Congress control number

Example: 010 ## \$a ###86000988#

### 020 International Standard Book Number -- (ISBN)

(R, or Repeatable)

Indicators undefined.

Subfields used most often:

**\$a** -- International Standard Book Number

**\$c** -- Terms of availability (often a price)

\$z -- Cancelled/invalid ISBN (R)

Example: 020 ## \$a 0877547637

### 040 Cataloging source -- (NR)

Indicators undefined.

Subfields used most often:

**\$a** -- Original cataloging agency

**\$c** -- Transcribing agency

**\$d** -- Modifying agency (R)

Example: 040 ## \$a DLC \$c DLC \$d gwhs

**100 Main entry -- Personal name -- (primary author)**

(NR; there can be only one main entry)

*Indicator 1:* Type of personal name entry element

0 -- Forename

1 -- Surname (this is the most common form)

3 -- Family name

*Indicator 2 undefined.*

Indicator 2 became obsolete in 1990. Older records may display 0 or 1 *Subfields used most often:*

**\$a** -- Personal name

**\$b** -- Numeration

**\$c** -- Titles and other words associated with a name (R)

**\$q** -- Fuller form of name

**\$d** -- Dates associated with a name (generally, year of birth)

```

Example: 100 1# $a Gregory, Ruth W. $q (Ruth Wilhelme), $d 1910-

```

### 130 Main entry -- Uniform title -- (NR)

*Indicator 1:* Nonfiling characters

0-9 -- Number of nonfiling characters present (for initial articles, including spaces)

Indicator 2 undefined.

Indicator 2 became obsolete in 1990. (See 100 above.)

Subfields used most often:

**\$a** -- Uniform title

**\$p** -- Name of part/section of a work (R)

\$1 -- Language of a work

**\$s** -- Version

**\$f** -- Date of a work

```

Example: 130 0# $a Bible.

$p O.T.

$p Psalms.

```

### 240 Uniform title (NR)

*Indicator 1:* Uniform title printed or displayed

0 -- Not printed or displayed

1 -- Printed or displayed (most common)

Indicator 2: Nonfiling characters

0-9 -- Number of nonfiling characters present (for initial articles, including spaces)

Subfields used most often:

**\$a** -- Uniform title

**\$1** -- Language of a work

**\$f** -- Date of a work

Example: 240 10 \$a Ile mystérieuse. \$1 English. \$f 1978

### 245 Title Statement (NR)

Indicator 1: Title added entry

(Should the title be indexed as a title added entry?)

0 -- No title added entry

(indicates a title main entry; i.e. no author is given)

1 -- Title added entry

(the proper indicator when an author given in 1XX; the most common situation)

### *Indicator 2:* Nonfiling characters

0-9 -- Number of nonfiling characters present, including spaces; usually set at zero, except when the title begins with an article; e.g., for *The robe*, the second indicator would be set to 4. The letters *T*, *h*, *e*, and the space following them are then ignored in alphabetizing titles. The record will be automatically filed under "*r*" -- for *Robe*.

Subfields used most often:

**\$a** -- Title proper

**\$h** -- Medium (often used for non-book media)

**\$p** -- Name of part/section of a work (R)

**\$b** -- Reminder of title (subtitles, etc.)

**\$c** -- Remainder of title page transcription/Statement of responsibility

Example: 245 14 \$a The DNA story:

\$b a documentary history of gene cloning /

\$c James D. Watson, John Tooze.

### 246 Varying form of title (R)

Indicator 1: Note/title added entry controller

1 -- Note, title added entry

3 -- No note, title added entry

*Indicator 2:* Type of title

# -- No information provided

0 -- Portion of title

1 -- Parallel title

4 -- Cover title

8 -- Spine title

Subfield used most often:

### **\$a** -- Title proper

Example: 246 3# \$a Four corners power review

### 250 Edition statement (NR)

Indicators undefined.

Subfield used most often:

**\$a** -- Edition statement

Example: 250 ## \$a 6th ed.

### 260 Publication, distribution, etc. (Imprint) (R)

*Indicator 1:* Sequence of publishing statements

# -- No information provided

Indicator 2: Undefined

Subfields used most often:

**\$a** -- Place of publication, distribution, etc. (R)

**\$b** -- Name of publisher, distributor, etc. (R)

**\$c** -- Date of publication, distribution, etc. (R)

Example: 260 ## \$a New York: \$b Chelsea House, \$c 1986.

### **300 Physical description (R)**

Indicators undefined.

Subfields used most often:

**\$a** -- Extent (number of pages) (R)

**\$b** -- Other physical details (usually illustration information)

**\$c** -- Dimensions (cm.) (R)

**\$e** -- Accompanying material (for example, "teacher's guide" or "manual")

Example: 300 ## \$a 139 p.: \$b ill.; \$c 24 cm.

440 Series statement / Added entry--Title

This field was made obsolete in 2008 to simplify the series statement. See 490 and 830.

### 490 Series statement (No added entry is traced from field) (R)

Indicator 1: Specifies whether series is traced (whether an 8XX tag is also present)

0 -- Series not traced

1 -- Series traced (8XX is in record)

*Indicator 2 undefined.*

Subfield used most often:

**\$a** -- Series statement (R)

**\$v** -- Volume number (R)

Example: 490 1# \$a Colonial American craftsmen

### 500 General note (R)

Indicators undefined.

Subfield used most often:

**\$a** -- General note (Used when no specialized note field has been defined for the information. Examples: Notes regarding the index; the source of the title; variations in title; descriptions of the nature, form, or scope of the item.)

Example: 500 ## \$a Includes index.

### 504 Bibliography, etc. note (R)

Indicators undefined.

Subfield used most often:

**\$a** -- Bibliography, etc. note

Example: 504 ## \$a Includes bibliographical references.

### 505 Formatted contents note (R)

*Indicator 1:* Type of contents note

0 -- Complete contents

1 -- Incomplete contents (used with multivolume set when some volumes are not yet published)

2 -- Partial contents

Indicator 2: Level of content designation

# -- Basic

Subfield used most often:

**\$a** -- Formatted contents note

Example: 505 0# \$a Pride and prejudice -- Emma -- Northanger Abbey.

### 520 Summary, etc. note (R)

*Indicator 1:* Display constant controller

# -- Summary

- 1 -- Review

- 2 -- Scope and content

- 3 -- Abstract

Indicator 2 undefined

Subfields used most often

- \$a -- Summary, abstract, or annotation

- **\$b** -- Expansion of summary note

Example: 520 ## \$a This basic guide to parliamentary procedure tells how to conduct and participate in a meeting properly.

### 600 Subject added entry -- Personal name (R)

*Indicator 1:* Type of personal name entry element

- 0 -- Forename

- 1 -- Surname (this is the most common form)

- 3 -- Family name

*Indicator 2:* Subject heading system/thesaurus (identifies the specific list or file which was used)

- 0 -- Library of Congress Subject Headings

- 1 -- LC subject headings for children's literature