Linköping Studies in Science and Technology. Dissertations. No. 319

# Smart Image Sensors

Anders Aström

Department of Electrical Engineering Linköping University, S-581 83 Linköping, Sweden

Linköping 1993

# Anders Åström: SMART IMAGE SENSORS

Linköping 1993

Linköping Studies in Science and Technology. Dissertations. No. 319

# Smart Image Sensors

Anders Åström

Department of Electrical Engineering Linköping University, S-581 83 Linköping, Sweden

Linköping 1993

#### Abstract

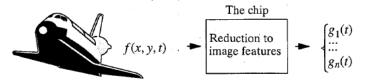

Today, modern VLSI technology makes it possible to integrate image input and low-level operations into one single chip. Such a chip can take in an image and apply fairly complex algorithms on the image and also extract features to be sent to higher levels of processing. These chips are known as *Smart Image Sensors*. All devices described in this thesis employ CMOS technology for the sensors as well as for other circuitry.

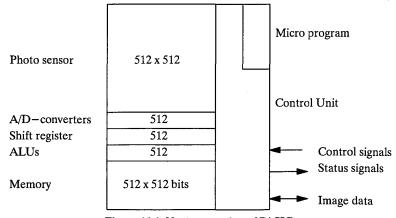

The first part of this thesis describes a smart image sensor called PASIC (Processor, A/D-converter, and Sensor Integrated Circuit). It is a two-dimensional sensor with a linear array of processing elements working in SIMD mode. The aim is to verify the performance by cycle counting a number of low-level algorithms such as shading correction, histogram based thresholding, edge detection, and segmentation. The studies show that the PASIC architecture is surprisingly effective.

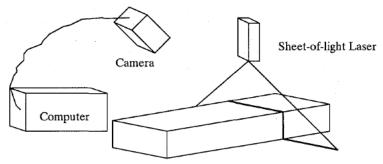

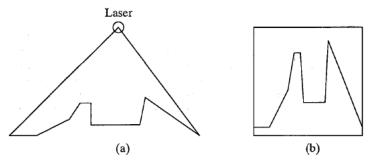

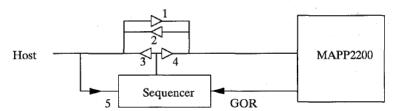

The second part of the thesis describes MAPP2200 which is a commercial available smart image sensor. It has the same basic structure as PASIC (2D sensor array and 1D processor array). The exposure control is performed in a very different manner compared to normal CCD-cameras. In MAPP2200 the sensor array is accessed much like a memory, row-wise in any sequence. The simple ALU-functions in each of the 256 processing elements is enhanced with a global logic for feature extraction. One group of algorithms which seams to suit MAPP2200 very well is moment calculations and we give three application examples with different demands on speed and segmentation. Finally, we show that range data from sheet-of-light can be obtained at very high speed by using a combination of analog and digital computation.

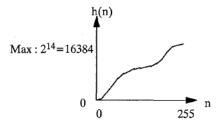

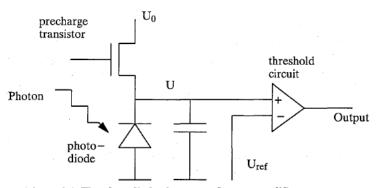

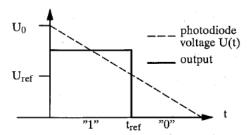

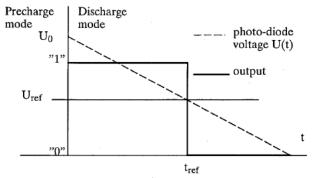

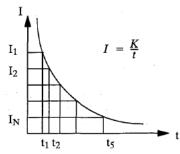

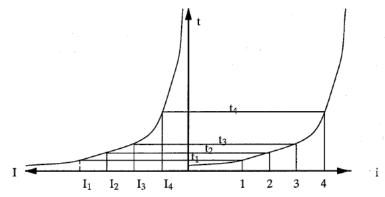

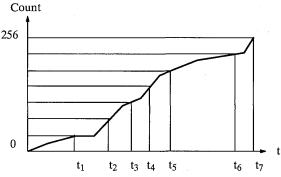

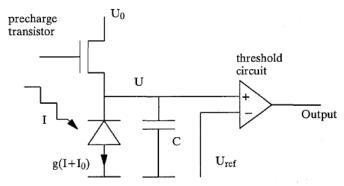

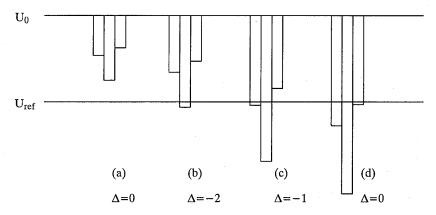

The third part introduces the concept of Near-Sensor Image Processing. It is shown that the analogue-temporal behavior of photodiodes as detected by thresholding amplifiers can be integrated with low-level algorithms such as median filtering, grayscale morphology, convolution, and adaption to different light levels. The quantity to be measured in NSIP is the time from the pre-charge of the photodiode until the voltage passes the reference voltage. This time is inversely proportional to the incoming light intensity. Various mapping strategies to modify this relation are discussed, and it is shown that histogram equalization comes naturally in this concept. For the sake of simplicity, most examples of operations and algorithms are given for the 1D-array LAPP1100. Suggestions for a 2D NSIP architecture are also provided. Finally, an application is described where NSIP is used in an architecture for sheet-of-light range imaging.

ISBN 91-7871-171-1 ISSN 0345-7524 Printed in Sweden by LJ Foto & Montage/Samhall Klintland, Linköping 1993 To my parents

# Acknowledgements

There are a number of people without whom this thesis would never have existed. This is my opportunity to thank at least some of them.

First of all I would like to thank my supervisor Professor Per-Erik Danielsson for many valuable suggestions to this thesis, and for making it more readable and understandable.

Invaluable inspiration to this thesis, especially for the parts on MAPP and NSIP has been given by Dr. Robert Forchheimer.

Further thanks goes to

All people involved in the PASIC-, VIP-, MAPP-, and NSIP projects, especially, to Per Ingelhag and Mattias Johannesson.

People at IVP for the opportunity to work with MAPP2200.

All members of the Image Processing Group.

Finally, I would like to thank the Swedish National Board for Technical Development (NUTEK) and Center for Industrial Information Technology (CENIIT) for financial support.

# CONTENTS

| Thesis overview                    | xi<br>xi<br>di<br>xv |

|------------------------------------|----------------------|

|                                    | cii                  |

| Similar projects                   |                      |

|                                    | ζV                   |

| References                         |                      |

|                                    |                      |

| Part I PASIC                       |                      |

|                                    |                      |

| 1 Introduction                     | 1                    |

| 1.1 Background                     | 1                    |

| 1.2 Bit-serial parallel processors | 3                    |

| 1.2.1 An overview                  | 3                    |

| 1.2.2 LUCAS                        | 3                    |

| 1.2.3 GAPP                         | 4                    |

| 1.2.4 AIS-5000                     | 5                    |

| 1.2.5 LAPP                         | 7                    |

| 2 The PASIC Architecture           | 9                    |

| 2.1 Overview                       | 9                    |

| 2.2 The photo sensors              | 9                    |

| 2.3 The A/D converters             | 0                    |

| 2.4 The processing elements, PE    | .1                   |

| 2.5 VLSI                           | 4                    |

| 2.6 The programming model          | 5                    |

| 3 Basic instruction set            | 8                    |

|                                    | .8                   |

|                                    | 23                   |

|                                    | 4                    |

| •                                  | 26                   |

|                                    | .7                   |

|                                    | 8                    |

|                                    | 0                    |

| 3.8 Summary of PASIC               | 2                    |

| ·                                  | 3                    |

|                                    | 3                    |

| -                                  | 4                    |

| •                                  | 6                    |

| _                                  | 7                    |

| 4.5     | Counting bits on a line                          | 38   |

|---------|--------------------------------------------------|------|

| 4.6     | Labeling objects on a line                       | 40   |

| 4.7     | Histogram collection                             | 41   |

| 5       | General comments about applications              | 45   |

| 5.1     | Definitions                                      | 45   |

| 5.2     | Row parallel pipelining                          | 45   |

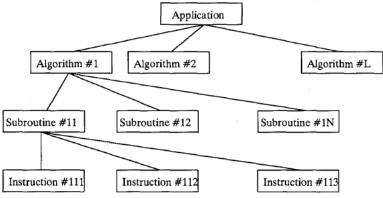

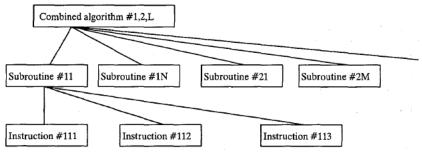

| 5.3     | Combining different algorithms                   | 46   |

| 6       | Shading correction                               | 49   |

| 6.1     | The need for shading correction                  | 49   |

| 6.2     | Calibration                                      | 49   |

| 6.3     | Correction                                       | - 51 |

| 7       | Histogram based thresholding                     | 53   |

| 7.1     | On thresholding and histograms                   | 53   |

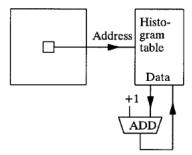

| 7.2     | Implementation and performance on PASIC          | 56   |

| 7.3     | Results from experiments                         | 59   |

| 8       | Edge detection                                   | 61   |

| 8.1     | On edge detection algorithms                     | 61   |

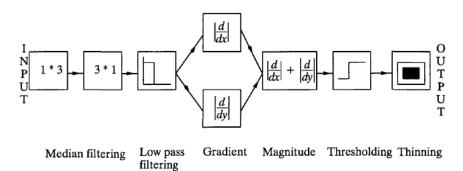

| 8.2     | Median - Sobel - Thinning                        | 62   |

| 8.3     | Second derivative zero-crossing                  | 66   |

| 8.4     | Extended second derivative zero-crossing         | 68   |

| 8.5     | Contrast amplification                           | 70   |

| 9       | Segmentation                                     | 73   |

| 9.1     | Segmentation on parallel machines                | 73   |

| 9.2     | Limitations for PASIC                            | 77   |

| 9.3     | Implementation of the multi-scan procedure       | 77   |

| 9.4     | Implementation of the one scan procedure         | 79   |

| 9.5     | Results from experiments                         | 80   |

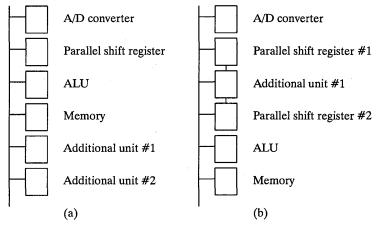

| 10      | Improvements of PASIC                            | 82   |

| 10.1    | Architecture extension, different approaches     | 82   |

| 10.2    | Extended ALU                                     | 82   |

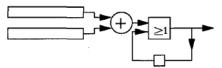

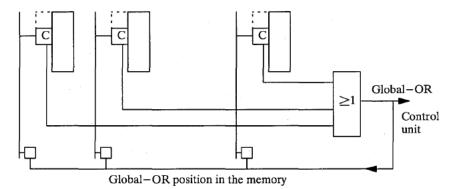

| 10.3    | Global-OR feedback                               | 85   |

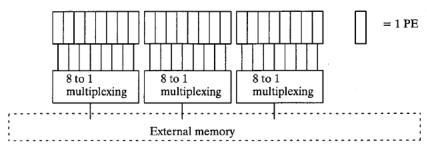

| 10.4    | External memory                                  | 86   |

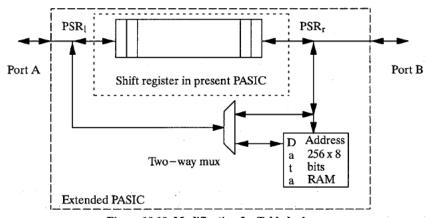

| 10.5    | Look-up table                                    | 87   |

| 10.6    | An application driven extension design for PASIC | 89   |

| 11      | Conclusions                                      | 92   |

| 12      | References                                       | 94   |

|         |                                                  |      |

| Pa      | rt II MAPP2200                                   |      |

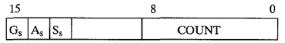

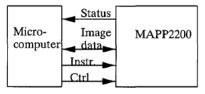

| 1       | Architecture                                     | 1    |

| а<br>11 | Overview                                         | · 1  |

| 1.1     | AND NOW                                          |      |

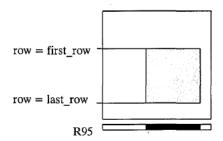

| 1.2 | The sensor                                            | 2    |

|-----|-------------------------------------------------------|------|

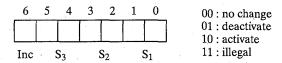

| 1.3 | Processor architecture and instruction set            | 4    |

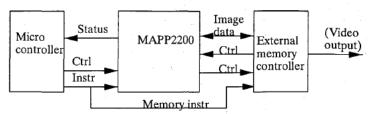

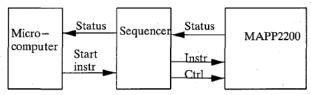

| 1.4 | MAPP2200 system configurations                        | 10   |

| 2   | Programming MAPP2200                                  | 12   |

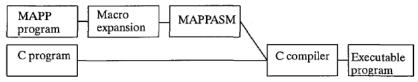

| 2.1 | Environment and syntax                                | 12   |

| 2.2 | Iterations                                            | 14   |

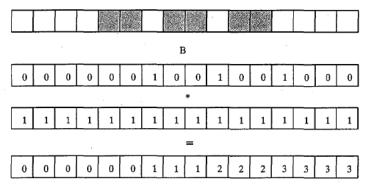

| 2.3 | Bit-serial arithmetic                                 | 16   |

| 2.4 | Macros                                                | 17   |

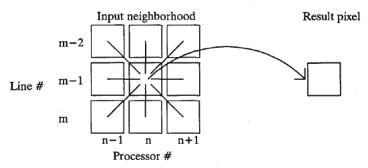

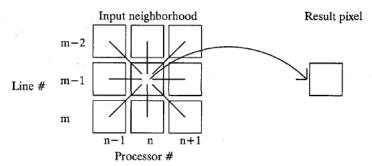

| 2.5 | 2D filtering                                          | 17   |

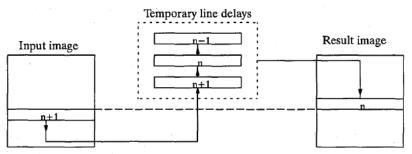

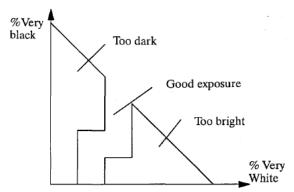

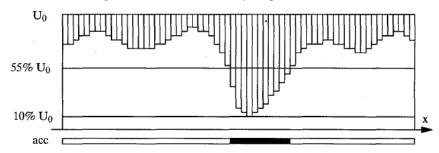

| 3   | Exposure control                                      | 20   |

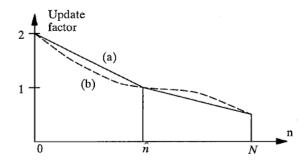

| 4   | Adaptive exposure control                             | 23   |

| 4.1 | A model for optimal exposure                          | 23   |

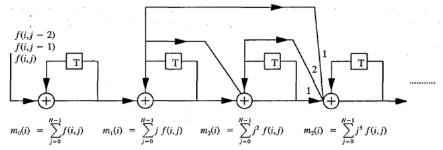

| 5   | Computation of moments                                | 28   |

| 5.1 | 2D discrete moments                                   | 28   |

| 5.2 | Moment calculation in MAPP2200                        | 30   |

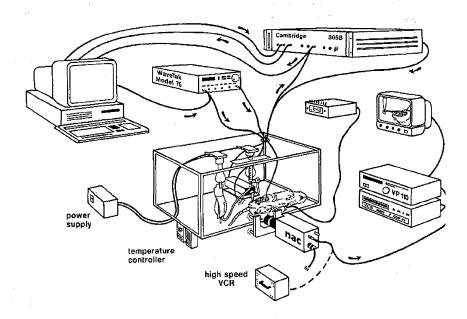

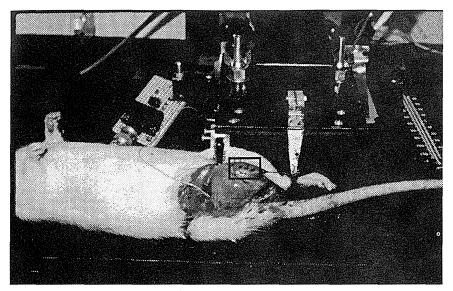

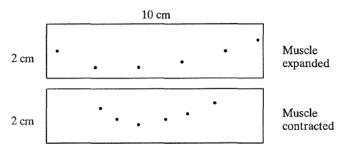

| 5.3 | A MAPP application. Tracking movement in a rat muscle | 32   |

| 5.4 | Segmentation and moment calculation, the general case | 36   |

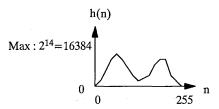

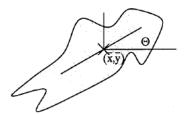

| 6   | Sheet-of-light range imaging                          | 40   |

| 6.1 | General                                               | 40   |

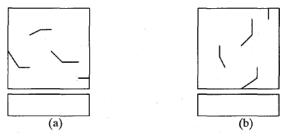

| 6.2 | Implementation on MAPP2200                            | 41   |

| 6.3 | Filtering during computation                          | 45   |

| 7   | Conclusions                                           | 47   |

| 8   | References                                            | 49   |

| Do  | rt III NSIP                                           |      |

| га  | IT III NOIF                                           |      |

| 1   | Introduction                                          | 1    |

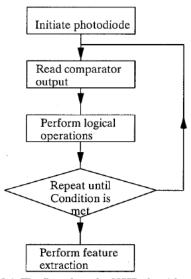

| 2   | A Near-Sensor Image Processor                         | 4    |

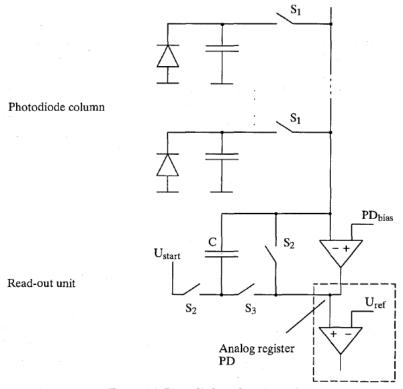

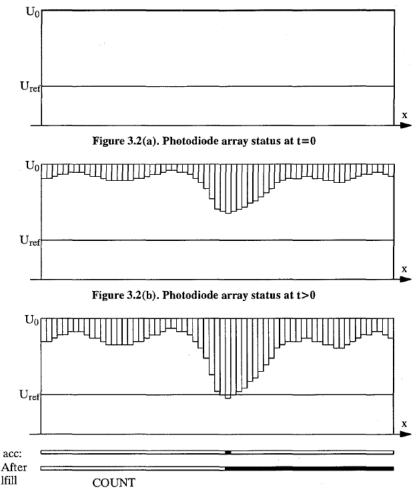

| 2.1 | The photodiode sensor                                 | 4    |

| 2.2 | LAPP1100 - a 1D architecture                          | 7    |

| 3   | Near-Sensor Image Processing algorithms               | 10   |

| 3.1 | General                                               | 10   |

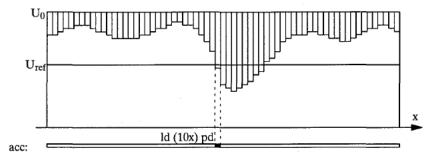

| 3.2 | Finding the position of maximum intensity             | . 10 |

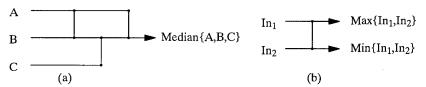

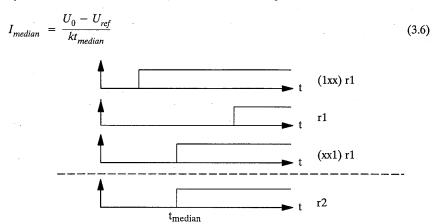

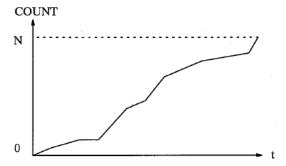

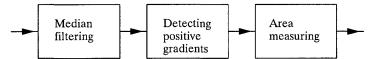

| 3.3 | Detecting positive gradients                          | 13   |

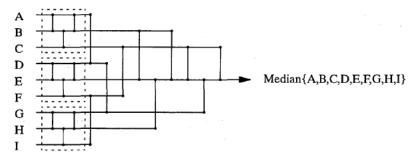

| 3.4 | Median and rank order filtering                       | 14   |

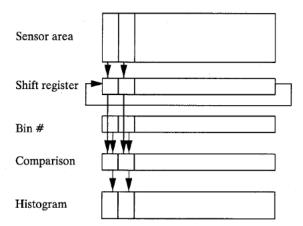

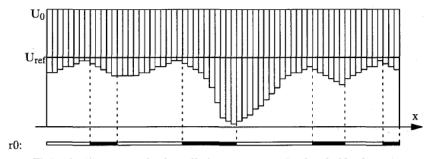

| 3.5 | Histogramming                                         | 17   |

| 3.6 | Combining operations                                  | 18   |

| 4   | Adaptive thresholding                                 | 20   |

| 4.1 | Using the maximum intensity                           | 20   |

| 4.2  | Pattern oriented thresholding                | 20 |

|------|----------------------------------------------|----|

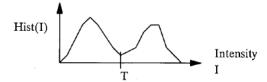

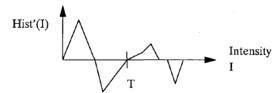

| 4.3  | Histogram based thresholding                 | 21 |

| 5    | Variable sampling time                       | 23 |

| 5.1  | General                                      | 23 |

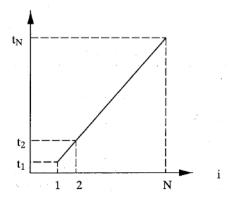

| 5.2  | Linear mapping                               | 24 |

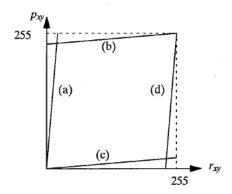

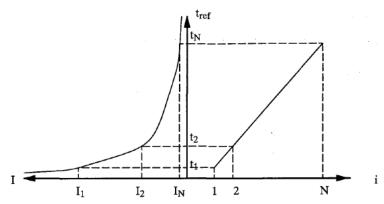

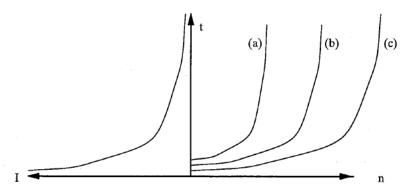

| 5.3  | Non-linear mapping                           | 26 |

| 5.4  | Data dependent mapping                       | 27 |

| 6    | Variable threshold                           | 31 |

| 6.1  | General                                      | 31 |

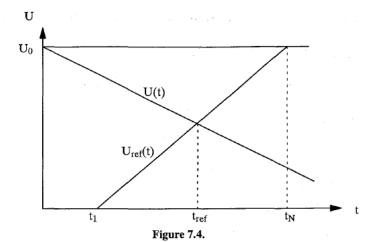

| 6.2  | Linear mapping                               | 31 |

| 6.3  | Non-linear mapping                           | 34 |

| 7    | Error analysis                               | 35 |

| 7.1  | Error model                                  | 35 |

| 7.2  | Variable sampling time                       | 36 |

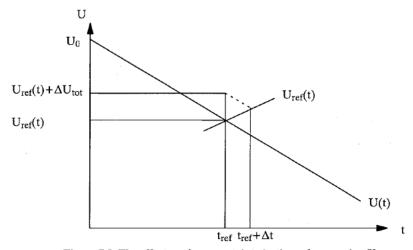

| 7.3  | Time variable threshold                      | 37 |

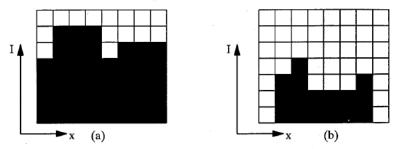

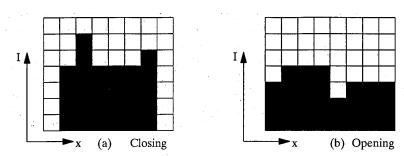

| 8    | Grayscale morphology                         | 40 |

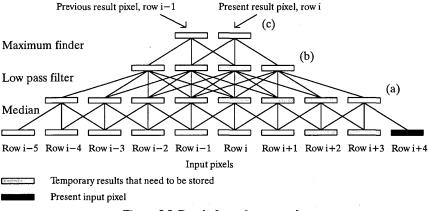

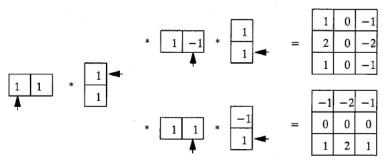

| 9    | Linear convolution                           | 44 |

| 10   | 2D NSIP model                                | 48 |

| 10.1 | Programming model                            | 48 |

| 10.2 | Generation of coordinates                    | 50 |

| 11   | Global operations                            | 53 |

| 11.1 | MARK and FILL                                | 53 |

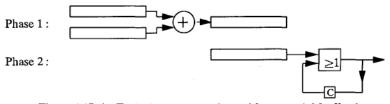

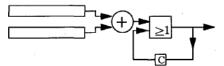

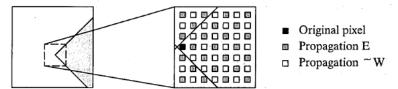

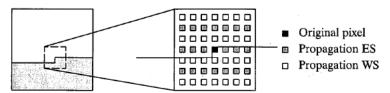

| 11.2 | Safe and unsafe propagation                  | 59 |

| 12   | Feature extraction                           | 62 |

| 12.1 | Finding a position                           | 62 |

| 12.2 | Moments                                      | 63 |

| 12.3 | Shape factor                                 | 65 |

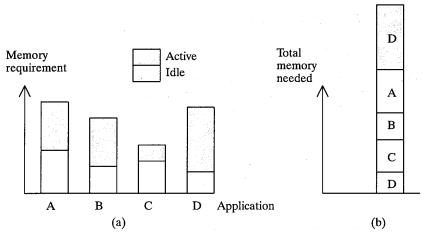

| 13   | VLSI realization of 2D NSIP                  | 67 |

| 14   | NSIP Sheet-of-light range images             | 72 |

| 14.1 | Implementation in NSIP                       | 72 |

| 14.2 | Special NSIP architecture for sheet-of-light | 73 |

| 15   | Conclusion                                   | 75 |

| 16   |                                              | 76 |

# **Smart Image Sensors**

#### Thesis overview

The expression "Smart image sensor" has no official definition and different authors tend to have different meanings of the concept. However, a common characteristic seams to be that the sensor should contain some processing power and/or programmable access to the image data. Hence, ordinary CCD-cameras are not regarded as smart, not even if they have some flexibility in terms of programmable integration time.

We feel that all Smart image sensors (proposed or implemented) can be categorized as follows.

- 1. Random access of sensor array, no processing capability

- 2. Integrated sensor and one single processor

- 3. Integrated sensor and linear processor array

- 4. Integrated sensor and 2D array of processors (one processor per pixel)

The smart image sensors to be presented in this thesis belong to categories 3 and 4.

Research within the field of smart image sensors has been an ongoing activity at the University of Linköping for a long time. At the beginning of the 1980s, Dr. Robert Forchheimer came forward with an idea to combine sensors and processors on the same chip. He was partly inspired by the optical mouse [19]. In cooperation with Anders Ödmark at the Physics Department, the sensor/processor LAPP [13], Linear Array Picture Processor, was born. A series of prototype chips were designed and manufactured in 1983–84. The project was then moved from the university to the spin-off company IVP Integrated Vision Products, which was founded to commercialize this product. The name of the chip was now changed to LAPP1100 where the first "1" stands for the dimension and the "100" stands for the magnitude of the number of sensor elements, which was 128. The marketing of the LAPP1100 chip began in 1987.

At the same time as the LAPP1100 chip was developed at IVP, several new ideas were investigated at the university as a joint venture between the LSI design group, Dept. of Physics, and the Image processing group, Dept. of Electrical Engineering. One of these was the PASIC architecture, first proposed by Dr. Keping Chen in 1988. At that time, PASIC was assumed to consist of a 128x128 array of photo-sensors and a 128 array of processors, [6][7]. Given the architecture of PASIC several algorithms were simulated and cycle counted. Sometimes the simulations showed that the design should be modified. After a number of architecture and algorithm iterations the architecture converged to a rather complete and powerful smart image sensor. Two different test chips were made and tested in 1991. One contained a 256x256 sensor array and 256 A/D-converters and the other contained a processing array of size 256. This work was published as a licentiate thesis [1] in december 1990 and forms Part I of this thesis.

During the work with PASIC, its processor part was discovered to be very powerful on its own. This resulted in a new chip design called VIP, Video Image Processor [4][5][8], which is

not covered in this thesis. This architecture has proved to be highly effective for radar signal processing [14][18]. A modified VIP chip, now called RVIP (Radar VIP), is going to be commercialized by Ericsson Radar Electronics, Mölndal, Sweden.

In 1990, the demand for a two-dimensional sensor persuaded IVP to develop MAPP2200, Matrix Array Picture Processor [12]. MAPP2200 is mainly an outgrowth of LAPP1100 although some of the ideas behind PASIC were also incorporated in the design. Especially, the software environment of MAPP2200 [3] has been influenced by PASIC. MAPP2200 has also been used for research at some universities. One of the applications is to serve as the key component in a sheet-of-light range camera [17]. The MAPP2200 architecture, algorithm implementations, and some applications form Part II of this thesis.

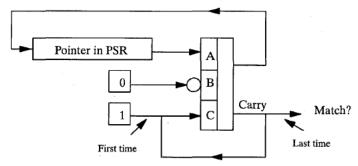

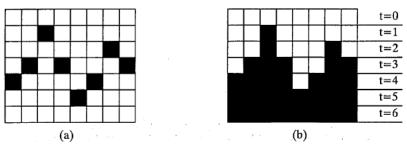

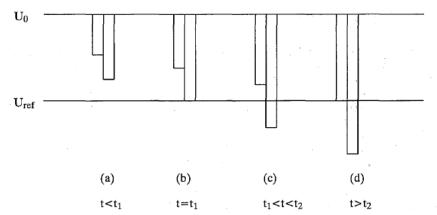

The idea of Near-Sensor Image Processing, NSIP, originates from LAPP1100 [13]. In the early 80's, VLSI constraints prevented the LAPP-designers from incorporating A/D-converters for the 128 sensor array. To obtain gray level data the threshold voltage had to be changed step by step and a number of binary image had to be taken care of. It was then discovered that many image processing problems could indeed be solved not by storing a sequence of binary images but by intelligent processing each time the sensor array delivers binary data. The final result is influenced by the full sequence of input data and the processing utilizes certain characteristics in these sequences, e.g. the fact if a sensor input has passed the threshold it will continue to do so. In effect, the A/D-conversion and the digital processing is interwoven in the innermost program loop where the sensor is repeatedly interrogated. This is the NSIP idea, "Near-Sensor Image Processing". Part III of this thesis, discusses NSIP both on the algorithmic level [10][11] and on the architectural/VLSI level [2].

# Similar projects

The litterature on smart image sensors is not large which is somewhat surprising. For anyone who is familiar with image processing and its applications, the smart image sensor would seam to be an obvious and natural development. Possible reasons why so little has been reported might be a certain conservatsim, feeling that the art of VLSI is still not ready for it, and the fact that the dominating sensor type, the CCD-chip does not lend itself so easily to add-on digital circuitry. In contrast, all smart image sensor reported in this thesis are CMOS for sensors as well as the digital parts.

We will will mention four other smart image sensor projects below; Two of them very breifly.

Carver Mead at Caltech [20] set as his goal to construct a silicon retina to emulate certain functions of the human eye. His strategy is to design a number of functional units in VLSI where each unit has a special neural-like function (axons, dendrites, etc.). He then configures these units according to demand. A motion detector which detects any kind of motion in the scene in the same way as a human eye has been demonstrated as well as a sensor with the same impulse response as the human retina.

Another approach has been reported from Laval University, Canada. This is the Multi-port Access photo-Receptor, MAR [22]. The main smartness of this sensor is that pixels in a hexagonal grid can be randomly accessed and for each pixel position, the whole 16 pixels neighborhood will be available at the analog output from the chip. In of the applications men-

tioned in [22] the 16 pixel output is transferred to several different lowpass/gradient filters concurrently.

Smart image sensor projects at the University of Edinburgh [21] has been going on for quite some time. The results have been successfully commercialized by the company VVL, VLSI Vision Limited. The idea behind the project and the company is to use a CMOS sensor array and on the same silicon chip implement an image processing system as a full-custom VLSI design dedicated to a certain application [9]. For example, if the application is just a compact video camera a special unit is implemented on the chip which takes the output from the photo-sensors and delivers a standard video signal output. If the application is a system for fingerprint capture and verification [21], the image processing part is totally different. In the latter case the chip consists of

258x258 photo-sensor array

Unit for image preprocessing and quantization

64-cell 2000 Mops/s correlator array

16k bits RAM cache

16k bits ROM look-up table

Together with a 64k bit off-chip RAM and a 8051 micro-controller, this device can capture and compare a fingerprint against a stored reference print within one second.

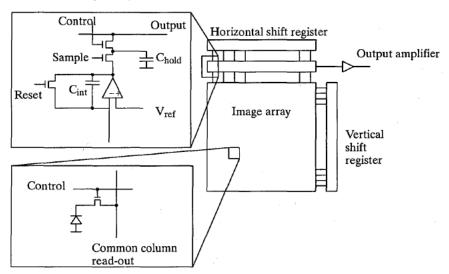

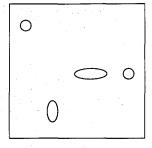

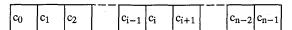

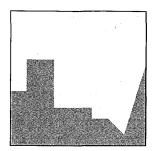

The photo-sensor array which is used in most of the applications is shown in Figure 1. The size of the array depends on the application. For the fingerprint application it is 258x258 and for the video output chip it is 312x287.

Figure 1. The sensor array in the VVL smart sensor

Each photo-sensing element consists of a photodiode and a CMOS transistor. It is precharged and after a certain time it is read-out via the column bus. The pre-charge and readout is done row-wise in parallel. The row address is controlled by the vertical shift register. For each column, there is a sense amplifier, which is responsible for both the reset and the read-out of the photodiodes. The charge is moved from the pixel element to the hold position by activating the Sample switch and deactivating the Reset switch. The row can now be read-out, sequentially over the output bus, by addressing one column at a time. This addressing is controlled by the horizontal shift register.

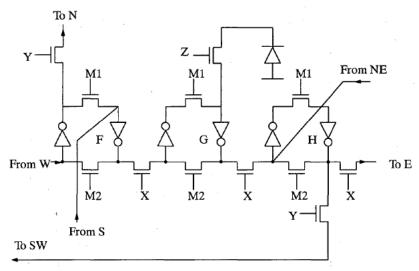

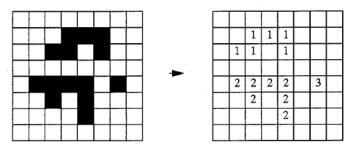

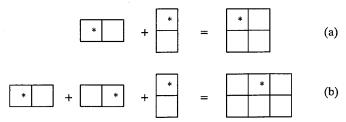

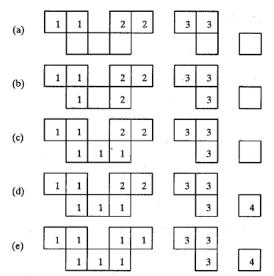

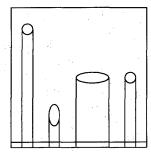

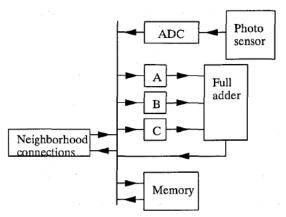

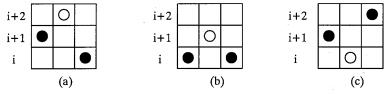

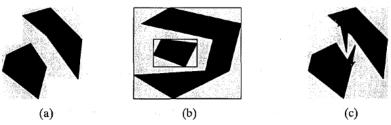

The VLSI Retina [23], has been developed at ETCA, France. This design has one processor per pixel. Each processor is based on a three-bit semi-static shift register, shown in Figure 2. Each of the memory cell F, G, and H is controlled by the two clock signals M1 and M2. Using the clock signal X the data can be shifted to the right and with Y, data can be moved to the north (with Y and M2) and to the south-east (Y and M1). These three shift possibilities, West, North, SouthEast, are sufficient to perform arbitrary 2D shifting in the array.

Figure 2. Semi-static shift register

With a control signal T and some extra transistors, not shown in Figure 2, it is possible to perform Boolean operations. The bit F or its complemented version in the first cell, may be copied or and'ed with the G bit in the second cell. It is also possible to take the value from the photo-sensor and latch that binary value into the second cell with the control signal Z. Table 1 shows the content in the three cells F, G, and H, after different operations.

The idea behind the design is to use what is called Neighborhood Combinatorial Processing [15], NCP. It is a concept to define edge detection, dithered halftoning, and other binary operations, in terms of iterated Boolean operations. It is well known that conjunction and complementation are sufficient to perform any computation. Since these are included in Table 1, the claim is that the VLSI Retina sensor/processing element can perform any operation. An edge detection is performed by using classical mathematical morphology technique, where the edge image is the difference between the initial image and the eroded version. This operation takes 30 instruction cycles.

| F                 | G                                                                              | Н                                                                                  |

|-------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| F <sub>0,-1</sub> | G                                                                              | Н                                                                                  |

| F                 | G                                                                              | H <sub>1,1</sub>                                                                   |

| H-1,0             | F                                                                              | G                                                                                  |

| H <sub>0,1</sub>  | F                                                                              | G                                                                                  |

| F                 | F                                                                              | H                                                                                  |

| F                 | F                                                                              | $H_{1,1}$                                                                          |

| F                 | F&G                                                                            | H                                                                                  |

| F                 | F&G                                                                            | $H_{1,1}$                                                                          |

| F                 | G+ ( $\phi$ > $\phi_T$ )                                                       | H                                                                                  |

|                   | F <sub>0,-1</sub><br>F<br>H <sub>-1,0</sub><br>H <sub>0,1</sub><br>F<br>F<br>F | F <sub>0,-1</sub> G F G H <sub>-1,0</sub> F H <sub>0,1</sub> F F F F F F F&G F F&G |

Table 1. Some operations on the VLSI Retina

There are at least two major differences between the VLSI Retina and the Near-Sensor Image Processing concept, described in part III in this thesis. Gray-level information in the VLSI retina is obtained by imaging the scene several times with decreasing exposure time, while in the Near-Sensor Image Processing concept, the photodiode is interrogated repeatedly during one single discharge event. The other difference is that feature extraction on a global level is not dealt with at all in the VLSI Retina.

### References

- [1] Åström A., A Smart Image Sensor. Evaluation and Description of PASIC., Lic Thesis, Linköpings University 1990.

- [2] Åström A., Forchheimer R., Ingelhag P., An Integrated Sensor/Processor Architecture Based on Near-Sensor Image Processing, To appear in Proc of CAMP93, New Orleans, USA.

- [3] Åström A., Forchheimer R., MAPP2200 Smart Vision Sensor: Programmability and Adaptivity, Proc of IAPR Workshop of Machine Vision Applications, Japan, 1992.

- [4] Åström A., Danielsson P.E., Chen K., Ingelhag P., Svensson C., Videorate signal processing with PASIC and VIP, Proc 2nd Int Specialist Seminar on the Design and Application of Parallel Digital Processors, Lissabon, Portugal 1991.

- [5] Chen K., Svensson C., A 512-processor array chip for video/image processing, Proc. of "From Pixels to Features II," Bonas, France, Aug. 27 Sept. 1, 1990, pp 349–361.

- [6] Chen K., Åström A., Danielsson P.E., *PASIC a smart Sensor for Computer Vision*, Proc of Pattern Recognition, Atlantic City, June 1990, pp. 286–291.

- [7] Chen K., Danielsson P.E., Åström A., PASIC a Sensor/Processor Array for Computer Vision, Proc of Application Specific Array Processors, Princeton, September 1990, pp. 352-366.

- [8] Danielsson P.E., Emanuelsson P., Chen K., Ingelhag P., Svensson C.. Single-Chip High-Speed Computation of Optical Flow, Proc IAPR International Workshop on Machine Vision Applications, November 1990, Tokyo, Japan

- [9] Findlay K. Personal Communication 1992. Kevin Findlay, <kevin@ee.edin-burgh.ac.uk>.

- [10] Forchheimer R., Åström A., Near-Sensor Image Processing. A new approach to low level image processing, Proc of ICIP, Singapore 1992

- [11] Forchheimer R., Åström A., Near-Sensor Image Processing. A New Paradigm, accepted for publication in IEEE trans on Image Processing.

- [12] Forchheimer R., Ingelhag P., Jansson C., MAPP2200, a second generation smart optical sensor, SPIE Vol 1659, 1992.

- [13] Forchheimer R., Ödmark A., Single chip linear array processor, in Applications of digital image processing, SPIE, Vol. 397, (1983).

- [14] Ingelhag P., Åström A., Chen K., Svensson C., Ehlersson T., RADAR Signal Processing Using A 512-Processor Array Chip. ICDP91, Florence, Italy 1991.

- [15] Garda P., Reichart A., Rodriguez H., Devos F., Zavidovique B, Yet Another Mesh Array Smart Sensor, Proc of ICPR88, Rome, Italy.

- [16] Johanneson M., Åström A, Danielsson P.-E., *A Range Image Architecture Using Sheet of Light*, Proc of IAPR Workshop of Machine Vision Applications, Japan, 1992.

- [17] Johanneson M., Åström A, Sheet-of-light Range Imaging with MAPP2200, Proc of SCIA8-93, Tromsø, Norway.

- [18] Johanneson M., Åström A, Ingelhag P., *The RVIP Image Processor Array*, To appear in Proc of CAMP93, New Orleans, USA.

- [19] Lyon R.F., The optical Mouse, and an Architectural Methodology for Smart Digital Sensors. Palo Alto Research Center.

- [20] Mead C., Analog VLSI and Neural Systems, Addison-Wesley, 1989

- [21] Renshaw D., Denyer P. B., Lu M., Wang G., On-chip CMOS Sensors for VLSI Imaging Systems, Proc VLSI-91, 1991.

- [22] Tremblay M., Larendeau D., Poussart D., Multi Module Focal Plane Processing Sensor with Parallel Analog Support for Computer Vision, Proc of Symposium on Integrated Systems, Seatle, 1993.

- [23] Bernard T., Zavidovique B, Devos F., *A Programmable Artificial Retina*, IEEE Journal of Solid-State Circuits, vol 28, no 7, July 1993.

# Part I PASIC

#### 1 Introduction

### 1.1 Background

Over the last 15 years image processing has established itself as a respectable scientific discipline. However, the great breakthrough in industrial applications has not yet been seen. The reason seems to be that the industry wants small, well defined and inexpensive systems that are easy to maintain, while the hardware developers often come up with big, general purpose and, due to that, expensive systems that require a continuous professional maintenance. This situation will force the vendors of image processing system to change their policy. They will probably have to make more compact systems that are less all-purpose but has the advantage of being cheap. The enormous development that has taken place within the field of VLSI the last 20 years, seems to be the key to the solution. Today we have efficient tools to produce compact, inexpensive, specialized, but yet powerful systems.

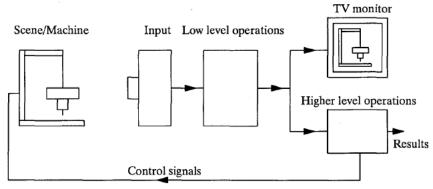

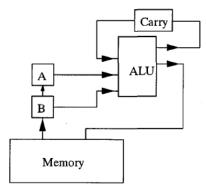

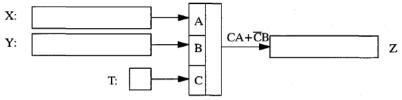

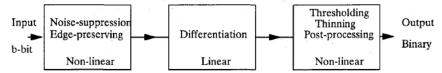

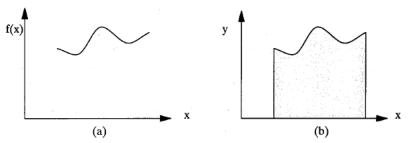

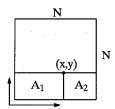

A typical machine vision system is shown in Figure 1.1. First, we have to get an image of the real world into some appropriate digital form. This is accomplished by using a number of photo-sensors followed by an A/D-converter. Secondly, we apply a number of low level operations on our image, such as convolutions, morphological operation and so on. These operation are often performed with a high degree of locality, i.e. they are mostly neighborhood operations. Finally, the output from the system could be either a preprocessed image, in which case we are finished, or used to produce a feedback in form of a control signal to the machine that the system is supervising. In the later case we will have to perform some higher level operations such as classification or decision to produce the control signal. Both type of systems are shown in Figure 1.1.

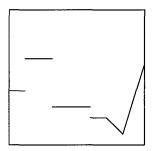

Figure 1.1, A typical image processing system

Today, modern VLSI technology makes it possible to integrate the input and the low level operations into one single chip. Such a chip can take in an image and apply fairly complex algorithms on the image and also extract features to be sent to higher level of processing. This type of chips are known as <u>smart sensors</u>.

This thesis will describe one such smart sensor called PASIC. PASIC stands for Processor, A/D-converter and Sensor Integrated Circuit. The project started in 1988 as a joint venture

between the Department of Electrical Engineering and the LSI Design center at the department of Physics and Measurement Technology, both at the University of Linköping.

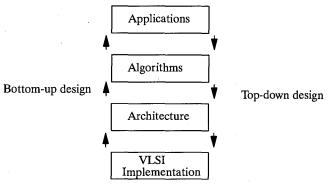

The architecture in a typical smart sensor is very VLSI driven. The design strategy is bottom-up meaning that the VLSI implementation sets the constraints for the architecture, which in its turn sets the constraints for the algorithms and the application. This strategy and the common top-down strategy are both illustrated in Figure 1.2. In both strategies the unidirectional influence has to be moderated and interleaved by verification loops. In fact, the main body of this thesis is part of such a procedure which verifies that PASIC efficiently can execute basic image processing algorithms. In several cases, the outcome of this verification has been fed back to a redesign at the VLSI level.

Figure 1.2, Bottom-up and top-down design

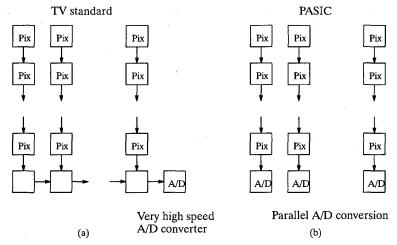

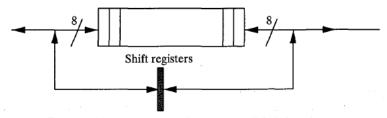

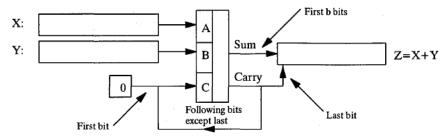

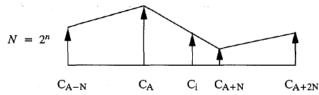

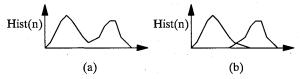

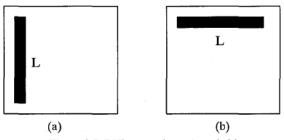

Most 2D image sensors are adapted to the standards of broadcast TV, see Figure 1.3(a). In CCD-cameras this means that every pixel first have to be shifted downwards and then, in a high speed, be shifted horizontally. Both shift paths carry data in analog representation. Every pixel then has to pass one common A/D-converter before it can be processed. The demands on the A/D-converter and the analog shift register are very high since we are dealing with pixel frequencies above 10 MHz.

In PASIC we have a 2D sensor, the A/D-conversion and the processing power integrated on a single chip. An immediate consequence is the possibility of a sensor layout as in Figure 1.3(b). To reduce the pixel frequency we insert more A/D-converters, ideally we would like to have one A/D-converter for each vertical column. If we could accomplish this we would avoid the high speed horizontal analog shift as well as the high speed A/D converter.

Figure 1.3, TV standard versus PASIC

The parallel A/D-conversion will become worthless unless we could process the data in a parallel fashion. This implies that beneath the A/D-converters there should be some form of linear processor array. The main character of the PASIC architecture took shape in this manner as will be shown in the next chapter of this thesis.

## 1.2 Bit-serial parallel processors

#### 1.2.1 An overview

Bit-serial processors have been used for quit a number of parallel computers most of them of type SIMD, (Single Instruction stream, Multiple Data stream). Many, but not all have been targeted for image processing. Some have been organized to communicate in a 2D mesh, for instance CLIP4 [10], DAP [14], MPP [1], CM1 and CM2 [17], and GAPP [11]. Others have a linear organization in form of a 1D array, for instance LUCAS [16] and AIS-5000 [18]. In the following sections we will take a brief look at the processor element in three of them, namely LUCAS, GAPP, and AIS-5000. Finally we will make a short presentation of LAPP, see [9], which is both a bit-serial machine, a smart sensor, and in many ways a predecessor of PASIC.

#### **1.2.2 LUCAS**

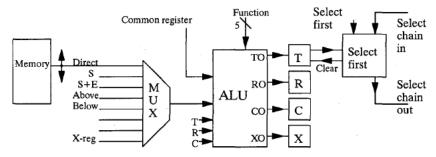

LUCAS was designed at Lund University, Sweden in the late 70's and is also a linear processor array. Each PE has an ALU using 5 inputs and 4 output functions. It also has its own

memory of 4096 bits, a special communication network called Select first network, and a communication multiplexer into the ALU, see Figure 1.4.

Figure 1.4, The processing element in LUCAS

The ALU has 5 input variables. Three of them are from the output registers, T(ag), R(esult), and C(arry). One is a common bit to all PEs to generate constants and one comes from the multiplexer. The multiplexer can select data from the PE's own memory or the auXilary register, called Direct and X. It can take data from its nearest neighbors, called Above and Below. Finally, it can take data from a perfect shuffle/exchange pattern, called S and S+E. This exchange pattern is used in for instance FFT computation.

The functions from the ALU to the output registers can be chosen from a set of 32 different functions. This means that we can perform both arithmetics and logic operations. An addition of two bit vectors consists of three steps. First load one bit from the first vector into the R register, then add the bit from the second vector with the R and C, and finally store the content of R in the memory. These three phases are repeated b times, where b is the number of bits. Thus, an addition is performed in 3b cycles.

With the Select first network, all the T-bit except the one in first PE is reset. The select feature is part of LUCAS' ambition to do associative processing.

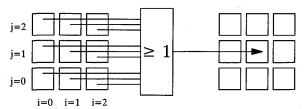

#### 1.2.3 GAPP

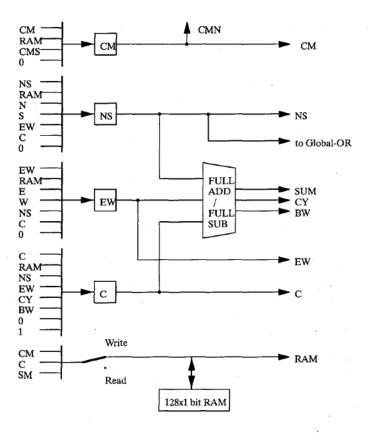

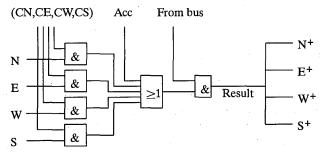

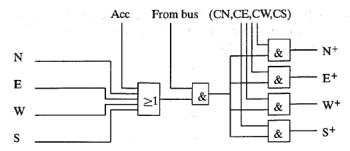

GAPP was developed at NCR in United States and presented as a product in 1984. The processor element, the PE, in GAPP contains four 1-bit registers, 128 bits of static RAM, 5 multiplexers to feed the input registers and the memory, one ALU, and connections to the four nearest neighbors, north, east, west, and south. This is shown in Figure 1.5.

The data input to the PEs are carried out by the CM registers. By opening the CMS-input, data is shifted in without interfering with the logical and arithmetic computation within the PE. The ALU unit is a full adder/subtracter which enables us to perform arithmetic as well as logic. A normal addition is setup by loading the NS and the EW registers with the two bits that we want to add. For each pair of input bits we store the result in the memory and at the same time feed the Carry from the previous result back to the C register. This means that an addition is done in 3b cycles, where b stands for the number of bits.

Figure 1.5, The processing element in GAPP

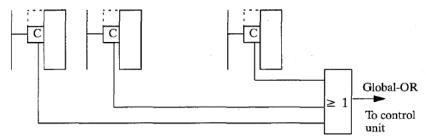

GAPP is equipped with a Global-OR function. This is an output pin on the chip that delivers a logical-OR of all NS registers in the array, which means that if any NS register holds the value 1, the Global-OR will be 1. This function can be used to terminate loops and to check for unwanted conditions.

GAPP has been used in a number of test design and experiments on parallel architecture but was never a great success.

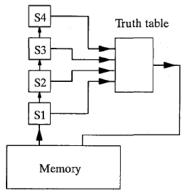

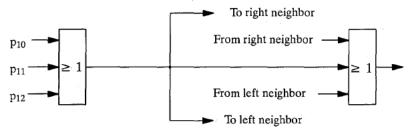

#### 1.2.4 AIS-5000

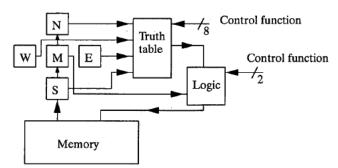

AIS-5000 is a commercially successful linear array of processors from Applied Intelligence, Ann Arbour, USA. The PE of AIS-5000 has four input registers. These can be arranged in different configurations depending on what task we want to perform. To perform a Boolean operation the registers are connected as in Figure 1.6. The truth table is pre-loaded with a arbitrary 16-bit value, which is common to the whole array. We can now load the S1 to S4 register with values and then read out the result from the truth table back into the memory.

The registers S1 to S4 are connected as a shift register which means that if we only want to change the value of for instance S2, we will have to shift in S1, S3, and S4 again.

Figure 1.6, AIS-5000 configurations for boolean operations

The arithmetic configuration is shown in Figure 1.7. The two input registers are loaded with the bit vectors from the memory. For each bit pair the result is written back to the memory and the Carry output is stored in the carry register, which means that it takes 3b cycles to perform an addition.

Figure 1.7, AIS-5000 configurations for arithmetic operations

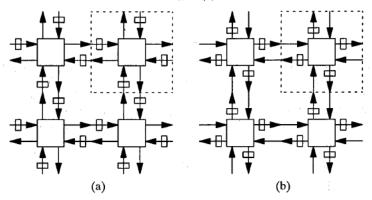

Finally AIS-5000 has the possibility to compute neighborhood binary templets in one cycle. The north, south, and center pixels are fetched from each PE. The east and west pixels are taken directly from the neighboring PEs, see Figure 1.8. The data paths makes it possible to perform erosion, dilation, and any other Boolean function on the neighborhood data in one cycle, by programing the truth table and the logic block in the appropriate way.

Figure 1.8, AIS-5000 configurations for neighborhood operations

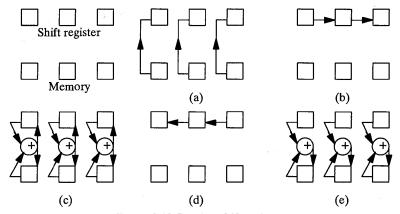

#### 1.2.5 LAPP

LAPP differs from the other processors that we have described, since it is has both input capability and processing power. It even contains these two features on one single chip. In many aspects LAPP has been an inspiration for PASIC, which can be thought of as a second generation of LAPP.

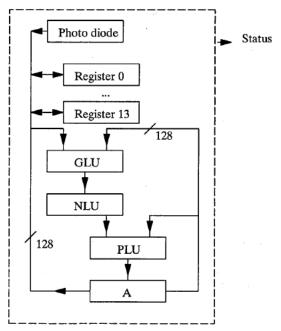

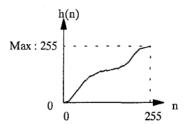

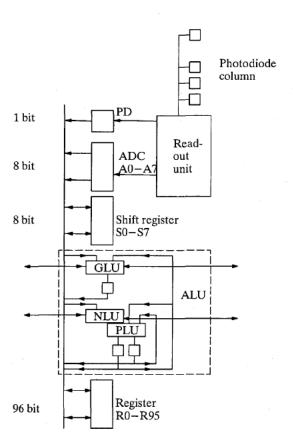

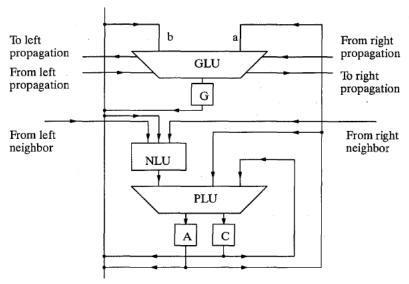

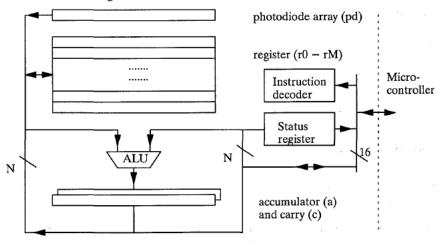

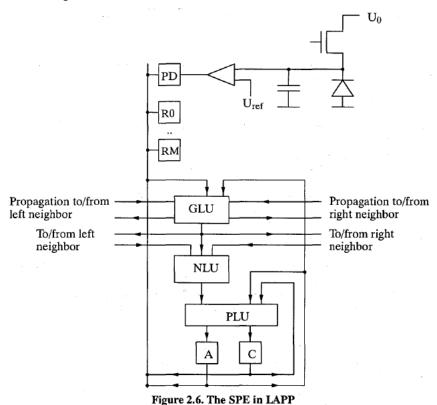

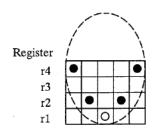

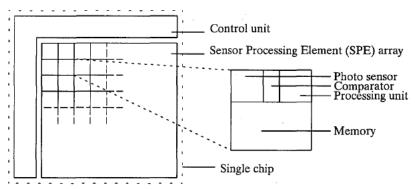

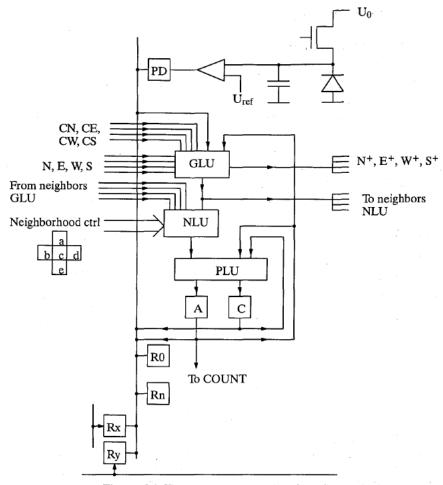

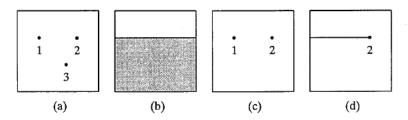

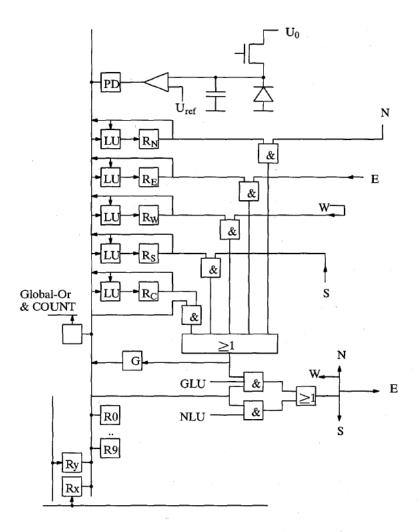

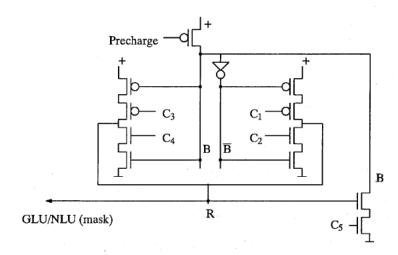

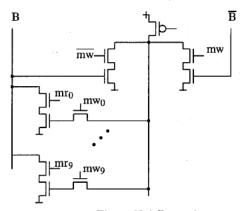

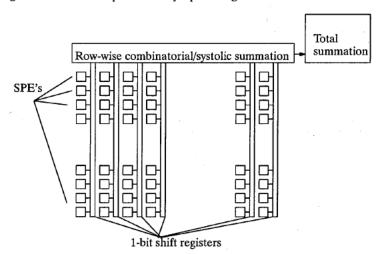

LAPP consists of a linear photo sensor array, 14 registers, one accumulator, and an ALU complex consisting of GLU, NLU, and PLU, see Figure 1.9.

Figure 1.9, The LAPP architecture

The image that we get from the photo sensor array is binary. However, as it is possible to adjust the thresholding level of the input line by an external reference voltage, it is possible

to some extent to work with gray scale images. The size of the photo diode array, the registers, the accumulator, and the logic is all 128 units.

A special hardware logic, the status output, detects and reports the number of 1s in the accumulator and, in the case there is a single 1, the position.

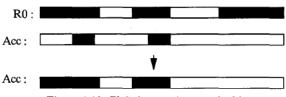

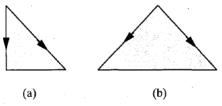

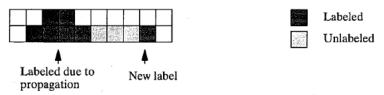

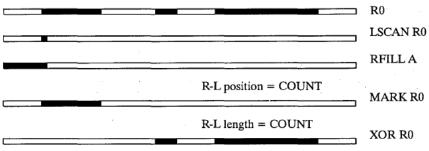

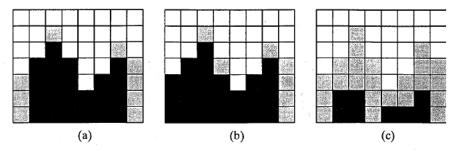

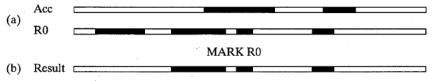

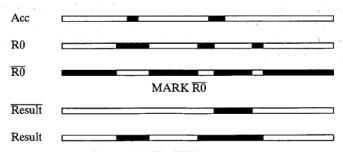

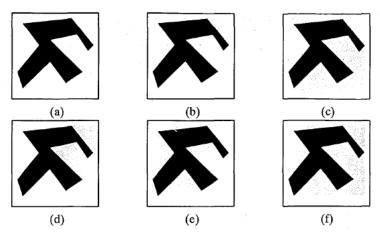

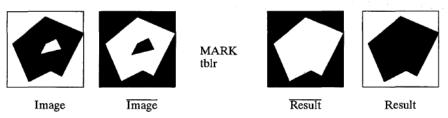

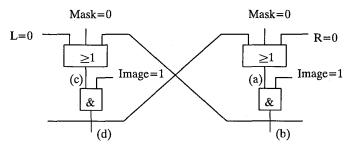

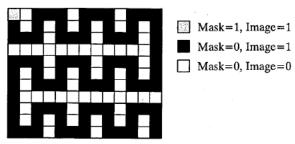

The ALU consists of three parts, the GLU, the NLU, and the PLU. The GLU, Global Logical Unit, performs global operation on the line, such as fill hole and mark object. Figure 1.10 shows the instruction MARK. All following instructions examples is taken from [13]. An object is considered to be a group of connected 1's, represented as black in the following Figures. MARK R0 means that all 1's in R0 which are within the same object as a pixel that has a 1 in the accumulator, is set to 1.

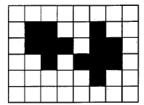

Figure 1.10, Global operation, mark objects

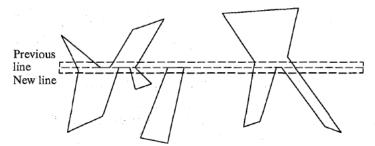

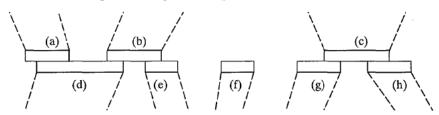

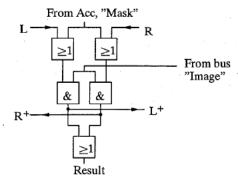

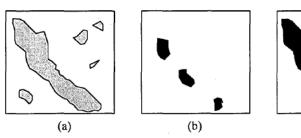

The NLU, Neighborhood Logical Unit, performs operation in a 3 by 1 neighborhood, like Erosion and Dilation. Each PE match its neighborhood with a common pattern containing three symbols, 0,1, and X don't care. To extract the left edges of the objects we use the LEDGE function, see Figure 1.11. This corresponds to the 01X pattern, which means that all 1 pixels remain set if they have a 0 neighbor to the left.

Figure 1.11, Neighborhood operation, find left edges

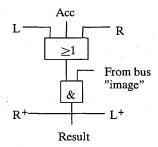

Finally, we have the PLU, Point Logical Unit, which performs logical and command instructions, such as AND, EXCLUSIVE-OR, and Load accumulator. Figure 1.12 shows an example of an OR operation, where the content of R0 and the accumulator are logically Ored.

Figure 1.12, Point logic operation, OR between R0 and the accumulator

LAPP has been a commercially successful product and a number of systems has been delivered. One common application for LAPP in industry is to measure length and width of moving objects.

# 2 The PASIC Architecture

#### 2.1 Overview

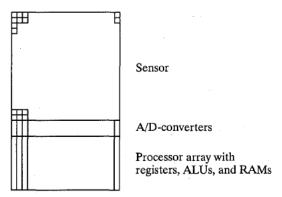

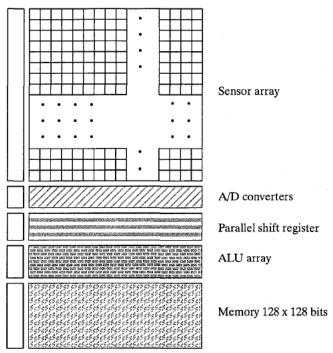

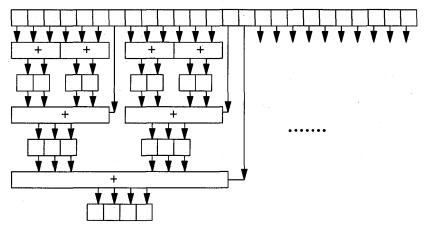

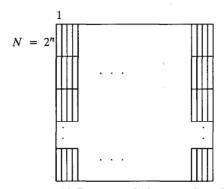

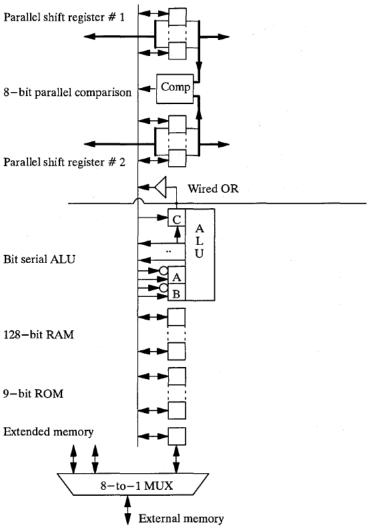

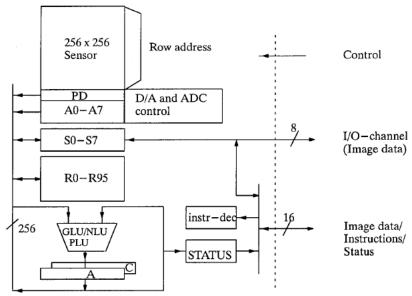

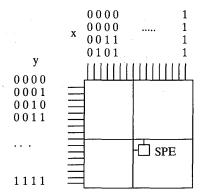

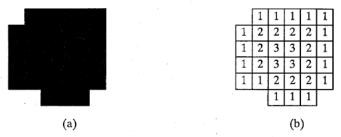

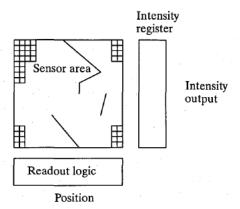

PASIC consists of three major parts: Sensors, A/D-converters, and Processors. The sensors form a two-dimensional array of photo sensors. Each column of the sensor area has its own A/D-converter and Processing Element. Thus, if we include the sensor column and the A/D-converter in the PE concept it makes perfectly sense to claim that the whole PASIC chip is organized as a 1D array of PEs. Each PE consists of a column of sensors, an A/D-converter, a register, an ALU, and a RAM. An out-line of the floor-plan of PASIC will then look like Figure 2.1.

Figure 2.1, PASIC

# 2.2 The photo sensors

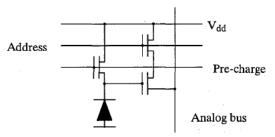

The sensor array consists of a matrix of photo diodes. Each sensor column is connected to its A/D-converter over a single bit bus, see Figure 2.2. The readout from the sensors is done line-by-line controlled by a vertical address decoder. The readout is non-destructive and the sensor array may be addressed randomly as well as scanned in any ordered manner. The reset of the elements is performed over a pre-charge line common to all photo sensors in a row. Each photo diode is guarded against blooming. In the present version of PASIC the size of the photo diodes is  $48x48\mu m^2$ , with a pitch of  $60\mu m$  in both dimensions.

Figure 2.2, An image sensing element

Control and addressing of the sensor array requires 8 bits as shown in Table 2.1. The leading bit selects between pre-charge and read-out.

| $P/\overline{R}$ | Address | Operation                        |

|------------------|---------|----------------------------------|

| 0                | 0000000 | Connect row 0 to A/D converter   |

| 0                | 0000001 | Connect row 1 to A/D converter   |

| 0                |         |                                  |

| 0                | 1111111 | Connect row 127 to A/D converter |

| 1                | 0000000 | Pre-charge row 0                 |

| 1                | 0000001 | Pre-charge row 1                 |

| 1                |         |                                  |

| 1                | 1111111 | Pre-charge row 127               |

Table 2.1, Sensor array operations

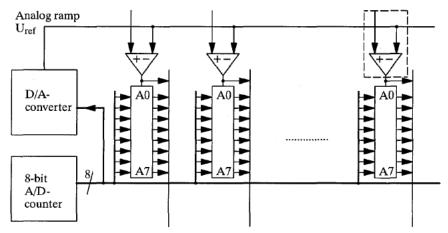

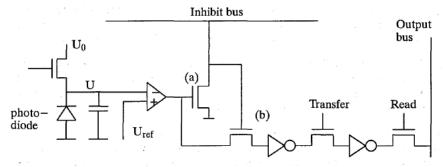

#### 2.3 The A/D converters

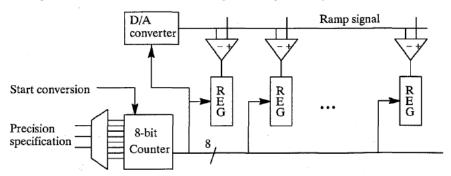

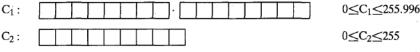

As was indicated in chapter 1, PASIC contains one A/D-converter for each column, which greatly reduces the requirement for high speed transfer of analog data over the chip. The Parallel A/D converter array consists of one counter, one D/A-converter, 128 comparators, and 128 8-bit registers, see Figure 2.3. The Counter is controlled by one control signal Start and one control field which specifies Precision. The Start signal activates the A/D-converters to perform an A/D-conversion with the precision specified by Precision field.

Figure 2.3, The parallel A/D-converter

Each bit in the register is a three transistor RAM cell. The value of the counter is broadcasted and written into the register as long as the ramp signal is less than the analog input. When an input analog signal in one channel is equal to the ramp value, the output of the comparator prohibits further writing. The 128 A/D-conversions are completed after a full ramp generation. The system clock of PASIC is 20 MHz. However, the A/D converter is stepped in 10 MHz rate to allow for the comparators to stabilize. One 8-bit A/D-conversion is therefore done in 256 \* 0.1  $\mu s = 25.6 \,\mu s$ . Since the resolution in the conversion is programmable it is possible to trade speed for precision. For instance, if we settle for 7 bits we may double the speed, for 6 bits quadruple it and so on. In many vision tasks such a programmability seems to come in handy. Since we have full control over the read out from the sensor, including the frame rate, it is possible to increase or decrease the signal-to-noise level.

The registers in Figure 2.3 are actually designed as RAM cells in a  $8 \times 128$  bits memory. The read out to the memory bus is controlled by a 3-to-8 decoder, see Figure 2.4. Altogether the A/D-conversion needs 5 bits in the control word shown in Table 2.2. The first bit is to start the A/D-conversion. The second bit changes the effect of the three last bits,  $CD_0$  to  $CD_2$ , from the indicating the bit to be read out from the A/D to selecting the precision in the A/D-conversion. If the two first bits are 00 or 11 the A/D-converter is either in data latch (quiescent) mode or in progress with an A/D-conversion.

| Start | Control | CD <sub>210</sub> | Operation                                 |

|-------|---------|-------------------|-------------------------------------------|

| 0     | 0       | x x x             | Data latch                                |

| 0     | 1       | 0 0 0             | Write bit position 0 to bus               |

| 0     | 1       | 0 0 1             | Write bit position 1 to bus               |

| 0     | 1       |                   |                                           |

| 0     | 1       | 1 1 1             | Write bit position 7 to bus               |

| 1     | 0       | 0 0 0             | Start A/D-conversion with 1-bit precision |

| 1     | 0       | 0 0 1             | Start A/D-conversion with 2-bit precision |

| 1 .   | 0       |                   |                                           |

| 1     | 0       | 1 1 1             | Start A/D-conversion with 8-bit precision |

| 1     | 1       | $x \times x$      | Data latch                                |

Table 2.2, A/D-conversion operations

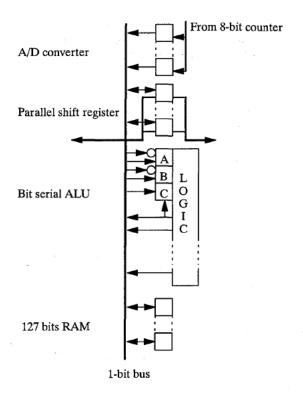

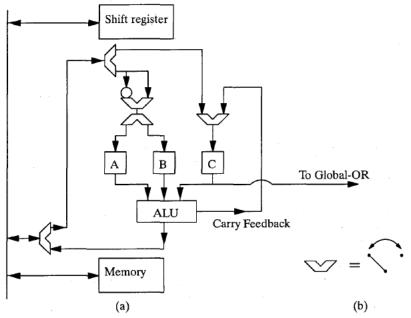

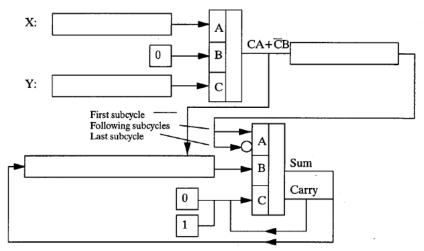

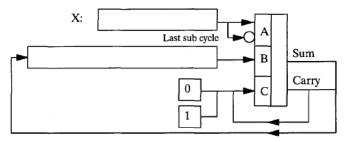

# 2.4 The processing elements, PE

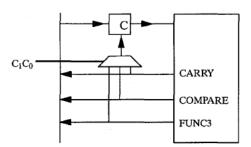

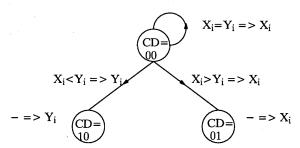

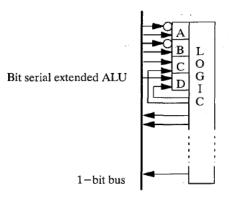

Each processing element consists of three parts, one bi-directional parallel shift register, one ALU-unit, and a memory. Figure 2.4 illustrates that all these units plus the A/D-converter are connected to the same bus. This is a 1-bit bus architecture, meaning that all operations can be seen as transfers over the 1-bit bus. As we will see later on there are a few exceptions from this. This architecture was first proposed by dr Keping Chen, former project leader of the PASIC project.

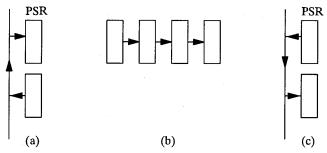

The parallel shift register contains 8 bits and is a bi-directional shift register, see Figure 2.5. Thus, we can shift a pixel value one step to the left or the right in one clock cycle. 8-bit parallel communication seems a reasonable choice since image processing often deals with 8-bit pixels. This shift register has 7 modes of operation, and it uses 3 control bits, PSC<sub>0</sub>, PSC<sub>1</sub>, and PSC<sub>2</sub>, listed in table 2.3. In 000 and 001 the register communicates with the bus. For 011 and 100 the register content is shifted one step in the desired direction. For a left shift data will be shifted one step to the left leaving the leftmost PE's data to the left I/O-pins, and at the same time input data are accepted from the right I/O-pins. Operations 101 and 110 are identical to 011 and 100 except that end around shift takes place and no I/O operation is performed.

Figure 2.4, The digital architecture of PASIC

| PSC <sub>210</sub> | Operation                                                  |

|--------------------|------------------------------------------------------------|

| 000                | Write into specified bit position in register from the bus |

| 001                | Read from specified bit position in register to the bus    |

| 010                | Latch                                                      |

| 011                | Shift left                                                 |

| 100                | Shift right                                                |

| 101                | Rotate left                                                |

| 110                | Rotate right                                               |

Table 2.3, Parallel shift register operations

Figure 2.5, Possible data path in the parallel shift register

The ALU is capable of evaluating 1-, 2-, and 3-input Boolean functions. It has 3 input registers and 8 output functions. The three input registers are called A, B, and C. The output functions are listed in Table 2.4. It is possible to load A and B with inverted data.

| Name          | Boolean function                             |

|---------------|----------------------------------------------|

|               |                                              |

| Carry         | AB+AC+BC                                     |

| Sum           | A⊕B⊕C                                        |

| $Multiplex_c$ | CA+CB                                        |

| $Multiplex_c$ | CA+CB                                        |

| NAND          | AB                                           |

| NOR           | A+B                                          |

| XOR           | $A\overline{B} + \overline{A}B = A \oplus B$ |

| Not           | B                                            |

Table 2.4, Boolean functions in PASIC

The ALU is designed in such a way that it is not possible to take data from one output to the bus and load it into an input register in a single clock cycle. Therefore, the input and output selection of the ALU can use the same decoder. The control signals are called  $PC_0$ ,  $PC_1$ ,  $PC_2$ , and  $PC_3$ , see Table 2.5.

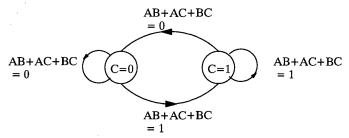

A very common operation in all types of algorithms is addition and when we perform an addition the carry is to be fed back to one of the input registers. To speed up the addition we have provided an extra data path from the carry output to the C register. This extra path is called Carry-feedback and it is controlled by a single bit. It enables us to perform various arithmetics with the same efficiency as other bit-serial processors.

| PC <sub>3210</sub> | Function                       |

|--------------------|--------------------------------|

| 0000               | A NOR B to bus                 |

| 0001               | A NAND B to bus                |

| 0010               | Carry to bus                   |

| 0011               | Bus to C                       |

| 0100               | Mux A to bus                   |

| 0101               | Mux $\overline{A}$ to bus      |

| 0110               | Bus to B                       |

| 0111               | $\overline{\mathtt{B}}$ to bus |

| 1000               | Bus to B                       |

| 1001               | A XOR B to bus                 |

| 1010               | Bus to A                       |

| 1011               | Bus to A                       |

| 1100               | Sum to bus                     |

| 1111               | Idle                           |

Table 2.5, ALU operations

The memory consists of 127 bits of dynamic RAM and one bit of ROM. The latter is set to zero and located at address zero. With this bit we can produce constants. The memory is controlled with 8 bits, listed in Table 2.6.

| Read/Write | Address | Operation                        |

|------------|---------|----------------------------------|

| 0          | 0000000 | Read a constant zero from memory |

| 0          | 0000001 | Read from memory cell 1          |

| 0          |         |                                  |

| 0          | 1111111 | Read from memory cell 127        |

| 1          | 0000000 | No operation                     |

| 1          | 0000001 | Write to memory cell 1           |

| 1          |         |                                  |

| 1          | 1111111 | Write to memory cell 127         |

Table 2.6, Memory operations

The 127 bits of RAM are a dynamic non-refreshed memory. This means that the user must make sure that all memory cells are rewritten with a frequency of at least 1 kHz, either as a natural course of events in the program execution or by means of extra rewriting cycles. A refresh cycle takes two clock cycles per bit as we have to read from the memory to the ALU or the shift register, and then write that bit back to the memory. In the worst case the refresh of the memory, where  $N_b=127$ ,  $f_{refresh}=1$  kHz, and  $f_{system}=20$  MHz, will take 1.3 % of the execution time, see Equation (2.1).

$$\eta = 2N_b \frac{f_{refresh}}{f_{system}} \tag{2.1}$$

In most cases the algorithm uses the memory cells in such a way that we do not need any extra refresh cycles.

#### 2.5 **VLSI**

The physical VLSI layout of PASIC is shown in Figure 2.6. The boxes to the left of the array is control logic for decoding. Further reading about the VLSI design can be found in [3]. The vertical size of each block is shown in Table 2.7. The horizontal size of PASIC is 7.7 mm.

| Region                                  |        | Size | (mm) |

|-----------------------------------------|--------|------|------|

| Sensor                                  |        | 7.7  |      |

| A/D-conv                                | erter  | 0.3  |      |

| PE                                      |        | 2.0  |      |

|                                         | PSR    | 0.5  |      |

|                                         | ALU    | 0.5  |      |

|                                         | Memory | 1.0  |      |

| ======================================= |        |      |      |

|                                         |        | 10.0 |      |

Table 2.7, The size of the building block of PASIC

Figure 2.6, The VLSI layout

# 2.6 The programming model

The control word for PASIC consists of 32 bits, as shown in Figure 2.7. Each unit in Figure 2.6 has its own field in the micro word. Due to the decoding, timing, and delay effects, we are limited in the way that the units can interact with each other. For instance, it is not normally possible to take the content of a boolean function and feed it back to some register, nor to read data from the parallel shift register while it is shifting.

| 8 bits                     | 5 bits      | 6 bits                  | 5 bits | 8 bits |  |  |  |  |  |

|----------------------------|-------------|-------------------------|--------|--------|--|--|--|--|--|

| Sensor address             | A/D control | Parallel shift register | ALU    | Memory |  |  |  |  |  |

| Figure 2.7, The micro word |             |                         |        |        |  |  |  |  |  |

The execution flow consists of two parallel processes, one part to control the sensor and the A/D-conversion, and the other to do the digital computation. These two parts are integrated into one single program.

The addressing of the sensor array and the control of the A/D-conversion is typically done once every 256 cycles, while the computation is done both during and between the conversions. A typical example is a low pass filtering of the image, shown in pseudo code in Table 2.8. In this example the result image is obtained by adding the value of the pixel to the left, its own value, and the pixel value to the right.

```

Loop over all rows

! Read from A/D registers

Loop over all bits

Read_A/D

End-loop

Reset(R-1)

! Pre-charge row R-1

Sensor_to_AD(R), Start_AD(P) ! Connect row R to sensor and perform an

! A/D conversion with P bit precision.

Loop over a neighborhood ! Get left and right

Loop over all bits ! Add them together

! Get left and right pixel

ADD

End-loop

End-loop

Output_pixel

! Output the pixels

End-loop

```

Table 2.8, A program example for low pass filtering

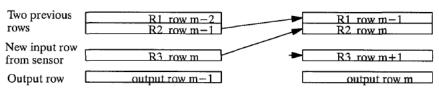

The outer loop starts by taking the data from the A/D register, resetting corresponding row in the sensor and starting the conversion of the next row. The time window for light exposure in the sensor is therefore skewed from one line to the next.

Next follows a loop over the neighborhood, in this case the left and right neighbors. We get their values and add them together with the PE's own value. The adding is done in the innermost loop, the bit loop. The row-loop ends with a transfer of bits to the shift register and shift-out of data.

Typically, as in the above example, the computation in PASIC consists of three nested loops. The overall loop is the loop over all rows and is normally done 128 time per frame. However, as we have the possibility to address the row of the sensor randomly, we can reduce the resolution and thereby the number of rows to 64, 32 or less. The size of the neighborhood loop depends on what algorithm we are using, in our case this was 3 x 1. If we use an algorithm that does not use any neighborhood processing, this loop is omitted. Embedded in the other loops are the bit loops, where the number of bits depends on the precision and word length. For the case of simplicity we will hereafter omit all addressing of the sensor and the control of the A/D-converter, and presume that the pixel values are presented in the A/D register when we want them.

As mentioned earlier there are some data moves that seem possible from just looking at Figure 2.4 but which are prohibited in PASIC. The following rules must be obeyed.

- (1) Due to self-imposed decoding and addressing limitation, data cannot be taken directly from an ALU output and loaded into an ALU input register in one cycle. Thus, if we want to load an input register with an ALU function we will have to use the memory or the shift register as a temporary storage and execute the procedure in two cycles.

- (2) Two input registers cannot receive the same data from the bus in one clock cycle. For instance, we cannot zero two registers in the same cycle. This is also due to the decoding limitation.

- (3) We cannot load a bit in its inverted form to the C register, only to the A and B registers.

In some cases the Carry-feedback path helps us to overcome the problem of (1) and (2), as we can retrieve the Carry from the ALU back to the C register without interfering with the bus. An attempt to illustrate the limitations and the data paths is shown in Figure 2.8(a) where each mux-symbol represents a switch, see Figure 2.8(b).

Figure 2.8, A different programming model of PASIC

We can now clearly see that we cannot break the three rules mentioned earlier. For instance, if we use an output function, the only data we can load in the input registers is the Carry to the Cregister using the CarryFeedback path. Similarly, if we connect the bus to the A register, the output functions and the B input are disabled. However, C can again be loaded from the CarryFeedback.

# 3 Basic instruction set

#### 3.1 Boolean functions

The ALU in PASIC generates 8 different 3-input Boolean functions. They are all combinatorial functions of the 3 input registers A, B, and C and listed in Table 3.1.

| Name          | Boolean function                             |

|---------------|----------------------------------------------|

|               |                                              |

| Carry         | AB+AC+BC                                     |

| Sum           | A⊕B⊕C                                        |

| $Multiplex_c$ | CA+CB                                        |

| $Multiplex_c$ | CA+CB                                        |

| NAND          | AB                                           |

| NOR           | A+B                                          |

| XOR           | $A\overline{B} + \overline{A}B = A \oplus B$ |

| Not           | B                                            |

Table 3.1, Boolean functions in PASIC

As was shown in chapter 2, the A and B registers can be loaded from the bus with inverted values,  $(\overline{X} \text{ and } \overline{Y} \text{ respectively})$ . Hereby, all non-trivial 2-input functions can directly be retrieved at the outputs as shown in Table 3.2.

| X<br>Y | 0     | 0<br>1 | 1<br>0 | 1  | Boolean<br>function               | Input operation                    | PASIC<br>function |

|--------|-------|--------|--------|----|-----------------------------------|------------------------------------|-------------------|

|        | <br>0 | 0      | 0      | 0  | 0                                 |                                    |                   |

|        | 0     | 0      | 0      | 1  | XY                                | $A:=\overline{X}, B:=\overline{Y}$ | A+B               |

|        | 0     | 0      | 1      | 0  | $X\overline{Y}$                   | $A:=\overline{X}, B:=Y$            | <del>A+B</del>    |

|        | 0     | 0      | 1      | 1  | х                                 |                                    |                   |

|        | 0     | 1      | 0      | 0  | $\overline{X}Y$                   | $A:=X,B:=\overline{Y}$             | <del>A+B</del>    |

|        | 0     | 1      | 0 .    | 1. | Y .                               |                                    |                   |

|        | 0     | 1      | 1      | 0  | х⊕ч                               | A:=X, B:=Y                         | A⊕B               |

|        | 0     | 1      | 1      | 1  | X+Y                               | $A:=\overline{X}, B:=\overline{Y}$ | AB                |

|        | 1     | 0      | 0      | 0  | $\overline{X+Y}$                  | A:=X,B:=Y                          | A+B               |

|        | 1     | 0      | 0      | 1  | $\overline{X \bigoplus X}$        | $A:=\overline{X}, B:=Y$            | A⊕B               |

|        | 1     | 0      | 1      | 0  | $\overline{Y}$                    | B:=Y                               | B                 |

|        | 1     | 0      | 1      | 1  | $X+\overline{Y}$                  | $A:=\overline{X}, B:=Y$            | ĀB                |

|        | 1     | 1      | 0      | 0  | $\overline{\mathbf{X}}$           | B:=X                               | B                 |

|        | 1     | 1      | 0      | 1  | $\overline{X}+Y$                  | $A:=X, B:=\overline{Y}$            | AB                |

|        | 1     | 1      | 1      | 0  | $\overline{X}{\cdot}\overline{Y}$ | A:=X,B:=Y                          | ĀB                |

|        | 1     | 1      | 1      | 1  | 1                                 |                                    |                   |

Table 3.2, All possible two input Boolean functions

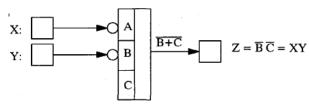

The actual execution of a 2-input function is illustrated in Figure 3.1 by an AND operation between the memory cell X and memory cell Y. The result is going to be stored in memory cell Z. First we place an inverted version of the memory content of X in register A. In the next cycle we put an inverted version of Y in register B. Finally we take the content of the output register  $\overline{A+B}$  and place that in memory cell Z.

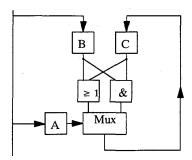

Figure 3.1, Z := X AND Y

3-input functions are performed in the same manner. For instance, a very useful operation is to select one of two **b**-bit vectors, in X and Y respectively, depending on the value of bit T, and store this vector in Z. This is called <u>multiplexing</u>. (We will often work with multi-bit words, for example a byte = 8 bits. Therefore, we will hereafter refer to the number of bits by the constant **b**). First we place T in the C register. Then we move the first bit in X and Y over the bus to registers A and B. We then read out the output  $CA + \overline{CB}$  and store in Z. This process is than repeated **b** times. The whole operation takes 3b+1 clock cycles and is described in Figure 3.2.

Figure 3.2, Multiplexing

There are 256 possible 3-input functions. To see exhaustively how many of these functions we can realize in PASIC we would have to build a large table in the same manner as table 3.2. However, the 256 entry table can be reduced on the following grounds.

- a) If one function f(x,y,z) can be implemented so can f(y,x,z) or any other permutation of the variables, since we are free to permute the inputs to (A,B,C).

- b) If a function f(x,y,z) = f(x,y,q) where q is a don't care, this function is really a 2-input function which we proved in Table 3.2 can be implemented directly.

- c) If a function f(x,y,z) can be implemented so can  $f(\bar{x},y,z)$ ,  $f(\bar{x},\bar{y},z)$ , and so on, since we have the possibility to invert the inputs to the A and B register.

When we use these three rules to find functions which are equivalently or trivially executed in PASIC, the number of different 3-input functions is reduced to 24, see Table 3.3.

|    | 0 1 0 1 0 1 0 1 | X                      |                                     |

|----|-----------------|------------------------|-------------------------------------|

|    | 0 0 1 1 0 0 1 1 | Y                      |                                     |

|    | 0 0 0 0 1 1 1 1 | Z                      |                                     |

| #  |                 | Function               | Name/equivalent function            |

| 0  | 0 0 0 1 0 1 1 1 | xy+xz+yz               | Carry                               |

| 1  | 0 1 0 1 0 0 1 1 | xz+yz                  | Mux                                 |

| 2  | 0 1 1 0 1 0 0 1 | x⊕y⊕z                  | Sum                                 |

| 3  | 0 1 1 0 1 1 1 1 | (x⊕y) z                | Comp1                               |

| 4  | 0 0 0 0 1 0 0 1 | x⊕y+z                  | Comp2                               |

| 5  | 0 0 0 0 0 0 0 1 | xyz                    | 3-AND                               |

| 6  | 0 0 0 0 0 1 1 1 | xz+yz                  |                                     |

| 7  | 0 0 0 1 0 1 1 0 | xyz+xyz+xyz            | x(y⊕z)+ <del>x</del> yz             |

| 8  | 0 0 0 1 1 0 0 0 | xy <del>z+xy</del> z   |                                     |

| 9  | 0 0 0 1 1 0 0 1 | xyz+xyz+xyz            | xy <del>z+ (x⊕y)</del> z            |

| 10 | 0 0 0 1 1 1 1 0 | xyz+yz+xz              | (xy)⊕z                              |

| 11 | 0 0 0 1 1 1 1 1 | xy+z                   |                                     |

| 12 | 0 0 1 1 1 1 0 1 | xy+xz+xz               | xy+x⊕z                              |

| 13 | 0 1 1 0 1 0 1 1 | x⊕y⊕z+xyz              |                                     |

| 14 | 0 1 1 1 1 1 1 0 | xy+xz+yz               |                                     |

| 15 | 0 1 1 1 1 1 1 1 | x+y+z                  | 3-OR                                |

| 16 | 0 1 1 0 1 0 0 0 | xyz+xyz+xyz            |                                     |

| 17 | 0 1 1 0 1 0 1 0 | xy+xyz+yz              | ȳ(x⊕z)                              |

| 18 | 1 0 0 0 0 0 0 0 | x·y·z                  | 3-NOR                               |

| 19 | 1 0 0 1 1 0 0 0 | xyz+xy                 |                                     |

| 20 | 10101000        | <del>x.y+y.z</del>     |                                     |

| 21 | 1 0 1 1 1 1 0 0 | xz+xz+yz               | $x \oplus z + \overline{y \cdot z}$ |

| 22 | 1 1 1 0 1 0 0 0 | <del>x.y+x.z+y.z</del> |                                     |

| 23 | 1 1 1 0 1 0 1 0 | x·z+y                  |                                     |

| 24 | 1 1 1 1 1 1 1 0 | x+y+z                  | 3-NAND                              |

Table 3.3, All unique three-input boolean functions

The first three functions in table 3.3, functions number 0 to 2, are the only one which are implemented in the original version of PASIC. In fact we have function number 1 in 2 versions, both  $CA+\overline{C}B$  and  $\overline{C}A+CB$  since we do not have the possibility to invert the C input. Number 3 and 4 are suggested in section 10.1 as an extension to the PASIC functions. Possibility to invert the input to the C register would reduce Table 3.3 to just 16 unique functions.

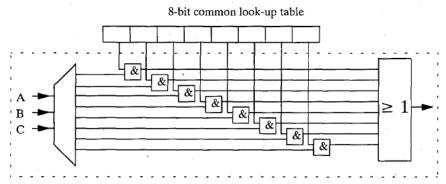

In some architectures, e.g. the Connection Machine, all 256 functions have been implemented. Consequently, in the Connection Machine any 3-input Boolean function is executed in four clock cycles. The first three are used to initialize the registers and the fourth to read out the output. One way to realize a 256-function machine is shown in Figure 3.3. The function is loaded into the 8-bit memory common to all the processors on the chip. Each processor generates its function output via a decoder followed by an AND/OR-network.

To say that a 3-input function takes 4 cycles to compute is of course not entirely true since the loading of the 8 bits into the memory takes at least one cycle. However, if we use the same function more than once or if the loading could take place in parallel with some other operation, 4 cycles per output bit is close to the true number.

Figure 3.3, A 256-function table look-up implementation

In PASIC the ALU only produce the three first 3-input functions in Table 3.3. The question then is: in how many clock cycles can we realize all 3-input functions. This is shown in Table 3.4, where we have compared PASIC with 256-M, a fictitious machine, that has the capability to realize all 256 function.

Table 3.4 shows that PASIC realizes most of the functions losing only one or two clock cycles compared to the optimum. Also, one should bear in mind that all functions do not have the same usage frequency. In general, Sum, Carry, and multiplexing, which we have implemented in PASIC, are far more common than other operations.

| #  | Boolean function                                                                        | 256-M | PASIC | Diff |

|----|-----------------------------------------------------------------------------------------|-------|-------|------|

| 0  | xy+xz+yz                                                                                | 4     | 4     | 0    |

| 1  | xz+yz                                                                                   | 4     | 4     | 0    |

| 2  | x⊕y⊕z                                                                                   | 4     | 4     | 0    |

| 3  | (x⊕y) z                                                                                 | 4     | 6     | 2    |

| 4  | x⊕y+z                                                                                   | 4     | 6     | 2    |

| 5  | xyz                                                                                     | 4     | 5     | 1    |

| 6  | xz+yz                                                                                   | · 4   | 5     | 1    |

| 7  | xyz+xyz+xyz                                                                             | 4     | 8     | 4    |

| 8  | xyz+xyz                                                                                 | 4     | 10    | 6    |

| 9  | xyz+xyz+xyz                                                                             | 4     | 8     | 4    |

| 10 | xyz+yz+xz                                                                               | 4     | 6     | 2    |

| 11 | xy+z                                                                                    | 4     | 6     | 2    |

| 12 | xy+xz+xz                                                                                | 4     | 8     | 4    |

| 13 | x⊕y⊕z+x <u>y</u> z                                                                      | 4     | 9     | 5    |

| 14 | xy+xz+yz                                                                                | 4     | 8     | 4    |

| 15 | x+y+z                                                                                   | 4     | 5     | 1    |

| 16 | xyz+xyz+xyz                                                                             | 4     | 9     | 5    |

| 17 | xy+xyz+yz                                                                               | 4     | 6     | 1    |

| 18 | x·y·z                                                                                   | 4     | 5     | 3    |

| 19 | xyz+xy                                                                                  | 4     | 8     | 4    |

| 20 | <u></u>                                                                                 | 4     | 6     | 2    |

| 21 | xz+xz+yz                                                                                | 4     | 8     | 4    |

| 22 | $\overline{x}\cdot y + \overline{x}\cdot \overline{z} + \overline{y}\cdot \overline{z}$ | 4     | 6     | 2    |

| 23 | x·z+y                                                                                   | 4     | 6     | 2    |

| 24 | <u>x+y+z</u>                                                                            | 4     | 5     | 1    |

Table 3.4, Performance of PASIC in three-input functions

PASIC does not have a specially dedicated accumulator. However, by using the Carry-feedback we can in some cases emulate an accumulator with the C-register. Depending on the value of A, the Carry function (3.1) can be interpreted as (3.2) or (3.3).

$$Cy = AB+AC+BC$$

(3.1)

$Cy_{A=0} = BC$  (3.2)

$Cy_{A=1} = B+C$  (3.3)

Figure 3.4 illustrates this in a logic-diagram of Equation (3.1).

Figure 3.4, Carry feedback used as an accumulator

As another example how to use the Carry-feedback data path, we show in pseudo code in Table 3.5 how to implement XZ+YZ, function 6 in Table 3.4.

Table 3.5, Implementation of XZ+YZ

The operation takes 5 clock cycles, which is just one cycle more than the minimum, and that is used to initialize the C register with a 0.

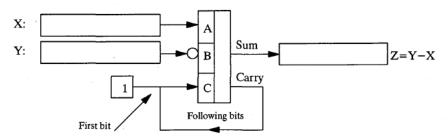

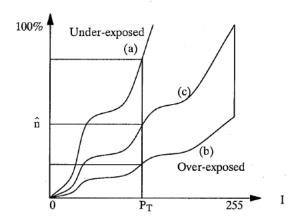

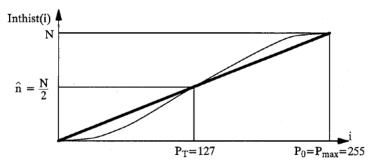

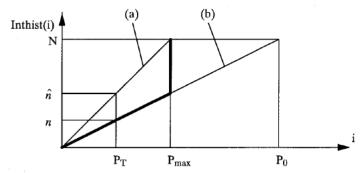

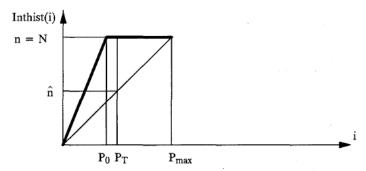

#### 3.2 Addition and subtraction

Basic arithmetic is supported in PASIC by two Boolean functions:

```

Carry = AB + AC + BC

Sum = A \oplus B \oplus C.

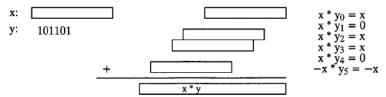

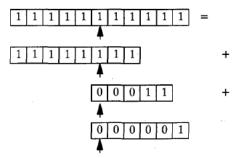

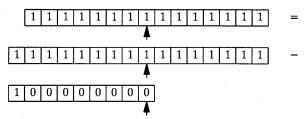

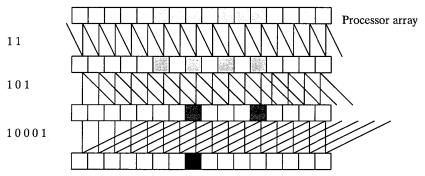

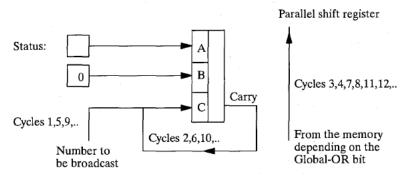

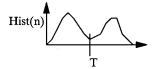

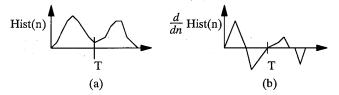

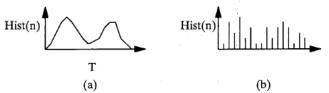

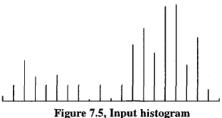

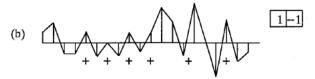

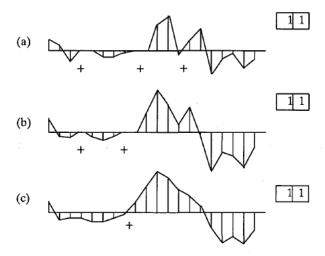

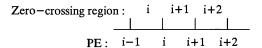

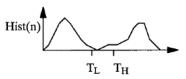

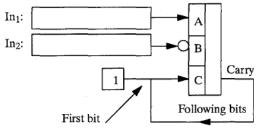

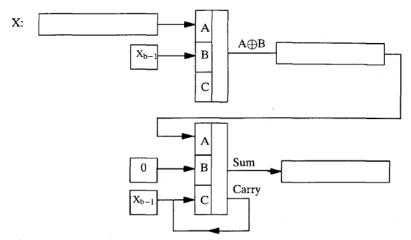

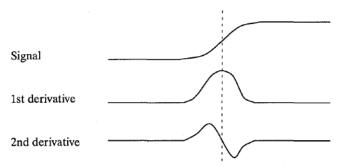

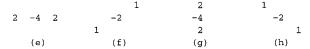

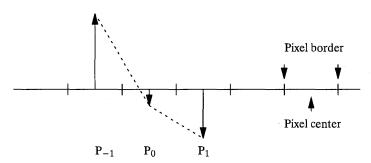

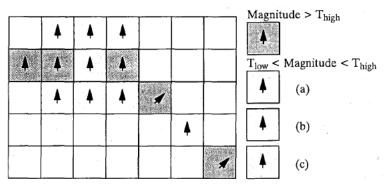

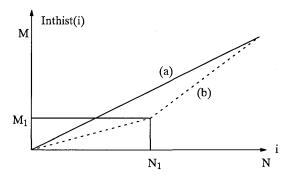

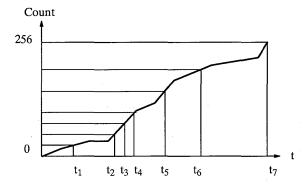

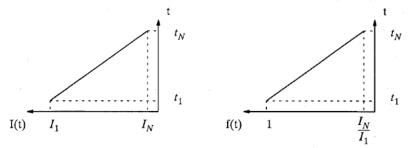

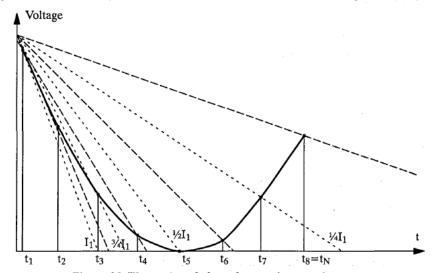

```