#### US005423019A

## United States Patent [19]

Lin

[11] Patent Number:

5,423,019

[45] Date of Patent:

Jun. 6, 1995

[54] AUTOMATIC CACHE FLUSH WITH READABLE AND WRITABLE CACHE TAG MEMORY

[75] Inventor: David Lin, San Jose, Calif.

[73] Assignee: OPTi Inc., Santa Clara, Calif.

[21] Appl. No.: 143,171

[22] Filed: Oct. 26, 1993

#### Related U.S. Application Data

[63] Continuation of Ser. No. 878,730, May 4, 1992, Pat. No. 5,287,481, which is a continuation-in-part of Ser. No. 812,074, Dec. 19, 1991.

[56] References Cited

U.S. PATENT DOCUMENTS

| 5,045,998 | 9/1991  | Begun et al       | 395/425 |

|-----------|---------|-------------------|---------|

| 5,091,850 | 8/1992  | Culley            | 395/400 |

| 5,157,774 | 10/1992 | Culley            | 395/425 |

| 5,210,850 | 5/1993  | Kelly et al       | 395/425 |

| 5,247,648 | 9/1993  | Watkins et al     | 395/425 |

| 5,293,603 | 3/1994  | MacWilliams et al | 395/425 |

Primary Examiner—Rebecca L. Rudolph

Assistant Examiner—Frank J. Asta

Attorney, Agent, or Firm—Fliesler, Dubb, Meyer &

Lovejoy

#### [57] ABSTRACT

A chipset is provided which permits reading and writing to cache tag memory for testing purposes and for writing non-cacheable tags into tag RAM entries to effectively invalidate the corresponding cache data entries.

7 Claims, 17 Drawing Sheets

Page 2 of 45

5,423,019

CONTROL REGISTER 1 INDEX: 20h

FIG. 2

| BIT | FUNCTION                                                                                                                                                       | FAULT |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7–6 | REVISION OF 82C391 AND IS READ-ONLY                                                                                                                            | 0 0   |

| 3   | SINGLE ALE ENABLE-SYSC WILL ACTIVATE SINGLE ALE INSTEAD OF MULTIPLE ALES DURING BUS CONVERSION CYCLE IF THIS BIT IS ENABLED.  O=DISABLE 1=ENABLE               | 0     |

| 2   | EXTRA AT CYCLE WAIT STATE ENABLE. INSERT ONE EXTRA WAIT STATE IN STANDARD AT BUS CYCLE. O=DISABLE 1=ENABLE                                                     | 0     |

| 1   | KEYBOARD AND FAST RESET CONTROL—TURN ON THIS BIT REQUIRES "HALT" INSTRUCTION TO BE EXECUTED BEFORE SYSC GENERATES CPURSTFROM KEYBOARD RESET 0=DISABLE 1=ENABLE | 0 .   |

| 0   | FAST RESET ENABLE-ALTERNATIVE FAST CPU RESET. 0=DISABLE 1=ENABLE                                                                                               | 0     |

CONTROL REGISTER 2

INDEX: 21h

FIG. 3

| BIT | FUNCTION                                                                                                                                                                                                                                                    | DEFAULT |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | MASTER MODE BYTE SWAP ENABLE<br>0=DISABLE 1=ENABLE                                                                                                                                                                                                          | 0       |

| 6   | FAST KEYBOARD RESET DELAY CONTROL  0=GENERATE RESSET PULSE 2 US LATER  1=GENERATE RESET PULSE IMMEDIATELY                                                                                                                                                   | 0       |

| 5   | PARITY CHECK<br>0=DISABLE 1=ENABLE                                                                                                                                                                                                                          | 0       |

| 4   | CACHE ENABLE 0=DISABLE 1=ENABLE                                                                                                                                                                                                                             | 0       |

| 3–2 | CACHE SIZE 3 2 CACHE SIZE 0 0 32KB 0 1 64KB 1 0 128KB 1 1 256KB                                                                                                                                                                                             | 00      |

| 1-0 | CACHE WRITE CONTROL  1 0 WRITE CONTROL  0 0=1 WAIT STATE, WRITE HIT CYCLE 0 1=0 WAIT STATE FOR 32KX8 SRAWs WHICH MAKES 128K OR 256K CACHE 1 0=NOT USED 1 1=0 WAIT STATE FOR 8KX8 SRAWs WHICH MAKES 32K OR 64K CHACHE NOTICE CHACHE READ ALWAYS 0 WAIT STATE | 00      |

SHADOW RAM CONTROL REGISTER I

INDEX: 22h

FIG. 4

| BIT | FUNCTION                                                                                                     | DEFAULT |

|-----|--------------------------------------------------------------------------------------------------------------|---------|

| 7   | ROM ENABLE AT F0000-FFFFF<br>1=READ FROM ROM, WRITE TO DRAM.<br>0=READ FROM DRAM AND DRAM IS WRITE-PROTECTED | 1       |

| 6   | SHADOW RAM AT DOOOODH-DFFFFH AREA<br>OO=DISABLE 1=ENABLE                                                     | 0       |

| 5   | SHADOW RAM AT E0000h—EFFFFH AREA<br>O=DISABLE SHADOW, ENABLE ROMCS#<br>1=ENABLE SHADOW, DISABLE ROMCS#       | 0       |

| 4   | SHADOW RAM AT DOOOOH-DFFFFH AREA WRITE PROTECT<br>ENABLE<br>O=DISABLE 1=ENABLE                               | 0       |

| 3   | SHADOW RAM AT E0000h-EFFFFh AREA WRITE PROTECT<br>ENABLE<br>O=DISABLE 1=ENABLE                               | 0       |

| 2   | HIDDEN REFRESH-REFRESH ENABLE (WITHOUT HOLDING CPU) 1=DISABLE 0=ENABLE                                       | 1       |

| 1   | UNUSED BIT                                                                                                   | 0       |

| 0   | SLOW REFRESH ENABLE (4 TIMES SLOWER THAN THE NORMAL REFRESH) 0=DISABLE 1=ENABLE                              | 0 .     |

SHADOW RAM CONTROL REGISTER II

INDEX: 23h

FIG. 5

| BIT | FUNCTION                                               | DEFAULT |

|-----|--------------------------------------------------------|---------|

| 7   | SHADOW RAM AT ECOOOH-EFFFFH AREA 0=DISABLE 1=ENABLE    | 0 .     |

| 6 . | SHADOW RAM AT E8000h—EBFFFh AREA 0=DISABLE 1=ENABLE    | 0       |

| 5   | SHADOW RAM AT E4000h—E7FFFh AREA 0=DISABLE 1=ENABLE    | 0       |

| 4   | SHADOW RAM AT E0000h—E3FFFh AREA 0=DISABLE 1=ENABLE    | 0       |

| 3   | SHADOW RAM AT DC000h—DFFFFh AREA 0=DISABLE 1=ENABLE    | 0       |

| 2   | SHADOW RAM AT D8000h—DBFFFh AREA 0=DISABLE 1=ENABLE    | 0       |

| 1   | SHADOW RAM AT D4000h-D7FFFh AREA<br>0=DISABLE 1=ENABLE | 0       |

| 0   | SHADOW RAM AT DOOOOh-D3FFFh AREA<br>O=DISABLE 1=ENABLE | 0       |

## SHADOW RAM CONTROL REGISTER III

June 6, 1995

INDEX: 26h

| BIT | FUNCTION                                              | DEFAULT |

|-----|-------------------------------------------------------|---------|

| 6   | SHADOW RAM COPY ENABLE FOR ADDRESS AREA COOOOH-EFFFFH | 0       |

|     | O=READ/WRITE at AT BUS                                |         |

|     | 1=READ FROM AT BUS AND WRITE INTO SHADOW RAM          |         |

| 5   | SHADOW WRITE PROTECT AT ADDRESS AREA COOOOH-CFFFFh    | 1       |

|     | O=WRITE PROTECT DISABLE                               |         |

|     | 1=WRITE PROTECT ENABLE                                |         |

| 4   | SHADOW RAM ENABLE AT COOOOH-CFFFFH AREA               | 1       |

|     | 0=DISABLE 1=ENABLE                                    |         |

| 3   | ENABLE SHADOW RAM AT CC000h-CFFFF AREA                | 0       |

|     | 0=DISABLE 1=ENABLE                                    |         |

| 2   | ENABLE SHADOW RAM AT C8000h-CBFFF AREA                | 0       |

|     | 0=DISABLE 1=ENABLE                                    |         |

| 1   | ENABLE SHADOW RAM AT C4000h-C7FFFh AREA               | 0       |

|     | O=DISABLE 1=ENABLE                                    |         |

| 0   | ENABLE SHADOW RAM AT COOOOH-C3FFFH AREA               | 0       |

|     | 0=DISABLE 1=ENABLE                                    | •       |

FIG. 6

DRAM CONTROL REGISTER I

INDEX: 24h

FIG. 7

| BIT | FUNCTION                                                                                                       | DEFAULT |

|-----|----------------------------------------------------------------------------------------------------------------|---------|

| 7   | 2 BANK MODE. WHEN ENABLED, ONLY FIRST TWO BANKS(BANK 0 AND BANK 1) ARE USED. 1=DISABLE O=ENABLE                | 0       |

| 6–4 | DRAM TYPES USED FOR BANKO AND BANK1. SEE THE FOLLOWINNG TABLE                                                  | ` 000   |

| 3   | NOT USED                                                                                                       | 0       |

| 2–0 | DRAM TYPES USED FOR BANK 2 AND BANK 3. SEE THE FOLLOWING TABLE. BIT 2-0 ARE NOT USED WHEN BIT 7 IS SET TO "O". | 111     |

FIG. 7A

June 6, 1995

| BITS<br>7 6 5 4 | BANK 0 | BANK 1 |

|-----------------|--------|--------|

| 1000            | 1M     | X      |

| 1 0 0 1         | 1M     | 1M     |

| 1010            | 1M     | 4M     |

| 1 0 1 1         | 4M     | 11/    |

| 1 1 0 0         | 4M     | X      |

| 1 1 0 1         | 4M     | 4M     |

| 1 1 1 X         | X      | X      |

| 0000            | 256K   | X      |

| 0 0 0 1         | 256K   | 256K   |

| 0 0 1 0         | 256K   | 1M     |

FIG. 7B

|                 | , 10. , 0 |        |

|-----------------|-----------|--------|

| BITS<br>7 2 1 0 | BANK 2    | BANK 3 |

| 1000            | 1M        | X      |

| 1001            | 1M        | 1M     |

| 1010            | X         | X      |

| 1011            | 4M        | 1M     |

| 1 1 0 0         | 4M        | X      |

| 1 1 0 1         | 4M        | 4M     |

| 1 1 1 X         | X         | X      |

DRAM CONTROL REGISTER II

INDEX: 25h

| BIT | FUNCTION                                                                                                                                | DEFAULT |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7–6 | READ CYCLE WAIT STATE  7 6 ADDITIONAL WAIT STATES  0 0 NOT USED  0 1 0  1 0 1  1 1 2  NOTE: BASE WAIT STATES IS "3".                    | 11      |

| 53  | WRITE CYCLE WAIT STATE  5 4 3 ADDITIONAL WAIT STATES  0 0 0 0  0 1 0 1  1 0 0 2  1 1 0 3  0 0 1 NOT USED  NOTE: BASE WAIT STATE IS "2". | 110     |

| 20  | UNUSED                                                                                                                                  | 00      |

FIG. 8

CONTROL REGISTER 3

INDEX: 27h

| BIT | FUNCTION                                                                                                  | DEFAULT |

|-----|-----------------------------------------------------------------------------------------------------------|---------|

| 7   | ENABLE NON-CACHEABLE FUNCTION 1 1=ALL DRAM ARE NON-CACHEABLE 0=DRAM CACHEABLE RANGE CONTROLLED BY BIT 3-0 |         |

| 6–5 | UNUSED                                                                                                    | 00      |

| 4   | VIDEO BIOS AT COOCOH-C8000H AREA NON-CACHEABLE  O=CACHEABLE, 1=NON CACHEABLE                              | 1       |

| 3–0 | CACHEABLE ADDRESS RANGE FOR LOCAL MEMORY.                                                                 | 0001    |

FIG. 9

| BITS<br>3 2 1 0 | CACHEABLE ADDRESS RANGE |

|-----------------|-------------------------|

| 0 0 0 0         | 0-64Mb                  |

| 0 0 0 1         | 0-4Mb                   |

| 0 0 1 0         | 0-8Mb                   |

| 0 0 1 1         | 0-12Mb                  |

| 0100            | 0-16Mb                  |

| 0 1 0 1         | 0-20Mb                  |

| 0 1 1 0         | 0-24Mb                  |

| 0 1 1 1         | 0-28Mb                  |

| 1 0 0 0         | 0-32Mb                  |

| 1 0 0 1         | 0-36Mb                  |

| 1010            | 0-40Mb                  |

| 1 0 1 1         | 0-44Mb                  |

| 1 1 0 0         | 0-48Mb                  |

| 1 1 0 1         | 0-52Mb                  |

| 1 1 1 0         | 0-56Mb                  |

| 1111            | 0-60Mb                  |

FIG. 9A

# NON-CACHEABLE BLOCK 1 REGISTER I-INDEX: 28h

| BIT | FUNCTION                                                    | DEFAULT |

|-----|-------------------------------------------------------------|---------|

| 7–5 | SIZE OF NON-CACHEABLE MEMORY BLOCK 1, SEE FOLLOWING TABLE   | 100     |

| 4-2 | UNUSED                                                      | 000     |

| 1-0 | ADDRESS BITS OF A25 AND A24 OF NON-CACHEABLE MEMORY BLOCK 1 | 00      |

FIG. 10A

## NON-CACHEABLE BLOCK 1 REGISTER II

INDEX: 29h

|   | BIT | FUNCTION                                            | DEFAULT  |

|---|-----|-----------------------------------------------------|----------|

| Ì | 7–0 | ADDRESS BIT A23-A16 OF NON-CACHEABLE MEMORY BLOCK 1 | 0001xxxx |

## FIG. 10B

| 7 6 5 | BLOCK SIZE |

|-------|------------|

| 0 0 0 | 64K        |

| 0 0 1 | 128K       |

| 0 1 0 | 256K       |

| 0 1 1 | 512K       |

| 1 X X | DISABLED   |

|       |            |

FIG. 10C

|            |     | ١   | /ALID S | TARTING | ADDRES | S BITS | · <u>-</u> |     |

|------------|-----|-----|---------|---------|--------|--------|------------|-----|

| BLOCK SIZE | A23 | A22 | A21     | A20     | A19    | A18    | A17        | A16 |

| 64K        | ٧   | ٧   | V       | ٧       | ٧      | ٧      | ٧          | ٧   |

| 128K       | ٧   | V   | ٧       | ٧       | V      | V      | ٧          | X   |

| 256K       | ٧   | ٧   | V       | ٧       | ٧      | ٧      | X          | X   |

| 512K       | ٧   | V   | ٧       | V       | ٧      | X      | Х          | X   |

FIG. 10D

FIG. 12

| 21h<br>(3) | 21h<br>(2) | CACHE<br>SIZE | BITS USED TO<br>ADDRESS TAG SRAM | TAG(7:3)  | TAG(2) | TAG(1) | TAG(0) |

|------------|------------|---------------|----------------------------------|-----------|--------|--------|--------|

| 0          | 0          | 32KB          | CA(14:4)                         | CA(22:18) | CA(17) | CA(16) | CA(15) |

| 0          | 1          | 64KB          | CA(15:4)                         | CA(22:18) | CA(17) | CA(16) | CA(23) |

| 1          | 0          | 128KB         | CA(16:4)                         | CA(22:18) | CA(17) | CA(24) | CA(23) |

| 1          | 1          | 256KB         | CA(17:4)                         | CA(22:18) | CA(25) | CA(24) | CA(23) |

FIG. 13

Page 12 of 45

Page 13 of 45

Page 14 of 45

Page 17 of 45

Page 18 of 45

## AUTOMATIC CACHE FLUSH WITH READABLE AND WRITABLE CACHE TAG MEMORY

## CROSS-REFERENCED TO RELATED APPLICATIONS

This is a continuation of U.S. patent application Ser. No. 07/878,730, filed May 4, 1992, now U.S. Pat. No. 5,287,481, entitled AUTOMATIC CACHE FLUSH WITH READABLE AND WRITABLE CACHE TAG MEMORY, inventor David Lin, which is a continuation-in-part of U.S. patent application Ser. No. 07/812,074, filed Dec. 19, 1991, entitled "Automatic Cache Flush", inventor David Lin. The related applications are assigned to the assignee of the present application and are incorporated herein by reference.

#### **BACKGROUND**

#### 1. Field of the Invention

The invention relates to IBM PC AT-compatible <sup>20</sup> computer architectures, and more particularly, to enhancements thereof for cache memory management.

#### 2. Description of Related Art

The IBM PC AT computer architecture is an industry standard architecture for personal computers and 25 is-typically built around a CPU such as an 80286, 80386SX, 80386DX, or 80486 microprocessor manufactured by Intel Corporation. The CPU is coupled to a local bus, capable of performing memory accesses and data transfers at high rates of speed (i.e., on the order of 30 10-50 MHz with today's technology). The local bus includes 16 or 32 data lines, a plurality of memory address lines, and various control lines.

The typical IBM PC AT-compatible platform also includes DRAM main memory, and in many cases a 35 timer, a real-time clock, and a cache memory, all coupled to the local bus.

The typical IBM PC AT-compatible computer also includes an I/O bus which is separate and distinct from the local bus. The I/O bus, an AT bus, an ISA bus or an 40 EISA bus, is coupled to the local bus via certain interface circuitry. The I/O bus includes 16 or 32 data lines, a plurality of I/O address lines, as well as control lines. The I/O address space is logically distinct from the memory address space and if the CPU desires to access 45 an I/O address, it does so by executing a special I/O instruction. The interface circuitry recognizes the I/O signals thereby generated by the CPU, performs the desired operation over the I/O bus, and if appropriate, returns results to the CPU over the local bus.

In practice, some I/O addresses may reside physically on the local bus and some memory addresses may reside physically on the I/O bus. The interface circuitry is responsible for recognizing that a memory or I/O address access must be emulated by an access to the 55 other bus, and is responsible for doing such emulation. For example, a ROM (or EPROM) BIOS may be physically on the I/O bus, but actually form part of the local memory address space. During system boot, when the CPU sends out a non-I/O address which is physically 60 within the ROM BIOS, the interface circuitry recognizes such, enables a buffer which couples the address onto the I/O bus, and activates the chip select for the ROM. The interface circuitry then assembles a data word of the size expected by the CPU, from the data 65 returned by the ROM, and couples the word onto the local bus for receipt by the CPU. In many systems, at some point during the ROM-based boot-up procedure,

2

the ROM BIOS is copied into equivalent locations in the DRAM main memory and thereafter accessed directly. The portion of DRAM main memory which receives such portions of the BIOS is sometimes referred to as "shadow RAM."

More specifically, in the standard PC AT architecture, the logical main memory address space is divided into a low memory range (0h-9FFFFh), a reserved memory range (A0000h-FFFFFh) and an extended memory range (100000h-FFFFFFh). In a typical system the system ROM BIOS is located logically at addresses F0000h-FFFFFh, and is located physically on the I/O bus. Additional system ROM BIOS may be located in expansion sockets at addresses E0000h--EFFFFh, physically located on the I/O bus. Addresses C0000h-EFFFFh contain ROM BIOS portions for specific add-on cards and are located physically on their respective cards on the I/O bus. Addresses A000-0h-BFFFFh contain the video buffer, located physically on a video controller on the I/O bus. The video buffer may be accessible directly over the local bus. Duplicate memory space is typically provided in DRAM on the local bus for addresses C0000h-FFFFFh, and the user of the system can select which portions of the ROM BIOS are to be "shadowed" by being copied into the duplicate DRAM space during boot-up. Subsequent accesses to "shadowed" portions of the BIOS are to the DRAM copy, which is typically much faster than accesses to the ROM copy. As used herein, the term "secondary memory" refers to any storage elements present in the system, which are accessible in the main memory address space.

When an Intel 80×86 microprocessor first powers up, it begins by executing the instruction located 16 bytes from the highest memory address. For the 8086/8088, this address is FFFF0h. For the 80286, it is FFFFF0h, for the 80386 it is FFFFFF0h, and for the 80486 it is FFFFFFF0h. Typical IBM PC AT-compatible systems have a jump instruction at this address, to the beginning of a power-on self-test (POST) routine in the system ROM BIOS. The POST tests the microprocessor, memory, and other hardware components for presence and reliability, and also initializes various interrupt vector table entries with default values pointing to handler routine within the system BIOS.

As part of its duties, the POST scans for add-on ROM BIOS modules beginning at every 2k byte increment from address C0000h to DFFFFh. At each increment, it checks for a signature of 55h at offset 0, and AAh at offset 1 to indicate a valid add-on ROM BIOS module. The byte at offset 2 then contains the length of the BIOS module (measured in 512 byte blocks), and offset 3 begins the executable code for the module. The POST performs a checksum on all the bytes in the module, which should always yield a value of 00h in each of the low-order two bytes, and then executes a "far call" instruction to the offset 3 byte to permit the module to perform its own initialization. The module executes a "far return" instruction to return to the POST. The portion of the POST which checks for ROM BIOS modules is known as BIOS sizing.

The BIOS sizing operation in the POST also checks for an expansion system BIOS ROM in the range E000-0h-EFFFFh. The POST checks for a valid signature at offsets 0 and 1 at each increment, performs a checksum verification for the modules it finds, and executes a far call to the offset 3 byte of the module to permit the

module to perform its own initialization. An overall checksum verification is also perform on the main system BIOS range F0000h-FFFFFh

The POST also checks the integrity of all the memory in the system from address 0h to 9FFFFh and 5 100000h to the top of memory by writing known data to these addresses and then reading it back. The POST also checks the integrity of whatever video memory is present in addresses A0000h-BFFFFh by the same or a similar method.

In addition to the above elements of a standard PC AT-compatible system, a keyboard controller typically is also coupled to the I/O bus, as is a video display controller. A typical IBM PC AT-compatible system may also include a DMA controller which permits 15 peripheral devices on the i/O bus to read or write directly to or from main memory, as well as an interrupt. controller for transmitting interrupts from various addon cards to the CPU. The add-on cards are cards which may be plugged into slot connectors coupled to the I/O 20 bus to increase the capabilities of the system.

General information on the various forms of IBM PC AT-compatible computers can be found in IBM, "PC/AT Technical Reference Manual" (1985); Sanchez, "IBM Microcomputers: A Programmer's Hand- 25 book" (McGraw-Hill: 1990) and Solari, "AT Bus Design" (San Diego: Annabooks, 1990). See also the various data books and data sheets published by Intel Corporation concerning the structure and use of the iAPX-86 family of microprocessors, including the "386 DX 30 Microprocessor", data sheet, published by Intel Corporation (1990), and "i486 TM Processor Hardware Reference Manual", published by Intel Corporation (1990). All the above references are incorporated herein by reference.

Recently, efforts have been made to reduce the size and improve the manufacturability of PC AT-compatible computers. Specifically, efforts have been made to minimize the number of integrated circuit chips required to build such a computer. Several manufacturers 40 have developed "PC AT chipsets", which integrate a large amount of the I/O interface circuitry and other circuitry onto only a few chips. An example of such a chipset for an ISA architecture is the 386WT PC/AT chipset manufactured by OPTi, Inc., Santa Clara, Calif., 45 made up of the OPTi 82C381, 82C382 and 82C206. Examples of such a chipset for an EISA architecture are described in Intel, "82350 EISA Chip set" (1990) and in Intel, "82350DT EISA Chip Set" (1992), both available from Intel Corp., Santa Clara, Calif.; and in Buchanan, 50 set associative cache architecture, each line of second-"A Highly Integrated VLSI Chip Set For EISA System Design," [Need Journal and date], pp. 293-[?] [this is the article re TI chipset].

Several of these chipsets, including the 386 WT chipprove performance. The use of a small, high speed cache in a computer design permits the use of relatively slow but inexpensive DRAM for the large main memory space, by taking advantage of the "property of temporal locality," i.e., the property inherent in most 60 computer programs wherein a memory location referenced at one point in time is very likely to be referenced again soon thereafter. Descriptions of the various uses of and methods of employing caches appear in the following articles: Kaplan, "Cache-based Computer Sys- 65 tems," Computer, 3/73 at 30-36; Rhodes, "Caches Keep Main Memories From Slowing Down Fast CPUs," Electronic Design, Jan. 21, 1982, at 179;

Strecker, "Cache Memories for PDP-11 Family Computers," in Bell, "Computer Engineering" (Digital Press), at 263-67, all incorporated herein by reference. See also the description at pp. 6-1 through 6-11 of the "i486 Processor Hardware Reference Manual" mentioned above.

In general, a direct mapped cache memory comprises a high speed data RAM and a parallel high speed tag RAM. The RAM address of each line in the data cache 10 is the same as the low-order portion of the main memory line address to which the entry corresponds, the high-order portion of the main memory address being stored in the tag RAM. Thus, if main memory is thought of as  $2^m$  blocks of  $2^n$  "lines" of one or more bytes each, the i'th line in the cache data RAM will be a copy of the i'th line of one of the  $2^m$  blocks in main memory. The identity of the main memory block that the line came from is stored in the i'th location in the tag RAM. Tag RAM typically also contains a "valid" bit corresponding to each entry, indicating whether the tag and data in that entry are valid.

When a CPU requests data from memory, the loworder portion of the line address is supplied as an address to both the cache data and cache tag RAMs. The tag for the selected cache entry is compared with the high-order portion of the CPU's address and, if it matches, then a "cache hit" is indicated and the data from the cache data RAM is enabled onto the data bus. If the tag does not match the high-order portion of the CPU's address, or the tag data is invalid, then a "cache miss" is indicated and the data is fetched from main memory. It is also placed in the cache for potential future use, overwriting the previous entry. Typically, an entire line is read from main memory and placed in the cache on a cache miss, even if only a byte is requested. On a data write from the CPU, either the cache RAM or main memory or both may be updated, it being understood that flags may be necessary to indicate to one that a write has occurred in the other.

Accordingly, in a direct mapped cache, each "line" of secondary memory can be mapped to one and only one line in the cache. In a fully associative cache, a particular line of secondary memory may be mapped to any of the lines in the cache; in this case, in a cacheable access, all of the tags must be compared to the address in order to determine whether a cache hit or miss has occurred. "k-way set associative" cache architectures also exist which represent a compromise between direct mapped caches and -fully associative caches. In a k-way ary memory may be mapped to any of k lines in the cache. In this case, k tags must be compared to the address during a cacheable secondary memory access in order to determine whether a cache hit or miss has set, implement a direct mapped cache memory to im- 55 occurred. Aspects of the present invention apply to each of the above cache architectural variations. Caches may also be "sector buffered" or "sub-block" type caches, in which several cache data lines, each with its own valid bit, correspond to a single cache tag RAM entry. Aspects of the invention may apply to sector buffered caches as well, especially to the extent that elimination of the valid bits effectively converts such caches to non-sector buffered caches with a line size equal to the former sector size.

> In PC AT-compatible computers, the chipset performs all the management functions for the cache, while the cache data memory itself is located in SRAM offchip. The tag memory is also located off-chip in a tag

RAM. The user can specify, through a user setup program which programs registers in thechipset, which memory address ranges are to be cacheable and which are not. Due to the special nature of addresses A000-0h-BFFFFh and C8000h-FFFFFh, these addresses are 5 never cacheable in a typical chipset.

On system power-up, the external cache data and tag RAM both contain random data, including in the valid bit. Unless special precautions are taken, therefore, one or more lines of random data in the cache erroneously may appear to the chipset to contain valid information. One solution to this problem might be to use a dedicated tag RAM chip which has a "flush" pin. The CY7B181 chip manufactured by Cypress Semiconductor Corp. is one such chip. The flush pin would be connected to the system reset line to force the tag RAM to invalidate all its entries before the first instruction fetch by the CPU. Dedicated tag RAM chips are expensive, however, and preferably avoided in PC AT-compatible computers. 20

In some chipsets, the problem is solved using standard SRAM chips to store tag RAM. These chipsets power up with cacheing disabled, and special routines in the setup program, or in a driver, invalidate each cache tag entry before enabling cacheing. Since the tag RAM is not directly accessible by the CPU in PC AT architectures, however, this technique usually requires the provision of special registers in the chipset through which the accesses can be made. It also requires specialized setup program code to accomplish the flush, which is undesirable since industry standard BIOS ROMs generally cannot be used. The technique also imposes a small time delay in the boot procedure which it would be desirable to avoid.

In the 386 WT chipset, a dedicated tag RAM was used which included an "invalidate" input pin to clear the valid bit for the entry currently being addressed. The chipset itself included an "invalidate" output for connection to that pin, and the chipset solved the pow- 40 er-up cache-flush problem by powering up in a default state with cacheing disabled and including logic to activate the invalidate output whenever cacheing was disabled. Thus, when the POST performed its standard memory test operation, which included (among other 45 things) reads from all the bytes in a memory address range much larger than the maximum allowed cache size of 256k bytes, all the tag RAM entries were invalidated automatically. This solution avoided the need for any special setup program routines, but still required the use of expensive dedicated tag RAM.

Another problem which occurs in PC AT-compatible computers arises because there is no way to directly read or write information in the cache tag RAM. In the typical PC AT-compatible computer, the data pins of the tag RAM are permanently coupled to receive input from the high-order address leads of the local bus as explained above, and are permanently coupled to provide output to a tag match comparator. Cache tag 60 entries have no corresponding address in the main memory or I/O address space. For diagnostic purposes, however, it would be desirable to be able to write any desired data to a selected tag RAM entry, and also to read the data currently in a tag RAM entry. This capa- 65 bility would be desirable so that, for example, the POST could test and size the cache much like it does so for DRAM main memory.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to address the power-up cache-flush problem while avoiding some or all of the problems raised by prior solutions.

It is another object of the present invention to provide a way of flushing a cache tag RAM during power-up initialization without using dedicated tag RAM chips and without modifications to standard setup program routines.

It is another object of the present invention to eliminate the "valid" bit from tag RAMs implemented with standard SRAMs in PC AT-compatible computer architectures.

It is another object of the present invention to provide a method for writing desired information into a cache tag entry and for reading the information from a cache tag entry.

It is another object of the present invention to provide such read/write capability while also addressing the power-up cache flush problem.

According to the invention, roughly described, a chipset is provided which powers up in a default state with cacheing disabled and which writes permanently non-cacheable tags into tag RAM entries corresponding to memory addresses being read while cacheing is disabled. Even though no "valid" bit is cleared, erroneous cache hits after cacheing is enabled are automatically prevented since any address which does match a tag in the tag RAM, is a non-cacheable address and will force retrieval directly from main memory anyway. The concept of writing permanently non-cacheable tags into tag RAM instead of clearing valid bits can be extended beyond the power-up cache-flush problem to normal operation, to thereby eliminate the need for any valid bit at all in tag RAMs implemented using standard SRAM. It can also be used in set associative, fully associative, and k-way set associative cache memories.

In another aspect of the invention, again roughly described, cache control circuitry is provided which can select from two or more sources for the data to be written to tag RAM. One such source is, conventionally, a portion of the CPU bus address bits. Another source may be a register in the chipset which may be written to and read from by the CPU. In this way, any desired data may be written to an entry in the tag RAM by writing the information to the chipset register and then selecting the cache control mode which writes the information from the register into the tag RAM on the next main memory read access. The low-order address bits for the read access address the tag RAM as they do for conventional cache operation. Further, in this aspect of the invention, an additional cache control mode may be provided in which the information read from a tag entry addressed in a read access is written to the chipset register and made available for reading by the CPU. Yet an additional mode also may be made available in the cache controller in which the address of a non-cacheable secondary memory block is selected for writing to the cache tag RAM at the address specified on the CPU address lines during a read access to main memory, thereby effectively invalidating the corresponding cache data line entry.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention will be described with respect to particular embodiments thereof and reference will be made to the drawings, in which:

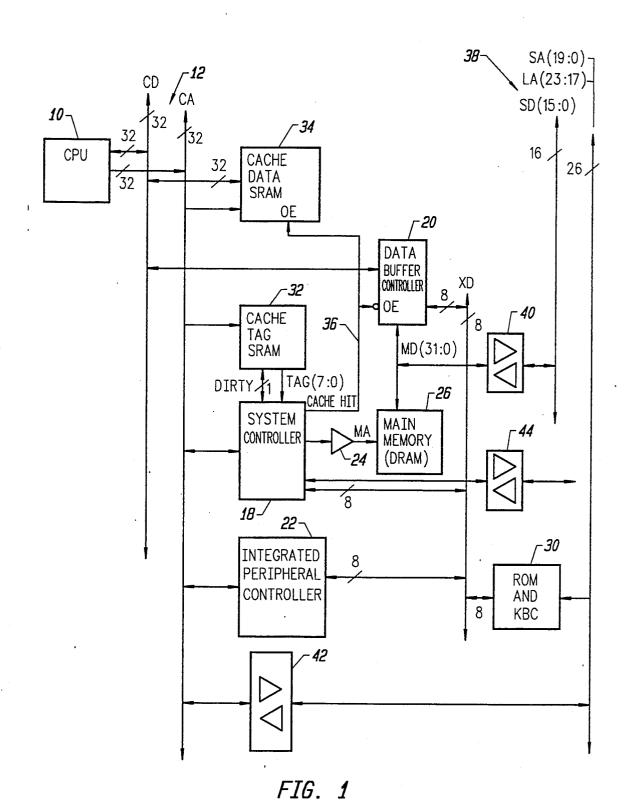

FIG. 1 is a block diagram of a PC AT-compatible computer architecture which may incorporate the in-

FIGS. 2-7, 7a, 7b, 8, 9, 9a, 10a, 10b, 10c and 10d illustrate register field definitions in the system control- 10 ler of FIG. 1;

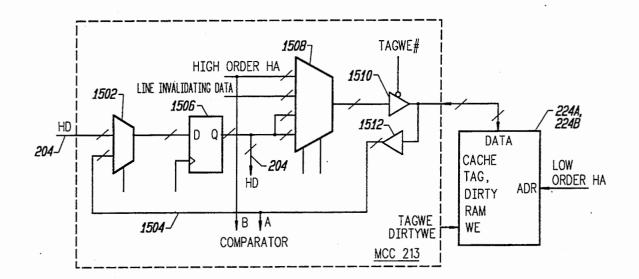

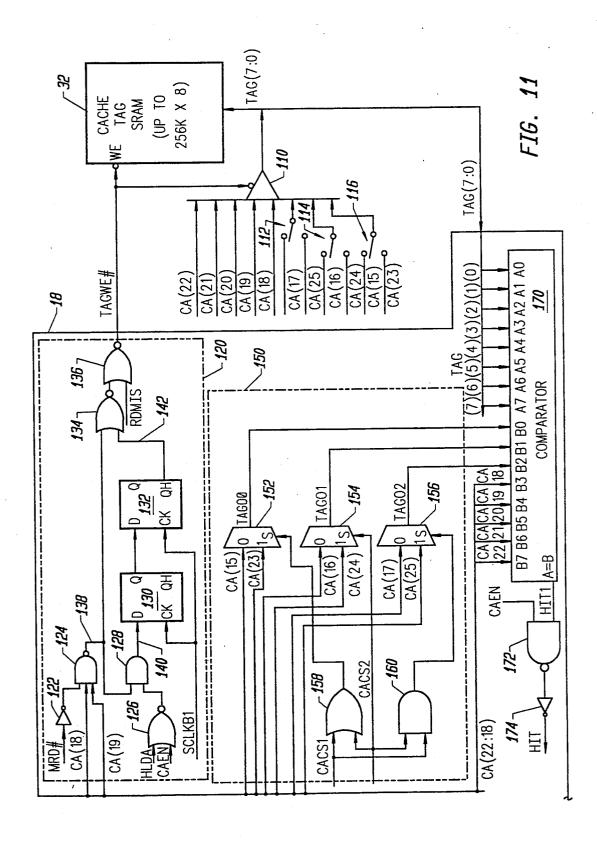

FIG. 11 is a block diagram of cache management related circuitry which may incorporate the invention;

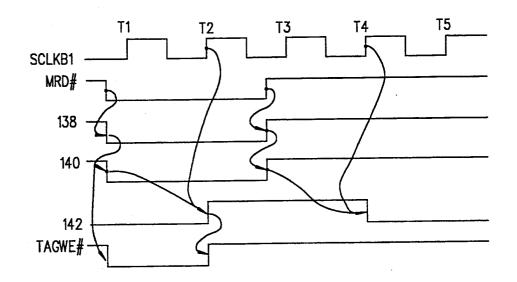

FIG. 12 is a timing diagram useful for understanding a portion of FIG. 11.

FIG. 13 is a table useful for explaining the operation of an aspect of FIG. 11.

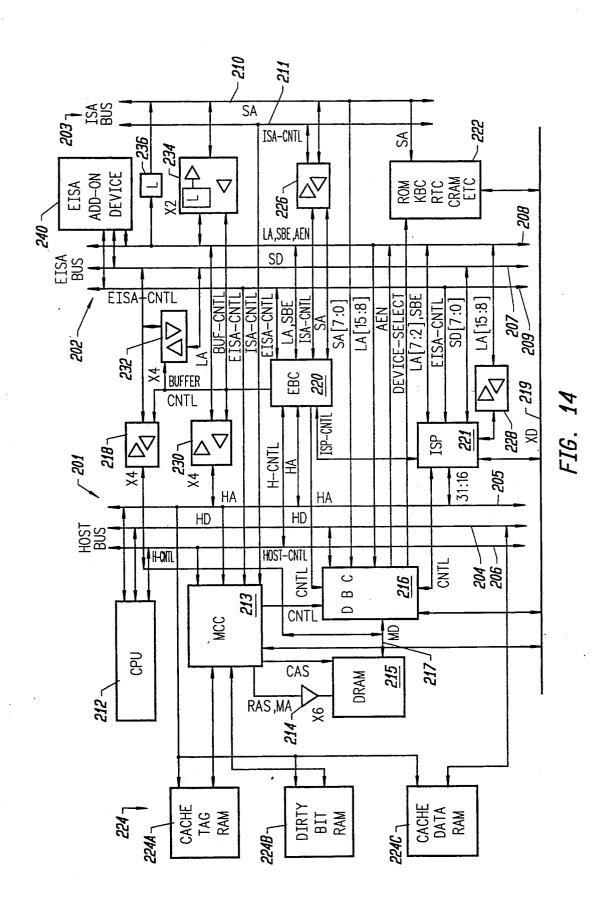

FIG. 14 is a block diagram of an EISA-compatible computer architecture which may incorporate the in-

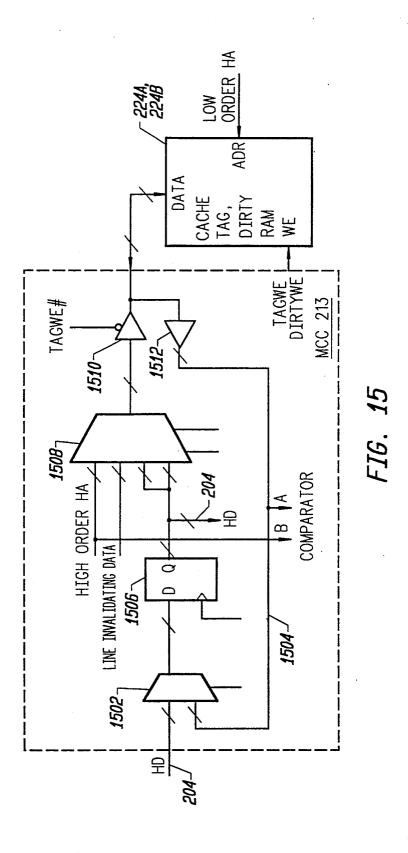

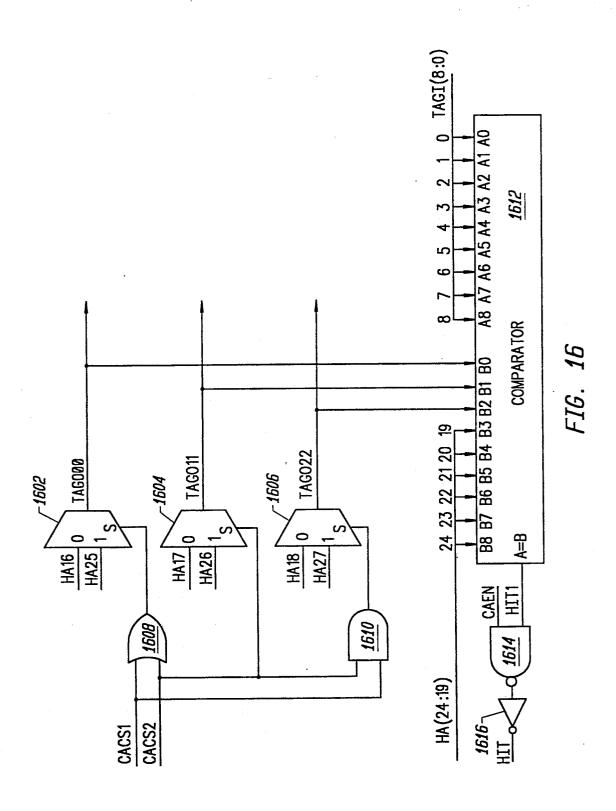

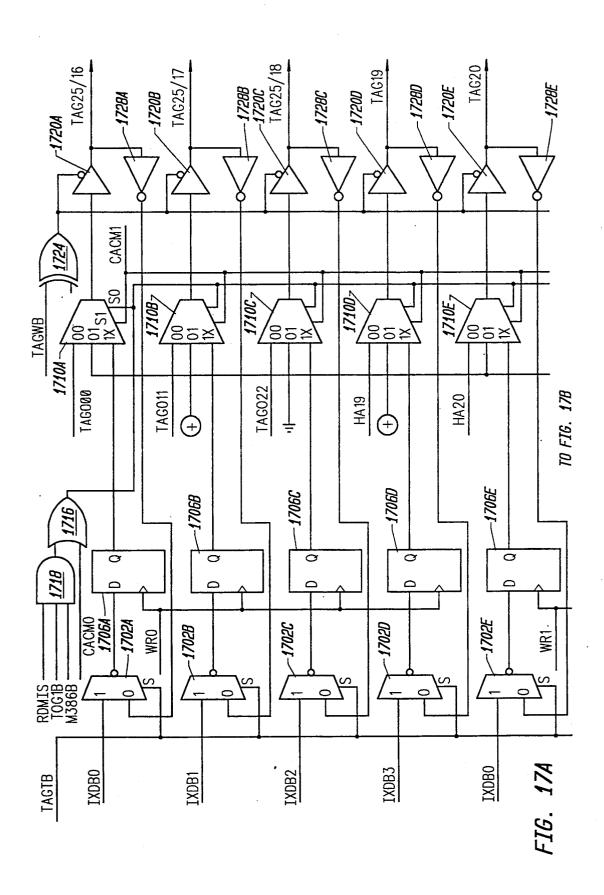

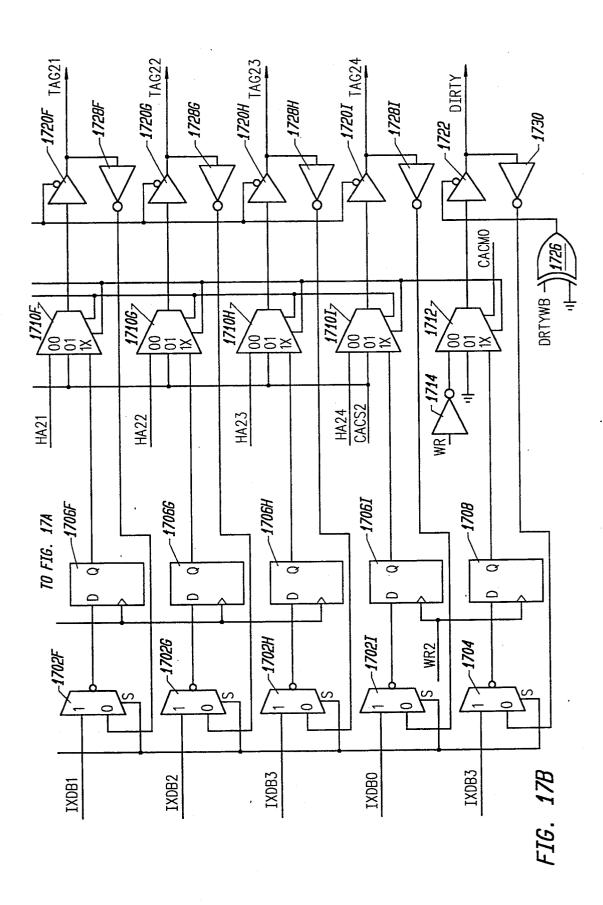

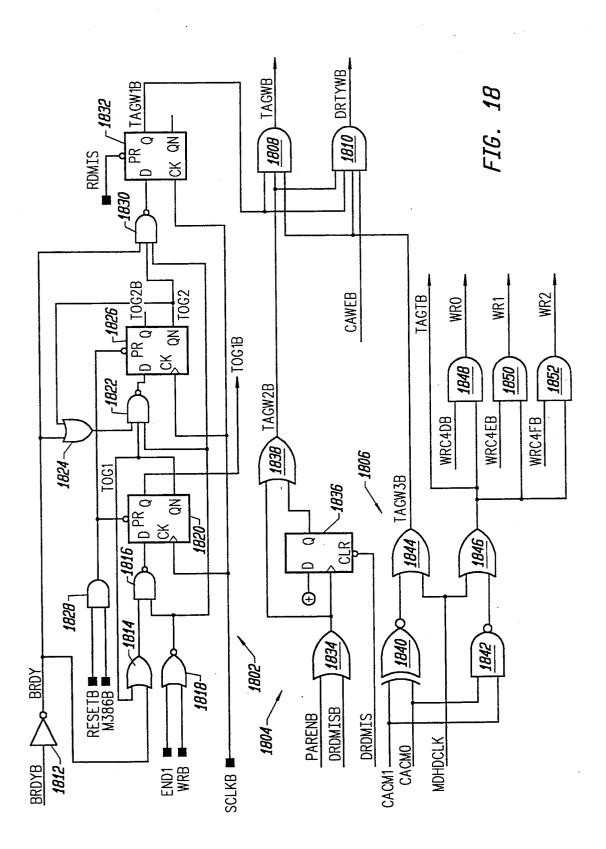

FIGS. 15-18 are logic diagrams of circuitry in the MCC of FIG. 14; and

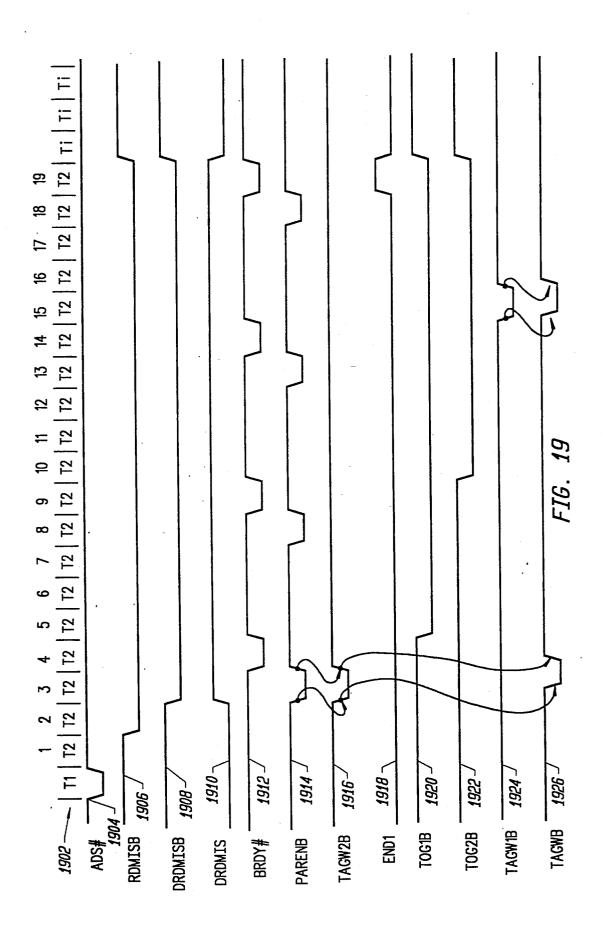

FIG. 19 is a timing diagram useful for understanding a portion of FIG. 18.

#### DETAILED DESCRIPTION

FIG. 1 is a simplified block diagram of a PC AT Compatible Computer System which may incorporate the present invention. It comprises a CPU 10, which is preferably an 80386DX Microprocessor manufactured 30 by Intel Corporation, Sunnyvale, Calif., coupled to a CPU bus 12. The CPU bus 12 (also called a local bus) comprises, among other things, a 32-bit CPU data bus CD and a 32-bit CPU address bus CA. A system controller (SYSC) chip 18 is coupled to the address lines of 35 the CPU bus 12, and a data buffer controller (DBC) 20 is coupled to the data lines of CPU bus 12. The system controller may be an 82C391, and the data buffer controller may be an 82C392, both manufactured by OPTI, Inc., Santa Clara, Calif. Roughly, the system controller 40 chip 18 performs duties related to the reset logic, system clock generation, the cache interface and cache control sub-system, local DRAM control sub-system, shadow RAM, AT bus state machine, bus arbitration logic, refresh logic, control of system BIOS ROM and I/O 45 ports, a turbo switch and multiplexed DRAM addressing. The data buffer controller generally performs duties related to data bus conversion, parity generation and detection, clock generation and reset control, and any interface to a numeric co-processor (not shown). 50 Also connected to the address lines of CPU bus 12 is an integrated peripheral controller (IPC) 22, which may be an 82C206 available from OPTI, Inc. The integrated peripheral controller includes a DMA controller, and interrupt controller, a timer peripheral and a real time 55 clock (RTC).

The system controller 18 provides a memory address output which is coupled through a set of buffers 24 and a memory address bus MA to a main memory array of DRAM 26. Up to 64 megabytes of 32-bit wide DRAM 60 can be accommodated in this array 26. The main memory DRAM 26 is also connected over a 32-bit memory data bus MD to the data buffer controller 20. The system controller 18 is also connected bi-directionally to an 8-bit ROM and keyboard data bus XD which is also 65 It includes a plurality of address lines and a plurality of connected bi-directionally to the data buffer controller 20, the integrated peripheral controller 22, and a ROM and keyboard controller unit 30. The ROM and key-

board controller (KBC) unit 30 includes the ROM BIOS at addresses F0000h-FFFFFh, possibly a socket for additional ROM at addresses E0000h-EFFFFh, and a keyboard controller chip such as an 8042 microcontroller manufactured by Intel Corp., and available preprogrammed for keyboard functions from Phoenix Technologies, Norwood, Mass.

The system controller 18 also communicates bi-directionally with Cache Tag SRAM 32 over an 8-bit TAG bus and a DIRTY line. The Cache Tag SRAM 32 and the Cache Data SRAM 34 are addressed by lines CA of the CPU bus 12, and the data SRAM 34 communicates bi-directionally with the CD data lines of the CPU bus 12. As will be seen, the system controller 18 includes 15 Cache Tag Match Logic, and generates a Cache Hit signal which is communicated over a line 36 to an inverting output enable of data buffer controller 20, and to a non-inverting output enable of Cache Data SRAM

The system also includes a so-called AT bus 38, which includes, among other things, a 16-bit data bus SD and an address bus including lines SA(19:0) and LA(23:17). The SA and LA lines both perform address functions, but the LA lines are valid earlier in an AT bus cycle and must be latched if needed later in the cycle. The SA lines are not valid as early as the LA lines, but remain valid longer. The SD lines are coupled to the memory data bus MD via a bi-directional buffer 40. Certain of the address lines on the AT bus 38 are coupled bi-directionally to the CPU bus 12 address lines CA via a bi-directional buffer 42, and certain control lines on the AT bus 38 are coupled to the system controller 18 via a set of buffers 44.

In general operation, on power up, a register bit in the system controller 18 comes up in a default state to indicate that cacheing is disabled. The first instruction fetch issued by the CPU 10 is to the address FFFFFF0h, which is recognized by the system controller 18. The system controller 18 responds by causing a jump to the first instruction in the POST. The CPU fetches instructions continuing at that address. Since the POST is contained physically within the ROM in ROM/KBC unit 30, the system controller recognizes this and activates the buffers 42 to couple the address on the CPU address lines CA to the AT bus address lines, and then enables the ROM output onto the XD bus. The data buffer controller 20 receives the data from the ROM over the XD bus, assembles the 32-bit words expected by the CPU 10, and delivers them to the CPU 10 over the CD lines of CPU bus 12. Since cacheing is disabled, the system controller 18 will maintain the Cache Hit signal on line 36 low which enables the data buffer controller 20 output to the CD lines and disables the Cache Data SRAM 34 output to the CD lines.

As mentioned above, the POST performs many testing and initialization functions including, among other things, a test of all the main memory present in the system. This involves writing known information to each address in main memory, reading it back and comparing it to the information which was previously written. The POST also loads in an operating system from disk into main memory 26 and calls the user setup pro-

The local bus 12 will now be described in more detail. data lines, as well as a number of control lines and power and ground. The exact set of lines which make up the local bus is well known in the industry, and may

be determined from various sources, including those identified above. For present purposes, it is sufficient to identify the local bus signal lines set forth in Table I. ("#" indicates active low.)

|           | TABLE I                                                    | 5  |

|-----------|------------------------------------------------------------|----|

| CA(31:2)  | Address lines. 32 bits of address are                      |    |

|           | available. The high-order 30 bits are provided             |    |

|           | on CA(31:2).                                               |    |

| BE#(3:0)  | Carries a 1-of-4 decode of the 2 low-order                 |    |

| CD (24.6) | address bits.                                              | 10 |

| CD(31:0)  | Data lines.                                                |    |

| M/IO#     | Memory/IO control line. When asserted high                 |    |

|           | by the CPU, indicates that the address on CA               | •  |

|           | is an I/O address as opposed to a main                     |    |

| READY#    | memory address.  Acknowledgment to CPU that a local memory |    |

| KEADI#    | access is complete.                                        | 15 |

| CLK2      | Bus clock signal.                                          |    |

| W/R#      | Distinguishes write cycles from read cycles.               |    |

| D/C#      | Distinguishes data cycles, either memory or                |    |

| D/Cπ      | I/O, from control cycles which are: interrupt              |    |

|           | acknowledge, halt, and instruction fetching.               |    |

| LOCK#     | Indicates that other system bus masters are                | 20 |

| LOCIL,    | denied access to the system bus while it is                |    |

|           | active.                                                    |    |

| ADS#      | Indicates that a valid bus cycle definition and            |    |

|           | address (W/R#, D/C#, M/IO#, BEO#, BE1#,                    |    |

|           | BE2#, BE3# (or BHE# and BLE#) and CA)                      |    |

|           | are being driven on the local bus.                         | 25 |

| NA#       | Requests address pipelining.                               |    |

| BS16#     | Allows direct connection of 32-bit and 16-bit              |    |

|           | data buses.                                                |    |

| HOLD      | Allows another bus master to request control               |    |

|           | of the local bus.                                          |    |

| HLDA      | Indicates that the CPU has surrendered                     | 30 |

|           | control of its local bus to another bus master.            |    |

| BUSY#     | Signals a busy condition from a processor                  |    |

|           | extension.                                                 |    |

| ERROR#    | Signals an error condition from a processor                |    |

|           | extension.                                                 |    |

The various signals on the I/O bus are also well speci-fied and well known in the industry. The Solari book identified above describes the lines in detail. For present purposes, only the signals set forth in Table II are important.

TABLE II

Indicates that the processor extension has data to be transferred by the CPU.

A maskable input to CPU that signals the CPU to suspend execution of the current program and execute an interrupt acknowledge

A non-maskable input that signals the CPU to suspend execution of the current program and execute an interrupt acknowledge function. Suspends any operation in progress and places the CPU in a known reset state.

**PEREQ**

INTR

NMI

RESET

| SA(19:0)  | 20 address lines. Sufficient to address 1MB of memory. Only SA(15:0) are used to address |

|-----------|------------------------------------------------------------------------------------------|

|           | the 64k I/O address space, and only SA(9:0)                                              |

|           | are used to address the basic 1k AT I/O                                                  |

|           | address space.                                                                           |

| LA(23:17) | Additional address lines for addressing a                                                |

|           | 16MB memory address space on the I/O bus.                                                |

|           | The LA lines are valid earlier in an I/O bus                                             |

|           | cycle, but must be latched if needed later in                                            |

|           | the cycle. The SA lines are not valid as early                                           |

|           | as the LA lines, but remain valid longer.                                                |

| BALE      | Bus address latch enable line. In a CPU                                                  |

|           | initiated I/O bus cycle, this line indicates when                                        |

|           | the address, AEN and SBHE# lines are valid.                                              |

|           | In other I/O bus cycles, the platform circuitry                                          |

TABLE II-continued

|    |                                       | TABLE II-continued                                                                                                                                                             |

|----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | SBHE#                                 | drives BALE high for the entire cycle.<br>System byte high enable. Indicates that                                                                                              |

| 5  |                                       | current access or transfer is a 16-bit access or<br>transfer (for which valid data will appear on<br>SD(15:8) as well as SD(7:0)) rather than an 8-                            |

|    | AEN                                   | bit access or transfer.  When active, informs I/O resources on I/O                                                                                                             |

| 10 |                                       | bus to ignore the address and I/O command<br>signals. Used primarily in DMA cycles where<br>only the I/O resource which has requested                                          |

| 10 |                                       | and received a DMA acknowledgment signal (DACK#) knows to ignore AEN and respond                                                                                               |

| •  | SD(15:0)                              | to the I/O signal lines. Some systems include slot-specific AEN <sub>x</sub> signal lines.  16 data lines.                                                                     |

| 15 | MEMR#,<br>SMEMR#                      | Read request lines to a memory resource on<br>the I/O bus. SMEMR# is the same as<br>MEMR# except that SMEMR# becomes<br>active only when the read address is below             |

|    | MEMW#                                 | 1MB (i.e., LA(23:20) = 0). Write request lines to a memory resource on                                                                                                         |

| 20 | SMEMW# IOR#                           | the I/O bus. SMEMW# becomes active only when the write address is below 1 MB.  Read request lines to an I/O resource on the                                                    |

|    | IOW#                                  | I/O bus.  Write request lines to an I/O resource on the                                                                                                                        |

|    | MEMCS16#                              | I/O bus.  Memory chip select 16. Asserted by an                                                                                                                                |

| 25 |                                       | addressed memory resource on the I/O bus if the resource can support a 16-bit access cycle.                                                                                    |

|    | IOCS16#                               | I/O chip select 16. Asserted by an addressed I/O resource on the I/O bus if the resource can support a 16-bit access cycle.                                                    |

| 30 | SRDY#                                 | Synchronous Ready line. Also sometimes called OWS# or ENDXFR#. Activated by an addressed I/O resource to indicate that it can support a shorter-than-normal access cycle.      |

| 35 | IOCHRDY#                              | I/O channel ready line. Activated by an addressed I/O resource to indicate that the I/O access cycle is either a default-length                                                |

|    |                                       | cycle or a 0 wait state cycle. if the resource de-activates this line, the cycle will not end until it is re-activated. A de-activated IOCHRDY# supersedes an activated SRDY#. |

| 40 | MASTER#                               | After requesting and receiving a DMA-<br>acknowledged (DACK#) signal, an I/O bus<br>add-on card can assert MASTER# to become                                                   |

|    | REFRESH#                              | the bus master.  Activated by refresh controller to indicate a refresh cycle.                                                                                                  |

| 45 | IRQ(15, 14,<br>12:9, 7:3)<br>DRQ(7:5, | Interrupt request lines to interrupt controller for CPU.  DMA Request lines from I/O resource on I/O                                                                           |

|    | 3:0)<br>DACK(7:5,<br>3:0)             | bus to platform DMA controller. DMA Acknowledge lines.                                                                                                                         |

|    | TC                                    | DMA terminal count signal. Indicates that all data has been transferred.                                                                                                       |

| 50 | BCLK                                  | I/O bus clock signal. 6-8.33MHz square wave.                                                                                                                                   |

|    | osc                                   | 14.318MHz square wave.                                                                                                                                                         |

The system controller 18, data buffer controller 20 and integrated peripheral controller 22 make up the OPTI-386WB PC/AT chipset. The system controller 18 and data buffer controller 20 are described in detail in OPTI, "OPTI-386WB PC/AT Chipset (82C391/82C392/82C206) Preliminary

82C391/82C392Data Book" (Mar. 28, 1991). The data book and each of the chips are incorporated herein by reference. In pertinent part, the system controller 18 has the input/output pins set forth in Table III.

#### TABLE III

| Name     | Direction | Description                             |

|----------|-----------|-----------------------------------------|

| CLOCK AN | ND RESET  |                                         |

| CLK21    | Input     | Clock input for internal state machine. |

TABLE III-continued

|                  |           | TABLE III-continued                                                                                                                                                                                                                                                                                                    |

|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name             | Direction | Description                                                                                                                                                                                                                                                                                                            |

| BCLK             | Output    | BCLK to AT bus.                                                                                                                                                                                                                                                                                                        |

| BCLKS            | Input     | BCLK Selection (OSCIN/6 or OSCIN/8)                                                                                                                                                                                                                                                                                    |

| RST1#            | Input     | Cold reset signal, deriving either from Powergood                                                                                                                                                                                                                                                                      |

| RST2#            | Input     | signal of power supply or from Reset Switch. CPU Reset input from Keyboard Controller or from                                                                                                                                                                                                                          |

| CPURST           | Output    | DBC ERST2# pin. Reset for 386 processor.                                                                                                                                                                                                                                                                               |

| OSCIN            | Input     | Clock input with frequency of twice the rated CPU                                                                                                                                                                                                                                                                      |

|                  | <b>x</b>  | clock frequency. Used to generate CPURST.                                                                                                                                                                                                                                                                              |

| CPU INTERFA      | CE_       |                                                                                                                                                                                                                                                                                                                        |

| CA(31:17, 7:2)   | Input     | CPU Address Lines.                                                                                                                                                                                                                                                                                                     |

| CA(16:8) BE(3:0) | Both      | CPU Address Lines 16-8. These are input pins during CPU cycle. CA(16:9) are output pins for DMA address A16-A9 by latching XD(7:0) during 16-bit DMA cycle and CA(15:8) are DMA address A15-A8 for 8-bit DMA cycle. Byte Enable 3-0.  In CPU cycle, driven by CPU.  In master and DMA cycle, they are outputs deriving |

|                  | _         | from XA0, XA1 and SBHE# from AT bus.                                                                                                                                                                                                                                                                                   |

| ADS#             | Input     | Status input from CPU. This active low signal indicates the CPU is starting a new cycle.                                                                                                                                                                                                                               |

| WR#              | Input     | CPU Write or Read Cycle Status. It indicates a write                                                                                                                                                                                                                                                                   |

| DC#              | <b>T</b>  | cycle if high and read cycle if low.                                                                                                                                                                                                                                                                                   |

| DC#              | Input     | CPU Data or Code Cycle Status. It indicates data transfer operations when high, or control operations (code fetch, halt, etc.) when low.                                                                                                                                                                               |

| MIO#             | Input     | CPU Memory or I/O Cycle Status. If MIO# is high,                                                                                                                                                                                                                                                                       |

| -                |           | then the address on the address lines refers to a                                                                                                                                                                                                                                                                      |

|                  |           | memory address. If MIO# is low, then the address on the address lines is an I/O address.                                                                                                                                                                                                                               |

| RDY#             | Output    | Ready output for CPU to terminate the current cycle.                                                                                                                                                                                                                                                                   |

|                  | <b>,</b>  | This pin is not a tri-state output.                                                                                                                                                                                                                                                                                    |

| TURBO            | Input     | Turbo mode selection.                                                                                                                                                                                                                                                                                                  |

| LDEV#            | Input     | Local Device indication. Permits external circuitry                                                                                                                                                                                                                                                                    |

|                  |           | (such as a coprocessor) to trap an access to a device on the I/O bus and inhibit the I/O bus cycle.                                                                                                                                                                                                                    |

| NUMERIC CO-      | PROCESSO  | OR INTERFACE                                                                                                                                                                                                                                                                                                           |

| NPERR#           | Input     | Numeric Processor Error indication.                                                                                                                                                                                                                                                                                    |

| NPRST            | Output    | Numerical Processor Reset. CPURST or I/O write to port F1h will assert NPRST. It is asserted for 40 clk2 cycles and 80387 cannot be accessed within 50 clk2 cycles after NPRST is negated.                                                                                                                             |

| RDYI#            | Input     | Local Device Ready Input, it will be synchronized by SYSC before sending to CPU. For 387 READYO#                                                                                                                                                                                                                       |

| BSYTOG#          | Output    | signal.  Toggled BUSY# when no numeric coprocessor installed.                                                                                                                                                                                                                                                          |

| EXTERNAL CA      | CHE CON   |                                                                                                                                                                                                                                                                                                                        |

| TAG(7:0)         | Input     | TAG RAM Lines 7-0. These lines are inputs from tag                                                                                                                                                                                                                                                                     |

| DRTY             | Both      | SRAM for TAG compare.  Dirty Bit of Tag RAM to indicate its line of cache                                                                                                                                                                                                                                              |

| DKI I            | Don       | memory has been written into.                                                                                                                                                                                                                                                                                          |

| TAGWE#           | Output    | TAG RAM Write Enable. It is used to update the tag                                                                                                                                                                                                                                                                     |

| CAEOE#           | Output    | RAM. External Cache Even Bank Output Enable. It is                                                                                                                                                                                                                                                                     |

|                  |           | always activated for 32k and 128k cache memory. CAEOE# is also asserted when CA15 and CA17 are low for 64KB and 256KB cache memory, respectively.                                                                                                                                                                      |

| CAOOE#           | Output    | External Cache Odd Bank Output Enable. It is deactivated for 32 KB and 128 KB cache. CAOOE#                                                                                                                                                                                                                            |

| •                |           | is only asserted when CA15 and CA17 are high for                                                                                                                                                                                                                                                                       |

| CAEWE#           | Output    | 64KB and 256KB cache memory respectively.  External Cache Even Bank Write Enable. It is always                                                                                                                                                                                                                         |

| 0.122,,          | Output    | activated for 32k and 128k cache size and only asserted when CA15 is low for 64KB and CA17 is                                                                                                                                                                                                                          |

| CAOWE#           | Output    | low for 256KB cache respectively.  External Cache Odd Bank Write Enable. It is only asserted when CA15 and CA17 is high for 64KB and 256Kb cache respectively.                                                                                                                                                         |

| DRTYW#           | Output    | Write strobe to Dirty Bit of Tag Ram.                                                                                                                                                                                                                                                                                  |

| A2CON            | Output    | Cache Address Bit 2 Toggle Control. It is toggled during cache read miss cycle.                                                                                                                                                                                                                                        |

| A3CON            | Output    | Cache Address Bit 3 Toggle Control. It is toggled during cache read miss cycle.                                                                                                                                                                                                                                        |

| LOCAL DRAM       | INTERFA   |                                                                                                                                                                                                                                                                                                                        |

| DWE#             | Output    | DRAM Write Enable signal.                                                                                                                                                                                                                                                                                              |

| RAS(3:0)#        | Output    | DRAM Row Address Strobes.                                                                                                                                                                                                                                                                                              |

| CAS(15:0)#       | Output    | DRAM Column Address Strobes.                                                                                                                                                                                                                                                                                           |

|                  |           |                                                                                                                                                                                                                                                                                                                        |

TABLE III-continued

|                                        |                 | 1 ADEL HI-continued                                                                              |

|----------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|

| Name                                   | Direction       | Description                                                                                      |

| MA(10:0)                               | Output          | DRAM Row/Column Address lines 10:0.                                                              |

|                                        |                 | BUS CONTROLLER CHIP                                                                              |

| LMEN#                                  | Output          | Local Memory Accessed Indication. Used by DBC                                                    |

|                                        |                 | to control the bus flow.                                                                         |

| DLE                                    | Output          | DRAM Read Data Latch Enable; used for parity                                                     |

| MIO16#                                 | Output          | checking.  Latched AT-bus 16-bit Slave Status; used for bus                                      |

| WIIO10#                                | Output          | conversion.                                                                                      |

| PCKEN#                                 | Output          | Parity checking Enable; used by Data Bus Controller                                              |

|                                        |                 | to perform parity checking.                                                                      |

| ATCYC# BUS ARBITRA                     | Output          | AT Cycle Indication for CPU cycle.                                                               |

|                                        |                 |                                                                                                  |

| HRQ<br>HLDA1                           | Input<br>Output | DMA or Master Cycle Request from IPC.  DMA or Master Cycle Granted Notice.                       |

| OUTI                                   | Input           | Refresh Request from Timer! Output.                                                              |

| HLDA                                   | Input           | CPU Hold Acknowledge.                                                                            |

| ADS8                                   | Input           | 8-bit DMA Transfer Address Strobe. The SYSC has                                                  |

|                                        |                 | to latch XD(7:0) by using ADS8 and translate to                                                  |

| A TONIO#                               | Ymmist          | CA(15:8) outputs.                                                                                |

| AEN8#<br>ADS16#                        | Input<br>Input  | 8-bit DMA Cycle Indication. 16-bit DMA Transfer Address Strobe. The SYSC has                     |

| 110010//                               | Input           | to latch XD(7:0) by using ADS16 and translate to                                                 |

|                                        |                 | CA(16:9) outputs.                                                                                |

| AEN 16#                                | Input           | 16-bit DMA Transfer Indication.                                                                  |

| HOLD                                   | Output          | Hold request to CPU. Hidden refresh will not hold                                                |

|                                        |                 | the CPU.                                                                                         |

| RFSH#                                  | Both            | AT Refresh Cycle Indication. It is an input pin during                                           |

| I/O BUS INTE                           | REACE           | master or DMA cycle                                                                              |

| CA0                                    | Both            | System Address Line 0, it is an input pin during                                                 |

| CAU                                    | Dom             | master or 8-bit DMA cycle; becomes output pin                                                    |

|                                        |                 | during CPU, 16-bit DMA cycle or refresh cycle.                                                   |

| CA1                                    | Both            | System Address Line 1, it is an input pin during                                                 |

|                                        |                 | master or DMA cycle; becomes output pin during                                                   |

|                                        |                 | CPU or refresh cycle.                                                                            |

| GATEA20                                | Input           | GateA20 input from 8042 or DBC emulated gate A20                                                 |

| C 4 20                                 | Dash            | pin. Geted AT has A20, connected to AT has I A20                                                 |

| GA20                                   | Both            | Gated AT bus A20; connected to AT bus LA20 indirectly through a buffer. It's an input pin during |

|                                        |                 | master cycle.                                                                                    |

| XD(7:0)                                | Both            | Peripheral Data Bus line 7-0. Two purposes for                                                   |