### (12) United States Patent

Vorbach et al.

#### US 9,075,605 B2 (10) Patent No.: (45) Date of Patent: Jul. 7, 2015

| (54) |            | S AND DEVICES FOR TREATING<br>CESSING DATA                                                                   |

|------|------------|--------------------------------------------------------------------------------------------------------------|

| (71) | Applicant: | PACT XPP TECHNOLOGIES AG,<br>Munich (DE)                                                                     |

| (72) | Inventors: | Martin Vorbach, Lingenfeld (DE);<br>Volker Baumgarte, Munich (DE)                                            |

| (73) | Assignee:  | PACT XPP TECHNOLOGIES AG,<br>Munich (DE)                                                                     |

| (*)  | Notice:    | Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. |

| (21) | Appl. No.: | 13/653,639                                                                                                   |

| (22) | Filed:     | Oct. 17, 2012                                                                                                |

| (65) |            | Prior Publication Data                                                                                       |

#### US 2013/0042137 A1 Feb. 14, 2013 Related U.S. Application Data

(60)Continuation of application No. 12/570,984, filed on Sep. 30, 2009, now Pat. No. 8,312,301, which is a

#### (Continued)

#### (30)Foreign Application Priority Data

| Mar. 5, 2001  | (DE) 101 10 530     |

|---------------|---------------------|

| Mar. 7, 2001  | (DE) 101 11 014     |

| Jun. 13, 2001 | (WO) PCT/EP01/06703 |

| Jun. 20, 2001 | (DE) 101 29 237     |

| Jun. 20, 2001 | (EP) 01115021       |

| Jul. 24, 2001 | (DE) 101 35 210     |

| Jul. 24, 2001 | (DE) 101 35 211     |

| Jul. 24, 2001 | (WO) PCT/EP01/08534 |

| Aug. 16, 2001 | (DE) 101 39 170     |

|               |                     |

| Aug. 29, 2001 | (DE) 101 42 231     |

| Sep. 3, 2001  | (DE) 101 42 894     |

| Sep. 3, 2001  | (DE) 101 42 903     |

| Sep. 11, 2001 | (DE) 101 44 732     |

| Sep. 13, 2001 | (DE) 101 42 904     |

| Sep. 17, 2001 | (DE) 101 45 792     |

| Sep. 17, 2001 | (DE) 101 45 795     |

| Sep. 19, 2001 | (DE) 101 46 132     |

| Sep. 30, 2001 | (WO) PCT/EP01/11299 |

| Nov. 5, 2001  | (DE) 101 54 259     |

| Nov. 5, 2001  | (DE) 101 54 260     |

| Nov. 9, 2001  |                     |

| /             |                     |

| Dec. 14, 2001 | (EP) 01129923       |

| Jan. 18, 2002 | (EP) 02001331       |

| Jan. 19, 2002 | (DE) 102 02 044     |

| Jan. 20, 2002 | (DE) 102 02 175     |

|               |                     |

| Feb. 15, 2002        | (DE)                                  | 102 06 653 |

|----------------------|---------------------------------------|------------|

| Feb. 18, 2002        | (DE)                                  | 102 06 856 |

| Feb. 18, 2002        | (DE)                                  | 102 06 857 |

| Feb. 21, 2002        | (DE)                                  | 102 07 224 |

| Feb. 21, 2002        | (DE)                                  | 102 07 225 |

| Feb. 21, 2002        | (DE)                                  | 102 07 226 |

| Feb. 27, 2002        | (DE)                                  | 102 08 434 |

| Feb. 27, 2002        | (DE)                                  | 102 08 435 |

| (51) <b>Int. Cl.</b> |                                       |            |

| G06F 1/00            | (2006.01)                             |            |

| G06F 1/32            | (2006.01)                             |            |

| (52) U.S. Cl.        | · · · · · · · · · · · · · · · · · · · |            |

CPC ...... G06F 1/3203 (2013.01); G06F 1/3237 (2013.01); Y02B 60/1221 (2013.01); Y02B

60/32 (2013.01) Field of Classification Search CPC . G06F 1/3203; G06F 1/3237; Y02B 60/1221; Y02B 60/32

See application file for complete search history.

#### (56)**References Cited**

# U.S. PATENT DOCUMENTS

3.473.160 A 10/1969 Wahlstrom et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

DE 42 21 278 1/1994 (Continued)

### OTHER PUBLICATIONS

Agarwal, A., et al., "APRIL: A Processor Architecture for Multiprocessing," Laboratory for Computer Science, MIT, Cambridge, MA, IEEE 1990, pp. 104-114.

(Continued)

Primary Examiner - M Elamin (74) Attorney, Agent, or Firm — Edward P. Heller, III

### ABSTRACT

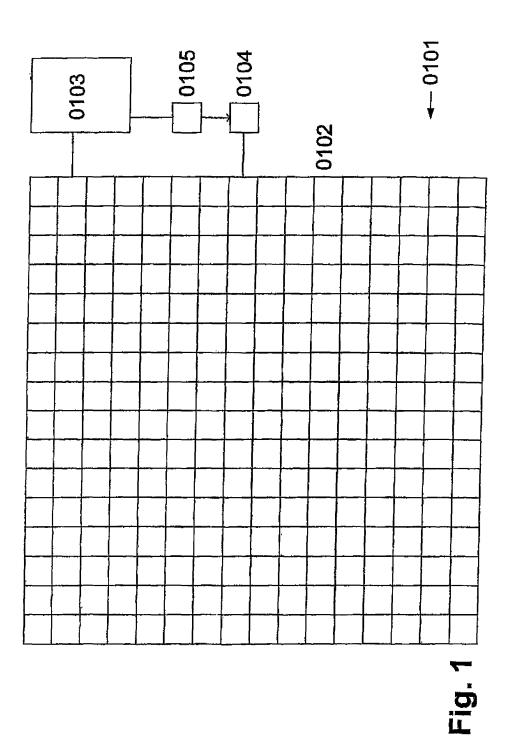

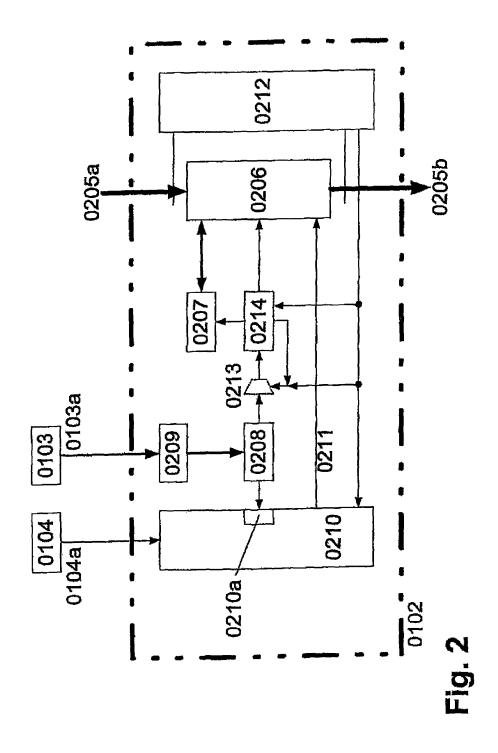

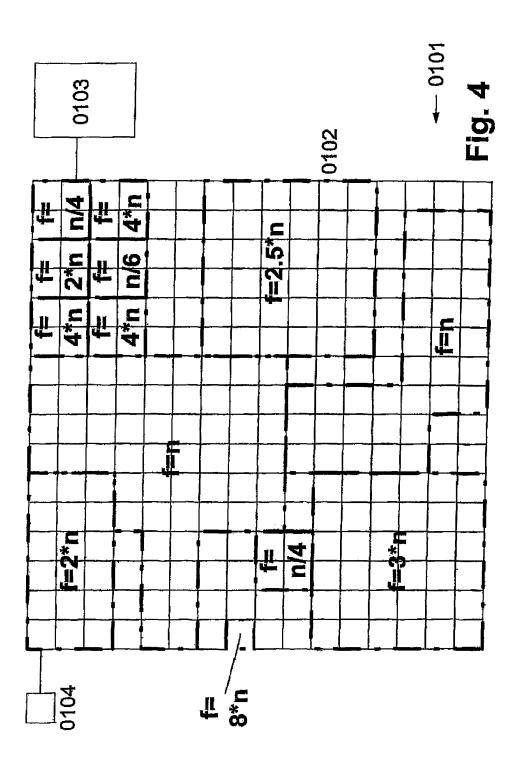

A data processing unit having a field of clocked logic cells (PAEs) which is operable in different configuration states and a clock preselecting means for preselecting logic cell clocking. The clock preselecting means is designed in such a way that, depending on the state, a first clock is preselected at least at a first cell (PAE) and an additional clock is preselected at least at an additional cell.

### 6 Claims, 7 Drawing Sheets

# US 9,075,605 B2 Page 2

|      | Relat                    | ed U.S. A          | application Data                 |      | 43,978           |              |                  | Nagler et al.                          |

|------|--------------------------|--------------------|----------------------------------|------|------------------|--------------|------------------|----------------------------------------|

|      | continuation             | of applic          | ation No. 12/257,075, filed on   |      | 47,924<br>55,997 |              |                  | Fujioka et al.<br>Sluijter et al.      |

|      |                          |                    | at. No. 8,099,618, which is a    |      | 55,308           |              | 11/1991          |                                        |

|      |                          |                    | on No. 10/469,909, filed as      |      | 70,475           |              |                  | Normoyle et al.                        |

|      |                          |                    | EP02/02402 on Mar. 5, 2002,      |      | 72,178<br>76,482 |              |                  | Matsumoto<br>Kozyrski et al.           |

|      | now Pat. No.             |                    | , ,                              |      | 81,375           |              |                  | Pickett et al.                         |

|      |                          | .,,.               |                                  | 5,0  | 31,575           | A            |                  | Hiller et al.                          |

| (56) |                          | Referen            | ces Cited                        |      | 99,447           |              |                  | Myszewski<br>Sluijter et al.           |

|      | II C                     | DATENT             | DOCLINATIVES                     |      | 09,503           |              |                  | Cruickshank et al.                     |

|      | U.S.                     | PALENT             | DOCUMENTS                        | 5,1  | 13,498           | A            |                  | Evan et al.                            |

| 3,   | ,531,662 A               | 9/1970             | Spandorfer et al.                |      | 15,510<br>19,290 |              |                  | Okamoto et al.<br>Loo et al.           |

|      | ,564,506 A               |                    | Bcc et al.                       |      | 23,109           |              | 6/1992           |                                        |

|      | ,681,578 A<br>,753,008 A |                    | Stevens<br>Guarnaschelli         | 5,12 | 28,559           | $\mathbf{A}$ | 7/1992           |                                        |

|      | ,754,211 A               |                    | Rocher et al.                    | 5,14 | 42,469<br>44,166 | A            |                  | Weisenborn<br>Camarota et al.          |

|      | ,855,577 A               |                    | Vandierendonck                   |      | 93,202           |              |                  | Jackson et al.                         |

|      | ,956,589 A<br>,020,469 A |                    | Weathers et al.<br>Manning       | 5,20 | 03,005           | A            | 4/1993           |                                        |

|      | ,151,611 A               |                    | Sugawara et al.                  |      | 04,935<br>08,491 |              |                  | Mihara et al.<br>Ebeling et al.        |

|      | ,233,667 A               |                    | Devine et al.                    |      | 12,716           |              |                  | Ferraiolo et al.                       |

|      | ,414,547 A<br>,498,134 A |                    | Knapp et al.<br>Hansen et al.    |      | 12,777           |              |                  | Gove et al.                            |

| 4,   | ,498,172 A               |                    | Bhavsar                          |      | 18,302<br>26,122 |              |                  | Loewe et al.<br>Thayer et al.          |

|      | ,566,102 A               |                    | Hefner                           |      | 34,363           |              |                  | Freeman                                |

|      | ,571,736 A<br>,590,583 A | 2/1986<br>5/1986   | Agrawal et al.                   |      | 33,539           |              |                  | Agrawal et al.                         |

|      | ,591,979 A               |                    | Iwashita                         |      | 37,686<br>43,238 |              | 8/1993<br>9/1993 | Asano et al.                           |

|      | ,594,682 A               |                    | Drimak                           |      | 45,227           |              |                  | Furtek et al.                          |

|      | ,623,997 A<br>,642,487 A | 11/1986<br>2/1987  |                                  | 5,24 | 45,616           | A            | 9/1993           |                                        |

|      | ,646,300 A               |                    | Goodman et al.                   |      | 47,689<br>34,444 |              | 9/1993           | Ewert<br>Kaplinsky                     |

|      | ,663,706 A               |                    | Allen et al.                     |      | 74,593           |              |                  | Proebsting                             |

|      | ,667,190 A<br>,682,284 A |                    | Fant et al.<br>Schrofer          |      | 76,836           |              |                  | Fukumaru et al.                        |

|      | ,686,386 A               | 8/1987             |                                  |      | 87,472<br>87,511 |              | 2/1994           | Horst<br>Robinson et al.               |

|      | ,700,187 A               | 10/1987            |                                  |      | 37,531           |              | 2/1994           |                                        |

|      | ,706,216 A<br>,720,778 A | 11/1987            | Hall et al.                      |      | 96,759           |              |                  | Sutherland et al.                      |

| 4,   | ,720,780 A               | 1/1988             | Dolecek                          |      | 98,805<br>01,284 |              |                  | Garverick et al.<br>Estes et al.       |

|      | ,722,084 A<br>,724,307 A |                    | Morton<br>Dutton et al.          | 5,30 | 01,344           | A            | 4/1994           | Kolchinsky                             |

|      | ,739,474 A               |                    | Holsztynski                      |      | 03,172<br>11,079 |              |                  | Magar et al.<br>Ditlow et al.          |

| 4,   | ,748,580 A               | 5/1988             | Ashton et al.                    | 5,3  | 27,125           | A            |                  | Iwase et al.                           |

|      | ,758,985 A<br>,760,525 A | 7/1988<br>7/1988   |                                  | 5,33 | 36,950           | A            | 8/1994           | Popli et al.                           |

|      | ,761,755 A               |                    | Ardini et al.                    |      | 43,406<br>47,639 |              |                  | Freeman et al.<br>Rechtschaffen et al. |

|      | ,768,196 A               |                    | Jou et al.                       |      | 49,193           |              |                  | Mott et al.                            |

|      | ,786,904 A<br>,791,603 A | 11/1988            | Graham, III et al.               |      | 53,432           |              |                  | Richek et al.                          |

|      | ,811,214 A               | 3/1989             | Nosenchuck et al.                |      | 55,508<br>57,152 |              | 10/1994          | Kan<br>Jennings, III et al.            |

|      | ,852,043 A               | 7/1989             |                                  |      | 51,373           |              | 11/1994          |                                        |

|      | ,852,048 A<br>,860,201 A | 8/1989             | Morton<br>Stolfo et al.          |      | 55,125           |              |                  | Goetting et al.                        |

| 4,   | ,870,302 A               | 9/1989             | Freeman                          |      | 79,444           |              |                  | Mumme<br>Goetting et al.               |

|      | ,873,666 A               |                    | Lefebvre et al.                  | 5,3  | 86,155           | A            | 1/1995           | Steele et al.                          |

|      | ,882,687 A<br>,884,231 A | 11/1989<br>11/1989 | Gordon<br>Mor et al.             |      | 86,518           |              |                  | Reagle et al.                          |

| 4,   | ,891,810 A               | 1/1990             | de Corlieu et al.                |      | 92,437           |              | 2/1995<br>2/1995 | Matter et al.<br>Jennings, III et al.  |

|      | ,901,268 A               | 2/1990             |                                  | 5,40 | 08,129           | A            | 4/1995           | Farmwald et al.                        |

|      | ,910,665 A<br>,918,440 A | 3/1990<br>4/1990   | Mattheyses et al.<br>Furtek      |      | 08,643           |              |                  | Katayose                               |

| 4,   | ,939,641 A               | 7/1990             | Schwartz et al.                  |      | 10,723<br>12,795 |              | 4/1995<br>5/1995 | Schmidt et al.<br>Larson               |

|      | ,959,781 A<br>,967,340 A | 9/1990<br>10/1990  | Rubenstein et al.                | 5,4  | 18,952           | A            | 5/1995           | Morley et al.                          |

|      | ,972,314 A               |                    | Getzinger et al.                 |      | 18,953           |              |                  | Hunt et al.                            |

| 4,   | ,992,933 A               | 2/1991             | Taylor                           |      | 21,019<br>22,823 |              | 5/1995<br>6/1995 | Holsztynski et al.<br>Agrawal et al.   |

|      | ,010,401 A<br>,014,193 A |                    | Murakami et al.<br>Garner et al. | 5,42 | 25,036           | $\mathbf{A}$ | 6/1995           | Liu et al.                             |

|      | ,014,193 A<br>,015,884 A |                    | Agrawal et al.                   |      | 26,378           |              | 6/1995           | Ong                                    |

| 5,   | ,021,947 A               | 6/1991             | Campbell et al.                  | ,    | 28,526<br>30,687 |              |                  | Flood et al.<br>Hung et al.            |

|      | ,023,775 A<br>,031,179 A | 6/1991<br>7/1991   | Poret<br>Yoshida et al.          |      | 35,000           |              | 7/1995           | Boothroyd et al.                       |

|      | ,031,179 A<br>,034,914 A |                    | Osterlund                        | 5,4  | 40,245           | $\mathbf{A}$ | 8/1995           | Galbraith et al.                       |

| 5,   | ,036,473 A               | 7/1991             | Butts et al.                     |      | 40,538           |              |                  |                                        |

|      | ,036,493 A<br>,041,924 A |                    | Nielsen<br>Blackborow et al.     |      | 40,711<br>42,790 |              | 8/1995<br>8/1995 | Sugimoto<br>Nosenchuck                 |

| 5,   | , , 7 . 1 1              | U, 1001            | Distribution of this             | 2,7  | ,,,,0            |              | 5,1773           | bellelidek                             |

| (56)                                     | Referen     | ces Cited                           | 5,625,806              |              |                  | Kromer                               |

|------------------------------------------|-------------|-------------------------------------|------------------------|--------------|------------------|--------------------------------------|

| T                                        | I C DATENIT | DOCUMENTS                           | 5,625,836<br>5,627,992 |              | 4/1997<br>5/1997 | Barker et al.                        |

| C                                        | .s. PATENT  | DOCUMENTS                           | 5,631,578              |              |                  | Clinton et al.                       |

| 5,444,394 A                              | 8/1995      | Watson et al.                       | 5,634,131              |              |                  | Matter et al.                        |

| 5,448,186 A                              |             | Kawata                              | 5,635,851<br>5,642,058 |              | 6/1997<br>6/1997 | Trimberger et al.                    |

| 5,448,496 A<br>5,450,022 A               |             | Butts et al.                        | 5,646,544              |              |                  | Iadanza                              |

| 5,455,525 A                              |             | Ho et al.                           | 5,646,545              | A            | 7/1997           | Trimberger et al.                    |

| 5,457,644 A                              | 10/1995     | McCollum                            | 5,646,546              |              |                  | Bertolet et al.                      |

| 5,465,375 A<br>5,469,003 A               |             | Thepaut et al.                      | 5,649,176<br>5,649,179 |              |                  | Selvidge et al.<br>Steenstra et al.  |

| 5,473,266 A                              |             | Ahanin et al.                       | 5,652,529              |              | 7/1997           | Gould et al.                         |

| 5,473,267                                | 12/1995     | Stansfield                          | 5,652,894              |              |                  | Hu et al.                            |

| 5,475,583 A                              |             | Bock et al.                         | 5,655,069<br>5,655,124 |              | 8/1997<br>8/1997 | Ogawara et al.                       |

| 5,475,803 A<br>5,475,856 A               |             | Stearns et al.                      | 5,656,950              | $\mathbf{A}$ |                  | Duong et al.                         |

| 5,477,525                                |             |                                     | 5,657,330              |              |                  | Matsumoto                            |

| 5,483,620 A                              |             | Pechanek et al.                     | 5,659,785<br>5,659,797 |              |                  | Pechanek et al.<br>Zandveld et al.   |

| 5,485,103 A<br>5,485,104 A               |             | Pedersen et al.<br>Agrawal et al.   | 5,671,432              |              |                  | Bertolet et al.                      |

| 5,488,582 A                              |             | Camarota                            | 5,675,262              |              |                  | Duong et al.                         |

| 5,489,857                                |             | Agrawal et al.                      | 5,675,743<br>5,675,757 |              | 10/1997          | Mavity Davidson et al.               |

| 5,491,353 A                              |             | Kean<br>Zlotnick                    | 5,675,777              |              |                  | Glickman                             |

| 5,493,239 A<br>5,493,663 A               |             |                                     | 5,677,909              | A            | 10/1997          | Heide                                |

| 5,497,498 A                              | A 3/1996    | Taylor                              | 5,680,583              |              |                  | Kuijsten                             |

| 5,500,609 A                              |             |                                     | 5,682,491<br>5,682,544 |              |                  | Pechanek et al.<br>Pechanek et al.   |

| 5,502,838 <i>A</i> 5,504,439 <i>A</i>    |             | Kikinis<br>Tavana                   | 5,687,325              |              | 11/1997          |                                      |

| 5,506,998 A                              |             | Kato et al.                         | 5,694,602              |              | 12/1997          |                                      |

| 5,510,730 A                              |             | El Gamal et al.                     | 5,696,791<br>5,696,976 |              | 12/1997          | Yeung<br>Nizar et al.                |

| 5,511,173 A<br>5,513,366 A               |             | Yamaura et al.<br>Agarwal et al.    | 5,701,091              |              | 12/1997          |                                      |

| 5,521,837 A                              |             | Frankle et al.                      | 5,705,938              | A            | 1/1998           | Kean                                 |

| 5,522,083 A                              | 5/1996      | Gove et al.                         | 5,706,482              |              |                  | Matsushima et al.                    |

| 5,525,971 A                              |             | Flynn<br>Takano                     | 5,713,037<br>5,715,476 |              |                  | Wilkinson et al.<br>Kundu et al.     |

| 5,530,873 A<br>5,530,946 A               |             | Bouvier et al.                      | 5,717,890              |              |                  | Ichida et al.                        |

| 5,532,693 A                              |             | Winters et al.                      | 5,717,943              |              |                  | Barker et al.                        |

| 5,532,957 A                              |             |                                     | 5,727,229<br>5,732,209 |              |                  | Kan et al.<br>Vigil et al.           |

| 5,535,406 A<br>5,537,057 A               |             | Kolchinsky<br>Leong et al.          | 5,734,869              |              | 3/1998           |                                      |

| 5,537,580 A                              |             | Giomi et al.                        | 5,734,921              |              |                  | Dapp et al.                          |

| 5,537,601 A                              |             | Kimura et al.                       | 5,737,516<br>5,737,565 |              |                  | Circello et al.<br>Mayfield          |

| 5,541,530 A<br>5,544,336 A               |             | Cliff et al.<br>Kato et al.         | 5,742,180              |              |                  | DeHon et al.                         |

| 5,548,773 A                              |             | Kemeny et al.                       | 5,745,734              | A            |                  | Craft et al.                         |

| 5,550,782 A                              | A 8/1996    | Cliff et al.                        | 5,748,872              |              |                  | Norman                               |

| 5,555,434 A<br>5,559,450 A               |             | Carlstedt<br>Ngai et al.            | 5,748,979<br>5,752,035 |              |                  | Trimberger<br>Trimberger             |

| 5,561,738 A                              |             | Kinerk et al.                       | 5,754,459              | A            | 5/1998           | Telikepalli                          |

| 5,568,624 A                              | 10/1996     | Sites et al.                        | 5,754,820              |              |                  | Yamagami<br>Dantisan da 1            |

| 5,570,040 A                              |             | Lytle et al.                        | 5,754,827<br>5,754,871 |              |                  | Barbier et al.<br>Wilkinson et al.   |

| 5,572,710 <i>F</i><br>5,574,927 <i>F</i> |             | Asano et al.<br>Scantlin            | 5,754,876              |              |                  | Tamaki et al.                        |

| 5,574,930 A                              | A 11/1996   | Halverson, Jr. et al.               | 5,760,602              |              | 6/1998           |                                      |

| 5,581,731 A                              |             | King et al.                         | 5,761,484<br>5,768,629 |              |                  | Agarwal et al.<br>Wise et al.        |

| 5,581,734 A<br>5,583,450 A               |             | DiBrino et al.<br>Trimberger et al. | 5,773,994              |              | 6/1998           |                                      |

| 5,584,013 A                              |             | Cheong et al.                       | 5,774,704              |              |                  | Williams 713/501                     |

| 5,586,044 A                              |             | Agrawal et al.                      | 5,778,237<br>5,778,439 |              |                  | Yamamoto et al.<br>Trimberger et al. |

| 5,587,921 A<br>5,588,152 A               |             | Agrawal et al. Dapp et al.          | 5,781,756              |              | 7/1998           |                                      |

| 5,590,345 A                              |             | Barker et al.                       | 5,784,313              |              |                  | Trimberger et al.                    |

| 5,590,348 A                              |             | Phillips et al.                     | 5,784,630<br>5,784,636 |              | 7/1998<br>7/1998 | Saito et al.                         |

| 5,596,742 A<br>5,596,743 A               |             | Agarwal et al.<br>Bhat et al.       | 5,784,636<br>5,794,059 |              |                  | Barker et al.                        |

| 5,600,265 A                              |             | El Gamal et al.                     | 5,794,062              | A            | 8/1998           | Baxter                               |

| 5,600,597 A                              | A 2/1997    | Kean et al.                         | 5,801,547              |              | 9/1998           |                                      |

| 5,600,845 A                              |             |                                     | 5,801,715<br>5,801,958 |              |                  | Norman<br>Dangelo et al              |

| 5,602,999 A<br>5,603,005 A               |             | Hyatt<br>Bauman et al.              | 5,802,290              |              |                  | Dangelo et al.<br>Casselman          |

| 5,606,698 A                              |             | Powell                              | 5,804,986              |              | 9/1998           |                                      |

| 5,608,342 A                              | 3/1997      | Trimberger                          | 5,805,477              |              | 9/1998           |                                      |

| 5,611,049 A                              |             |                                     | 5,815,004              |              |                  | Trimberger et al.                    |

| 5,617,547 <i>F</i><br>5,617,577 <i>F</i> |             | Feeney et al.<br>Barker et al.      | 5,815,715<br>5,815,726 |              | 9/1998           | Kuçukçakar<br>Cliff                  |

| 5,619,720 A                              |             | Garde et al.                        | 5,821,774              |              |                  | Veytsman et al.                      |

|                                          |             |                                     |                        |              |                  |                                      |

| (56)                       | Referen          | ces Cited                             |    | 058,469            |    | 5/2000           |                                      |

|----------------------------|------------------|---------------------------------------|----|--------------------|----|------------------|--------------------------------------|

|                            |                  |                                       |    | 064,819            |    |                  | Franssen et al.                      |

| U.S                        | . PATENT         | DOCUMENTS                             |    | 072,348<br>075,935 |    |                  | New et al.<br>Ussery et al.          |

| 5,828,229 A                | 10/1009          | Cliff et al.                          |    | 075,933            |    |                  | Borkenhagen et al.                   |

| 5,828,858 A                |                  | Athanas et al.                        |    | 077,315            |    |                  | Greenbaum et al.                     |

| 5,831,448 A                | 11/1998          |                                       |    | 078,736            |    |                  | Guccione                             |

| 5,832,288 A                | 11/1998          |                                       |    | 081,903            |    |                  | Vorbach et al.                       |

| 5,838,165 A                | 11/1998          |                                       |    | 084,429<br>085,317 |    | 7/2000           | Trimberger<br>Smith                  |

| 5,838,988 A<br>5,841,973 A |                  | Panwar et al.<br>Kessler et al.       |    | 086,628            |    |                  | Dave et al.                          |

| 5,844,422 A                |                  | Trimberger et al.                     |    | 088,795            |    | 7/2000           | Vorbach et al.                       |

| 5,844,888 A                |                  | Markkula, Jr. et al.                  |    | 092,174            |    |                  | Roussakov                            |

| 5,848,238 A                |                  | Shimomura et al.                      |    | E36,839<br>096,091 |    |                  | Simmons et al.<br>Hartmann           |

| 5,854,918 A                | 12/1998          |                                       |    | 105,105            |    |                  | Trimberger et al.                    |

| 5,857,097 A<br>5,857,109 A | 1/1999           | Henzinger et al.                      |    | 105,106            |    |                  | Manning                              |

| 5,859,544 A                |                  | Norman                                |    | 108,760            |    |                  | Mirsky et al.                        |

| 5,860,119 A                | 1/1999           | Dockser                               |    | 118,724            |    |                  | Higginbottom                         |

| 5,862,403 A                |                  | Kanai et al.                          |    | 119,181<br>122,719 |    |                  | Vorbach et al.<br>Mirsky et al.      |

| 5,867,691 A                |                  | Shiraishi<br>Chin et al.              |    | 125,072            |    | 9/2000           |                                      |

| 5,867,723 A<br>5,870,620 A |                  | Kadosumi et al.                       |    | 125,408            |    |                  | McGee et al.                         |

| 5,884,075 A                |                  | Hester et al.                         |    | 127,908            |    |                  | Bozler et al.                        |

| 5,887,162 A                |                  | Williams et al.                       |    | 128,720            |    |                  | Pechanek et al.                      |

| 5,887,165 A                |                  | Martel et al.                         |    | 134,166<br>137,307 |    |                  | Lytle et al.<br>Iwanczuk et al.      |

| 5,889,533 A                | 3/1999           |                                       |    | 145,072            |    |                  | Shams et al.                         |

| 5,889,982 A<br>5,892,370 A |                  | Rodgers et al.<br>Eaton et al.        |    | 150,837            |    |                  | Beal et al.                          |

| 5,892,961 A                |                  | Trimberger                            |    | 150,839            |    |                  | New et al.                           |

| 5,892,962 A                | 4/1999           | Cloutier                              |    | 154,048            |    |                  | Iwanczuk et al.                      |

| 5,894,565 A                |                  | Furtek et al.                         |    | 154,049<br>154,826 |    | 11/2000          | New<br>Wulf et al.                   |

| 5,895,487 A                |                  | Boyd et al.                           |    | 157,214            |    |                  | Marshall                             |

| 5,898,602 A<br>5,901,279 A |                  | Rothman et al.<br>Davis, III          |    | 170,051            |    |                  | Dowling                              |

| 5,913,925 A                |                  | Kahle et al.                          |    | 172,520            |    |                  | Lawman et al.                        |

| 5,915,099 A                | 6/1999           | Takata et al.                         |    | 173,419            |    |                  | Barnett                              |

| 5,915,123 A                |                  | Mirsky et al.                         |    | 173,434<br>178,494 |    |                  | Wirthlin et al.<br>Casselman         |

| 5,924,119 A                | 7/1999<br>7/1999 | Sindhu et al.                         |    | 185,256            |    |                  | Saito et al.                         |

| 5,926,638 A<br>5,933,023 A | 8/1999           |                                       |    | 185,731            |    |                  | Maeda et al.                         |

| 5,933,642 A                |                  | Greenbaum et al.                      | 6, | 188,240            | В1 |                  | Nakaya                               |

| 5,936,424 A                | 8/1999           | Young et al.                          |    | 188,650            |    |                  | Hamada et al.                        |

| 5,943,242 A                |                  | Vorbach et al.                        |    | 191,614<br>198,304 |    | 3/2001           | Schultz et al.                       |

| 5,956,518 A<br>5,960,193 A |                  | DeHon et al.<br>Guttag et al.         |    | 201,406            |    |                  | Iwanczuk et al.                      |

| 5,960,200 A                |                  | Eager et al.                          |    | 202,163            |    |                  | Gabzdyl et al.                       |

| 5,966,143 A                |                  | Breternitz, Jr.                       |    | 202,182            |    |                  | Abramovici et al.                    |

| 5,966,534 A                |                  | Cooke et al.                          |    | 204,687            |    |                  | Schultz et al.                       |

| 5,970,254 A                |                  | Cooke et al.                          |    | 211,697<br>212,544 |    |                  | Lien et al.<br>Borkenhagen et al.    |

| 5,978,260 A                |                  | Trimberger et al.<br>Ekanadham et al. |    | 212,650            |    |                  | Guccione                             |

| 5,978,583 A<br>5,996,048 A |                  | Cherabuddi et al.                     |    | 215,326            |    |                  | Jefferson et al.                     |

| 5,996,083 A                |                  | Gupta et al.                          |    | 216,223            |    |                  | Revilla et al.                       |

| 5,999,990 A                |                  | Sharrit et al.                        |    | 219,833            |    |                  | Solomon et al.                       |

| 6,003,143 A                |                  | Kim et al.                            |    | E37,195<br>230,307 |    | 5/2001<br>5/2001 | Rean<br>Davis et al.                 |

| 6,011,407 A<br>6,014,509 A | 1/2000           | New<br>Furtek et al.                  |    | 240,502            |    |                  | Panwar et al.                        |

| 6,020,758 A                |                  | Patel et al.                          | 6, | 243,808            | B1 | 6/2001           | Wang                                 |

| 6,020,760 A                |                  | Sample et al.                         |    | 247,036            |    |                  | Landers et al.                       |

| 6,021,490 A                |                  | Vorbach et al.                        |    | 247,147            |    |                  | Beenstra et al.                      |

| 6,023,564 A                |                  | Trimberger                            |    | 249,756<br>252,792 |    | 6/2001<br>6/2001 | Bunton et al.<br>Marshall et al.     |

| 6,023,742 A<br>6,026,478 A |                  | Ebeling et al. Dowling                |    | 256,724            |    |                  | Hocevar et al.                       |

| 6,026,481 A                |                  | New et al.                            |    | 260,114            |    | 7/2001           | Schug                                |

| 6,034,538 A                |                  | Abramovici                            |    | 260,179            |    |                  | Ohsawa et al.                        |

| 6,035,371 A                |                  | Magloire                              |    | 262,908            |    |                  | Marshall et al.<br>Trimberger et al. |

| 6,038,650 A                |                  | Vorbach et al.                        |    | 263,430<br>266,760 |    | 7/2001<br>7/2001 | DeHon et al.                         |

| 6,038,656 A                |                  | Martin et al. Zheng et al.            |    | 279,077            |    |                  | Nasserbakht et al.                   |

| 6,044,030 A<br>6,045,585 A |                  | Blainey                               |    | 282,627            |    |                  | Wong et al.                          |

| 6,047,115 A                |                  | Mohan et al.                          | 6, | 282,701            | В1 | 8/2001           | Wygodny et al.                       |

| 6,049,222 A                | 4/2000           | Lawman                                |    | 285,624            |    | 9/2001           |                                      |

| 6,049,866 A                | 4/2000           |                                       |    | 286,134            |    |                  | Click, Jr. et al.                    |

| 6,052,524 A                | 4/2000           |                                       |    | 288,566            |    |                  | Hanrahan et al.                      |

| 6,052,773 A<br>6,054,873 A |                  | DeHon et al.<br>Laramie               |    | 289,369<br>289,440 |    | 9/2001           | Sundaresan<br>Casselman              |

| 6,055,619 A                |                  | North et al.                          |    | 298,043            |    | 10/2001          | Mauger et al.                        |

| 6,058,266 A                |                  | Megiddo et al.                        |    | 298,396            |    |                  | Loyer et al.                         |

| -,, **                     |                  | G                                     | ٠, | ,                  |    |                  | , —·                                 |

| (56)                         | Referen            | nces Cited                            | 6,553,479 H                |            | Mirsky et al.                        |

|------------------------------|--------------------|---------------------------------------|----------------------------|------------|--------------------------------------|

| U.S                          | . PATENT           | DOCUMENTS                             | 6,567,834 E<br>6,571,381 E |            | Marshall et al.<br>Vorbach et al.    |

|                              |                    |                                       | 6,587,939 H                |            | Takano                               |

| 6,298,472 B1<br>6,301,706 B1 | 10/2001<br>10/2001 | Phillips et al.<br>Maslennikov et al. | 6,598,128 E<br>6,606,704 E |            | Yoshioka et al.<br>Adiletta et al.   |

| 6,311,200 B1                 |                    | Hanrahan et al.                       | 6,624,819 E                | 31 9/2003  | Lewis                                |

| 6,311,265 B1                 | 10/2001            | Beckerle et al.                       | 6,625,631 H                |            | Ruehle                               |

| 6,321,298 B1                 | 11/2001            |                                       | 6,631,487 H<br>6,633,181 H |            | Abramovici et al.                    |

| 6,321,366 B1<br>6,321,373 B1 |                    | Tseng et al.<br>Ekanadham et al.      | 6,657,457 E                |            | Hanrahan et al.                      |

| 6,338,106 B1                 |                    | Vorbach et al.                        | 6,658,564 H                |            | Smith et al.                         |

| 6,339,424 B1                 |                    | Ishikawa et al.                       | 6,665,758 E                |            | Frazier et al.<br>Ruf                |

| 6,339,840 B1<br>6,341,318 B1 |                    | Kothari et al.<br>Dakhil              | 6,668,237 E                | 31 12/2003 | Guccione et al.                      |

| 6,347,346 B1                 | 2/2002             | Taylor                                | 6,681,388 H                |            |                                      |

| 6,349,346 B1<br>6,353,841 B1 |                    | Hanrahan et al.<br>Marshall et al.    | 6,687,788 E<br>6,694,434 E |            | Vorbach et al.<br>McGee et al.       |

| 6,362,650 B1                 |                    | New et al.                            | 6,697,979 E                | 31 2/2004  | Vorbach et al.                       |

| 6,370,596 B1                 | 4/2002             | Dakhil                                | 6,704,816 H<br>6,708,223 H |            | Burke<br>Wang et al.                 |

| 6,373,779 B1<br>6,374,286 B1 | 4/2002<br>4/2002   | Pang et al.                           | 6,708,325 E                |            | Cooke et al.                         |

| 6,378,068 B1                 |                    | Foster et al.                         | 6,717,436 H                | 32 4/2004  | Kress et al.                         |

| 6,381,624 B1                 |                    | Colon-Bonet et al.                    | 6,721,830 H<br>6,725,334 H |            | Vorbach et al.<br>Barroso et al.     |

| 6,389,379 B1<br>6,389,579 B1 |                    | Lin et al.<br>Phillips et al.         | 6,728,871 E                |            | Vorbach et al.                       |

| 6,392,912 B1                 |                    | Hanrahan et al.                       | 6,745,317 E                | 31 6/2004  | Mirsky et al.                        |

| 6,400,601 B1                 |                    | Sudo et al.                           | 6,748,440 H<br>6,751,722 H |            | Lisitsa et al.<br>Mirsky et al.      |

| 6,404,224 B1<br>6,405,185 B1 |                    | Azegami et al.<br>Pechanek et al.     | 6,754,805 E                |            |                                      |

| 6,405,299 B1                 |                    | Vorbach et al.                        | 6,757,847 H                | 31 6/2004  | Farkash et al.                       |

| 6,421,808 B1                 |                    | McGeer                                | 6,757,892 E<br>6,782,445 E |            | Gokhale et al.<br>Olgiati et al.     |

| 6,421,809 B1<br>6,421,817 B1 |                    | Wuytack et al.<br>Mohan et al.        | 6,785,826 H                |            | Durham et al.                        |

| 6,425,054 B1                 | 7/2002             | Nguyen                                | 6,802,026 H                |            | Patterson et al.                     |

| 6,425,068 B1                 |                    | Vorbach                               | 6,803,787 E<br>6,820,188 E |            | Wicker, Jr.<br>Stansfield et al.     |

| 6,426,649 B1<br>6,427,156 B1 |                    | Fu et al.<br>Chapman et al.           | 6,829,697 E                | 31 12/2004 | Davis et al.                         |

| 6,430,309 B1                 | 8/2002             | Pressman et al.                       | 6,836,842 E                |            | Guccione et al.                      |

| 6,434,642 B1<br>6,434,672 B1 |                    | Camilleri et al.<br>Gaither           | 6,847,370 H<br>6,859,869 H |            | Baldwin et al.<br>Vorbach            |

| 6,434,695 B1                 |                    | Esfahani et al.                       | 6,868,476 E                | 3/2005     | Rosenbluth                           |

| 6,434,699 B1                 |                    | Jones et al.                          | 6,871,341 E<br>6,874,108 E |            | Shyr<br>Abramovici et al.            |

| 6,437,441 B1<br>6,438,747 B1 |                    | Yamamoto<br>Schreiber et al.          | 6,886,092 E                |            | Douglass et al.                      |

| 6,449,283 B1                 | 9/2002             | Chao et al.                           | 6,901,502 H                |            | Yano et al.                          |

| 6,456,628 B1                 |                    | Greim et al.                          | 6,928,523 E<br>6,957,306 E |            | Yamada<br>So et al.                  |

| 6,457,116 B1<br>6,476,634 B1 | 11/2002            | Mirsky et al.<br>Bilski               | 6,961,924 H                |            | Bates et al.                         |

| 6,477,643 B1                 | 11/2002            | Vorbach et al.                        | 6,975,138 H                |            | Pani et al.                          |

| 6,480,937 B1<br>6,480,954 B2 |                    | Vorbach et al.                        | 6,977,649 H<br>7,000,161 H |            | Baldwin et al.<br>Allen et al.       |

| 6,483,343 B1                 |                    | Trimberger et al.<br>Faith et al.     | 7,007,096 E                | 31 2/2006  | Lisitsa et al.                       |

| 6,487,709 B1                 | 11/2002            | Keller et al.                         | 7,010,667 E                |            | Vorbach                              |

| 6,490,695 B1<br>6,496,740 B1 |                    | Zagorski et al.<br>Robertson et al.   | 7,010,687 H<br>7,028,107 H |            | Ichimura Vorbach et al.              |

| 6,496,902 B1                 |                    | Faanes et al.                         | 7,036,114 E                | 32 4/2006  | McWilliams et al.                    |

| 6,496,971 B1                 | 12/2002            | Lesea et al.                          | 7,038,952 H<br>7,043,416 H |            | Zack et al.                          |

| 6,504,398 B1<br>6,507,898 B1 |                    | Lien et al.<br>Gibson et al.          | 7,043,416 E<br>7,144,152 E |            | Rusu et al.                          |

| 6,507,947 B1                 |                    | Schreiber et al.                      | 7,155,708 H                | 32 12/2006 | Hammes et al.                        |

| 6,512,804 B1                 | 1/2003             |                                       | 7,164,422 H<br>7,210,129 H |            | Wholey et al.<br>May et al.          |

| 6,513,077 B2<br>6,516,382 B2 |                    | Vorbach et al.<br>Manning             | 7,216,129 E                |            | Rosenbluth                           |

| 6,518,787 B1                 | 2/2003             |                                       | 7,237,087 E                |            | Vorbach et al.                       |

| 6,519,674 B1                 |                    | Lam et al.                            | 7,249,351 H<br>7,254,649 H |            |                                      |

| 6,523,107 B1<br>6,525,678 B1 |                    | Stansfield et al.<br>Veenstra et al.  | 7,266,725 E                | 32 9/2007  | Vorbach et al.                       |

| 6,526,461 B1                 | 2/2003             | Cliff                                 | 7,340,596 H                |            | Crosland et al.                      |

| 6,526,520 B1                 |                    | Vorbach et al.                        | 7,346,644 H<br>7,350,178 H |            | Langhammer et al.<br>Crosland et al. |

| 6,538,468 B1<br>6,538,470 B1 |                    | Moore<br>Langhammer et al.            | 7,382,156 H                |            | Pani et al.                          |

| 6,539,415 B1                 | 3/2003             | Mercs                                 | 7,455,450 E                | 32 11/2008 | Liu et al.                           |

| 6,539,438 B1                 |                    | Ledzius et al.                        | 7,595,659 E                |            | Vorbach et al.                       |

| 6,539,477 B1<br>6,542,394 B2 | 3/2003<br>4/2003   | Seawright<br>Marshall et al.          | 7,650,448 H                |            | Vorbach et al.<br>Vorbach et al.     |

| 6,542,844 B1                 | 4/2003             | Hanna                                 | 7,759,968 E                | 31 7/2010  | Hussein et al.                       |

| 6,542,998 B1                 |                    | Vorbach                               | 7,873,811 H                |            | Wolinski et al.                      |

| 6,553,395 B2                 | 4/2003             | Marshall et al.                       | 7,971,051 H                | 52 6/2011  | Paul et al.                          |

| (56) References Cited        |        |                  |                                 | DI       |              | 6/1998              |

|------------------------------|--------|------------------|---------------------------------|----------|--------------|---------------------|

|                              | U.S. I | PATENT           | DOCUMENTS                       | DI<br>DI | E 196 54 595 | 7/1998<br>7/1998    |

|                              |        |                  |                                 | DI       |              | 7/1998              |

| 2001/0001860                 |        | 5/2001           |                                 | DI<br>DI |              | 8/1998<br>8/1998    |

| 2001/0003834<br>2001/0010074 |        | 6/2001<br>7/2001 | Shimonishi<br>Nishihara et al.  | Di       |              | 9/1998              |

| 2001/0010074                 |        | 8/2001           | Fujii et al.                    | DI       | E 198 22 776 | 3/1999              |

| 2002/0004916                 | A1     |                  | Marchand et al.                 | DI       |              | 8/1999              |

| 2002/0010853                 |        | 1/2002           | Trimberger et al.               | DI<br>DI |              | 2/2000<br>12/2000   |

| 2002/0013861<br>2002/0032305 |        | 3/2002           | Adiletta et al.                 | Di       |              | 12/2001             |

| 2002/0038414                 |        | 3/2002           |                                 | DI       |              | 2/2002              |

| 2002/0045952                 |        |                  | Blemel                          | DI<br>DI |              | 4/2002              |

| 2002/0051482<br>2002/0073282 |        | 5/2002           | Lomp<br>Chauvel et al.          | EF       |              | 8/2003<br>1/1987    |

| 2002/00/3282                 |        |                  | Pereira et al.                  | EF       |              | 5/1987              |

| 2002/0099759                 |        |                  | Gootherts                       | EF       |              | 11/1990             |

| 2002/0103839                 |        | 8/2002           |                                 | EF<br>EF |              | 5/1991<br>1/1992    |

| 2002/0124238<br>2002/0138716 |        |                  | Metzgen<br>Master et al.        | EF       |              | 4/1992              |

| 2002/0138710                 |        |                  | Drusinsky                       | EF       | 0 485 690    | 5/1992              |

| 2002/0144229                 |        | 10/2002          | Hanrahan                        | EF       |              | 8/1992              |

| 2002/0147932                 |        |                  | Brock et al.                    | EF<br>EF |              | 5/1993<br>A2 8/1994 |

| 2002/0152060<br>2002/0156962 |        | 10/2002          | Tseng<br>Chopra et al.          | EF       |              | 12/1994             |

| 2002/0162097                 |        |                  | Meribout                        | EF       | 0 678 985    | 10/1995             |

| 2002/0165886                 |        | 11/2002          |                                 | EF       |              | 12/1995             |

| 2003/0001615                 |        |                  | Sueyoshi et al.                 | EF<br>EF |              | 2/1996<br>4/1996    |

| 2003/0014743<br>2003/0046607 |        | 3/2003           | Cooke et al.<br>May et al.      | EF       |              | 8/1996              |

| 2003/0052711                 |        | 3/2003           | Taylor                          | EF       |              | 10/1996             |

| 2003/0055861                 |        |                  | Lai et al.                      | EF<br>EF |              | 12/1996<br>12/1996  |

| 2003/0056062<br>2003/0056085 |        | 3/2003<br>3/2003 | Prabhu<br>Vorbach               | EF       |              | 6/1999              |

| 2003/0056091                 |        | 3/2003           | Greenberg                       | EF       | 1 061 439    | 12/2000             |

| 2003/0056202                 | A1     | 3/2003           | May et al.                      | EF       |              | 7/2001              |

| 2003/0061542                 |        | 3/2003           | Bates et al.                    | EF<br>EF |              | 10/2001<br>6/2006   |

| 2003/0062922<br>2003/0070059 |        | 4/2003<br>4/2003 | Douglass et al. Dally et al.    | FF       |              | 2/1998              |

| 2003/0086300                 |        | 5/2003           | Noyes et al.                    | Gl       |              | 3/1997              |

| 2003/0093662                 |        | 5/2003           | Vorbach et al.                  | JР<br>JР |              | 8/1946<br>4/1983    |

| 2003/0097513<br>2003/0123579 |        | 5/2003<br>7/2003 | Vorbach et al.<br>Safavi et al. | JP       |              | 2/1989              |

| 2003/0125579                 |        | 7/2003           |                                 | JP       | 1-229378     | 9/1989              |

| 2003/0154349                 | A1     | 8/2003           | Berg et al.                     | JP       |              | 5/1990              |

| 2003/0192032                 |        | 10/2003          | Andrade et al.                  | JP<br>JP |              | 9/1990<br>10/1993   |

| 2003/0226056<br>2004/0015899 |        | 1/2003           | Yip et al.<br>May et al.        | JP       |              | 10/1993             |

| 2004/0025005                 |        | 2/2004           | Vorbach et al.                  | JP       |              | 12/1993             |

| 2004/0039880                 |        |                  | Pentkovski et al.               | JР<br>JР |              | 9/1994<br>3/1995    |

| 2004/0078548<br>2004/0088689 |        | 4/2004           | Claydon et al.<br>Hammes        | JP       |              | 6/1995              |

| 2004/0088691                 |        |                  | Hammes et al.                   | JP       | 8-148989     | 6/1995              |

| 2004/0168099                 |        | 8/2004           | Vorbach et al.                  | JP       |              | 7/1995              |

| 2004/0199688                 |        | 10/2004          | Vorbach et al.                  | JР<br>JР |              | 7/1995<br>2/1996    |

| 2005/0066213<br>2005/0091468 |        | 3/2005           | Vorbach et al.<br>Morita et al. | JP       |              | 3/1996              |

| 2005/0144210                 |        |                  | Simkins et al.                  | JP       | 1 712112     | 4/1996              |

| 2005/0144212                 |        |                  | Simkins et al.                  | JP<br>JP |              | 4/1996<br>4/1996    |

| 2005/0144215                 |        | 6/2005           | Simkins et al.                  | JP       |              | 9/1996              |

| 2006/0036988                 |        | 2/2006           | Allen et al.                    | JP       | 9-027745     | 1/1997              |

| 2006/0095716<br>2006/0230094 |        | 10/2006          | Ramesh<br>Simkins et al.        | JP       |              | 9/1997              |

| 2006/0230096                 |        |                  | Thendean et al.                 | JР<br>JР |              | 11/1997<br>2/1999   |

| 2007/0050603                 | A1     | 3/2007           | Vorbach et al.                  | JP       |              | 7/1999              |

| 2007/0083730                 |        | 4/2007           | Vorbach et al.                  | JP       | 11-307725    | 11/1999             |

| 2007/0143577                 |        | 6/2007           |                                 | JР<br>JР |              | 3/2000<br>6/2000    |

| 2008/0313383<br>2009/0085603 |        | 4/2009           | Morita et al.<br>Paul et al.    | JP<br>JP |              | 6/2000<br>7/2000    |

| 2009/0193384                 |        | 7/2009           |                                 | JP       |              | 11/2000             |

| 2010/0306602                 |        |                  | Kamiya et al.                   | JP       | 2001-500682  | 1/2001              |

|                              | . D. E |                  |                                 | JP       |              | 6/2001              |

| FC                           | REIG   | N PATE           | NT DOCUMENTS                    | JP<br>JP |              | 7/2001<br>8/2001    |

| DE                           | 44 16  | 881              | 11/1994                         | JP<br>JP |              | 1/2002              |

| DE                           |        | 5881 A1          | 11/1994                         | JP       | 3-961028     | 8/2007              |

| DE                           | 38 55  | 673              | 11/1996                         | W        | O WO90/04835 | 5/1990              |

|                              |        |                  |                                 |          |              |                     |

| (56)                                   | Refere                                                                                                                         | ences Cited                                                                              |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                                        | FOREIGN PAT                                                                                                                    | ENT DOCUMENTS                                                                            |

| WO<br>WO<br>WO<br>WO<br>WO<br>WO<br>WO | WO90/11648<br>WO92/01987<br>WO93/11503<br>WO94/06077<br>WO94/08399<br>WO95/26001<br>W09528671<br>WO98/10517<br>WO98/26356      | 10/1990<br>2/1992<br>6/1993<br>3/1994<br>4/1994<br>9/1995<br>10/1995<br>3/1998<br>6/1998 |

| WO<br>WO<br>WO<br>WO<br>WO<br>WO       | WO98/26330<br>WO98/28697<br>WO98/29952<br>WO98/31102<br>WO98/35294<br>WO99/00731<br>WO99/00731                                 | 6/1998<br>7/1998<br>7/1998<br>7/1998<br>8/1998<br>8/1998<br>1/1999                       |

| WO<br>WO<br>WO<br>WO<br>WO             | WO99/12111<br>WO99/32975<br>WO99/40522<br>WO99/44120<br>WO99/44147<br>WO00/17771                                               | 3/1999<br>7/1999<br>8/1999<br>9/1999<br>9/1999<br>3/2000                                 |

| WO<br>WO<br>WO<br>WO<br>WO<br>WO       | WO00/38087<br>WO00/45282<br>WO00/49496<br>WO00/77652<br>WO01/55917<br>WO02/13000<br>WO02/29600                                 | 6/2000<br>8/2000<br>8/2000<br>12/2000<br>8/2001<br>2/2002<br>4/2002                      |

| WO<br>WO<br>WO<br>WO<br>WO<br>WO       | WO02/50665<br>WO02/071196<br>WO02/071248<br>WO02/071249<br>WO02/103532<br>WO03/017095<br>WO03/023616                           | 6/2002<br>9/2002<br>9/2002<br>9/2002<br>12/2002<br>2/2003<br>3/2003                      |

| WO<br>WO<br>WO<br>WO<br>WO<br>WO       | WO03/025781<br>WO03/025781<br>WO03/036507<br>WO 03/091875<br>WO2004/053718<br>WO2004/114128<br>WO2005/045692<br>WO 2007/030395 | 3/2003<br>5/2003<br>5/2003<br>11/2003<br>6/2004<br>12/2004<br>5/2005<br>3/2007           |

### OTHER PUBLICATIONS

Almasi and Gottlieb, *Highly Parallel Computing*, The Benjamin/Cummings Publishing Company, Inc., Redwood City, CA, 1989, 3 pages (Fig. 4.1).

Advanced RISC Machines Ltd (ARM), "AMBA—Advanced Microcontroller Bus Architecture Specification," (Document No. ARM IHI 0001C), Sep. 1995, 72 pages.

Alfke, Peter; New, Bernie, Xilinx Application Note, "Additional XC3000 Data," XAPP 024.000, 1994, pp. 8-11 through 8-20.

Alfke, Peter; New, Bernie, Xilinx Application Note, "Adders, Subtracters and Accumulators in XC3000," XAPP 022.000, 1994, pp. 8-98 through 8-104.

Alfke, Peter, Xilinx Application Note, "Megabit FIFO in Two Chips: One LCA Device and One DRAM," XAPP 030.000, 1994, pp. 8-148 through 8-150.

Alfke, Peter, Xilinx Application Note, "Dynamic Reconfiguration," XAPP 093, Nov. 10, 1997, pp. 13-45 through 13-46.

Alfke, Peter; New, Bernie, Xilinx Application Note, "Implementing State Machines in LCA Devices," XAPP 027.001, 1994, pp. 8-169 through 8-172.

Algotronix, Ltd., CAL64K Preliminary Data Sheet, Apr. 1989, pp. 1-24.

Algotronix, Ltd., CAL4096 Datasheet, 1992, pp. 1-53.

Algotronix, Ltd., CHS2x4 User Manual, "CHA2x4 Custom Computer," 1991, pp. 1-38.

Allaire, Bill; Fischer, Bud, Xilinx Application Note, "Block Adaptive Filter," XAPP 055, Aug. 15, 1996 (Version 1.0), pp. 1-10.

Altera Application Note (73), "Implementing FIR Filters in FLEX Devices," Altera Corporation, Feb. 1998, ver. 1.01, pp. 1-23.

Athanas, P. (Thesis), "An adaptive machine architecture and compiler for dynamic processor reconfiguration," Brown University 1992, pp. 1-157.

Berkeley Design Technology, Inc., Buyer's Guide to DSP Processors, 1995, Fremont, CA., pp. 673-698.

Bittner, R. et al., "Colt: An Experiment in Wormhole Run-Time Reconfiguration," Bradley Department of Electrical and Computer Engineering, Blacksburg, VA, SPIE—International Society for Optical Engineering, vol. 2914/187, Nov. 1996, Boston, MA, pp. 187-194

Camilleri, Nick; Lockhard, Chris, *Xilinx Application Note*, "Improving XC4000 Design Performance," XAPP 043.000, 1994, pp. 8-21 through 8-35.

Cartier, Lois, *Xilinx Application Note*, "System Design with New XC4000EX I/O Features," Feb. 21, 1996, pp. 1-8.

Chen, D., (Thesis) "Programmable arithmetic devices for high speed digital signal processing," U. California Berkeley 1992, pp. 1-175. Churcher, S., et al., "The XC6200 FastMap TM Processor Interface," Xilinx, Inc., Aug. 1995, pp. 1-8.

Cowie, Beth, Xilinx Application Note, "High Performance, Low Area, Interpolator Design for the XC6200," XAPP 081, May 7, 1997 (Version 1.0), pp. 1-10.

Duncan, Ann, Xilinx Application Note, "A32x16 Reconfigurable Correlator for the XC6200," XAPP 084, Jul. 25, 1997 (Version 1.0), pp. 1-14.

Ebeling, C., et al., "RaPiD—Reconfigurable Pipelined Datapath," Dept. of Computer Science and Engineering, U. Washington, 1996, pp. 126-135.

Epstein, D., "IBM Extends DSP Performance with Mfast—Powerful Chip Uses Mesh Architecture to Accelerate Graphics, Video," 1995 MicroDesign Resources, vol. 9, No. 16, Dec. 4, 1995, pp. 231-236. Fawcett, B., "New SRAM-Based FPGA Architectures Address New Applications," Xilinx, Inc. San Jose, CA, Nov. 1995, pp. 231-236. Goslin, G., Wewgard, D., Xilinx Application Note, "16-Tap, 8-Bit FIR Elter Application Coulds" New 21, 1994, pp. 16-Tap, 8-Bit FIR

Gosin, G; Newgard, D; Atlinx Application Note; 16-1ap, 8-Bit FIR Filter Applications Guide," Nov. 21, 1994, pp. 1-5.

Iwanczuk, Roman, Xilinx Application Note, "Using the XC4000 RAM Capability," XAPP 031.000, 1994, pp. 8-127 through 8-138.

Knapp, Steven, "Using Programmable Logic to Accelerate DSP Functions," Xilinx, Inc., 1995, pp. 1-8.

New, Bernie, Xilinx Application Note, "Accelerating Loadable Counters in SC4000," XAPP 023.001, 1994, pp. 8-82 through 8-85. New, Bernie, Xilinx Application Note, "Boundary Scan Emulator for XC3000," XAPP 007.001, 1994, pp. 8-53 through 8-59.

New, Bernie, Xilinx Application Note, "Ultra-Fast Synchronous Counters," XAPP 014.001, 1994, pp. 8-78 through 8-81.

New, Bernie, Xilinx Application Note, "Using the Dedicated Carry Logic in XC4000," XAPP 013.001, 1994, pp. 8-105 through 8-115. New, Bernie, Xilinx Application Note, "Complex Digital Waveform Generator," XAPP 008.002, 1994, pp. 8-163 through 8-164.

New, Bernie, Xilinx Application Note, "Bus-Structured Serial Input-Output Device," XAPP 010.001, 1994, pp. 8-181 through 8-182. Ridgeway, David, Xilinx Application Note, "Designing Complex 2-Dimensional Convolution Filters," XAPP 037.000, 1994, pp. 8-175 through 8-177.

Rowson, J., et al., "Second-generation compilers optimize semicustom circuits," Electronic Design, Feb. 19, 1987, pp. 92-96. Schewel, J., "A Hardware/Software Co-Design System using Configurable Computing Technology," Virtual Computer Corporation, Reseda, CA, IEEE 1998, pp. 620-625.

Segers, Dennis, Xilinx Memorandum, "MIKE—Product Description and MRD," Jun. 8, 1994, pp. 1-29.

Texas Instruments, "TM\$320C8x System—Level Synopsis," Sep. 1995, 75 pages.

Texas Instruments, "TMS320C80 Digital Signal Processor," Data Sheet, Digital Signal Processing Solutions 1997, 171 pages.

Texas Instruments, "TMS320C80 (MVP) Parallel Processor," User's Guide, Digital Signal Processing Products 1995, 73 pages.

Trainor, D.W., et al., "Implementation of the 2D DCT Using a Xilinx XC6264 FPGA," 1997, IEEE Workshop of Signal Processing Systems SiPS 97, pp. 541-550.

#### OTHER PUBLICATIONS

Trimberger, S, (Ed.) et al., "Field-Programmable Gate Array Technology," 1994, Kluwer Academic Press, pp. 1-258 (and the Title Page, Table of Contents, and Preface) [274 pages total].

Trimberger, S., "A Reprogrammable Gate Array and Applications," IEEE 1993, Proceedings of the IEEE, vol. 81, No. 7, Jul. 1993, pp. 1030-1041.

Trimberger, S., et al., "A Time-Multiplexed FPGA," Xilinx, Inc., 1997 IEEE, pp. 22-28

Ujvari, Dan, Xilinx Application Note, "Digital Mixer in an XC7272,"

XAPP 035.002, 1994, p. 1. Veendrick, H., et al., "A 1.5 GiPS video signal processor (VSP)," Philips Research Laboratories, The Netherlands, IEEE 1994 Custom Integrated Circuits Conference, pp. 95-98.

Wilkie, Bill, Xilinx Application Note, "Interfacing XC6200 to Microprocessors (TMS320C50 Example)," XAPP 064, Oct. 9, 1996 (Version 1.1), pp. 1-9.

Wilkie, Bill, Xilinx Application Note, "Interfacing XC6200 to Microprocessors (MC68020 Example)," XAPP 063, Oct. 9, 1996 (Version 1.1), pp. 1-8.

XCELL, Issue 18, Third Quarter 1995, "Introducing three new FPGA Families!"; "Introducing the XC6200 FPGA Architecture: The First FPGA Architecture Optimized for Coprocessing in Embedded System Applications," 40 pages.

Xilinx Application Note, Advanced Product Specification, "XC6200 Field Programmable Gate Arrays," Jun. 1, 1996 (Version 1.0), pp. 4-253-4-286.

Xilinx Application Note, "A Fast Constant Coefficient Multiplier for the XC6200," XAPP 082, Aug. 24, 1997 (Version 1.0), pp. 1-5.

Xilinx Technical Data, "XC5200 Logic Cell Array Family," Preliminary (v1.0), Apr. 1995, pp. 1-43.

Xilinx Data Book, "The Programmable Logic Data Book," 1996, 909 pages.

Xilinx. Series 6000 User's Guide, Jun. 26, 1997, 223 pages.

Yeung, K., (Thesis) "A Data-Driven Multiprocessor Architecture for High Throughput Digital Signal Processing," Electronics Research Laboratory, U. California Berkeley, Jul. 10, 1995, pp. 1-153

Yeung, L., et al., "A 2.4GOPS Data-Driven Reconfigurable Multiprocessor IC for DSP," Dept. of EECS, U. California Berkeley, 1995 IEEE International Solid State Circuits Conference, pp. 108-110.

ZILOG Preliminary Product Specification, "Z86C95 CMOS Z8 Digital Signal Processor," 1992, pp. 1-82.

ZILOG Preliminary Product Specification, "Z89120 Z89920 (ROMless) 16-Bit Mixed Signal Processor," 1992, pp. 1-82. Defendants' Invalidity Contentions in *PACT XPP Technologies, AG*

v. XILINX, Inc., et al., (E.D. Texas Dec. 28, 2007) (No. 2:07cv563), including Exhibits A through K in separate PDF files.

Microsoft Press Computer Dictionary, Third Edition, Redmond, WA, 1997, 3 pages.

Microsoft Press Computer Dictionary, Second Edition, Redmond, WA, 1994, 3 pages.

A Dictionary of Computing, Fourth Edition, Oxford University Press, 1997, 4 pages.

Communications Standard Dictionary, Third Edition, Martin Weik (Ed.), Chapman & Hall, 1996, 3 pages.

Dictionary of Communications Technology, Terms Definitions and Abbreviations, Second Edition, Gilbert Held (Ed.), John Wiley & Sons, England, 1995, 5 pages

The Random House College Dictionary, Revised Edition, Random House, Inc., 1984, 14 pages

The Random House College Dictionary, Revised Edition, Random House, Inc., 1984, 7 pages.

Random House Webster's College Dictionary with CD-ROM, Random House, 2001, 7 pages.

Random House Webster's College Dictionary with CD-ROM, Random House, 2001, 4 pages.

Random House Personal Computer Dictionary, Second Edition, Philip E. Margolis (Ed.), Random House, New York, 1996, 5 pages. The IEEE Standard Dictionary of Electrical and Electronics Terms, Sixth Edition, 1996, 36 pages.

The IEEE Standard Dictionary of Electrical and Electronics Terms, Sixth Edition, 1996, 8 pages.

McGraw-Hill Electronics Dictionary, Sixth Edition, Neil Sclater et al. (Ed.), McGraw-Hill, 1997, 3 pages

Modern Dictionary of Electronics, Sixth Edition, Rudolf Graf (Ed.), Newnes (Butterwoth-Heinemann), 1997, 5 pages

The American Heritage Dictionary, Fourth Edition, Dell (Houghton-Mifflin), 2001, 5 pages.

The American Heritage Dictionary, Second College Edition, Houghton Mifflin, 1982, 23 pages.

The American Heritage Dictionary, Second College Edition. Houghton Mifflin, 1982, 8 pages.

The American Heritage Dictionary, Third Edition, Dell Publishing (Bantam Doubleday Dell Publishing Group, Inc.), 1994, 4 pages.

The American Heritage Dictionary, Fourth Edition, Dell/Houghton Mifflin 2001, 5 pages.

Webster's New Collegiate Dictionary, Merriam Co., 1981, 5 pages. Webster's New Collegiate Dictionary, Merriam Co., 1981, 4 pages. The Oxford American Dictionary and Language Guide, Oxford University Press, 1999, 5 pages

The Oxford Duden German Dictionary, Edited by the Dudenredaktion and the German Section of the Oxford University Press, W. Scholze-Stuhenrecht et al. (Eds), Clarendon Press, Oxford, 1990, 7 pages

Oxford Dictionary of Computing, Oxford University Press, 2008, 4

Modern Dictionary of Electronics, Sixth Edition Revised and Updated, Rudolf F. Graf (Ed.), Butterworth-Heinemann, 1997, 7 pages

Modern Dictionary of Electronics, Sixth Edition Revised and Updated, Rudolf F. Graf (Ed.), Butterworth-Heinemann, 1997, 5 pages.

Garner's Modern American Usage, Bryan A. Garner (Ed.), Oxford University Press, 2003, 3 pages

The New Fowler's Modern English Usage, R.W. Burchfield (Ed.), Oxford University Press, 2000, 3 pages.

Wikipedia, the free encyclopedia, "Granularity," at http://en. wikipedia.org/wiki/Granularity, Jun. 18, 2010, 4 pages.

Wordsmyth, The Premier Educational Dictionary-Thesaurus, at http://www.wordsmyth.net, "communication," Jun. 18, 2010, 1 page. Yahoo! Education, "affect," at http://education.yaboo.com/reference/dictionary/entry/affect, Jun. 18, 2010, 2 pages.

mPulse Living Language, "high-level," macmillandictionary.com/dictionary/american/high-level, Jun. 18, 2010, 1 page.

MSN Encarta, "regroup," at http://encarta.msn.com/encnet/features/ dictionary/Dictionary/Results.aspx?lextype=3&search=regroup, Jun. 17, 2010, 2 pages.

MSN Encarta, "synchronize," at http://encarta.msn.com/encnet/features/dictionary/DictionaryResults.aspx?lextype=3

&search=synchronize, Jun. 17, 2010, 2 pages.

MSN Encarta, "pattern," at http://encarta.msn.com/encnet/features/ dictionary/DictionaryResults.aspx?lextype=3&search=pattern, Jun. 17, 2010, 2 pages.

MSN Encarta, "dimension," at http://encarta.msn.com/encnet/features/dictionary/DictionaryResutls.aspx?lextype=3

&search=dimension, Jun. 17, 2010, 2 pages.

MSN Encarta, "communication," at http://encarta.msn.com/encnet/  $features/dictionary/DictionaryResults.aspx?lextype{=}3$

&search=communication, Jun. 17, 2010, 2 pages.

MSN Encarta, "arrangement," at http://encarta.msn.com/encnet/features/dictionary/DictionaryResults.aspx?lextype=3

&search=arrangement, Jun. 17, 2010, 2 pages.

MSN Encarta, "vector," at http://encarta.msn.com/encnet/features/ dictionary/DictionaryResults.aspx?textype=3&search=vector, Jul. 30, 2010, 2 pages.

Dictionary.com, "address," at http://dictionary.reference.com/ browse/address, Jun. 18, 2010, 4 pages.

P.R. 4-3 Joint Claim Constructions Statement, PACT XPP Technologies, AG v. Xilinx, Inc. and Avnet, Inc. et al., E.D., Texas, 2:07-cv-00563-CE, Jul. 19, 2010, pp. 1-50.

#### OTHER PUBLICATIONS

Order Granting Joint Motion for Leave to File an Amended Joint Claim Construction and Prehearing Statement and Joint Motion to File an Amended Joint Claim Construction and Prehearing Statement Pursuant to Local Patent Rule 4-3, and Exhibit A: P.R. 4-3 Amended Joint Claim Constructions Statement, *PACTXPP Technologies, AGv. Xilinx, Inc. and Awnet, Inc. et al.*, E.D. Texas, 2:07-cv-00563-CE, Aug. 2, 2010, 72 pages.

P.R. 4-3 Amended Joint Claim Constructions Statement, *PACT XPP Technologies*, *AG* v. *Xilinx, Inc. and Avnet, Inc. et al.*, E.D. Texas, 2:07-cv-00563-CE, Aug. 3, 2010, pp. 1-65.

Exhibit A—P.R. 4-3 Amended Joint Claim Constructions Statement, *PACT XPP Technologies, AG v. Xilinx, Inc. and Avnet, Inc. et al.*, E.D., Texas, 2:07-cv-00563-CE, Aug. 2, 2010, pp. 1-66.

PACT's Opening Claim Construction Brief, *PACT XPP Technologies*, *AG* v. *Xilinx*, *Inc. and Avnet, Inc. et al.*, E.D. Texas, 2:07-cv-00563-CE, Nov. 1, 2010, pp. 1-55.

Declaration of Harry L. (Nick) Tredennick in Support of PACT's Claim Constructions, *PACTXPP Technologies, AG* v. *Xilinx, Inc. and Avnet Inc. et al.*, E.D. Texas, 2:07-cv-00563-CE, Nov. 1, 2010, pp. 1-87.

Transcript of Harry (Nick) L. Tredennick III, Ph.D., Oct. 11, 2010, vol. 1, Exhibit 16 of PACT's Opening Claim Construction Brief, *PACTXPP Technologies, AG* v. *Xilinx, Inc. and Avnet, Inc. et al.*, E.D. Texas, 2:07-cv-00563-CE, Nov. 1, 2010, pp. 1-3.