# INTEL CORPORATION v. PACT XPP SCHWEIZ AG

IPR2020-00541 Patent 9,075,605

Patent Owner's Presentation

PA

## Power Management involves "paradoxical goals"

#### 8. Processor Control

This section describes the OS runtime aspects of managing the processor's power consumption and other controls while the system is in the *working* state<sup>12</sup>. The major controls over the processors are:

- ?? Processor power states: C0, C1, C2, C3

- ?? Processor clock throttling

- ?? Cooling control

These controls are used in combination by the operating software to achieve the desired balance of the following, sometimes paradoxical, goals:

- ?? Performance

- ?? Power consumption and battery life

- ?? Thermal requirements

- ?? Noise level requirements

Because the goals interact with each other, the operating software needs to implement a policy as to when and where tradeoffs between the goals are to be made<sup>13</sup>. For example, the operating software would determine when the audible noise of the fan is undesirable and would trade off that requirement for lower thermal requirements, which can lead to lower processing performance. Each processor control is discussed in the following sections along with how the control interacts with the various goals.

Ex. 1020 (ACPI) at 213.

## The '605 Patent

PATENT OWNER'S DEMONSTRAT

.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

2. The method of claim 1 wherein: said clock frequency is determined in part by processor voltage.

Ex. 1003 (US 9,075,605) at 16:6-8.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

3. The method of claim 1 wherein: said clock frequency is determined in part by available power.

Ex. 1003 (US 9,075,605) at 16:9-11.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

4. The method of claim 1 wherein: said clock frequency is determined in part by a user setting.

Ex. 1003 (US 9,075,605) at 16:12-13.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

5. The method of claim 1 wherein: said clock frequency is determined in part by available power and a user setting.

Ex. 1003 (US 9,075,605) at 16:14-16.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

6. The method of claim 1 wherein:

said number of pending operations is determined at by the fill level of one or more buffers.

Ex. 1003 (US 9,075,605) at 16:17-19.

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

3. The method of claim 1 wherein: said clock frequency is determined in part by available power.

Ex. 1003 (US 9,075,605) at 16:8-11.

4. The method of claim 1 wherein: said clock frequency is determined in part by a user setting.

Ex. 1003 (US 9,075,605) at 16:12-13.

5. The method of claim 1 wherein: said clock frequency is determined in part by available power and a user setting.

Ex. 1003 (US 9,075,605) at 16:14-16.

# A POSITA would not be motivated to combine different embodiments of Nicol

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and the multiprocessor system subsequently reducing the clock

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

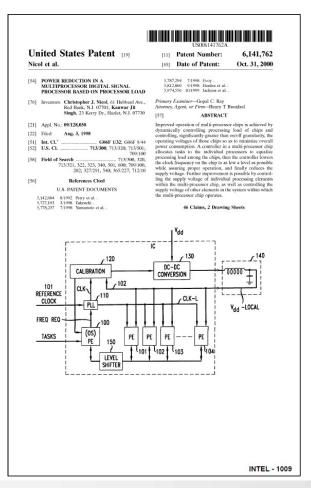

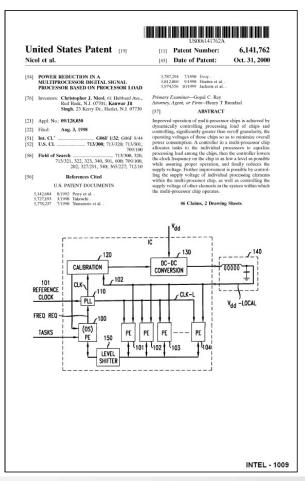

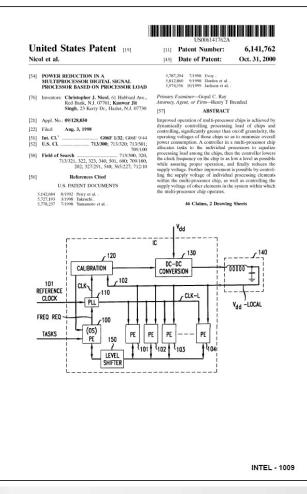

[54] POWER REDUCTION IN A

MULTIPROCESSOR DIGITAL SIGNAL

PROCESSOR BASED ON PROCESSOR LOAD

#### [57] ABSTRACT

Improved operation of multi-processor chips is achieved by dynamically controlling processing load of chips and controlling, significantly greater than on/off granularity, the operating voltages of those chips so as to minimize overall power consumption. A controller in a multi-processor chip allocates tasks to the individual processors to equalize processing load among the chips, then the controller lowers the clock frequency on the chip to as low a level as possible while assuring proper operation, and finally reduces the supply voltage. Further improvement is possible by controlling the supply voltage of individual processing elements within the multi-processor chip, as well as controlling the supply voltage of other elements in the system within which the multi-processor chip operates.

Ex. 1009 (Nicol) Title and Abstract

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

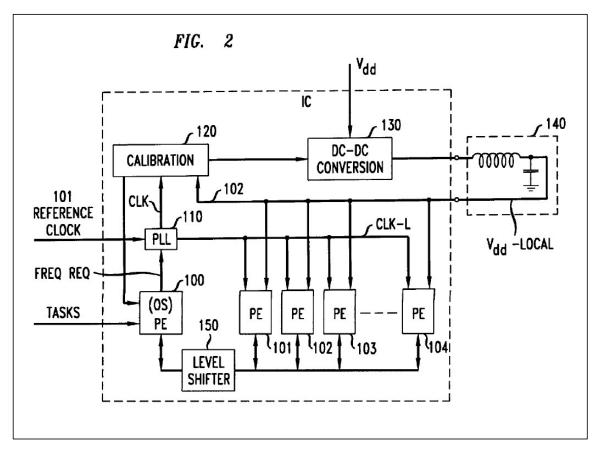

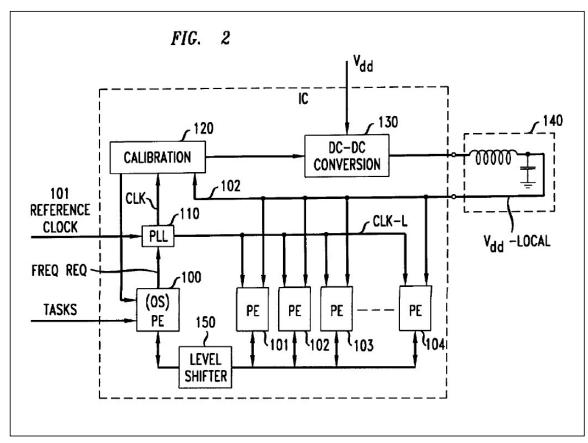

Ex. 1009 (Nicol) at Fig. 2.

In the FIG. 2 arrangement, in accordance with the principles disclosed herein, the applications that need to be processed are mapped to the N PEs under control of real time operating system (RTOS) executed on PE 100. If the number of instructions that need to be executed for each task is known and made available to the operating system, a scheduler within the operating system can use this information to determine the best way to allocate the tasks to the available processors in order to balance the computation. The intermediate goal, of course, is to maximize the parallelism and to evenly distribute the load presented to the FIG. 2 system among all of the PE's.

Ex. 1009 (Nicol) at 3:9-21.

Hence, the operating system of PE 100 needs to ascertain the required completion time, divide the collection of tasks as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and adjust the clock frequency to insure that the most heavily loaded PE carries out its assigned tasks within the required completion time. Once the frequency is thus determined, a minimum supply voltage can be determined.

Ex. 1009 (Nicol) at 3:66-4:6.

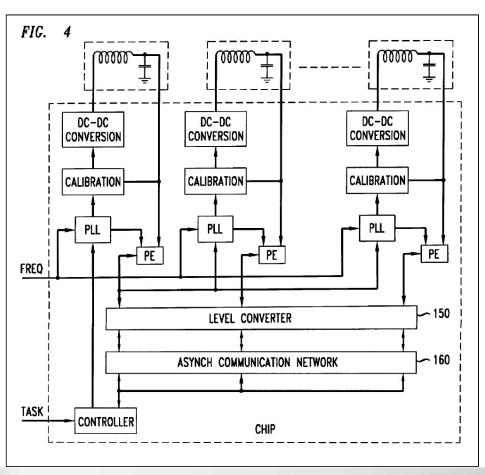

The notion of adjusting operating frequency to load and adjusting supply voltage to track the operating frequency can be extended to allow each PE to have its own supply voltage. The benefit of this approach for some applications becomes apparent when it is realized that the chip-wise voltage scaling is most effective when the load of the computation can be evenly distributed across all of the PEs. In some applications, however, one may encounter tasks that cannot be partitioned into concurrent evenly-loaded threads and, therefore, some PE within the multiprocessor would require a higher operating frequency and a higher operating voltage. This would require raising the frequency and voltage of the entire multiprocessor chip.

Ex. 1009 (Nicol) at 5:53-65.

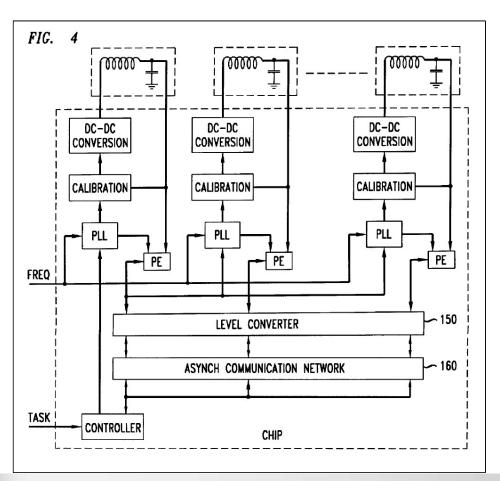

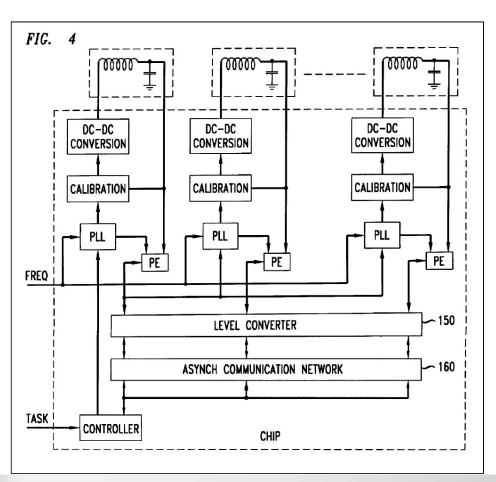

A separate power supply for each PE in a chip overcomes this limitation by allowing the operating system to independently program the lowest operating frequency and corresponding lowest supply voltage for each PE. The architecture of such an arrangement is shown in FIG. 4. Each PE in FIG. 4 needs an independent controller that performs the functions of PE 100 (except it does not divide tasks among PEs). As shown in FIG. 4, all of the controllers are embodied in a single controller 200, which may be just another processing element of the integrated circuit that contains the other processing elements. Each processing element also

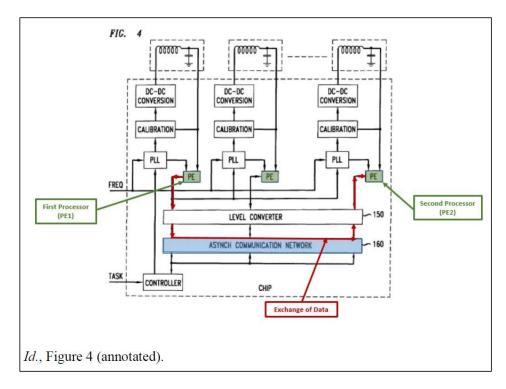

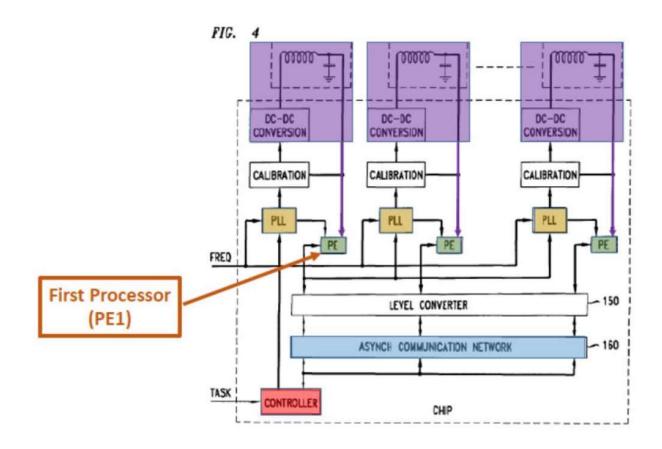

## Petitioner identifies ACN in Figure 4 for "sequentially processing data"

#### d) "and (b) being adapted for sequentially processing data, the method comprising:"

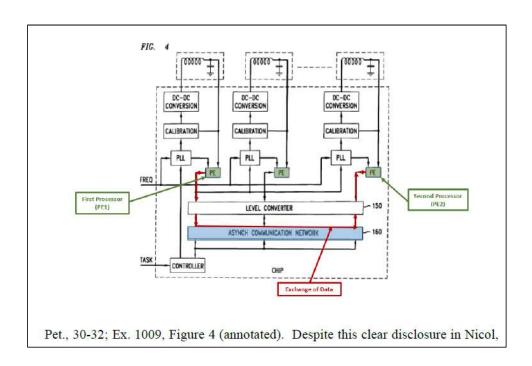

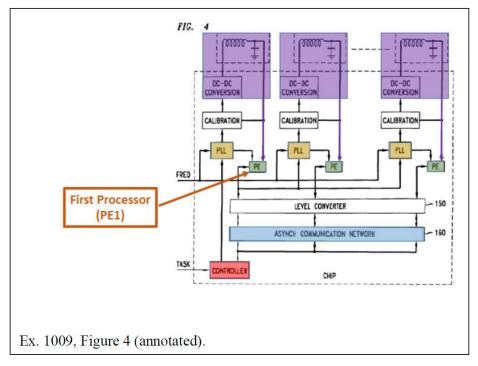

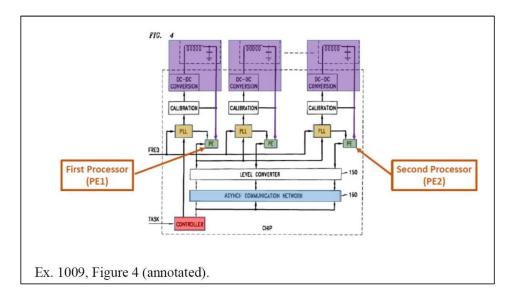

Nicol renders obvious this limitation under Patent Owner's construction of the term "sequentially processing data" to mean "passing results onto one or more other data processing units which are subsequently processing data." Ex. 1001 ¶147; Ex. 1016 (JCC) at 11 and 17. Specifically, Nicol teaches the need for "synchronizing the exchange of data among the PEs [green] of a multiprocessor chip" through an "asynch[ronous] communication network" 160 (highlighted in blue in Figure 4). Ex. 1009, 6:26–28, 6:14–18, Figure 4. For example, Nicol's annotated Figure 4 below depicts the passing of data (red) from PE1 (green) through the asynchronous communication network (blue) to PE2 (green) for further processing. Ex. 1001 ¶148; Ex. 1009, Figure 4.

Paper 2 (Petition) at 30-31.

Paper 2 (Petition) at 31.

## Petitioner identifies ACN in Figure 4 for "sequentially processing data"

#### "being adapted for sequentially processing data"

The Petition provides three independent reasons for why a POSITA would understand Nicol to disclose, or at least render obvious, "being adapted for sequentially processing data." See Pet., 30-35. While the POR mischaracterizes these independent grounds as being part of a "three step analysis" (POR, 20-21), no such effort is necessary: as explained in the Petition, Nicol discloses that data can be processed by one PE and then sequentially passed to another PE for further processing. Pet., 30-32. Nicol discloses this functionality via its PE-to-PE asynchronous communication network ("ACN") which passes data from one PE to another PE for sequential processing. See id.; Ex. 1009, 6:18-21 ("a synchronization schema must be implemented when there is a need to communicate data between PEs (or with other system elements) that operate at different frequencies."), 6:25-33 (discussing the need and the asynchronous communication network solution for "synchronizing the exchange of data among the PEs of a multiprocessor chip"); Ex. 1055, ¶16.

Paper 27 (Reply) at 9.

Paper 27 (Reply) at 8-9.

It may be noted that if the frequencies at which the individual PEs operate differ from one another and from other elements within the system where the multiprocessor chip is employed, there is an issue of synchronization that must be addressed. That is, a synchronization schema must be implemented when there is a need to communicate data between PEs (or with other system elements) that operate at different frequencies. It is possible to arrange the frequencies so that the collection of tasks that are assigned to the multiprocessor is completed at a predetermined time. In such a case, the synchronization problem of the multiprocessor vis-a-vis other elements within the system where the multiprocessor is employed is minimized. However, that leaves the issue of synchronizing the exchange of data among the PEs of a multiprocessor chip.

To effect such synchronization, each PE within the FIG. 4 arrangement is connection to an arrangement comprising elements 150 and 160. Level converter 150 converts the variable voltage swings of the PEs to a fixed level swing, and network 160 resolves the issue of different clock domains.

Ex. 1009 (Nicol) at 6:14-33.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

11

#### Petitioner relies on methodology of Figure 2 for setting clock frequency

e) "the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;"

Nicol discloses this claim element. Ex. 1001 ¶161. Nicol explains that the controller (red) in its multiprocessor system sets a clock frequency to a minimum according to a number of pending operations (instructions) of each of the PEs of the

\* \* \* \* \*

Indeed, Nicol explains that the controller "allocates tasks to the individual processors [PEs, including PE1] to equalize processing load among the [PEs, including PE1], then the controller *lowers the clock frequency* on the chip to *as low a level as possible* while assuring proper operation, and finally reduces the supply voltage." Ex. 1009, 2:23–27. Nicol further explains that the controller takes into account the number of pending operations (instructions) of each PE—including of PE1 ("first processor")—in its determination of processing load and task allocation. Ex. 1009, 3:13–18 ("If *the number of instructions* that need to be executed for each task is known and made available to the operating system, a scheduler within the operating system can use this information to determine the best way to allocate the

Paper 2 (Petition) at 36.

Paper 2 (Petition) at 35-36.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

#### Petitioner relies on methodology of Figure 2 for setting clock frequency

f) "the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor;"

Nicol discloses this element. Ex. 1001 ¶173. As discussed above in Section X.A (Overview of Nicol) and in the preceding section XI.A.2.e, the controller in Nicol's multiprocessor system adjusts the clock frequency of the system according to a number of pending operations of each of the PEs—including the number of pending operations of PE2 ("second processor")—identified in Figure 4 (annotated) below. *Id.*; Ex. 1009, 2:23–27 (discussing allocating tasks to the PEs and setting an appropriate clock frequency for task execution) and 3:13–18 (discussing using "*the number of instructions* that need to be executed for each task" for task allocation).

\* \* \* \* \*

Notably, the controller takes into account the number of pending instructions for each PE—including PE1 ("first processor") and PE2 ("second processor")—because it sets the clock frequency based on identifying the processing requirement of "the most heavily loaded PE." Ex. 1001, ¶176; Ex. 1009, 3:66–4:5 (explaining that the operating system "needs to ascertain the required completion time [of the tasks], divide the collection of tasks as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and *adjust the clock frequency* [common to all PEs] to insure that *the most heavily loaded PE* carries out its assigned task within the required completion time.").

Paper 2 (Petition) at 40.

Paper 2 (Petition) at 39-40.

#### Nicol's controllers

#### Figure 2 controller PE 100

Figure 4 controllers PE 100 and PE 200

Hence, the operating system of PE 100 needs to ascertain the required completion time, divide the collection of tasks as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and adjust the clock frequency to insure that the most heavily loaded PE carries out its assigned tasks within the required completion time. Once the frequency is thus determined, a minimum supply voltage can be determined.

Ex. 1009 (Nicol) at 3:66-4:6.

ture of such an arrangement is shown in FIG. 4. Each PE in FIG. 4 needs an independent controller that performs the functions of PE 100 (except it does not divide tasks among PEs). As shown in FIG. 4, all of the controllers are embodied in a single controller 200, which may be just another processing element of the integrated circuit that contains the other processing elements. Each processing element also requires a calibration circuit like circuit 120, and a voltage converter circuit like circuits 130 and 140. It also has a PE 200 that assigns the tasks given to the multi-processor chip of FIG. 4 among the PEs.

Ex. 1009 (Nicol) at 6:3-13.

# A POSITA would not be motivated to combine Nicol and Kling

[54] POWER REDUCTION IN A

MULTIPROCESSOR DIGITAL SIGNAL

PROCESSOR BASED ON PROCESSOR LOAD

#### [57] ABSTRACT

Improved operation of multi-processor chips is achieved by dynamically controlling processing load of chips and controlling, significantly greater than on/off granularity, the operating voltages of those chips so as to minimize overall power consumption. A controller in a multi-processor chip allocates tasks to the individual processors to equalize processing load among the chips, then the controller lowers the clock frequency on the chip to as low a level as possible while assuring proper operation, and finally reduces the supply voltage. Further improvement is possible by controlling the supply voltage of individual processing elements within the multi-processor chip, as well as controlling the supply voltage of other elements in the system within which the multi-processor chip operates.

Ex. 1009 (Nicol), Title and Abstract.

Ex. 1009 (Nicol) at Fig. 2.

In the FIG. 2 arrangement, in accordance with the principles disclosed herein, the applications that need to be processed are mapped to the N PEs under control of real time operating system (RTOS) executed on PE 100. If the number of instructions that need to be executed for each task is known and made available to the operating system, a scheduler within the operating system can use this information to determine the best way to allocate the tasks to the available processors in order to balance the computation. The intermediate goal, of course, is to maximize the parallelism and to evenly distribute the load presented to the FIG. 2 system among all of the PE's.

Ex. 1009 (Nicol) at 3:9-21.

Hence, the operating system of PE 100 needs to ascertain the required completion time, divide the collection of tasks as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and adjust the clock frequency to insure that the most heavily loaded PE carries out its assigned tasks within the required completion time. Once the frequency is thus determined, a minimum supply voltage can be determined.

Ex. 1009 (Nicol) at 3:66-4:6.

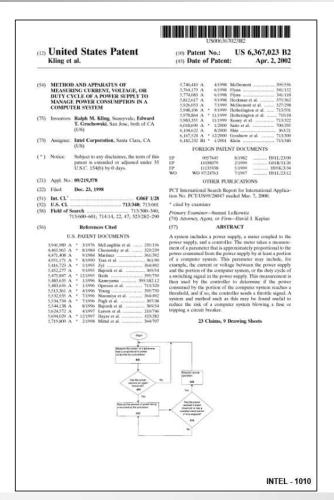

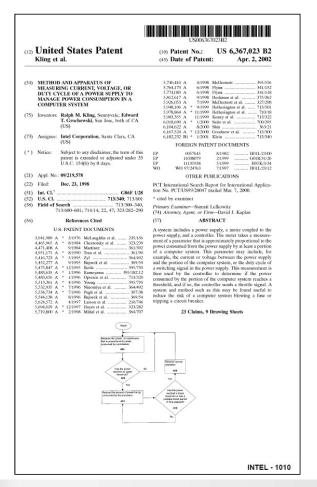

(54) METHOD AND APPARATUS OF

MEASURING CURRENT, VOLTAGE, OR

DUTY CYCLE OF A POWER SUPPLY TO

MANAGE POWER CONSUMPTION IN A

COMPUTER SYSTEM

#### (57) ABSTRACT

A system includes a power supply, a meter coupled to the power supply, and a controller. The meter takes a measurement of a parameter that is approximately proportional to the power consumed from the power supply by at least a portion of a computer system. This parameter may include, for example, the current or voltage between the power supply and the portion of the computer system, or the duty cycle of a switching signal in the power supply. This measurement is then used by the controller to determine if the power consumed by the portion of the computer system reaches a threshold, and if so, the controller sends a throttle signal. A system and method such as this may be found useful to reduce the risk of a computer system blowing a fuse or tripping a circuit breaker.

Ex. 1010 (Kling), Title and Abstract.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

\_ 4

#### US 6,367,023 B2

#### METHOD AND APPARATUS OF METHOD AND APPARATUS OF MEASURING CURRENT, VOLTAGE, OR DUTY CYCLE OF A POWER SUPPLY TO MANAGE POWER CONSUMPTION IN A COMPUTER SYSTEM

The present invention relates to computer systems and more particularly to limiting the power consumed in a computer system by throttling the power consumed by an integrated circuit in response to a high power condition.

#### BACKGROUND

Computer systems, from small handheld electronic devices to medium-sized mobile and desktop systems to large servers and workstations, are becoming increasingly 15 pervasive in our society. Computer systems typically include one or more processors. A processor manipulates and controls the flow of data in a computer by executing instructions. To provide more powerful computer systems for consumers, processor designers surive to continually 20 increase the operating speed of the processor. Unfortunately, more than the processor tends to increase as well. Historically, the power consumed by the processor has been limited by two factors. First, as power consumed from the consumption increases, the processor tends. 25 Computer systems, from small handheld electronic Second, as power consumption increases, the battery life of mobile computer systems decreases, leading to less attrac-tive systems for consumers.

Processor and computer system designers have developed.

rincessor alto compiler system escapes in few ever-open minerous methods to deal with these issues. For example, processor designers implement specialized circuit design techniques that reduce power consumption. In addition, modern computer systems are designed to shut down por-tions of the system that are not needed during a particular including the control of the control help extend battery life.

To address the thermal issue, elaborate thermal dissipa-tion systems are often affixed to the processor to help dissipate the heat from the processor to the ambient envi-ronment. Some processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the processor temperature exceeds a particular threshold, the processor is placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself

embodiment of the present invention;

- FIG. 1A is a switching regulator in a power supply of FIG.

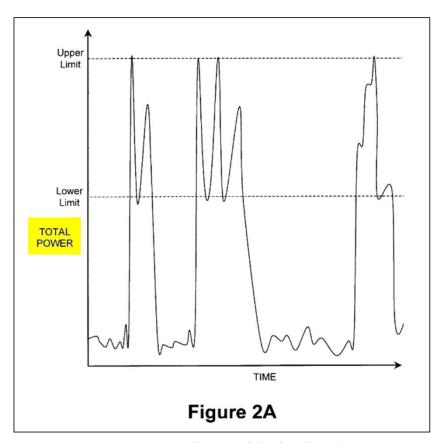

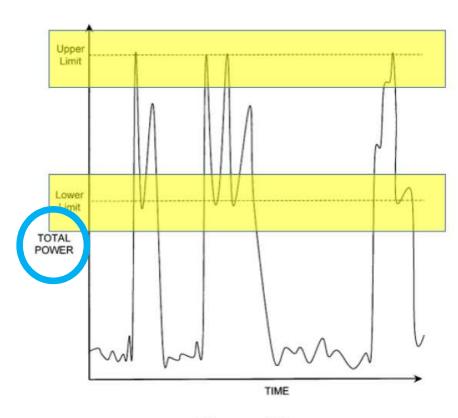

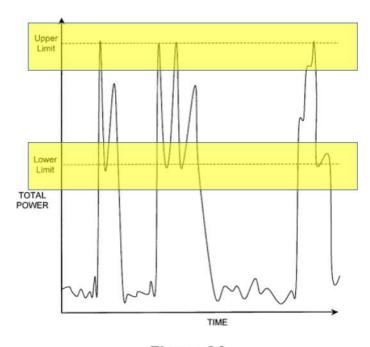

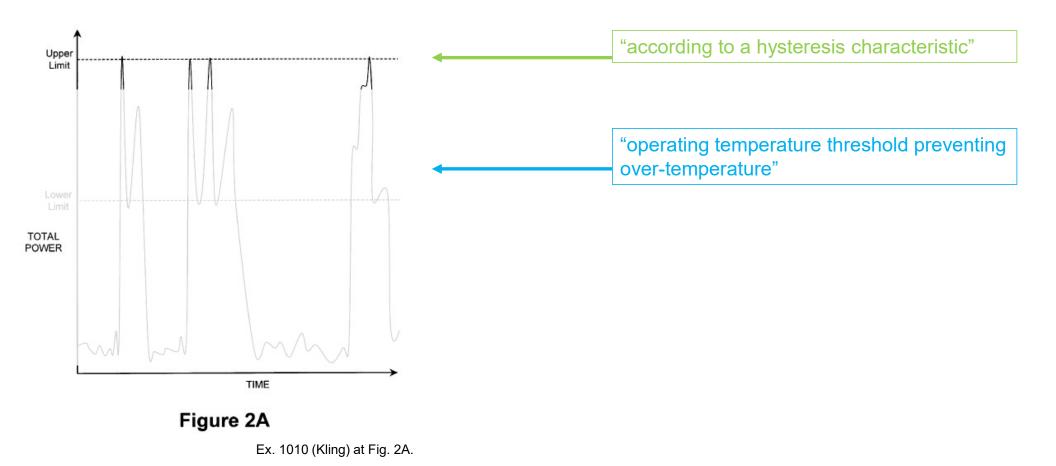

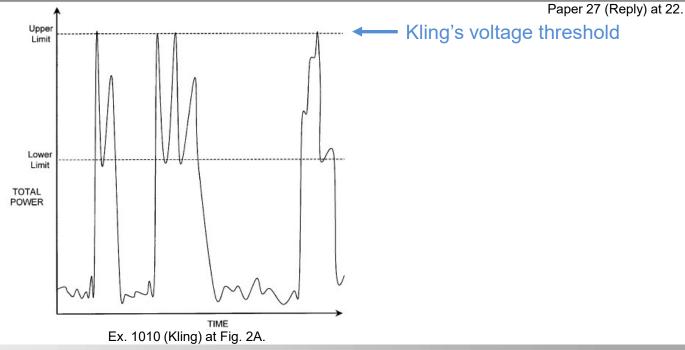

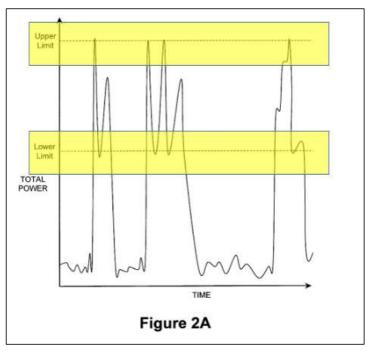

- FIG. 2A is a graph showing total power consumption versus time for an embodiment of the present invention; FIG. 2B is a graph showing total power consumption versus time for an alternate embodiment of the present

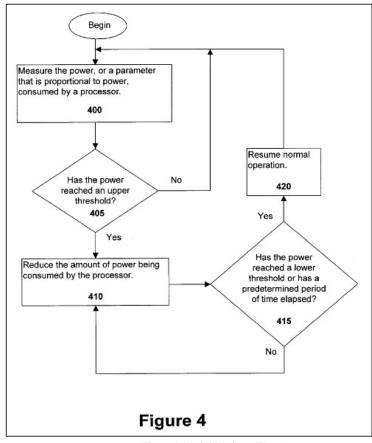

- FIG. 3 is a computer system including a processor formed in accordance with an embodiment of the present invention; FIG. 4 is a flow chart showing a method of reducing mption of a processor in accordance with an

- embodiment of the present invention; FIG. 5 is a flow chart showing the method of FIG. 4 in a first embodiment of the present invention;

- FIG. 6 is a flow chart showing the method of FIG. 4 in a second embodiment of the present invention; and FIG. 7 is a flow chart showing the method of FIG. 4 in a third embodiment of the present invention

#### DETAILED DESCRIPTION

Computer system power consumption is now rapidly approaching the point at which the power required to operate consumed by the processor has been limited by two factors.

First, as power consumption increases, the pattern life of the consumeration of the processor has been limited by two factors.

Second, as power consumption increases, the battery life of much botter, leading to thermal dissipation problems.

Second, as power consumption increases, the battery life of mobile comparer on symmetro in the consumeration of the processor of the symmetry of the consumeration of the processor of the symmetry of the symm circuit breaker that protects the power outlet can be tripped (or blown) during normal operation of the system.

In accordance with an embodiment of the present invention, the power consumed by at least a portion of a computer system is monitored by measuring a parameter that is approximately proportional to the consumed power, such as voltage, current, or the duty cycle of a switching such as vottage, current, or the duty eyele of a switching signal in a power supply. These measurements are provided to a power controller. The portion of the computer system that is monitored may include one or more processors of the computer system in addition to other integrated circuits (ICs) that consume a significant amount of power such as, for example, the bridge (or "chipset") or the video terminal.

Once the consumed power, as determined by the power controller, reaches a threshold, a throttle signal is sent to one as or more ICs of the computer system by the controller. In response to receiving this throttle signal, one or more of the ICs reduces its power consumption. For example, for one

SUMMARY OF THE INVENTION

A method and apparatus are described for managing the power consumed in expension of the present invention at taken of an electrical parameter that is approximately proportional to the power consumed by at least a portion of a computer system. This measurement is then of an electrical parameter that is approximately proportional to the power consumed by the portion of the computer system has reached a threshold.

Other features and advantages of the present invention of the computer system has reached a threshold.

\*\*\*NNYS\*\*

\*\*\* BRIEF DESCRIPTION OF THE DRAWINGS

The present invention is illustrated by way of example and not limitation in the accompanying figures in which like references indicate similar elements and in which:

18G, I as computer versetin formed in accordance with an embodiment of the present invention. The present invention is a multiprocessor computer system formed in a correlance with an embodiment of the present invention.

Primary bridge 110 is coupled to processors 100 and 101 via

INTEL - 1010

#### BACKGROUND

To address the thermal issue, elaborate thermal dissipation systems are often affixed to the processor to help dissipate the heat from the processor to the ambient environment. Some processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the processor is placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself by its own heat.

Ex. 1010 (Kling; US 6,367,023) at 1:38-46.

#### DETAILED DESCRIPTION

By directly monitoring power consumption, or a value proportional thereto, temperature measurement inaccuracies related to poor positioning of thermal sensors in proximity to the processor are avoided. In addition, the response time between detecting a high power condition and reducing the power consumption of the computer system is greatly improved over the use of thermal sensors to detect the high power condition. A more detailed description of embodiments of the present invention, including various configurations and implementations, is provided below.

Ex. 1010 (Kling) at 2:55-64; Paper 20 (POR) at 14, 56-57.

Ex. 1010 (Kling) at Fig. 4.

FIG. 4 is a flow chart showing a method of reducing power consumption of a processor in accordance with an 40 embodiment of the present invention. At step 400, the power, or a parameter that is proportional to power, consumed by the processor is measured. This power may be measured by a meter and the value provided in either digital or analog form to a power controller. For example, an ammeter may 45 provide a measurement of the current consumed by the processor to the power controller. Next, at step 405, the power controller determines if the power has reached an upper threshold. If the power has not reached the threshold, normal operation continues at step 400. If, however, the 50 power has reached the threshold, then, at step 410, the amount of power being consumed by the processor is reduced. This reduction may be in response to a throttle signal sent from the power controller to the processor.

Ex. 1010 (Kling) at 7:39-54.

Ex. 1010 (Kling) at Fig. 2A.

Once the consumed power, as determined by the power controller, reaches a threshold, a throttle signal is sent to one or more ICs of the computer system by the controller. In response to receiving this throttle signal, one or more of the ICs reduces its power consumption. For example, for one embodiment of the present invention, a processor of the computer system reduces its core frequency while maintaining a consistent bus frequency in response to receiving the throttle signal. For another embodiment, the processor stalls all or a portion of one or more pipelines, or issues no-ops to one or more pipelines, in response to receiving the throttle signal.

Ex. 1010 (Kling) at 2:42-55.

## Nicol and Kling take different approaches

United States Patent [19]

Nicol et al.

1] Patent Number:

6,141,762

[45] Date of Patent:

Oct. 31, 2000

Hence, the operating system of PE 100 needs to ascertain the required completion time, divide the collection of tasks

as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and adjust the clock frequency to insure that the most heavily loaded PE carries out its assigned tasks within the required completion time. Once the frequency is thus determined, a minimum supply voltage can be determined.

Ex. 1009 (Nicol) at 3:66-4:5; Paper 20 (POR) at 10, 44.

0000

(10) Patent No.: US 6,367,023 B2

Kling et al.

(12) United States Patent

(45) Date of Patent: Apr. 2, 2002

power supply, and a controller. The meter takes a measurement of a parameter that is approximately proportional to the power consumed from the power supply by at least a portion of a computer system. This parameter may include, for example, the current or voltage between the power supply and the portion of the computer system, or the duty cycle of a switching signal in the power supply. This measurement is then used by the controller to determine if the power consumed by the portion of the computer system reaches a threshold, and if so, the controller sends a throttle signal. A

Ex. 1010 (Kling), Abstract; Paper 20 (POR) at 45.

### Petitioner's motivation to combine Nicol and Kling

Third, Nicol is focused on minimizing power consumption and does not discuss over-temperature protection. Because over-temperature protection is critical for high-performance systems such as Nicol's multiprocessor system and SoC, a POSITA seeking to improve Nicol would have been motivated to consult Kling, which discusses well-known techniques of providing over-temperature protection, as well as additional improvements. Ex. 1001 ¶127. One such improvement

Paper 2 (Petition) at 24.

### Petitioner's motivation to combine Nicol and Kling

as well as additional improvements. Ex. 1001 ¶127. One such improvement described in Kling uses simple power measurement, such as measuring current, to detect excessive power consumption (when it is above a threshold) and use that information to "throttle" back processors to reduce power consumption. Ex. 1010, 5:38–59. A POSITA would have been motivated to implement this functionality in Nicol's system for over-temperature protection and, more generally, to detect excessive power consumption and reduce it, which is consistent with Nicol's objective of minimizing power consumption. Ex. 1009, 2:18–22; Ex. 1001 ¶129.

Paper 2 (Petition) at 24-25.

### Petitioner's motivation to combine Nicol and Kling

For example, the Petition explains that Nicol does not discuss over-temperature protection and thus "a POSITA seeking to improve Nicol would have been motivated to consult Kling, which discusses well-known techniques of providing over-temperature protection, as well as additional improvements." Pet., 24-25. In particular, a POSITA would have been motivated to use temperature measurements both to improve voltage scaling (taught in Nicol) and for over-temperature protection (discussed in Kling). Pet., 42-43; Ex. 1055, ¶7. Likewise, a POSITA would have been motivated to use power measurements both for over-temperature protection (detailed in Kling) and to detect excessive power consumption consistent with Nicol's objective of minimizing power consumption. Pet., 25; Ex. 1055, ¶7.

Paper 27 (Reply) at 2-3.

## Reasonable Expectation of Success

requirement refers to the likelihood of success in combining references to meet the limitations of the claimed invention. "[F]ailure to consider the appropriate scope of the ... patent's claimed invention in evaluating the reasonable expectation of success ... constitutes a legal error that [is] review[ed] without deference."

Allergan, 754 F.3d at 966 (emphasis added). Under the Board's uncontested construction, "claim

Intelligent Bio-Systems, Inc. v. Illumina Cambridge Ltd., 821 F.3d 1359, 1367 (Fed. Cir. 2016).

Paper 31 (Sur-Reply) at 11.

#### Prior Art Needs to be Enabled

To render a claim obvious, the prior art, taken as a whole, must enable a skilled artisan to make and use the claimed invention. See In re Kumar, 418 F.3d 1361, 1368 (Fed. Cir. 2005). In general, a prior art reference asserted under § 103 does not necessarily have to enable its own disclosure, i.e., be "self-enabling," to be relevant to the obviousness inquiry. See Symbol Techs., Inc. v. Opticon, Inc., 935 F.2d 1569, 1578 (Fed. Cir. 1991) ("While a reference must enable someone to practice the invention in order to anticipate under § 102(b), a non-enabling reference may qualify as prior art for the purpose of determining obviousness under § 103.");

But even though a non-enabling reference can play a role in an obviousness analysis, the evidence of record must still establish that a skilled artisan could have made the claimed invention. As the Sixth Circuit aptly explained:

Raytheon Techs. Corp. v. General Electric Co., 2021 WL 1432964, at \*4 (Fed. Cir. 2021); Paper 31 (Sur-Reply) at 14.

## Combining Nicol with Kling is difficult and could occupy an entire career

- (c) Incorporating Kling's upper power limit would not be a simple matter as Petitioner asserts

- 75. In my opinion, the idea that a POSITA would easily incorporate the invention of Kling into Nicol via simple add-on software is untrue. Balancing upper limits with Nicol's power management system would have been a complex task in which a POSITA would have to balance the power needs of individual processors to accomplish tasks within a designated time along with temperature consideration which is also an element of the claim. A POSITA may spend their entire career developing such a system that responds appropriately and efficiently to these variables.

Ex. 2024 (Mangione-Smith POR Decl.) at 59, ¶75.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

3

## U.S. Patent 9,075,605 B2 Independent Claim 1

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

#### **Claim Construction**

Data processing unit and/or data processing units . . . adapted for sequentially processing data '047 Patent, Claims 1-5, 8, 10, 15, 19, 22, 24 '605 Patent, Claim 1

Sequential data processors that pass results to one or more additional data processing units to perform additional computations

Ex. 1054 (Claim Construction Order) at 2.

#### **Nicol**

It may be noted that if the frequencies at which the individual PEs operate differ from one another and from other elements within the system where the multiprocessor chip is employed, there is an issue of synchronization that must be addressed. That is, a synchronization schema must be implemented when there is a need to communicate data between PEs (or with other system elements) that operate at different frequencies. It is possible to arrange the frequencies so that the collection of tasks that are assigned to the multiprocessor is completed at a predetermined time. In such a case, the synchronization problem of the multiprocessor vis-a-vis other elements within the system where the multiprocessor is employed is minimized. However, that leaves the issue of synchronizing the exchange of data among the PEs of a multiprocessor chip.

To effect such synchronization, each PE within the FIG. 4 arrangement is connection to an arrangement comprising elements 150 and 160. Level converter 150 converts the variable voltage swings of the PEs to a fixed level swing, and network 160 resolves the issue of different clock domains.

Ex. 1009 (Nicol) at 6:14-33.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

30

### Mangione-Smith Depo. Tr. (1/15/21)

```

A. Yeah, I don't recall if I said

that they were all communicating amongst

each other. The level shifter is there to

do voltage equalization between the PEs 101

through 104 and the PE 100. There is --

it's clear to me from the written

description that the application for

figure 2 anticipates communications back to

the PE 100 from the various computation PEs.

```

Ex. 1052 (Mangione-Smith 1/15/21 Depo.) at 46:20-47:3.

```

In the case of communications

among the PEs, there is a whole world of

scheduling aspects, scheduling issues, that

would have to be addressed because one task

is now dependent upon another. None of

which are discussed in Nicol.

```

Ex. 1052 (Mangione-Smith 1/15/21 Depo.) at 47:15-20.

### Mangione-Smith Depo. Tr. (1/15/21)

```

A. Yeah. It's not clear to me that

figure 4 discloses direct communication

among the PEs. It may be intended to do

that. It does disclose -- direct

communication among PEs of that sort was

generally known. One of the interesting

things here is the differences in clock

speed, and the synchronizer would address

that.

```

Ex. 1052 (Mangione-Smith 1/15/21 Depo.) at 109:22-110:5.

```

10

So a person of ordinary skill

11

looking at figure 4 would understand --

well, figure 4 and the spec, would

12

13

understand that, you know, Nicol is

intending for the PEs to talk to one another

14

15

but that there might be additional sort of

changes required in order to completely

17

allow that; right?

18

I wouldn't --

19

Did I get that right?

20

Yeah, I wouldn't quite phrase it

21

that way. I think a person of ordinary

22

skill in the art would see that Nicol

23

anticipates that figure 4 could be used to

24

build a system where the PEs communicate and

envisions that as a possibility. I don't

know that it actually discloses that on its

2

own.

```

Ex. 1052 (Mangione-Smith 1/15/21 Depo.) at 110:10-111:2.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

### Petitioner has not Established the Disclosure of "Temperature Threshold" (Claim 1)

## U.S. Patent 9,075,605 B2 Independent Claim 1 ("temperature threshold")

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:7-16:5.

#### Petitioner relies on Kling for the "temperature threshold"

#### METHOD AND APPARATUS OF METHOD AND APPARATUS OF MEASURING CURRENT, VOLTAGE, OR DUTY CYCLE OF A POWER SUPPLY TO MANAGE POWER CONSUMPTION IN A COMPUTER SYSTEM

more particularly to limiting the power consumed in a computer system by throttling the power consumed by an integrated circuit in response to a high power condition.

#### BACKGROUND

Computer systems, from small handlead electronic decircus on mediumsocial mobile and decktop systems to large servers and workstations, are becoming increasingly pervasive in our society. Computer systems typically include one or more processor fastignates and controls the flowe of data in a computer by executing installed and content of the present inventions. To provide more powerful computer systems for consumers, processor designars strive to continued by the processor designars strive to continued by the processor special increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor factor of the previous provided to operate systems for consumers.

\*\*Computer Systems\*\* power consumption increases, the processor factors are increased by the processor has been limited by two factors. First, as power consumption increases, the processor factors are consumption increases, the processor factors are consumption increases, the processor factors are not not force that an one or more processor in the processor factors are consumption increases, the processor factors are not not force that are compared to the processor factors are consumption increases, the processor factors a Computer systems, from small handheld electronic

riocesso and complex system coagen's niew ever-coopen numerous methods to deal with these issues. For example, processor designers implement specialized circuit design techniques that reduce power consumption. In addition, modern computer systems are designed to shut down por-tions of the system that are not needed during a particular period of time. Both of these techniques conserve power and help extend battery life.

To address the thermal issue, elaborate thermal dissipa-tion systems are often affixed to the processor to help dissipate the heat from the processor to the ambient envi-ronment. Some processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the processor temperature exceeds a particular threshold, the processor is placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself

#### SUMMARY OF THE INVENTION

SUMMARY OF THE INVENTION

A method and apparatus are described for manging the power consumed in a computer system. In accordance with the power consumed in a computer system. In accordance with the power consumed of the present invention, a measurement is taken of an electrical parameter that is appreciately processor as the processor invention. This measurement is then used to determine if the power consumed by the portion of the computer system. In accordance with the processor invention. Other features and advantages of the present invention. Other features and advantages of the present invention will be apparent from the accompanying drawings and the detailed description that follows.

BRIEE DESCRIPTION OF THE DRAWINGS

embodiment of the present invention;

- FIG. 1A is a switching regulator in a power supply of FIG.

- FIG. 2A is a graph showing total power consumption versus time for an embodiment of the present invention; FIG. 2B is a graph showing total power consumption versus time for an alternate embodiment of the present

- FIG. 3 is a computer system including a processor formed FIG. 4 is a flow chart showing a method of reducing amption of a processor in accordance with an

- embodiment of the present invention; FIG. 5 is a flow chart showing the method of FIG. 4 in a

Second, a spower consumption increases, the battery life of mobile computer systems decreases, leading to less attractive systems for consumers.

Processor and computer system designers have developed of Processor and computer system designers have developed of the blown during normal operation of the system.

In accordance with an embodiment of the present invention, the power consumed by at least a portion of a computer system is monitored by measuring a parameter that is approximately proportional to the consumed power, such as voltage, current, or the duty cycle of a switching signal in a power supply. These measurements are provided to a power controller. The portion of the computer system that is monitored may include one or more processors of the computer system in addition to other integrated circuits (ICs) that consume a significant amount of power such as, for example, the bridge (or "chipset") or the video terminal.

Once the consumed power, as determined by the power controller, reaches a threshold, a throttle signal is sent to one as or more ICs of the computer system by the controller. In response to receiving this throttle signal, one or more of the ICs reduces its power consumption. For example, for one embodiment of the present invention, a processor of the computer system reduces its core frequency while maintain

BRIEF DESCRIPTION OF THE DRAWINGS

The present invention is illustrated by way of example and not limitation in the accompanying figures in which like references indicate similar elements and in which:

18G, I as computer versetin formed in accordance with an embodiment of the present invention. The present invention is a multiprocessor computer system formed in a correlance with an embodiment of the present invention.

Primary bridge 110 is coupled to processors 100 and 101 via

INTEL - 1010

#### BACKGROUND

To address the thermal issue, elaborate thermal dissipation systems are often affixed to the processor to help dissipate the heat from the processor to the ambient environment. Some processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the processor is placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself by its own heat.

Ex. 1010 (Kling) at 1:38-46.

#### DETAILED DESCRIPTION

By directly monitoring power consumption, or a value proportional thereto, temperature measurement inaccuracies related to poor positioning of thermal sensors in proximity to the processor are avoided. In addition, the response time between detecting a high power condition and reducing the power consumption of the computer system is greatly improved over the use of thermal sensors to detect the high power condition. A more detailed description of embodiments of the present invention, including various configurations and implementations, is provided below.

Ex. 1010 (Kling) at 2:55-64; Paper 20 (POR) at 14, 56-57.

### Petitioner relies on Kling for the "temperature threshold"

Kling explains that processing systems must be able to rapidly detect and mitigate over-temperature situations. Ex. 1010, 1:38–46 ("To address the thermal issue [in modern computer systems] . . . processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the processor is placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself by its own heat.").

Paper 2 (Petition) at 42.

### Petitioner has not Established the Disclosure of "Hysteresis" (Claim 1)

## U.S. Patent 9,075,605 B2 Independent Claim 1 ("hysteresis")

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:7-16:5.

### Petitioner's interpretation of "hysteresis"

value. Another example is the manner in which a thermostat utilizes the right amount of hysteresis to maintain the desired temperature. Too little hysteresis would result in constant switching between cycles, and too much would allow too large a temperature interval between cycles. 4. In an os-

Ex. 1053 (Wiley) at 355; Paper 27 (Reply) at 22.

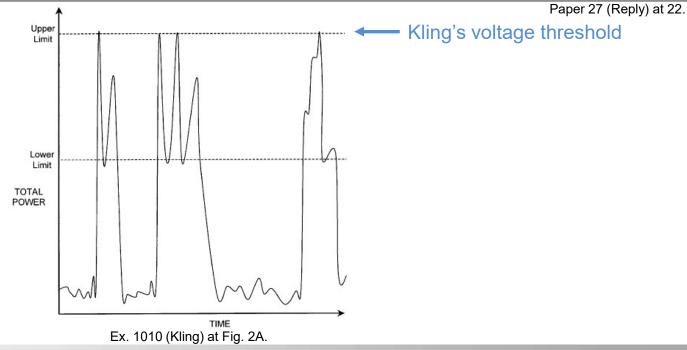

### Petitioner's argument on "hysteresis"

Ex. 1053 (Wiley), 355 ("[A] thermostat utilizes the right amount of hysteresis to maintain the desired temperature. Too little hysteresis would result in constant switching between cycles, and too much would allow too large a temperature interval between cycles.")). This admission is fatal to PO's strained position. Just like thermostat control and as taught in Kling, an over-temperature protection system requires the use of hysteresis to avoid constantly switching between normal operation mode (e.g., high frequency/voltage for maximum performance) and an over-temperature protection mode (e.g., reduced frequency/voltage to "cool off" an over-heating PE). Pet., 44-45; Ex. 1055, ¶37; Ex. 1010, 5:45-54; Ex. 1021, 471.

Paper 27 (Reply) at 22.

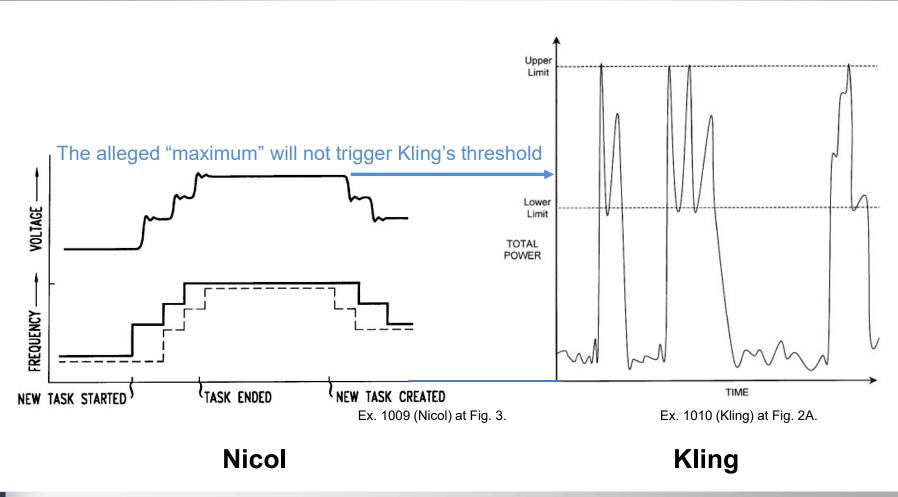

#### Petitioner points to Kling's power oscillation

old may be set to a predetermined value selected to provide hysteresis to reduce the occurrence of power oscillation between the upper and lower thresholds. This lower thresh-

Ex. 1010 (Kling) at 5:51-54; Paper 2 (Petition) at 44.

Kling also discusses the use of hysteresis to improve robustness and "reduce the occurrence of power oscillation," as would also have been well-known in the art.

Paper 2 (Petition) at 44.

Figure 2A

Paper 2 (Petition) at 45.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

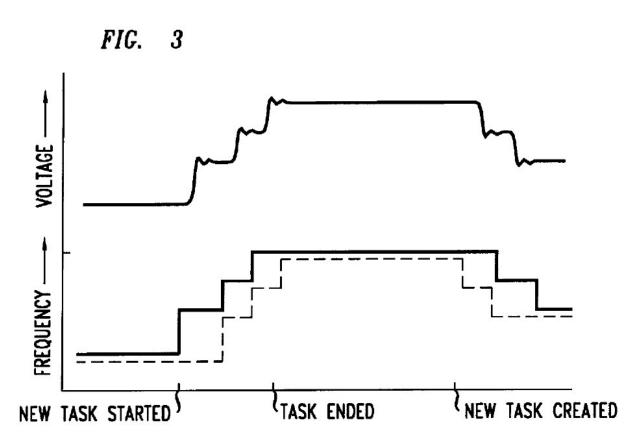

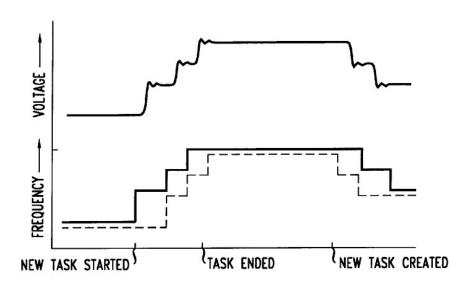

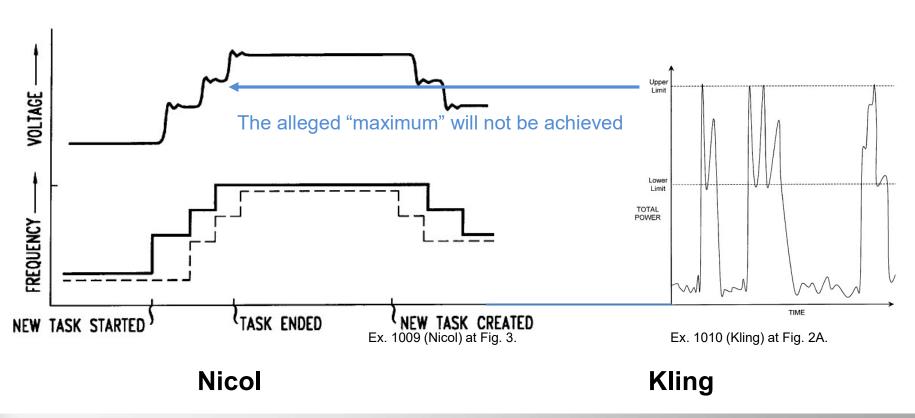

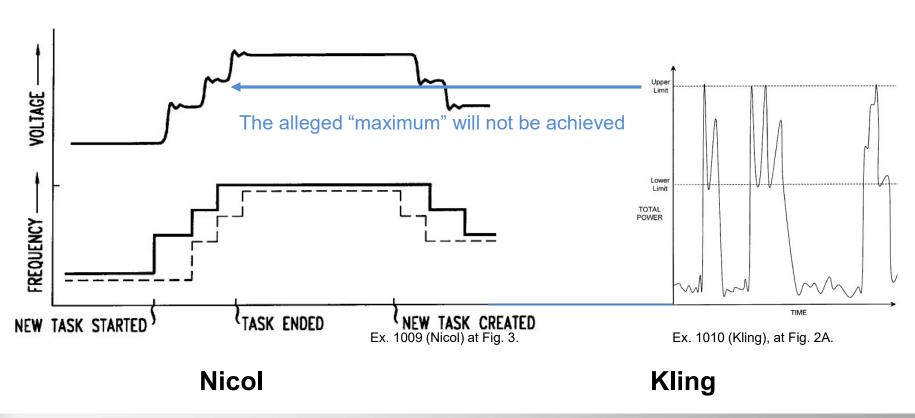

### Nicol does not have power oscillation

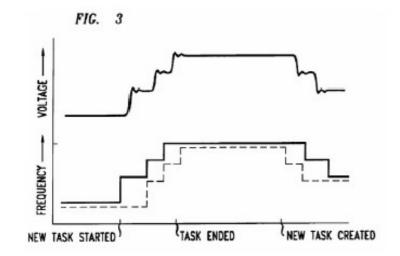

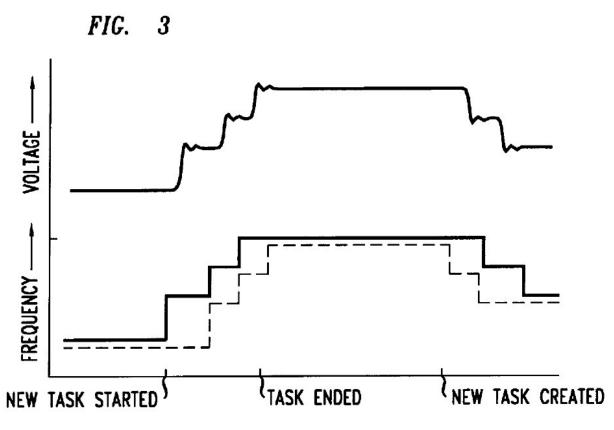

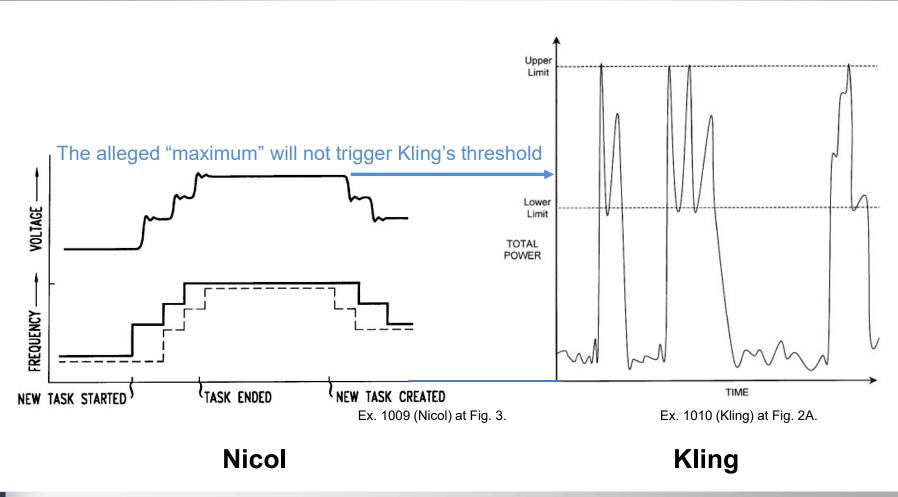

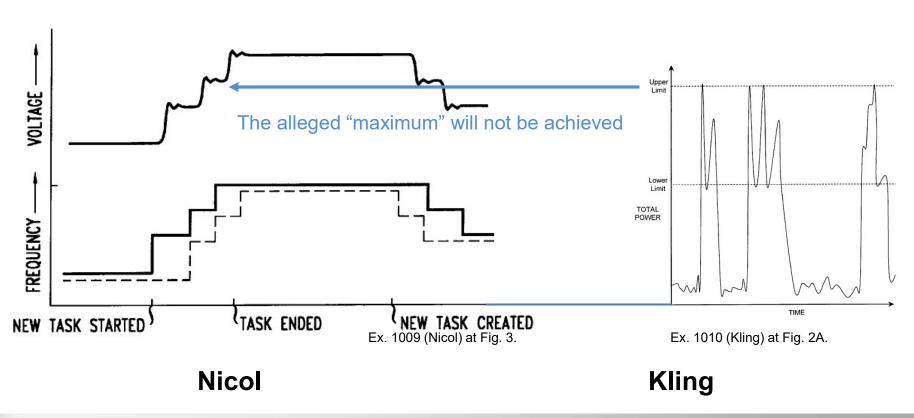

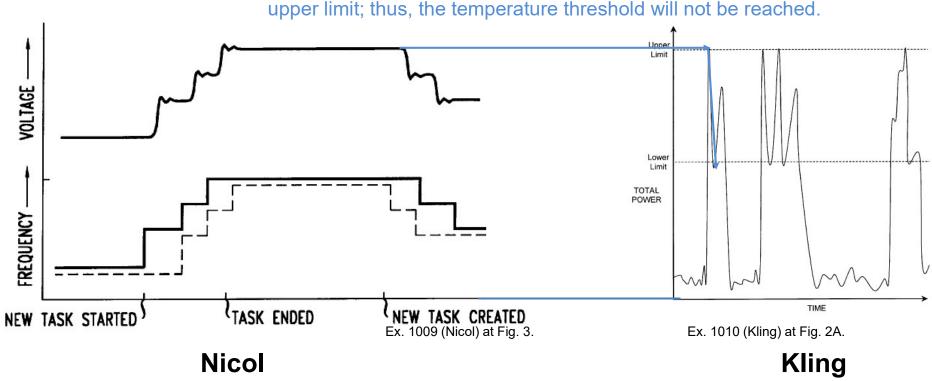

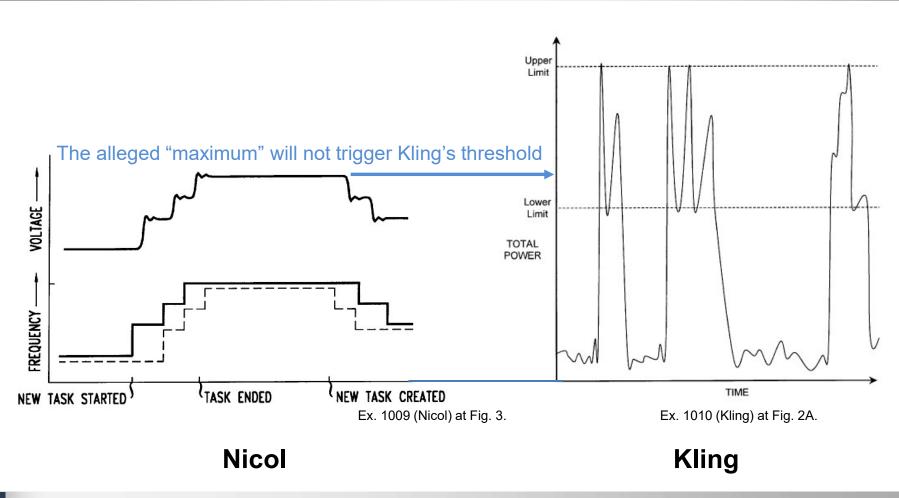

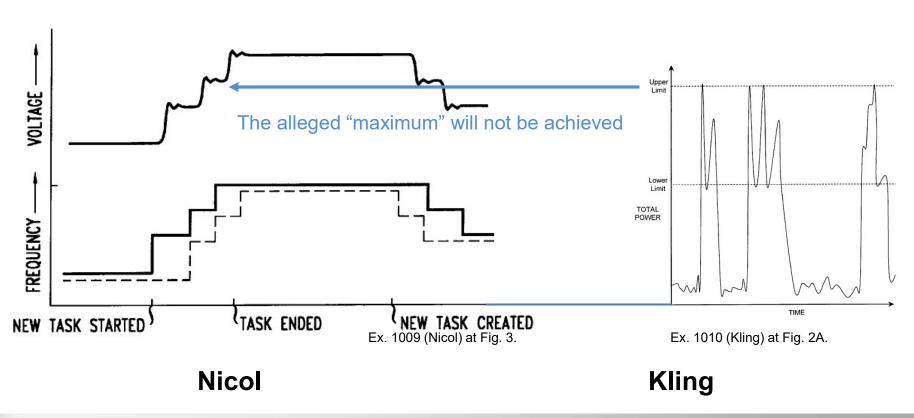

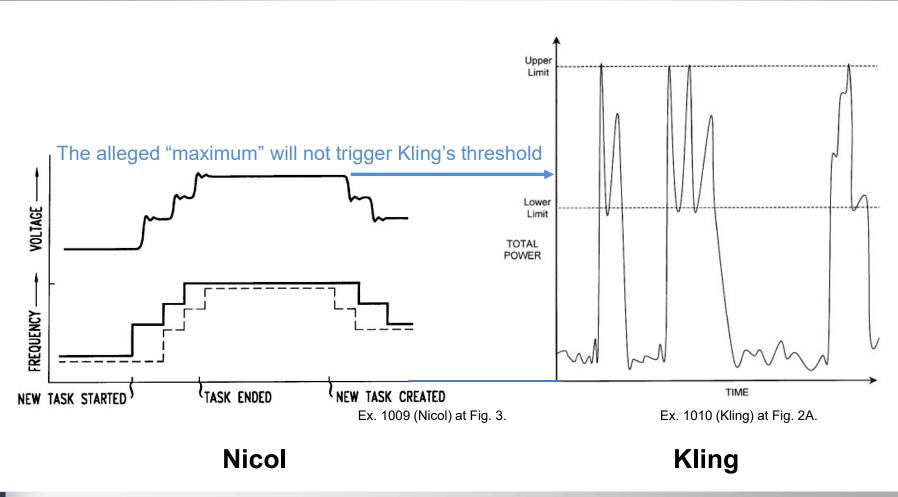

Ex. 1009 (Nicol) at Fig. 3; Paper 20 (POR) at 11, 41-42.

**PACT EX. 2028**

## Kennedy's "hysteresis" is about "noise rejection and oscillator circuits"

INTERNATIONAL JOURNAL OF CIRCUIT THEORY AND APPLICATIONS, VOL. 19, 471-515 (1991)

HYSTERESIS IN ELECTRONIC CIRCUITS: A CIRCUIT THEORIST'S PERSPECTIVE

Department of El

In this exposition we We show that the ju 'hysteretic' element of the static charac We examine the S type pulse oscillato illustrate the concer show how a clear u for 'hysteretic' circuits' The principal features of electronic hysteresis elements which endear them to design engineers are rapid switching between states, inherent noise immunity and memory of the input. Consequently, these elements have become indispensable building blocks in a variety of noise rejection and oscillator circuits.

#### 1. INTRODUCTION

In this paper we study the phenomenon whereby the driving point or transfer characteristic of an electronic circuit exhibits a 'loop'. The presence of such a 'loop' is commonly referred to as 'hysteresis' because the value of the output depends on both the present and past values of the input.

The principal features of electronic hysteresis elements which endear them to design engineers are rapid switching between states, inherent noise immunity and memory of the input. Consequently, these elements have become indispensable building blocks in a variety of noise rejection and oscillator circuits.

Traditionally, driving point and transfer hysteresis characteristics have been exploited in comparators, Schmitt triggers' and multivibrator circuits. They are used in noisy environments to guard against false triggers, in communication systems to convert slowly varying analogue signals to digital form and in nonlinear oscillators to produce relaxation wave forms. 2-4 More recently, they have been used to generate chaos<sup>3-5</sup> and in artificial neural networks-46 to model biological behaviours.

Despite its pervasive use, the loop hysteresis phenomenon is not widely understood. Consequently, models of it are often misleading; typical representations of the driving point (DP) and transfer characteristics (TC) of hysteretic elements consist of closed loops or disjoint line segments connected together by dashed lines and labelled with arrows, <sup>1,2,7,8</sup> quite unlike 'normal' DC characteristics (see Figure 1). In particular, the symbol commonly used in the integrated circuits literature to denote a Schmitt trigger is a stylized representation of a hysteresis loop in a transfer characteristic (see Figure 2). The loop consists of a flat top and bottom, joined together by two line segments. These joining lines are usually very steep, suggesting a region of high gain in the transfer characteristic. This begs the questions: what is the value of this gain? How do we measure it? Indeed, does it make sense to talk about a gain at all?'

In this work we hope to dispel some common misconceptions about the nature of hysteresis in electronic circuits. We will explain how it arises and, with an understanding of the mechanism, how to model it. We will show by example that resistive models of hysteresis which assume discontinuous characteristics and jumps are incorrect. Not only do they complicate the analysis unnecessarily at times, but they do not alays yield solutions. Further, we will show that it is necessary to augment these resistive models with parasitic energy storage elements in order to explain the mechanism for switching between states.

0098-9886/91/050471-45\$22.50 © 1991 by John Wiley & Sons, Ltd. Received 26 April 1990 Revised 17 December 1990

INTEL - 102

Ex. 1021 (Kennedy) at 471; Paper 20 (POR) at 43.

1021 (Kennedy, M. & Chua, L., *Hysteresis in Electronic Circuits: A Circuit Theorist's Perspective*, International Journal of Circuit Theory and Applications, Vol. 19, (1991)) at 471 (explaining that circuits with hysteresis characteristics were "indispensable" and commonly used "in noisy environments and to guard against false triggers"),.

Paper 20 (POR) at 43.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

#### Nicol uses an alternate method to prevent noise

It is noted that the frequency is gradually programmed into the system (as shown by the stepped changes in FIG. 3). This prevents excessive noise on the  $V_{dd}$ -local supply voltage and possible circuit failure. For example, if the system

Ex. 1009 (Nicol) at 5:29-31, Fig. 3; Paper 20 (POR) at 43.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

3

# Petitioner has not Established the Motivation to Combine for the Method Claim

### Claim 1(c)

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

#### Kling is about power threshold, not temperature threshold

#### METHOD AND APPARATUS OF METHOD AND APPARATUS OF MEASURING CURRENT, VOLTAGE, OR DUTY CYCLE OF A POWER SUPPLY TO MANAGE POWER CONSUMPTION IN A COMPUTER SYSTEM

more particularly to limiting the power consumed in a computer system by throttling the power consumed by an integrated circuit in response to a high power condition.

#### BACKGROUND

Computer systems, from small handlead electronic decircus on mediumsocial mobile and decktop systems to large servers and workstations, are becoming increasingly pervasive in our society. Computer systems typically include one or more processor fastignates and controls the flowe of data in a computer by executing installed and content of the present inventions. To provide more powerful computer systems for consumers, processor designars strive to continued by the processor designars strive to continued by the processor special increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor has been limited by two factors. First, as power consumption increases, the proves crossmend by the processor factor of the previous provided to operate systems for consumers.

\*\*Computer Systems\*\* power consumption increases, the processor factors are increased by the processor has been limited by two factors. First, as power consumption increases, the processor factors are consumption increases, the processor factors are consumption increases, the processor factors are not not force that an one or more processor in the processor factors are consumption increases, the processor factors are not not force that are compared to the processor factors are consumption increases, the processor factors a Computer systems, from small handheld electronic Second, as power consumption increases, the battery life of mobile computer systems decreases, leading to less attrac-tive systems for consumers.

Processor and computer system designers have developed.

rivocess and conjunct system escapes in twee averaging intermediate momentum methods to deal with these issues. For example, processor designers implement specialized circuit design techniques that reduce power consumption. In addition, modern computer systems are designed to shut down portions of the system that are not needed during a particular increase of the particular designed to the partic help extend battery life.

To address the thermal issue, elaborate thermal dissipa-tion systems are often affixed to the processor to help dissipate the heat from the processor to the ambient envi-ronment. Some processor packages include a thermal sensor to monitor the temperature of the processor. If the processor temperature exceeds a particular threshold, the pr placed into low power mode until it cools off. If these precautions are not taken, the processor may destroy itself

#### SUMMARY OF THE INVENTION

A method and apparatus are described for managing the A method and apparatus are described for managing the 20 power consumed in a computer system. In accordance with one embodament of the present invention, a measurement is taken of an electrical parameter that is approximately proportional to the power consumed by at least a portion of a computer system. This measurement is then used to detect-rising if the power consumed by the portion of the computer system. The properties of the computer system has reached a threshold.

Other features and advantages of the present invention will be apparent from the accompanying drawings and the detailed description that follows.

#### BRIEF DESCRIPTION OF THE DRAWINGS

embodiment of the present invention;

- FIG. 1A is a switching regulator in a power supply of FIG.

- FIG. 2A is a graph showing total power consumption versus time for an embodiment of the present invention; FIG. 2B is a graph showing total power consumption versus time for an alternate embodiment of the present

- FIG. 3 is a computer system including a processor formed FIG. 4 is a flow chart showing a method of reducing mption of a processor in accordance with an

- embodiment of the present invention; FIG. 5 is a flow chart showing the method of FIG. 4 in a

circuit breaker that protects the power outlet can be tripped (or blown) during normal operation of the system.

In accordance with an embodiment of the present invention, the power consumed by at least a portion of a computer system is monitored by measuring a parameter that is approximately proportional to the consumed power, such as voltage, current, or the duty cycle of a switching such as vottage, current, or the duty eyele of a switching signal in a power supply. These measurements are provided to a power controller. The portion of the computer system that is monitored may include one or more processors of the computer system in addition to other integrated circuits (ICs) that consume a significant amount of power such as, for example, the bridge (or "chipset") or the video terminal.

Once the consumed power, as determined by the power controller, reaches a threshold, a throttle signal is sent to one as or more ICs of the computer system by the controller. In response to receiving this throttle signal, one or more of the ICs reduces its power consumption. For example, for one embodiment of the present invention, a processor of the computer system reduces its core frequency while maintain ing a consistent bus frequency in response to receiving the throttle signal. For another embodiment, the processor stalls all or a portion of one or more pipelines, or issues no ops to one or more pipelines, in response to receiving the throttle

signal.

The state of the state BRIEF DESCRIPTION OF THE DRAWINGS

The present invention is illustrated by way of example and not limitation in the accompanying figures in which like references indicate similar elements and in which:

18G, I as computer versetin formed in accordance with an embodiment of the present invention. The present invention is a multiprocessor computer system formed in a correlance with an embodiment of the present invention.

Primary bridge 110 is coupled to processors 100 and 101 via

By directly monitoring power consumption, or a value proportional thereto, temperature measurement inaccuracies related to poor positioning of thermal sensors in proximity to the processor are avoided. In addition, the response time between detecting a high power condition and reducing the power consumption of the computer system is greatly improved over the use of thermal sensors to detect the high power condition. A more detailed description of embodiments of the present invention, including various configurations and implementations, is provided below.

Ex. 1010 (Kling) at 2:55-64; Paper 20 (POR) at 14, 56-57.

INTEL - 1010

### Claim 1(c) - hysteresis

Kling also discusses the use of hysteresis to improve robustness and "reduce

the occurrence of power oscillation," as would also have been well-known in the art.

Figure 2A

Paper 2 (Petition) at 44-45.

F

## Petitioner argues temperature threshold reached before power threshold

spots" that power measurements alone could miss. Ex. 1055, ¶10. This is because the same amount of power consumed by the system (e.g., a chip) may not be high enough to trigger a power measurement trip point, but still could cause a local temperature to rise to an unsafe level if most of the power is consumed by one small circuit of the chip, creating a dangerous "hot spot." *Id.*, ¶11.

Paper 27 (Reply) at 5.

#### Petitioner argues temperature threshold reached before power threshold

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

\_

### Method Claims Require More Than "Being Capable"

"While [the petitioner] was only required to identify a prior art reference that discloses an apparatus 'capable of' performing the recited functions to prove that the apparatus claims would have been obvious, more was required with respect to the method claims. Specifically, [the petitioner] needed to present evidence and argument that a person of ordinary skill would have been motivated to operate [the prior art] in a manner that satisfied the [claim] limitation."

ParkerVision, Inc. v. Qualcomm Incorporated, 903 F.3d 1354, 1363 (Fed. Cir. 2018).

### Method Claims Require More Than "Being Capable"

"[T]o show the obviousness of the <u>claimed method</u>, Petitioner <u>cannot merely show an apparatus</u> <u>capable of performing the method</u> would have been obvious but <u>must present</u> evidence and argument that a person of ordinary skill would have been <u>motivated to operate the prior art apparatus in a manner that satisfied the limitations of the challenged claims."</u>

United Industries Corporation et al v. Susan McKnight, Inc. et al., Paper 31 (Case IPR2017-01687, PTAB, Jan. 22, 2019) at 10, 27 (citing ParkerVision, Inc. v. Qualcomm Incorporated, 903 F.3d 1354 (Fed. Cir. 2018)).

# Petitioner Fails to Establish a Reasonable Expectation of Achieving What is Claimed

#### Claim 1

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

Ex. 1003 (US 9,075,605) at 15:6-20.

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 16:1-5.

### Nicol

Ex. 1009 (Nicol) at Fig. 3.

### Kling's voltage threshold

Pet., 45-46. Kling teaches reducing clock frequency when a voltage representing

the power consumed by a processor reaches a threshold. *Id.*; Ex. 1010, 2:31-51 ("the

ATENT OWNER'S DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

### Case 1: Nicol's voltage < Kling's voltage threshold

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

### Case 2: Nicol's voltage > Kling's voltage threshold

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

0

### Case 3: Nicol's voltage = Kling's voltage threshold

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

0

#### Kling's response time

By directly monitoring power consumption, or a value proportional thereto, temperature measurement inaccuracies related to poor positioning of thermal sensors in proximity to the processor are avoided. In addition, the response time between detecting a high power condition and reducing the power consumption of the computer system is greatly improved over the use of thermal sensors to detect the high power condition. A more detailed description of embodiments of the present invention, including various configurations and implementations, is provided below.

Ex. 1010 (Kling) at 2:55-64; Paper 20 (POR) at 14, 56-57.

PATENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

### Nicol and Kling do not render claim 2 obvious

#### U.S. Patent 9,075,605 B2 Dependent Claim 2

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

2. The method of claim 1 wherein: said clock frequency is determined in part by processor voltage.

Ex. 1003 (US 9,075,605) at 16:6-8.

Ex. 1003 (US 9,075,605) at 15:6-16:5.

71

### Kling's voltage threshold

Pet., 45-46. Kling teaches reducing clock frequency when a voltage representing

the power consumed by a processor reaches a threshold. *Id.*; Ex. 1010, 2:31-51 ("the

TENT OWNER'S DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

7

#### **Nicol**

United States Patent [19]

11] Patent Number:

6,141,762

Nicol et al.

[45] Date of Patent: Oct. 31, 2000

Hence, the operating system of PE 100 needs to ascertain the required completion time, divide the collection of tasks

as evenly as possible (in terms of needed processing time), consider the PE with the tasks that require the most time to carry out, and adjust the clock frequency to insure that the most heavily loaded PE carries out its assigned tasks within the required completion time. Once the frequency is thus determined, a minimum supply voltage can be determined.

Ex. 1009 (Nicol) at 3:66-4:5; Paper 20 (POR) at 10, 44.

Ex. 1009 (Nicol) at Fig. 3.

### Nicol and Kling do not render claim 3 obvious

#### U.S. Patent 9,075,605 B2 Dependent Claim 3

1. A method for operating a multiprocessor system comprising a plurality of data processing cells, each of the plurality of data processing units (a) including at least one Arithmetic Logic Unit (ALU) and a register unit and (b) being adapted for sequentially processing data, the method comprising:

the multiprocessor system setting a clock frequency, of at least a part of the multiprocessor system to a minimum in accordance with a number of pending operations of a first processor;

the multiprocessor system subsequently increasing the clock frequency of the at least the part of the multiprocessor system to a maximum in accordance with a number of pending operations of a second processor; and

the multiprocessor system subsequently reducing the clock frequency of the at least the part of the multiprocessor system in accordance with (a) an operating temperature threshold preventing over-temperature and (b) a hysteresis characteristic.

Ex. 1003 (US 9,075,605) at 15:6-16:5.