# TRANSLATOR CERTIFICATION

I, Timothy Pennington , hereby declare:

That I possess advanced knowledge of the Japanese and English. My qualifications are as follows:

- 20 years of experience as Japanese-English translator, including patents, clinical studies, patient case studies, and documents concerning motion control.

- M.A. Education, M.A. Japanese Linguistics, JLPT 1

I attached the translation is, to the best of my knowledge and belief, a true and accurate translation from Japanese to English of Japanese patent S62-104075. All statements made in this declaration of my own knowledge are true and all statements made on information and belief are believed to be true. I make these statements with the understanding that willful false statements are the like arc punishable by fine or imprisonment, or both (17 U.S.C. 1001).

I declare under penalty of perjury that the forgoing is true and correct. Executed on this 7 day of January, 2020.

At: Fukuoka, Japan

Tim Pennington

| 12. Unex                                    | 19. Japan Patent Office (JP)<br>amined patent publication (A)<br>11. Published unexamined patent application<br>S62-104075 |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 51. Int. Cl. <sup>4</sup> Classification co | Patent office filing number 43. Published 14 May 1987                                                                      |  |  |  |  |

| H 01 L 27/14                                | 7525-5F                                                                                                                    |  |  |  |  |

| H 04 N 5/225                                | D-8523-5C                                                                                                                  |  |  |  |  |

| 5/335                                       | Z-8420-5C Examination request No request No. of Inventions: 1 (5 pages total)                                              |  |  |  |  |

|                                             |                                                                                                                            |  |  |  |  |

| 54. Name of invention Solid state ima       | Solid state imaging device                                                                                                 |  |  |  |  |

|                                             | 21. Patent application S60-243353                                                                                          |  |  |  |  |

|                    |                      | 22. Application submission 30 Oct 1985                                                |

|--------------------|----------------------|---------------------------------------------------------------------------------------|

| 72. Inventor       | TANUMA Chiaki        | Corporate Research & Development Center, Komukai-toshiba-cho, Saiwai-ku, Kawasaki-shi |

| 72. Inventor       | IZUMI Mamoru         | Corporate Research & Development Center, Komukai-toshiba-cho, Saiwai-ku, Kawasaki-shi |

| 72. Inventor       | Honda Hiroki         | Corporate Research & Development Center, Komukai-toshiba-cho, Saiwai-ku, Kawasaki-shi |

| 71. Applicant      | Toshiba Corporation  | 72, Horikawa-cho, Saiwai-ku, Kawasaki-shi                                             |

| 74. Representative | Attorney SUZUE Takeh | iko, 2 others                                                                         |

### **Patent Description**

### 1. Name of invention

Solid state imaging device

### 2. Scope of claims

(1) Solid state imaging device that is characterized by a configuration consisting of a solid state imaging element and a 1st PCB upon which the solid state imaging element is located. The solid state imaging device has a matching circuit in order to match the solid state imaging element with an external circuit, and that matching circuit consists of a 2nd circuit board positioned to form a single unit with the 1<sup>st</sup> circuit board on the underside of the 1<sup>st</sup> circuit board, and is loaded with multiple chip components.

(2) The 2<sup>nd</sup> circuit board is made of a flexible PCB or a glass epoxy board, forming a solid state imaging device as described in paragraph 1 of the scope of the patent claims.

(3) The 2<sup>nd</sup> circuit board described above adheres closely to the 1<sup>st</sup> circuit board so that it forms a single unit, and is aligned so that it extends to the exterior of the 1<sup>st</sup> circuit board. Both sides of the circuit board are loaded with the multiple chip components noted earlier, forming a solid state imaging device as described in paragraph 1 of the scope of the patent claims.

(4) Part of the component with multiple chips that comprises the aforementioned integrated circuit is installed to the underside of the 1<sup>st</sup> circuit board, and the 2<sup>nd</sup> circuit board that has the remaining chip components overlaps with the underside of the 1<sup>st</sup> circuit board through a mold resin layer, forming a solid state imaging device as described in paragraph 1 of the scope of the patent claims.

(5) A solid state imaging device as described in paragraph 1 of the scope of the patent claims that is equipped with at least one fiber optic glass filter sheet adhering closely to the surface of the solid state imaging device.

### 3. Detailed description

### Industrial fields of application

The invention of the solid state imaging device is particularly concerned with the mounting structure of a matching circuit in order to match the imaging device with an exterior circuit.

Prior art

Compared to a camera tube, solid state imaging elements have the advantages of not producing an after-image or ghost image, and of having less image distortion, etc. In recent years, the application of solid state elements has quickly progressed, such as their use in video cassette (VTR) cameras and ITV cameras, etc. They have recently also been used as imaging elements in single-unit VTR cameras and 8 mm VTR cameras, etc. Solid state imaging elements currently used are mainly CCD imaging elements and MOS-type imaging elements. The size of these element chips are 2/3 inch, 1/2 inch, 8 mm "cine film size" and so on, depending on the lens that is used. These imaging element chips are mounted as a normal package.

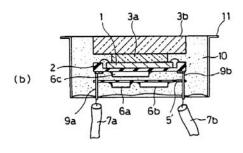

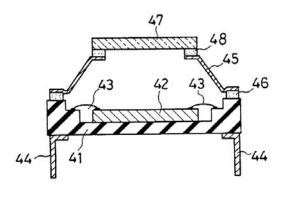

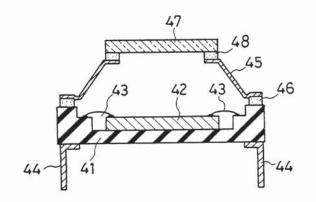

Fig. 4 shows an example of the representative chip mounting structure for a conventional solid state imaging device. Solid state element chip 41 (such as CCD, etc.), is affixed using a die bond adhesive onto stem 41, or some package substrate formed by ceramic, etc. There is a bonding wire 43 made of aluminum, etc. between the terminal on chip 42 and the terminal on chip 41 that connects them. I/O lead 44 is installed to the bottom of stem 41. In order to protect image element chip 42, the top of stem 41 is covered by cap 45, which is installed to glass substrate 47, which functions as an optical window. Ceramic ring 48 adheres to glass substrate 47 by using fritted glass, and to cap 45 adheres using a wax material. Cap 45 is welded to weld ring 46 that it is installed near stem 41, forming a seal. Representative examples of this type of conventional mounting have a shape 25 mm x 25 mm, with a height as much as 8 mm.

Problems that this invention attempts to solve

There has been an increasing demand to make cameras more compact in recent years, and progress has been made with ultra-compact camera heads and endoscopy. These applications require separation of the solid state imaging element and external circuitry such as the drive circuit, etc. that is connected to that imaging element using the current technology. In order to have a signal cable between the solid state imaging element and the external circuit in such designs to connect them, it is difficult to get the correct impedance matching. If the proper impedance matching cannot be achieved, then loss of image quality cannot be avoided due to reduced S/N.

Conventional technology therefore forms a matching circuit that uses an emitter-follower on a printed circuit board, and this is installed between the solid state imaging element and the external circuit. Between the printed circuit board equipped with the solid state imaging element and the matching circuit, and between the printed circuit board and the external circuit, each has a lead connecting them. With this method, many lead lines are required, increasing the probability that a lead line would become disconnected. Furthermore, because there is a lead line running between the solid state imaging element and the matching circuit, there is still the problem with reduced S/N. The use of a separate matching circuit PCB and the solid state imaging element makes it difficult to make the camera head more compact.

In light of the description above, the objective of this invention is to provide a solid state imaging device that improves characteristics, improves reliability, and achieves a more compact design through an improved mounting configuration.

Means to solve the aforementioned problems

This invention is configured so that the 1<sup>st</sup> PCB is loaded with a solid state imaging element, and a 2<sup>nd</sup> PCB loaded with a chip component that is configured with a matching circuit forms a single unit with the underside of that 1<sup>st</sup> PCB. It is fine for the 1<sup>st</sup> PCB and the 2<sup>nd</sup> PCB to be made into a single unit, stuck together by an adhesive, and for those PCBs to form a single unit by a specified gap between them. In either case, it would be good to use a mold resin to harden the 1<sup>st</sup> PCB and the 2<sup>nd</sup> PCB to be the 2<sup>nd</sup> PCB to be made into a single unit.

### Effects

With the configuration of this device, it is not necessary to connect a lead wire between the 1<sup>st</sup> PCB and the 2<sup>nd</sup> PCB. In other words, the I/O lead or the terminal of the solid state imaging device installed to the 1<sup>st</sup> PCB is connected to the terminal

of the matching circuit formed on the 2<sup>nd</sup> PCB through soldering or bonding, etc. As this invention is configured with a camera head as a single unit that includes the matching circuit, it is fine to have only a lead line wired between the camera head and the external circuit.

### Practical application examples

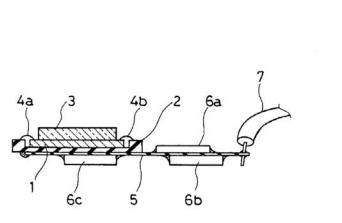

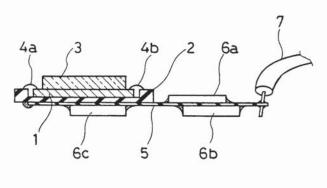

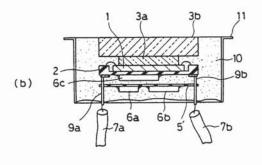

Fig. 1 shows the main cross section of the camera head in a practical application example of this invention. Solid state imaging element chip 1 (such as CCD, etc.) is attached to package mount 2 (on the 1<sup>st</sup> PCB) using normal die bonding. Between the bonding pads (not shown) installed to both solid state imaging element chip 1 and to package mount 2, there is aluminum wire 4 (4a, 4b, etc.) forming a connection. Optical glass filter 3 for color correction is directly affixed to the surface of solid state imaging element chip 1 using an adhesive for optical components. In other words, by not using the cap that is conventionally used, optical glass filter 3 is itself used as a surface protective material for solid state imaging element chip 1, making the design thinner.

The matching circuit needed to achieve impedance matching between solid state imaging chip 1 and the external circuit is formed with multiple units of chip component 6 (6a, 6b, 6c, etc.) mounted to transistor flexible printed circuit board 5 (the 2<sup>nd</sup> PCB) using solder, etc. The matching circuit is configured by, for example, an emitter-follower circuit. Flexible printed circuit board 5 adheres to the underside of package substrate 2 with an adhesive, forming a single unit. Soldering connects the solid state element I/O terminal installed to the underside of package mount 2 and the matching circuit terminal on flexible printed circuit board 5. In this application example, the size of flexible printed circuit board 5 is determined by how far out the extension is beyond the outside of package substrate 2. Chip component 6 that makes up the matching circuit is mounted by using both sides of flexible printed circuit board 5. Lead wire 7 used to connect to the external circuit is connected to the terminal formed on the end of flexible printed circuit board 5.

Although omitted from the drawing, the camera head that forms a single unit with the matching circuit board and the solid state imaging element board using this configuration is fixed in place using a mold resin.

The actual prototype has a camera head with width 8 mm, length 17 mm, and depth 3 mm, and used an electric endoscope with a circumference of 12 mm  $\emptyset$ .

With this application example, there is no lead wire between the matching circuit board and the solid state element board, thus reducing the possibility of disconnect from occurring, and making it possible to achieve more stable impedance matching. Furthermore, by adopting the gap-less configuration with the circuit boards forming a single unit, it is possible to achieve large-scale reduction in the size of the camera head.

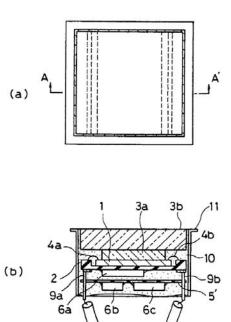

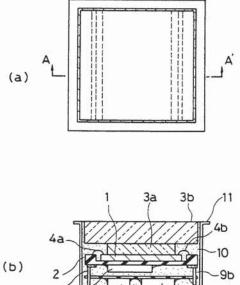

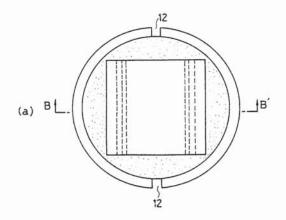

Fig. 2 (a) and (b) show a planar view of the camera head in another practical application example, and a cross-section of A-A. The portion that matches Fig. 1 uses the same symbols as Fig. 1, and thus omits the detailed explanation of components. In this practical application example, glass filter 3a for color correction and quartz filter 3a (which is used as a space-reduction filter) overlap with the surface of solid state imaging element chip 1, which is loaded onto package mount 2, and are secured by an adhesive for optical components. I/O lead 9 (9a, 9b, etc.) is installed to the underside of package mount 2, to which solid state element chip 1 is mounted. A portion of the chip components 6a that make-up the matching circuit that are also on the underside of package mount 2 are directly secured by solder. I/O lead 9 here does not form the terminal of solid state imaging element chip 1, but includes the lead that functions as the terminal for the matching circuit only. Mounted to the underside of package mount 2, we find glass epoxy board 5' (the 2<sup>nd</sup> PCB), which is equipped with the other chip components 6b, 6c, etc., that form the matching circuit, positioned to form the designated gap. In other words, glass epoxy board 5' is

already equipped with a hole through which I/O lead will pass, and I/O lead 9 is installed by being placed through that hole. The wiring terminal on glass epoxy board 5' is connected to I/O lead 9 by solder, etc.

The solid state imaging element chip board that is loaded as described above and the matching circuit board are placed in frame 11 so that the outer circumference is protected. Frame 11 is filled up by mold resin 10, which blocks out outside air for each element, and improves moisture resistance. This way, the solid state imaging element chip board and the matching circuit board are then connected to the camera head, forming a single unit, and to the external circuit by soldering lead wire 7 (7a, 7b, etc.) to I/O lead 9.

Just like with the previous application example, this application example does not require many lead wires, so there is a high degree of reliability, and excellent matching characteristics because of the matching circuit board forming a single unit, allowing for a more compact camera head.

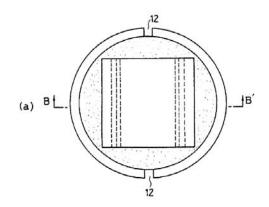

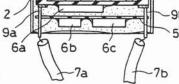

Fig. 3 (a) and (b) shows a planar view of an application example that is a slight variation of what is shown in Fig. 2, along with a cross-section of B-B'. The portion that matches Fig. 2 uses the same symbols, so a detailed explanation has been omitted. This application example differs from the previous application example in that frame 11 is cylindrical, and that slit 12 has been formed in frame 11 for positioning.

Technical advantages of the invention

With the invention as described above, it is possible to achieve a greater compact design by forming a single unit with the matching circuit board, as well as achieve a solid state imaging device with improved reliability and better characteristics. 4. Simple explanation using diagrams

Fig. 1 is a cross-section diagram showing the camera head in an application example for this invention. Fig. 2 (a) and (b) show a planar view of the camera head in another application example, along with a cross-section of A-A'. Fig. 3 (a) and (b) show a planar view of the camera head in yet another application example, along with a cross-section of B-B'. Fig. 4 is a cross-section diagram showing the mounting configuration of conventional solid state imaging elements.

1. Solid state imaging element chip

2. Package mount (1<sup>st</sup> PCB)

3. 3a. Glass filter for color correction, 3b. Quartz filter for space reduction filter

4. (4a, 4b, etc.) Aluminum wire

5. Flexible printed circuit board (2<sup>nd</sup> PCB)

5'. Glass epoxy board (2<sup>nd</sup> PCB)

6. (6a, 6b, 6c, etc.) Chip components for matching circuit

7. (7a, 7b, etc.) Lead line

9. (9a, 9b, etc.) I/O lead

10. Mold resin

11. Frame

12. Slit for positioning

Application Representative Attorney SUZUE Takehiko

7a

-7ь

Fig. 4

### (19日本国特許庁(JP) ①特許出願公開

## <sup>10</sup> 公開特許公報(A) 昭62-104075

| <pre>⑤Int.Cl.⁴</pre>                  | 識別記号 | 庁内整理番号                            |      | 43公開 | 昭和62年(1987)5月14日 | 1 |

|---------------------------------------|------|-----------------------------------|------|------|------------------|---|

| H 01 L 27/14<br>H 04 N 5/225<br>5/335 |      | 7525-5F<br>D-8523-5C<br>Z-8420-5C | 審查請求 | 未請求  | 発明の数 1 (全5頁)     |   |

公発明の名称 固体撮像装置

20特 願 昭60-24335320出 願 昭60(1985)10月30日

| ⑦発 | 明 | 者 | 田沼    | 千   | 秋 | 川崎市幸区小向東芝町1番地 | 株式会社東芝総合研究所内 |

|----|---|---|-------|-----|---|---------------|--------------|

| 個発 | 明 | 者 | 泉     |     | 守 | 川崎市幸区小向東芝町1番地 | 株式会社東芝総合研究所内 |

| 個発 | 明 | 者 | 本 多   | 博   | 樹 | 川崎市幸区小向東芝町1番地 | 株式会社東芝総合研究所内 |

| ⑦出 | 願 | 人 | 株式会   | 社 東 | 芝 | 川崎市幸区堀川町72番地  |              |

| 個代 | 理 | 人 | 弁理士 鈴 | 江 武 | 彦 | 外2名           |              |

| 1.00 |   | 1000 |

|------|---|------|

| 明    | 細 | 콾    |

|      |   |      |

1. 発明の名称

### 固体最像装置

2.特許請求の範囲

(1) 固体跟像素子と、この素子が搭載された 第1の基板と、前記固体最像素子と外部回路との 整合をとるための整合回路とを有する固体撮像装 置において、前記整合回路は、前記第1の基板の 裏面側に第1の基板と一体的に配置された第2の 基板に複数のチップ部品を搭載して構成されてい ることを特徴とする固体撮像装置。

(2) 前記第2の基板は、フレキシブルプリント基板またはガラスエポキシ基板である特許請求の範囲第1項記載の固体顕像装置。

(3) 前記第2の基板は、前記第1の基板の裏面に一部密着させて第1の基板の外側に延在する ように配置され、この第2の基板の両面に前記複 数のデップ部品が搭載されている特許請求の範囲 第1項記載の固体攝像装置。

(4) 前記整合回路を構成する複数のチップ部

品の一部は前記第1の基板の裏面に搭載され、残 りのチップ部品が搭載された第2の基板は第1の 基板裏面側にモールド樹脂層を介して重ねられて いる特許請求の範囲第1項記載の固体照像装置。 (5) 前記固体瞬像素子の表面に密着して少な くとも一枚の光学ガラスフィルタが設けられてい る特許請求の範囲第1項記載の固体蹑像装置。

3. 発明の詳細な説明

産業上の利用分野

木 発明は固体 服像装置に係り、特に 服像素子と 外部回路との整合をとるための整合回路部の実装 構造に関する。

従来の技術

固体嚴像素子は嚴像管と比較して、残像がない、 焼付がない、画像歪みがない等の特長を有し、近 年、VTR用カメラ、ITVカメラなどへの適用 が急速に進んでいる。 最近では、カメラー体型 VTRや8mm VTRなどの嚴像素子としても用い られている。現在用いられている固体最像素子は、 主にCCD撮像素子やMOS型最像素子であり、

### 特開昭62-104075(2)

これらの素子チップのサイズは使用されるレンズ に合せて2/3インチ、1/2インチ、8 mmシネ サイズなどとなっている。これらの最像素子チッ プは通常パッケージに実装されている。

第4図は従来の固体撮像装置の代表的なチップ 実装構造例である。CCDなどの固体撮像素子チ ップ42は、セラミックなどで形成されたパッケ ージ基板即ちステム41上にダイボンド用接着剤 により取付けられている。チップ42上の端子と ステム41上の端子との間は、アルミニウムなど のボンディング・ワイヤ43により接続されてい る。ステム41の底部には、I/Oリード44が 設けられている。撮像素子チップ42の保護のた め、ステム41上には光学用窓としてのガラス板 47が取付けられたキャップ45が被せられてい る。セラミック・リング48は、ガラスフリット によりガラス板47と接着され、またキャップ4 5にろう材により接着されている。キャップ45 はステム41の周辺に設けられたウェルド・リン グ46にウェルド法により接着されて封止が行わ

る。この様な方式では、リード線を多く必要とす るため、リード線の断線事故が発生し易い。また 固体機像素子と整合回路の間にリード線が配設さ れるため、S/N低下が未だ問題となる。更に固 体機像素子と別に整合回路基板を設けることは、 カメラ・ヘッド部の小型化を難しくしている。

本発明は上記の点に整み、整合回路を含めた実 装偶造の改良により特性向上と信頼性向上および 小型化を図った固体顕像装置を提供することを目 的とする。

問題点を解決するための手段

本発明においては、固体機像素子を搭載した第 1の基板に対してその裏面側に、整合回路を構成 するチップ部品を搭載した第2の基板を一体的に 設けた構造とする。第1の基板と第2の基板は接 着剤により密着させた状態で一体化してもよいし、 両者の間に所定の間隊がある状態で一体化しても よい。いずれの場合も一体化された第1の基板と 第2の基板はモールド樹脂で固めることが望まし いが、この場合上記の間隙にはモールド樹脂が注 れている。このような従来の実装構造では代表的には、その形状が25mm×25mm程度であり、高さは8mm程度になる。

発明が解決しようとする問題点

近年、カメラの小型化への要求が高まっており、 超小型カメラヘッドや内視鏡等の開発が盛んであ る。この様な応用においては、固体機像素子と、 これと接続される駆動回路等の外部回路とは現在 の技術では分離することが必要である。この場合、 固体機像素子と外部回路との間を信号ケーブルで 接続することになるため、両者の間のインピーダ ンス整合をとることが難しい。インピーダンス整 合がとれないと、S/Nの低下による画質低下が 免れない。

そこで従来は、エミッタホロアなどを用いた整合回路をプリント基板上に形成して、これを固体撮像素子と外部回路との間に設けることが行われている。固体撮像素子と整合回路を搭載したプリント基板との間、およびこのプリント基板と外部回路との間は、それぞれリード線により接続され

入されるようにするのがよい。

#### 作用

本発明の構造では、第1の基板と第2の基板の間をリード線で接続する必要がない。即ち、第1の基板に設けられた固体撮像素子の1/〇リードあるいは端子と、第2の基板に形成された整合回路の端子との間はハンダ付やワイヤボンディングなどにより接続される。そして本発明では整合回路基板を含めて一体としてカメラ・ヘッドが構成されるから、リード線はこのカメラ・ヘッドと外部回路との間にのみ配設すればよい。

#### 実施例

第 1 図 は本 発 明 の 一 実 施 例 の カ メ ラ ・ ヘッド の 要 部 断 面 を 示 す 。 C C D な ど の 固 体 撮 像 素 子 チッ ブ 1 は、 パッケージ 基 台 (第 1 の 基 板 ) 2 に 通 常 の ダ イ ボ ン ディング 接 着 剤 に よ り 取 着 さ れ て い る 。 固 体 機 像 素 子 チッ ブ 1 と パ ッケージ 基 台 2 に そ れ ぞ れ 設 け ら れ た ボ ン ディング パ ッド ( 図 示 せ ず ) の 間 は ア ル ミ ニ ウ ム ・ ワ イ ヤ 4 ( 4 a ・ 4 b ・ … ) に よ り 接続 さ れ て い る 。 固 体 撮 像 素 子 チッブ 1 表

-380-

特開昭62-104075(3)

面には、 色補正用光学ガラスフィルタ3が光学用 接着剤により直接接着されている。 即ち従来のよ うにキャップを用いず、 光学ガラスフィルタ3 自 身を固体撮像素子チップ 1 の表面保護部材として 用いて薄型としている。

固体機像素子チップ1と外部回路との間のイン ビーダンス整合をとるための整合回路は、フレキ シブルプリント基板(第2の基板)5にチップ・ トランジスタ等の複数のチップ部品6(6 a , 6 b , 6 c , …)をハンダ付等により搭載して形成 されている。整合回路は例えば、エミッタホロア 回路により構成される。フレキシブルプリント基 板5 はパッケージ基板2の裏面に接着剤により接 替されて一体化されており、パッケージ基台2の 裏面に設けられた固体機像素子の!/O 端子とフ レキシブルプリント基板5上の整合回路端子との 間はハンダ付により接続されている。この実施例 では、フレキシブルプリント基板5 はパッケージ 基板2 の外側にまで延在する大きさであり、整合 回路を構成するチップ部品6 はこのフレキシブル

ッケージ基台2に搭載された固体撮像素子チップ 1の表面に色補正用ガラスィルタ3aと空間低域 フィルタとしての水晶フィルタ3bが重ねられて 光学用接着剤により貼り合せられている。固体量 像素子チップ1が搭載されたパッケージ基台2の 裏面に1/0リード9(9a,9b,…)が設け られ、またこの裏面に整合回路を構成するチップ 部品の一部6aが直接ハンダ付されている。ここ での「ノ〇リード9は、固体撮像素子チップ1の 蟷子にはならず、整合回路のみの端子となるリー ドを含む。そしてこのパッケージ基台2の裏面側 に、整合回路を構成する他のチップ部品6 b, 6 c, …が搭載されたガラスエポキシ基板(第2の 基板) 5′ が所定の間隙をおいて配置されている。 即ちガラスエポキシ基板5′は、予め1/0リー ド9が貫通する孔が設けられていて、1/〇リー ド9にはめ込む形で取付けられている。ガラスエ ポキシ基板5′上の配線端子は、1/0リード9 にハンダ付等により接続されている。

このように積層された固体撮像素子チップ基板

プリント基板5の両面を利用して搭載されている。 フレキシブルプリント基板5の端部に形成された 端子に、外部回路との接続を行うためのリード線 7が接続されている。

図では省略したが、このようにして固体撮像素 子基板と整合回路基板を一体化したカメラ・ヘッ ドは、モールド樹脂により固められている。

実際の試作例では、幅8 mm、長さ17 mm、厚み3 mmのカメラ・ヘッドが得られ、これを外径約12 mm ゆの電子内視鏡に適用することができた。 この実施例によれば、固体撮像素子基板と整合 回路基板の間にリード線を配設しないため、断線 事故等が減少し、またインビーダンス整合をより 確実にとることができる。またこれらの基板の一 体化とキャップレス構造の採用により、カメラ・

ヘッドの大幅な小型化が図られる。 第2図(a)(b)は他の実施例のカメラ・ヘ

ッドを示す平面図とそのA – A ´ 断面図である。 第1図と対応する部分には第1図と同一符号を付 して詳細な説明は省略する。この実施例では、バ

と整合回路基板は、フレーム11に納められて外 周が保護されるようになっている。またフレーム 11内にはモールド樹脂10が充填され、これに より各素子の外気との遮断・耐湿性向上が図られ ている。こうして固体撮像素子チップ基板と整合 回路基板が一体化されたカメラ・ヘッドと外部回 路との接続を行うために、リード線7(7a,7 し、…)が!/〇リード9にハンダ付けされてい る。

この実施例によっても先の実施例と同様に、多 くのリード線を必要としないため信頼性が高く、 整合回路基板が一体化されているため整合特性に も優れた、小型化カメラ・ヘッドが得られる。

第3図(a)(b)は第2図のものを僅かに変 形した実施例のカメラ・ヘッドを示す平面図とそ のB-B<sup>-</sup>断面図である。従って第2図と対応す る部分には同一符号を付して詳細な説明は省略す る。この実施例では、フレーム11を円筒状とし た点、およびこのフレーム11に位置決め用のス リット12を設けた点が先の実施例と異なる。

### 特開昭62-104075(4)

### 発明の効果

以上述べたように本発明によれば、整合回路基 板を一体化して小型化を図ると共に、特性向上と 信頼性向上を図った固体最優装置を実現すること ができる。

4. 図面の簡単な説明

第1図は本発明の一実施例のカメラ・ヘッドを 示す断面図、第2図(a)(b)は他の実施例の カメラ・ヘッドを示す平面図とそのA-A´断面 図、第3図(a)(b)は更に他の実施例のカメ ラ・ヘッドを示す平面図とそのB-B´断面図、 第4図は従来の固体撮像素子の実装構造例を示す 断面図である。

1 … 固体撮像素子チップ、2 … パッケージ基合 (第 1 の基板)、3,3 a … 色補正用ガラスフィ ルタ、3 b … 空間低域フィルタ用水品フィルタ、

4 (4 a,4 b,…) … アルミニウム・ワイヤ、

5 … フレキシブルプリント基板(第 2 の基板)、

5 ′ … ガラスエポキシ基板(第 2 の基板)、

6 a,6 b,6 c,…) … 整合回路用チップ部 品、7(7a,7b,…)…リード線、9(9a, 9b,…)…!/Oリード、10…モールド樹脂、 11…フレーム、12…位置決め用スリット。

出願人代理人 弁理士 鈴江武彦

第 1 図

-382-

第 2 図

Samsung Exhibit 1016 Page 10 of 11

第 3 図

第 4 図