# UNITED STATES DISTRICT COURT FOR THE NORTHERN DISTRICT OF CALIFORNIA SAN FRANCISCO DIVISION BROADCOM CORPORATION, et al., Plaintiffs, Case No. 3:20-ev-04677-JD v. NETFLIX, INC. JOINT CLAIM CONSTRUCTION AND PREHEARING STATEMENT

In accordance with Patent L.R. 4-3 and the Court's Standing Order for Claim Construction in Patent Cases Before Judge James Donato, Plaintiffs Broadcom Corporation and Avago Technologies International Sales PTE Ltd. and Defendant Netflix, Inc. (collectively the "Parties") jointly submit this Joint Claim Construction and Prehearing Statement (the "Statement") for U.S. Patent Nos. 7,266,079 (the "'079 Patent"); 8,259,121 ("the '121 Patent"); 8,959,245 ("the '245 Patent"); 8,270,992 ("the '992 Patent"); 6,341,375 ("the '375 Patent"); 8,572,138 ("the '138 Patent"); 6,744,387 ("the '387 Patent"); 6,982,663 ("the '663 Patent"); 9,332,283 ("the '283 Patent"), 8,548,976 ("the '976 Patent"); 7,457,722 ("the '722 Patent"); and 8,365,183 ("the '183 Patent"). This Statement contains information on claim construction for these patents under Patent L.R. 4-3 as follows.

# Term(s) Patent Claim(s) Stipulated Construction "flow control module" '121 1, 35 "valve to control data flow"

To narrow their disputes, the Parties have met and conferred and have reached agreement

STIPULATED CLAIM CONSTRUCTIONS UNDER PATENT L.R. 4–3(a)

I.

Defendants.

on claim constructions for the following terms:

| "decoder devices" / "decoders"                                               | '375         | 15                  | "decoders" in Steps (C) and (D) of Clai<br>15 refers to the "decoder devices"<br>included in Steps (B) and (D) of Claim |

|------------------------------------------------------------------------------|--------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| "said exp-Golomb<br>binarization comprises                                   | '387         | 4                   | Governed by 35 U.S.C. § 112(6).                                                                                         |

| means for"                                                                   |              |                     | Function: "a) forming b) determining an                                                                                 |

|                                                                              |              |                     | appending"                                                                                                              |

|                                                                              |              |                     | Structure: binarization module configured to perform at least Steps 4 4(e).                                             |

| "determining the least significant bits, of v-(N=2)-2**γ"                    | '387         | 4, 6                | "determining the least significant bits, $v-(N-2)-2**\gamma$ "                                                          |

| "determining the number of bits, γ+1, required to                            | '387         | 4                   | "determining the number of bits, $\gamma+1$ , required to represent v–(N–2) where                                       |

| represent $v-(N-2)$ where $\gamma = \frac{1}{2} \log 2(v-(N-2))^{-1}$ , v is |              |                     | $\gamma = \frac{1}{\log 2(v - (N-2))^{-1}}$ , v is the code symindex value, and N is the threshold value                |

| the code symbol index value, and N is the                                    |              |                     | and thereafter transforming γ into a una representation to create a result"                                             |

| threshold value, and then transforming y into a                              |              |                     | No further construction is necessary regarding order of limitations.                                                    |

| unary representation to create a result"                                     |              |                     |                                                                                                                         |

| "determining the number of bits, $\gamma+1$ , required to                    | '387         | 6                   | "determining the number of bits, $\gamma+1$ , required to represent $v-(N-2)$ where                                     |

| represent v-(N=2) where $\gamma = \frac{\log 2(v-(N-2))J}{v}$ , v is         |              |                     | $\gamma = \frac{1}{\log 2}(v - (N-2))^{-1}$ , v is the code symindex value, and N is the threshold value                |

| the code symbol index value, and N is the                                    |              |                     | and thereafter transforming γ into a una representation to create a result"                                             |

| threshold value, and then transforming γ into a                              |              |                     | No further construction is necessary regarding order of limitations.                                                    |

| unary representation to create a result"                                     |              |                     |                                                                                                                         |

| Claim 12's Preamble                                                          | '663         | 12                  | The preamble of Claim 12 is limiting.                                                                                   |

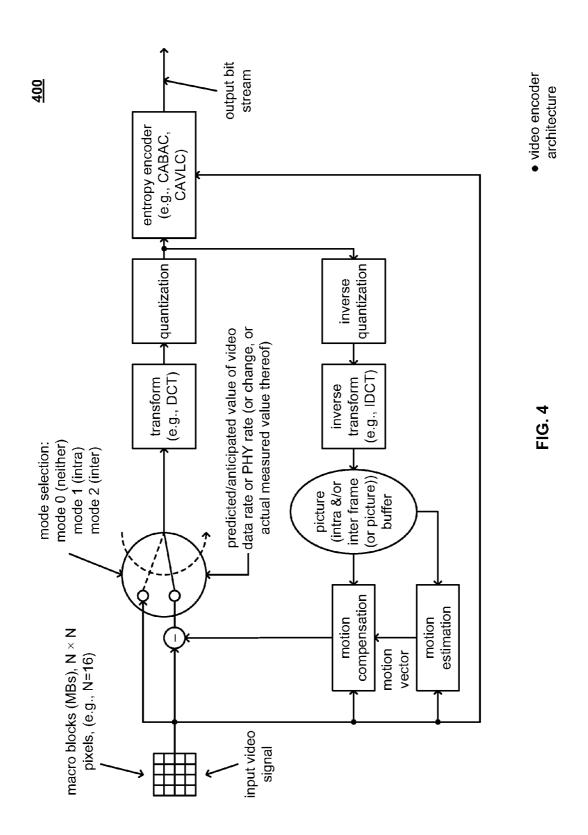

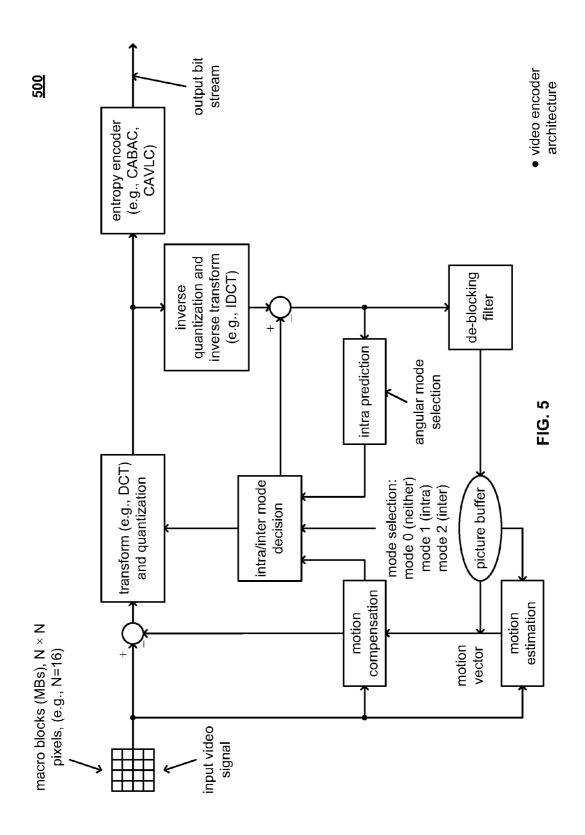

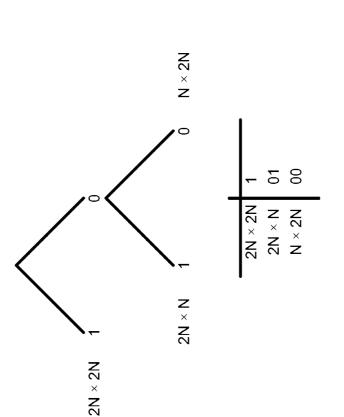

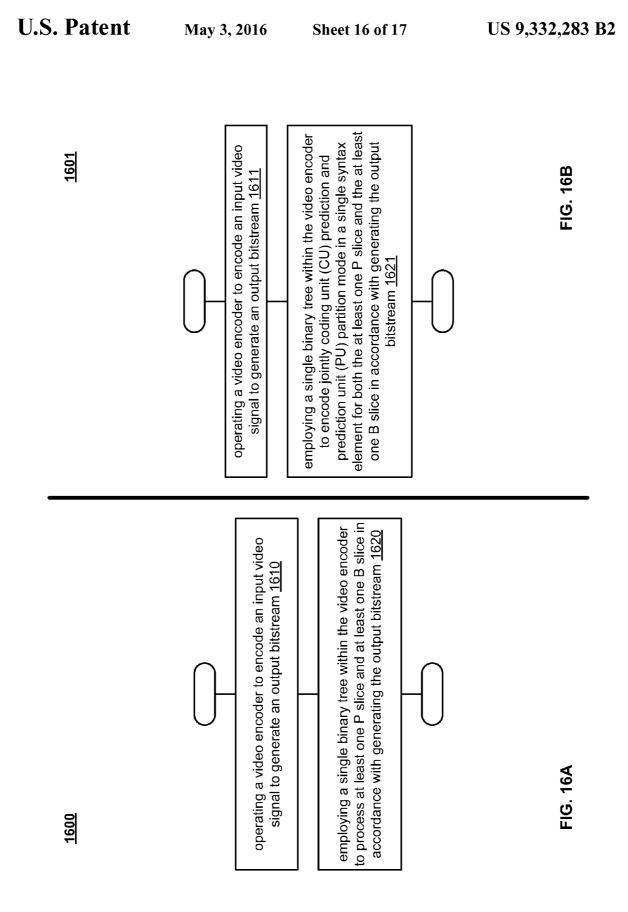

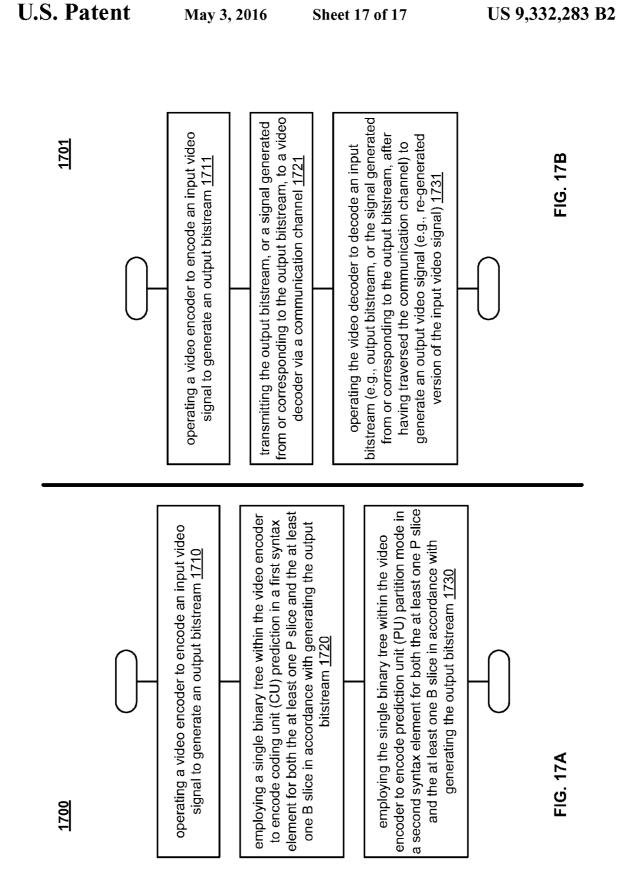

| "to generate to generate" "syntax element"                                   | '283<br>'283 | 1, 14, 16           | "to generate"  "a value that is encoded to form part of output bitstream"                                               |

| "output bitstream"                                                           | '283         | 1, 3, 14,<br>16, 18 | "a sequence of bits representing an encoded video signal"                                                               |

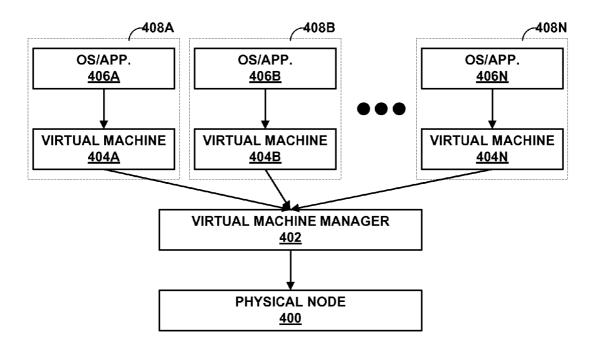

| "virtual machine"                                                            | '138         | 1, 9, 19,<br>22, 23 | "software that emulates a physical computing platform"                                                                  |

| "image instance"                                                             | '138         | 1, 19               | "a snapshot, or copy, of installed and configured software"                                                             |

| 1   | "operational                          | '183 | 1, 11, 16 | "hardware and/or software characteristics"                            |

|-----|---------------------------------------|------|-----------|-----------------------------------------------------------------------|

| 2   | characteristics"                      |      |           |                                                                       |

| 2   | "utilization criteria"                | '183 | 1, 4, 5,  | "criteria specifying a level of hardware                              |

| 3   |                                       |      | 8, 9, 11– | and/or software utilization"                                          |

| 4   |                                       |      | 13, 15–   |                                                                       |

| 4   | 66-11                                 | 2002 | 18, 20    | 6-1                                                                   |

| 5   | "wherein said codeword                | '663 | 20        | "wherein said codeword is compatible with a binarization scheme of an |

|     | in compatible with at least one of an |      |           | International Organization for                                        |

| 6   | International                         |      |           | Standardization/ International                                        |

| 7   | Organization for                      |      |           | Electrotechnical Commission [ISO/IEC]                                 |

|     | Standardization/                      |      |           | 14496-10 standard or of an International                              |

| 8   | International                         |      |           | Telecommunication Union-                                              |

| 9   | Electrotechnical                      |      |           | Telecommunications Standardization                                    |

| ,   | Commission 14496-10                   |      |           | Sector [ITU-T] Recommendation H.264"                                  |

| 10  | standard and an                       |      |           |                                                                       |

| 11  | International                         |      |           |                                                                       |

| 11  | Telecommunication                     |      |           |                                                                       |

| 12  | Union-<br>Telecommunications          |      |           |                                                                       |

| 1.0 | Standardization Sector                |      |           |                                                                       |

| 13  | Recommendation H.264"                 |      |           |                                                                       |

| 14  | "employ [a/the] single                | '283 | 1, 14, 16 | "employ [a/the] common binary tree                                    |

|     | binary tree"                          |      | ,, - 0    | [when processing at least one P slice and                             |

| 15  |                                       |      |           | at least one B slice to generate the output                           |

| 16  |                                       |      |           | bitstream]."                                                          |

| 10  | "a compute program"                   | '079 | 38        | "a computer program"                                                  |

# II. DISPUTED TERMS, PROPOSED CONSTRUCTIONS, AND SUPPORTING EVIDENCE UNDER PATENT L.R. 4–3(b)

In accordance with Patent L.R. 4–3(b) and the Court's Standing Order on Claim Construction, the Parties identify the following ten terms for construction<sup>1</sup>:

| Claim Terms                           | Plaintiffs' Proposed          | Defendant's Proposed                   |

|---------------------------------------|-------------------------------|----------------------------------------|

|                                       | Construction and Support      | Construction and Support               |

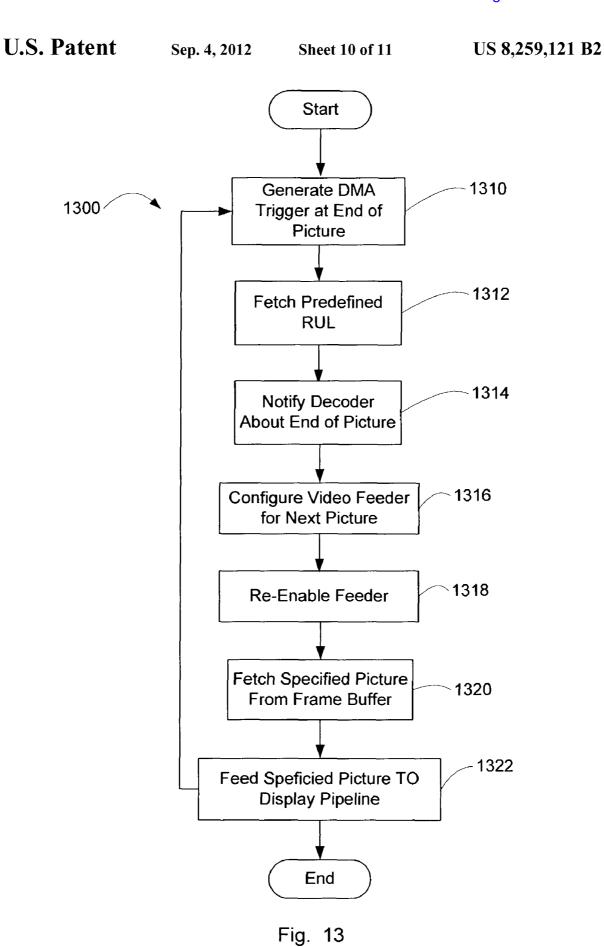

| "display pipeline"                    | <b>Proposed Construction:</b> | <b>Proposed Construction:</b>          |

| ('121 Patent, Claims 1-4, 33, 35, 36) | No construction necessary.    | "a series of video processing modules" |

<sup>&</sup>lt;sup>1</sup> Copies of the patents for which the parties have requested the Court to construe terms are attached to this Joint Statement — Ex. 1: '121 Patent; Ex. 2: '387 Patent; Ex. 3: '663 Patent; Ex. 4: '283 Patent; Ex. 5: '138 Patent.

17

18

19

20

21

22

23

24

25

26

27

28

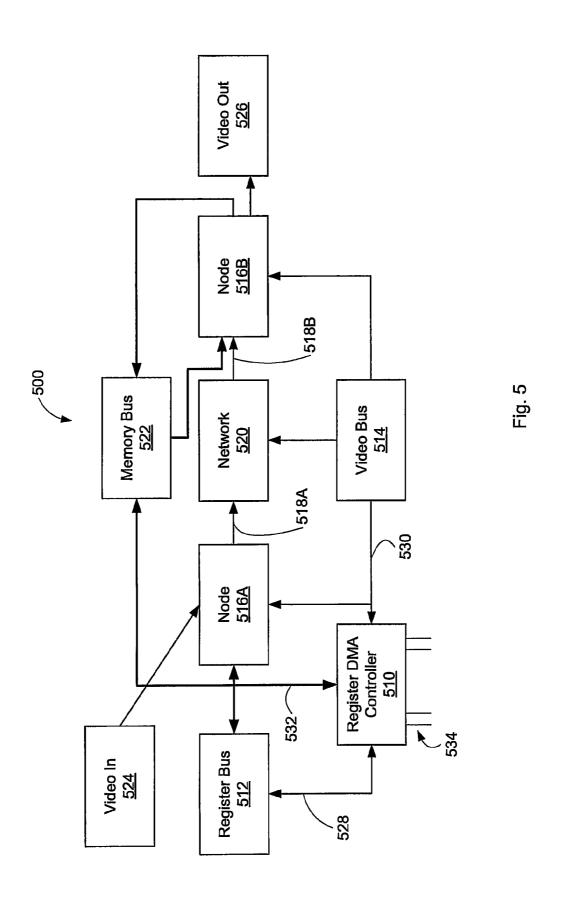

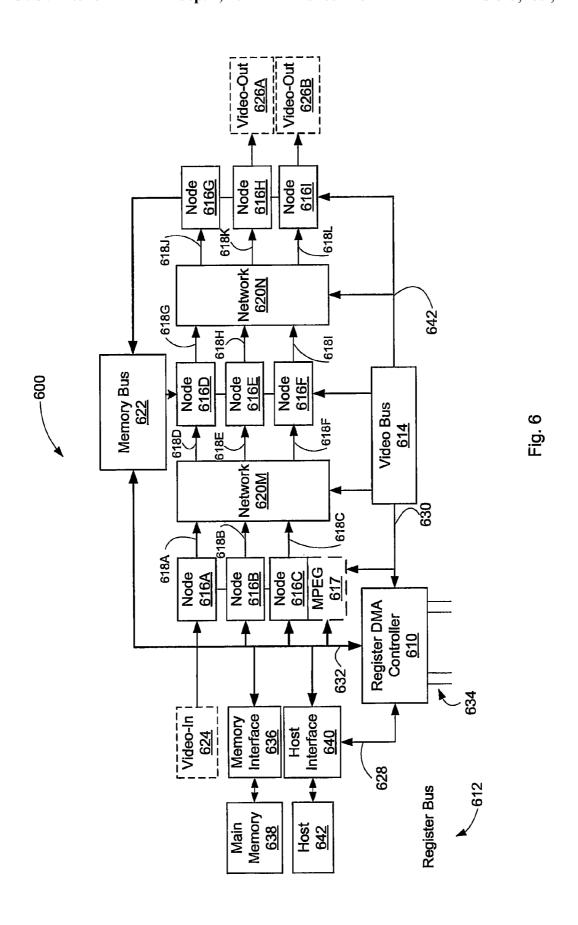

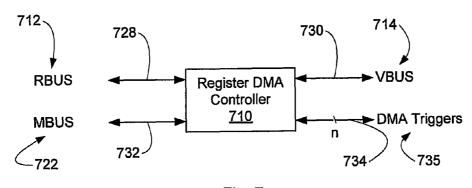

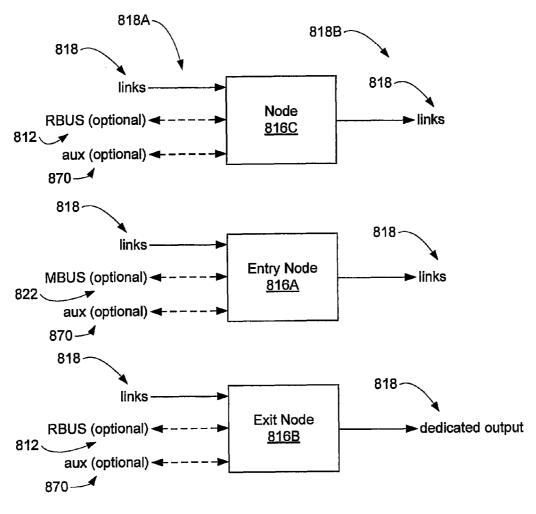

| 1  | Plain and ordinary meaning        | Intrinsic Evidence:                            |

|----|-----------------------------------|------------------------------------------------|

| •  | which, in the context of the      |                                                |

| 2  | patent, is "chain of multiple     | 1:41-49                                        |

| 3  | nodes"                            | 1:66-2:4                                       |

|    |                                   | 2:5-9                                          |

| 4  | Intrinsic Evidence:               | 2:55-59                                        |

| 5  |                                   | 3:23-25                                        |

| 5  | '121 Patent at 6:42–50, 7:36–38,  |                                                |

| 6  | 8:46–54, Fig. 4.                  | 4:54-58                                        |

| _  | 2121 D 4 4 E'1 H' 4 D             | 5:41-44                                        |

| 7  | '121 Patent File History Response |                                                |

| 8  | (Dec. 9, 2008).                   | 6:15-17<br>6:42-53                             |

|    | Extrinsic Evidence:               | 7:1-4                                          |

| 9  | Extrinsic Evidence.               | 7:13-19                                        |

| 10 | Declaration of Dr. Nathaniel      | 7:36-44                                        |

| 10 | Polish                            | 8:6-8                                          |

| 11 |                                   | 8:25-33                                        |

|    |                                   | 8:46-54                                        |

| 12 |                                   | 9:45-64                                        |

| 13 |                                   | 10:23-26                                       |

| 13 |                                   | 11:20-24                                       |

| 14 |                                   | Figs. 4, 5, 6, 8                               |

| 15 |                                   | U.S. Prosecution History: pp.                  |

| 13 |                                   | 535-36 (Dec. 9, 2008 Response to               |

| 16 |                                   | Final Office Action, pp. 15-16);               |

|    |                                   | p. 392 (Office Action of June 23,              |

| 17 |                                   | 2010, p. 3);<br>IPR 2020-01647: Patent Owner's |

| 18 |                                   | Preliminary Response; Decision                 |

| 10 |                                   | Denying Institution of <i>Inter</i>            |

| 19 |                                   | Partes Review;                                 |

| 20 |                                   | U.S. Pat. App. No. 10/300,370 at:              |

| 20 |                                   | Figs. 11A, 14                                  |

| 21 |                                   | Pg. 14, № [57];                                |

| 22 |                                   | Pg. 9, ₱ [39]                                  |

| 22 |                                   | Pg. 22, № [89];                                |

| 23 |                                   | U.S. Pat. App. No. 10/114,798 at               |

|    |                                   | Pgs. 21-22, PP [66 & 68];                      |

| 24 |                                   | U.S. Prov. App. No. 60/420,347                 |

| 25 |                                   | at Pg. 18, <b>№</b> [66]                       |

| 26 |                                   | Extrinsic Evidence:                            |

| 27 |                                   | IPR 2020-01647: Declaration of                 |

| 20 |                                   | James A. Storer;                               |

| 28 |                                   |                                                |

| 1  |                                             |                                                                   | IBM Dictionary of Computing                                         |

|----|---------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|

| 2  |                                             |                                                                   | (1994), p. 512 ("pipeline");<br>U.S. Patent No. 4,187,539 to        |

| 3  |                                             |                                                                   | Eaton at 1:8-22; Computer                                           |

|    |                                             |                                                                   | Desktop Encyclopedia (9th ed.                                       |

| 4  |                                             |                                                                   | 2001) ("pipeline processing"); "Pipe (Pipelined Image-              |

| 5  |                                             |                                                                   | Processing Engine)," Journal of                                     |

| 6  |                                             |                                                                   | Parallel and Distributed                                            |

|    |                                             |                                                                   | Computing 2, pp. 50-78 (1995);<br>Computer Graphics (2nd ed.        |

| 7  |                                             |                                                                   | 1992) (18.4.1 "Pipelining");                                        |

| 8  |                                             |                                                                   | IEEE Standard Glossary of                                           |

| 9  |                                             |                                                                   | Computer Hardware Terminology                                       |

| 10 |                                             |                                                                   | (1994), p.69 ("pipeline processor,"                                 |

| 10 |                                             |                                                                   | "pipelining");                                                      |

| 11 |                                             |                                                                   | Microsoft Press Computer                                            |

| 12 |                                             |                                                                   | Dictionary (1991) ("pipelining");<br>The Computer Glossary (7th ed. |

| 13 |                                             |                                                                   | 1995), p. 302 ("pipeline                                            |

| 13 |                                             |                                                                   | processing");                                                       |

| 14 |                                             |                                                                   | Webster's New World Dictionary                                      |

| 15 |                                             |                                                                   | of Computer Terms (1983), p.193 ("pipelining");                     |

| 16 |                                             |                                                                   | U.S. Patent No. 5,798,770 to                                        |

|    |                                             |                                                                   | Baldwin at 5:15-25;                                                 |

| 17 |                                             |                                                                   | U.S. Patent No. 6,628,243 to Lyons at 6:12-55 & Figs. 2-6;          |

| 18 |                                             |                                                                   | U.S. Patent No. 7,054,867 to                                        |

| 19 |                                             |                                                                   | Bosley at 4:49-55, 5:22-27;                                         |

|    |                                             |                                                                   | U.S. Patent No. 6,489,953 to Chen at 3:16-33                        |

| 20 |                                             |                                                                   | Chen at 3.10-33                                                     |

| 21 |                                             |                                                                   | Declaration of Prof. K.K.                                           |

| 22 |                                             |                                                                   | Ramakrishnan                                                        |

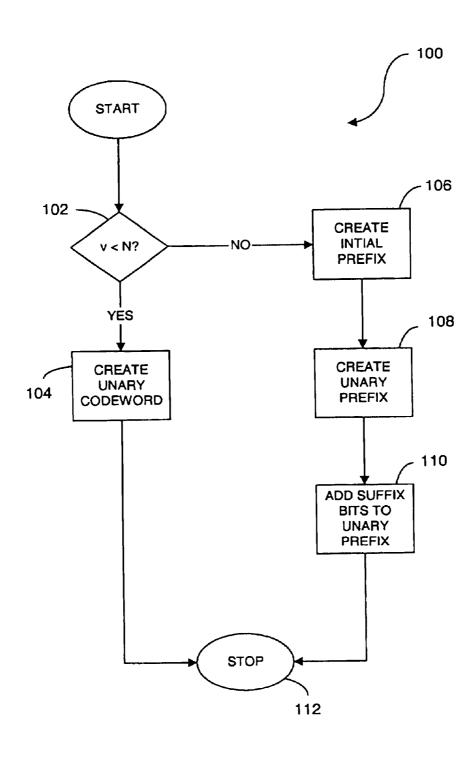

| 23 | "means for                                  | <b>Proposed Construction</b>                                      | Proposed Construction                                               |

| 24 | determining if a code symbol index value is | Governed by 35 U.S.C. § 112(6).                                   | Function: determining if a code                                     |

| 25 | less than a threshold                       |                                                                   | symbol index value is less than a                                   |

|    | value" ('387 Patent,                        | Function: determining if a code symbol index value is less than a | threshold value                                                     |

| 26 | Claim 3)                                    | threshold value                                                   | Structure: binarization module 62                                   |

| 27 |                                             |                                                                   | and step 102 of Figure 4 as                                         |

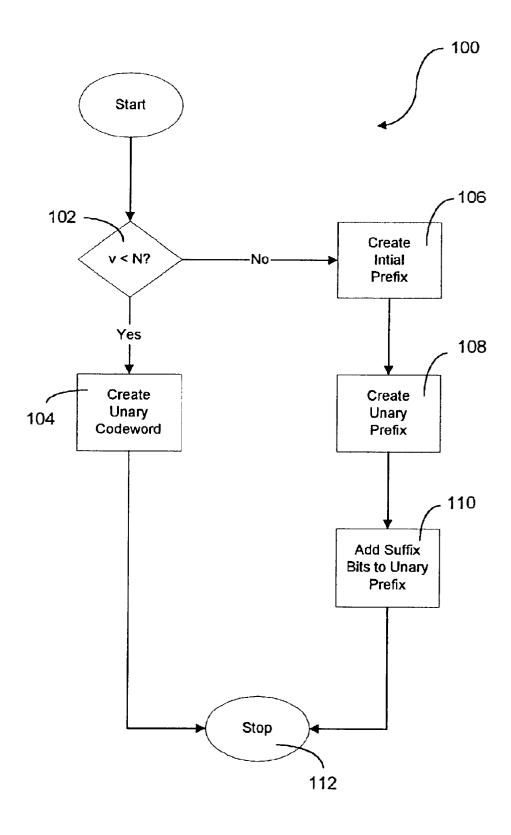

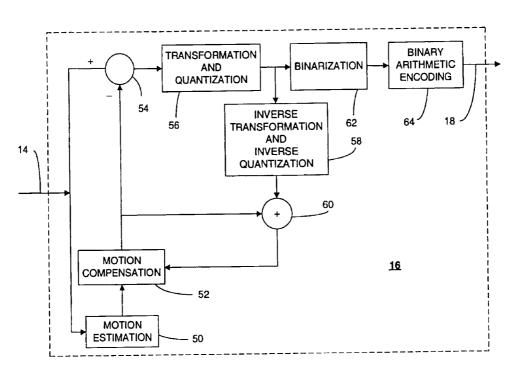

| 28 |                                             | Structure is disclosed in Fig. 2,                                 | described at 7:46 and 7:63-66                                       |

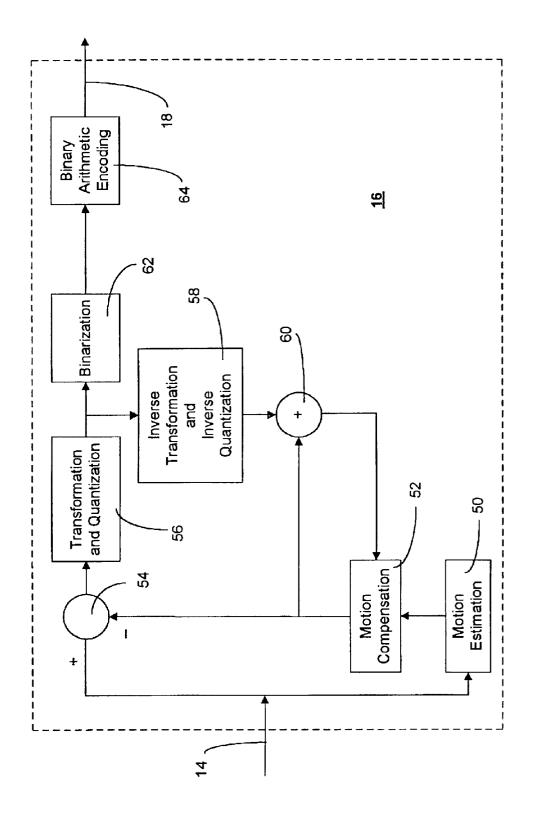

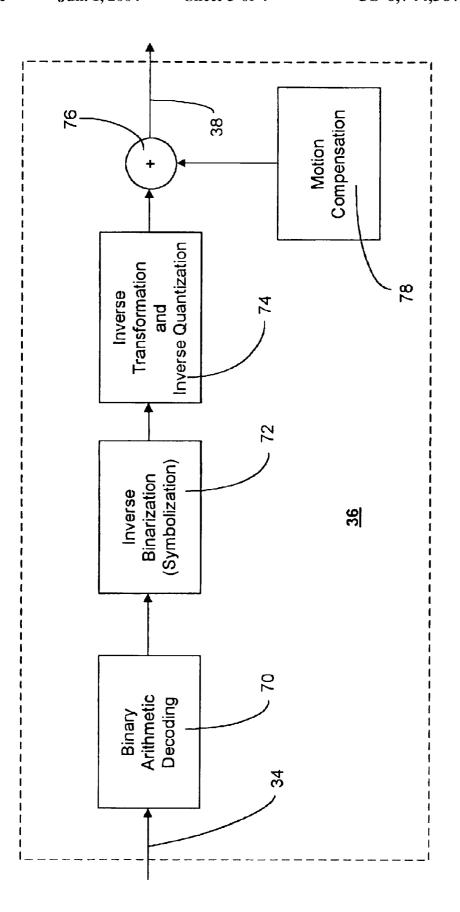

| 1        |                                        | which describes an encoder, and in particular binarization block 62  | Intrinsic and Extrinsic                                           |

|----------|----------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|

| 2        |                                        | in conjunction with Fig. 4, and                                      | Evidence                                                          |

| 3        |                                        | Fig. 4, step 102, Col. 4, lines 1-                                   | 1:6-11                                                            |

|          |                                        | 13, Tables 3 and 4, Col. 6, line 26                                  | 2:15-34                                                           |

| 4        |                                        | through Col. 8, line 23; and Claim                                   | 4:01-05                                                           |

| 5        |                                        | 1.                                                                   | 6:26-8:10<br>Fig. 2                                               |

|          |                                        | Intrinsic and Extrinsic                                              | Fig. 4.                                                           |

| 6        |                                        | Evidence                                                             | 1 - 25                                                            |

| 7        |                                        | See e.g., '387 patent at: 4:1-13; 6:26–8:23; Tables 3-4; Figs. 2, 4; | Prior claim construction briefing (including extrinsic evidence   |

| 8        |                                        | Claims 1-2.                                                          | cited therein) from IPR 2017-                                     |

| 9        |                                        | Dr. Richardson may provide                                           | 00963; IPR 2017-01181.                                            |

| 10       |                                        | expert testimony regarding the                                       | Prior claim construction briefing (including extrinsic evidence   |

| 11       |                                        | level of skill of a person having ordinary skill in the art for the  | cited therein) from IPR 2017-                                     |

| 12       |                                        | field of the '387 Patent, the meaning of this term, binarization     | 00963; IPR 2017-01181;<br>Broadcom Corp v. Amazon (16-            |

| 13       |                                        | modules within encoders, as well                                     | cv-1774) (C.D. Cal); Broadcom                                     |

| 14       |                                        | as rebuttal testimony (if appropriate).                              | Corp v. Sony Corp (16-cv-1052)<br>(C.D. Cal.); Avago Technologies |

| 15       |                                        | appropriate).                                                        | General IP (Singapore) Pte. Ltd.                                  |

|          |                                        |                                                                      | v. ASUSTeK Computer, Inc. et al. (No. 3:15-cv-04525) (N.D.        |

| 16       |                                        |                                                                      | Cal.)                                                             |

| 17       |                                        |                                                                      | Expert testimony of Prof. Michael                                 |

| 18<br>19 |                                        |                                                                      | Orchard regarding the understanding of a person of                |

|          |                                        |                                                                      | ordinary skill regarding                                          |

| 20       |                                        |                                                                      | corresponding structure and the intrinsic evidence, technical     |

| 21       |                                        |                                                                      | background, and rebuttal of any                                   |

| 22       |                                        |                                                                      | incorrect positions or expert                                     |

| 23       | "means for                             | <b>Proposed Construction</b>                                         | testimony asserted by Broadcom. <b>Proposed Construction</b>      |

|          | constructing a                         | 210poseu Combiluedon                                                 | 210posea Constituction                                            |

| 24       | codeword using a                       | Governed by 35 U.S.C. § 112(6).                                      | Function: constructing a                                          |

| 25       | unary binarization if said code symbol | Function: constructing a                                             | codeword using a unary binarization if said code symbol           |

| 26       | index value is less                    | codeword using a unary                                               | index value is less than said                                     |

| 27       | than a threshold                       | binarization if said code symbol index value is less than said       | threshold value                                                   |

| 28       | value" ('387 Patent,<br>Claim 3)       | threshold value                                                      |                                                                   |

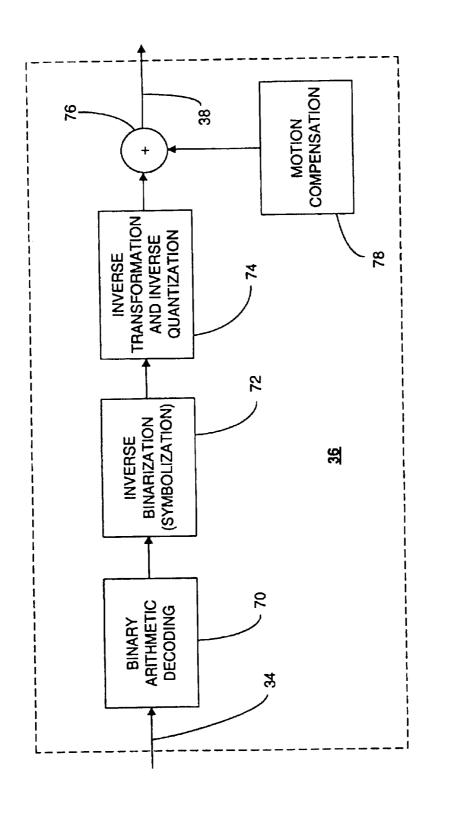

1 Structure: binarization module 62 Structure is disclosed in Fig. 2, and steps 102 and 104 of Figure 4 2 which describes an encoder, and as described at 7:46-47 and 7:61in particular binarization block 62 8:1 3 in conjunction with Fig. 4, and Fig. 4, steps 102, 104 and 112, 4 **Intrinsic and Extrinsic** Col. 4, lines 1-13, Tables 3 and 4, **Evidence** 5 Col. 6, line 26 through Col. 8, 1:6-11 line 23; and Claim 1. 2:15-34 6 4:01-05 **Intrinsic and Extrinsic** 7 6:26-8:10 Evidence Fig. 2 8 Fig. 4. See e.g., '387 patent at: 4:1-13; 9 4:52-54; 6:26-8:23; Tables 3-4; Prior claim construction briefing Figs. 2, 4; Claims 1-2. (including extrinsic evidence 10 cited therein) from IPR 2017-11 Dr. Richardson may provide 00963; IPR 2017-01181. expert testimony regarding the 12 level of skill of a person having Prior claim construction briefing ordinary skill in the art for the (including extrinsic evidence 13 field of the '387 Patent, the cited therein) from IPR 2017-14 00963; IPR 2017-01181; meaning of this term, binarization Broadcom Corp v. Amazon (16modules within encoders, as well 15 cv-1774) (C.D. Cal); Broadcom as rebuttal testimony (if Corp v. Sony Corp (16-cv-1052) appropriate). 16 (C.D. Cal.); Avago Technologies 17 General IP (Singapore) Pte. Ltd. v. ASUSTeK Computer, Inc. et 18 al. (No. 3:15-cv-04525) (N.D. Cal.) 19 Expert testimony of Prof. Michael 20 Orchard regarding the 21 understanding of a person of ordinary skill regarding 22 corresponding structure and the intrinsic evidence, technical 23 background, and rebuttal of any 24 incorrect positions or expert testimony asserted by Broadcom. 25 A. Moffat et al., Compression and 26 Coding Algorithms, Kluwer 27 Academic Publishers (Mar. 31, 2002) at Ch. 3 28

| 1  |                                       |                                                                     |                                                                     |

|----|---------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| 2  | "means for                            | Proposed Construction                                               | Proposed Construction                                               |

| 3  | constructing a codeword using a       | Governed by 35 U.S.C. § 112(6).                                     | Function: constructing a                                            |

|    | exp-Golomb                            |                                                                     | codeword using a exp-Golomb                                         |

| 4  | binarization if said                  | Function: constructing a codeword using a exp-Golomb                | binarization if said code symbol                                    |

| 5  | code symbol index value is [not] less | binarization if said code symbol                                    | index value is [not] less than said threshold value                 |

| 6  | than a threshold                      | index value is not less than said threshold value                   |                                                                     |

| 7  | value" ('387 Patent,<br>Claim 3)      |                                                                     | Structure: binarization module 62                                   |

| 8  |                                       | Structure is disclosed in Fig. 2, which describes an encoder, and   | and steps 106, 108, and 110 of                                      |

| 9  |                                       | in particular binarization block 62 in conjunction with Fig. 4, and | Figure 4 as described at 7:49-60 and 8:1-8:10.                      |

| 10 |                                       | Fig. 4, steps 102, 106, 108, 110, 112; Col. 4, lines 1-13, Tables 3 | Intrinsic and Extrinsic                                             |

| 11 |                                       | and 4, Col. 6, line 26 through Col.                                 | <b>Evidence</b>                                                     |

| 12 |                                       | 8, line 23; and Claims 1-2.                                         | 1:6-11                                                              |

| 13 |                                       | Intrinsic and Extrinsic                                             | 2:15-34<br>4:01-05                                                  |

| 13 |                                       | <b>Evidence</b>                                                     | 5:54-67                                                             |

| 14 |                                       |                                                                     | 6:26-8:10                                                           |

| 15 |                                       | See e.g., '387 patent at: 4:1–13;                                   | Fig. 2                                                              |

|    |                                       | 4:52–54; 6:26–8:23; Tables 3-4; Figs. 2, 4; Claims 1-2.             | Fig. 4                                                              |

| 16 |                                       | Dr. Richardson may provide                                          | Prior claim construction briefing                                   |

| 17 |                                       | expert testimony regarding the                                      | (including extrinsic evidence                                       |

| 18 |                                       | level of skill of a person having ordinary skill in the art for the | cited therein) from IPR 2017-<br>00963; IPR 2017-01181.             |

| 19 |                                       | field of the '387 Patent, the                                       |                                                                     |

| 20 |                                       | meaning of this term, binarization modules within encoders, as well | Prior claim construction briefing (including extrinsic evidence     |

| 21 |                                       | as rebuttal testimony (if                                           | cited therein) from IPR 2017-                                       |

|    |                                       | appropriate).                                                       | 00963; IPR 2017-01181;<br>Broadcom Corp v. Amazon (16-              |

| 22 |                                       |                                                                     | cv-1774) (C.D. Cal); Broadcom                                       |

| 23 |                                       |                                                                     | Corp v. Sony Corp (16-cv-1052)                                      |

| 24 |                                       |                                                                     | (C.D. Cal.); Avago Technologies<br>General IP (Singapore) Pte. Ltd. |

| 25 |                                       |                                                                     | v. ASUSTeK Computer, Inc. et                                        |

| 26 |                                       |                                                                     | al. (No. 3:15-cv-04525) (N.D. Cal.)                                 |

| 27 |                                       |                                                                     | Potential expert testimony of                                       |

| 28 |                                       |                                                                     | Prof. Michael Orchard regarding                                     |

| 1 2 |                       |                                                                                                 | the understanding of a person of ordinary skill regarding          |

|-----|-----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 3   |                       |                                                                                                 | corresponding structure and the intrinsic evidence, technical      |

| 4   |                       |                                                                                                 | background, and rebuttal of any incorrect positions or expert      |

| 5   |                       |                                                                                                 | testimony asserted by Broadcom.                                    |

| 6   |                       |                                                                                                 | Teuhola, A Compression Method                                      |

| 7   |                       |                                                                                                 | for Clustered Bit-Vectors, Information Processing Letters,         |

| 8   |                       |                                                                                                 | Vol. 7, No. 6 (Oct. 1978) at 1-4;                                  |

| 9   |                       |                                                                                                 | D. Marpe et al., Improved CABAC, VCEG-O18 (Dec. 4,                 |

| 10  |                       |                                                                                                 | 2001) at 1–2;<br>U.S. Patent No. 6,304,607 to                      |

| 11  |                       |                                                                                                 | Talluri et al. at 4:43-60, 5:08-                                   |

| 12  |                       |                                                                                                 | 6:14, Table 1, Table 2; P. Howard, Interleaving Entropy            |

| 13  |                       |                                                                                                 | Codes, IEEE (June 11, 1997) at                                     |

| 14  |                       |                                                                                                 | 45–46, 48; A. Moffat et al., Compression and                       |

| 15  |                       |                                                                                                 | Coding                                                             |

| 16  |                       |                                                                                                 | Algorithms, Kluwer Academic Publishers (Mar. 31, 2002) at Ch.      |

| 17  | '663 Patent, Claim 12 | <b>Proposed Construction:</b>                                                                   | 3. Proposed Construction:                                          |

| 18  | (Entire Claim)        | The claim should be given its                                                                   | Steps recited within this claim                                    |

| 19  |                       | plain and ordinary meaning, in                                                                  | must be performed in order                                         |

| 20  |                       | the context of the patent. No further construction is necessary regarding order of limitations. | Intrinsic Evidence:                                                |

| 21  |                       |                                                                                                 | '663 Patent at Abstract, Figs. 4-6,                                |

| 22  |                       | Intrinsic Evidence:                                                                             | 1:37-2:33, 3:10-20, 4:46-7:12, 7:30-10:3; '387 Patent at           |

| 23  |                       | '663 patent at: 1:38–62, 3:21–39, 4:42–50, 5:41–54, 6:24–28, 6:44–                              | Abstract, Fig. 4, 1:36-2:34, 3:7-18, 4:52-8:10; '663 File History: |

| 24  |                       | 7:13; Fig. 4; Tables 1 and 2;                                                                   | Non-final Rejection dated Dec. 2,                                  |

| 25  |                       | Claims 1, 11–13, 18–19, 21.                                                                     | 2004 at 2-5; '663 File History:<br>Amendment dated Mar. 4, 2005    |

| 26  |                       |                                                                                                 | at 4, 6-7, 9, 11-19.                                               |

| 27  |                       |                                                                                                 | Prior claim construction briefing                                  |

| 28  |                       |                                                                                                 | (including extrinsic evidence                                      |

| 1  |                                         |                                                                      | cited therein) from ITC No. 337-                                  |

|----|-----------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|

| 2  |                                         |                                                                      | TA-837, IPR 2021-00468, IPR 2017-00964, IPR 2017-01182.           |

| 3  |                                         |                                                                      | Extrinsic Evidence:                                               |

| 4  |                                         |                                                                      | Extrinsic Evidence:                                               |

| 5  |                                         |                                                                      | Prior claim construction briefing (including extrinsic evidence   |

| 6  |                                         |                                                                      | cited therein) from ITC No. 337-                                  |

| 7  |                                         |                                                                      | TA-837, IPR 2021-00468, IPR 2017-00964, IPR 2017-01182,           |

|    |                                         |                                                                      | Barnes & Noble, Inc. v. LSI                                       |

| 8  |                                         |                                                                      | Corp., (No. 3:11-cv-2709) (N.D. Cal.); Avago Technologies         |

| 9  |                                         |                                                                      | General IP (Singapore) Pte. Ltd.                                  |

| 10 |                                         |                                                                      | v. ASUSTeK Computer, Inc. et al. (No. 3:15-cv-04525) (N.D. Cal.), |

| 11 |                                         |                                                                      | Broadcom Corp. et al v.                                           |

| 12 |                                         |                                                                      | Amazon.com, Inc. et al. (No. 8:16-cv-01774-JVS-JCG) (C.D.         |

| 13 |                                         |                                                                      | Cal.), Broadcom Corp. et al v.                                    |

| 14 |                                         |                                                                      | Sony Corp. et al. (No. 8:16-cv-01052-JVS-JCG) (C.D. Cal.)         |

| 15 |                                         |                                                                      | Lowell Winger, JVT-C162 (May                                      |

| 16 |                                         |                                                                      | 2, 2002); "Draft ITU-T                                            |

| 17 |                                         |                                                                      | Recommendation H.264," Joint Video Team, JVT-C167 (May 10,        |

|    |                                         |                                                                      | 2002); U.S. Patent No. 6,236,960                                  |

| 18 |                                         |                                                                      | at Figs. 5 & 7, 11:11–12:30, 13:15–54;                            |

| 19 |                                         |                                                                      | Expert testimony of Prof. Michael                                 |

| 20 |                                         |                                                                      | Orchard regarding the understanding of a person of                |

| 21 |                                         |                                                                      | ordinary skill regarding the                                      |

| 22 |                                         |                                                                      | intrinsic evidence, technical background, and rebuttal of any     |

| 23 |                                         |                                                                      | incorrect positions or expert testimony asserted by Broadcom.     |

| 24 |                                         |                                                                      |                                                                   |

| 25 | "a fourth pattern in said first portion | <b>Proposed Construction:</b>                                        | <b>Proposed Construction:</b>                                     |

| 26 | based on said index                     | Plain and ordinary meaning. No                                       | Indefinite                                                        |

| 27 | value in response to said index value   | construction of "[generating] a fourth pattern in said first portion | Intrinsic Evidence:                                               |

| 28 |                                         | based on said index value in                                         |                                                                   |

| 1  | being below said                        | response to said index value                                    | '663 Patent at Abstract, Figs. 3-6,                               |

|----|-----------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|

| 2  | threshold"                              | being below said threshold" needed.                             | 2:15-33, 3:10-20, 4:1-12; 4:13-<br>33; 4:46-7:12; 7:30-10:3       |

| 3  | ('663 Patent, Claim                     | needed.                                                         | 35, 4.40-7.12, 7.30-10.5                                          |

|    | 13)                                     | Intrinsic Evidence:                                             | Prior claim construction briefing                                 |

| 4  |                                         | '663 patent at: Tables 3–4, 6:50–                               | (including extrinsic evidence cited therein) from ITC No. 337-    |

| 5  |                                         | 7:13.                                                           | TA-837, IPR 2021-00468, IPR                                       |

| 6  |                                         | D. C. C. D. C.                                                  | 2017-00964, IPR 2017-01182                                        |

| 7  |                                         | <b>Extrinsic Evidence:</b>                                      | Extrinsic Evidence:                                               |

|    |                                         | Declaration of Dr. Iain                                         | Extraste Evidence.                                                |

| 8  |                                         | Richardson                                                      | Prior claim construction briefing                                 |

| 9  |                                         |                                                                 | (including extrinsic evidence cited therein) from ITC No. 337-    |

| 10 |                                         |                                                                 | TA-837, IPR 2021-00468, IPR                                       |

| 11 |                                         |                                                                 | 2017-00964, IPR 2017-01182,                                       |

|    |                                         |                                                                 | Barnes & Noble, Inc. v. LSI<br>Corp., (No. 3:11-cv-2709) (N.D.    |

| 12 |                                         |                                                                 | Cal.); Avago Technologies                                         |

| 13 |                                         |                                                                 | General IP (Singapore) Pte. Ltd.                                  |

| 14 |                                         |                                                                 | v. ASUSTeK Computer, Inc. et al. (No. 3:15-cv-04525) (N.D. Cal.), |

| 15 |                                         |                                                                 | Broadcom Corp. et al v.                                           |

|    |                                         |                                                                 | Amazon.com, Inc. et al. (No. 8:16-cv-01774-JVS-JCG) (C.D.         |

| 16 |                                         |                                                                 | Cal.), Broadcom Corp. et al v.                                    |

| 17 |                                         |                                                                 | Sony Corp. et al. (No. 8:16-cv-                                   |

| 18 |                                         |                                                                 | 01052-JVS-JCG) (C.D. Cal.).                                       |

| 19 |                                         |                                                                 | Lowell Winger, JVT-C162 (May                                      |

|    |                                         |                                                                 | 2, 2002); "Draft ITU-T                                            |

| 20 |                                         |                                                                 | Recommendation H.264," Joint Video Team, JVT-C167 (May 10,        |

| 21 |                                         |                                                                 | 2002)                                                             |

| 22 |                                         |                                                                 | Declaration of Prof. Michael                                      |

| 23 |                                         |                                                                 | Orchard                                                           |

|    | " 1 · · · · · · · · · · · · · · · · · · | D IC /                                                          | D IC ( )                                                          |

| 24 | "wherein said [second/third] portion    | <b>Proposed Construction:</b>                                   | Proposed Construction:                                            |

| 25 | is void in response to                  | Plain and ordinary meaning,                                     | Indefinite                                                        |

| 26 | said index value                        | which in the context of the patent                              | Intrinsia Evidanas                                                |

| 27 | being below said threshold"             | is "wherein said [second/third] portion does not contribute any | Intrinsic Evidence:                                               |

|    |                                         | bins to the codeword in response                                |                                                                   |

| 28 |                                         |                                                                 |                                                                   |

| 1 2 | ('663 Patent, Claims 18, 19)          | to said index value being below said threshold."                  | '663 Patent at Abstract, Figs. 3-6,<br>2:15-33, 3:10-20, 4:1-12; 4:13-<br>33; 4:46-7:12; 7:30-10:3 |

|-----|---------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 3   |                                       | Intrinsic Evidence:                                               | 33, 107.112, 7.30 10.3                                                                             |

|     |                                       |                                                                   | Prior claim construction briefing                                                                  |

| 4   |                                       | '663 patent at: Tables 3–4, 6:50–7:13.                            | (including extrinsic evidence cited therein) from ITC No. 337-                                     |

| 5   |                                       | 7.13.                                                             | TA-837, IPR 2021-00468, IPR                                                                        |

| 6   |                                       | <b>Extrinsic Evidence:</b>                                        | 2017-00964, IPR 2017-01182.                                                                        |

| 7   |                                       | Void, MERRIAM-WEBSTER'S                                           | Extrinsic Evidence:                                                                                |

| 8   |                                       | COLLEGIATE DICTIONARY                                             | B. I                                                                                               |

|     |                                       | (10th ed. 1993).                                                  | Prior claim construction briefing (including extrinsic evidence                                    |

| 9   |                                       | Void, THE AMERICAN                                                | cited therein) from ITC No. 337-                                                                   |

| 10  |                                       | HERITAGE DICTIONARY OF THE ENGLISH LANGUAGE                       | TA-837, IPR 2021-00468, IPR 2017-00964, IPR 2017-01182,                                            |

| 11  |                                       | (4th ed. 2000).                                                   | Barnes & Noble, Inc. v. LSI                                                                        |

| 12  |                                       |                                                                   | Corp., (No. 3:11-cv-2709) (N.D.                                                                    |

|     |                                       | Declaration of Dr. Iain Richardson                                | Cal.); Avago Technologies<br>General IP (Singapore) Pte. Ltd.                                      |

| 13  |                                       | Richardson                                                        | v. ASUSTeK Computer, Inc. et al.                                                                   |

| 14  |                                       |                                                                   | (No. 3:15-cv-04525) (N.D. Cal.),                                                                   |

| 15  |                                       |                                                                   | Broadcom Corp. et al v.<br>Amazon.com, Inc. et al. (No.                                            |

| 16  |                                       |                                                                   | 8:16-cv-01774-JVS-JCG) (C.D.                                                                       |

|     |                                       |                                                                   | Cal.), Broadcom Corp. et al v.<br>Sony Corp. et al. (No. 8:16-cv-                                  |

| 17  |                                       |                                                                   | 01052-JVS-JCG) (C.D. Cal.).                                                                        |

| 18  |                                       |                                                                   | Lawall Winson, IVT C162 (May                                                                       |

| 19  |                                       |                                                                   | Lowell Winger, JVT-C162 (May 2, 2002); "Draft ITU-T                                                |

| 20  |                                       |                                                                   | Recommendation H.264," Joint                                                                       |

| 21  |                                       |                                                                   | Video Team, JVT-C167 (May 10, 2002);                                                               |

|     |                                       |                                                                   | 2002),                                                                                             |

| 22  |                                       |                                                                   | Declaration of Prof. Michael Orchard                                                               |

| 23  |                                       |                                                                   |                                                                                                    |

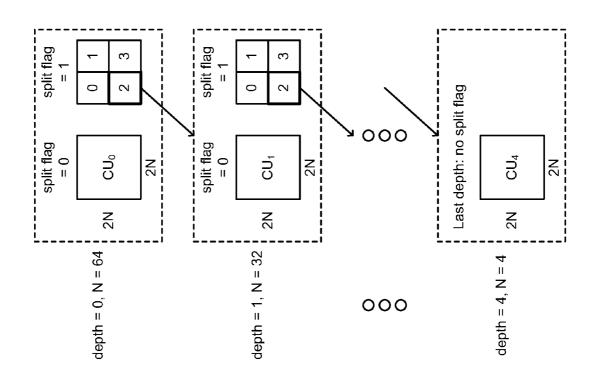

| 24  | "wherein the second syntax element    | <b>Proposed Construction:</b>                                     | <b>Proposed Construction:</b>                                                                      |

| 25  | specifies the PU                      | Plaintiffs object to Defendant's                                  | Indefinite                                                                                         |

| 26  | partition mode for the                | request to construe this entire                                   |                                                                                                    |

| 27  | selected CU, wherein the PU partition | phrase without specifying which portion(s)/element(s) it contends | Intrinsic Evidence:                                                                                |

|     | mode is based on a                    | require construction.                                             | 17:19-23                                                                                           |

| 28  |                                       |                                                                   |                                                                                                    |

|          | size N×N PU when                            |                                    | 18:12-54                         |

|----------|---------------------------------------------|------------------------------------|----------------------------------|

|          | the selected CU is a                        | No construction necessary.         | 19:62-20:18                      |

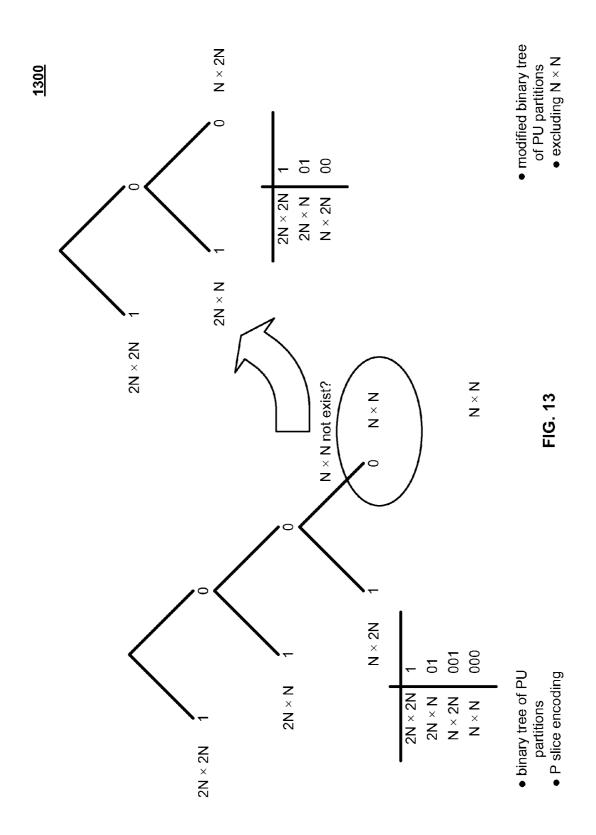

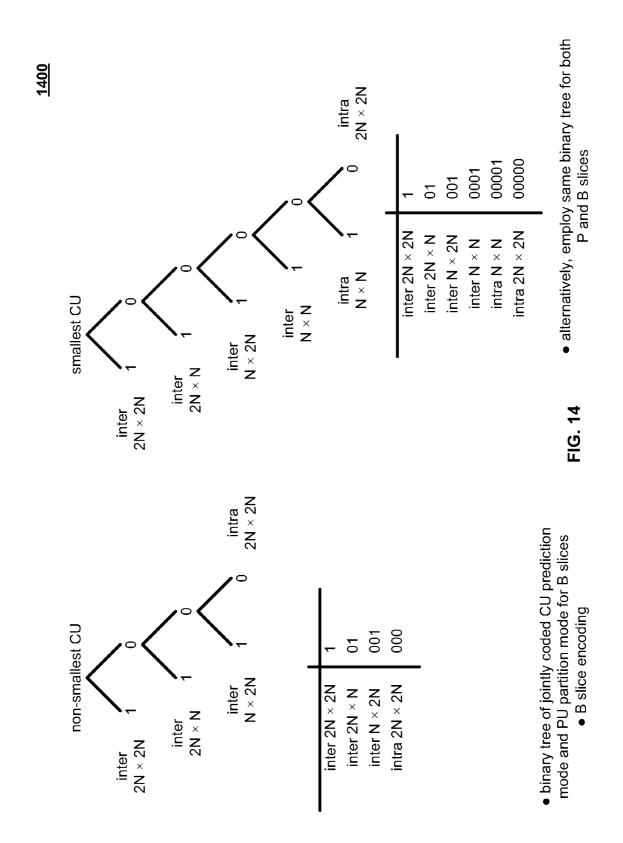

| 2        | smallest CU (SCU)                           |                                    | Figs. 12, 13, 14 & 15            |

| 3        | of the plurality of CUs and is based on     | Plain and ordinary meaning.        | Claims 2 &17                     |

| ŀ        | a different size PU<br>than the size N×N PU | Intrinsic Evidence:                | <b>Extrinsic Evidence:</b>       |

| 5        | when the selected CU                        | '283 patent at: 16:41–19:12, Figs. | Declaration of Dr. Vivienne Sze  |

| )        | is another CU than the SCU of the           | 11–13.                             |                                  |

| ,        | plurality of CUs"                           | Extrinsic Evidence:                |                                  |

| 3        | ('283 Patent, Claims                        | Declaration of Dr. Iain            |                                  |

| ,        | 1, 14)                                      | Richardson                         |                                  |

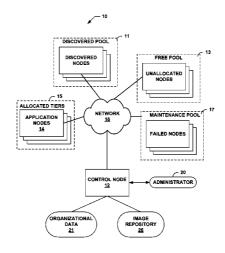

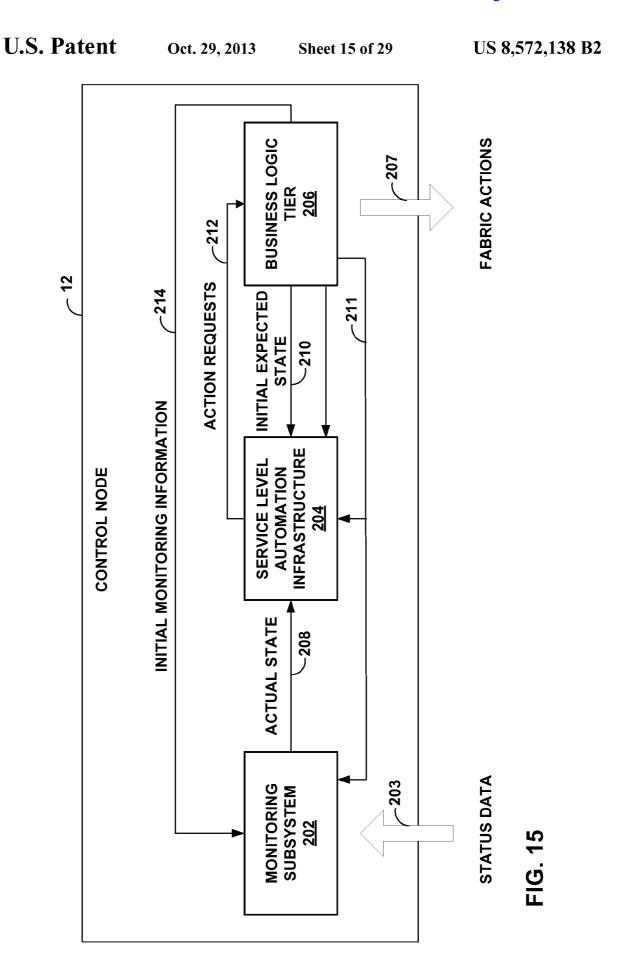

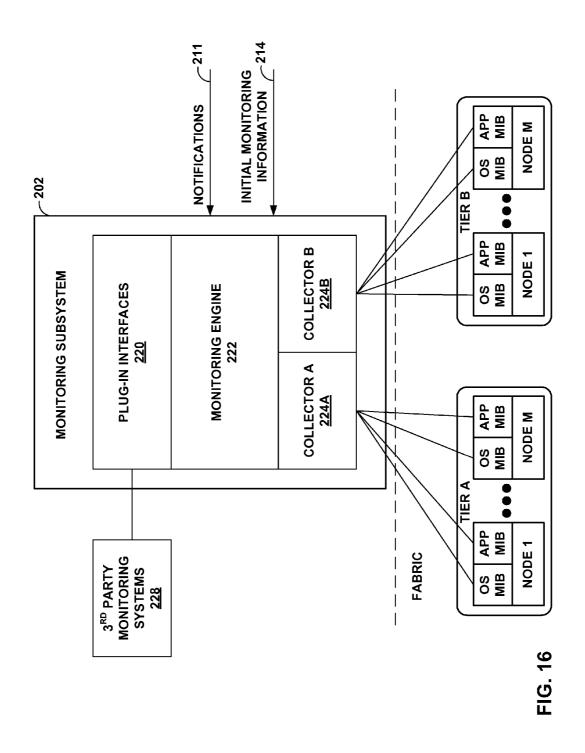

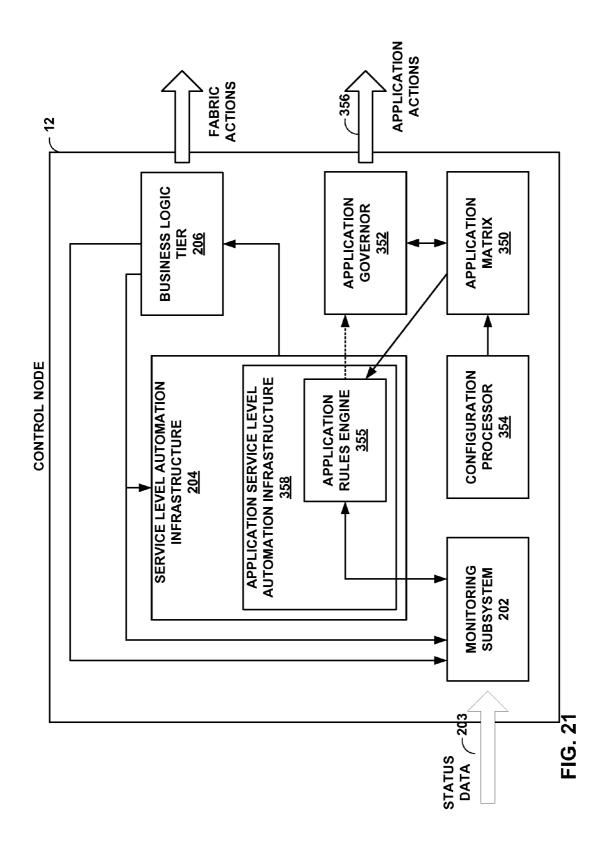

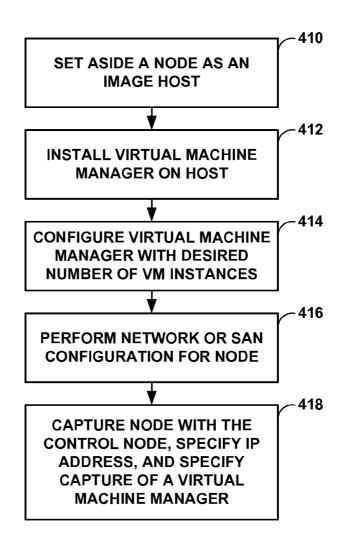

| ,        | "virtual machine manager"                   | <b>Proposed Construction:</b>      | <b>Proposed Construction:</b>    |

|          |                                             | No construction necessary.         | "software program that manages   |

|          | ('138 patent, claims 1, 19)                 | Plain and ordinary meaning.        | one or more virtual machines"    |

| <b>,</b> |                                             | Intrinsic Evidence:                | Intrinsic Evidence:              |

| ŀ        |                                             |                                    | Claim 1                          |

|          |                                             | '138 Patent at 32:60-62.           | 32:59-67<br>33:21-23             |

|          |                                             | Extrinsic Evidence:                | 33:39-41<br>Fig. 24              |

| ,        |                                             | MICROSOFT COMPUTER                 | 8                                |

|          |                                             | DICTIONARY 327 (5th ed. 2002).     |                                  |

|          |                                             | INTRODUCTION TO                    |                                  |

|          |                                             | VMWARE INFRASTRUCTURE              |                                  |

|          |                                             | 44 (2006-2007).                    |                                  |

|          |                                             | MERRIAM-WEBSTER                    |                                  |

|          |                                             | DICTIONARY [706, 1993]             |                                  |

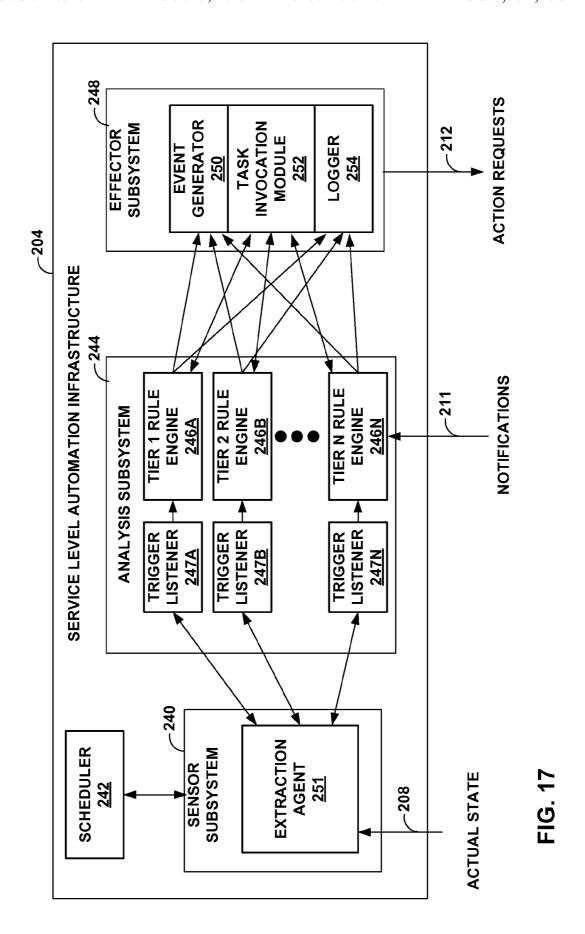

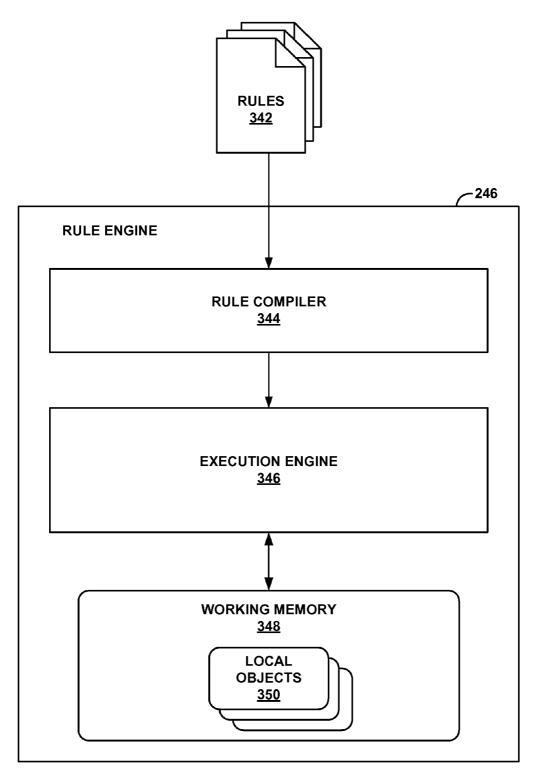

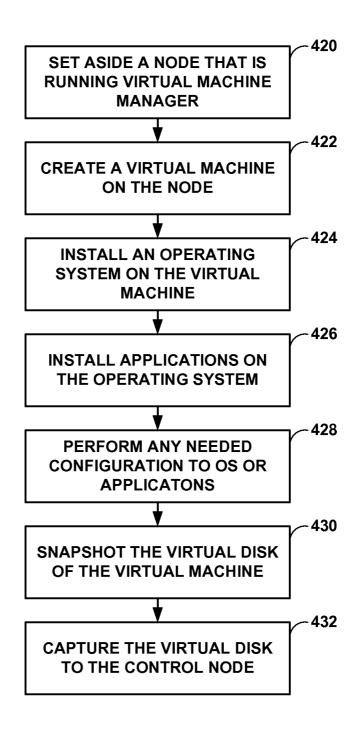

|          | "rules engine"                              | <b>Proposed Construction:</b>      | <b>Proposed Construction:</b>    |

|          | ('138 patent, claims                        | No construction necessary.         | "software that performs logical  |

|          | 11, 14, 19)                                 | Plain and ordinary meaning.        | reasoning using 'if/then' rules" |

| ,        |                                             | , ,                                | Intrinsic Evidence:              |

| - 11     | İ                                           | Intrinsic Evidence:                | İ                                |

| 1        | '138 Patent at 22:56-58; 25:60- | 22:38-49                        |

|----------|---------------------------------|---------------------------------|

|          | 65; 2                           | 22:54-62                        |

| 2        |                                 | 25:60-66                        |

| 3        | <b>Extrinsic Evidence:</b>      | 27:15-34                        |

| ,        |                                 | 27:56-28:11                     |

| 4        | MICROSOFT COMPUTER              | Fig. 20                         |

| 5        | DICTIONARY 193 (5th ed. 2002).  | Extrinsic Evidence              |

| 6        |                                 | Computer Dictionary, Microsoft  |

| ,        |                                 | Press, 2d Ed. (1994) (cross-    |

| <b>'</b> |                                 | referencing "rule-based system" |

| 3        |                                 | with "expert system")           |

| ,        |                                 | Computer Dictionary, Microsoft  |

|          |                                 | Press, 5th Ed. (2002) (cross-   |

| )        |                                 | referencing "rule-based system" |

|          |                                 | with "expert system")           |

# III. IDENTIFICATION OF CASE-DISPOSITIVE TERMS UNDER PATENT L.R. 4–3(a)

# A. Plaintiffs' Position:

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

None of the disputed terms will be case dispositive. Plaintiffs disagree with Defendant's statements in Subparagraph B below regarding the alleged dispositive nature of each of the terms listed with respect to Defendant's alleged non-infringement. Regarding Defendant's statements regarding invalidity, Plaintiffs state only that a finding of indefiniteness as to a claim term applies only to claims including such term and are not dispositive of the case or all claims of a particular patent.

Plaintiffs object to Defendant's attempt to reserve the right to later seek construction of "one or more underutilized computer devices" in the '183 Patent or any other term not set forth in this Joint Statement. Neither party identified "one or more underutilized computer devices" in their Patent L.R. 4-1 or 4-2 disclosures.

# **B.** Defendant's Position:

The following disputed claim terms are dispositive of non-infringement:

• "display pipeline"

- "means for determining if a code symbol index value is less than a threshold value"

- "means for constructing a codeword using a unary binarization if said code symbol index value is less than a threshold value"

- "means for constructing a codeword using a exp-Golomb binarization if said code symbol index value is [not] less than a threshold value"

- Claim 12 (Entire Claim)

- "virtual machine manager"

- "rules engine"

The following disputed claim terms are dispositive of invalidity:

- "wherein the second syntax element specifies the PU partition mode for the selected CU, wherein the PU partition mode is based on a size N×N PU when the selected CU is a smallest CU (SCU) of the plurality of CUs and is based on a different size PU than the size N×N PU when the selected CU is another CU than the SCU of the plurality of CUs"

- "a fourth pattern in said first portion based on said index value in response to said index value being below said threshold"

- "wherein said [second/third] portion is void in response to said index value being below said threshold"

On May 17, 2021, the Patent Trial and Appeals Board issued an institution decision for the '183 patent. The PTAB construed "one or more underutilized computer devices" to mean "one or more computer devices that have a utilization level below, or less than, a specified utilization level." Accordingly, it found that Claim 1 "requires both a determination that 'one or more underutilized computer devices exist on the list of suitable computer devices' and that the 'one or more underutilized computer devices hav[e] a suitable level of utilization for performing the job." IPR2021-00098. This decision is not yet final. Netflix reserves the right to move for leave to supplement its proposed terms for claim construction in light of a final decision.

# IV. ANTICIPATED LENGTH OF CLAIM CONSTRUCTION HEARING

The Parties request that the Court provide three hours for the hearing.

1 V. PROPOSED CLAIM-CONSTRUCTION WITNESSES 2 The parties plan to submit expert declarations with their claim-construction briefs as 3 outlined in Section II above. The parties do not intend to call live witnesses at the claim-4 construction hearing. 5 Dated: May 18, 2021 Respectfully submitted, 6 7 /s/ Richard L. Wynne, Jr. Bruce S. Sostek, admitted pro hac vice 8 bruce.sostek@tklaw.com 9 Richard L. Wynne, Jr., admitted pro hac vice richard.wynne@tklaw.com 10 Adrienne E. Dominguez, admitted pro hac vice adrienne.dominguez@tklaw.com THOMPSON & KNIGHT LLP 11 One Arts Plaza 12 1722 Routh Street, Suite 1500 Dallas, Texas 75201 13 Telephone:(214) 969-1700 Facsimile: (214) 969-1751 14 John V. Picone III, Bar No. 187226 15 ipicone@hopkinscarley.com HOPKINS & CARLEY 16 A Law Corporation The Letitia Building 17 70 South First Street San Jose, CA 95113-2406 18 mailing address: 19 P.O. Box 1469 San Jose, CA 95109-1469 20 Telephone: (408) 286-9800 Facsimile: (408) 998-4790 21 Attorneys for Plaintiffs 22 COUNSEL FOR BROADCOM CORPORATION and AVAGO 23 TECHNOLOGIES INTERNATIONAL SALES PTE. LIMITED. 24 25 26 27 28

| 1      |           |                                      |

|--------|-----------|--------------------------------------|

| 2      | •         | KER, VAN NEST & PETERS LLP           |

| 3      | Dr. /a/ 9 | Sharif E. Jacob                      |

| 4      | RO        | BERT A. VAN NEST<br>TTHIAS A. KAMBER |

| 5      | PA        | VEN MALHOTRA<br>ARIF E. JACOB        |

| 6<br>7 | THO       | OMAS E. GORMAN<br>WARD A. BAYLEY     |

| 8      |           |                                      |

| 9      |           | orneys for Defendant ΓFLIX, INC.     |

| 10     |           |                                      |

| 11     |           |                                      |

| 12     |           |                                      |

| 13     | 3         |                                      |

| 14     | 1         |                                      |

| 15     | 5         |                                      |

| 16     | 5         |                                      |

| 17     | 7         |                                      |

| 18     | 3         |                                      |

| 19     |           |                                      |

| 20     |           |                                      |

| 21     |           |                                      |

| 22     |           |                                      |

| 23     | 3         |                                      |

| 24     | 1         |                                      |

| 25     | 5         |                                      |

| 26     |           |                                      |

| 27     | 7         |                                      |

| 28     | 3         |                                      |

# Exhibit 1

U.S. Patent No. 8,259,121

# (12) United States Patent

Law et al.

(10) Patent No.:

US 8,259,121 B2

(45) Date of Patent:

Sep. 4, 2012

# (54) SYSTEM AND METHOD FOR PROCESSING DATA USING A NETWORK

(75) Inventors: Patrick Law, Milpitas, CA (US); Darren Neuman, San Jose, CA (US); David Baer, San Jose, CA (US)

Assignee: **Broadcom Corporation**, Irvine, CA

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 1509 days.

Appl. No.: 10/314,525

(22)Filed: Dec. 9, 2002

(65)**Prior Publication Data**

> US 2004/0078418 A1 Apr. 22, 2004

# Related U.S. Application Data

(60) Provisional application No. 60/420,151, filed on Oct. 22, 2002.

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | G06T 1/20  | (2006.01) |

|      | G06F 12/02 | (2006.01) |

|      | G06F 13/28 | (2006.01) |

|      | G06F 3/00  | (2006.01) |

|      | G06K 9/54  | (2006.01) |

- (52) U.S. Cl. ....... 345/506; 345/567; 382/303; 382/304

- Field of Classification Search ...... 345/505, 345/501, 502, 506, 567; 382/303, 304; 710/22, 710/29

See application file for complete search history.

### (56)**References Cited**

# U.S. PATENT DOCUMENTS

|             | 5,638,533 A * | 6/1997  | Law 711/157            |  |  |

|-------------|---------------|---------|------------------------|--|--|

|             | 5,646,693 A * | 7/1997  | Cismas 348/441         |  |  |

|             | 5,822,779 A * | 10/1998 | Intrater et al 711/168 |  |  |

|             | 5,828,903 A * | 10/1998 | Sethuram et al 710/53  |  |  |

|             | 5,841,439 A * | 11/1998 | Pose et al 345/418     |  |  |

|             | 5,987,246 A * | 11/1999 | Thomsen et al 717/109  |  |  |

|             | 6,101,591 A * | 8/2000  | Foster et al 711/219   |  |  |

|             | 6,412,061 B1  | 6/2002  | Dye                    |  |  |

|             | 6,429,902 B1* | 8/2002  | Har-Chen et al 348/518 |  |  |

|             | 6,489,953 B1* | 12/2002 | Chen 345/213           |  |  |

|             | 6,525,738 B1* | 2/2003  | Devins et al 345/553   |  |  |

|             | 6,628,243 B1* | 9/2003  | Lyons et al 345/1.1    |  |  |

|             | 6,636,214 B1* | 10/2003 | Leather et al 345/422  |  |  |

| (Continued) |               |         |                        |  |  |

(Continued)

# FOREIGN PATENT DOCUMENTS

EP 1091318 A2 4/2001 (Continued)

# OTHER PUBLICATIONS

European Patent Office, Communication with European Search Report, in Application No. 03023968.5, dated Oct. 1, 2010, pp. 1-3.

Primary Examiner — Hoang-Vu A Nguyen-Ba (74) Attorney, Agent, or Firm — Thomas, Horstemeyer & Risley LLP.

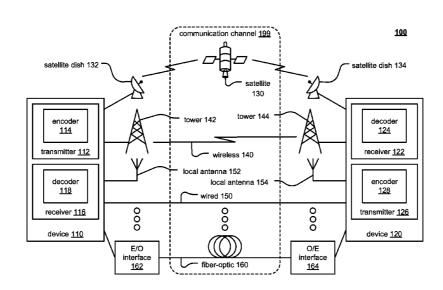

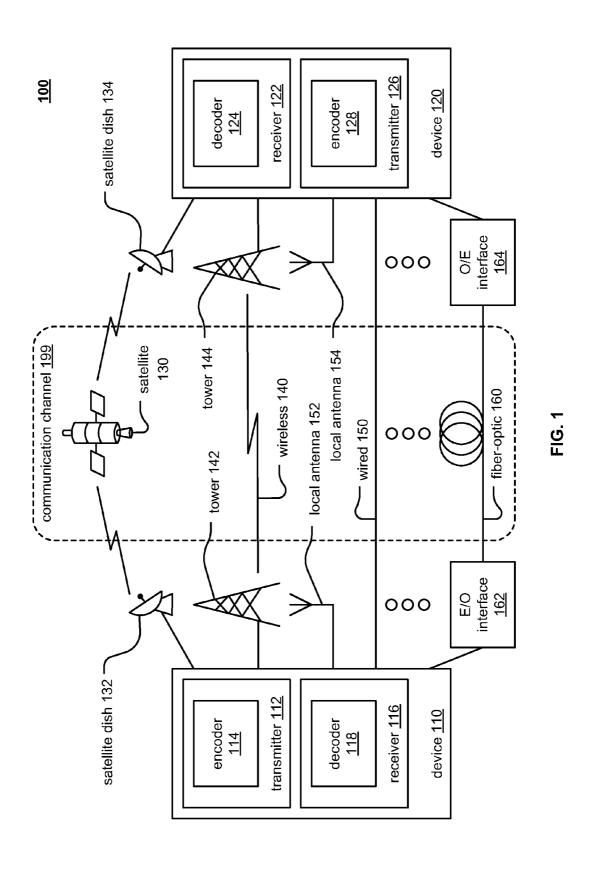

### (57)ABSTRACT

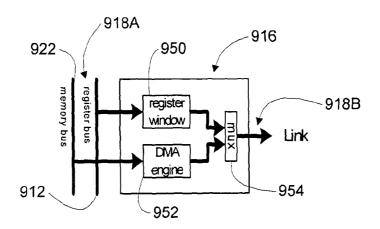

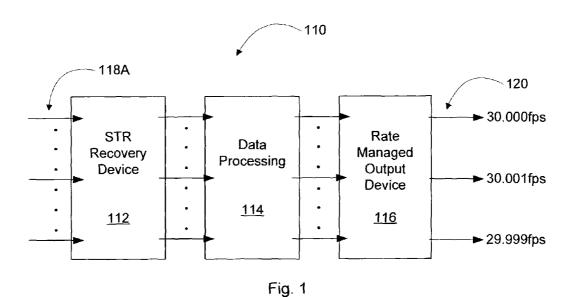

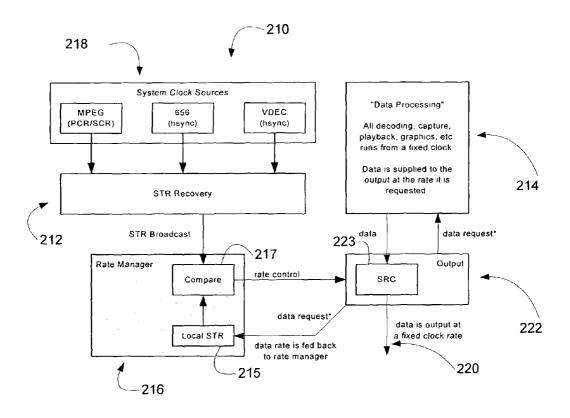

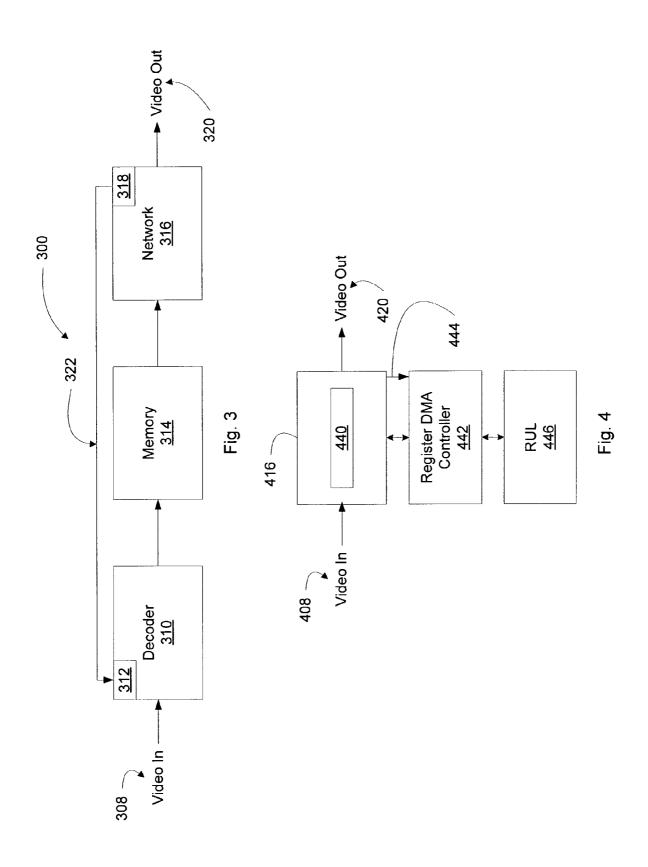

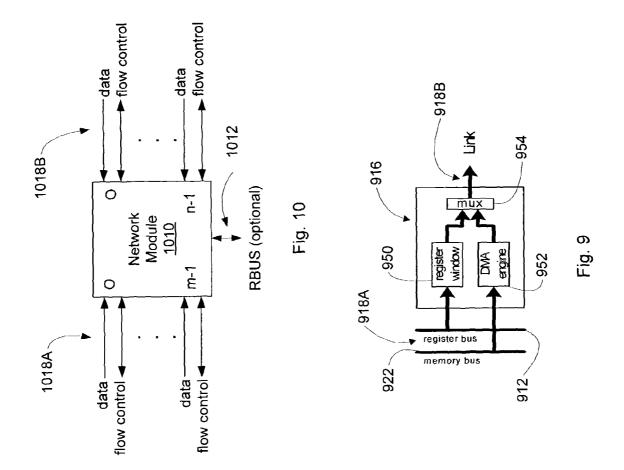

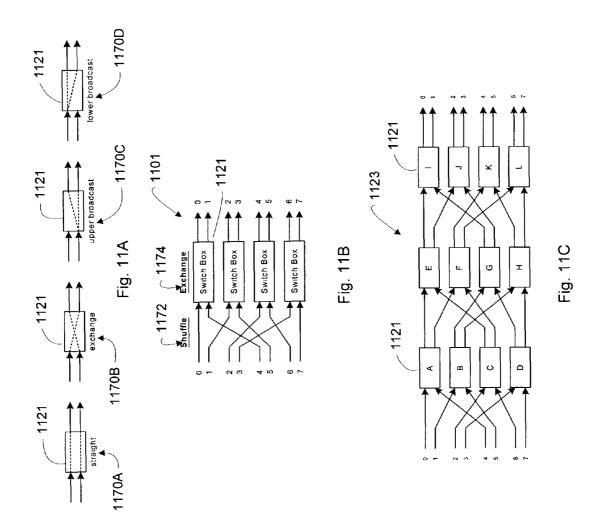

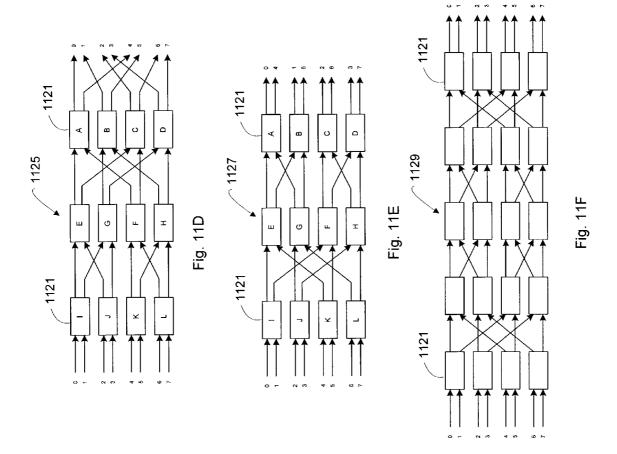

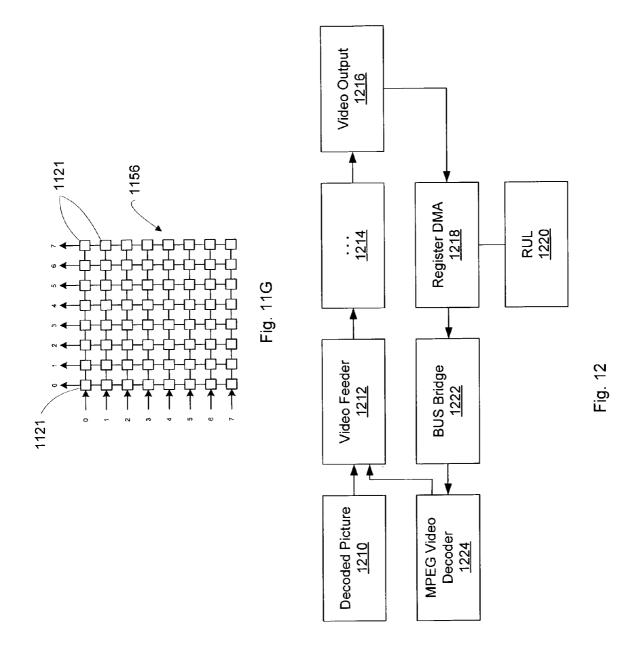

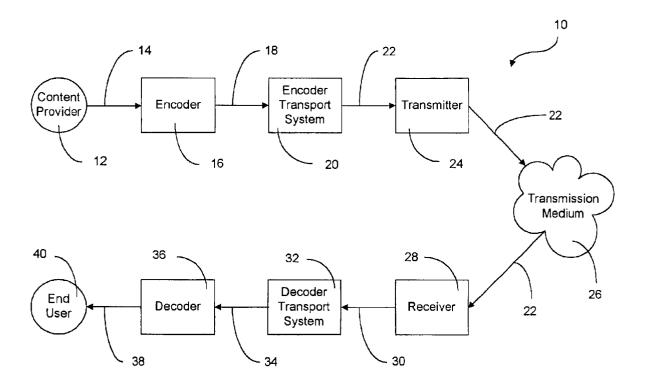

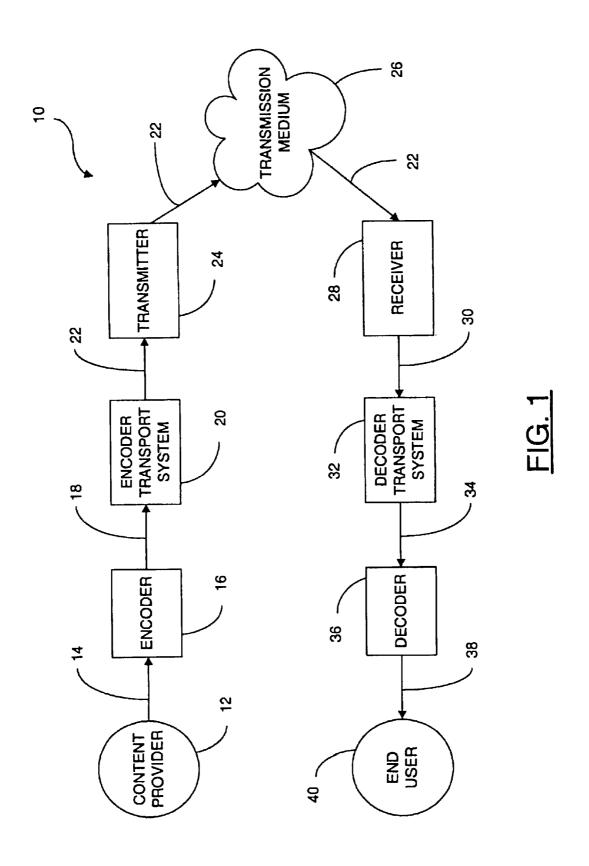

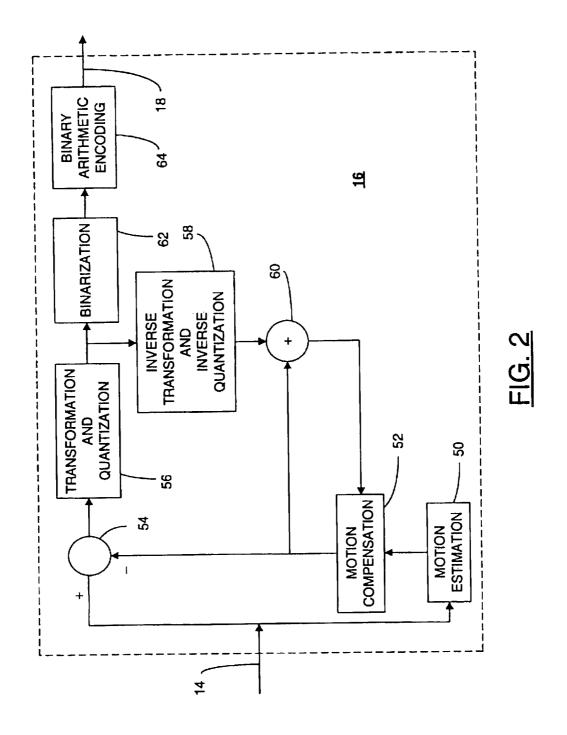

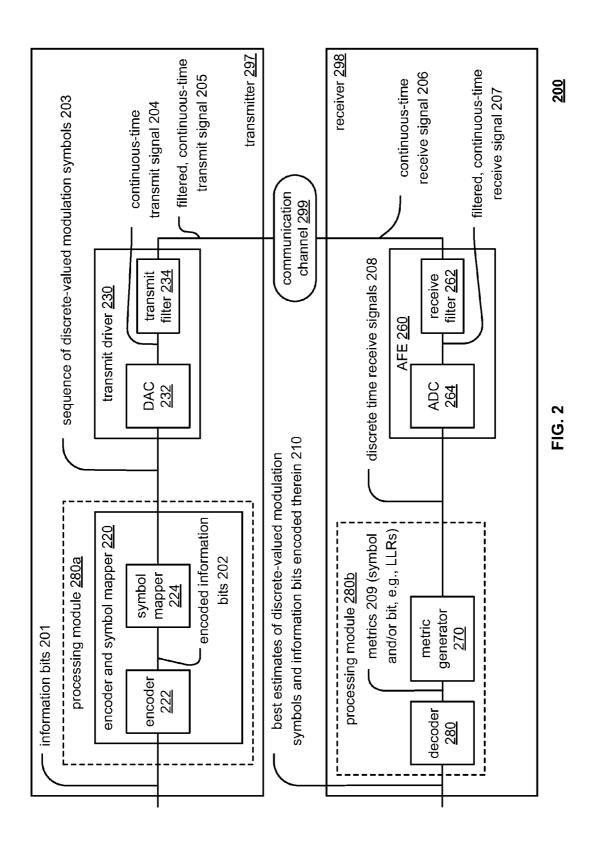

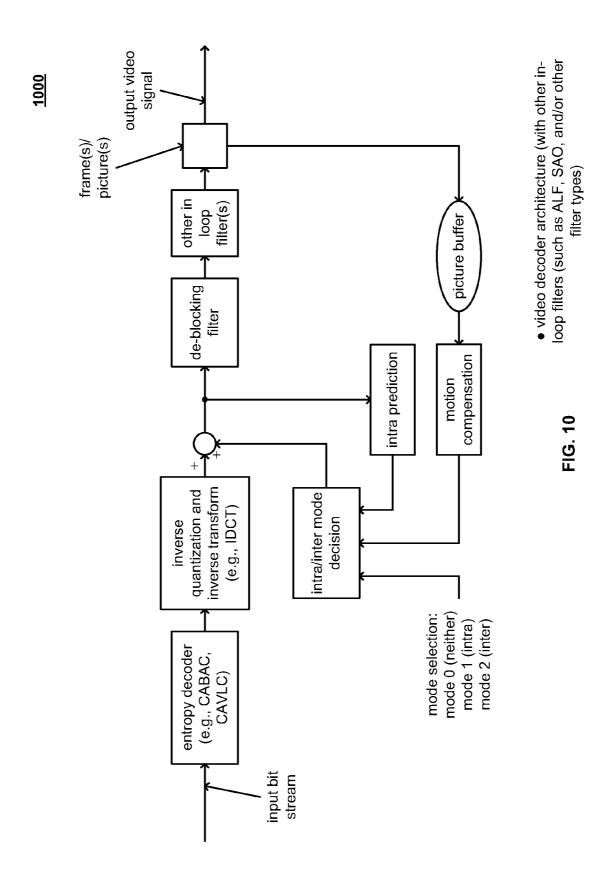

Systems and methods are disclosed for video processing modules. More specifically a network is disclosed for processing data. The network comprises a register DMA controller adapted to support register access and at least one node adapted to the data. At least one link communicates with the node, and is adapted to transmit data and at least one network module communicates with at least the link, and is adapted to route data to at least the link.

# 36 Claims, 11 Drawing Sheets

# Case 3:20-cv-04677-JD Document 112-1 Filed 05/18/21 Page 3 of 23

# **US 8,259,121 B2**Page 2

| 6,700,588 B1* 3/2004 MacInnis et al. 345/629 6,801,591 B1* 10/2004 Frencken 375/373 6,919,896 B2* 7/2005 Sasaki et al. 345/505 7,034,828 B1* 4/2006 Drebin et al. 345/426 7,054,867 B2* 5/2006 Bosley et al. 707/10 WO WC 7,218,676 B2* 5/2007 Kono et al. 375/240.25 WO WC 7,230,651 B2* 6/2007 Schoner et al. 348/500 | REIGN PATENT DOCUMENTS<br>099/13637 A2 3/1999<br>099/52277 A1 10/1999<br>-01/22736 * 3/2001 |