#### IN THE

#### UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

MICROCHIP TECHNOLOGY INCORPORATED; AND MICROSEMI CORPORATION

Petitioners

v.

BELL SEMICONDUCTOR, LLC

Patent Owner

Inter Partes Review Case No. IPR2021-00191

Patent No. 7,221,173

\_\_\_\_

# PETITION FOR INTER PARTES REVIEW UNDER 35 U.S.C. §§ 311-319 AND 37 C.F.R. § 42

Mail Stop Patent Board Patent Trial and Appeal Board P.O. Box 1450 Alexandria, VA 22313-1450

November 16, 2020

# LIST OF EXHIBITS

| 1001 | Bachman et al., U.S. Patent No. 7,221,173 ("the '173 patent")        |

|------|----------------------------------------------------------------------|

| 1002 | Prosecution History File Wrapper of the '173 patent                  |

| 1003 | U.S. Patent Publication No. 2003/0094966 ("Fang")                    |

| 1004 | U.S. Patent No. 6,869,809 ("Yu")                                     |

| 1005 | U.S. Patent No. 7,235,412 ("Mardi")                                  |

| 1006 | U.S. Patent No. 6,765,228 ("Lin")                                    |

| 1007 | U.S. Patent Publication No. 2003/0173667 ("Yong")                    |

| 1008 | Declaration of Dr. Stanley Shanfield, Ph.D.                          |

| 1009 | Curriculum vitae of Dr. Stanley Shanfield, Ph.D.                     |

| 1010 | U.S. Patent No. 5,550,480 ("Nelson")                                 |

| 1011 | U.S. Patent No. 6,744,067 ("Farnworth")                              |

| 1012 | U.S. Patent No. 6,597,187 ("Eldridge")                               |

| 1013 | Waizman et al., U.S. Patent No. 6,392,301 ("Waizman")                |

| 1014 | Hsu et al., U.S. Patent Application Publication 2005/0037601 ("Hsu") |

# TABLE OF CONTENTS

| I.   | INTRODUCTORY STATEMENT                                                                                                                                                                                                                                 | 1  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| II.  | REQUIREMENTS FOR REVIEW UNDER 37 C.F.R. § 42.104                                                                                                                                                                                                       | 1  |

| A    | Standing Under 37 C.F.R. § 42.104(a)                                                                                                                                                                                                                   | 1  |

| В.   | Challenged Claims and Statutory Grounds Under 37 C.F.R. § 42.104(b)(1)-(2)                                                                                                                                                                             | 1  |

| C.   | Unpatentability of Challenged Claims – 37 C.F.R. § 42.104(b)(4)                                                                                                                                                                                        | 2  |

| D.   | Supporting Evidence - 37 C.F.R. § 42.104(b)(5)                                                                                                                                                                                                         | 2  |

| III. | LEVEL OF ORDINARY SKILL IN THE ART                                                                                                                                                                                                                     | 2  |

| IV.  | TECHNOLOGY BACKGROUND                                                                                                                                                                                                                                  | 3  |

| V.   | SUMMARY OF THE '173 PATENT                                                                                                                                                                                                                             | 10 |

| A    | The Patent                                                                                                                                                                                                                                             | 10 |

| В.   | Prosecution History                                                                                                                                                                                                                                    | 14 |

| VI.  | CLAIM CONSTRUCTION UNDER 37 C.F.R. § 42.104(B)(3)                                                                                                                                                                                                      | 15 |

| VII. | GROUND 1: CLAIMS 1-10 ARE ANTICIPATED BY MARDI                                                                                                                                                                                                         | 15 |

| A    | Overview of Mardi                                                                                                                                                                                                                                      | 15 |

| В.   | Independent Claim 1                                                                                                                                                                                                                                    | 19 |

|      | 1. Element 1[preamble] — "an interface assembly for a semiconductor wafer"                                                                                                                                                                             | 19 |

|      | 2. Element 1[a] — "a flip chip bonding pad including a region for performing a bumping process; and"                                                                                                                                                   | 20 |

|      | 3. Element 1[b] — "a test pad integrally constructed with said bonding pad that form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure" | 22 |

|      | 4. Element 1[c] — "said test pad being coplanar relative to said flip chip bonding pad and"                                                                                                                                                            | 23 |

|                                                    | 5.                                                                                                                                                                         | Element 1[d] — "said test pad including a probe region for performing wafer-level testing prior to performing said bumping process"                                                                                                             | 24 |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| C.                                                 |                                                                                                                                                                            | Claim 2 — "The interface assembly of claim 1 wherein said test pad may be disposed anywhere along a periphery of said bonding pad."                                                                                                             |    |

| D.                                                 | D. Claim 3 — "The interface assembly of claim 1 wherein said bonding pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape." |                                                                                                                                                                                                                                                 | 28 |

| test pad comprises a shape selected from the group |                                                                                                                                                                            | Claim 4 — "The interface assembly of claim 1 wherein said test pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape."                                                                            | 28 |

| c                                                  |                                                                                                                                                                            | Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."                                                 | 28 |

| G.                                                 |                                                                                                                                                                            | Claim 6 — "The interface assembly of claim 5 wherein said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer." | 31 |

| Η.                                                 |                                                                                                                                                                            | Claim 7 — "The interface assembly of claim 1 wherein the region to be bumped is defined by a first opening in a passivation layer."                                                                                                             | 32 |

| I.                                                 |                                                                                                                                                                            | Claim 8 — "The interface assembly of claim 7 wherein the probe region is defined by a second opening in said passivation layer, said first and second openings being spaced apart from one another."                                            | 35 |

| J.                                                 |                                                                                                                                                                            | Independent Claim 9                                                                                                                                                                                                                             | 36 |

|                                                    | 1.                                                                                                                                                                         | Element 9[preamble] — "method for testing a semiconductor wafer prior to performing a flip chip bumping process"                                                                                                                                | 36 |

|                                                    | 2.                                                                                                                                                                         | Element 9[a] — "providing a flip chip bonding pad having a region for performing said bumping process"                                                                                                                                          | 37 |

| 3. | Element 9[b] — "integrally constructing a test pad with said bonding pad to form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure" | 38 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4. |                                                                                                                                                                                                                                                    |    |

| 5. | for performing a wafer test prior to performing said bumping process"                                                                                                                                                                              | 39 |

| K. | Independent Claim 10                                                                                                                                                                                                                               | 39 |

| 1. | Element 10[preamble] — "an interface assembly for a semiconductor wafer"                                                                                                                                                                           | 39 |

| 2. | Element 10[a] — "a flip chip bonding pad including a region for performing a bumping process"                                                                                                                                                      | 39 |

| 3. | Element 10[b] — "a test pad integrally constructed with said bonding pad"                                                                                                                                                                          | 39 |

| 4. | Element 10[c] — "said test pad being coplanar relative to said flip chip bonding pad"                                                                                                                                                              | 39 |

| 5. | Element 10[d] — "said test pad including a probe region for performing wafer-level testing prior to performing said bumping process"                                                                                                               | 40 |

| 6. | Element 10[e] — "a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another"                                                                                                    | 40 |

| 7. | Element 10[f] — "said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer"                                         | 40 |

|    | ROUND 2: CLAIMS 1-10 ARE OBVIOUS OVER <i>MARDI</i><br>N VEIW OF A POSITA'S KNOWLEDGE                                                                                                                                                               |    |

| A. | Independent Claim 1 (and all dependent claims) — "wafer-level testing"                                                                                                                                                                             | 40 |

|    |                                                                                                                                                                                                                                                    |    |

| В. | B. Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."                                                  |    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| C. | C. Claim 6 — "The interface assembly of claim 5 wherein said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer."  |    |

| D. | Independent Claim 9 — "wafer test"                                                                                                                                                                                                                  | 49 |

| E. | Independent Claim 10 — "performing wafer-level testing"                                                                                                                                                                                             | 49 |

|    | ROUND 3: CLAIMS 1-4, 7 AND 9 ARE ANTICIPATED Y <i>LIN</i>                                                                                                                                                                                           | 50 |

| A. | Overview of <i>Lin</i>                                                                                                                                                                                                                              | 50 |

| B. | Independent Claim 1                                                                                                                                                                                                                                 | 51 |

| 1. | Element 1[preamble] — "an interface assembly for a semiconductor wafer"                                                                                                                                                                             | 51 |

| 2. | Element 1[a] — "a flip chip bonding pad including a region for performing a bumping process; and"                                                                                                                                                   | 52 |

| 3. | Element 1[b] — "a test pad integrally constructed with said bonding pad that form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure" | 53 |

| 4. |                                                                                                                                                                                                                                                     |    |

| 5. | Element 1[d] — "said test pad including a probe region for performing wafer-level testing prior to performing said bumping process"                                                                                                                 | 55 |

| C. | Claim 2 — "The interface assembly of claim 1 wherein said test pad may be disposed anywhere along a periphery of said bonding pad."                                                                                                                 | 56 |

|    | O I                                                                                                                                                                                                                                                 |    |

| Γ  | D. Claim 3 — "The interface assembly of claim 1 wherein said bonding pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape." |                                                                                                                                                                                                                                                    | 57 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Ε  | E. Claim 4 — "The interface assembly of claim 1 wherein said test pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape."    |                                                                                                                                                                                                                                                    |    |

| F  | 7.                                                                                                                                                                         | Claim 7 — "The interface assembly of claim 1 wherein the region to be bumped is defined by a first opening in a passivation layer."                                                                                                                | 58 |

|    | J.                                                                                                                                                                         | Independent Claim 9                                                                                                                                                                                                                                | 60 |

|    | 1.                                                                                                                                                                         | Element 9[preamble] — "method for testing a semiconductor wafer prior to performing a flip chip bumping process"                                                                                                                                   | 60 |

|    | 2.                                                                                                                                                                         | Element 9[a] — "providing a flip chip bonding pad having a region for performing said bumping process"                                                                                                                                             | 60 |

|    | 3.                                                                                                                                                                         | Element 9[b] — "integrally constructing a test pad with said bonding pad to form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure" | 61 |

|    | 4.                                                                                                                                                                         | Element 9[c] — "disposing said test pad coplanar with said flip chip bonding pad"                                                                                                                                                                  | 61 |

|    | 5.                                                                                                                                                                         | Element 9[d] — "said test pad including a probe region for performing a wafer test prior to performing said bumping process"                                                                                                                       | 62 |

| X. |                                                                                                                                                                            | ROUND 4: CLAIMS 1-7 AND 9-10 ARE OBVIOUS OVER N IN VEIW OF POSITA'S KNOWLEDGE                                                                                                                                                                      | 62 |

| A  | Λ.                                                                                                                                                                         | Independent Claim 1 (and all dependent claims) — "performing wafer-level testing"                                                                                                                                                                  | 63 |

| E  | 3.                                                                                                                                                                         | Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."                                                    | 65 |

|    |                                                                                                                                                                            | with one another                                                                                                                                                                                                                                   |    |

| A.  | first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer."                         |    |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| В.  | Independent Claim 9 — "wafer test"                                                                                                                                                                            | 71 |  |

| C.  | Independent Claim 10                                                                                                                                                                                          | 71 |  |

|     | 1. Element 10[preamble] — "an interface assembly for a semiconductor wafer"                                                                                                                                   |    |  |

|     | 2. Element 10[a] — "a flip chip bonding pad including a region for performing a bumping process"                                                                                                              | 71 |  |

|     | 3. Element 10[b] — "a test pad integrally constructed with said bonding pad"                                                                                                                                  | 71 |  |

|     | 4. Element 10[c] — "said test pad being coplanar relative to said flip chip bonding pad"                                                                                                                      | 71 |  |

|     | 5. Element 10[d] — "said test pad including a probe region for performing wafer-level testing prior to performing said bumping process"                                                                       | 72 |  |

|     | 6. Element 10[e] — "a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another"                                                            | 72 |  |

|     | 7. Element 10[f] — "said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer" | 72 |  |

| D.  | Independent Claim 10 — "performing wafer-level testing"                                                                                                                                                       | 72 |  |

| XI. | GROUND 5: CLAIMS 5-6 AND 10 ARE OBVIOUS IN VIEW OF <i>LIN</i> AND <i>YONG</i>                                                                                                                                 | 72 |  |

| A.  | Overview of <i>Yong</i>                                                                                                                                                                                       | 72 |  |

| B.  | Independent Claim 1                                                                                                                                                                                           | 73 |  |

| C.  | Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."               | 73 |  |

|     |                                                                                                                                                                                                               |    |  |

| D.    | first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer."                         | 79 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| E.    | Independent Claim 10                                                                                                                                                                                          | 81 |

|       | 1. Element 10[preamble] — "an interface assembly for a semiconductor wafer"                                                                                                                                   | 81 |

|       | 2. Element 10[a] — "a flip chip bonding pad including a region for performing a bumping process"                                                                                                              | 81 |

|       | 3. Element 10[b] — "a test pad integrally constructed with said bonding pad"                                                                                                                                  | 81 |

|       | 4. Element 10[c] — "said test pad being coplanar relative to said flip chip bonding pad"                                                                                                                      | 81 |

|       | 5. Element 10[d] — "said test pad including a probe region for performing wafer-level testing prior to performing said bumping process"                                                                       | 81 |

|       | 6. Element 10[e] — "a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another"                                                            | 82 |

|       | 7. Element 10[f] — "said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer" | 82 |

| XII.  | DISCRETIONARY DENIAL IS UNWARRANTED                                                                                                                                                                           |    |

| XIII. | CONCLUSION                                                                                                                                                                                                    |    |

| XIV.  | FEES                                                                                                                                                                                                          |    |

| XV.   | MANDATORY NOTICES UNDER 37 C.F.R. § 42.8                                                                                                                                                                      | 84 |

| A.    | Real Parties-in-Interest Under 37 C.F.R. § 42.8(b)(1)                                                                                                                                                         |    |

| В.    | Related Matters Under 37 C.F.R. § 42.8(b)(2)                                                                                                                                                                  | 85 |

| C.    | Lead and Back-up Counsel Under 37 C.F.R. § 42.8(b)(3)                                                                                                                                                         | 85 |

| D.    | Service Information Under 37 C.F.R. § 42.8(b)(4)                                                                                                                                                              | 86 |

#### I. INTRODUCTORY STATEMENT

Microchip Technology Incorporated and Microsemi Corporation ("Petitioners") petition for *Inter Partes* Review ("IPR") under 35 U.S.C. §§ 311-319 and 37 C.F.R. § 42.100 *et seq.* of all claims (claims 1-10) of U.S. Patent No. 7,221,173 ("the '173 patent") (Ex. 1001), which is currently assigned to Bell Semiconductor, LLC ("Patent Owner"). Because it is reasonably likely that Petitioners will prevail on at least one challenged claim, the PTAB should institute review of the '173 patent. *See* 35 U.S.C. § 314(a).

## II. REQUIREMENTS FOR REVIEW UNDER 37 C.F.R. § 42.104

## A. Standing Under 37 C.F.R. § 42.104(a)

Petitioners certify the '173 patent is eligible for IPR and Petitioners are not barred or estopped from requesting IPR of the '173 patent.

# B. Challenged Claims and Statutory Grounds Under 37 C.F.R. § 42.104(b)(1)-(2)

Petitioners request IPR and cancellation of all claims (claims 1-10) of the '173 patent on the following grounds.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Unless otherwise noted, references to 35 U.S.C. §§ 102 and 103 are to the pre-AIA versions of the Patent Statute.

| Ground | Basis | References                    | Challenged Claims |

|--------|-------|-------------------------------|-------------------|

| 1      | § 102 | Mardi                         | 1-10              |

| 2      | § 103 | Mardi and knowledge of POSITA | 1-10              |

| 3      | § 102 | Lin                           | 1-4, 7, 9         |

| 4      | § 103 | Lin and knowledge of POSITA   | 1-7, 9-10         |

| 5      | § 103 | Lin, and                      | 5-6, 10           |

|        |       | Yong                          |                   |

# C. Unpatentability of Challenged Claims – 37 C.F.R. § 42.104(b)(4)

An explanation of why claims 1-10 are unpatentable is set forth below.

## **D.** Supporting Evidence - 37 C.F.R. § 42.104(b)(5)

Petitioners rely upon the evidence cited in the List of Exhibits, including the Declaration of Stanley Shanfield, Ph.D. (Ex. 1008).

#### III. LEVEL OF ORDINARY SKILL IN THE ART

A "person of ordinary skill in the art" (POSITA) at the time of the effective filing date of the '173 patent would have possessed at least a bachelor's degree in physics or electrical engineering or a related field as well as at least three (3) years of experience in semiconductor wafer and packaging engineering and development, or alternatively would have an equivalent combination of advanced education and practical experience, such as a master's or a Ph.D. degree and at least one (1) year

of experience in semiconductor wafer and packaging engineering and development. Ex. 1008, ¶44.

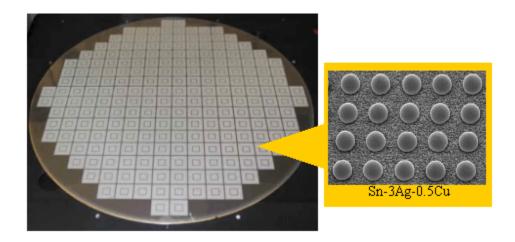

#### IV. TECHNOLOGY BACKGROUND

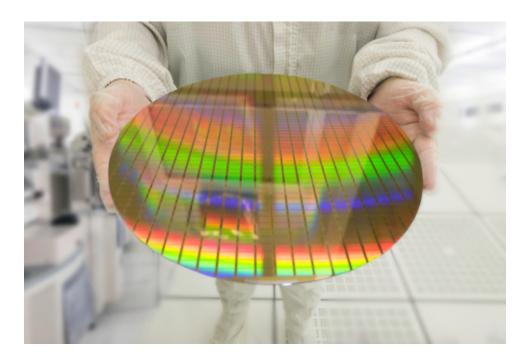

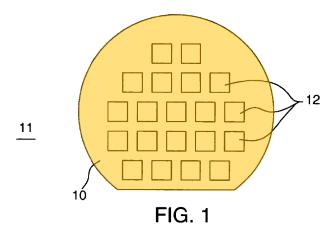

The technology at issue relates to testing flip chip semiconductor wafers prior to soldering bumps to the wafers. Ex. 1001-1, [54] (Title). Semiconductor devices, such as integrated circuit ("IC") chips, are typically created on a silicon wafer. Ex. 1008, ¶18. A silicon wafer is a thin (usually circular) slice of silicon. *Id.* One wafer can contain tens to hundreds of individual IC chips, also known as "die." *Id.* The image below shows an example wafer containing a number of ICs (each square is an identical IC): <sup>2</sup>

<sup>&</sup>lt;sup>2</sup> The images in this Technology Background section were copied from the Internet and accurately illustrate the technology described. Ex. 1008, ¶18.

*Id.* Eventually, each die will be cut from the wafer in a process called "dicing." The die will then be put into a "package" so that it can be connected to external circuitry such as a circuit board or another IC or wafer. Ex. 1008, ¶19.

One method of packaging a die uses a procedure known as "wire bonding." Ex. 1008, ¶20. In a wire bonding process, the individual die is patterned with small pads of metal near its edges that serve as the connections to an eventual mechanical package. *Id.* After the die are cut from the wafer, they are electrically connected to their package terminals via wire bonding. *Id.* The image below shows metal wires attaching the pads around the perimeter of the die ("die pads") to connections on the package ("package connections"):

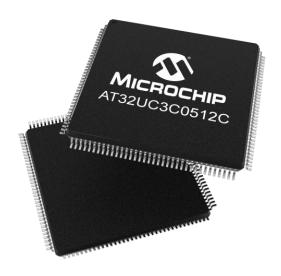

*Id.* The package connections eventually lead to pins on the outside of the package, resulting in a final, packaged product like the one depicted below:

Ex. 1008, ¶21.

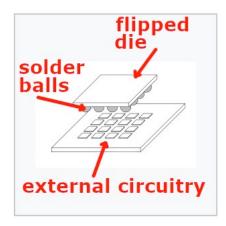

"Flip chip" packaging is a packaging technique that was developed in the 1960s. Ex. 1008, ¶22 (citing Aviation Week & Space Technology, Sept. 23, 1963, at 96 ("Flip-Chip' Interconnections—Novel technique for packaging and interconnecting group of semiconductor microcircuit chips, in which 30 to 40 individual circuit function chips are interconnected . . . has been developed by General Electric's Light Military Electronics Dept....") (available at

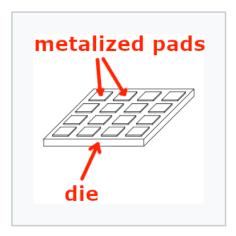

https://archive.org/stream/Aviation\_Week\_1963-09-23#page/n48/mode/1up) (last accessed Aug. 21, 2020)). For flip chip packaging, the attachment pads—also known as "bond pads"—on the die are metalized to make them more receptive to solder:

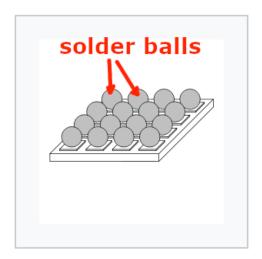

Ex. 1008, ¶23. Then, a small ball (or "bump") of solder is deposited on each metalized bond pad on the die:

Ex. 1008, ¶24. The die is flipped and positioned so that the solder balls are facing the connectors on the external circuitry:

Ex. 1008, ¶25. The solder balls are then re-melted (typically using hot air):

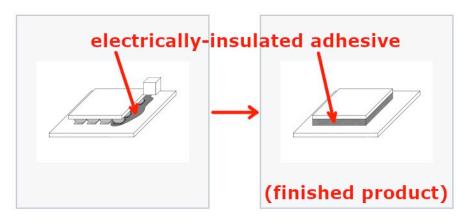

Ex. 1008, ¶26. The mounted die is "underfilled" using an electrically-insulated adhesive:

Ex. 1008, ¶27.

The above description of flip chip packaging leaves out a number of intermediate steps that involve testing of the die on the wafer. Ex. 1008, ¶28. In particular, it is typical that the solder balls/bumps are deposited onto the bond pads on a wafer *before the wafer is diced into individual die. Id.* A wafer with solder balls/bumps is shown below:

Id.

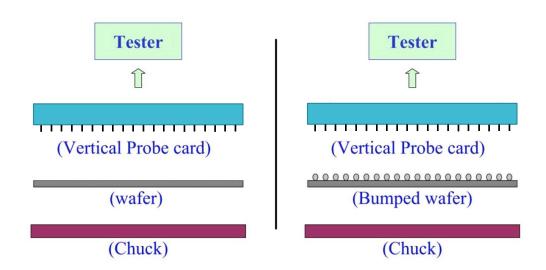

At some point before the wafer is diced into individual die/chips, the functionality of the chips are typically tested to make sure the manufacturing process produced functional chips. Ex. 1008, ¶29. Testing typically involves "probing" the wafer with a machine known as a tester. *Id.* The tester is connected to a "probe card" that includes "probes" that sit on top of the wafer during testing. *Id.* The testing can be done before the wafer is "bumped" (*i.e.*, solder balls deposited) or after, as depicted in the illustrations below. *Id.* During testing, the probes physically touch

either (1) the bond pads on the wafer (without solder balls/bumps) or (2) the solder balls/bumps:

*Id.* (The "chuck" is a part of the tester that holds the wafer in place during testing.)

After the circuitry in each die on the wafer is tested, and the solder balls/bumps deposited, the wafer is diced into individual die, as described above. Ex. 1008, ¶30. Unnecessary packaging costs are avoided because die that are found not to be functional during testing are discarded after dicing:

*Id.* Independent of whether wafers incorporate flip chip technology, semiconductor manufacturers are strongly motivated to test die for functionality before any

packaging operation. Ex. 1008, ¶31. A significant fraction of the cost of manufacturing an integrated circuit is associated with the packaging operation itself, *i.e.* die attachment, wiring bonding, encapsulation, etc. *Id.* In the very competitive IC manufacturing environment, testing individual die before packaging is normally an economic necessity. *Id.*

#### V. SUMMARY OF THE '173 PATENT

#### A. The Patent

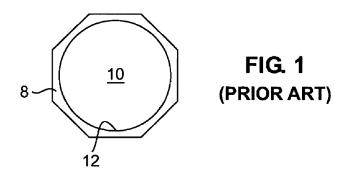

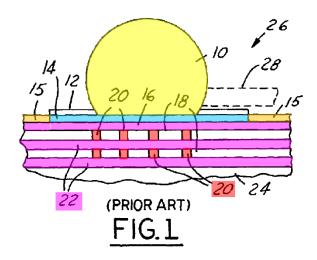

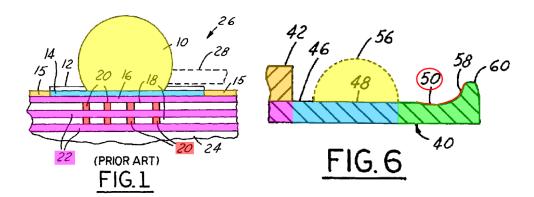

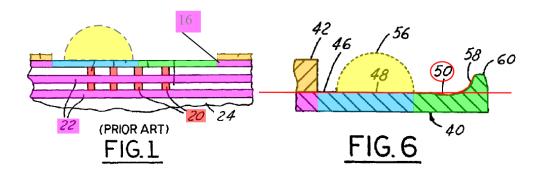

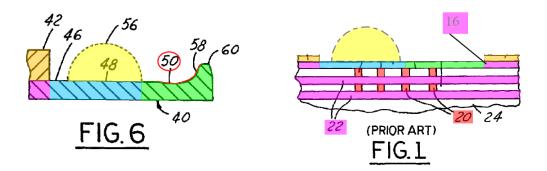

The '173 patent was filed on September 29, 2004 and is titled "Method and Structures for Testing a Semiconductor Wafer Prior to Performing a Flip Chip Bumping Process," and generally describes separate bonding and testing pads. Ex. 1001-1, [22], [54]. "Flip chip" generally refers to a direct electrical connection of face-down (hence, "flipped") electronic components to circuit boards via conductive bumps on the chip bond pads. Ex. 1008, ¶32. The '173 patent teaches it was known at the relevant time that a semiconductor device would include a bump region 10 defined by an opening 12 in the passivation layer over a metal bonding pad 8, as shown in Figure 1 and identified as prior art:

Ex. 1008, ¶32; Ex. 1001-4, 1:28-37, 2:50-52; Ex. 1001-2, Fig. 1. It was also known to solder an electrically conductive bump to the bump region 10 to create a "flip chip" assembly. *Id*.

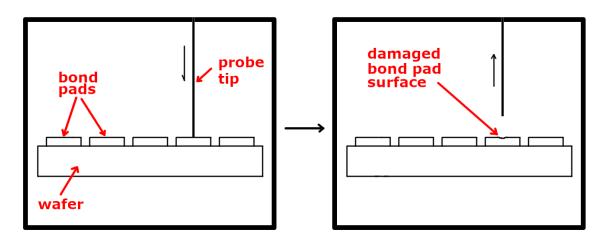

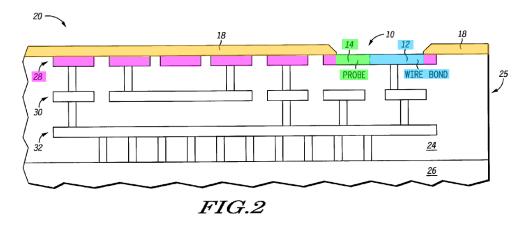

The '173 patent alleges damage to the bump region of the bond pad occurs when a test probe tip contacts the bump region prior to adding the solder bump. Ex. 1008, ¶33; Ex. 1001-4, 1:38-56. The test probe tip gouges the bump region and forms irregularities in the surface, which makes it difficult to adhere or solder the electrically conductive bump to the bump region. Ex. 1008, ¶33; Ex. 1001-4, 1:38-56. The alleged problem is illustrated in the cross-sectional view below:

Ex. 1008, ¶33.

Admitted prior art attempted to address these problems, including using test pads that are physically separate but electrically connected (by interconnect/trace lines) to the bond pad. Ex. 1008, ¶34; Ex. 1001-4, 1:56-60. Because the test pads are physically separate from the bond pads, the probe tip may damage the test pad

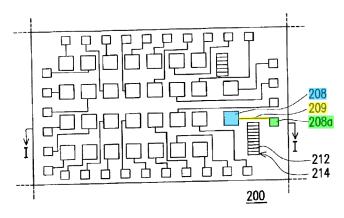

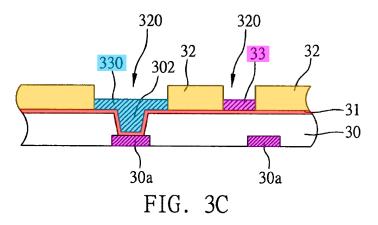

without consequence. Ex. 1008, ¶34. The solder bump is placed on the bond pad, not the damaged test pad. *Id*. This type of prior art test pad is discussed in U.S. Patent 6,869,809 ("*Yu*") (Ex. 1004), which was cited during prosecution of the '173 patent. Ex. 1001-1, [56]. *Yu*'s Figure 3A shows test pads 208a that are physically separate from bond pads 208, connected by interconnect/trace lines 209:

FIG. 3A

Ex. 1004-8, 4:52-55; Ex. 1004-4, Fig. 3A.<sup>3</sup> According to the '173 patent, these interconnect lines between are problematic because (1) they introduce undesirable propagation delays to test signals, and (2) they require "additional processing steps of deposition, pattern and etch." Ex. 1001-4, 1:62-2:4; Ex. 1008, ¶36.

<sup>&</sup>lt;sup>3</sup> All highlighting, colors, and emphasis added to patent text or figures herein has been added. Any such citations should be understood to include an "(annotated)" and/or "(emphasis added)" parenthetical.

Another admitted prior art testing method involved probing the wafers after the bumping process is performed. Ex. 1001-4, 2:26-27. "[T]his attempt also fails to provide a fully satisfactory solution. For example, this post-bumping probing technique may lead to incremental costs since there is a possibility that the bumping process (that takes valuable time and resources) may have been performed in an already defective wafer...." Ex. 1001-4, 2:27-32; Ex. 1008, ¶37.

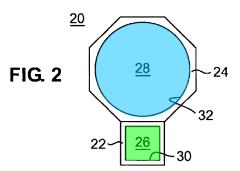

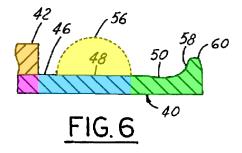

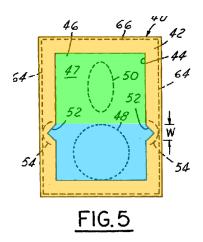

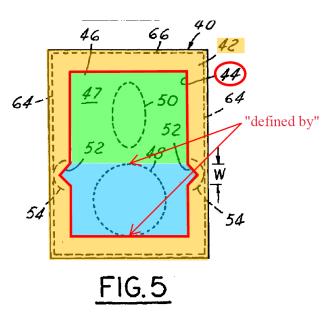

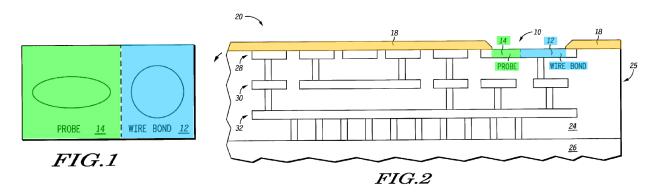

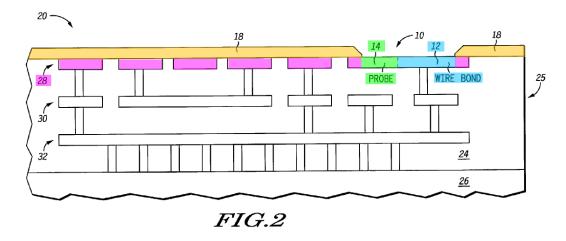

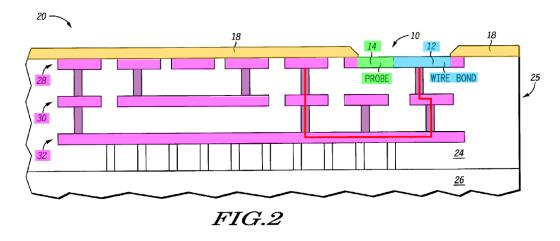

The '173 patent explains "it would be desirable to provide structures and techniques for allowing a semiconductor device or wafer to be tested prior to a bumping process so that wafer level tests can be undertaken without compromising the integrity of the metal bonding pads therein and without introducing delays to signals used for test purposes." Ex. 1001-4, 2:38-43; Ex. 1008, ¶38. Accordingly, the '173 patent discloses "a conductive test pad 22 integrally constructed with a conductive bonding pad 24":

Ex. 1001-5, 3:1-2, and Fig. 2. The **bump region 28** and the **probe region 26** are exposed through individual openings 32 and 30, respectively, in the passivation

layer. Ex. 1008, ¶39. The '173 patent suggests this configuration is advantageous because:

conductive test pad 22 provides a respective probe region 26 where a probe tip may be placed for performing, for example, wafer level testing. The bonding pad 24 includes a bump region 28 that is no longer subject to mechanical contact with the probe tip and resulting surface irregularities. It is envisioned that since the test pad and bonding pad comprise an integral structure that no longer requires interconnect lines and avoids or substantially reduces propagation delays in test signals passing therethrough, an interface assembly embodying aspects of the present invention should lead to more reliable and accurate test results.

Ex. 1001-5, 3:4-14; Ex. 1008, ¶39.

### **B.** Prosecution History

The application for the '173 patent was filed September 29, 2004. Ex. 1001-1, [22]. The '173 patent issued on May 22, 2007. *Id.*, [45]. The prosecution history does not impact the art or arguments of this Petition. Ex. 1008, ¶43.

## VI. CLAIM CONSTRUCTION UNDER 37 C.F.R. § 42.104(B)(3)

Unless otherwise noted below, Petitioners submit that terms should be given their plain meaning, but reserve the opportunity to respond to constructions offered by Patent Owner or adopted by the Board.<sup>4</sup>

#### VII. GROUND 1: CLAIMS 1-10 ARE ANTICIPATED BY MARDI

#### A. Overview of *Mardi*

U.S. Patent No. 7,235,412 ("*Mardi*") (Ex. 1005), issued to *Mardi et al.* and titled "Semiconductor Component Having Test Pads and Method and Apparatus for Testing Same," was filed on May 11, 2004 (Ex. 1005-1, [22]), and thus qualifies as §102(e) prior art because it was filed before the '173 patent's September 29, 2004 filing date. *Mardi* is directed to testing flip chip semiconductor wafers prior to bump soldering. Ex. 1005-1, [52], [57]; Ex. 1008, ¶48.

<sup>&</sup>lt;sup>4</sup> Petitioners do not concede the challenged claims meet all statutory standards. Patentability under §101 or compliance with §112 is not appropriate for IPR, and Petitioners reserve all rights to challenge claims for reasons outside the scope of IPR. Petitioners may advance specific constructions consistent with the plain and ordinary meaning in the related district court proceeding.

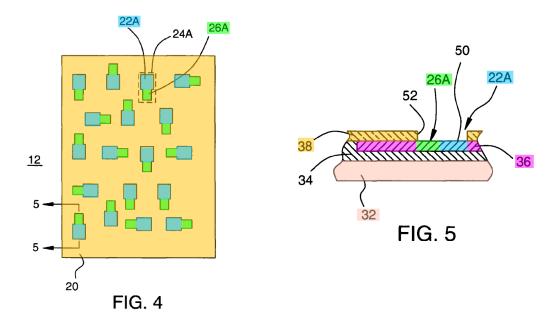

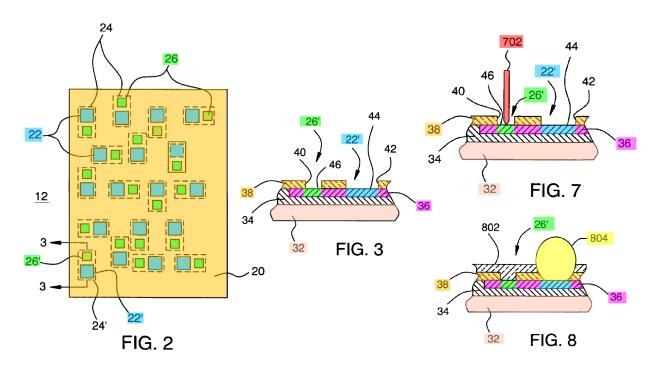

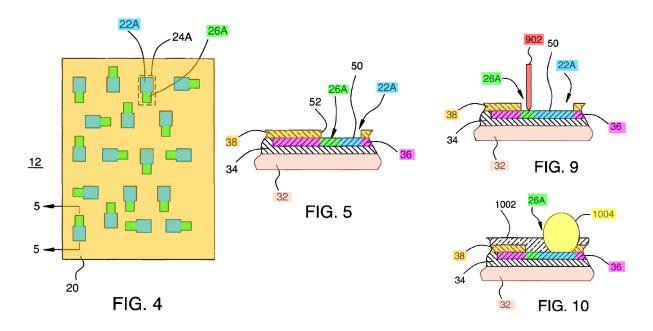

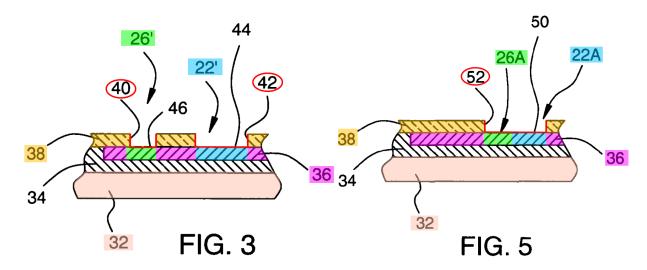

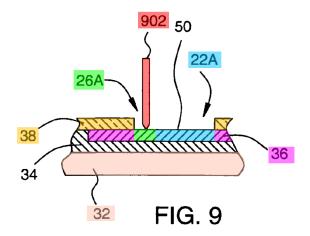

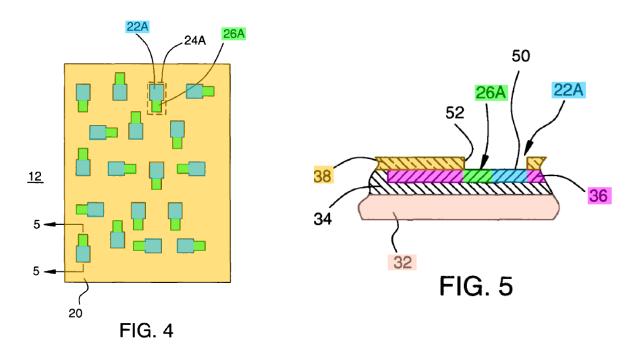

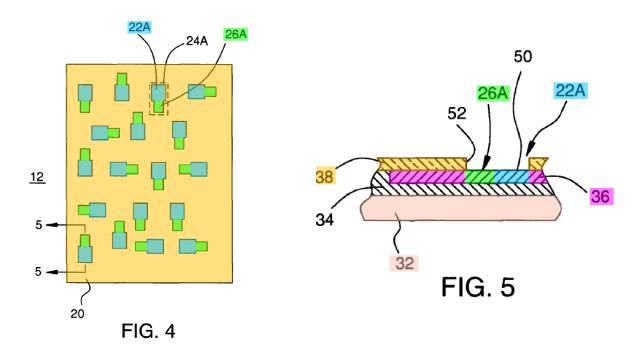

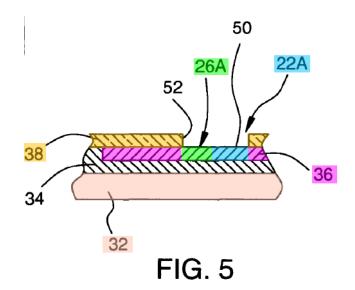

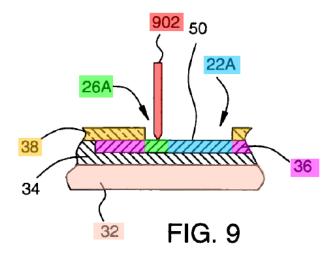

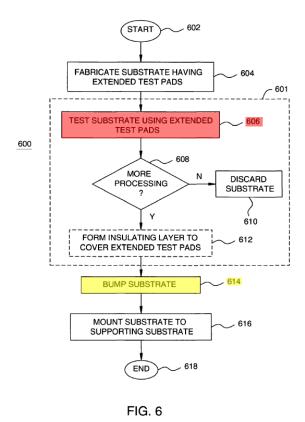

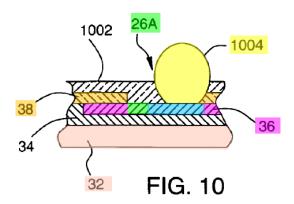

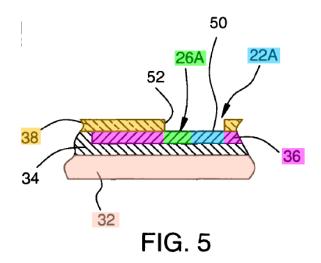

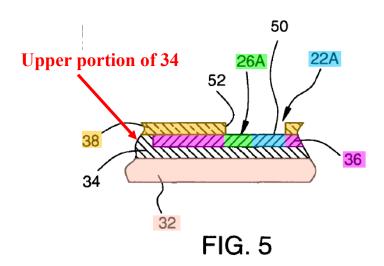

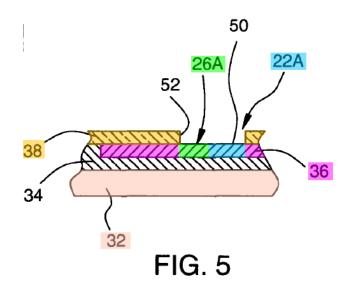

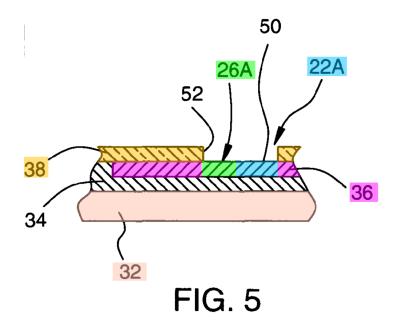

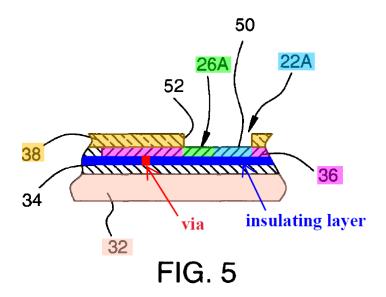

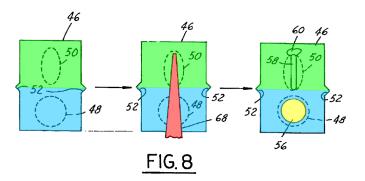

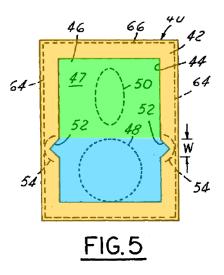

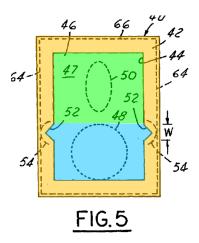

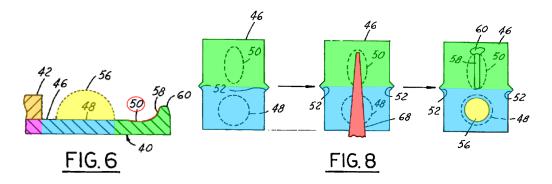

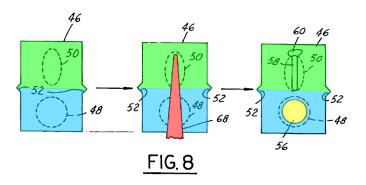

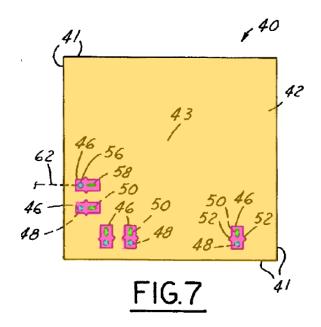

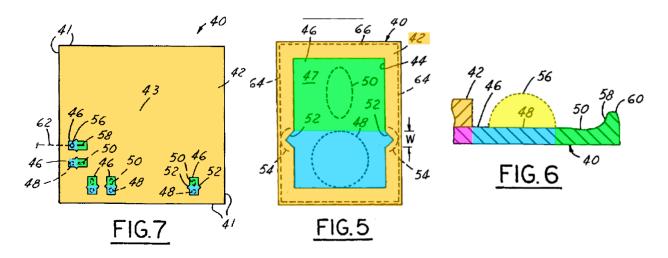

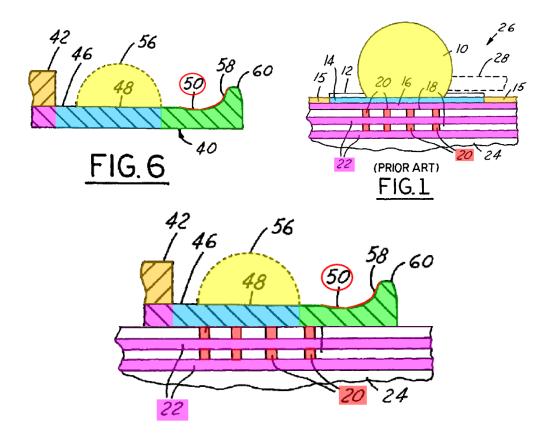

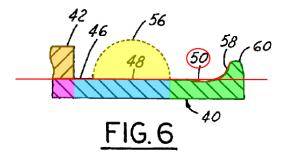

Ex. 1005-3, Figs. 4-5. *Mardi* discloses **test pads 26A** and **bond pads 22A** are integrated together as "separate regions" of a **top conductor layer 36**. Ex. 1005-8, 5:34-44; Ex. 1008, ¶48. A method for testing flip chip semiconductor wafers is also disclosed, wherein the semiconductors are probe tested via the test pads prior to soldering bumps on the bond pads. Ex. 1005-9, 7:24-36; Ex. 1005-4, Fig. 6; Ex. 1008, ¶48.

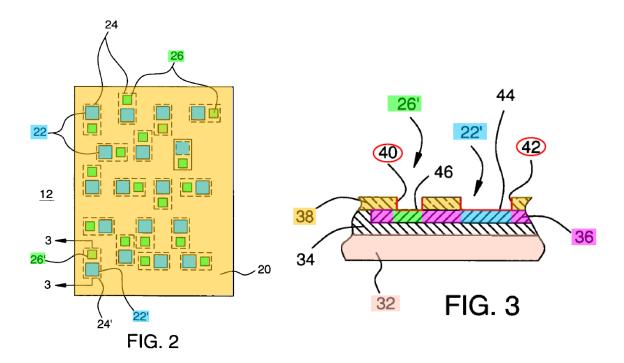

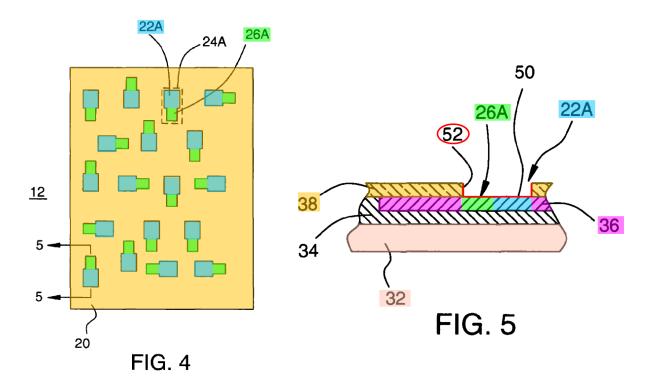

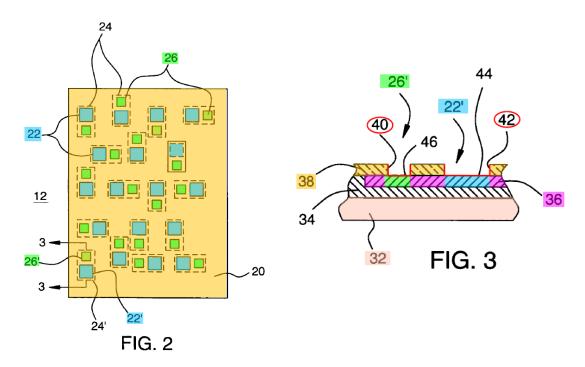

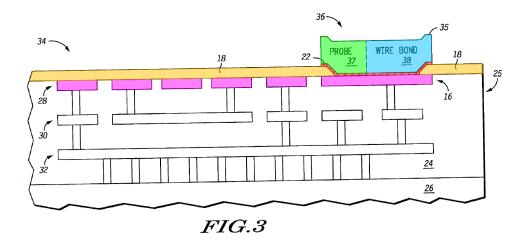

*Mardi* discloses at least two exemplary embodiments. The first is depicted in Figures 2-3 and 7-8 ("First Mardi Embodiment"):

Ex. 1005-6, 2:53-59; Ex. 1005-7, 3:3-5; Ex. 1005-2, Figs. 2-3; Ex. 1005-5, Figs. 7-8; Ex. 1008, ¶49. The second is depicted in Figures 4-5 and 9-10 ("Second Mardi Embodiment"):

Ex. 1005-6, 2:6-65; Ex. 1005-7, 3:6-8; Ex. 1005-3, Figs. 4-5; Ex. 1005-5, Figs. 9-10; Ex. 1008, ¶49. One difference between the two embodiments is the number of openings in passivation layer 38. In the First Mardi Embodiment, there are separate openings for the test pad and bond pad ("opening 40" and "opening 42"), while the Second Mardi Embodiment only has one opening for both ("opening 52"):

Ex. 1005-7, 4:59-62; Ex. 1005-8, 5:34-35; and Ex. 1005-2 to -3, Figs. 3, 5; Ex. 1008, ¶50.

## B. Independent Claim 1<sup>5</sup>

1. Element 1[preamble] — "an interface assembly for a semiconductor wafer"

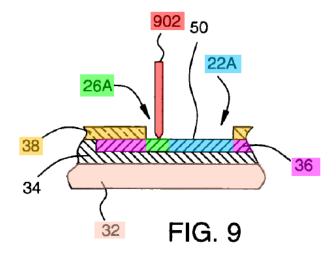

To the extent the preamble is limiting, *Mardi* discloses this element. Ex. 1008, ¶¶53-55. *Mardi* teaches a semiconductor wafer with bond pads and test pad interfaces ("interface assembly") for testing the semiconductor wafer prior to soldering balls to the bond pads. Ex. 1005-1, [57] ("A semiconductor component having **test pads** and a method and apparatus for testing the same is described."). The "invention relates to testing a semiconductor component" (Ex. 1005-6, 1:62-63), and "[t]he semiconductor component 11 comprises a substrate 10 ... [which] may be a wafer...." Ex. 1005-7, 3:18-23. The **test pad** provides an "interface assembly" whereby a **probe element 902** may be brought into contact with the **test pad 26A** to interface with the semiconductor wafer. Ex. 1008, ¶55.

<sup>&</sup>lt;sup>5</sup> The mapping of claim elements 1[preamble]-[d] is directed at the Second Mardi Embodiment found in Figures 4-5 and 9-10. That mapping applies equally to the First Mardi Embodiment shown in Figures 2-3 and 7-8. Ex. 1008, ¶ 65.1.

Ex. 1005-5, Fig. 9. "In this manner, the die or dice of the substrate may be tested or 'burned-in' before further processing (e.g., bumping, packaging, etc.)." Ex. 1005-8, 6:21-23; Ex. 1008, ¶55.

# 2. Element 1[a] — "a flip chip bonding pad including a region for performing a bumping process; and"

Mardi discloses this element. Ex. 1008, ¶56-57. In Mardi, "bond pad 22A" corresponds to the claimed "flip chip bonding pad including a region for performing a bumping process."

Ex. 1005-3, Figs. 4-5. The "test/bond pad pair 24A" is a flip chip bonding pad. Ex. 1005-8, 5:5-11 ("bond pads 22 are adapted to support bumped contacts (e.g., solder balls) for providing external electrical connections for the semiconductor die 12. Once the bumped contacts are in place, the semiconductor die 12 may be 'flip chip' mounted (i.e., circuit-side down) to mating electrodes on a supporting substrate, such as a circuit board or lead-frame.")

The **bond pad 22A** includes a region for performing a bumping process because "bond pads 22 are adapted to support bumped contacts (e.g., solder balls) for providing external electrical connections for the semiconductor die 12." Ex. 1005-8, 5:5-11; *see also* Ex. 1005-8, 5:26-33 ("With simultaneous reference to FIGS. 4 and 5, in the present embodiment, the semiconductor die 12 includes a pattern of test/bond pad pairs 24A embedded within the die passivation layer 38.

Each of the test/bond pad pairs 24A comprises a die contact portion ('bond pad 22A') in electrical communication with a test contact portion ('test pad 26A'). FIG. 5 shows a cross-section of one of the test/bond pad pairs 24A.") Ex. 1008, ¶57.

3. Element 1[b] — "a test pad integrally constructed with said bonding pad that form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure"

Mardi discloses this element. Ex. 1008, ¶¶58-61. The "test pad 26A" in Mardi corresponds to the claimed "test pad."

Ex. 1005-3, Figs. 4-5.

Further, the "bond pad 22A" and the "test pad 26A" are integrally constructed as an integral conductive structure, as claimed. Ex. 1005-8, 5:29-33 ("the semiconductor die 12 includes a pattern of test/bond pad pairs 24A embedded

within the die passivation layer 38. Each of the test/bond pad pairs 24A comprises a die contact portion ('bond pad 22A') in electrical communication with a test contact portion ('test pad 26A'). FIG. 5 shows a cross-section of one of the test/bond pad pairs 24A.") Ex. 1008, ¶59.

There are no interconnect testing lines between the **test pad 26A** and the **bond pad 22A**. Ex. 1005-8, 5:34-44 ("The top conductor layer 36 electrically couples the **bond pad 22A** with the **test pad 26A**. The **test pad 26A** may be considered as an 'extended test pad' with respect to the **bond pad 22A**.") The integral nature of the test/bond pad pairs 24A is evident from (1) the shape of element 24A in Figure 4, and (2) the fact that the **bond pad 22A** and the **test pad 26A** are merely "separate regions of the section 50 of the top conductor layer 36" (shown in Fig. 5). Ex. 1005-8, 5:39-44; Ex. 1005-3, Fig. 4; Ex. 1008, ¶60-61.

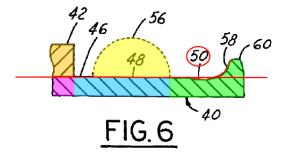

# 4. Element 1[c] — "said test pad being coplanar relative to said flip chip bonding pad and"

Mardi discloses this element. Ex. 1008, ¶62. In Mardi, test pad 26A is coplanar with the bond pad 22A because they are merely "regions" of the same conductor layer.

Ex. 1005-3, Fig. 5; Ex. 1005-8, 5:34-44 ("In the present embodiment, each of the test/bond pad pairs 24A is located in an opening 52 of the passivation layer 38 and comprises a section 50 of the top conductor layer 36. A first portion of the section 50 defines the **bond pad 22A**, and a second portion of the section 50 defines the **test pad 26A**. That is, the **bond pad 22A** and the **test pad 26A** comprise separate regions of the section 50 of the top conductor layer 36.")

# 5. Element 1[d] — "said test pad . . . including a probe region for performing wafer-level testing prior to performing said bumping process"

*Mardi* discloses this element. Ex. 1008, ¶¶63-65. Figure 9 illustrates that **test** pad 26A is a probe region during wafer-level testing because "a probe element 902 is in contact with the portion of the conductor section 50 that defines the **test pad** 26A." Ex. 1005-9, 7:31-32.

Ex. 1005-5, Fig. 9. Further, "the **test pad 26A** may be used to test the semiconductor die 12 *before the semiconductor die 12 is bumped* [*i.e.* the 'bumping process'] and without contacting the **bond pad 22A**." Ex. 1005-8, 5:54-56.

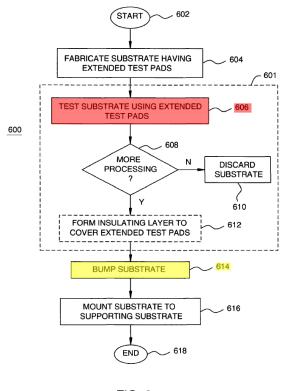

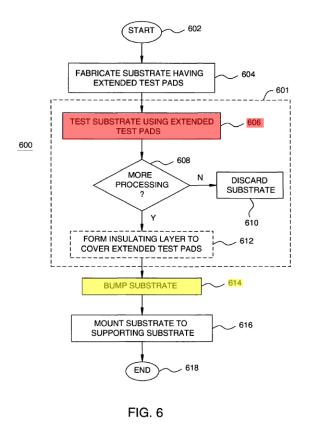

Figure 6 confirms the test pad's probe region is for performing wafer-level testing prior to performing the bumping process:

Ex. 1005-4, Fig. 6. Test pads are fabricated in step 604, the substrate is tested using the probe regions at step 606 ("wafer-level testing"), and the "bumping process" is performed later in step 614. Ex. 1005-9, 7:24-36 ("... FIG. 5 depicts a cross-section of the test/bond pad pair 24A after *fabrication at step 604*. FIG. 9 depicts a cross-section of the test/bond pad pair 24A during the *testing at step 606*. Notably, a **probe element 902** is in contact with the portion of the conductor section 50 that defines the **test pad 26A**. The **probe element 902** does not contact the portion of the conductor section 50 that defines the **bond pad 22A**. Thus, damage to the **bond pad**

22A is avoided during the testing at step 606."); Ex. 1005-8, 6:51-55 ("At step 614,

the semiconductor substrate is bumped ... using a conventional bumping process.").

Ex. 1005-5, Fig. 10. Figure 10 shows "a bumped contact 1004 formed in electrical communication with the **bump pad 22A**." Ex. 1008, ¶¶64-65.

# C. Claim 2 — "The interface assembly of claim 1 wherein said test pad may be disposed anywhere along a periphery of said bonding pad."

Mardi discloses this claim. Ex. 1008, ¶66. Mardi explains the test pad in the First Mardi Embodiment may be anywhere along the periphery of the bonding pad. Ex. 1005-7, 4:30-33 ("Illustratively, the test pad 26' may be disposed at any point around the perimeter of the bond pad 22'....") Likewise, Mardi explains the test pad in the Second Mardi Embodiment may anywhere along the periphery of the bond pad because "[t]he shapes and sizes of the bond pad 22A and the test pad 26A may be selected substantially as described above with respect to FIGS. 2 and 3," i.e., the First Mardi Embodiment. Ex. 1005-8, 5:48-50.

D. Claim 3 — "The interface assembly of claim 1 wherein said bonding pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape."

*Mardi* discloses this claim. Ex. 1008, ¶67. *Mardi* expressly describes polygonal and circular shaped bonding pads: "The bond pad 22A and the test pads 26 may be generally square as illustrated in FIG. 2, or may have other shapes known in the art (e.g., other polygonal or elliptical shapes)." Ex. 1005-7, 4:6-8.

E. Claim 4 — "The interface assembly of claim 1 wherein said test pad comprises a shape selected from the group consisting of a polygonal shape, and a circular shape."

*Mardi* discloses this claim. Ex. 1008, ¶68. *Mardi* expressly describes polygonal and circular shaped test pads: "The bond pad 22A and the test pads 26 may be generally square as illustrated in FIG. 2, or may have other shapes known in the art (e.g., other polygonal or elliptical shapes)." Ex. 1005-7, 4:6-8.

F. Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."

Mardi discloses this claim. Ex. 1008, ¶¶69-72. The top conductor layer 36 of Mardi corresponds to the claimed "first metal redistribution layer."

Ex. 1005-3, Fig. 5. The **test pad 26A** and the **bond pad 22A** are electrically connected to the **top conductor layer 36** because they are a section of that layer. *See* Ex. 1005-8, 5:34-41 ("each of the test/bond pad pairs 24A [*i.e.*, **test pad 26A** and **bond pad 22A**] ... comprises a section 50 of the **top conductor layer 36**"). As illustrated and described, **top conductor layer 36** is a redistribution layer because it provides electrical communication between the **test pad 26A** and **bond pad 22A** and various semiconductor devices (semiconductor circuits) within the semiconductor. Ex. 1005-7, 4:36-39 (**top conductor layer 36** is "in electrical communication with the various semiconductor devices (semiconductor circuits) within the semiconductor portion 32.") Ex. 1008, ¶69.

As shown in Figure 5, the top conductor layer 36 extends under the passivation layer 38 for some distance beyond the test pad 26A and bond pad 22A, which is typical for a "redistribution layer." The extending "redistribution layer" portion of the top conductor layer 36 is coplanar with the test pad 26A and bond

**pad 22A** because all are part of the same "top conductor layer 36." Ex. 1005-8, 5:34-36; Ex. 1008, ¶70.

Further, a conductor layer within the internal conductor portion 34 may also correspond to the "first metal redistribution layer" because "internal conductor portion 34 compris[es] one or more internal conductor layers between the substrate portion 32 and the top conductor layer 36." Ex. 1005-7, 4:39-42. As illustrated in Figure 5, the uppermost portion of conductor portion 34 is coplanar with the **test pad 26A** and **bond pad 22A**. That portion would be electrically connected to other metal layers using vias: "all of the conductor layers may be separated by respective insulating layers, and may be connected to each other using vias (not shown for simplicity)." Ex. 1005-8, 5:42-45; Ex. 1005-3, Fig. 5; Ex. 1008, ¶71.

Similarly, all of the test/bond pad pairs 24' (Figure 2) and 24A (Figure 4) are on the same plane because the "the bond pads 22 and the test pads 26 [are] disposed below the level of the die passivation layer 38." Ex. 1005-7, 4:1-5. Thus, other

test/bond pad pairs are part of the same "redistribution layer" and are coplanar with the test pad 26A and bond pad 22A. Ex. 1008, ¶72.

G. Claim 6 — "The interface assembly of claim 5 wherein said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer."

*Mardi* discloses this claim. Ex. 1008, ¶¶73-75. *Mardi* expressly discloses vias are used to connect "redistribution layers" at different planes within the semiconductor. As noted above with respect to claim 5, the **top conductor layer 36** and/or the uppermost conductor layer within the internal conductor portion 34 correspond to a "redistribution layer" as claimed. Ex. 1005-8, 4:36-39.

Ex. 1005-3, Fig. 5.

Lower conductor layers in the "internal conductor portion 34" of *Mardi* correspond to the claimed "second redistribution layer" because portion 34 includes "one or more internal conductor layers between the **substrate portion 32** and the

top conductor layer 36" (Ex. 1005-7, 4:39-42) and it "may be in electrical communication with the top conductor layer 36 and the semiconductor devices/circuits within the semiconductor portion 32." Ex. 1005-7, 4:45-48; Ex. 1008, ¶74.

*Mardi* teaches these "redistribution layers" may be connected by vias: "all of the conductor layers may be separated by respective insulating layers, and may be connected to each other using vias (not shown for simplicity)." Ex. 1005-7, 4:42-45. Because *Mardi* discloses there are insulating layers separating all of the conductor layers (including **top conductor layer 36** and any conductor layer(s) inside internal conductor portion 34), *Mardi* expressly discloses the conductor layers are disposed in different planes. Ex. 1008, ¶75.

## H. Claim 7 — "The interface assembly of claim 1 wherein the region to be bumped is defined by a first opening in a passivation layer."

Mardi discloses this claim. Ex. 1008, ¶¶76-80. In the First Mardi Embodiment, the "opening 42" is the claimed "first opening":

Ex. 1005-2 to -3, Figs. 2-3. "The passivation layer 38 is formed over the top conductor layer 36. Each of the bond pads 22 is located in an opening 42 of the passivation layer 38 and comprises a portion 44 of the top conductor layer 36." Ex. 1005-7, 4:58-63; Ex. 1008, ¶76.

The **bond pad 22** is defined by the **opening 42** in the **passivation layer 38** as claimed because the bond pad is the region to be bumped. Ex. 1005-8, 5:5-7 ("The bond pads 22 are adapted to support bumped contacts (e.g., solder balls) for providing external electrical connections for the semiconductor die 12.") Ex. 1008, ¶77.

In the Second Mardi Embodiment, the "opening 52" is the claimed "first opening":

Ex. 1005-3, Figs. 4-5. "[E]ach of the test/bond pad pairs 24A is located in an **opening** 52 of the passivation layer 38 and comprises a section 50 of the top conductor layer 36. A first portion of the section 50 defines the **bond pad 22A**, and a second portion of the section 50 defines the **test pad 26A**." Ex. 1005-8, 5:34-38; Ex. 1008, ¶78.

The **bond pad 22A** is defined by the **opening 52** in the passivation layer 38 as claimed because the bond pad is the region to be bumped. Ex. 1005-8, 5:5-7 ("The bond pads 22 are adapted to support bumped contacts (e.g., solder balls) for providing external electrical connections for the semiconductor die 12.") Ex. 1008, ¶¶79-80.

I. Claim 8 — "The interface assembly of claim 7 wherein the probe region is defined by a second opening in said passivation layer, said first and second openings being spaced apart from one another."

*Mardi* discloses this claim. Ex. 1008, ¶¶81-82. In the First Mardi Embodiment, the "opening 40" corresponds to the claimed "second opening":

Ex. 1005-2, Figs. 2-3; Ex. 1008, ¶81. "The passivation layer 38 is formed over the top conductor layer 36. Each of the bond pads 22 is located in an opening 42 of the passivation layer 38 and comprises a portion 44 of the top conductor layer 36. Each of the test pads 26 is located in an opening 40 of the passivation layer 38 and comprises a portion 46 of the top conductor layer 36." Ex. 1005-7, 4:58-63.

Thus, in the passivation layer 38, the bond pad 22' is defined by the opening 42 and the test pad 26' is defined by the opening 40, as claimed because the test

pad is used as a probe region. Ex. 1005-9, 7:10-13 ("Notably, a probe element 702 is in contact with the portion 46 of the **top metal layer 36** defining the **test pad 26**'. The probe element 702 does not contact the portion 44 of the **top metal layer 36** defining the **bond pad 22**'.") Ex. 1008, ¶82.

### J. Independent Claim 9

1. Element 9[preamble] — "method for testing a semiconductor wafer prior to performing a flip chip bumping process"

To the extent the preamble is limiting, *Mardi* discloses this element. Ex. 1008, ¶83-84. *Mardi* discloses a method for testing a wafer prior to performing a flip chip bumping process so as not to damage the bond pad: "Fig. 6 is a flow diagram depicting ... a process for fabricating an integrated circuit including a semiconductor component testing process ...." Ex. 1005-6, 2:66-3:2.

FIG. 6

Ex. 1005-4, Fig. 6. Testing occurs at step 606, and a flip chip bumping process occurs later at step 614. Ex. 1005-9, 7:24-36 ("damage to the bond pad 22A is avoided during the testing at step 606"); Ex. 1005-8, 6:51-55 ("At step 614, the semiconductor substrate is bumped. That is, bumped contacts (e.g., solder balls) are formed on the substrate in electrical communication with the bump pads using a conventional bumping process.") Ex. 1008, ¶84.

## 2. Element 9[a] — "providing a flip chip bonding pad having a region for performing said bumping process"

Mardi discloses this element. Ex. 1008, ¶85. Mardi discloses "a flip chip bonding pad having a region for performing said bumping process" as shown for element 1[a] above. To the extent the method claim step of "providing" this

structural feature requires additional disclosure, *Mardi* discloses "providing" such a structure via fabrication in step 604 of the Figure 6 method: "The semiconductor substrate 10 fabricated at step 604 is then tested in accordance with the test process 601." Ex. 1005-8, 6:10-12.

3. Element 9[b] — "integrally constructing a test pad with said bonding pad to form an integral conductive structure such that separate interconnect testing lines from said test pad to said bonding pad are not present in said integral structure"

Mardi discloses this element. Ex. 1008, ¶86. Mardi discloses this element as shown for element 1[b] above. To the extent the method claim step of "integrally constructing" this structural feature requires additional disclosure, Mardi discloses "integrally constructing" such a structure via fabrication in step 604 of the Figure 6 method: "The semiconductor substrate 10 fabricated at step 604 is then tested in accordance with the test process 601." Ex. 1005-8, 6:10-12.

4. Element 9[c] — "disposing said test pad coplanar with said flip chip bonding pad"

Mardi discloses this element. Ex. 1008, ¶87. Mardi discloses this element as shown for element 1[c] above. To the extent the method claim step of "disposing" this structural feature requires additional disclosure, Mardi discloses "disposing" such a structure via fabrication in step 604 of the Figure 6 method: "The semiconductor substrate 10 fabricated at step 604 is then tested in accordance with the test process 601." Ex. 1005-8, 6:10-12.

# 5. Element 9[d] — "said test pad including a probe region for performing a wafer test prior to performing said bumping process"

Mardi discloses this element. Ex. 1008, ¶88. Mardi discloses this element as shown for element 1[d] above. To the extent the method claim step of "disposing" this structural feature requires additional disclosure, Mardi discloses "disposing" such a structure via fabrication in step 604 of the Figure 6 method: "The semiconductor substrate 10 fabricated at step 604 is then tested in accordance with the test process 601." Ex. 1005-8, 6:10-12.

### K. Independent Claim 10

1. Element 10[preamble] — "an interface assembly for a semiconductor wafer"

Mardi teaches this element as shown for element 1[preamble] above. Ex. 1008, ¶89.

2. Element 10[a] — "a flip chip bonding pad including a region for performing a bumping process"

Mardi teaches this element as shown for element 1[a] above. Ex. 1008, ¶90.

3. Element 10[b] — "a test pad integrally constructed with said bonding pad"

Mardi teaches this element as shown for element 1[b] above. Ex. 1008, ¶91.

4. Element 10[c] — "said test pad being coplanar relative to said flip chip bonding pad"

Mardi teaches this element as shown for element 1[c] above. Ex. 1008, ¶92.

5. Element 10[d] — "said test pad . . . including a probe region for performing wafer-level testing prior to performing said bumping process"

Mardi teaches this element as shown for element 1[d] above. Ex. 1008, ¶93.

6. Element 10[e] — "a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another"

Mardi teaches this element as shown for claim 5 above. Ex. 1008, ¶94.

7. Element 10[f] — "said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer"

*Mardi* teaches this element as shown for claim 6 above. Ex. 1008, ¶95.

### VIII. GROUND 2: CLAIMS 1-10 ARE OBVIOUS OVER *MARDI* IN VEIW OF A POSITA'S KNOWLEDGE

As addressed in Ground 1, *Mardi* fully discloses all elements of claims 1-10. Alternatively, it would have been obvious to a POSITA to modify *Mardi* in view of the POSITA's knowledge to achieve the features of claims 1-10. Ex. 1008, ¶96.

## A. Independent Claim 1 (and all dependent claims) — "wafer-level testing"

As discussed for claim 1, *supra*, with reference to Figures 6 and 9, *Mardi* discloses "performing wafer-level testing prior to performing said bumping process." Ex. 1001-5, 4:6-8. First, Figure 9 illustrates testing with a **probe element** 902.

Ex. 1005-5, Fig. 9. Second, Figure 6 shows testing *before* the bumping process. Ex. 1005-8, 5:54-56.

Ex. 1005-4, Fig. 6; Ex. 1008, ¶97.

Further, *Mardi* confirms Figures 6 and 9 show "wafer-level testing." In particular, *Mardi* says "the term 'semiconductor component' is meant to encompass a substrate having multiple semiconductor dice" (Ex. 1005-7, 3:30-32), as shown in Figure 1.

Ex. 1005-2, Fig. 1; Ex. 1008, ¶98. A POSITA understands a "substrate having multiple semiconductor dice" is a wafer. Ex. 1008, ¶99. Relative to Figure 6, *Mardi* says "the process 600 is described with respect to a semiconductor component comprising a substrate with a plurality of semiconductor dice," *i.e.*, a wafer. Ex. 1005-8, 5:65-67. *Mardi* teaches process 600 relates to a wafer that is singulated or diced at the mounting step 616. Ex. 1005-9, 7:1-2 ("If the substrate includes multiple dice, the dice are singulated (i.e., diced) before mounting.") Thus, *Mardi* teaches "wafer-level testing." Ex. 1008, ¶99.

Alternatively, a POSITA would have found it obvious to use *Mardi*'s process for "wafer-level testing" because POSITAs knew that wafer-level testing (as opposed to testing one chip at a time) reduces manufacturing costs and

manufacturing time. U.S. Patent No. 5,550,480 to Nelson *et al.* was filed in 1994 (over 10 years before the '173 patent), and shows that a POSITA would have knowledge of the benefits of testing semiconductor devices at the wafer level:

Generally, integrated devices are fabricated in a thin flat substrate material commonly referred to as a semiconductor wafer. After fabrication, the integrated devices in the semiconductor wafer are tested, the semiconductor wafer is separated or divided into individual semiconductor chips or die, and each chip is encapsulated in a package. Since each semiconductor chip typically contains a large number of integrated devices, there is a probability of producing one or more defective integrated devices. Therefore, it is desirable to test the integrated devices prior to packaging them to ensure that time, money, and manufacturing capacity are not wasted by packaging defective semiconductor chips. Moreover, testing semiconductor chips in wafer form is easier and more cost efficient than testing a single semiconductor chip that has been separated from the semiconductor wafer. In other words, wafer-level testing or probing, i.e., testing semiconductor chips before the semiconductor wafer is separated into individual chips, reduces the manufacturing costs and cycle times associated with manufacturing semiconductor products.

Ex. 1010-7, 1:13-33; *see also* Ex. 1011-1, [57]; Ex. 1011-9, 1:23-49 ("wafer level testing" of wafer comprising flip-chip type semiconductor chips) (2004); Ex. 1012-19, 1:18-27; Ex. 1012-21, 6:42-46 (wafer-level testing of flip chips) (2003); Ex. 1004-1, [57] (same) (2005). Ex. 1008, ¶100-101. These references show a POSITA

knew wafer-level testing of flip-chips reduces manufacturing costs and cycle times. A POSITA would have used the *Mardi* testing method to test flip-chips at the wafer-level. Thus, "wafer-level testing" as claimed in claim 1 (and claims 2-7 that depend from claim 1) would have been obvious to a POSITA. Ex. 1008, ¶102.

B. Claim 5 — "The interface assembly of claim 1 further comprising a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another."

As discussed for claim 5 in Ground 1, *Mardi* expressly discloses claim 5. Ex. 1008, ¶¶ 69-72. Alternatively, it would have been obvious to modify *Mardi* to include a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another. Ex. 1008, ¶103. A POSITA knows that **top conductor layer 36** is a metal layer, and this layer can include conductive routing interconnect in addition to the conductive metal that makes up **test pad 26A** and **bond pad 22A**. A POSITA knows this because metal layers are typically fabricated as solid metal layers which are then patterned to remove portions of the metal and leave behind structures such as routing interconnect (*e.g.*, traces) and test/bond pads.

This knowledge is evidenced by patent references that predate the '173 patent's September 29, 2004 filing date, such as *Yong* (published September 18, 2003) (Ex. 1007-1); U.S Patent No. 6,392,301 to Waizman (issued May 21, 2002) ("*Waizman*") (Ex. 1013); and U.S. Patent Application Publication 2005/0037601 to

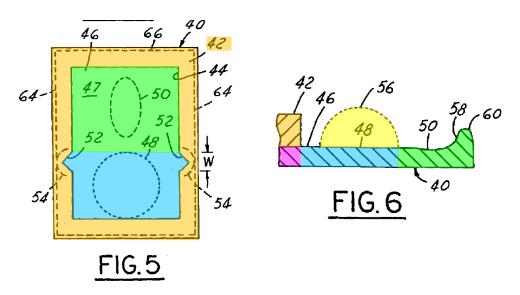

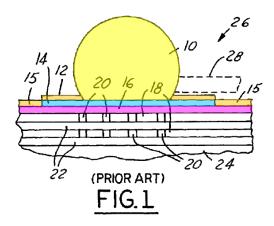

Hsu (filed October 27, 2003) ("Hsu") (Ex. 1014). For example, as discussed in Ground 5, infra, Yong discloses pad 10 (which has probe region 14 and wire bond region 12) as part of the upper conductive metal layer 28:

Ex. 1007-2, Fig. 2. Pad 10 is coplanar with, and electrically connected to, other routing interconnect traces that are part of upper conductive layer 28. Ex. 1007-10 to -11, [0013]-[0015]; Ex. 1008, ¶104.

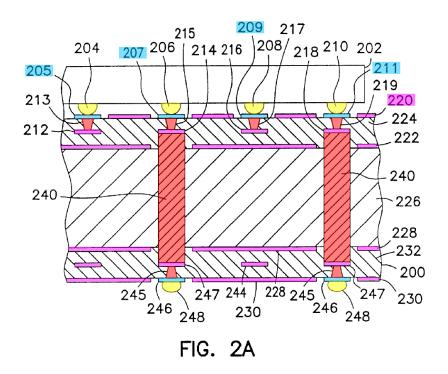

Similarly, *Waizman* discloses metal routing/trace layer 220, which is coplanar with pads 205, 207, 209, and 211 (Ex. 1013-8, 3:1-4:12):

Ex. 1013-3, Fig. 2a. And *Hsu* discloses "patterned trace layer 33" which is coplanar with "a plurality of contact pads 330" (Ex. 1014-14, [0046]):

Ex. 1014-7, Fig. 3C; Ex. 1008, ¶105.

Yong, Waizman, and Hsu show that it was common—and a POSITA would have known—to include a redistribution layer for interconnect routing on the same metal layer that is used to form the bond/test pads. Ex. 1008, ¶106. A POSITA would know that such interconnect would be electrically connected to one or more

bonding/test pads in order to route the signals connected to those pads to "the semiconductor devices/circuits within the semiconductor portion 32" of *Mardi*. Ex. 1005-7, 4:45-48. Thus, it would have been obvious to modify *Mardi* to include a first metal redistribution layer electrically connected to said bonding and test pads, and being co-planar with one another. Ex. 1008, ¶106.

C. Claim 6 — "The interface assembly of claim 5 wherein said first metal redistribution layer is electrically connected by way of a via to a second redistribution layer being disposed in a different plane than the first redistribution layer."

As discussed for claim 6 in Ground 1, *Mardi* expressly discloses vias are used to connect "redistribution layers" at different planes within the semiconductor. As noted above with respect to claim 5, top conductor layer 36 and/or the uppermost conductor layer within the internal conductor portion 34 correspond to a "first metal redistribution layer" (Ex. 1005-7, 4:36-39; Ex. 1005-3, Fig. 5), and at least one of the conductor layers within the internal conductor portion 34 corresponds to the claimed "second redistribution layer":

Ex. 1005-3, Fig. 5; Ex. 1005-7, 4:39-42 ("[I]nternal conductor portion 34 compris[es] one or more internal conductor layers between the substrate portion 32 and the top conductor layer 36.") *Mardi* teaches these "redistribution layers" are separated by insulating layers and connected by vias: "all of the conductor layers may be separated by respective insulating layers, and may be connected to each other using vias (not shown for simplicity)." Ex. 1005-7, 4:42-45; Ex. 1008, ¶107.

However, Figure 5 of *Mardi* does not expressly show insulating layers between the redistribution layers and it does not expressly show the vias connecting the redistribution layers. These features are described in the text. Alternatively, these features would be obvious based on a POSITA's knowledge. A POSITA was familiar with both insulation layers and vias. *Id. Mardi* says these features are "not shown for simplicity" (Ex. 1005-7, 4:42-45), and a POSITA would agree it is not necessary for these features to be illustrated. Ex. 1008, ¶108.