US006731627B1

## (12) United States Patent Gupta et al.

(10) Patent No.: US 6,731,627 B1 (45) Date of Patent: May 4, 2004

### (54) VIRTUAL LOOP CARRIER SYSTEM

# (75) Inventors: Dev V. Gupta, Concord, MA (US); Subra Dravida, Shrewsbury, MA (US); Vikram Saksena, Acton, MA (US); Paiman Nodoushani, Northboro, MA (US); Denis Claveloux, Hudson, NH (US); Sriram Narayan, Westford, MA (US); Kyung-Yeop Hong, Acton, MA (US); Anthony Monteiro, North Andover, MA (US); Wei Ye, Westford, MA (US); David S. Yoon, Windham, NH (US)

- (73) Assignee: Cisco Technology, Inc., San Jose, CA

(US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/441,587

- (22) Filed: Nov. 17, 1999

#### Related U.S. Application Data

- (60) Provisional application No. 60/130,170, filed on Apr. 20, 1999, and provisional application No. 60/108,924, filed on Nov. 17, 1998.

- (51) **Int. Cl.**<sup>7</sup> ...... **H04L 12/66**; H04L 12/50 (52) **U.S. Cl.** ...... **370/352**; 370/359; 370/463

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,533,018 A | * 7/1996  | DeJager et al 370/395.5 |

|-------------|-----------|-------------------------|

| 5,687,174 A | * 11/1997 | Edem et al 370/446      |

| 5,696,790 A | 12/1997   | Graham et al 375/238    |

| 5,724,355 A | * 3/1998  | Bruno et al 370/401     |

| 5,742,596 A | * 4/1998  | Baratz et al 370/356    |

| 5,778,001 A | 7/1998    | Nakayama et al.         |

| 5,818,511 A | 10/1998   | Farry et al 725/116     |

| 5,896,443 A |           | Dichter 379/93.08       |

| 5,936,936    | A          |   | 8/1999                | Alexander et al 370/216    |

|--------------|------------|---|-----------------------|----------------------------|

| 6,065,061    | A          |   | 5/2000                | Blahut et al 709/203       |

| 6,069,899    | A          | * | 5/2000                | Foley 370/494              |

| 6,075,784    | A          |   | 6/2000                | Frankel et al 370/352      |

| 6,101,182    | A          |   | 8/2000                | Sistanizadeh et al 370/352 |

| 6,141,339    | A          | * | 10/2000               | Kaplan et al 370/395.61    |

| 6,195,714    | B1         |   | 2/2001                | Li et al 370/352           |

| 6,198,752    | <b>B</b> 1 |   | 3/2001                | Lee 370/238                |

| 6,208,653    | <b>B</b> 1 |   | 3/2001                | Ogawa et al 370/229        |

| 6,289,097    | <b>B</b> 1 |   | 9/2001                | Gregory et al 370/352      |

| 6,339,594    | B1         | * | 1/2002                | Civanlar et al 370/352     |

| 6,370,153    | B1         | * | 4/2002                | Eng 370/438                |

| 6,385,193    | B1         |   | 5/2002                | Civanlar et al.            |

| 6,388,997    | B1         | * | 5/2002                | Scott 370/280              |

| 6,404,782    | B1         | * | 6/2002                | Berenbaum et al 370/522    |

| 6,407,997    | <b>B</b> 1 |   | 6/2002                | DeNap et al 370/352        |

| 6,414,950    | <b>B</b> 1 | * | 7/2002                | Rai et al 370/338          |

| 6,414,952    |            | * | 7/2002                | Foley 370/352              |

| 6,456,594    | <b>B</b> 1 | * | 9/2002                | Kaplan et al 370/238       |

| 6,487,405    | B1         |   | 11/2002               | Dapper 455/424             |

| 2001/0012319 |            |   | 8/2001                | Foley 375/222              |

| 2001/0043568 | A1         |   | 11/2001               | McHale et al 370/254       |

|              |            |   | 11 15 THE POST OF THE |                            |

#### OTHER PUBLICATIONS

"Lucent Joins Home Networking Crowd", Electronics News, Oct. 12, 1998, vol. 44, No. 2240, p. 64.

Primary Examiner—Hassan Kizou

Assistant Examiner—Timothy Lee

(74) Attorney, Agent, or Firm—Hamilton, Brook, Smith &

Reynolds, P.C.

#### (57) ABSTRACT

A loop carrier system includes a home local area network having plural telephone modules and a hub coupled to in-home telephone wiring. The telephone modules and the hub communicate voice signals over the in-home wiring in a dedicated frequency band above baseband POTS. The hub converts between voice signals and voice packets and is connected to a network access device for transferring the voice packets from the home local area network to a telecommunications network which routes the voice packets to a gateway. The gateway converts between the voice packets and a circuit format compatible with a local digital voice switch.

#### 20 Claims, 45 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG. 3A

FIG. 3B

U.S. Patent

May 4, 2004

Sheet 5 of 45

FIG. 4

FIG. 5

FIG. 7B

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 20

FIG. 21

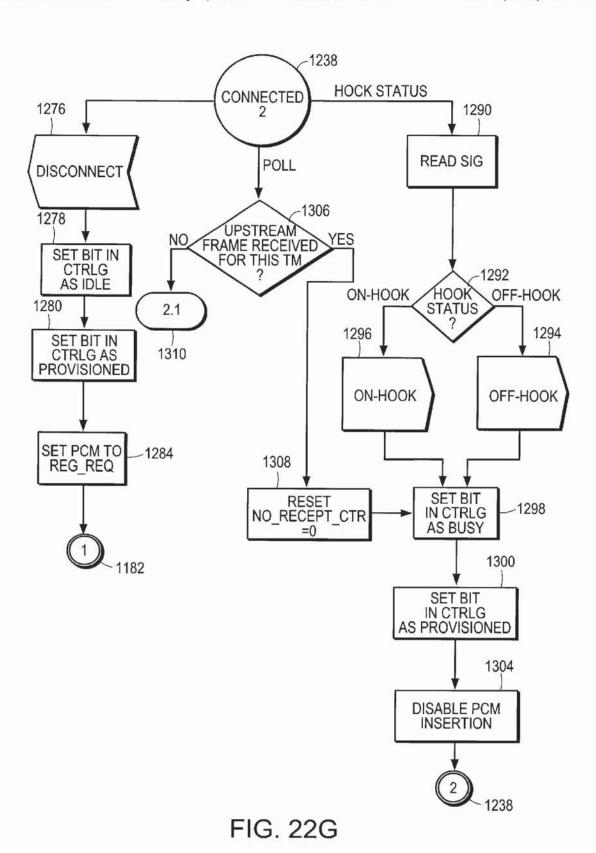

FIG. 22B

FIG. 22C

FIG. 22D

FIG. 22E

FIG. 22F

24

FIG. 22H

27

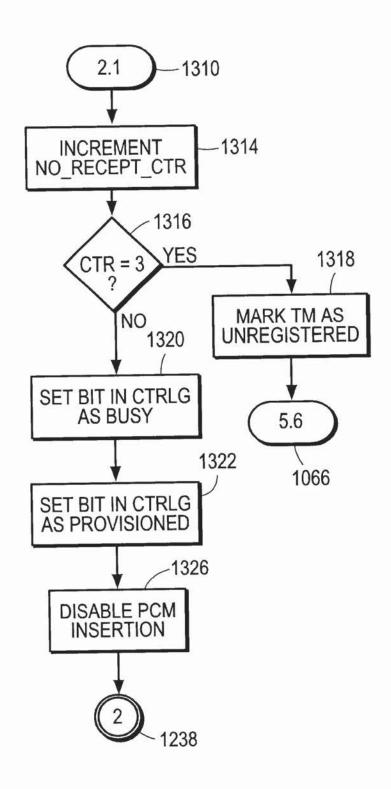

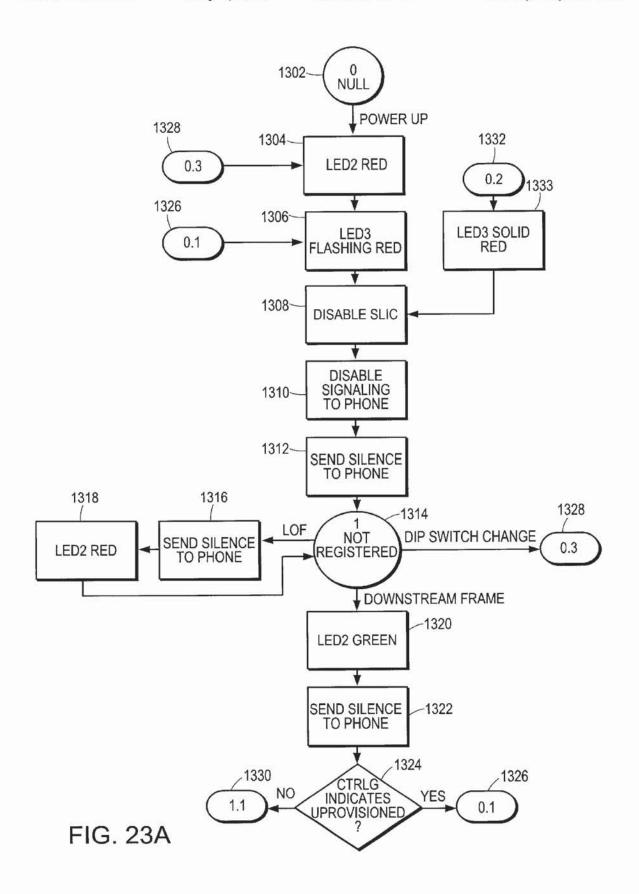

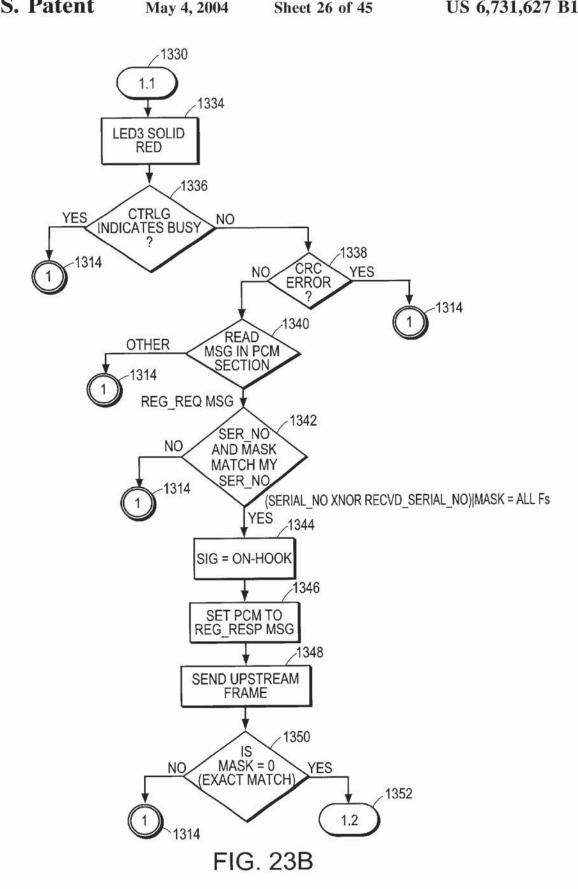

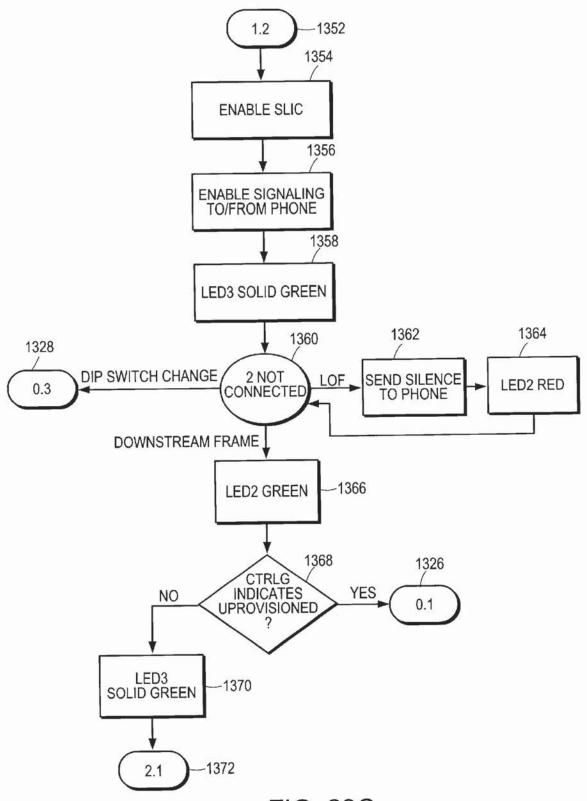

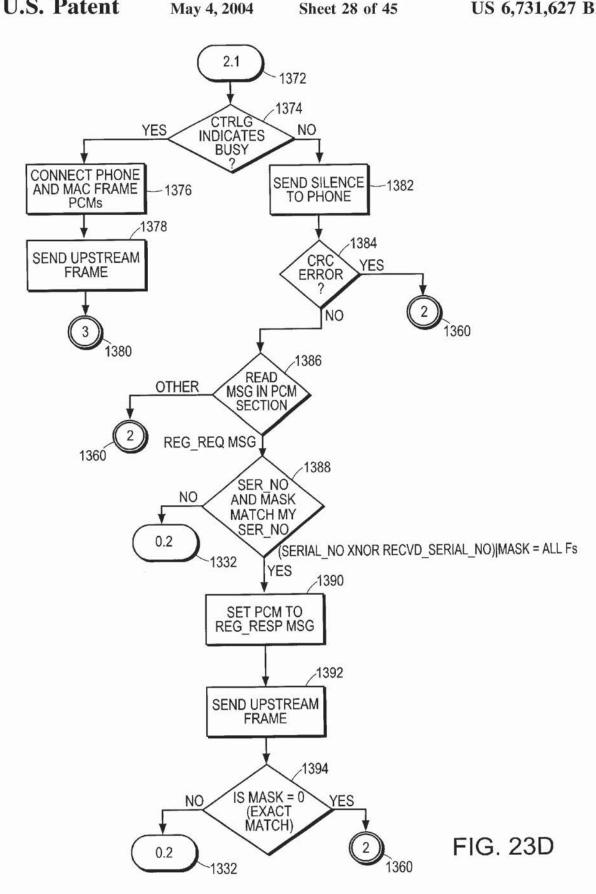

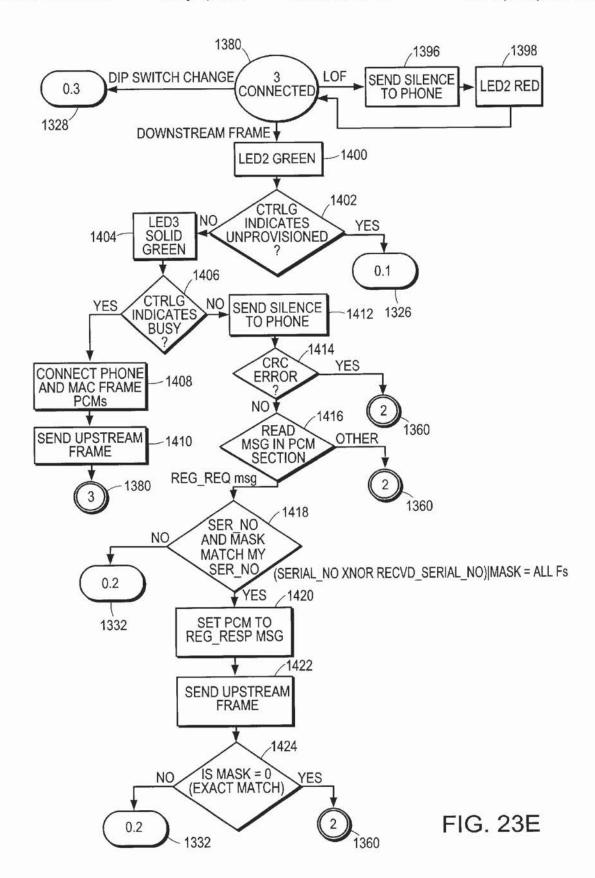

FIG. 23C

Sheet 31 of 45

U.S. Patent

May 4, 2004

Sheet 32 of 45

Sheet 33 of 45

FIG. 26B

FIG. 26D

FIG. 26E

May 4, 2004

FIG. 26F

FIG. 26G

FIG. 27A

FIG. 28

FIG. 29

U.S. Patent

May 4, 2004

Sheet 42 of 45

US 6,731,627 B1

FIG. 33

U.S. Patent

May 4, 2004

Sheet 45 of 45

US 6,731,627 B1

## VIRTUAL LOOP CARRIER SYSTEM

#### RELATED APPLICATIONS

This application claims the benefit of U.S. Provisional Application No. 60/108,924, filed on Nov. 17, 1998, and U.S. Provisional Application No. 60/130,170, filed Apr. 20, 1999, the entire teachings of which are incorporated herein by reference.

## BACKGROUND OF THE INVENTION

The public switched telephone network (PSTN) based on circuit switching technology has served well for the past several decades in making a broad range of telephony services possible for consumers and businesses. However, its infrastructure is fraught with cost inefficiencies, inflexible service creation and delivery platforms, and manuallyintensive, error-prone operations, administration and maintenance (OA&M) applications and processes. All of these aspects combine to keep prices artificially high and make service creation and delivery intervals unduly long from an end-user perspective. In contrast, the broadband networking platforms that are being deployed for data services are optimized for high efficiencies and fast service creation due to the speed at which the market is driving the growth of new services. Given the large-scale investments in broadband 25 network technologies being undertaken by the service providers to meet the explosive growth in demand, planning is underway to migrate voice services from the legacy circuitswitched environment to the newer broadband networking environment to take advantage of economies of scale. However, this migration needs to be carefully planned so it does not create a significant discontinuity in the features, services, and overall quality that customers have come to expect from the well-established circuit-switched network.

In the past, the typical home had a single telephone line for all the residents to share. Today, there has been a dramatic increase in the need for communication services in the home driven by such factors as telecommuting, home offices, residential facsimile machines and computer networking including Internet access.

In the traditional PSTN environment, each telephone circuit, called a "loop", requires a separate wire pair from the access service provider's facilities to the subscriber's locathat may be available at each subscriber location, especially for residential subscribers. The access service provider generally does not have sufficient capacity in the loop facilities to provide multiple telephone lines to every subscriber.

Furthermore, most homes have been wired for one or at 50 most two telephone lines. Adding a new telephone line beyond this usually requires adding new wiring in the home. This home wiring limit acts as a barrier to residential users who may want additional telephone lines and to service providers who would like to gain additional revenues from 55 in the upstream direction using time division duplex transproviding new communication services.

# SUMMARY OF THE INVENTION

It is desirable to provide a migration strategy that uses the broadband network for multiplexing efficiencies (which 60 leads to significantly lower unit costs) and logical provisioning benefits (which leads to significant reduction in service turn-up times) while continuing to leverage the PSTN's switching and service control engines (Class 4/5 switches, SCPs, etc.) for providing value-added services. 65 This low-risk migration can be achieved by using a gateway between the broadband network and the PSTN.

It is desirable to provide a capability that could enable greater communication services in the home without adding wiring in the home or to the service provider's facilities.

The present invention provides a gateway between the broadband network and the PSTN while also providing distribution of multiple voice lines over a home local area

In accordance with the present invention, a loop carrier system includes a home local area network having plural 10 telephone modules and a hub coupled to a communications medium. The communications medium in a preferred embodiment comprises in-home telephone wiring, though other communications media are possible, including wireless. The telephone modules and the hub communicate digitized voice signals over the in-home wiring in a dedicated frequency band located above the traditional baseband services, e.g., plain old telephone service (POTS). The hub converts between voice signals and voice packets and is connected to a network access device for transferring the voice packets from the home local area network to a telecommunications network which routes the voice packets to a gateway. The gateway converts between the voice packets and a circuit format compatible with a local digital voice switch. The voice packets can be any packet format such as ATM cells (e.g., ATM Adaptation Layer versions AAL1, AAL2, AAL5) or IP packets. The network access device can be, for example, an xDSL device, a cable modem or wireless access device.

According to an aspect of an embodiment of the system, the hub includes a data interface circuit for converting between data signals and data packets and a packet multiplexer for multiplexing data packets with voice and signaling packets for transfer between the hub and the gateway.

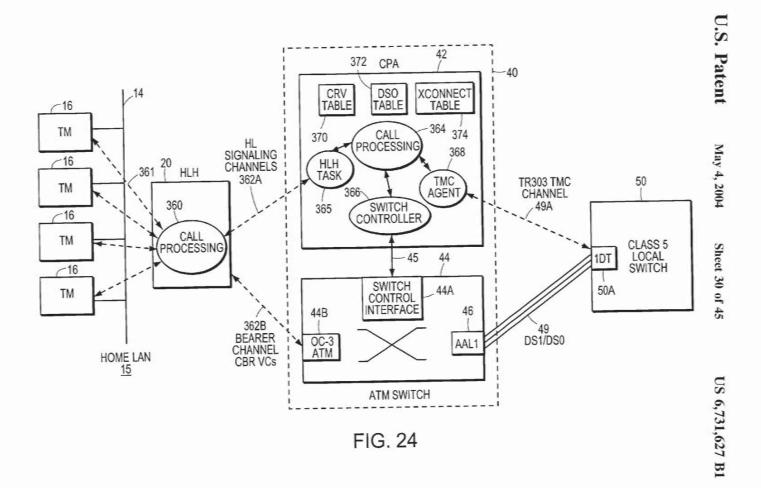

In an embodiment, the gateway comprises an ATM switch and a call processing adjunct which controls the conversion between voice packets and the circuit format at the ATM switch. The call processing adjunct communicates with the hub and with the local digital switch using signaling protocols (e.g., Media Gateway Control Protocol and GR-303, respectively) for controlling call processing in the loop carrier system.

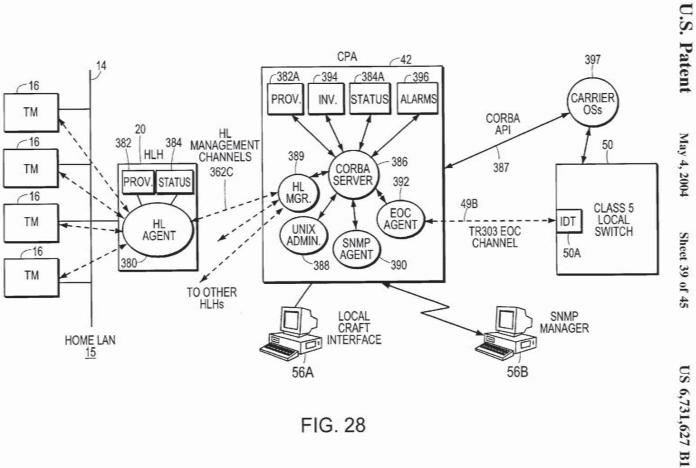

According to an aspect of the invention, a network element includes a Common Object Request Broker Architecture (CORBA)-based server, CORBA-based managed tion. This places practical limits on the number of circuits 45 objects accessible by the CORBA-based server and a CORBA-based applications programming interface (API). The CORBA-based API is coupled to an external operations support system which can manage the plural CORBA-based managed objects directly.

> According to an aspect of the home local area network, a communication protocol is used between the hub and the telephone modules in which the voice signals are transmitted within frames of digital bits from the hub to the modules in the downstream direction and from the modules to the hub mission. The downstream and upstream frames include communication timeslots assigned to individual modules for communication between the modules and the hub. The timeslots are assigned such that no two modules have the same timeslot, thereby avoiding collision on the in-home wiring.

> According to another aspect of the home local area network, the digital bits are transmitted using a raised cosine pulse signal modulated by a carrier signal at the center of the dedicated frequency band.

> In accordance with the invention, a telephone module for communicating between a local hub and a telephone set over

telephone wiring includes a digitizer for converting analog voice signals from the telephone set to digital signals at a baseband frequency and a modulator for modulating a carrier signal with the digital signals for transmission in a dedicated frequency band above baseband over the telephone wiring to the local hub.

According to another aspect of the home local area network, a timing recovery mechanism in the absence of a clock that is traceable to the Primary Reference Clock on the public network is robust to clock drift, cell delay variation 10 and cell impairments.

According to another aspect of the invention, a method of configuring a selected ATM endpoint connected to a server across an ATM network for Internet Protocol (IP) over ATM communications comprises transmitting an unsolicited message from the server to the selected ATM endpoint. The message is send at a first transmission interval over an associated virtual circuit and includes a server IP address and an ATM endpoint IP address. At the ATM endpoint, the unsolicited message is received, the server IP address and the ATM endpoint IP address are extracted from the unsolicited message, and an SNMP TRAP message is sent to the server.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of preferred embodiments of the invention, as illustrated in the accompanying drawings in which like reference characters refer to the same parts throughout the different views. The drawings are not necessarily to scale, emphasis instead being placed upon illustrating the principles of the invention.

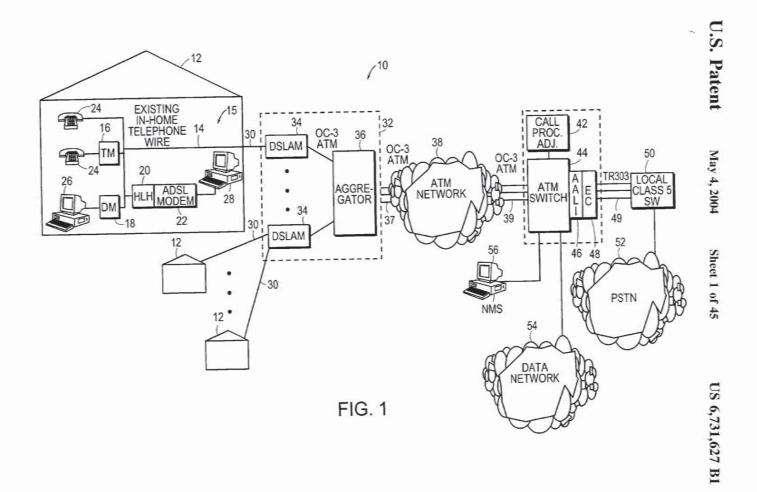

- FIG. 1 is a block diagram of an embodiment of a virtual loop carrier system in accordance with the invention.

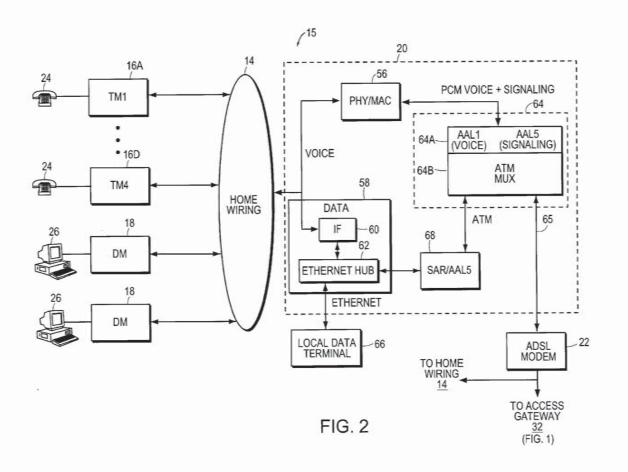

- FIG. 2 is a block diagram of the home local area network shown in FIG. 1.

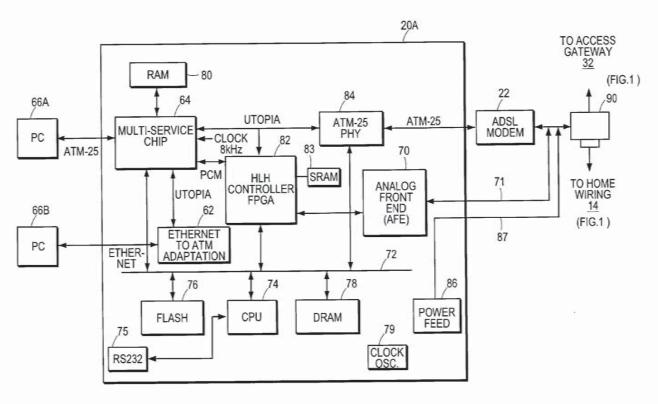

- FIG. 3A is a block diagram of an embodiment of a home LAN hub for use in the system of FIG. 1.

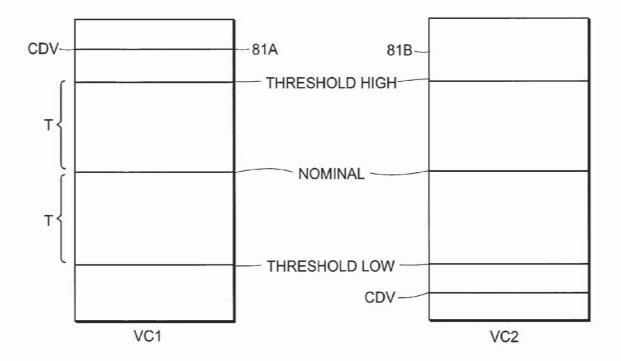

- FIG. 3B is a block diagram showing buffer fullness thresholds used in a timing recovery mechanism in the home LAN hub.

- FIG. 3C is a state diagram illustrating adaptive clock recovery for the timing recovery mechanism in the home 45 LAN hub.

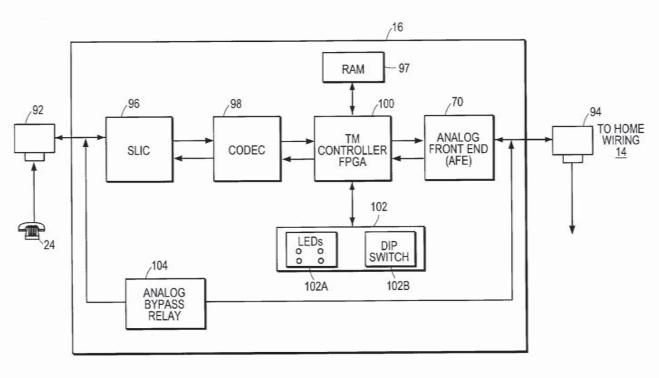

- FIG. 4 is a block diagram of an embodiment of a telephone module for use in the system of FIG. 1.

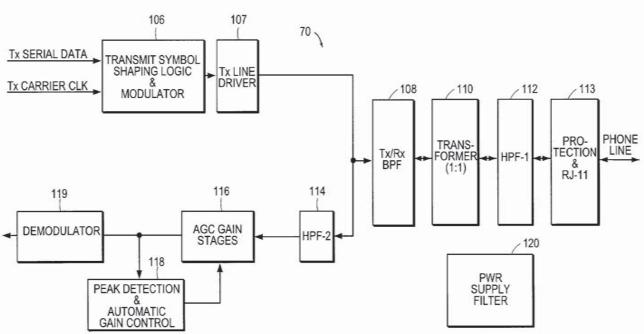

- FIG. 5 is a schematic block diagram of analog front end circuitry for use in the home LAN hub of FIG. 3A and the telephone module of FIG. 4.

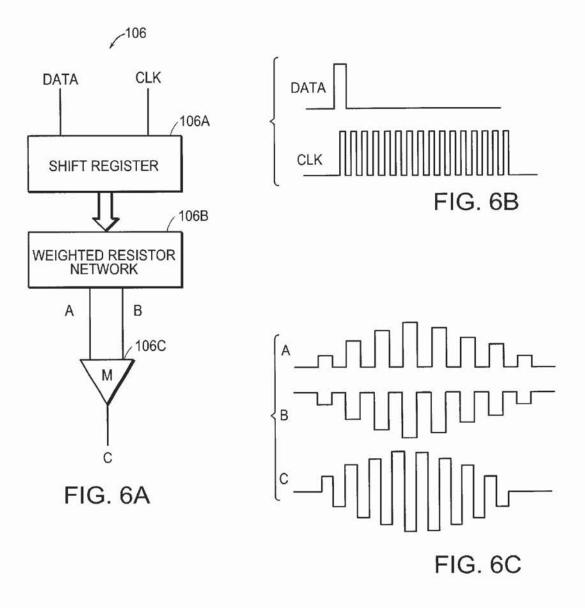

- FIG. 6A is a circuit diagram of a transmit symbol shaping logic and modulator circuit for the circuitry of FIG. 5. FIG. 6B shows data and clock signal inputs to the circuit of FIG. 6A. FIG. 6C shows signal outputs of the circuit of FIG. 6A.

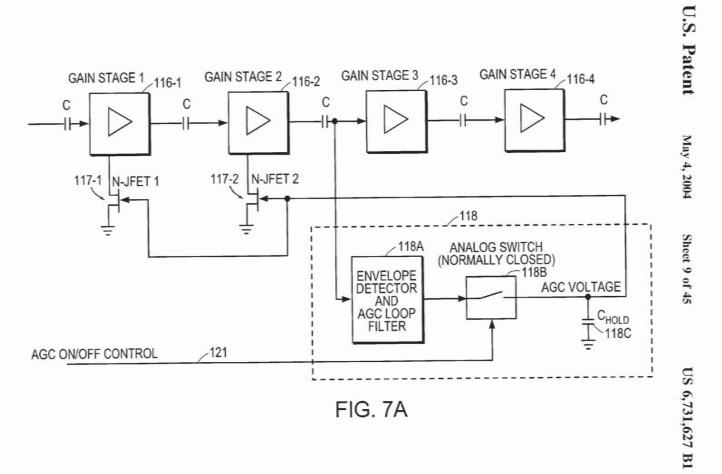

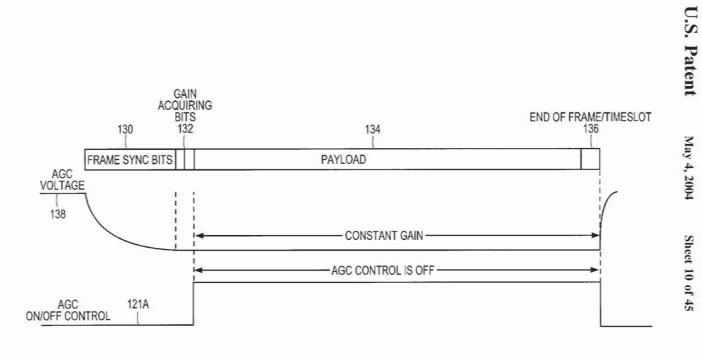

- FIG. 7A is a schematic block diagram of automatic gain control circuitry of the circuitry of FIG. 5. FIG. 7B is a timing diagram illustrating automatic gain control in relation to reception of a downstream frame or an upstream timeslot for the circuitry of FIG. 7A.

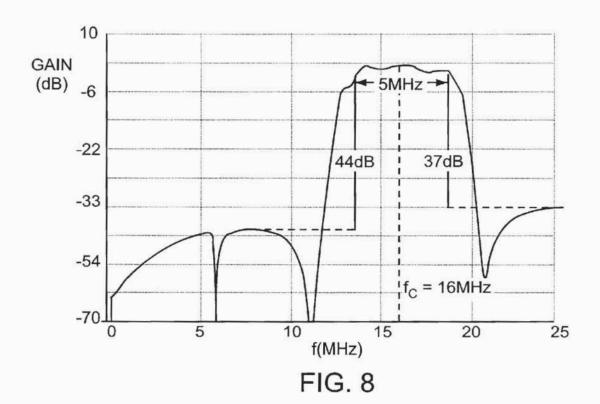

- FIG. 8 shows the spectral characteristics of a transmit/receive bandpass filter used in the circuitry of FIG. 5.

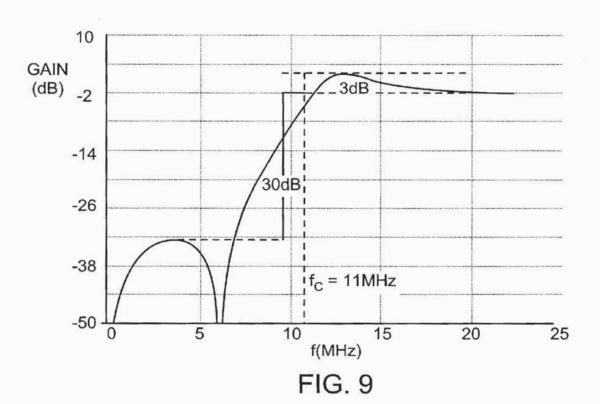

- FIG. 9 shows the spectral characteristics of a transmit/receive highpass filter used in the circuitry of FIG. 5.

- FIG. 10 shows the spectral characteristics of a receive highpass filter used in the circuitry of FIG. 5.

4

- FIG. 11 shows a simulated baseband data signal X(t) in the time domain.

- FIG. 12 shows the frequency spectrum X(f) for the simulated baseband data signal of FIG. 11.

- FIG. 13 shows a passband signal Xtx(t) in the time domain.

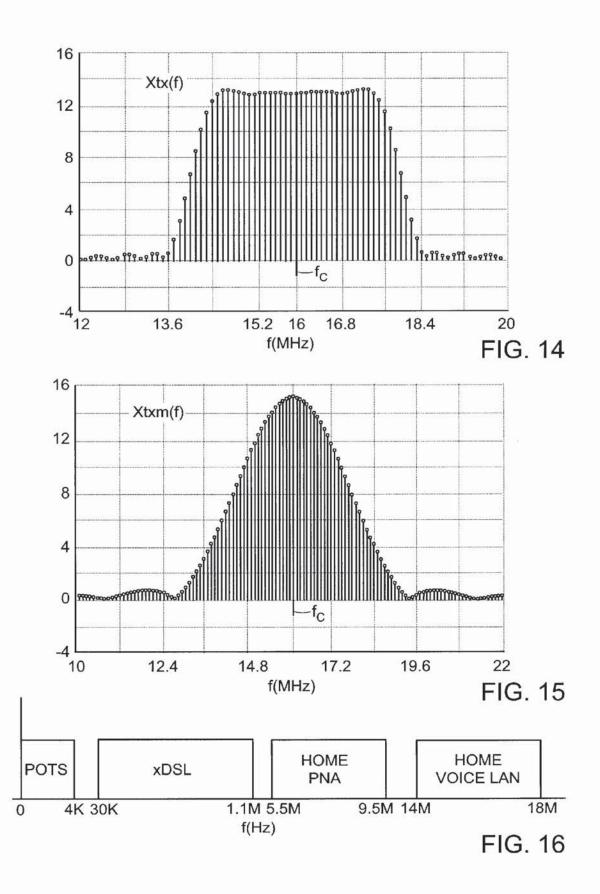

- FIG. 14 shows the frequency spectrum for the passband signal Xtx(f).

- FIG. 15 shows a simulated spectrum for passband signal Xtxm(f).

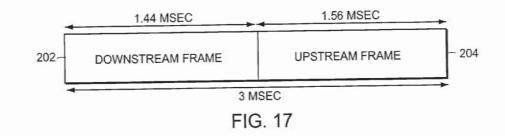

- FIG. 16 illustrates a spectrum arrangement on the in-home wiring which accommodates voice signals in a dedicated passband located above existing communication services.

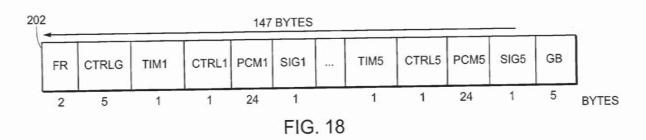

- FIG. 17 shows media access layer framing for the home local area network.

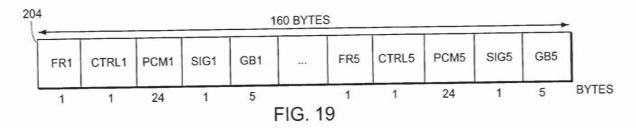

- FIG. 18 shows a framing format for the downstream frame shown in FIG. 17.

- FIG. 19 shows a framing format for the upstream frame shown in FIG. 17.

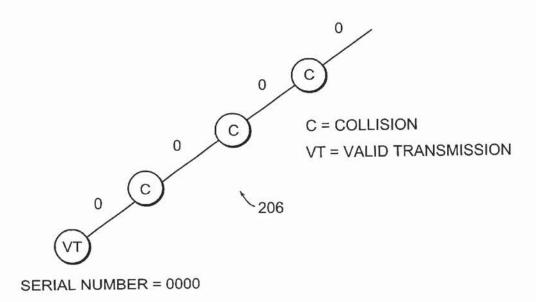

- FIG. 20 illustrates a partial binary tree used in determining misconfigured telephone modules.

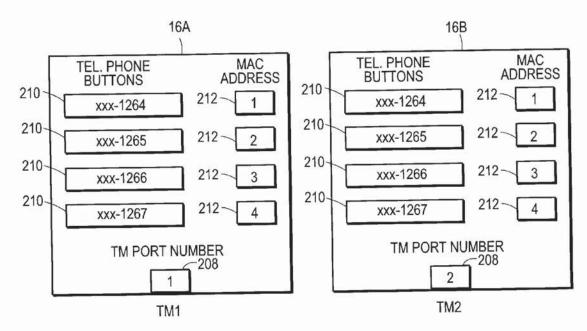

- FIG. 21 illustrates a configuration arrangement for a pair of telephone modules.

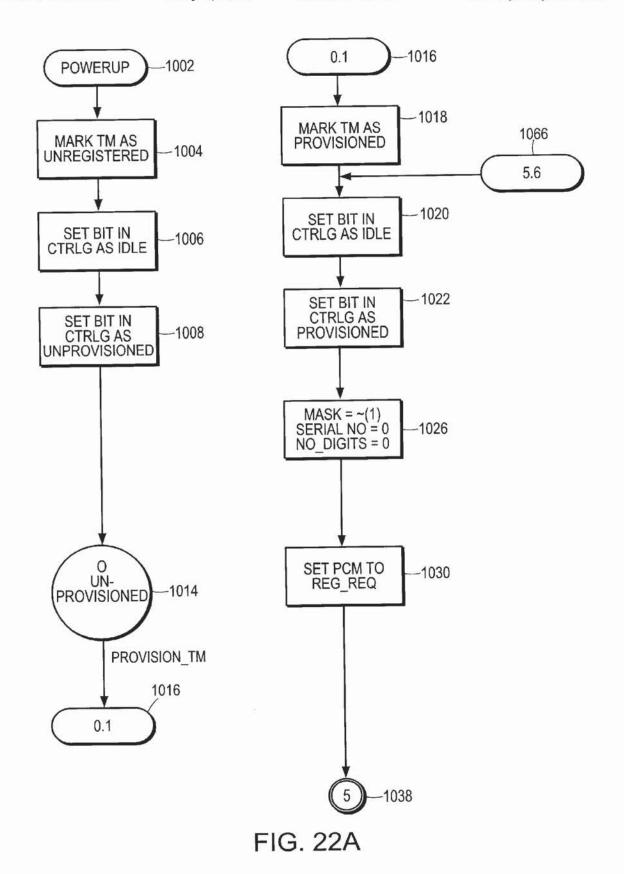

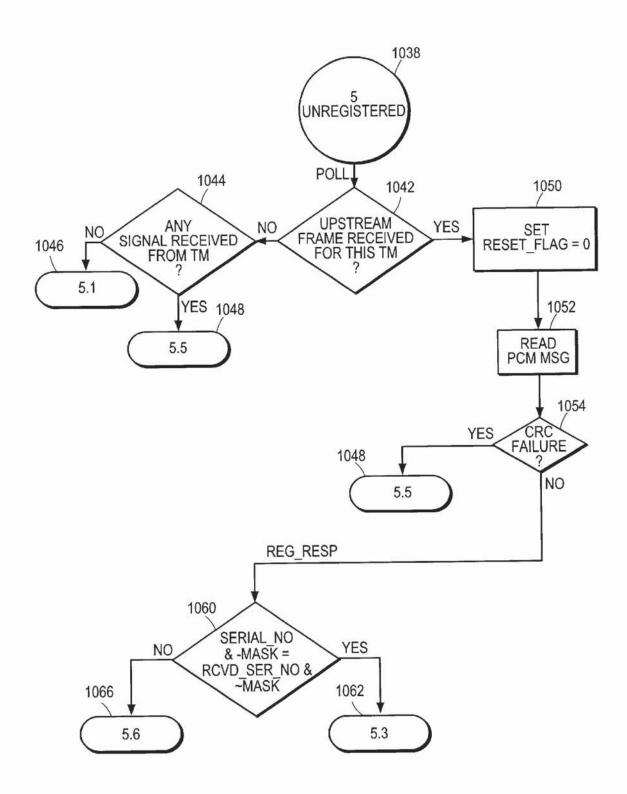

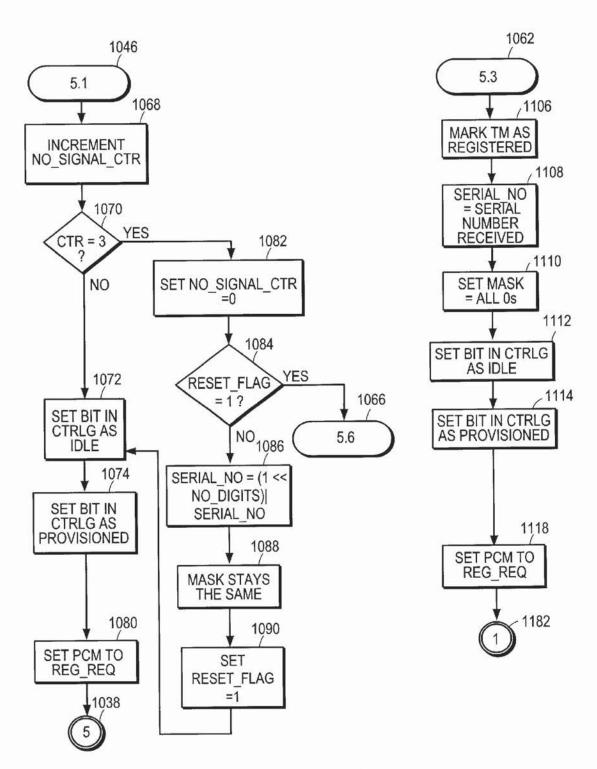

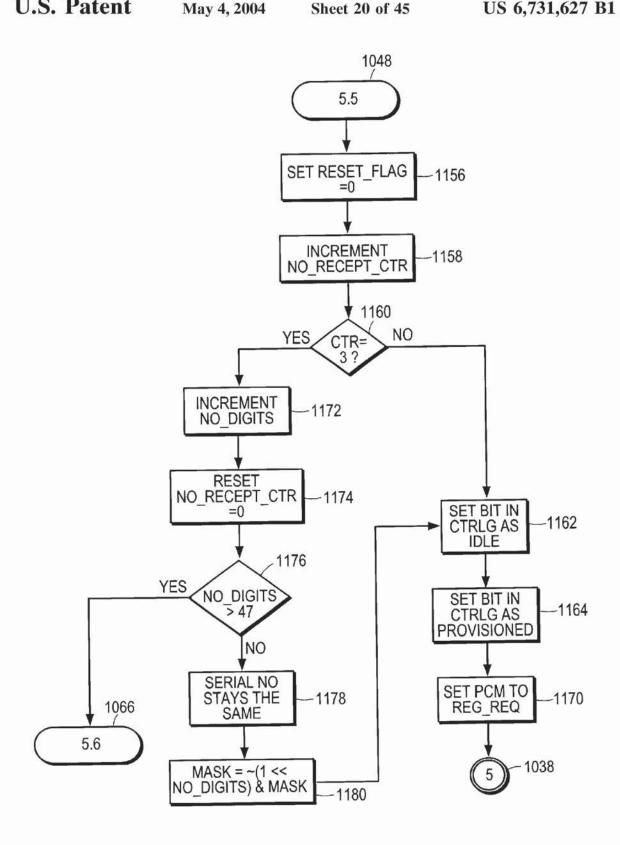

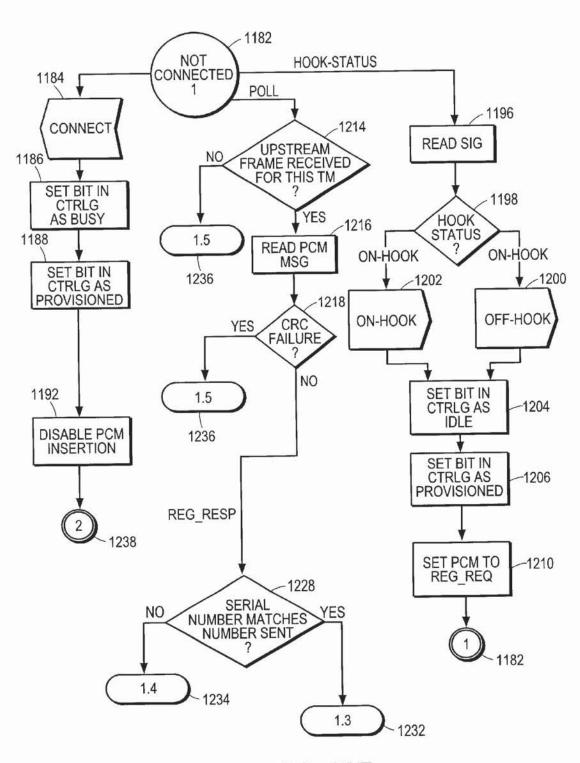

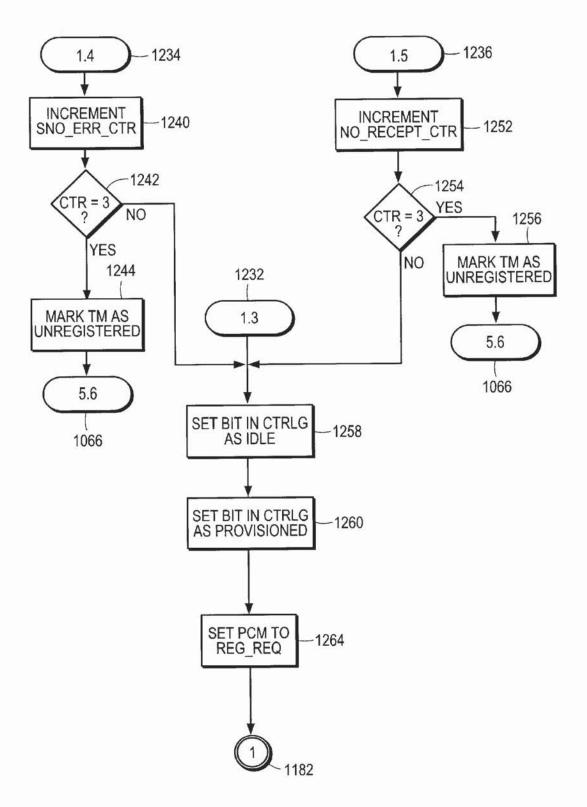

- FIGS. 22A-22H are state machine diagrams for the home LAN hub of FIG. 3A.

- FIGS. 23A-23E are state machine diagrams for the telephone module of FIG. 4.

- FIG. 24 is a block diagram of a call processing arrangement for the loop carrier system of FIG. 1.

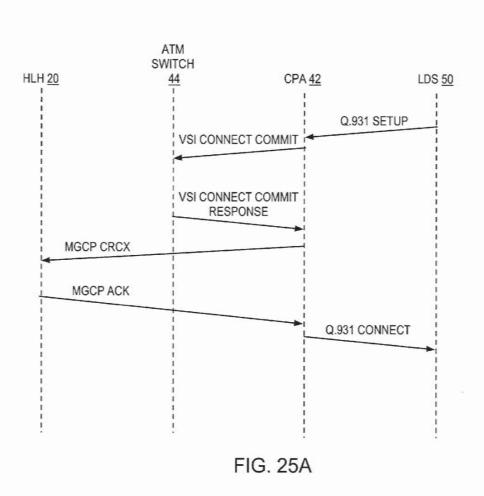

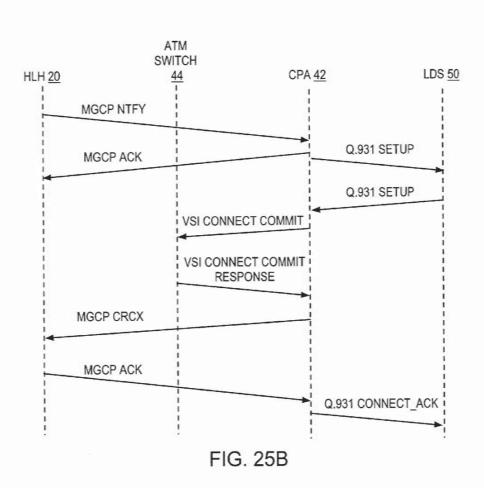

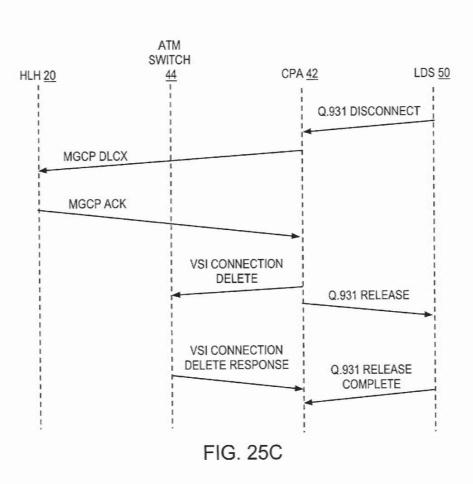

- FIGS. 25A-25C show call processing flows for the call processing arrangement of FIG. 24.

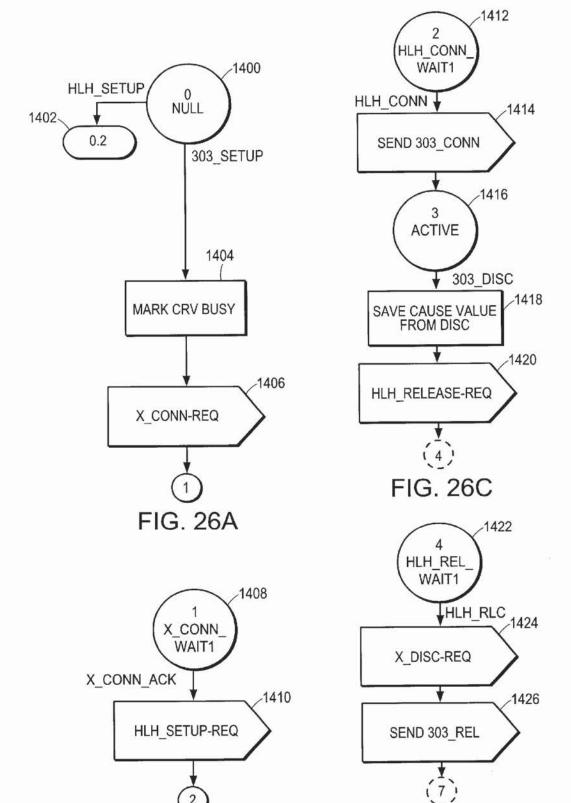

- FIGS. 26A-26G are state machine diagrams for a call processing task at the call processing adjunct of FIG. 24.

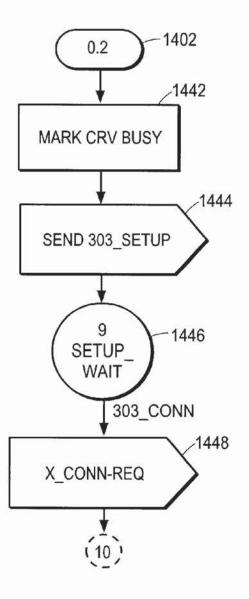

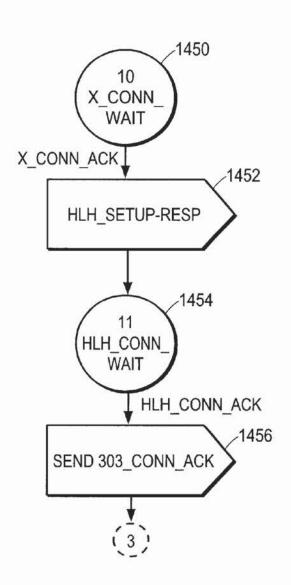

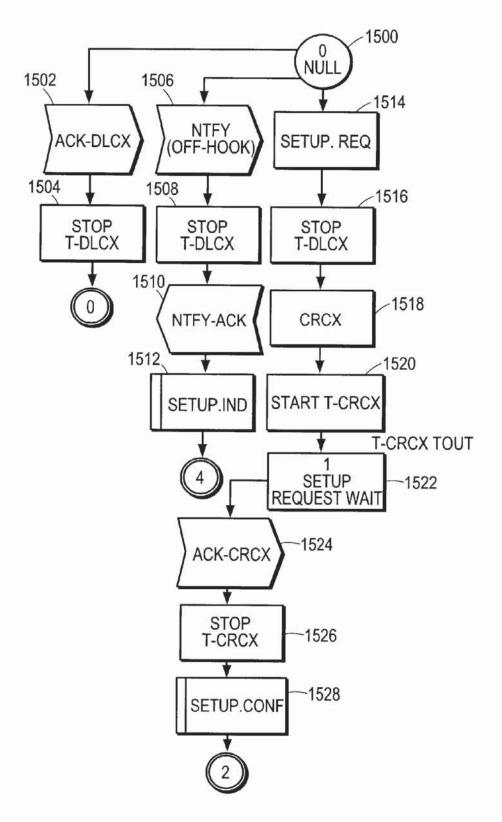

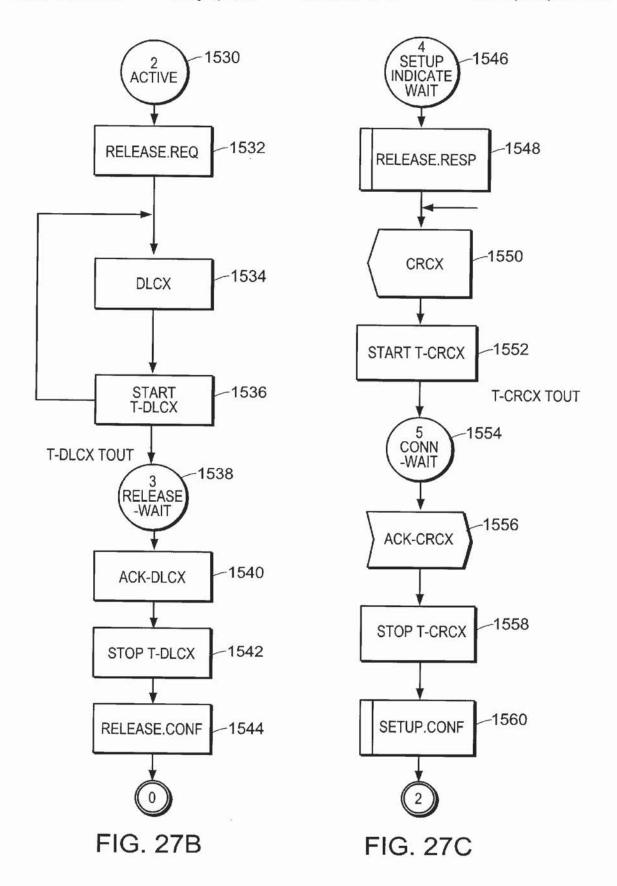

- FIGS. 27A-27C are state machine diagrams for a home LAN hub signaling task at the call processing adjunct of <sup>0</sup> FIG. 24.

- FIG. 28 shows a management plane architecture diagram for the loop carrier system of FIG. 1.

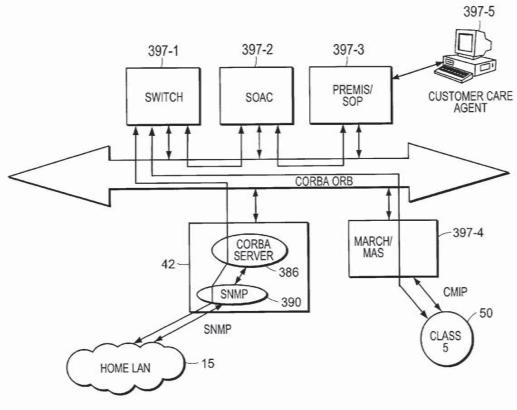

- FIG. 29 is a management plane diagram illustrating a CORBA-based provisioning configuration.

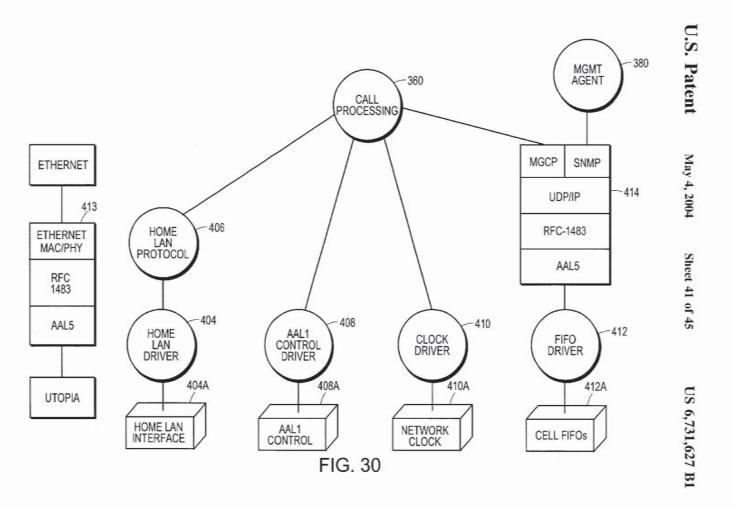

- FIG. 30 is a software architecture diagram for the home LAN hub of FIG. 1.

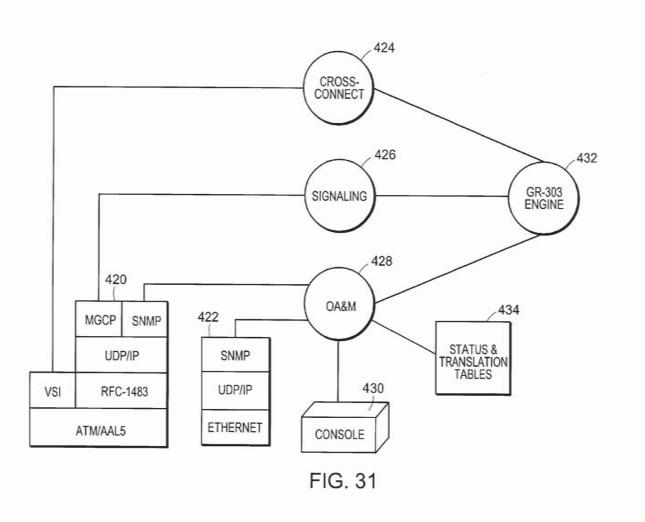

- FIG. 31 is a software architecture diagram for the gateway of FIG. 1.

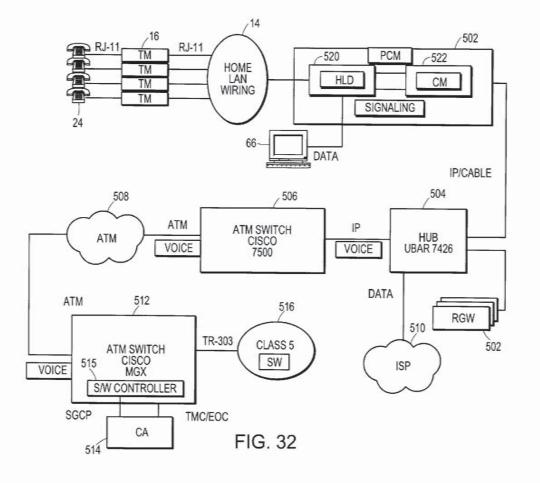

- FIG. 32 is a block diagram of an alternate embodiment of a loop carrier system.

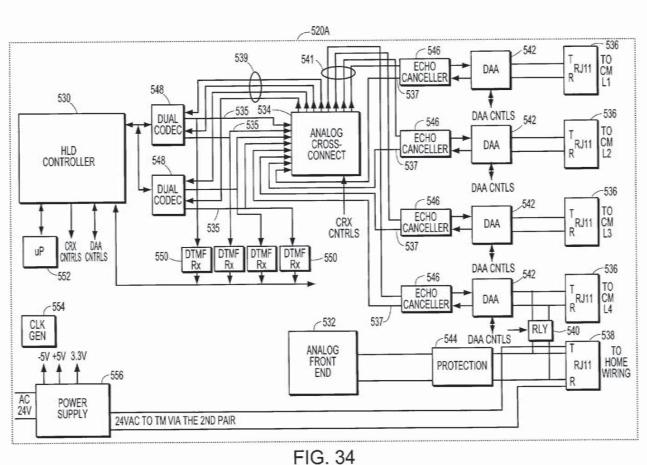

- FIG. 33 is a block diagram of an alternate embodiment of a home local area network.

- FIG. 34 is a schematic block diagram of an alternate embodiment of a home LAN device for the network of FIG. 33.

# DETAILED DESCRIPTION OF THE INVENTION

#### 1.0 Virtual Loop Carrier System Overview

FIG. 1 is a block diagram that shows the main elements of an embodiment of an exemplary virtual loop carrier system 10 which provides access to voice and data services in accordance with the present invention. The system 10 comprises a number of local area networks (LANs) 15 at

48

homes 12; an access gateway 32 which aggregates voice and data from the home LANs 15 for transport over an ATM network 38; and a virtual loop gateway (VLG) 40 which connects the voice and data between the ATM network 38 and a local digital switch (LDS) 50 or data network 54.

The home LAN 15 includes telephone modules (TMs) 16 and data modules (DMs) 18 connected to a home LAN hub (HLH) 20 over existing in-home telephone wiring 14. For a telephone call, the TM 16 converts analog voice signals from a connected telephone 24 to digital signals in the form of pulse code modulation (PCM) samples. The TMs 16 transmit and receive PCM samples to and from the HLH 20 using a physical layer/media access control layer protocol described further herein. The HLH 20 converts the PCM samples along with channel associated signaling (CAS) into an ATM cell format optimized for transport of voice. The embodiment described herein uses an ATM cell format known as ATM Adaptation Layer 1 (AAL1). Other signaling and management information and data is formatted by the HLH 20 according to ATM Adaptation Layer 5 (AAL5). It 20 should be noted that the PCM voice samples can alternatively be formatted according to AAL2 or AAL5.

The AAL1 and AAL5 formatted cells are transmitted to the access gateway 32 over a local copper loop 30 using an asynchronous digital subscriber line (ADSL) modem 22. It should be noted that in alternate embodiments described further herein, the local loop 30 can be a cable television transmission facility, the ADSL modem 22 can be a cable modem and the voice samples can be converted to Internet Protocol (IP) packets rather than ATM cells. The ADSL modem 22 can also be an xDSL device or a wireless access device.

The access gateway 32 includes digital subscriber line access multiplexers (DSLAMs) 34 which terminate the ADSL connections 30 and an ATM aggregator 36 which aggregates the AAL1 and AAL5 cells received from the HLHs 20 for transport over the ATM network 38 to the virtual loop gateway 40 through SONET based transmission facilities 39. The DSLAM 34 and ATM aggregator 36 can be conventional networking equipment such as Cisco Systems equipment numbers 6100/6200 and 6400, respectively.

At the virtual loop gateway 40, the AAL1 and AAL5 cells are converted to a standard format known as GR-303 that is compatible with standard loop carrier interfaces 49 on the 45 LDS 50. The GR-303 standard (formerly known as TR-303) is a Bellcore-defined interface between a local digital switch (LDS) and systems that provide network access to local loop telephone subscribers. In particular, the AAL1 cells are routed through ATM switch 44 and converted by AAL1 module 46 to PCM samples for insertion into DS0s of the GR-303 interfaces 49. In addition, the AAL5 cells are routed to a call processing adjunct (CPA) 42 which converts these particular cells to GR-303 call processing messages. These conversions enable subscribers at homes 12 to access wellknown services and custom calling features offered by the LDS 50 in a transparent manner, thereby obviating the need for access service providers to develop and deploy their own software and services.

It should be apparent that while the foregoing overview has described the handling of voice and data transport from the home LAN 15 towards the LDS 50, i.e., in the "upstream" direction, the system 10 also provides voice and data transport from the LDS 50 towards the home LAN 15 in the "downstream" direction in a similar manner.

The system components, including the home LAN 15 and the VLG 40, are now described in more detail.

6

#### 2.0 Home LAN

The home LAN 15 includes telephone modules 16 and data modules 18 connected to a home LAN hub 20 over the existing in-home telephone wiring 14. The home LAN 15 is shown in more detail in the functional block diagram of FIG.

2. In a particular embodiment, the home LAN 15 accommodates up to four telephone modules 16A–16D and one or more data modules 18.

The HLH 20 connects to the home wiring 14 to transmit and receive voice and data. As described further herein, voice signals associated with the TMs 16A–16D are carried on the home wiring 14 according to a physical (PHY) layer/media access control (MAC) layer protocol that is terminated in a PHY/MAC block 56. The PHY/MAC block 56 provides PCM voice samples and signaling in the upstream direction using time division multiple access from the TMs to a multi-service chip (MSC) device 64 which includes an ATM adaptation layer circuit 64A that is configured to convert the PCM samples to AAL1 cells and the signaling to AAL5 cells. These AAL1 and AAL5 cells are multiplexed via an ATM multiplexer 64B which in this embodiment is part of the MSC device 64.

Data signals associated with the DMs 18 are carried separately over the home wiring 14 using a known protocol such as the Home Phoneline Networking Alliance (HomePNA) specification. These data signals are applied to a data module 58 which includes a data interface 60 for converting the HomePNA data signals to Ethernet frames. An Ethernet hub 62 coupled to the data interface 60 connects these Ethernet frames to a SAR/AAL5 device 68 which provides segmentation and reassembly to AAL5 cells for inclusion in the multiplex signal 65 provided by the ATM multiplexer 64B. The Ethernet hub 62 also terminates an Ethernet connection to a local data terminal 66. The multiplex signal 65 provided by the ATM multiplexer 64B is applied to the ADSL modem 22 which connects to the access gateway 32 (FIG. 1) over the local loop 30. Downstream ATM signals are received from the access gateway 32 through the ADSL modem 22 and demultiplexed by ATM multiplexer 64B to AAL1 and AAL5 cells. These received downstream AAL1 and AAL5 cells are converted to PCM voice samples and signaling by ATM adaptation layer circuit 64A for transport on the home wiring 14 via PHY/MAC block 56.

#### 2.1 Components

2.1.1 Home LAN Hub

The HLH 20, as shown in FIG. 1, provides a gateway function for communication between devices on the home LAN 15 and the wide area network (WAN) that includes the access gateway 32, ATM network 38, the virtual loop gateway 40, the LDS 50 and other networks including the PSTN 52 and data networks 54. The HLH 20 has been described above with reference to the functional block diagram of FIG. 2. An embodiment of a home LAN hub is shown in FIG. 3A. The HLH 20A includes an analog front end (AFE) 70 which connects to the home wiring 14 (FIG. 1) on line 71 for transmitting and receiving voice signals according to the home LAN physical (PHY) layer that is described further herein. An HLH controller 82, which can be implemented as a field programmable gate array (FPGA), is connected to the AFE 70 and provides an interface to the home LAN MAC layer also described further herein.

The MSC 64, which can be an Ericsson device number PBM-990-08-1, provides the AAL1/AAL5 and ATM multiplexing functions described above with reference to FIG. 2. In particular, the MSC 64 provides conversion between

AAL1 cells and PCM voice samples and aggregates ATM-25 data from an external PC 66A, Ethernet data from Ethernet to ATM adaptation block 62', and PCM voice from the HLH controller FPGA 82 in the upstream (i.e., to the network) direction. The MSC 64 accesses an external RAM 580. The HLH controller FPGA 82 throttles the total upstream traffic to the maximum upstream data rate of the ADSL modem 22. This allows the MSC 64 to give higher priority to the time-critical voice traffic through a quality-of-service buffer therein. The HLH controller FPGA 82 also adapts the 10 internal clocking of PCM data in the HLH 20A to track the rate of data received from the network over the ATM-25 PHY interface 84.

The HLH 20A includes a power feed 86 which converts AC power to the internal voltages required by the HLH and 15 to provide power to the telephone modules 16 (FIG. 1) through a second line 87 in the two-pair wiring arrangement typical of most homes. Note that the first line 71 in the two-pair wiring arrangement is used for voice and data according to the PHY/MAC layer protocol aspect of the 20 16.

The HLH 20A further includes a CPU 74 with synchronous DRAM 78, SRAM 83, flash memory 76, RS-232 interface 75 and clock generator 79. The CPU 74 configures and monitors the HLH 20A.

As noted above, the MSC 64 provides circuit emulation with channel associated signaling (CAS). The following describes an improvement which allows the MSC chip to support CAS for T1 type circuits.

A standard E1 multiframe comprises 16 consecutive frames numbered from 0 to 15 with a multiframe repetition rate of 500 Hz. The frame includes 32 channel timeslots numbered from 0 to 31 with a frame repetition rate of 8 KHz. Each channel timeslot is composed of 8 bits numbered 1 to 8. A multiframe alignment signal comprising the value 0000 occupies bit positions 1 to 4 of channel timeslot 16 in frame 0.

For channel associated signaling in the E1 interface, channel timeslot 16 in frames I to 15 is assigned for CAS (i.e., ABCD bit allocation) as follows: Channel timeslot 16 40 in frame 1—ABCD (for channel 1), ABCD (for channel 16) Channel timeslot 16 in frame 2—ABCD (for channel 2), ABCD (for channel 17) and so on down to:

Channel timeslot 16 in frame 15—ABCD (for channel 15), ABCD (for channel 30)

In a PCM mode of operation of the MSC 64, a frame sync signal PCM\_FS and four data valid signals along with clock and data signals are used to suit different types of codec circuits. The frame sync signal is used to identify frame boundaries. To identify multiframe boundaries and to sup-

8

port CAS signaling in structured circuit emulation, a multiframe sync signal PCM\_MFS is included. The timing transitions on PCM\_MFS and PCM\_FS are made the same. The repetition period of the PCM\_MFS signal is 2 ms. The PCM\_MFS signal indicates the start of the 2 ms multiframe and points out the first channel timeslot in the first frame. The CAS signaling bits can be located within the multiframe boundaries as follows:

ABCD bits for channel 1 are sampled during channel timeslot 16 in frame 1;

ABCD bits for channel 2 are sampled during channel timeslot 16 in frame 2;

ABCD bits for channel 3 are sampled during channel timeslot 16 in frame 3;

ABCD bits for channel 4 are sampled during channel timeslot 16 in frame 4; etc.

Note that the A signaling bits for channels 1 to 4 occupy bit position 1 (MSB) of each corresponding channel timeslot 16.

Cell coding for T1 is now described in relation to CAS. In AAL1 CAS mode, the payload part of the structure is one multiframe in length. For 64 kbps T1 with extended superframe (ESF) framing, this portion of the AAL1 structure is 24 bytes in length. In an E1 PCM interface, the payload portion in one multiframe is 16 bytes in length. Therefore, a mapping mechanism is needed when providing circuit emulation in the MSC. In particular, a cell encoding from PCM to AAL1 is as follows. 16 bytes from E1 multiframe 1 and 8 bytes from E1 multiframe 2 are collected to form AAL1 payload block 1. AAL1 payload block 2 is formed by collecting the remaining bytes from E1 multiframe 2 and 16 bytes from E1 multiframe 3. The succeeding payload blocks are formed in the same manner. A problem is that two different ABCD signaling bits can be extracted from multidifferent multiframes. To avoid this problem, the previous signaling status can be selected at the price of 2 ms signaling transition delay.

A cell decoding from AAL1 to PCM is as follows. 24 bytes from AAL1 payload block 1 are divided into 16 bytes and 8 bytes. The first 16 bytes are used for E1 multiframe 1. The remaining 8 bytes and 8 bytes from AAL1 payload block 2 are used for E1 multiframe 2. The remaining 16 bytes from AAL1 payload block 2 are used for E1 multiframe 3. The signaling bits from AAL1 payload block 1 are used for E1 multiframes 1 and 2. The signaling bits from AAL1 payload block 2 are used for E1 multiframe 3. This results in the same 2 ms signaling transition delay.

The MSC 64 is provided with a PCM multiframe which is converted into AAL1 blocks as shown in the following table:

| T     | 1 Superframe   |              | PCM Multiframe |                             |              | AAL1 Block |                              |              |

|-------|----------------|--------------|----------------|-----------------------------|--------------|------------|------------------------------|--------------|

| No.   | Data<br>Octets | Sign<br>Bits | No.            | Data<br>Octets              | Sign<br>Bits | No.        | Data<br>Octets               | Sign<br>Bits |

| М     | T1 (1-24)      | S1           | N              | T1 (1-16)                   | S1'          | M          | T1 (1-16)<br>&<br>T1 (17-24) | S1"          |

|       |                |              | N + 1          | T1 (17-24)<br>&<br>T2 (1-8) | S2'          |            | 29/20/40/20 - 20/20/20       |              |

| M + 1 | T2 (1-24)      | S2           | N + 2          | T2 (9-24)                   | S3'          | M + 1      | T2 (1-8)<br>&<br>T2 (9-24)   | S2"          |

An important consideration is the relationship between the signaling bytes { S1, S2}, {S1', S2',S3'} and {S1'', S2''}. It is preferable that S1"=S1 and S2"=S2 under all circumstances.

Even if the relative alignment between the PCM Multi- 5 frames and the AAL1 blocks changes, it is still preferable to carry all of the signaling bytes correctly (e.g., alignment can change if N+1, N+2 and N+3 multiframes are mapped into

The simplest way to achieve this is by mapping S1 into 10 S1', S2 into S2' and entering an invalid ABCD code into S3' (for example, invalid code 1010). In the MCS, mapping the signaling bytes from the PCM multiframe into AAL1 blocks requires that only the legal ABCD code words be inserted into the AAL1 blocks and that the invalid 1010 code be 15 contain one P format cell and seven non-P format cells. The deleted. In other words, the MSC looks at the incoming signaling bytes and ignores all ABCD codes with the code

When mapping the T1 superframe into PCM multiframe, strips this off, thereby always transporting all the legal

In the reverse direction, when the MCS generates the PCM multiframe from the received AAL1 blocks, the MSC inserts the illegal code 1010 as the extra signaling byte 25 which is stripped off to generate the T1 superframe from the PCM multiframe.

The VLC system 10 uses AAL1 to deliver voice services. Voice over AAL1 is a constant bit rate (CBR) service that implies that, in an ideal network, cells arrive at the receiver 30 cell impairments. Next, the maximum CDV is calculated. at a constant pre-determined rate. The receiver must lock on to this constant rate and stay synchronized to this network clock rate. In a real network, any clock synchronization algorithm on the receiver has to contend with cell delay variation (CDV), clock drift and cell impairments caused by 35 three other calls, together with an additional cell of data, for delays or congestion through the network. As a result of these problems, the cell arrival rate at the receiver is no longer constant (cells may even be dropped) leading to an unacceptable drop in voice quality. A network clock synchronization algorithm and implementation that is robust in 40 the face of CDV, clock drift and cell impairments is now described.

The basic clock drift problem is first described. The ADSL modem 22 that sources the ATM stream entering the HLH 20 has no clock available that is traceable to the Primary 45 4.417 ms. The external SRAM 83 is used for the purpose of Reference Clock on the network. The main clock oscillator on the HLH has a frequency of 32.768 MHz and a tolerance of 100 ppm. Over a period of time, any local reference clock generated from this clock will drift with respect to the network clock, causing ATM cell buffers to overflow or 50 underflow. The only source of network timing information on the HLH 20 is from the arrival of ATM cells containing AAL1 Circuit Emulation (CE) data. Therefore, it is necessary to devise a mechanism to infer network timing from the arrival of AAL1 cells containing voice samples, in the 55 presence of both CDV and cell impairments.

In order to provide such a network timing mechanism, several assumptions are made regarding the delivery of ATM cells from the access gateway 32 and ATM network 38 (FIG. 1). In particular, it is assumed that quality of service (QoS) is available at the DSLAM 34, that CES uses the structured data transfer (SDT) method with channel associated signaling (CAS) to transfer voice on AAL1 and that there is no padding of AAL1 ATM cells.

cells from the ADSL modem 22 are received through the ATM-25 PHY 84 into the HLH controller 82 and then into 10

the MSC 64. The MSC 64 requires a stable 8 KHz clock derived from the network clock. Clock synchronization is provided in the HLH controller 82 as described further herein.

The nominal rate of arrival of cells at the HLH 20 is first calculated. The SDT method uses two formats for transmitting AAL1 user data. In the first format (referred to as P format), there are 2 bytes of SAR overhead and 46 bytes of user data per cell. The first byte of overhead is a SAR header, consisting of a Sequence Number (SN) field, CS Layer indicator and a Sequence Number Protection (SNP) field. The second byte of overhead is a pointer. The second format (non-P format) includes the SAR header, followed by 47 bytes of user data per cell. A sequence of 8 ATM cells will AAL1 user data consists of superframes, each containing 24 bytes of TDM (voice) data belonging to one voice channel and one byte of CAS information.

From the foregoing, the following calculations can be every third signaling byte inserted is invalid and the MSC 20 made. In a sequence of 8 cells, there are 46 bytes (P format)+47\*7 bytes (non-P format)=375 bytes of user data. Since there are 25 bytes per superframe, there are 375/25=15 superframes in a sequence of 8 cells. Hence, the number of TDM bytes in 8 cells is 15\*24=360. Since each TDM byte represents 125 us, the 8 cell sequence should arrive in 360 bytes\*125 us/byte=45 ms, and the average time per ATM cell for each voice channel is 45 msec/8 cells 5.625 ms/cell.

> The actual rate of cell arrival at the HLH 20 is different from the average cell rate calculated above due to CDV and

> A measure of CDV at the HLH 20 can be determined by considering the following. In an embodiment in which the HLH 20 supports four independent voice calls, an ATM cell from one call can be queued behind one cell each from the a total of four cell delays. With a nominal link rate of 384 Kbits/sec between the DSLAM 34 and the ADSL modem 22, the delay for four cells is given as (53 bytes/cell\*8 bits/byte\*4 cells)/(384 Kbits/sec)=4.417 msec (also referred to as a cell delay of 4.417/5.625=0.7852 cells). Hence, ATM cells at the input to the HLH controller 82 experience CDV between 0 and a maximum of 4.417 ms. This CDV can be positive or negative with respect to the previous received cell, but its total cumulative value cannot exceed the value cell buffering to smooth out the random variations in the cell arrival rate.

The clock adjustment method described herein tracks the arrival of ATM cells from a virtual circuit (VC) carrying CES data and compares it against the rate of data being transferred to the TDM output (via the MSC 64, FIG. 3). As the local clock drifts with respect to the network clock, the fullness of the cell buffers in the SRAM 83 (or alternatively the fullness of a virtual buffer maintained in the HLH controller 82), either exceeds or falls below a nominal value, and can be used either to speed up or slow down the 8 KHz reference clock input to the MSC 64. Note that selecting the nominal buffer fullness is a tradeoff between the delay that can be tolerated and the susceptibility to buffer overflow/ 60 underflow due to CDV and reference clock drift.

The 8 KHz reference clock is generated by dividing the nominal oscillator clock (32.768 MHz) by 4096. The oscillator has a tolerance of 100 ppm or 3276.8 Hz, so the actual frequency is between 32.7647 MHz and 32.7713 MHz. In the downstream direction (i.e. from the network), ATM 65 Dividing these frequencies by 4096 gives a reference clock between 7999.2 Hz and 8000.8 Hz, causing a drift between this clock and the network clock. To adjust this clock, first

note that simply dividing by 4095 or 4097 to speed up or slow down the clock, respectively, is to be avoided since abrupt changes in reference frequency adversely affects voice quality. So, a half-cycle clock stretch is used to get the proper clock adjustment.

For example, if the oscillator 79 is running at the lower tolerance value of 32.7647 MHz then starting with the nominal divisor of 4096, provides a reference clock of 7999.2 Hz and a buffer fill rate of (8000-7999.2)=0.8 bytes/sec. Over time, the buffer fills causing cells to be dropped. When the buffer fullness exceeds a high threshold, the divisor is changed to 4095. In addition, the high portion of the reference clock is stretched by half a cycle of the oscillator clock. In this example, the oscillator clock halfcycle is 15.2603 ns. Hence the reference clock period is 30.52063ns\*4095+15.2603 ns=124.99724 us, and the reference frequency is 8000.18 Hz. At this frequency, the buffer empties at the rate of 0.18 bytes/sec, eventually causing the nominal buffer fullness threshold to be reached. When the actual fullness is less than the nominal fullness, a change is triggered to a divisor of 4096 with no clock stretch and the 20 reference clock returns to the original reference frequency (7999.2 Hz). In the case that the oscillator is operating at the higher tolerance value, the procedure is similar, except that only the half cycle clock stretch is needed and not a change in the divisor. In this case, the buffer fullness varies between 25 the nominal value and a low threshold, while the reference frequency changes from 8000.8 Hz to 7999.8 Hz.

Thus, the same buffer used to smooth out CDV is also used to adjust the local reference clock to the network clock such that there is no cell overflow or underflow.

As noted above, selection of buffer thresholds is a tradeoff between cell delay and probability of overflow/underflow. The clock adjustment algorithm described herein above calls for three buffer thresholds: a nominal threshold, a low threshold and a high threshold. These thresholds are calcu- 35 fullness is NOM). The variable "count" refers to the count lated next.

The nominal threshold is set to be two cells based on the delay that can be tolerated on the voice samples (11.25 ms). Assume that the high and low thresholds are symmetric about the nominal with a difference of T from the nominal, 40 NOM. If two VCs (VC1 and VC2) are active, the maximum difference in the buffer thresholds of the VCs is 2\*MaxCdv+ T, where MaxCdv denotes the maximum cell delay variation. This is true because CDV is independent for the two VCs (i.e. VC1 can experience a positive CDV of MaxCdv 45 calls, no TDM bytes are available for timing adjustment, and and VC2 can experience a negative CDV of MaxCdv). Additionally, the fullness can differ by up to T based on when VC2 became active in relation to VC1. Thus VC1 can have a buffer fullness of NOM+T+MaxCdv while VC2 can have a fullness of NOM-MaxCdv. Assuming that clock 50 adaptation is enabled for VC1, the clock will be speeded up, causing buffers for both VC1 and VC2 to drain down. This will continue until VC1's buffer drains down below NOM (a change of T+MaxCdv), at which time the clock is set back to nominal. VC2's buffer drains down by the same amount 55 and hence is at the level NOM-MaxCdv-(T+MaxCdv). To avoid underflow, this quantity must be greater than 0. Solving this inequality with NOM set to 2 cells and MaxCdv to 0.7852 cells (4.417/5.625), yields T<0.4295 cells (53 bytes/cell\*0.4295 cells=19.328 bytes). Setting T to 16 bytes 60 selection and averaging are done as described herein above satisfies this requirement. Thus, the nominal threshold is two cells and the high and low thresholds are set, respectively, to +16 bytes and -16 bytes from the nominal. The thresholds for buffers 81A, 81B for VC1, VC2, respectively are shown in FIG. 3B.

It was calculated earlier that with zero CDV, a voice channel should receive 360 bytes of TDM data every eight 12

ATM cells. Therefore, a natural place to check for buffer fullness is at an eight-cell boundary (or a multiple of it). However, the effect of a CDV of 4.42 ms is to change the actual fullness by about +/-0.7852 cells. If CDV is not accounted for, there will be many rapid and unnecessary clock adjustments. The effect of CDV is averaged out over a large number of cells, but at any one point, the fullness can be off by up to +/-0.7852 cells. Averaging is necessary to nullify the effect of CDV. One way to perform averaging is 10 to check the buffer fullness multiple times, and make a clock adjustment only if the fullness is above or below threshold for all of the checks.

An embodiment of the algorithm requires the fullness to be above or below the threshold for 16 consecutive cells before clock adjustment is initiated and sets the nominal buffer threshold (NOM) to two cells and the upper and lower thresholds (T) to be +16 bytes and -16 bytes respectively from nominal. The algorithm starts with the nominal clock rate (no clock stretch and divisor equal to 4096). As long as (NOM-16) <=buffer fullness <=(NOM+16), the clock remains at the nominal rate. When buffer fullness exceeds NOM+16 for sixteen consecutive cell arrivals, the fast clock is chosen (clock stretch and divisor equal to 4095). The clock rate remains fast until the buffer fullness is less than NOM for sixteen consecutive cell arrivals. At this point, the clock rate switches to nominal. Similarly, if the buffer fullness < NOM-16 for sixteen consecutive cell arrivals, the slow clock is chosen (clock stretch and divisor equal to 4096). The clock rate remains slow until buffer fullness exceeds NOM for sixteen consecutive clock cycles, at which point the clock rate switches back to nominal.

Referring now to FIG. 3C, an adaptive clock recovery state diagram is shown. In the state diagram, "buf" is the buffer fullness relative to NOM (i.e., if buf is zero, the of incoming ATM cells. The states include Nominal, Slow, Fast, and count states CNT0, CNT1, CNT2, CNT3.

In an embodiment, the HLH 20 can handle four simultaneous voice calls, implying that the ATM stream can carry TDM data for four separate VCs. In addition, incoming cells also carry signaling and data cells, which contain no timing information. These cells are not considered for network timing. The cell stream of each VC contains the same network timing information. In the absence of any voice the reference clock is derived from the clock oscillator without adjustment. When multiple voice calls are in progress, one VC must be chosen for performing clock adjustment. Since clock adjustment is needed most for long-lived calls, it makes sense to use the VC corresponding to the first established call for clock adjustment. In an embodiment, fullness information is maintained for all four VCs since the first established call can be terminated at any time. In the event that the call used for clock adjustment is terminated, the algorithm switches the clock adjustment to look at the VC corresponding to the call that was established second. Note that it is not necessary to maintain fullness information for all AAL1 VCs. A single hypothetical buffer can be used for all voice calls provided buffer threshold and impaired cells are handled as described herein below. In an embodiment, the HLH controller 82 has registers that the CPU 74 can write to identify the four AAL1 VCs. In addition, the CPU also identifies the VC that is currently 65 used for clock adjustment.

Generation of a constant cell stream is now described. Incoming cells to the HLH controller 82 are buffered in the

external SRAM 83. The HLH controller 82 partitions the SRAM into FIFO queues that are maintained per VC. It was calculated earlier that an ATM cell must be provided to the MSC 64 and the TMs 16 every 5.625 ms, which translates to 45 clock periods of the adjusted 8 KHz reference clock. Internal to the HLH controller 82, timers clocked by the adjusted reference clock are provided for each AAL1 VC. These timers become operative when the nominal threshold has been reached (i.e., two cells have been received for that AAL1 VC and placed in its queue), generating a timeout 10 signal every 45 clock periods of the reference clock. When the timeout occurs, the HLH controller 82 reads the cell at the head of the queue and outputs it to the MSC 64. Since the adjusted reference clock is used to clock the timers, the rate of cell transfer is synchronized to the network and is 15 constant (to within the +/-1 Hz required to correct the clock drift). Thus, as long as the queues maintained in SRAM 83 do not overflow or underflow due to cell impairments, the MSC 64 and the TMs 16 will receive a constant cell stream synchronized to the network.

The effects of cell impairments and their nullification are now described. ATM cells in a real network are subject to several kinds of impairments such as cell delay greater than the maximum CDV calculated above, cells being dropped and cells becoming corrupted. The timing recovery algo- 25 rithm described herein above relies on timely arrival of cells with delay less than the maximum CDV. The effect of the impairments described above is an interruption in the constant cell stream, leading to cell underflows. The HLH controller 82 detects cell impairments and missing or cor- 30 rupted cells, drops the offending cell (the MSC 64 substitutes the voice samples in dropped cells with silence) and modifies the buffer fullness information to maintain bit integrity and to prevent cell underflows. The SAR header of AAL1 cells contains a 3-bit sequence number which incre- 35 ments modulo 8 with each successive cell. The sequence number (SN) field is protected by a 4-bit sequence number protection (SNP) field. Additionally, the ATM layer has a header error check (HEC) byte which protects the ATM header. Thus, out of sequence and corrupted cells can be 40 detected and cell underflow prevented.

An embodiment which implements the timing recovery mechanism is now described. The CPU 74 controls the following timing-recovery related registers in the HLH controller 82:

VP\_ID: 12 bits—Identifies the Virtual Path common to all VCs.

VC0\_ID: 16 bits: Identifies VC0

VC1\_ID: 16 bits: Identifies VC1

VC2\_ID: 16 bits: Identifies VC2

VC3\_ID: 16 bits: Identifies VC3

VC\_SEL: 2-bit pointer: Identifies VC currently used for clock adjustment

VC\_ENA[3:0]—Setting a bit enables buffer tracking for 55 the corresponding VC.

CLK\_ADJ\_ENA: 1 bit-Enables clock adjustment using VC selected by VC\_SEL.

The CPU 74 sets up registers on the HLH controller 82 for proper operation. Some registers, such as VC{0-3}\_ID and 60 VP\_ID, are set up once at the beginning of operation. The VC\_SEL, VC\_ENA and CLK\_ADJ\_ENA registers are set by the CPU at the time a voice call is set up or torn down. VC\_ENA enables buffer tracking on a per-VC basis. clock adaptation and CLK\_ADJ\_ENA enables clock adap14

The HLH controller 82 maintains separate cell buffers in SRAM 83 for the four voice channels and the signaling and data channels. There is an eight-cell buffer for each voice channel, a 512-cell buffer for the signaling channel and a 1024-cell buffer for the data channel. The HLH controller 82 maintains two bits of state information for each of the 8 cells of an AAL1 cell sequence: a cell arrival tag bit and a drop cell indicator (DCI) bit. Initially, both bits are reset for the entire 8-cell sequence. Additionally, three variables related to sequence numbers are maintained per-VC: last received sequence number (Irsno), current sequence number (csno) and transmit sequence number (xsno). When the first cell for a VC is received, its Irsno is set equal to csno and the xsno is set to 0. Note that these three variables vary between 0 and 7 corresponding to the 8 sequence numbers.

When an AAL1 cell arrives at the input of the HLH controller 82, ATM header and AAL1 SAR header error checks are performed. The HLH controller 82 examines the header of the incoming cell. A 3-bit VC-identifier (VC\_ID) is internally generated to specify which VC the current cell belongs to (four voice channels, one signaling channel or one data channel). A cell is determined to be a valid voice cell and is written to the tail of the queue (in SRAM 83) corresponding to VC\_ID if all the following are true:

- (1) it is a non-OAM AAL1 cell whose VPI/VC1 field matches the VP\_ID and the ID in one of the  $VC{0-3}_{ID}$  registers;

- (2) no ATM or AAL1 SAR header error is detected;

- (3) the cell has the correct sequence number;

- (4) The DCI bit for that cell is reset. The tag bit for that cell is also set and a start of cell (SOC) indication is provided to the buffer fullness algorithm described below. If one of the above four checks fails, the cell is dropped (i.e. it is not written into the queue), and the tag bit for that cell is reset. A drop cell count for that VC is also incremented. If checks (1) and (2) pass, the DCI bits for all 8 cells in an AAL1 cell sequence are reset.

As described earlier, the four voice VCs are provided with timers which generate timeouts every 45 clock periods of the adjusted reference clock (8 KHz). When a timeout is generated for a VC (identified by VC\_ID), the tag bit corresponding to xsno is examined. If the tag bit is set, a cell is read out from the head of the queue in the SRAM and sent to the MSC 64. If the tag bit is not set, no cell is read out, 45 the DCI bit corresponding to xsno is set, and a SOC indication is sent to the buffer fullness logic. The latter action guarantees that in the absence of incoming cells at the HLH controller 82 (due to cell impairments), passage of time is recognized by the buffer fullness algorithm.

The buffer fullness algorithm described earlier is implemented as follows. Each AAL1 VC has a block that is provided with an 8-bit counter and an 8-bit accumulator called Level Register. The Level Register is cleared when VC\_ENA for that VC is turned on. It was calculated earlier that on the average each AAL1 cell carries 45 bytes of voice data. When VC\_ENA for a particular VC is on, and a SOC indication is received and the VC\_ID matches the VC for a block, the counter is pre-loaded with 45. The counter is decremented by the adjusted 8 KHz clock. When the next cell arrives for the VC in question, the counter value is added to the Level Register. When the local clock is exactly synchronized with the network clock, the counter value will be zero at the arrival of every new cell and hence on the average, the Level Register will remain close to zero. If local VC\_SEL identifies which of the four VCs is selected for 65 clock deviates from the network clock, the counter will have a non-zero positive or negative value (a counter underflow resulting in values between hex FF and hex80 is treated as

a negative number). The Level Register thus starts to deviate from zero and over time crosses the threshold limit of +/-16 bytes. If the Level Register remains outside the threshold limits for 16 consecutive cell periods for that VC, clock adaptation takes place if the VC\_SEL field has been set to this VC and CLK\_ADJ\_ENA is on. The adaptation follows the state diagram shown in FIG. 3C.

In addition, a priority arbitration scheme with timers can be implemented to read cells out of SRAM 83 to the MSC 64. The four voice channels, the signaling channel and the 10 herein below with reference to FIGS. 7A and 7B. The data channel all have independent timers. The voice channel timers generate a request every forty-five 8 KHz clocks. The setting of the signaling and data channel timers is under microprocessor control. When multiple requests are present, the highest priority request is selected for service. The 15 priority order from highest to lowest is: VC0, VC1, VC2, VC3, SIG, DATA. By selecting the timer values appropriately, it can be guaranteed that no channel is starved of service, mimicking a prioritized round-robin queue.

The foregoing sections have described an AAL1 timing 20 recovery mechanism in the absence of a clock that is traceable to the Primary Reference Clock on the network. The algorithm and implementation described are robust to clock drift, cell delay variation and cell impairments. 2.1.2 Telephone Module

A block diagram of an embodiment of the telephone module (TM) 16 is shown in FIG. 4. The TM 16 connects an analog telephone 24 to the home LAN 15 and includes an analog front end (AFE) 70, TM controller 100, codec 98, memory 97, subscriber line interface circuit (SLIC) 96, line 30 connectors 92, 94, user interface 102 and analog bypass relay 104.

The AFE 70 connects to the home wiring 14 (FIG. 1) for communicating digitized voice, data and signaling informaphysical (PHY) layer that is described further herein. The TM controller 100, which can be implemented as a field programmable gate array (FPGA), connects to the AFE 70 and interfaces to the home LAN MAC layer as a slave device to the HLH 20. The TM controller 100 performs 40 timing recovery on the signal received from the HLH to keep the voice circuits synchronized to HLH clock timing. The codec 98 interfaces to the TM controller 100 using digital time division multiplexed (TDM) data.

devices which convert between analog voice signals and PCM. In particular, the codec 98 provides analog to digital and digital to analog conversion, and the SLIC 96 provides line interface functions required for standard analog voice services, i.e., POTS.

The bypass relay 104 is provided so that the customer can select the original POTS line for use directly by an analog telephone 24. If power is lost, the relay selects the bypass mode so that lifeline POTS is maintained. The user interface 102 includes LED indicators 102A and a line selection 55 switch (e.g., dip switch or rotary switch) 102B which are described further herein.

2.1.3 Analog Front End

An embodiment of the AFE 70 is shown in FIG. 5. The AFE 70, common to the HLH 20 (FIGS. 2 and 3A) and the 60 TM 16 (FIG. 4), shifts the frequency range of signals used on the home wiring 14 to a frequency range above that used by analog POTS and ADSL so that the home LAN can use the same wire pair that is used for POTS and ADSL. The The transmitter and receiver operate in a time-division duplex (TDD) fashion. To prevent intersymbol interference

16

(ISI) caused by open termination reflection, a guard space is provided between each modulated symbol as described further herein.

The transmitter section includes a transmit symbol shaping logic/modulator block 106 and a transmitter line driver 107. The receiver section includes a highpass filter HPF-2 114, an automatic gain control (AGC) gain stage 116, an envelope detector/AGC control block 118 and a demodulator 119. The AGC circuitry 116, 118 is described further common section includes line protection and RJ-11 interface 113, a highpass filter HPF-1 112, a transformer 110 and a transmit/receive bandpass filter (BPF) 108. Each of these elements is now described.

The transmit symbol shaping logic and modulator block 106 takes framed data and a 32.768 MHz burst clock pulse from a MAC layer processor, such as HLH controller 82 (FIG. 3A) or TM controller 100 (FIG. 4), to perform symbol shaping in the time domain in accordance with the physical layer characteristics described further herein. To avoid using an expensive digital filter and an analog modulator to shift the baseband data signal to a passband signal for transmission on the home wiring 14, the scheme shown in FIG. 6A is used to achieve accurate pulse shaping and modulation. 25 FIG. 6B shows the framed data signal and clock signal that are input to shift register 106A of FIG. 6A. The output of shift register 106A is coupled to a weighted resistor network 106B to provide shaped signals A and B (FIG. 6C). The shaped signals A and B are summed in summer 106C to provide an output shaped signal C. The pulse shape of signal C is generated only if data is a logic 'I', otherwise the signal C remains 0 volts.

Referring again to FIG. 5, the transmitter line driver 107 is a high-speed operational amplifier, which is able to drive tion to and from the HLH 20 according to the home LAN 35 a minimum load of 100 ohms. The requirement on slew rate is calculated as follows:

> If output peak voltage is +4 V for a 16.384 MHz sinusoidal carrier, the time taken to change from 0 V to +4 V is

> > t=(1/16.384 MHz)/4=0.01527 μs

and therefore the slew rate is

4V/0.01527 µs=262.1V/µs

The codec 98 and SLIC 96 are standard, off-the-shelf 45 The Tx line driver delivers the following performance in the 12 MHz to 20 MHz frequency range:

Gain flatness less than 1 dB,

Better than 61 dBc THD if output 8 Vp-p at 16 MHz;

Slew rate better than 262.1 V/us;

Nominal output voltage level 8 Vp-p across 100 ohm termination.

The Tx/Rx BPF 108 comprises a passive seventh-order elliptic-function bandpass filter which is designed to provide superior stop band rejection performance. The transmitter and receiver share this bandpass filter. The spectral characteristics of the bandpass filter 108, as shown in FIG. 8, include

Center frequency at 16 MHz

In-band ripple less than 3 dB

3 dB bandwidth of 5 MHz with 3 dB points of 13.5 MHz and 18.5 MHz.

Referring again to FIG. 5, the transformer 110 can be a conventional 100 Base-T Ethernet transformer with a com-AFE 70 includes transmitter, receiver and common sections. 65 mon mode choke built in to reduce common mode noise. In the 12 MHz to 20 MHz range, a preferred transformer

Insertion loss <1 dB;

Return Loss >20 dB;

Differential to common mode rejection better than -42

Hipot safety voltage at least 1500 Vrms.

The HPF-1 112 comprises a third order elliptic-function highpass filter with the spectral characteristics shown in FIG. 9. This highpass filter is located on the 2-wire phone network side of the AFE 70 circuit. The HPF-1 provides low frequency rejection of other signals generated by other applications, such ADSL and HDSL. It also shows high balanced impedance to other applications that may use spectrum below 10 MHz. The spectral characteristics of the HPF-1 include

3 dB cutoff frequency at 11 MHz

Ripple less than 3 dB

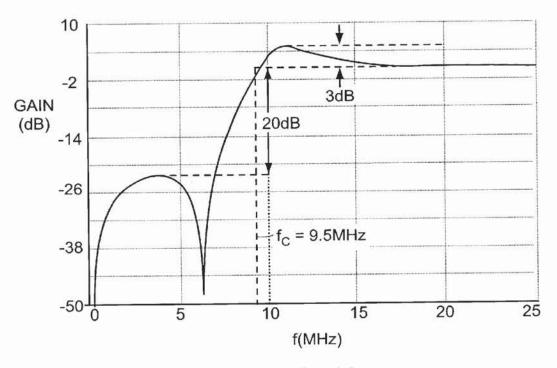

30 dB minimum at 3.5 MHz, -56 dB minimum at 6 MHz. The HPF-2 (FIG. 5) comprises a third order ellipticfunction highpass filter with the spectral characteristics 20 shown in FIG. 10. This highpass filter is designed for the receiver section to provide additional low frequency rejection of other signals generated by other applications, such ADSL and HDSL. The spectral characteristics of the HPF-2 include

3 dB cutoff frequency at 9.5 MHz

Ripple less than 3 dB

20 dB minimum at 3.5 MHz, -46 dB minimum at 6 MHz.

The home LAN 15 (FIG. 1) is a point-to-multipoint communication system. In this system, the HLH 20 receives 30 signals from the TMs 16 which are physically located at different distances from the HLH. Thus, the HLH receiver needs AGC to equalize the received signals by adjusting the receiver gain based on received signal strength. As described further herein, the system uses time division multiple access 35 age filter, which continuously monitors the envelope peak for upstream communication to the HLH from the TMs. To effectively utilize bandwidth on the home LAN, transient time between two adjacent timeslots should be minimized. This requires that the AGC be able to rapidly track a received signal that varies in signal strength from timeslot to 40 timeslot. Another challenge is that if the received signal envelope is not constant, the receiver has to be able to lock and hold the gain, which is based on an average of received signal strength, so as to keep the "fast tracking" AGC from unnecessarily tracking the changing envelope of the 45

The AFE 70 (FIG. 5) includes AGC circuitry 116, 118 that overcomes the challenges associated with fast tracking and locking. Referring now to FIG. 7A, the AGC gain stage block 116 preferably includes four gain stages, two that are 50 AGC gain stages 116-1, 116-2 and two that are fixed gain stages 116-3, 116-4. The AGC control block 118 includes envelope detector and AGC loop filter 118A, analog switch 118B controlled by AGC on/off control line 121 and holding capacitor 118C. The two AGC gain stages 116-1, 116-2 are 55 used to equalize time-varying attenuation caused by the particular wiring topology employed. Since the AFE 70 receives signals from other AFE modules (e.g., other TMs 16 and the HLH 20) located in different positions on the in-home wiring, the AGC has to be robust and must react fast 60 enough such that the gain can be changed from maximum to minimum within a relatively short time interval, e.g., a guard space of two timeslots as defined in the MAC layer described further herein. Two N-channel JFET transistors 117-1, 117-2 are used to control AGC gain stages 116-1, 65 116-2, respectively to ensure a wide AGC dynamic range and fast tracking ability.

18

Referring now to FIG. 7B, there is shown a timing diagram of AGC gain and control signals in relation to a downstream frame or alternatively an upstream timeslot as described further herein with reference to the MAC laver. The frame or timeslot includes frame sync bits 130 followed by gain acquiring bits 132, payload 134 and end of frame/ timeslot 136. The frame sync bits 130 are used to help the AGC circuitry converge quickly. The gain acquiring bits 132 are used to assist the AGC circuitry to achieve high locking 10 accuracy of automatic gain control. Once AGC converges, the AGC gain is held constant during the period corresponding to the payload 134. The control signal 121 indicating payload time from the MAC layer is used to open the analog switch 118B. Capacitor 118C is used to hold and lock gain 15 control such that the receiver remains a constant gain during transmission time of the payload.

The AGC circuitry 116, 118 has the following character-

Overall gain 60 dB min;

AGC control range better than 40 dB;

AGC maximum gain settling time less than 21 µs;

AGC minimum gain recovery time less than 21 µs;

Nominal output level 8 Vp-p.

The demodulator 119 demodulates the equalized signal received from the AGC circuitry 116, 118 to a baseband signal. For on-off keying modulation, the envelope of the equalized signal is actually the transmitter baseband pulse shape. The demodulator includes an envelope detector which extracts the signal envelope. Since channel distortion and additive noise are superimposed on the envelope, the demodulator includes a likelihood decision circuit which compares the envelope with a detection threshold. The detection threshold is generated adaptively by a peak averand the biggest eye opening.

## 2.2 Physical Layer

The AFE 70 (FIG. 5) described above implements the physical layer on the home wiring 14. The theory of operation for the physical layer is now described.

To avoid an expensive echo canceller, the transmitter and receiver operate in a time-division duplex (TDD) fashion. This means that when a transmitter is sending, the receiver on the same AFE circuit does not receive signals from any other AFE circuit on the home LAN. Likewise, when a receiver is receiving signals, the transmitter on the same AFE circuit does not send any signals to any other AFE circuit on the home LAN.

To multiplex five 64 kb/s voice channels and other control signaling, a TDM framing format is used downstream toward the TMs while TDMA is used upstream. All frame formatting and frame control and timing is controlled by the MAC layer processor, and is described in the MAC layer section further herein.

The modulation used in the embodiment of AFE 70 is on-off amplitude shift keying with a carrier frequency of 16 MHz. As noted above, a guard space is provided between each modulated symbol to prevent IS1 caused by open termination reflections. In an embodiment, the symbol period is given as

symbol period=2T+guard band space=2×244 nsec+732 nsec=1.22

symbol rate=1/symbol period=1/1.22 µsec=820 kbps

where T is the pulse width of a symbol.

30

19

To avoid IS1 in a band-limited system, a raised cosine spectrum-shaping approach is used. If u(t) is the binary digital signal, the baseband signal can be expressed as

$$X(t)=u(t)^*[(\sin \pi t/T)/(\pi t/T)]^*[(\cos \beta \pi t/T)(1-4\beta^2 t^2/T^2)]$$

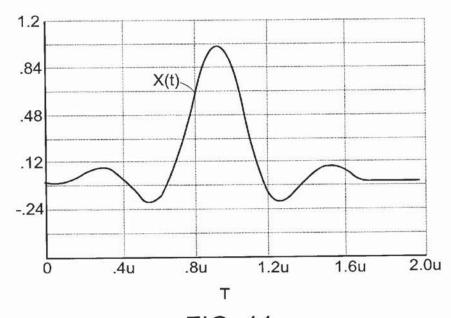

FIG. 11 shows the simulated baseband signal X(t) in the time domain (T=244 nsec).

The raised cosine spectral characteristic X(f) of the baseband pulse is defined as:

$X(f)=T,0 \le |f| \le (1-\beta)/2T$

$$X(f) = \frac{T}{2} \Big[ 1 - \mathrm{sin}\tau T \bigg( f - \frac{1}{2T} \bigg) \bigg/ \beta \Big], \quad (1 - \beta)/2T \le |f| \le (1 + \beta)/2T$$

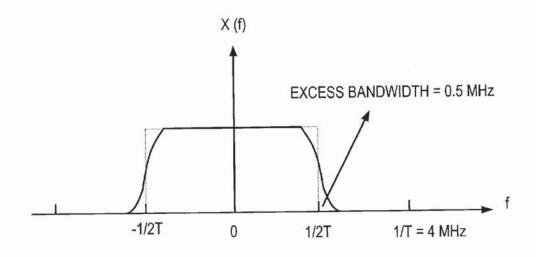

For the characteristic X(f), shown in FIG. 12, the excess bandwidth= $\beta/2T$ =0.5 MHz, where roll-off parameter  $\beta$ =0.25 (25%); 1/T=4.096 MHz; and T=244 nsec.

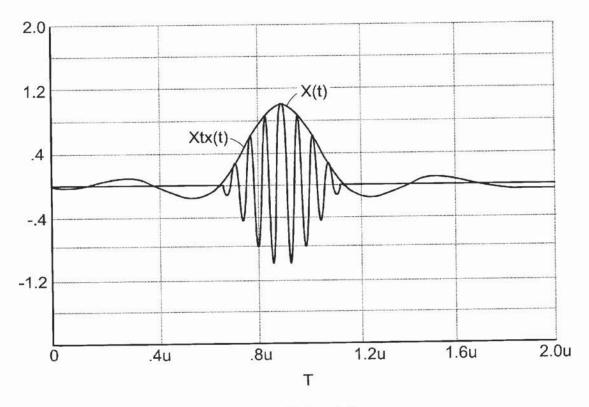

The baseband signal is modulated by a sinusoidal carrier signal ( $f_c$ =16 MHz) and shifted to a passband signal centered around 16 MHz with 4 MHz passband bandwidth. The passband signal in the time domain is defined as Xtx(t):

$$Xtx(t)=X(t)*\sin(2\pi fc*t+\theta)$$

FIG. 13 shows the passband signal Xtx(t) in the time domain (T=244 nsec). In the frequency domain, the passband signal is defined as Xtx(t):

$$Xtx(f)=X(f+f_c)$$

FIG. 14 shows the theoretical spectrum of Xtx(f). A simulated spectrum Xtxm(f) for the passband signal implemented in the embodiment of AFE 70 (FIG. 5) is shown in FIG. 15. This signal spectrum corresponds to the shaped pulse signal 35 in the time domain shown in FIG. 6C.

In terms of demodulation, the received on-off keying modulated signal can be expressed as:

$$Xrv(t)=K(t)*Xtx(t)+n(t)$$

where n(t) is additive noise and K(t) is time-varying channel distortion caused by echo and non-linear attenuation. Since a guard space is used between transmitted symbols, K(t) is mainly represented by time-varying attenuation. As noted above with respect to the embodiment of AFE 70 (FIG. 5), two AGC gain stages with fast tracking control capabilities are used to equalize the K(t) attenuation. Following equalization, the 16 MHz carrier is removed by an envelope detector as noted above in the description of AFE 70. The envelope detector output is then sliced by a hard decision circuit. The threshold level for the hard decision circuit is adaptively adjusted based on signal eye openings. The output of the hard decision circuit is a regenerated TTL compatible binary digital data signal.

In the embodiment of the home LAN physical layer described herein, operation occurs in the frequency range between 14 and 18 MHz. This location in the frequency spectrum is above that used by other services that can coexist on the wiring, such as POTS ("plain old telephone service") (0 to 4 Hz), xDSL (30 KHz to 1.1 MHz) and HomePNA (5.5 to 9.5 MHz), as shown in the spectrum diagram of FIG. 16.

# 2.3 MAC layer

Communication to the HLH 20 upstream from the TMs 16 (FIG. 1) and downstream from the HLH to the TMs is

20

provided in frame structures: one structure for the downstream direction and another for the upstream direction. As shown in the diagram of FIG. 17, a downstream frame 202 is of 1.44 ms duration and an upstream frame 204 is of 1.56 ms for a total transmission time of 3 ms.

In the downstream direction, only the HLH transmits. The downstream frame structure of five timeslots is shown in FIG. 18 and includes 147 bytes in fields defined as follows:

- FR field of two framing bytes which allows the TMs to adjust their gain levels and to derive their timing from the HLH;

- CTRLG field of 5 bytes used for non-call associated control and OAM functions;

- TIM1, . . . ,TIM5 fields each comprising a timing byte which further helps the TMs to gain timing;

- CTRL1,...,CTRL5 fields each comprising a control byte associated with corresponding telephone modules TM1,...,TM5;

- PCM1, . . . ,PCM5 fields each comprising 24 bytes of voice information from the HLH to corresponding telephone modules TM1, . . . ,TM5; the PCM fields are used to exchange messages between the HLH and a TM while the particular TM is not connected on a call;

- SIG1, . . . ,SIG5 fields each comprising a signaling byte used for call associated signaling (ABCD bits) for corresponding telephone modules TM1, . . . ,TM5; the lower nibble includes CRC for the ABCD bits;

- GB field of five bytes which provides a guard band to avoid false framing.

The upstream frame structure of five timeslots is shown in FIG. 19 and includes 160 bytes in fields defined as follows:

- FR1, . . . ,FR5 fields each comprising a framing byte to enable the HLH to lock on to the power level and timing of transmitted signals from a particular TM;

- CTRL1,...,CTRL5 fields each comprising a control byte for non-call associated control and OAM functions;

- PCM1, . . . ,PCM5 fields each comprising 24 bytes of voice information to the HLH from corresponding telephone modules TM1, . . . ,TM5;

- SIG1, ..., SIG5 fields each comprising a signaling byte used for call associated signaling (ABCD bits) for corresponding telephone modules TM1, ..., TM5;

- GB1, . . . ,GB5 fields each comprising five bytes which provides a guard band to avoid false framing.

The TMs are slaved to the HLH. The TMs use the framing information sent by the HLH to derive timing. Upon power-up, each TM waits to see the downstream framing bytes FR which are set to 0xF6F6 (i.e., two bytes as opposed to the upstream framing bytes from other TMs which are only one byte long). Each TM determines four pieces of information to derive framing, namely:

- the framing bytes in the FR field are set to 0xF6F6;

- the framing bytes follow a guard band GB of 5 bytes;

- the timing bytes in the TIM1, . . . , TIM5 fields are each set to 0xEB and occur at pre-specified positions with respect to the framing bytes; and

the next guard band in the GB field occurs 140 bytes following the framing bytes FR.

Furthermore, to prevent the possibility of achieving false framing by the TMs, the following steps are taken. First, the TM declares that framing has been achieved only after seeing three consecutive downstream frames with the correct framing bytes in field FR. Second, all of the payload bytes included in the CTRLG, CTRL1, . . . , CTRL5,

PCM1, ..., PCM5 and SIG1, ..., SIG5 fields are scrambled using a self-synchronous scrambler. This scrambling minimizes the probability of the payload bytes being equal to the framing bytes in successive frames either by accident or by design (e.g., a malicious user). Only the framing and timing bytes are in the clear and are not scrambled.

Once the TM achieves framing, it declares itself to be in the synchronization state. In this state the TM continues to look for framing bytes (FR field) at the beginning of every downstream MAC frame 202. If the TM does not see 10 framing bytes in three consecutive frames, it declares itself out of synchronization and enters the synchronization hunt state (i.e., the state at power up).

Note that the framing byte in fields FR1, . . . ,FR5 used in the upstream direction by each TM is only one byte long. 15 This helps the TMs distinguish between upstream transmissions from other TMs versus downstream transmission from the HLH.

The values of the particular fields defined in the downstream frame 202 are preferably set as follows:

The framing bytes in the FR field are set to 0xF6F6.

The global control bytes in the CTRLG field are defined below:

| 1 byte      |       | 1 byte       |            | 1 byte   | 2 bytes |

|-------------|-------|--------------|------------|----------|---------|

| idle status | prov  | isioned stat | tus        | reserved | CRC     |

|             |       | 1 byte - io  | ile status |          |         |

| 3 bits      | 1 bit | 1 bit        | 1 bit      | 1 bit    | 1 bit   |

| reserved    | TS1   | TS2          | TS3        | TS4      | TS5     |

|             | 1 t   | yte - provi  | sioned s   | tatus    |         |

| 3 bits      | 1 bit | 1 bit        | 1 bit      | 1 bit    | 1 bit   |

| reserved    | TS1   | TS2          | TS3        | TS4      | TS5     |

where TS1, ..., TS5 in the idle status byte indicate whether 40 a timeslot is currently being used for a voice call (1) or is on-hook or idle (0) and where TS1, . . . ,TS5 in the provisioned status byte indicate whether a timeslot is currently provisioned (1) or not (0).

The control byte in fields CTRL1, ..., CTRL5 can be used 45 are described further herein. to exchange OA&M messages between TMs and the HLH.

The PCM bytes in fields PCM1, . . . , PCM5 include the PCM values (u-law encoded) for the previous 3 ms. While the telephone 24 connected to a particular TM 16 50 (FIG. 1) is on-hook, this field can be used to send information from the HLH 20 to the corresponding TM.

The signaling byte in fields SIG1, ..., SIG5 can have one of the following values as defined in GR-303 for ABCD signaling:

| ABCD Code | Comments                  |  |

|-----------|---------------------------|--|

| 0000      | -R Ringing                |  |

| 0010      | DS0 AIS                   |  |

| 0100      | Reverse Loop Current Feed |  |

| 0101      | Loop Current Feed         |  |

| 0111      | DS0 Yellow                |  |

| 1111      | Loop Current Feed Open    |  |

The timing byte in fields TIM1, ..., TIM5 is set to 0xEB.

The guard bytes in field GB are each set to 0x00.

The values of the particular fields defined in the upstream frame 204 are preferably set as follows:

The framing byte in fields FR1, . . . ,FR5 is set to 0xF7.

The control byte in fields CTRL1, ..., CTRL5 can be used to exchange OA&M messages between TMs and the HLH.

The PCM bytes in fields PCM1, . . . , PCM5 include the PCM values (u-law encoded) for the previous 3 ms. While the phone is on-hook, this field can be used to send information to the HLH.

The signaling byte in fields SIG1, ..., SIG5 can have one of the following values as defined in GR-303 for ABCD signaling:

| <br>ABCD Code | Comments    |  |

|---------------|-------------|--|

| <br>0010      | DS0 AIS     |  |

| 0101          | Loop Open   |  |

| 0111          | DS0 Yellow  |  |

| 1111          | Loop Closed |  |

The guard bytes in fields GB1, . . . , GB5 are each set to 0x00.

The MAC layer is the only means of communication between the HLH and TMs. The MAC layer is used to convey signaling information (e.g., on-hook, off-hook events), PCM formatted voice information, as well as OAM functions between the HLH and TMs. The home LAN system includes a message based communication protocol to automatically "discover" TMs and monitor any error conditions that may arise as a result of misconfiguration by the end user. For example, each TM is assigned a timeslot to operate in, as determined by a dip switch setting 102 (FIG. 4) on the TM. A registration process is provided to discover TMs once they are plugged into the RJ-11 jack, and to ensure that TMs with the same dip switch setting are not allowed to use the timeslot which has already been assigned to another TM already connected to the home LAN. The state machines governing this process for the HLH and TMs

The PCM fields in the upstream and downstream frames can be used to exchange messages between the HLH and TMs. The message format is defined as follows:

|         | 24 bytes |         |  |