DOCKET NO.: 1745950-00120US1

Filed on behalf of STMicroelectronics, Inc.

By: Richard Goldenberg, Reg. No. 38,895 (Lead Counsel)

Gregory Lantier (pro hac vice to be filed) (Backup Counsel)

Scott Bertulli, Reg. No. 75,886 (Backup Counsel)

Trishan Esram, Reg. No. 74,075 (Backup Counsel)

Wilmer Cutler Pickering Hale and Dorr LLP

60 State Street

Boston, MA 02109

Email: richard.goldenberg@wilmerhale.com gregory.lantier@wilmerhale.com

scott.bertulli@wilmerhale.com

trishan.esram@wilmerhale.com

UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_\_

# STMICROELECTRONICS, INC. Petitioner

v.

THE TRUSTEES OF PURDUE UNIVERSITY

Patent Owner

IPR2022-00252

U.S. Patent No. 7,498,633

DECLARATION OF VIVEK SUBRAMANIAN, PH.D. U.S. PATENT NO. 7,498,633 CHALLENGING CLAIMS 9–11

# **TABLE OF CONTENTS**

| I.    | INTRODUCTION                                |                                                              |     |  |

|-------|---------------------------------------------|--------------------------------------------------------------|-----|--|

| II.   | QUALIFICATIONS AND PROFESSIONAL EXPERIENCE1 |                                                              |     |  |

| III.  | MATERIALS CONSIDERED4                       |                                                              |     |  |

| IV.   | LEGAL PRINCIPLES6                           |                                                              |     |  |

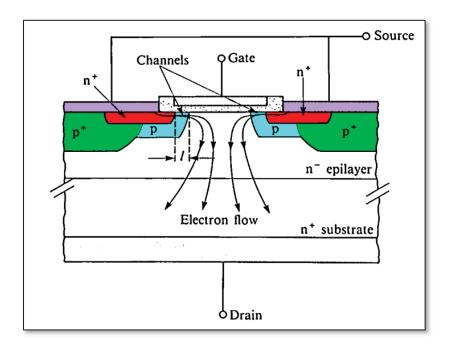

| V.    | LEVEL OF ORDINARY SKILL IN THE ART          |                                                              |     |  |

| VI.   | TECHNICAL BACKGROUND                        |                                                              |     |  |

|       | A.                                          | Field-Effect Transistor ("FET")                              | 10  |  |

|       | B.                                          | Power MOSFET                                                 | 14  |  |

|       | C.                                          | On-Resistance                                                | 18  |  |

|       | D.                                          | Unwanted Activation of Parasitic Components—Latch Up         | 20  |  |

|       | E.                                          | Silicon Carbide (SiC)                                        | 25  |  |

|       | F.                                          | Visualizing Three-Dimensional Semiconductor Structures       | 27  |  |

| VII.  | OVERVIEW OF THE '633 PATENT                 |                                                              |     |  |

|       | A.                                          | The Alleged Invention of the '633 Patent                     | 32  |  |

|       | B.                                          | Prosecution History                                          | 39  |  |

| VIII. | CLA                                         | IM CONSTRUCTION                                              | 42  |  |

| IX.   | OVERVIEW OF THE PRIOR ART REFERENCES        |                                                              |     |  |

|       | A.                                          | Ryu                                                          | 43  |  |

|       | <i>B</i> .                                  | Williams                                                     | 48  |  |

| Χ.    | SPECIFIC GROUND FOR PETITION                |                                                              |     |  |

|       | A.                                          | Ground I: Claims 9–11 are Obvious Over <i>Ryu</i> in View of | 50  |  |

|       |                                             | Williams                                                     |     |  |

|       |                                             | 1. Independent Claim 9                                       |     |  |

|       |                                             | 2. Dependent Claim 10                                        |     |  |

| 371   | A <b>T</b> 7 A                              | 3. Dependent Claim 11                                        |     |  |

| XI.   |                                             | AILABILITY FOR CROSS EXAMINATION                             |     |  |

| XII.  | KIGI                                        | HT TO SUPPLEMENT                                             | 95  |  |

| VIII  | 11 11                                       | /\ I                                                         | (14 |  |

I, Vivek Subramanian, declare as follows:

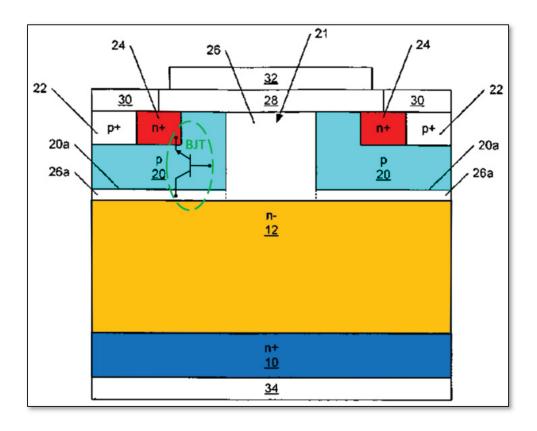

## I. INTRODUCTION

- 1. My name is Vivek Subramanian. I am a Professor of Microtechnology at the École polytechnique fédérale de Lausanne (EPFL) (also known as the Swiss Federal Institute of Technology in Lausanne) in Switzerland. Until recently, I was also a professor of Electrical Engineering and Computer Sciences at the University of California, Berkeley. As of July 1, 2020, I have become an adjunct professor at UC Berkeley upon completion of my move to EPFL.

- 2. I have been retained as an expert in this proceeding by counsel for STMicroelectronics, Inc. ("ST"). I have been asked for my expert conclusions regarding the validity of claims 9–11 of U.S. Patent No. 7,498,633 (the "'633 patent") (EX1001). For the reasons set forth below, it is my conclusion that claims 9–11 of the '633 patent are invalid.

# II. QUALIFICATIONS AND PROFESSIONAL EXPERIENCE

- 3. My qualifications are stated more fully in my curriculum vitae, which is attached as Exhibit A. Below is a summary of my education, work experience, and other qualifications.

- 4. I received a bachelor's degree *summa cum laude* in electrical engineering from Louisiana State University in 1994. I received M.S. and Ph.D.

degrees in electrical engineering, in 1996 and 1998, respectively, from Stanford University.

- 5. Throughout the course of my education, including my B.S., M.S., and Ph.D. degrees, I was involved in the design, fabrication, characterization, and modeling of semiconductor devices, including specifically devices designed for high voltage and high power applications. For example, I have designed high voltage transistors for operation of Flash memory devices using silicon, which have gone into commercial products, and have designed and fabricated high voltage wide bandgap devices for use in MEMS actuators based on zinc oxide.

- 6. After completing my Ph.D., I held multiple appointments simultaneously between 1998 and 2000. I served as a Consulting Assistant Professor in the Electrical Engineering Department of Stanford University. I also served as a Visiting Research Engineer in the Department of Electrical Engineering and Computer Sciences at the University of California, Berkeley, where my research focused on 25nm metal oxide semiconductor field effect transistor (MOSFET) design and fabrication. I worked on technologies for high-performance transistor processes, and I published several papers as a direct outcome of this technology development.

- 7. In 2000, I became an assistant professor at the University of California, Berkeley in the Department of Electrical Engineering & Computer Sciences. In 2005, I was promoted to the position of tenured Associate Professor, and in 2011, I was promoted to full Professor. In 2018, I became a full Professor of Microtechnology at EPFL in Switzerland, where I lead the Laboratory for Advanced Fabrication Technologies (LAFT). The lab focuses on the development and application of advanced additive fabrication techniques for realizing precision microelectronic and electromechanical systems. As of 2020, I have completed my move to EPFL and have therefore converted to an adjunct appointment at Berkeley.

- 8. My research has maintained a large effort on semiconductor devices, including working on various types of high voltage and high power devices, as mentioned above.

- 9. Starting in 2004, I was a founding technical advisor for Kovio. I led the development of Kovio's first commercial RFID tag product, including the design of both the tag and the reader, and including the development of the underlying proprietary transistor technology. This included the development of the materials, fabrication processes, and device design. My involvement with Kovio ended with Kovio's acquisition by thin film electronics, but Kovio continues to focus on this area.

- 10. I co-founded Locix Inc. in 2014. Locix develops and sells a range of wireless-enabled products, including proprietary Wi-Fi-based RF localization systems and sub-GHz low-power wireless sensor networks. As CTO of Locix, I led the development of the entire Locix RF product portfolio. I continue to be involved with Locix on a regular basis.

- 11. I have authored or co-authored over 200 technical papers in international journals and conferences and have been named an inventor or co-inventor on more than 50 patents, many of which cover aspects of semiconductor device design and fabrication.

- 12. I am being compensated for my time at my ordinary hourly rate of \$650. My compensation is not dependent on the outcome of these proceedings or the content of my opinions. To the best of my knowledge, I have no financial interest in either party or in the outcome of this proceeding.

#### III. MATERIALS CONSIDERED

13. In preparing this declaration, I have reviewed the claims, specification, and file history of the '633 patent. I understand that the '633 patent issued from U.S. Patent Application No. 11/338,007, which was filed on January 23, 2006, claiming priority to U.S. Provisional Application No. 60/646,152, filed on January 21, 2005.

# 14. I have reviewed and understand the references and exhibits cited in this Declaration, including the following:

| Exhibit | Description                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1001    | U.S. Patent No. 7,498,633                                                                                                                      |

| 1003    | U.S. Patent Application Publication No. 2004/0119076 ("Ryu")                                                                                   |

| 1004    | U.S. Patent No. 6,413,822 ("Williams")                                                                                                         |

| 1005    | U.S. Patent No. 5,233,215 ("Baliga")                                                                                                           |

| 1006    | U.S. Patent No. 6,316,791 ("Schörner")                                                                                                         |

| 1007    | U.S. Patent Application No. 2006/0267092 ("Jun")                                                                                               |

| 1008    | '633 Patent File History, 4/4/2007 Non-Final Rejection                                                                                         |

| 1009    | '633 Patent File History, 8/6/2007 Response to Office Action                                                                                   |

| 1010    | '633 Patent File History, 10/12/2007 Final Rejection                                                                                           |

| 1011    | '633 Patent File History, 3/12/2008 Response to Office Action                                                                                  |

| 1012    | '633 Patent File History, 6/25/2008 Non-Final Rejection                                                                                        |

| 1013    | '633 Patent File History, 8/22/2008 Response to Office Action                                                                                  |

| 1014    | '633 Patent File History, 12/17/2008 Notice of Allowance                                                                                       |

| 1015    | U.S. Patent No. 5,317,184 ("Rexer")                                                                                                            |

| 1016    | "Modern Power Devices," B. Jayant Baliga, 1987 (relevant sections)                                                                             |

| 1017    | A. G. Jost et al., "Implementation of a VLSI Layout Tool on Personal Computers," ACM, 1990                                                     |

| 1018    | E. S. Kuh et al., "Recent Advances in VLSI Layout," Proceedings of the IEEE, vol 78, no. 2, February 1990                                      |

| 1019    | "Power MOSFETs – Theory and Applications," Duncan A. Grant and John Gowar, 1989 ("Grant") (relevant sections)                                  |

| 1020    | J. A. Cooper, Jr. et al., "SiC Power-Switching Devices—The Second Electronics Revolution?," Proceedings of the IEEE, vol. 90, no. 6, June 2002 |

| 1021    | U.S. Patent No. 5,510,281 ("Ghezzo")                                                                                                           |

| 1022 | J. A. Cooper, Jr. et al., "Status and Prospects for SiC Power MOSFETs," IEEE Transactions on Electron Devices, vol. 49, no. 4, April 2002                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

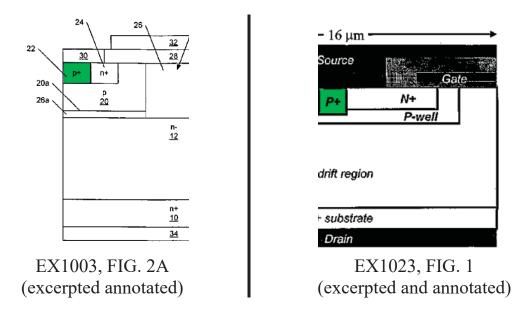

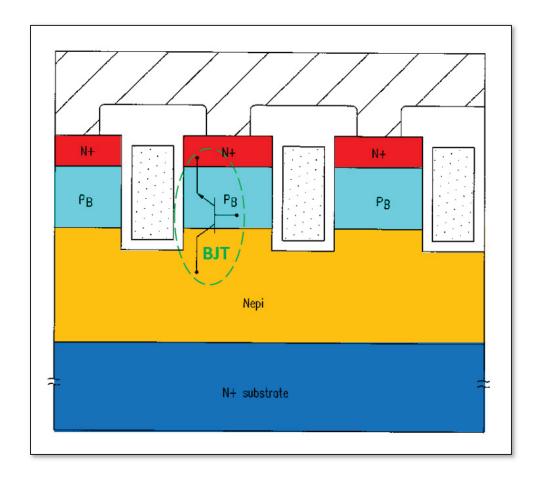

| 1023 | S-H Ryu et al., "10 A, 2.4 kV Power DiMOSFETs in 4H-SiC," IEEE Electron Device Letters, vol. 23, no. 6, June 2002                                                                   |

| 1024 | S-H Ryu et al., "2 kV 4H-SiC DMOSFETs for Low Loss, High<br>Frequency Switching Applications," International Journal of High<br>Speed Electronics and Systems, vol. 14, no. 3, 2004 |

| 1025 | Plaintiff's Disclosure of Earliest Date of Invention                                                                                                                                |

### IV. LEGAL PRINCIPLES

- 15. I am not an attorney. For the purposes of this declaration, I have been informed by ST's counsel about certain aspects of the law that are relevant to my opinions, as stated in the following paragraphs. I have applied these legal principles in arriving at my conclusions expressed in this declaration.

- 16. I have been informed and understand that a patent claim is invalid if it would have been obvious to a person of ordinary skill in the art (POSITA) at the time of the alleged invention. This means that, even if all of the requirements of a claim are not found in a single prior art reference, the claim is not patentable if the differences between the subject matter in the prior art and the subject matter in the claim would have been obvious to a POSITA at the time of the alleged invention.

- 17. I have been informed and understand that a determination of whether a claim was obvious should be based upon several factors, including, among others:

(1) the level of ordinary skill in the art at the time of the alleged invention; (2) the

scope and content of the prior art; (3) the differences, if any, that existed between the claimed invention and the prior art; and (4) any objective considerations of nonobviousness.

- 18. I have been informed and understand that when determining any differences between the invention covered by the patent claims and the prior art, one should not look at the individual differences between the patent claims and the prior art in isolation, but rather consider the claimed invention as a whole and determine whether or not it would have been obvious in light of all of the prior art.

- 19. I have been informed and understand that a single reference can render a patent claim obvious if any differences between that reference and the claims would have been obvious to a POSITA. Alternatively, the teachings of two or more references may be combined in the same way as disclosed in the claims. I have been informed and understand that when deciding whether to combine the various items described in the prior art, the relevant question is whether the prior art combination would have been obvious to a person with ordinary skill in the art at the time of the invention. I have been further informed that it can be important to identify a teaching, suggestion, or motivation, in either the prior art or the knowledge of persons skilled in the art, that would have prompted a person of ordinary skill in the

relevant field to combine the elements in the prior art in the way the claimed invention does.

- 20. In determining whether a combination based on either a single reference or multiple references would have been obvious, it is appropriate to consider, among other factors:

- whether the teachings of the prior art references disclose known concepts combined in familiar ways, and when combined, would yield predictable results;

- whether a POSITA would implement a predictable variation, and would see the benefit of doing so;

- whether the claimed elements represent one of a limited number of known design choices, and would have a reasonable expectation of success by a POSITA;

- whether a POSITA would have recognized a reason to combine known elements in the manner described in the claim;

- whether there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent; and

- whether the innovation applies a known technique that had been used to improve a similar device or method in a similar way.

- 21. I have been informed and understand that one of ordinary skill in the art has ordinary creativity, and is not an automaton. I have been informed and understand that in considering obviousness, it is important not to determine obviousness using the benefit of hindsight derived from the patent being considered. I have been informed and understand that a patent composed of several elements is not proved obvious merely by demonstrating that each of its elements was independently known in the prior art.

- 22. I have been informed and understand that to show a motivation to combine, one is not required to show how the references would be physically combined to render a claim obvious. The analysis is not focused on whether the features of one reference can be physically incorporated into the structure of another reference, but rather whether a person of ordinary skill in the art would have been motivated to combine the teachings of the references to achieve the claimed invention. For example, a person of ordinary skill in the art would understand how predictable variations of known concepts could be combined and would recognize that were where multiple tools were available in a toolbox, any could be chosen.

#### V. LEVEL OF ORDINARY SKILL IN THE ART

23. I have considered the '633 patent from the perspective of a POSITA at the time of the alleged invention. A POSITA for the '633 patent would have had the

equivalent of a Bachelor's degree in electrical engineering or a related subject and two or more years of experience in the field of semiconductor devices. Less work experience may be compensated by a higher level of education, such as a Master's Degree, and vice versa. At the time of the claimed invention, I would have qualified as a POSITA under this standard.

#### VI. TECHNICAL BACKGROUND

# A. Field-Effect Transistor ("FET")

A field-effect transistor ("FET") is a type of transistor that uses an 24. electric field to control the flow of current in a semiconductor. See "Power MOSFETs – Theory and Applications," Duncan A. Grant and John Gowar, 1989 ("Grant") (EX1019) at 1 ("The metal-oxide-semiconductor field-effect transistor (MOSFET) is the most commonly used active device in the very large-scale integration of digital integrated circuits .... The conductance of a piece of semiconductor depends on the number of free carriers it contains and on their mobility. The effective number of free carriers can be modified by establishing a static electric field in the semiconductor in the direction transverse to the current flow."); EX1015, 1:13–18 ("Semiconductor devices, and more particularly metal oxide semiconductor (MOS) devices used in power applications, are operated when an electric potential is applied across a drain and a source and a voltage is applied to a gate to control current flow between the drain and the source."). A FET generally

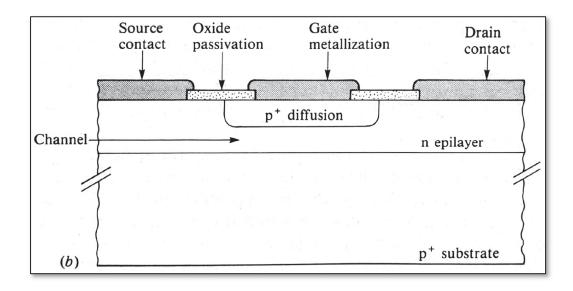

includes a source, a drain, and a gate, as *Grant* illustrates in a cross section of a junction field-effect transistor (JFET) in Figure 1.1, reproduced below. *See, e.g., id.* at 2, Figure 1.1.

EX1019, Figure 1.1

25. The flow of current is controlled by applying a voltage (*i.e.*, creating an electric field) to the gate, which in turn alters the conductivity of the channel formed between the drain and the source. *Id.* at 3 ("it is normally ON or in the freely conducting state, and it can be turned OFF by a voltage of suitable polarity applied to the gate. This reverse-biases the gate-channel pn junction and so expands the depletion layer. As a result the effective cross-sectional area of the conducting channel is reduced and its resistance is increased.").

- 26. Grant notes that "[t]he successful manufacture of the JFET depended on the introduction of *planar* silicon technology in 1960" that involves a "combination of processes." EX1019 at 3. Grant goes on to explain that these processes include:

- 1. Epitaxial crystal growth from the vapor phase.

- 2. The formation of thermally grown silicon dioxide layers for surface passivation, for masking, and as an insulating layer over which metal interconnections may be run.

- 3. The photolithographic etching of "windows" in the oxide layer.

- 4. The introduction of controlled levels of impurity into selected regions of the silicon through these windows in the oxide, either by diffusion from the vapor phase or by ion implantation.

- 5. The deposition by evaporation or sputtering of a thin conducting film (usually Al) and the etching of this film to form a pattern of interconnections on the surface.

- *Id. Grant* illustrates the above processes in Figure 1.2. *Id.* at 4. The introduction of impurities is often referred to as "doping."

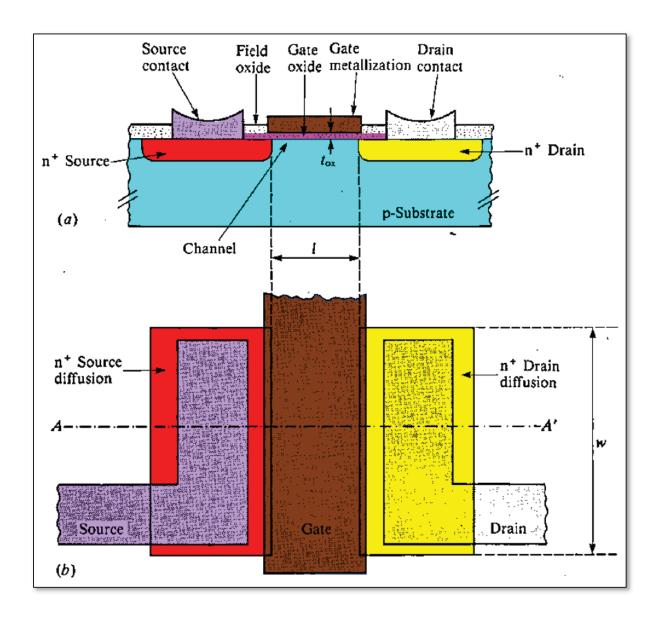

- 27. "Further technological refinements in the early 1960s enabled a different type of field-effect transistor to be made. This was the metal-oxide-

semiconductor field-effect transistor (MOSFET)." EX1019 at 5. Grant points out that the difference between a JFET and a MOSFET is "[t]he controlling gate electrode is now separated from the semiconductor by a thin insulating layer of gate oxide, as shown in Figure 1.3." *Id.*; see also U.S. Patent No. 5,233,215 ("Baliga") (EX1005), 1:45-50. ("These device types are commonly referred to as Metal Oxide Semiconductor Field Effect Transistors (MOSFET) because they include a conducting gate electrode, typically metal, that is separated from a semiconductor surface by an intervening insulator, typically silicon dioxide."). In Figure 1.3 (reproduced below), *Grant* illustrates a cross section and a plan view of a MOSFET. EX1009 at 5. When the MOSFET is turned on, current can flow between the source and drain through the channel, shown in the figure and formed in the p-type substrate. The n+ source region, the p-type substrate, and the n+ drain region essentially forms an npn transistor. The source region is annotated in red, the drain region in yellow, the p-type substrate in cyan, the gate in brown, the gate oxide in magenta, and the source contact in lavender. The source contact is often referred to as "source metallization," "source metal," or "source electrode." See, e.g., EX1019, Figure 1.13 (illustrating the source metallization); EX1015, Figure 1, 1:38 ("source metal"); EX1005, 2:64 ("source electrode").

EX1019, Figure 1.3 (annotated)

### **B.** Power MOSFET

28. While useful in a variety of electronics applications, the MOSFET also became "important in devices designed for power applications." EX1019 at 5; see also EX1005, 2:14–16 ("In view of the above desirable characteristics, many variations of power MOSFETs have been designed for power devices."). Grant

notes that "the decision as to what constitutes a power device is quite arbitrary" and the term is applied to "any device capable of switching at least 1 A" (*i.e.*, turning on and off a current of 1 ampere flowing from the drain to the source). EX1019 at 5–6.

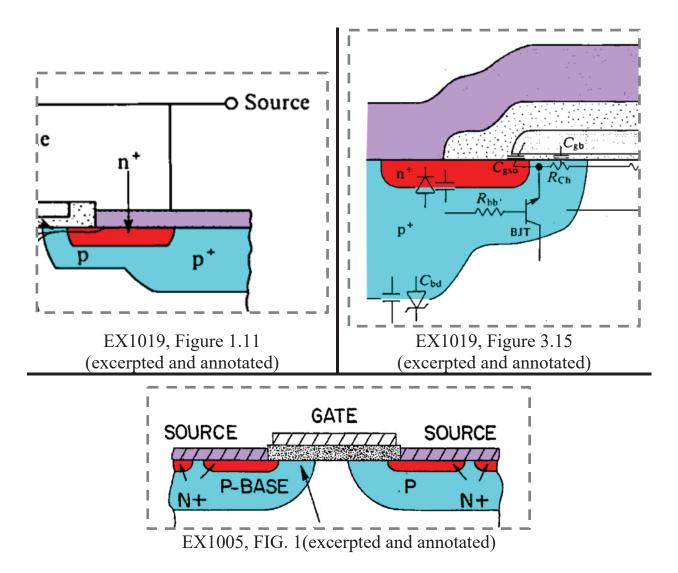

29. *Grant* further notes that "the planar structure of Figure 1.3 is unsatisfactory if it is simply scaled up for higher powers." EX1019 at 8. "[T]he drain-source spacing has to be increased in order to obtain a high voltage blocking capability." *Id.* One solution well known in the art was to change the lateral structure as illustrated in *Grant*'s Figure 1.3 to a vertical structure that uses the substrate material to form the drain region such that "the current flows 'vertically' through the silicon from drain to source." *Id.* This change led to the *vertical double-diffused MOSFET*, which *Grant* illustrates in Figure 1.11, reproduced below. *Id.* at 13–14.

EX1019, Figure 1.11 (annotated)

30. *Baliga* also illustrates a vertical double-diffused MOSFET in Figure 1, which is reproduced below. EX1005, 6:12–13 ("FIG. 1 is a cross-sectional view of a known DMOSFET device").

EX1005, FIG. 1 (annotated) 16

- 31. The term "double-diffused" derives from a manufacturing technique commonly used to form the n+ source regions within the p-type body region: "[t]he p-type 'body' region . . . and the n+ source contact regions are diffused successively through the same window etched in the oxide layer." EX1019 at 14; *see also* EX1005, 2:35–38 ("The p-base region and the n+ source region are typically diffused through a common window defined by the edge of the polysilicon gate."). The p-type body region is often referred to as "p-type wells" or "p-base regions." *See, e.g.*, EX1019 at 146 ("p-type wells"); EX1005, 2:35 ("p-base region"), Figure 1 (illustrating p-base regions).

- 32. In each of the above *Grant*'s Figure 1.11 and *Baliga*'s Figure 1, the source regions are annotated in red, the p-type body regions in cyan, the gate in brown, the gate oxide in magenta, and the source contacts in lavender. The drain region (outlined in yellow) comprises the substrate (annotated in blue) and the epilayer (annotated in orange). Electrons flow from the source to the drain through the channels formed in the p-type wells, the epilayer, and the substrate. The epilayer is often referred to as the drift region. *Grant* notes that "[t]he drain drift region is particularly critical to the design of a power MOSFET" because "[i]ts principal function is to block and support the full forward voltage held off by the transistor in

its turned-OFF state" and "it has also to carry the full forward current in the ON state." *Id.* at 74.

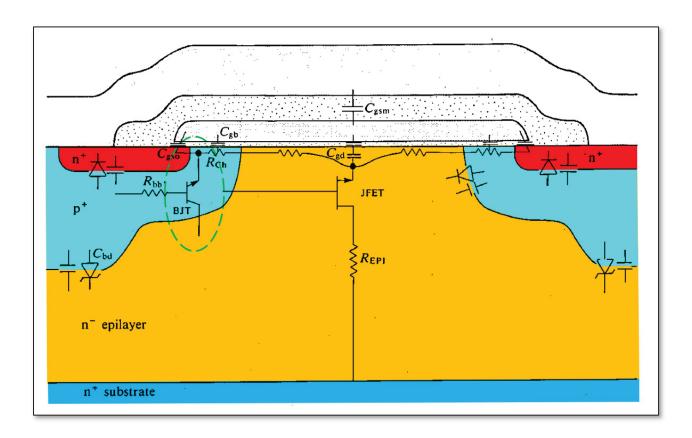

#### C. On-Resistance

- 33. According to *Grant*, "[t]he minimization of the ON-state voltage drop is an important consideration in power devices." EX1019 at 18. This ON-state voltage drop depends on the "ON-state drain-source resistance,  $R_{DS(on)}$ "—also known simply as the "on-resistance." *Id.* U.S. Patent No. 6,413,822 to Williams and Grabowski ("*Williams*"), discussed further herein, explains that the on-resistance of a MOSFET is determined by the "sum of its resistive components," which includes "its substrate resistance ( $R_{sub}$ )," "its epitaxial drain resistance ( $R_{epi}$ )," "its source contact resistance ( $R_c$ )," *etc. See id.*, 1:33–37. *Williams* notes that "[t]he primary design goal for a power MOSFET used as a switch is to achieve the lowest on-resistance by simultaneously minimizing each of its resistive constituents." EX1004, 1:50–52.

- 34. Indeed, for example, *Grant* recognizes the contribution of the epilayer to the on-resistance and states that "[i]t is thus most important that its contribution  $R_{\text{EPI}}$  to the total ON-state resistance  $R_{\text{DS(on)}}$  be kept as small as possible." EX1019 at 74. *Grant* explains that "the epilayer should be no thicker than it has to be in order

to support the maximum blocking voltage" and that "[t]his minimizes dissipation and maximizes the current rating of the device." *Id.* at 74–75.

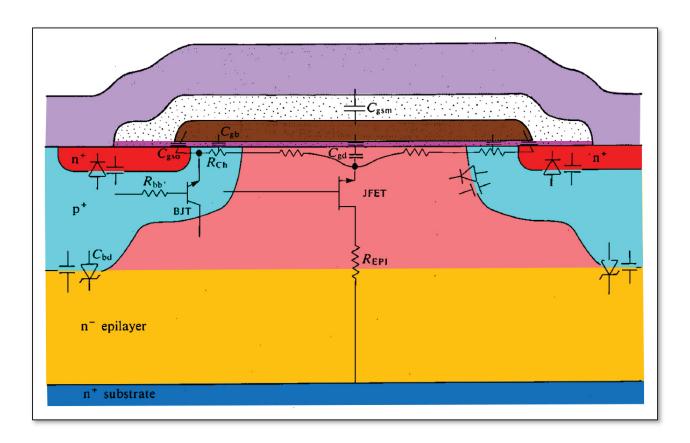

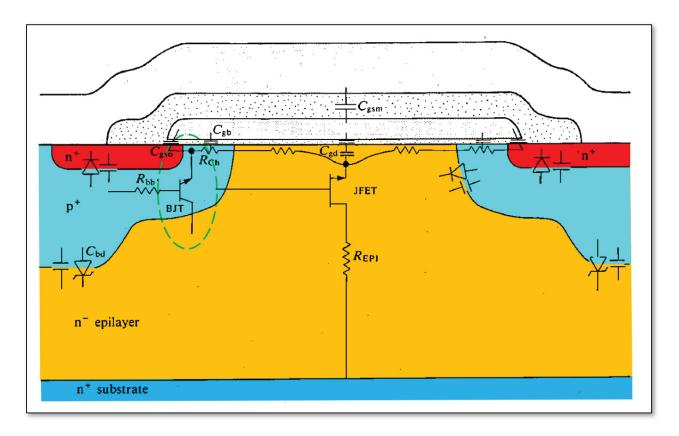

35. Grant also describes that the vertical MOSFET structure includes socalled parasitic elements as a result of the junctions between the n-type and p-type In particular, Grant describes the existence of a parasitic "n-channel regions. junction field-effect transistor (JFET) that forms in the epilayer, in between the channel diffusions." EX1019 at 81. Grant illustrates this parasitic JFET in Figure 3.15, reproduced below. *Id.* at 80, Figure 3.15. *Grant* explains that "[t]he JFET action occurs in the region between the p diffusions." Id. at 81. Accordingly, this region is typically referred to as the "JFET region" of the MOSFET. See, e.g., EX1003, ¶44. The JFET region—in the epilayer and between p diffusions/wells is annotated in pink in Grant's Figure 3.15 below. Grant also points out that "[i]ncreasing the donor doping concentration in the drain throats [(i.e., the JFET regions)]... has two beneficial effects"—"the cell size can be reduced and... lower  $R_{\rm DS(on)}$  can be realized." EX1019 at 83–84.

EX1019, Figure 3.15 (annotated)

36. Also to reduce the on-resistance, *Williams* discloses topological configurations (*i.e.*, the physical shape, size, and arrangement of the structures) that minimize the source contact resistance, as will be discussed in more detail below. *See* EX1004, 10:17–18; 16:28–35.

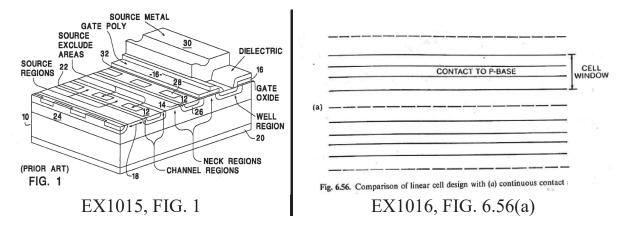

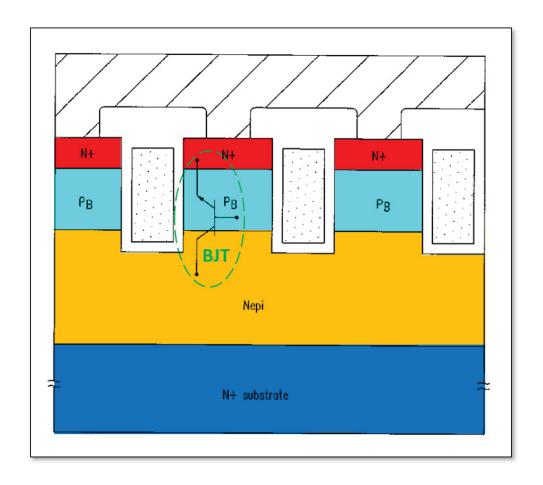

# D. Unwanted Activation of Parasitic Components—Latch Up

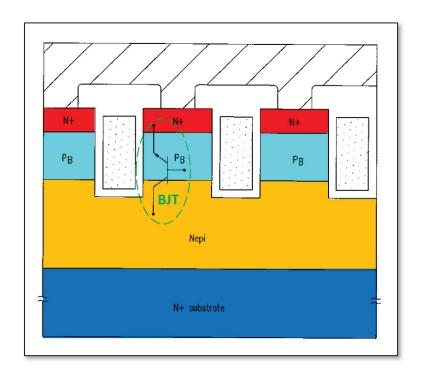

37. *Grant* notes, and illustrates in Figure 3.15 (reproduced above), an "npn bipolar junction transistor (BJT) formed between the source, the body, and the drain." EX1019 at 81. The parasitic BJT "may be activated, and this can seriously

degrade the overall performance of the MOSFET." See EX1019 at 81; see also EX1007, ¶¶ 6–7 ("[A] parasitical bipolar transistor will exist in the high power MOSFET . . . When the parasitical bipolar transistor turns on, a latch phenomenon will arise to increase the possibility of device breakdown."). This phenomenon is typically known as "latch up." To prevent latch up, "[t]his parasitic bipolar transistor must be kept inactive during all modes of operation of the power MOSFET." EX1016 at 266. "To accomplish this, the P-base region is short-circuited to the N<sup>+</sup>emitter region by the source metallization . . ." *Id.*; see also EX1004, 6:8–14 ("The source-to-body short prevents conduction and snapback breakdown of the parasitic NPN bipolar transistor . . . by maintaining the emitter and base at the same potential. Shorting the emitter and base terminals ideally prevents forward-biasing of the emitter-base junction and avoids consequent minority carrier (electron) injection into the MOSFET's body (i.e. base)."). Indeed, as depicted by the annotated excerpts below, it was well known to connect the p-type body or p-base region (i.e., the base of the parasitic BJT; annotated in cyan) to the source region (i.e., the emitter of the parasitic BJT; annotated in red) by an overlying and contacting source metallization (annotated in lavender) to keep the parasitic BJT inactive. See, e.g., EX1019, Figures 1.11 and 3.15; EX1005, Figure 1.

38. Such a parasitic BJT exists in any power MOSFET, regardless of the gate configuration, because the source, the body, and the drain form an npn configuration, *i.e.*, two regions of n-type semiconductor material separated by p-type material. For instance, *Williams* describes and illustrates in Figure 7A (reproduced below) a "parasitic NPN bipolar transistor" in a trench-gate vertical MOSFET. EX1004, 6:9.

EX1004, FIG. 7A (annotated)

39. *Grant* further explains that current flowing through the resistance  $R_{bb'}$  (see Grant's Figure 3.15, reproduced above) at the base of the parasitic BJT causes an ohmic voltage drop (as a result of resistance in the connection) which, if it exceeds about 0.6 V, "will initiate transistor action in the parasitic BJT." EX1019 at 87. To reduce resistance and minimize voltage drop, *Grant* notes that "[t]he use of the p+ diffusion to connect the body region back to the source contact can be seen to be an important part of the VDMOS FET design." *Id.* at 90; see also id., Figures 1.11 and 1.13(a) (illustrating p+ diffusion in p-type body regions). "It reduces  $R_{bb'}$ ..." *Id.* Thus, in addition to connecting the body region to the source region, a MOSFET may be ruggedized against inadvertent activation of the parasitic BJT by having p+

diffusion in the p-type body region to reduce the resistance  $R_{\rm bb'}$  and keep the ohmic voltage drop low. See also EX1004, 16:32–34 ("maximize the P+ contact to the body region (to suppress parasitic bipolar turn-on, prevent snapback and ruggedize the device)"); EX1021, 5:28–30 ("Although an electrical connection can be made directly to the p type base region, the p+ base contact region provides an improved connection."). The p+ diffusions of *Grant*'s Figure 1.11 below are annotated in green. *Grant* cautions, however, that "any mask misalignment that causes the p+ diffusion to be displaced . . . increases  $R_{\rm bb'}$  locally." EX1019 at 90.

EX1019, Figure 1.11 (annotated)

# E. Silicon Carbide (SiC)

40. Historically, power MOSFETs were fabricated using monocrystalline silicon (i.e., a single-crystal silicon). But by the early 1990s, an alternative material—silicon carbide—was also known to be particularly well suited for use in such devices. EX1005, 4:22-27 ("Almost all power MOSFETs being marketed today are fabricated in monocrystalline silicon . . . [,] as is known to those skilled in the art, crystalline silicon carbide is particularly well suited for use in semiconductor devices, and in particular, for power semiconductor devices."). 1 Silicon carbide was known to have many benefits, including "a wide bandgap, a high melting point, a low dielectric constant, a high breakdown field strength, a high thermal conductivity and a high saturated electron drift velocity compared to silicon." Id., 4:27–31. "These characteristics would allow silicon carbide power devices to operate at higher temperatures, higher power levels and with lower specific on resistance than conventional silicon based power devices." *Id.*, 4:31–34; see also U.S. Patent No. 5,510,281 ("Ghezzo") (EX1021), 1:52-56 ("Because SiC has a higher critical electric field than silicon, the specific on-resistance of a SiC

<sup>&</sup>lt;sup>1</sup> Unless otherwise noted, all emphasis has been added.

DMOS is expected to be significantly lower than that of a silicon DMOS with the same high voltage rating.").

Moreover, Baliga teaches that "power MOSFET such as the above 41. described DMOSFET . . . can be readily translated into silicon carbide using known manufacturing techniques." EX1005, 4:35–38. Baliga goes on to explain how to translate the DMOSFET into a silicon carbide device using known manufacturing techniques, e.g., by using higher temperature, and longer, diffusions to compensate for the lower diffusion coefficient in silicon carbide. Id., 4:38-43. Ghezzo, which was filed in 1995, further teaches that "[a] method of implementing vertical power SiC transistor is to replace the conventional double-diffusion with an edge-shifted double ion implantation sequence to overcome the problem of very small dopant diffusivity in SiC" and that "[t]he channel is formed by successive ion implantation of an acceptor atom (such as boron or aluminum) and a donor atom (such as nitrogen or phosphorous) to form the base and source regions, respectively." EX1021, 1:56– 63. Accordingly, SiC power MOSFETs are sometimes referred to as "doubleimplanted" MOSFETs to distinguish the fabrication technique used to make them from "double-diffused" used in silicon.

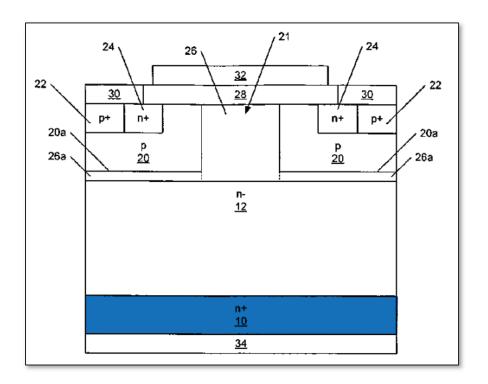

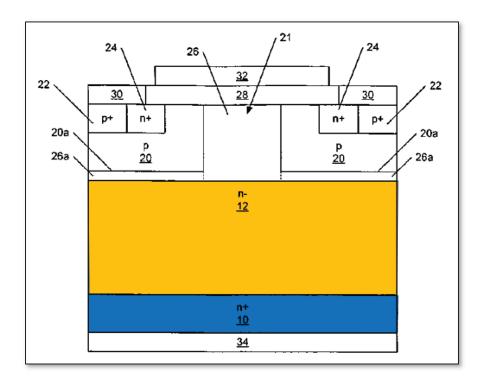

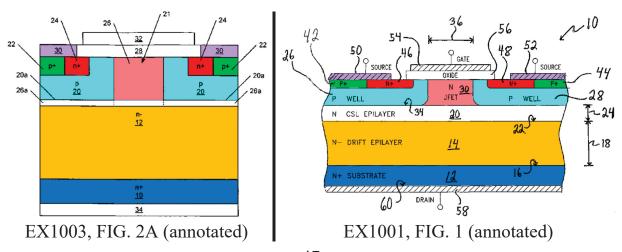

# F. Visualizing Three-Dimensional Semiconductor Structures

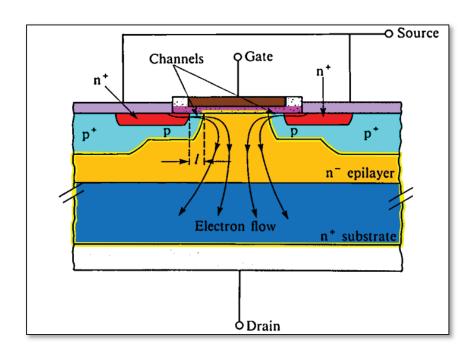

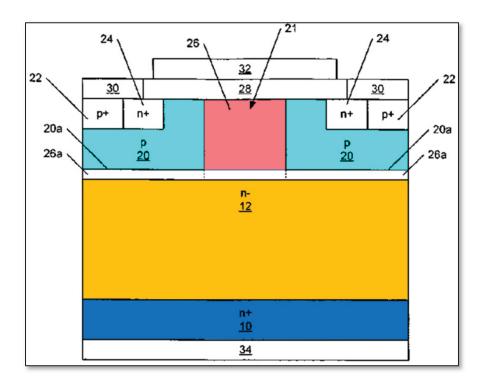

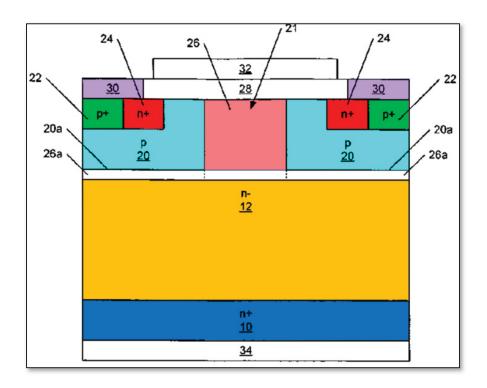

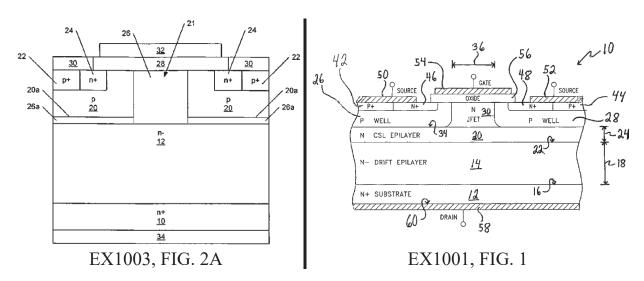

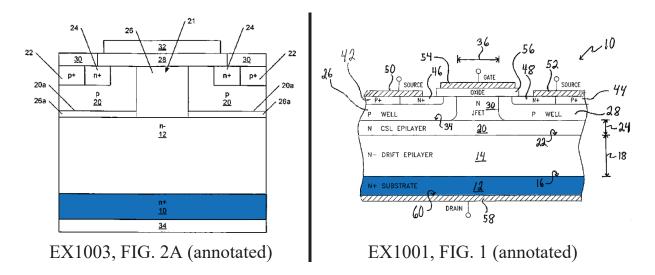

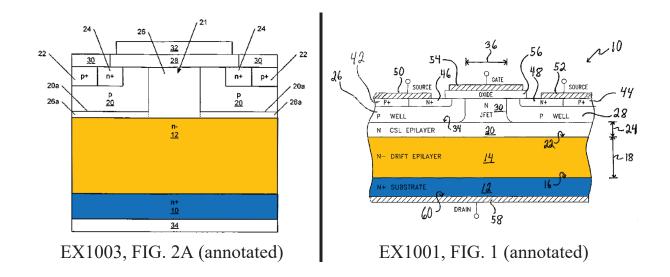

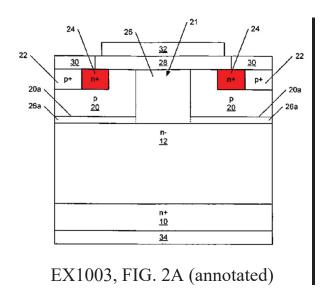

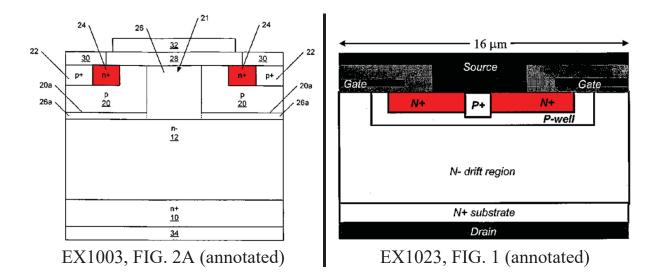

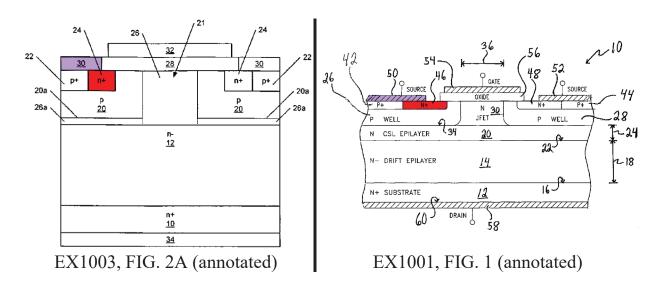

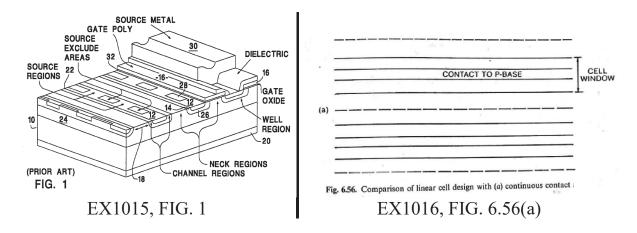

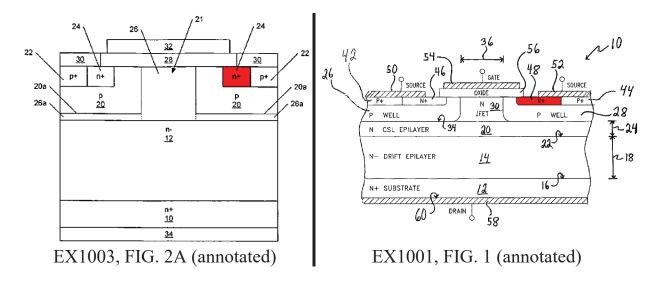

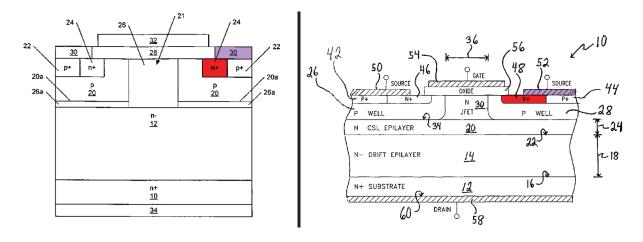

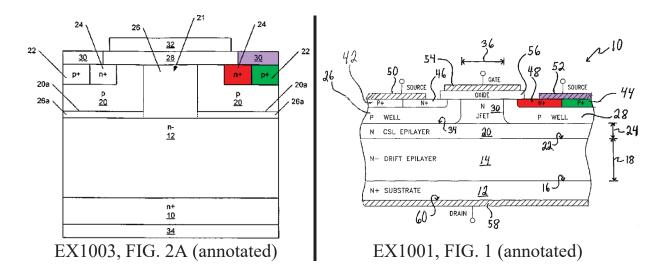

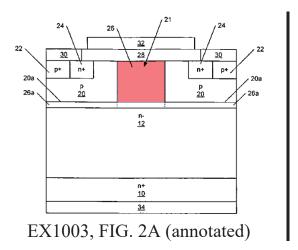

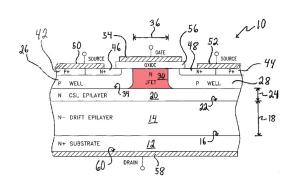

42. Prior art references conventionally use a two-dimensional cross-sectional view to depict a unit cell of a power MOSFET (*e.g.*, as in *Grant*'s Figure 1.11 and *Baliga*'s Figure 1, both reproduced above). U.S. Patent Application Publication No. 2004/0119076 to Ryu ("*Ryu*") (EX1003), discussed in further detail herein, shows a similar example of a cross-sectional view of a unit cell of a MOSFET in Figure 2A, reproduced below. *See* EX1003, ¶51.

EX1003, FIG. 2A

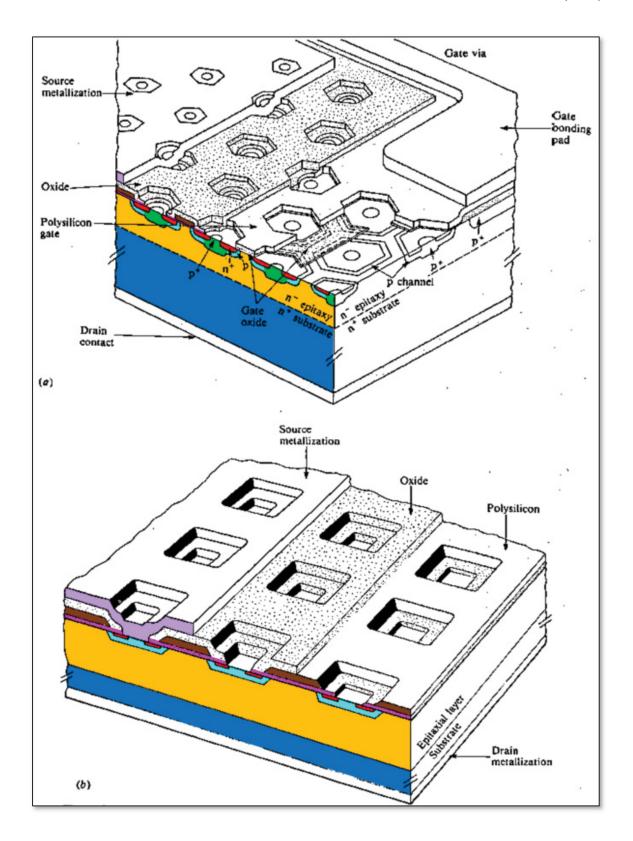

43. MOSFETs may have cross sections that are the same as or similar to the example shown in *Grant*'s Figure 1.11, *Baliga*'s Figure 1, and *Ryu*'s Figure 2A, yet have different—though all well-known—three-dimensional cellular structures.

See EX1016 at 338–339 ("the DMOS structure allows any conceivable cell topology as long as it meets all technological constraints such as alignment tolerances"); *id.*, Figures 6.55 and 6.56; EX1019 at 15–17, 70–73, 455–457, Figures 1.13 and 3.9. Such cellular structures may include shapes that are hexagonal, square, circular, linear, or triangular. For example, *Grant*'s Figure 1.13 (reproduced below) illustrates two cellular structures—hexagonal and square—that have similar cross sections.

EX1019, Figure 1.13 (annotated)

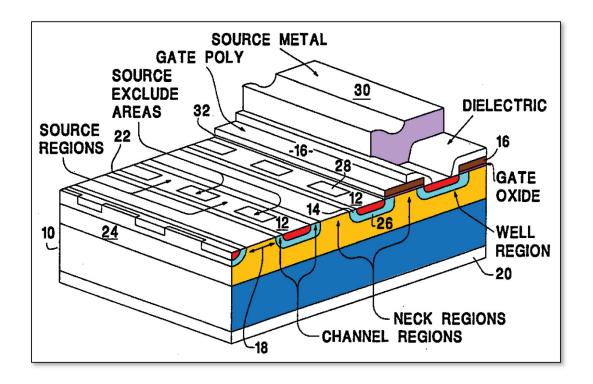

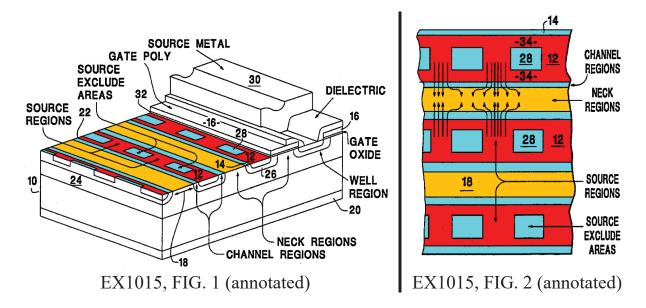

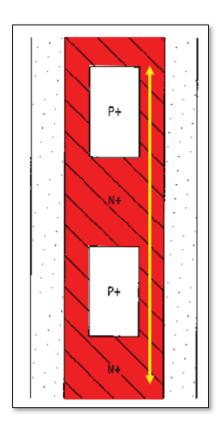

44. Figure 1 (reproduced below) of U.S. Patent No. 5,317,184 ("*Rexer*") (EX1015) shows a three-dimensional linear cellular design of a MOSFET that also has a similar cross section to those in *Grant*'s Figure 1.13 but a linear shape to its cellular structure.

EX1015, FIG. 1 (annotated)

45. In addition to or instead of perspective views, top or plan views of power MOSFETs may be shown. For example, *Rexer* illustrates, in Figure 2, a partial plan view of the surface 22 of its MOSFET of Figure 1, "with the gate oxide, gate, and source metal removed." *Id.*, 1:43–45, 2:34–36. *Rexer*'s Figures 1 and 2 are reproduced and annotated side-by-side below. In *Rexer*'s Figure 2, the linear cellular structure is shown extending left-to-right in the plan view.

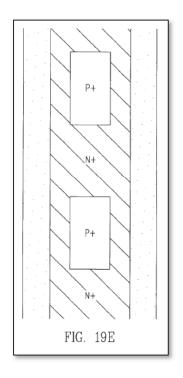

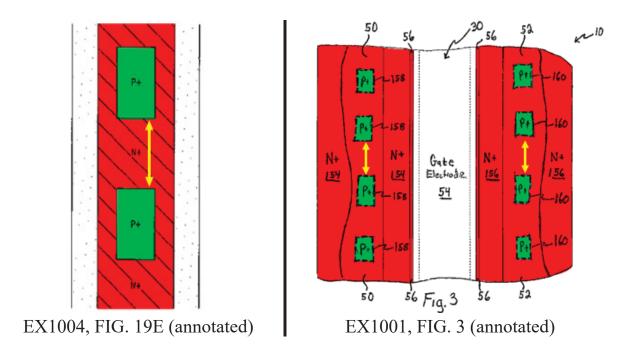

46. *Williams* shows top views of other known MOSFET features, for example in its Figure 19E, which is reproduced below. *Williams*'s Figure 19E shows a linear cellular structure extending top-to-bottom.

EX1004, FIG. 19E

47. The relationships between cross-sectional, perspective, and top views of MOSFETs were well known. For example, a POSITA would have understood that, if a cross-sectional view of a unit cell of a MOSFET like shown in *Ryu*'s Figure 2A were of a linear cellular design like in *Rexer*, then *Ryu*'s cellular structure would extend perpendicular to the page just like the structure shown in *Rexer*'s Figure 1 perspective view. Similarly, a POSITA would have recognized that a top view like shown in *Williams*'s Figure 19E would extend in the same longitudinal direction as the top side of *Rexer's* three-dimensional MOSFET. Relatedly, a POSITA would have understood that a power MOSFET includes a plurality of adjacent unit cells. *See, e.g.*, EX1019, Figure 1.13; EX1015, FIG. 1 (illustrating three full unit cells); *see also* EX1019 at 15 ("High-current capability is obtained by connecting many cells together in parallel.").

#### VII. OVERVIEW OF THE '633 PATENT

# A. The Alleged Invention of the '633 Patent

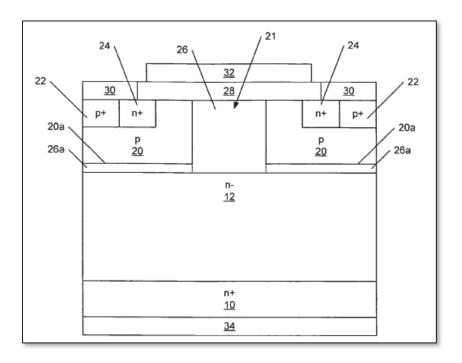

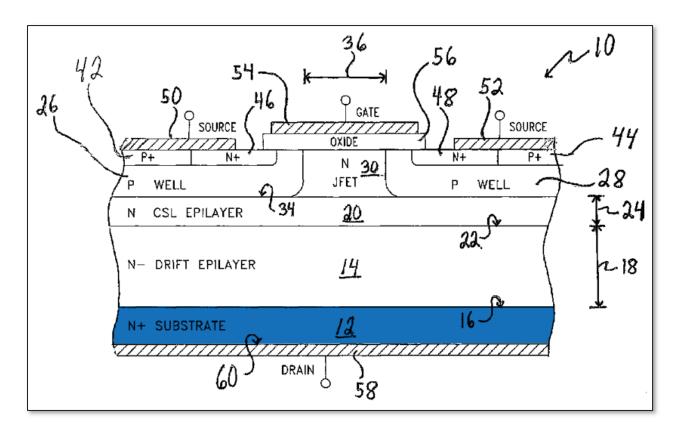

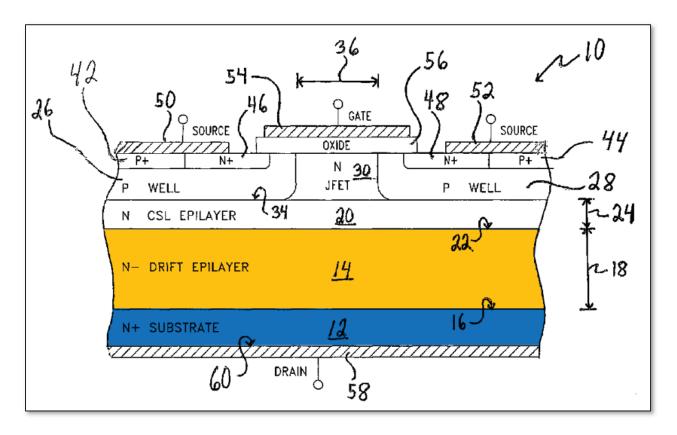

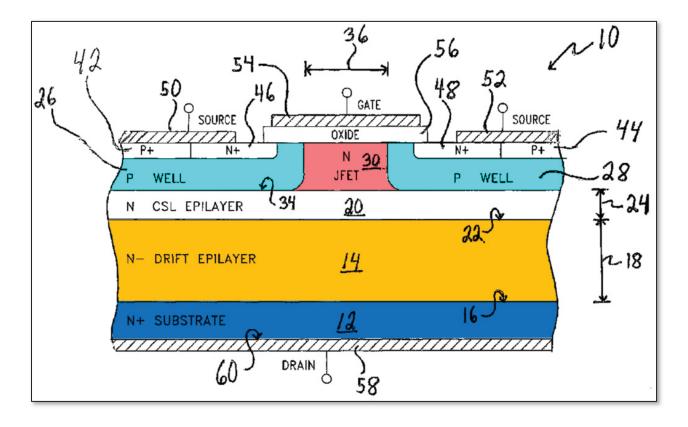

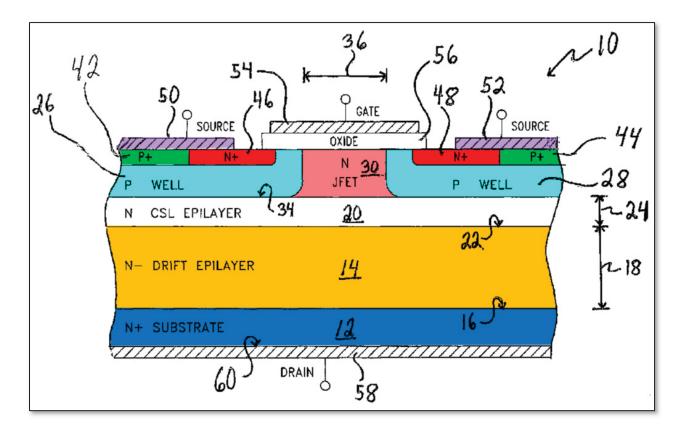

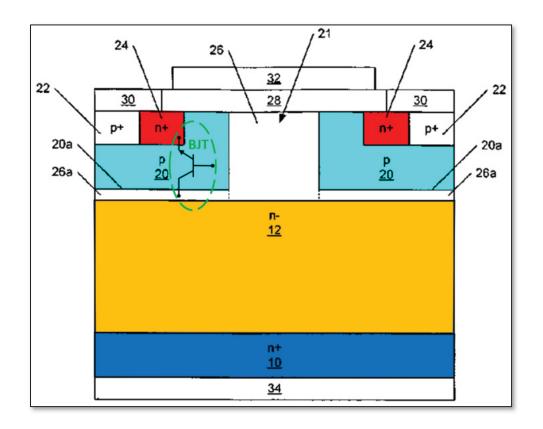

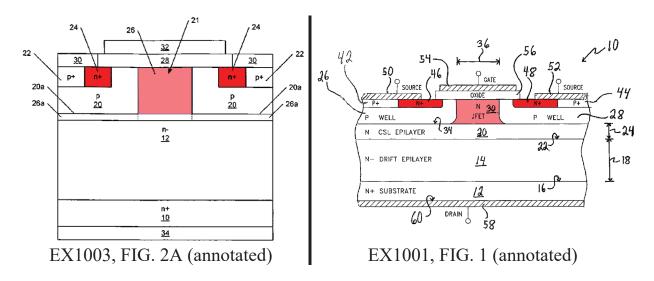

48. The '633 patent is generally directed to semiconductor devices for high-voltage power applications. EX1001, 1:12–14. In particular, the '633 patent describes and claims a semiconductor device referred to as a "vertical double-implanted metal-oxide semiconductor field-effect transistor," having a structure as depicted in Figure 1. *Id.*, 3:7–8, 4:4-9, Figure 1. The '633 patent notes that Figure 1

shows "a single 'transistor cell' and that a completely fabricated transistor device may include any number of" these devices. *Id.*, 5:26-30. As the '633 patent's Figure 1 shows, the semiconductor device 10 includes a **substrate 12** (annotated in blue below) that can be formed from silicon-carbide material and doped with N-type impurity to an "N+" concentration. EX1001, 4:4–13.

EX1001, FIG. 1 (annotated)

49. The '633 patent's semiconductor device also includes a **drift layer 14** (annotated in orange below) formed on a front side 16 of the **substrate 12**. *Id.*, 4:20–21. The **drift layer 14** may be epitaxially grown by, for example, a chemical vapor

deposition process, formed of silicon-carbide, and doped with N-type impurities to an "N-" concentration. *Id.*, 4:35–41. Not relevant to this petition, the '633 patent's Figure 1 also shows an optional current spreading layer 20 ("CSL").

EX1001, FIG. 1 (annotated)

50. "The semiconductor device 10 also includes two doped semiconductor wells or base regions 26, 28" that "are doped with a P-type impurity to a 'P' concentration." *Id.*, 5:23–24, 5:42–43. The region between the wells 26 and 28 represents the **JFET region 30** (annotated in salmon below). *Id.*, 5:25–26, 6:3–5; *cf.* EX1019 at 81 ("The JFET action occurs in the region between the p diffusions.");

id. at 44 ("JFET region"). The '633 patent notes that "the wells 26, 28 and the JFET region 30 may be formed by growing an extra-thick current spreading layer 20 and forming the 'P' wells 26, 28 using a suitable incorporation process such as an ion implantation process." Id., 5:56–60. Thus, the JFET region 30 and the current spreading layer 20 have similar doping concentrations (i.e., "N" concentration). Id., 5:54–56, Figure 1 (which labels both JFET region 30 and current spreading layer 20 as having "N" concentration).

EX1001, FIG. 1 (annotated)

51. Optionally and alternatively, according to the '633 patent, "[b]y forming a **JFET region 30** with a doping concentration that is greater than the

doping concentration of the **drift layer 14**, the specific on-resistance of the semiconductor device 10 may be reduced compared to a MOSFET device having JFET regions and drift layers of substantially equal impurity concentrations." *Id.*, 6:16–21; *cf.* EX1019 at 83–84 ("Increasing the donor doping concentration in the drain throats . . . has two beneficial effects." "[T]he cell size can be reduced and . . . *lower R<sub>DS(on)</sub> can be realized*."). The '633 patent also explains that fabricating the JFET region 30 to have a width 36 of "three micrometers or less," which is short "relative to a typical DMOSFET device [may] reduce the specific on-resistance of the semiconductor device 10." *Id.*, 6:21–26; *cf.* EX1019 at 83–84 ("Increasing the donor doping concentration in the drain throats . . . has two beneficial effects." "[T]he *cell size can be reduced* and . . . lower R<sub>DS(on)</sub> can be realized.").

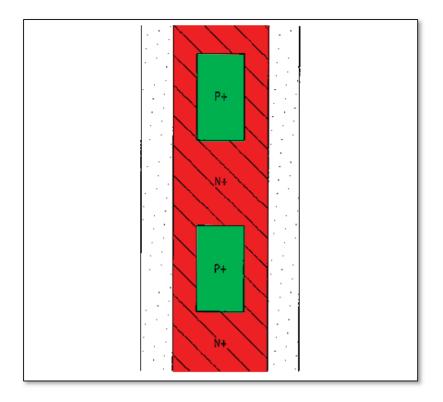

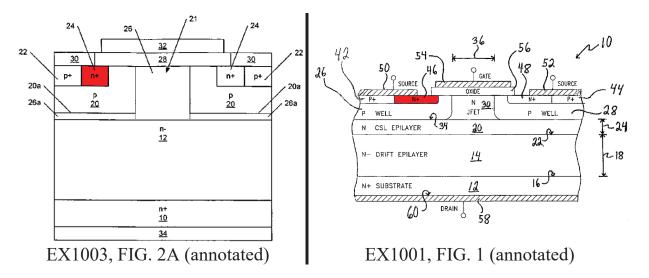

52. The semiconductor device 10 also includes **source regions 46 and 48** (annotated in red below) "defined in the P wells 26 and 28, respectively." EX1001, 6:63–65. "The **source regions 46 and 48** are doped with N-type impurities to an 'N+' concentration." EX1001, 6:65–66. **Base electrode regions 42 and 44** (annotated in green below and alternately referred to as "base contact regions" in the '633 patent specification) are located beside **source regions 46 and 48**, respectively, and are doped with P-type impurities to a "P+" concentration. *Id.*, 6:66–7:2; 7:30. The '633 patent explains that regions **42**, **44**, **46**, **and 48** may be doped "using any

suitable doping technique such as, for example, an ion implantation process or the like." *Id.*, 7:2–4. As Figure 1 illustrates, metallic **source electrodes 50 and 52** (annotated in lavender below) are formed over the **source regions 46 and 48**, respectively. *Id.*, 7:4–6. As shown in Figure 1, the **source electrodes 50 and 52** also extend over the **base electrode regions 42 and 44**.

EX1001, FIG. 1 (annotated)

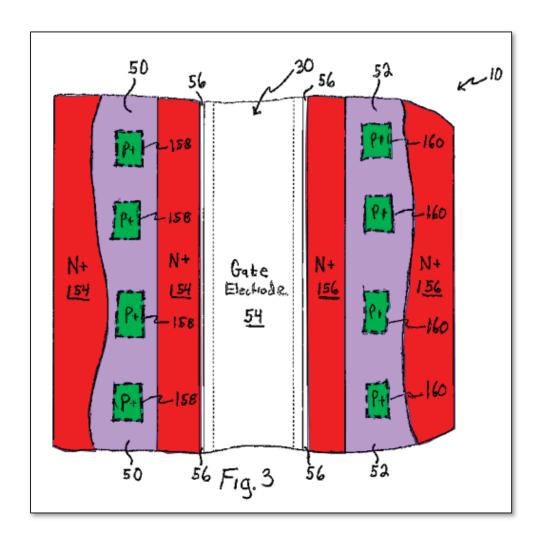

53. The '633 patent describes a "topological configuration" that, "[b]ecause of semiconductor manufacturing process variations, . . . can result in an undesirable source resistance if the **source regions 46, 48** are misaligned with

respect to the **base contact regions 42**, **44** and/or the **source regions 46**, **48** are misaligned with respect to the **source electrodes 50**, **[52]**." *Id.*, 7:39–44, Figure 2. "[T]o reduce the likelihood of misalignment between the source electrodes and the source regions," the '633 patent describes other topological configurations of its semiconductor device having source regions that each include "a plurality of base contact regions" arranged geometrically to increase "the tolerance to manufacturing variability." *Id.*, 7:52–8:6.

54. Whereas Figure 1 shows a cross-sectional side view, Figures 2–4 show views looking down onto the top of the device. *Id.*, 3:52–57. In particular, Figure 3 shows that "the **base contact regions 158, 160** are embodied as small 'islands' or regions within the larger **source regions 154, 156**." *Id.*, 7:57–59. In this arrangement, the "base contact regions 158, 160 are formed to be located in a central location under the **source metallic electrodes 50, 52** with areas of **source regions 154, 156** spaced between each **base contact regions 158, 160**." *Id.*, 7:59–63. For the sake of illustration, the annotated Figure 3 below shows the "islands" of **base contact regions 158, 160** as if they are visible in the plan (or top) view; however, it is understood that **source electrodes 50, 52** would cover **base contact regions 158, 160** in the physical device such that the "islands" would not be visible in the plan view (as denoted by dashed lines in the original Figure 3).

EX1001, FIG. 3 (annotated)

55. As the ground below demonstrates, the semiconductor structures described and claimed by the '633 patent were well-known in the art before the '633 patent's priority date.

# **B.** Prosecution History

56. The '633 patent issued from U.S. Patent Application No. 11/338,007, which was filed on January 23, 2006, claiming priority to U.S. Provisional

Application No. 60/646,152, filed on January 21, 2005. Independent claims 1, 12, and 17 referenced during prosecution correspond to issued claims 1, 9, and 12, respectively.

Based on my review of the correspondence between the patent 57. applicant and the U.S. Patent and Trademark Office, the Examiner issued a non-final Office Action on April 4, 2007, rejecting all originally-filed claims 1–23 as being either anticipated by or obvious over several prior art references. EX1008 at 2–15. In response, the Applicant amended independent claims 1 and 12 to require a siliconcarbide substrate, and claims 12 and 17 to be respectively directed to specific topological configurations of the '633 patent's Figures 3 and 4, among other things. EX1009 at 2–6. The Applicant argued in relevant part that, because "Ono and Zeng are directed toward MOSFET device having silicon substrates, while Kumar is directed toward silicon-carbide MOSFET devices, . . . it is clear that no one of ordinary skill in the art would combine Ono or Zeng with Kumar." *Id.* at 9–10. As I will explain further below, I disagree with the argument that the Applicant advanced. That is, a POSITA would have been motivated to modify prior art silicon carbide references based on teachings regarding silicon structures. EX1005, 4:22– 38 ("Almost all power MOSFETs being marketed today are fabricated in

monocrystalline silicon. . . . A power MOSFET . . . can be readily translated into silicon carbide using known manufacturing techniques.").

- 58. Correctly unpersuaded by the Applicant's argument, the Examiner issued a final Office Action, rejecting all pending claims and noting that, because "Ono and Zeng disclose *the structure of the DMOS device* and Kumar teaches the alternative of silicon-carbide with its known advantages[,] one of ordinary skill would indeed consider whether their particular problem would call for siliconcarbide." EX1010 at 12. The Applicant responded with similar arguments, but also further amended claims 12 and 17. *See* EX1011 at 2–9.

- 59. The Examiner rejected claim 1, maintaining that a POSITA would combine silicon and silicon carbide references, and allowed claims 12 and 17. EX1012 at 2, 9–10. The Examiner also indicated the allowability of claim 1's dependent claim 11, which was directed to the same configuration as claim 17. EX1012 at 9. Thereafter, Applicant amended claim 1 to include the subject matter of claim 11. EX1013 at 2, 8. The Examiner subsequently issued a Notice of Allowance on December 17, 2008, stating that the claimed configurations of the source regions and the base contact regions were not taught by the prior art. EX1014, Notice of Allowability at 2.

60. The Examiner did not have the benefit of *Ryu* and *Williams*, which are not of record. As I will show below, *Ryu* and *Williams*, disclose and render obvious the allegedly inventive features of the '633 patent, including the configuration recited by issued claim 9 and its dependents, all challenged herein.

## VIII. CLAIM CONSTRUCTION

61. I understand that "claim construction" is the process of determining a patent claim's meaning. I have been informed that claim construction is a matter of law and that in this proceeding, claim construction will be determined by the Patent Trial and Appeal Board ("the Board"). I understand that, during IPR, claims are construed according to the "Phillips standard." I understand that the Board need only construe the claims when necessary to resolve the underlying controversy. I also understand that, given the close correlation between the asserted prior art and the challenged claims of the '633 patent, the Board need not construe any terms of the challenged claims to resolve the underlying controversy, as any reasonable interpretation of those terms consistent with their plain meaning (as would have been understood by a POSITA at the time of the invention, having taken into consideration the language of the claims, the specification, and the prosecution history of record) reads on the prior art.

#### IX. OVERVIEW OF THE PRIOR ART REFERENCES

### A. Ryu

- 62. U.S. Patent Application Publication No. 2004/0119076 to Ryu ("*Ryu*") (EX1003), like the '633 patent, relates to "semiconductor devices . . . and, more particularly, to silicon carbide (SiC) metal-oxide semiconductor field effect transistors (MOSFETs)." EX1003, ¶3. Also like the '633 patent, *Ryu*'s embodiments of SiC MOSFETs "may reduce on-state resistance." *Id.*, ¶39, 64, 65.

- 63. For example, *Ryu*'s Figure 2A (reproduced below) shows a cross-sectional view of an embodiment of *Ryu*'s vertical MOSFET, which, as explained below, is strikingly similar to the cross-sectional view of '633 patent's MOSFET. EX1003, ¶¶28, 40. In *Ryu*'s Figure 2A, **layer 10** (annotated in blue below) may be a substrate made of silicon carbide and doped to an "n+" concentration. *See id.*, ¶40.

EX1003, FIG. 2A (annotated)

64. Ryu's MOSFET further includes a **drift layer 12** (annotated in orange below) on the substrate **layer 10**. Id., ¶40. Like in the '633 patent, the **drift layer 12** may be an epitaxial layer of silicon carbide and doped to an "n—" concentration. Id.

EX1003, FIG. 2A (annotated)

as the JFET region 21" (annotated in salmon below). *Id.*, ¶44. *Ryu* points out that "the gap 21 [(*i.e.*, the JFET region 21)] between the p-wells 20 has a higher carrier concentration than the drift layer 12." *Id.*, ¶42; *cf.* EX1001, 6:16–19 ("By forming a JFET region 30 with a doping concentration that is greater than the doping concentration of the drift layer 14, the specific on-resistance of the semiconductor device 10 may be reduced . . ."). According to *Ryu*, "if the gap is too narrow, the resistance of the JFET region 21 may become very high." EX1003, ¶44. For this

reason, Ryu discloses that "gaps of from about 1  $\mu$ m to about 10  $\mu$ m are preferred." Id.

EX1003, FIG. 2A (annotated)

66. Ryu's MOSFET also includes **n**+ **regions 24** (annotated in red below) and **p**+ **regions 22** (annotated in green below) disposed within the **p**-wells 20. EX1003, ¶45. The **n**+ **regions 24** are doped with n-type dopants to a "n+" concentration. Id., ¶¶6, 45, and Figure 1. The **p**+ **regions 22** are adjacent to the **n**+ **regions 24** and formed by implanting p-type impurities to a "p+" concentration. Id., ¶55. Ryu further discloses **source contacts 30** (annotated in lavender below) "to

provide an ohmic contact to both the p+ regions 22 and the n+ regions 24." EX1003, ¶47.

EX1003, FIG. 2A (annotated)

67. Comparing *Ryu*'s Figure 2A with the '633 patent's Figure 1 reveals that that *Ryu* discloses the same relevant semiconductor structure as the '633 patent.

#### B. Williams

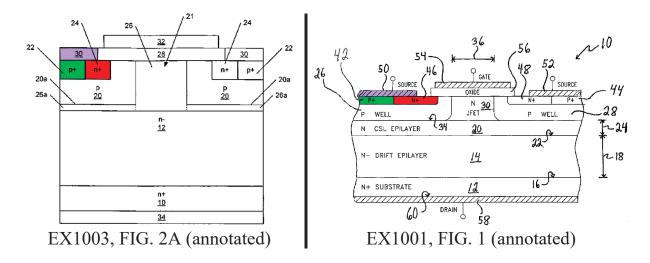

- 68. U.S. Patent No. 6,413,822 to Williams and Grabowski ("Williams") (EX1004), like the '633 patent, relates to vertical MOSFETs. See, e.g., EX1004, 1:7–8, Figure 1. Williams notes that "[t]he primary design goal for a power MOSFET used as a switch is to achieve the lowest on-resistance by simultaneously minimizing each of its resistive constituents." Id., 1:50–52. One of these resistive constituents is the source contact resistance. See id., 1:33–37. Williams discloses "plan views of various source-body designs" in Figures 19A–19F—including plan views just like those of the '633 patent—to "achieve the lowest possible resistance" by maximizing the area of the N+ source regions and/or to "suppress parasitic bipolar turn-on, prevent snapback and ruggedize the device" (i.e., prevent unwanted activation of the parasitic bipolar transistor) by maximizing the contact of the P+ body contact regions to the body region. Id., 10:17–18; 16:28–35.

- 69. Like the '633 patent's source regions 154, 156 with "island" base contact regions 158, 160, *Williams* also discloses a continuous **N+ source region** (annotated in red below) with **P+ body contact windows** (annotated in green below) in Figure 19E. EX1004, 10:23–24; EX1001, Figure 3. Like the '633 patent, *Williams* also uses the term "island," but in reference to the geometry shown in its Figure 19C where the **N+ source regions** are *not* continuous, and instead take the

"island" shape. EX1004, 10:20-21 ("FIG. 19C shows continuous P+ body contact region with N+ source 'islands'."). Nevertheless, a POSITA would have readily appreciated that *Williams*'s P+ body contact "windows" of Figure 19E correspond to the "island" base contact regions of the '633 patent. *Williams* teaches that such a source-body design provides "better N+ contact resistance and less P+ contact area (less rugged)." *Id.*, 17:18–19.

EX1004, FIG. 19E (annotated)

### X. SPECIFIC GROUND FOR PETITION

70. In my opinion, for the reasons noted below, claims 9–11 would have been obvious in light of the combined teachings of *Ryu* and *Williams*.

- A. Ground I: Claims 9–11 are Obvious Over *Ryu* in View of *Williams*

- 1. Independent Claim 9

- 71. The combined teachings of *Ryu* and *Williams* renders claim 9 obvious.

- (a) 9[preamble]: "A double-implanted metal-oxide semiconductor field-effect transistor comprising:"

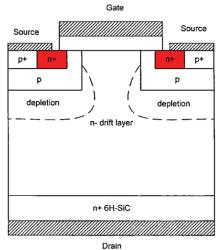

- 72. In my opinion, even if the preamble is limiting, *Ryu* discloses it. *Ryu* discloses a metal-oxide semiconductor field-effect transistor (MOSFET). EX1003, ¶¶3, 28, 40. *Ryu* explicitly states that Figure 2A is a MOSFET. *Id.*, ¶40 ("MOSFETs according to embodiments of the present invention are illustrated in FIG. 2A."). *Ryu*'s Figure 2A is reproduced below, alongside the '633 patent's Figure 1 for comparison.

73. Ryu's MOSFET includes a gate contact 32 ("the gate contact is **metal**"; EX1003, ¶13; see also id., claims 10 and 41), over a gate oxide 28 ("The gate oxide may be thermally grown and may be a nitrided **oxide** and/or may be other oxides.";

id., ¶46), over a combination of silicon carbide (i.e., a semiconductor) layers 26, 12, and 10 (id., ¶¶40–41), thereby creating a metal-oxide semiconductor device. *Cf.* EX1005, 1:45–50 (describing a MOSFET as including "a conducting gate electrode, typically metal, that is separated from a semiconductor surface by an intervening insulator, typically silicon dioxide.").

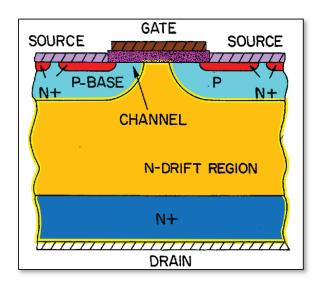

74. Ryu's MOSFET is doubly implanted. Ryu explains that, during the fabrication process of its MOSFET, using a mask 100, "impurities are implanted into the n-type epitaxial layer 26 to provide the p-wells 20," and in the next step of the process, "n-type impurities are implanted utilizing the mask 104 to provide the n+ regions 24." EX1003, ¶¶ 53–54, Figures 4B and 4C; cf. EX1021, 1:56–63 ("double" ion implantation sequence . . . by successive ion implantation of an acceptor atom (such as boron or aluminum) and a donor atom (such as nitrogen or phosphorous) to form the base and source regions, respectively."); EX1020 at 960 ("DMOS structure is formed in SiC using a double ion implantation with two separate *implantation masks*."); EX1022 at 659 ("the base and source regions are formed by successive ion implantation using aluminum or boron for the p-type base and nitrogen for the n+ source."). Ryu's doubly implanted p-wells 20 and n+ regions 24 configuration is also the same as in the "Vertical Doubly Implanted MOSFET (DIMOSFET)" that Ryu illustrates in Figure 1. Id., ¶6, 27, Figure 1.

75. Therefore, Ryu's MOSFET corresponds to the '633 patent's "double-implanted metal-oxide semiconductor field-effect transistor."

## (b) 9[a]: "a silicon-carbide substrate;"

76. Ryu discloses element 9[a]. Ryu explains that its layer 10, which is shown in various figures such as Figures 2A, 2B, 3, and 4E, is made of silicon carbide. For example, Ryu states that "...layer 12 of silicon carbide is on an optional n+ layer 10 of silicon carbide." EX1003, ¶40. Ryu also explains that layer 10 can be the substrate. Id., ¶56 ("...layer 10, which may be formed by a backside implant of n-type impurities in a substrate or may be an epitaxial layer or the substrate itself"). Ryu's claims 13 and 23, which were published along with the rest of Ryu on June 24, 2004, and therefore qualify as prior art, also clearly disclose a silicon Id., claims 13 ("... comprising an n-type silicon carbide carbide substrate. substrate"), 23 ("... wherein the n-type silicon carbide layer comprises an n-type silicon carbide substrate."). As shown by Ryu's Figure 2A and the '633 patent's Figure 1, both of which are reproduced below, Ryu's silicon carbide substrate 10 corresponds to the '633 patent's silicon carbide substrate 12.

(c) 9[b]: "a drift semiconductor layer formed on a front side of the semiconductor substrate;"

- 77. Ryu discloses element 9[b]. For example, Ryu's Figure 2A (reproduced below, alongside the '633 patent's Figure 1), shows that "a lightly doped n— drift layer 12 of silicon carbide" (i.e., "a drift semiconductor layer") is on the n+ layer 10. EX1003, ¶40.

- 78. Ryu further explains that its drift layer 12 is "formed on a front side of the semiconductor substrate." Ryu's Figure 2A shows that drift layer 12 is on the front side of substrate 10, just as the drift layer 14 of the '633 patent is on its substrate 12. Ryu also makes clear that its drift layer 12 is formed on substrate 10. Id., ¶53 ("Alternatively, the drift layer 12 may be provided on an n+ silicon carbide substrate.").

# (d) 9[c]: "a first source region;"

- 79. Ryu discloses element 9[c]. Ryu discloses that "regions of n+ silicon carbide 24 . . . are disposed within p-wells 20." EX1003, ¶45. A POSITA would have understood Ryu's n+ regions 24 to be source regions because Ryu's n+ regions 24: (1) are contacted by source contacts 30; and (2) correspond to the same "source regions" both in Ryu and Ryu's other articles describing the same structure.

- 80. *First*, *Ryu* explains that *source* contacts 30 provide ohmic contact to the **n**+ **regions 24**. EX1003, ¶47 ("Source contacts 30 ... provide an ohmic contact to ... the n+ regions 24."); *see also id.*, claims 6 and 36 ("a source contact on the first n-type silicon carbide region"). A POSITA would have understood that the **n**+ **regions 24** are *source* regions because they are contacted by the *source* contacts 30. In the same way, the '633 patent forms "source metallic electrode 50, 52 ... over the source regions 46, 48, respectively" to achieve the same function. EX1001, 7:4-6.

A comparison below of *Ryu*'s Figure 2A and the '633 patent's Figure 1 also shows that *Ryu*'s **n**+ **regions 24** correspond to the '633 patent's **source regions 46 and 48** and are similarly of n-type doping at an "n+" concentration.

81. **Second,** the n+ regions 24 in Ryu's Figure 2A correspond, in location and in relative position to other structures, to the n+ regions in Ryu's double-implanted MOSFET of Figure 1. Id., ¶27 ("FIG. 1 is a cross-sectional view of a conventional DIMOSFET"). Ryu's Figures 1 and 2A are reproduced below with the n+ regions highlighted in red. Ryu explicitly discloses that the n+ regions in Figure 1 are "source regions." Id., ¶6 ("source regions (n+)"). A POSITA would have understood that the n+ regions 24 in Figure 2A correspond to the n+ regions in Ryu's Figure 1 and that they were all source regions.

EX1003, FIG. 1 (annotated)

82. Similarly, the **n+ regions 24** in *Ryu*'s Figure 2A correspond to the N+ regions in the "DiMOSFET" that the inventor of *Ryu* presents in Figure 1 (reproduced below side-by-side with *Ryu*'s Figure 2A, with the N+ regions annotated in red) of a 2002 article titled "10 A, 2.4 kV Power DiMOSFETs in 4H-SiC." EX1023, Figure 1; *see also* EX1024, Figure 2. In Ryu's articles, EX1023 and EX1024, the DiMOSFET is drawn with a P-well structure centered and a portion of a gate at each of the left- and right-hand sides. In *Ryu*, EX1003, the same structure is drawn in Figure 2A with a gate centered and a portion of a p-well structure at each of the left- and right-hand sides. It would be readily apparent to a POSITA viewing these two drawings that the same structure is shown, just from a viewpoint shifted slightly to the left or right.

83. Ryu's articles explicitly disclose that the N+ regions are "source regions."

A 15  $\mu$ m thick, 5.5 x 10<sup>15</sup> cm<sup>-3</sup> doped n-type epilayer was grown on an n<sup>+</sup>, 4H-SiC substrate as the drift layer for the device. P-wells, 0.7  $\mu$ m deep, were formed via aluminum ion implantation, after which 0.3  $\mu$ m deep n<sup>+</sup> source regions were formed by nitrogen implantation. The MOS gate length, defined by these two implants, was 0.5  $\mu$ m.

EX1024 at 881; see also EX1023 at 321 (also describing "N+ source regions")

- 84. Accordingly, a POSITA would have understood *Ryu*'s **n**+ **regions 24** in Figure 2A to be *source* regions.

- 85. Thus, for example, *Ryu* discloses at least a first **n+ region 24** (*i.e.*, "*a first source region*") on the left in Figure 2A and a second n+ region 24 on the right.

- (e) 9[d]: "a first source electrode formed over the first source region, the first source electrode defining a longitudinal axis;"

- 86. The combination of *Ryu* and *Williams* renders element 9[d] obvious. As I will explain below, *Ryu*'s **source contact** 30 is a source electrode that is over **source region 24**. Moreover, it would have been obvious for *Ryu*'s **source contact** 30 to define a longitudinal axis.

#### i. "source electrode"

87. Ryu discloses that "one or more source contacts 30, in some embodiments are formed of nickel (Ni), titanium (Ti), platinum (Pt) or aluminum (Al), combinations thereof... to provide an ohmic contact to both the p+ regions 22 and the n+ regions 24." EX1003, ¶47. Because Ryu's source contacts 30 are formed from a conductor, and because they physically contact the n+ regions 24 (i.e., "source regions"), they are "source electrodes." Moreover, Ryu's source contacts 30 perform the same function as the '633 patent's source electrodes. Ryu's Figure 2A, for example, shows that the source contacts 30 are over the n+ regions 24, just like the '633 patent's source electrodes 50 and 52 are over the source regions 46 and 48. See also id., claims 6 and 36 ("a source contact on the first n-type silicon carbide region").

ii. "longitudinal axis"

88. Ryu in view of Williams teaches that the source contact 30 defines a longitudinal axis. Williams discloses vertical MOSFETs having linear cellular configurations. EX1004, Figures 4A, 7A–7B, and 18. Related to these configurations, Williams explains that "[t]he source and body contact construction can also be varied geometrically . . . as shown in the plan views of FIGS. 19A–19F." Id., 16:28-30. As shown in Williams's Figure 19E, for example, the N+ source region extends along a "longitudinal axis" (i.e., up-down with respect to the page), as annotated using a yellow arrow.

EX1004, FIG. 19E (annotated)

89. The obviousness of using *Williams*'s linear N+ source region configuration, which extends along a longitudinal axis, in *Ryu* is further shown by many other references, as I discussed herein, which demonstrate that MOSFETs with linear geometry were notoriously well-known. Moreover, a POSITA would have understood that, for a MOSFET to operate, a source electrode (*e.g.*, a metal or other conductive layer, such as *Ryu*'s source contacts 30) would be laid on top of and provide contact to the linear N+ source region and that, due to the linear geometry of the N+ source region, the source electrode would also extend in the direction of the linear source region and the electrode would thereby define a longitudinal axis.

- 90. As I discussed above in Section VI.F, Ryu's Figure 2A is a crosssectional view of a three-dimensional MOSFET and it was known in the art that such a cross section would correspond to a three-dimensional structure such as any of the well-known hexagonal, square, circular, linear, or triangular cellular structures. See EX1016 at 338–339 ("the DMOS structure allows any conceivable cell topology as long as it meets all technological constraints such as alignment tolerances"); id., Figures 6.55 and 6.56; EX1019 at 15–17, 70–73, 455–457, Figures 1.13 and 3.9. A POSITA would have found it obvious to fabricate Ryu's MOSFET into any one of these known cellular structures and, in particular, the linear cell structure taught by Williams. See, e.g., EX1019 at 455 ("[O]ne manufacturer advocates the use of a linear metal gate structure, in conjunction with a simple four-mask fabrication process, for producing inexpensive high-voltage devices. Another, quite sophisticated interdigitated design has been made for high-frequency application.").

- 91. A POSITA would have understood that, if fabricated as a linear cell, *Ryu*'s cross-sectional view of its MOSFET would extend perpendicularly to the page. The linear cellular arrangement of *Williams* was well-known in the art, as shown by, for example, *Rexer* (at left, below) and Baliga (at right, below), and as explained above, would have been an obvious design choice for *Ryu*'s cellular structure.

Linear cells have been commonly used in semiconductor technology 92. since they have often been the easiest and most reliable structures to pattern lithographically. See, e.g., EX1017 at 186 ("One common constraint imposed on VLSI layouts is the "manhattan" property, which requires that every edge of every feature be parallel to either the X or Y axis."); EX1018 at 238 ("A typical example of linear placement is the placement of a linear array, such as in gate matrix layout."). Additionally, most layout tools and software for such purposes have made it convenient to draw linear structures. See, e.g., EX1017 at 186 ("It can be shown that any complex set of manhattan mask features can be represented exactly in the form of a collection of abutting rectangles. It follows that a layout editor which can manipulate only rectangles can be used to create and edit any manhattan design. Indeed, this approach was taken in early 1980's with the Caesar editor from Berkeley . . . "). As a consequence, linear structures have been overwhelmingly the most common structures used in semiconductor layouts. Additionally, for a device that might be subject to high fields during use, the use of linear cells ensures more uniform and more predictable fields over the axis of the device. Accordingly, because the linear geometry was well known and because a POSITA would have been motivated to use it, it would have been obvious to construct the MOSFET of *Ryu*'s Figure 2A in view of *Williams*'s teachings of a linear cellular structure such that *Ryu*'s **n**+ **regions 24** and, consequently, *Ryu*'s **source contacts 30** extended perpendicularly to the page, thereby each **source contact 30** defining a longitudinal axis.

93. Thus, *Ryu* in view of *Williams* renders obvious at least a first **source contact 30** (*i.e.*, "a first source electrode") on the left, for example, formed over the left **n+ region 24** (*i.e.*, "the first source region"), with the first **source contact 30** defining a longitudinal axis.

## iii. Motivation to Combine Ryu and Williams

- 94. A POSITA would have been motivated to implement *Ryu*'s MOSFET according to *Williams*'s teachings such that *Ryu*'s MOSFET was formed using a linear cell structure having the **source contacts** 30 define and extend along a longitudinal axis.

- 95. Ryu and Williams are from the same field of endeavor. Both references are directed to vertical MOSFETs. Ryu discloses embodiments of vertical

MOSFETs that "may reduce on-state resistance" compared to conventional vertical MOSFETs. EX1003, ¶¶6, 9, 39, Figure 1. *Williams* discloses structures for vertical MOSFETs that are used to reduce on-resistance. *See, e.g.*, EX1004, , Figure 1, 8:15–16 ("reduce the on-resistance of the DMOSFET"), 16:31–32 ("achieve the lowest possible resistance"). Thus, both references are directed to vertical MOSFETs and aim at reducing on-resistance. EX1003, ¶6; EX1004, 1:7–8.

96. Although *Williams* discloses MOSFETs with a so-called trench gate and *Ryu* discloses a MOSFET with a so-called planar gate, a POSITA would nonetheless have been motivated to use *Williams*'s teachings in *Ryu*. This is because *Williams*'s and *Ryu*'s MOSFETs share many common features to which the shape of the gate is irrelevant. For example, both *Williams*'s trench-gated vertical MOSFETs and *Ryu*'s non-trench-gated vertical MOSFET include a parasitic BJT within the epilayer that could inadvertently be activated. For both *Williams* and *Ryu*, the solution to the potential problem caused by this parasitic transistor is the same. For example, *Williams* describes such a "parasitic NPN bipolar transistor," which it illustrates in Figure 7A (reproduced below). EX1004, 6:9.

EX1004, FIG. 7A (annotated)

97. *Williams*'s parasitic BJT is formed between the source, the body, and the drain in the same way *Grant* illustrates a parasitic "npn bipolar junction transistor (BJT) formed between the source, the body, and the drain" of a non-trench-gated vertical MOSFET in Figure 3.15, reproduced below. EX1019 at 81.

EX1019, Figure 3.15 (annotated)

98. Based on at least *Grant*'s teachings, a POSITA would have understood that a parasitic npn BJT would also be formed in *Ryu*'s MOSFET between the n+ region 24 (*i.e.*, source region), p-well 20 (*i.e.*, body), and the n-type epitaxial layer 26 (*i.e.*, portion of drain region), as annotated in *Ryu*'s Figure 2A below. *See* EX1003, ¶53.

EX1003, FIG. 2A (annotated)

99. Both *Ryu* and *Williams* prevent the parasitic BJT from activating by shorting the source to the body, via p+ diffusion, using a source electrode. EX1003, Figure 2A (illustrating **source contacts 30** shorting **n**+ **regions 24** to p-wells 20 via **p**+ **regions 22**); *see*, *e.g.*, EX1004, Figure 15D, 15:6–8 ("Metal layer [158] contacts both N+ source region 159 and P+ body contact region 160, thereby shorting the source and body together."). *See also* Section VI.D above. At least because *Ryu* and *Williams* both share the common problem of preventing the parasitic BJT from activating, and both solve that problem in the same way, *i.e.*, by shorting the body

to the source, a POSITA would have recognized that features of *Williams*, such as *Williams*'s well-known linear geometry, were applicable in *Ryu*.

- and *Williams* to silicon MOSFETs, *Baliga* teaches that conventional power MOSFETs, including silicon MOSFETs, "can be readily translated into silicon carbide using known manufacturing techniques." EX1005, 4:22–38. *Ghezzo* also teaches a method of replacing the conventional double-diffusion used in silicon MOSFETs with a double ion implantation sequence for silicon carbide MOSFETs. EX1021, 1:56–63.

- 101. Accordingly, a POSITA would have understood that the teachings of *Williams* were directly applicable to *Ryu*'s silicon carbide MOSFETs.

- n+ regions 24 and, consequently, *Ryu*'s source contacts 30 define and extend along a longitudinal axis as taught by *Williams* would have yielded expected, predictable results. *Ryu* discloses that "one or more source contacts 30, in some embodiments are formed of nickel (Ni), titanium (Ti), platinum (Pt) or aluminum (Al), combinations thereof . . . to provide an ohmic contact to both the p+ regions 22 and the n+ regions 24." EX1003, ¶47. *Ryu*'s source contacts 30 are formed from a conductor in physical contact with the n+ regions 24. As I described above,

Williams teaches, in Figure 19E, for example, an N+ source region that extends along a longitudinal axis. As also described above, the linear cell arrangement of Williams was well-known in the art, as shown by, for example, Rexer (at left, below) and Baliga (at right, below), and as explained above, would have been an obvious design choice for Ryu's cell structure having predictable results.

103. A POSITA would have been further motivated to combine the teachings of *Ryu* and *Williams* because forming *Ryu*'s structure using *Williams*'s linear cell arrangement would have been obvious to try. As I explained above, MOSFETs may have cross sections that are the same as or similar to the example shown in *Ryu*'s Figure 2A, yet have different—though all well-known—three-dimensional cellular structures. *See* EX1016 at 338–339 ("the DMOS structure allows any conceivable cell topology as long as it meets all technological constraints such as alignment tolerances"); *id.*, Figures 6.55 and 6.56; EX1019 at 15–17, 70–73, 455–457, Figures 1.13 and 3.9. Such cellular structures may include shapes that are

hexagonal, square, circular, linear, or triangular. A POSITA could have pursued any of these potential cellular structures, in particular the linear cellular structure, with a reasonable expectation of success because the analysis would have simply involved trying each one of these solutions. *See, e.g.,* EX1019 at 455 ("[O]ne manufacturer advocates the use of a linear metal gate structure, in conjunction with a simple fourmask fabrication process, for producing inexpensive high-voltage devices. Another, quite sophisticated interdigitated design has been made for high-frequency application."). Moreover, this implementation of *Ryu* using a linear cellular structure would have been well within the knowledge and skillset of a POSITA.

# iv. Reasonable Expectation of Success in Combining Ryu and Williams

The combination of *Ryu* and *Williams* represents a straight-forward implementation of steps of the well-understood semiconductor fabrication processes to change the shape and location of the structures, which a POSITA would have been familiar with and been able to implement. The reasons a POSITA would have expected success parallel those that provide motivation for this combination—including because both *Ryu* and *Williams* are directed to vertical MOSFETs. EX1003, ¶6, 9, 39, Figure 1; EX1004, Abstract, 1:7–8, Figure 1. As I discussed above, linear cell geometry was well known and a POSITA would have expected a linear cell implementation of

Ryu's structure to operate, just as linear cell implementations of other MOSFETs were known to operate. A POSITA would have had a reasonable expectation of success in implementing Ryu's MOSFET in a linear geometry because Ryu's underlying specification was designed to be extensible and flexible in its application to well-known cellular shapes and layouts. EX1003, ¶¶38 ("This invention may, however, be embodied in many different forms..."), 63, 66.

- 105. Accordingly, *Ryu* in view of *Williams* renders obvious element 9[d] and a POSITA would have been motivated to combine the teachings of these references and would have had a reasonable expectation of success.

- (f) 9[e]: "a plurality of first base contact regions defined in the first source region, each of the plurality of first base contact regions being spaced apart from each other in a direction parallel to the longitudinal axis defined by the first source electrode;"

- 106. The combination of *Ryu* and *Williams* renders element 9[e] obvious. As I will explain below, *Ryu*'s **p+ regions 22** are base contact regions. Moreover, it would have been obvious to form a plurality of *Ryu*'s **p+ regions 22** in the **n+ source regions 24** described in limitation 9[c], above, and spaced apart from each other in a direction parallel to the longitudinal axis defined by the **source contact 30**, all as taught by *Williams*. A POSITA would have been motivated to make this

combination for the reasons discussed below and would have had a reasonable expectation of success in doing so.

### i. "base contact region"

of p+ silicon carbide 22 are disposed within p-wells 20" and that the "regions of p+ silicon carbide 22 may be adjacent the regions of n+ silicon carbide 24." EX1003, ¶45. A POSITA would have understood that Ryu's p+ regions 22 are base contact regions because Ryu's p+ regions 22: (1) correspond to the same "p+ contacts" in Ryu's other articles describing the same structure; and (2) provide low resistance ohmic contact to the p-wells 20 to short the source to the base as was well known in the art.