# **Recent Advances in VLSI Layout**

ERNEST S. KUH, FELLOW, IEEE, AND TATSUO OHTSUKI, FELLOW, IEEE

Research in layout design during the past decade has had a significant impact on the entire VLSI industry. Because of advances made in automatic placement and routing, application specific integrated circuit (ASIC) design now represents a sizeable portion of the chip market. The influence of computer-aided physical design will continue to be felt in the future; for example, in further popularizing the sea-of-gates and building-block design styles. Recent advances in floorplanning and placement and in global and detailed routing pertinent to these design styles are reviewed. Also included are the subjects of computational geometry and layout engines. The former has received a great deal of attention among computer scientists and has found interesting applications in gridless routing and compaction. The latter is becoming an interesting research topic along with other hardware accelerators and special-purpose engines. Although all these subjects are carefully reviewed, much greater emphasis is placed on the discussion of the authors' own research.

#### I. Introduction

Computer-aided design has made a major impact in advancing the state of the art of microelectronics in the past decade. This is especially true in the area of physical design, where automatic and interactive design tools have become indispensable to the layout of VLSI chips. The turnaround time for layout design has been reduced from months and weeks to days and hours. Standard-cell and gate-array technology are now prevalent in application specific integrated circuits (ASIC) design. Even for high-volume custom chips such as microprocessors, CAD programs for floorplanning, placement, and routing are essential. As chips become increasingly complex, larger in dimension, and smaller in feature size, more sophisticated algorithms and layout software are clearly necessary. The sea-of-gates design style, for example, calls for efficient algorithms which deal with hundreds of thousands of gates. Previously useful algorithms based on simulated annealing or other random methods have become unusable: the computation time is unbearable in spite of the growing accessibility of faster

Manuscript received April 11, 1989; revised August 8, 1989. This work was supported in part by the Semiconductor Research Corporation, in part by the National Science Foundation under grant MIP-88-3711, and in part by the Japan Society for the Promotion of Science.

E.S. Kuh is with the Department of Electrical Engineering and Computer Sciences and the Electronics Research Laboratory, University of California, Berkeley, CA 94720.

T. Ohtsuki is with the Department of Electronics and Communication Engineering, Waseda University, Tokyo 169, Japan.

IEEE Log Number 8934098.

The current status of VLSI layout and the challenges in research for the future are the issues we will attempt to address. In an earlier special issue on computer-aided design, published in 1981, Soukup wrote an excellent review article on circuit layout [1]. Since then, several edited books on the subject have also appeared [2]-[4]. Because of page limitations we will not cover many of the problems and methods which appeared in these earlier review publications. For example, channel routing, although used extensively in current-day chip layout, is now a mature subject and will not be discussed. Others have become obsolete; gate matrix design, for instance, with the prevalent use of multiple metal layers. Simulated annealing, although useful in some applications, will not be included because its effectiveness in solving large and complex problems remains to be seen.

The standard-cell and gate-array design styles best illustrate the power of CAD. There are many good in-house, university, and commercial software packages. For example, the Timberwolf package [5], [6], which is based on simulated annealing, has proven to be an effective tool for small- and medium-size designs and is widely used. Therefore we will not review the methods used for placement and routing which are pertinent to standard-cell and gate-array designs. Instead, we have decided to tailor our discussions to seaof-gates and building-block (macrocell or general cell) designs. The building-block design style, which was first introduced at NEC [7] in the mid 1970's, has gradually been accepted in industry, especially in Japan [8], [9] and among those companies that deal with silicon compilation. However, because of the complexity involved, there is a lack of commercial software that offers not only versatile interactive features but also the capability of obtaining efficient layout with an area usage comparable to manual designs. The potential of building-block layout clearly has not been realized.

Roughly speaking, VLSI layout refers to the transformation of the functional and logic specifications of a desired chip to physical realization of transistors, cells, and macros together with their interconnection pattern. This in turn leads to a full mask specification in multiple layers with detailed geometrical data and processing information for chip production. The task is complicated, and it is impossible to speak of the truly optimum design. What is possible is to cleverly break up the overall problem into subproblems which then can be managed and possibly optimized.

0018-9219/90/0200-0237\$01.00 © 1990 IEEE

PROCEEDINGS OF THE IEEE, VOL. 78, NO. 2, FEBRUARY 1990

237

The well-known subproblems are partitioning, floorplanning, placement, global routing, and detailed routing. Each subproblem can then be formulated more precisely subject to the design styles. Within each subproblem, if suitable modeling is employed, there are problems that can be specified mathematically. Unfortunately, almost all such problems encountered in layout turn out to be NP hard. Roughly speaking, it is unlikely that the exact solution could be found in polynomial time. Furthermore, the objective function often does not reflect all the criteria that are ultimately desired. Therefore heuristics have played a major role in developing layout software. For the benefit of readers with no background in layout, we will try to give a concise overview of the subject, including necessary terminology and definitions, and whenever possible, a precise formulation of the problems. We will review some recent approaches but will emphasize our own work, which has yielded good overall results.

In Section II we will address placement and floorplanning for both the sea-of-gates and building-block designs. The former emphasizes the connectivity specification while the latter must also consider module shape and size. In Section III we will discuss global routing based on a method of successive cuts on a chip. This is a hierarchical top-down approach which is useful for both the sea-of-gates and the building-block designs. Next we will discuss a two-dimensional detailed routing problem. Finally, we will review the rip-up and rerouting problem.

In Section IV we will review the field of computational geometry and its application to layout—in particular, to gridless routing and compaction. Computational geometry has received a great deal of attention recently among computer scientists and could be a fruitful area of research in layout. In Section V we will discuss layout engines. Recent hardware advances and the increasing accessibility of parallel machines and supercomputers create an interesting debate as to the eventual fate of hardware engines for layout.

Finally, we will conclude with a brief mention of some of the topics of interest not treated in the paper.

#### II. PLACEMENT AND FLOORPLANNING

The placement problem for VLSI design is to place modules on a plane based on the given information on module interconnection. The purpose of placement is to facilitate routing with an overall objective; for example, to minimize the area of the resulting chip. The placement problem as stated is a two-dimensional problem; however, sometimes we encounter one-dimensional or linear placement. A typical example of linear placement is the placement of a linear array, such as in gate matrix layout. The placement problem is usually solved in two successive states: constructive placement and iterative improvement. Numerous methods have been proposed: clustering from bottom up, partitioning from top down, force directed, resistive network analogy, eigenvalue approach, etc. for constructive placement; and two-way or multiway exchange, simulated annealing, or other random methods for iterative improvement.

The interconnection specification is usually given by means of a *net list*. It specifies the precise topological relation between nets and pins of modules. Nets can be two-

terminal or multiterminal depending on whether they are to connect two pins or many pins. By modules we mean gates, cells, macros, or pads. The term macro, or macrocell, is used here to designate large cells whose shape and area must be considered in placement. Thus the placement problem can also be classified into two kinds: point-module placement and macrocell placement. Constructive placement for gate-array and standard-cell design is usually treated as a point-module placement problem, i.e., we ignore the size of the gate or cell. However, for iterative improvement, we need to take into account the position of the pins of the cell. In building-block layout, we consider the macrocell placement problem. It is more difficult because, in addition to the topological specification of the net list, we must consider the geometrical specification of the macros or building blocks. Although some macros may be rectilinear, we consider only rectangular modules, for simplicity. Even for rectangular modules, macrocell placement is a difficult problem. It is related to the simpler binpacking problem, which is known to be NP complete. In bin packing there is no net list specification; the sole purpose is to fit rectangular modules into a rectangle of min-

The floorplanning problem is related to the macrocell placement problem in that some modules may be soft, i.e., they have a fixed area but a variable aspect ratio. In addition, pin positions may need to be optimized. Typical examples of soft modules are PLA and logic blocks created by standard-cell design. Thus macrocell placement may be considered a special case of the floorplanning problem in which all modules are hard, i.e., with fixed area and aspect ratio. Obviously, floorplanning is a harder problem since it offers additional degrees of freedom to optimize the total layout area.

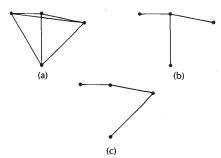

The quality of placement or floorplanning cannot be easily measured. Ideally, we need to complete the routing and obtain the total area. This is clearly not feasible because routing cannot begin without placement. Therefore a criterion based on some measure of wire length is usually used. Since routing is almost always carried out with horizontal and vertical wires, we may use the Manhattan geometry. A commonly accepted measure for placement is the sum of net length based on the half-perimeter of the enclosing rectangle of all the pins which belong to a net. In the case of a two-terminal net, this measure represents the shortest direct route of a Manhattan connection. For a three-terminal net, this is the length of a rectilinear Steiner tree, as shown in Fig. 1; thus it also equals the shortest horizontal/

**Fig. 1.** Half-perimeter wire length is equal to length of Steiner tree for three-terminal net. *S* is Steiner point.

vertical connection. For a multiterminal net, the half-perimeter length is, at best, a crude approximation. Fortunately, statistically speaking, over 75 percent of the nets of a typical chip are two-terminal or three-terminal. Thus the half-perimeter measure does give a good indication of the quality of the placement.

When point-module is used in the formulation, the net list must be modified first by merging all the pins which belong to a module. The resulting net list can be characterized by a 0-1 incidence matrix,  $\mathbf{A} = [a_{ij}]$ , where  $a_{ij}$  is zero if net i is not connected to module j; it is equal to one if net i is connected to module j. Another commonly used characterization for the net list is in terms of the connectivity matrix  $C = [c_{ij}]$ ; however, it is restricted to two-terminal nets. For an *n*-module problem, the  $n \times n$  connectivity matrix is symmetric with  $c_{ii} = 0$ , and the off-diagonal term  $c_{ii}$  represents the total number of connections between module i and module j. The connectivity matrix has nice properties. As seen later, it makes the formulation of the optimization problem obvious. Therefore it is important to be able to use the connectivity matrix to treat a general net list which consists of not just two-terminal nets. The three possible representations of a multiterminal net in terms of equivalent two-terminal nets are illustrated in Fig. 2, where a weighted clique of a four-terminal net is shown in Fig. 2(a), a minimum

Fig. 2. Representations of four-terminal net in following terms. (a) Weighted clique. (b) Minimum spanning tree. (c) Linear tree.

spanning tree is shown in Fig. 2(b), and a linear tree is shown in Fig. 2(c). Depending on the application, one representation may be better than another. In linear placement, for example, the linear tree representation may be the best one to use.

With the introduction of the connectivity matrix, the point-module placement problem can be formulated in terms of an objective function which measures the sum of the squared wire lengths of two-terminal nets. Let  $x_i$ ,  $y_i$  denote the coordinate of the ith module. The squared wire length objective function is defined as

$$L(x, y) = \frac{1}{2} \sum_{i,j=1}^{n} c_{ij} [(x_i - x_j)^2 + (y_i - y_j)^2] = x^T B x + y^T B y$$

where  $\mathbf{B} = [b_{ij}]$  is a modified connectivity matrix defined by

$$\mathbf{B} = \mathbf{D} - \mathbf{C} \tag{2a}$$

and thus

$$b_{ij} = -c_{ij}, \quad \text{for } i \neq j$$

(2b)

and D is a diagonal matrix with

$$d_{ii} = \sum_{i=1}^{n} c_{ij}. \tag{2c}$$

The point-module placement problem is then to minimize L(x,y) subject to the slot constraint, i.e., all modules are to be located on a two-dimensional grid, called the legal position. Since the coordinate vectors x and y enter separately in the sum of two quadratic forms in (1), we may consider each coordinate independently, which amounts to considering the linear placement problem. The slot constraints for linear placement can be expressed by a set of n algebraic equations in x, in terms of the coordinates of the legal positions [10]. Let  $P_i$  represent the ith legal position, then the constraint equations are

$$\sum_{i=1}^{n} x_{i} = \sum_{i=1}^{n} P_{i}$$

$$\sum_{i=1}^{n} x_{i}^{2} = \sum_{i=1}^{n} P_{i}^{2}$$

$$\vdots$$

$$\sum_{i=1}^{n} x_{i}^{n} = \sum_{i=1}^{n} P_{i}^{n}.$$

(3)

The problem of minimizing the quadratic objective function  $L = x^T B x$  subject to the constraint equation in (3) is clearly difficult if not impossible.

The eigenvalue approach first introduced by Hall [11] can be shown to be equivalent to minimize the quadratic objective function  $\mathbf{x}^T \mathbf{B} \mathbf{x}$  subject to the constraints of the first two equations in (3). By taking the two smallest nonzero eigenvalues of matrix  $\mathbf{B}$  and their associated eigenvectors, one obtains the coordinates of the point-modules on a plane. We call the solution the global placement. The modules so obtained will not be on slots since only two constraint equations are used in the formulation. Thus they must be moved onto slots by successive partitioning and/or iteration. The method is useful for small or medium-sized gate-array placement. Since determining the eigenvectors of a large matrix is a difficult numerical problem it is clearly not feasible for sea-of-gates design.

## A. Sea-of-Gates Placement

Sea-of-gates design differs from gate-array design in two aspects. First, in usual sea-of-gates designs, no routing channel is used, which means all routing is done over the gates. Second, the total number of gates could be very large, for example 50K or more, so computation algorithms that can handle very large problems efficiently are essential. Unlike the conventional gate array, there are very few software packages for sea-of-gates design.

The input to placement is in terms of a net-list for the cells. Each cell represents either a gate or an interconnected set of gates which form a basic logic element. The pads are placed at the periphery of the chip of I/O and power and ground connection. We assume that there are two or three metal layers for interconnection of the cells; however, throughout the chip there are blockages at various locations with one or more metal layers representing committed internal cell connection. The objective of the placement is to locate all the cells and pads in such a way that nets are uniformly distributed across the chip. To achieve 100-percent connection, which is required in gate-array technology, some of the active devices cannot be utilized because

their space must be reserved for routing. Thus the effectiveness of a sea-of-gates design can be measured by the percentage of gate utilization.

One of the main concerns in sea-of-gates placement is the size of the problem. To deal with more than 50K gates on a chip, hierarchical layout approaches have been proposed. One commonly used method is to divide the layout of a chip recursively into the layout of a set of smaller blocks, and place and route these blocks at a higher level using building-block techniques [12]. A series of steps needs to be addressed in the process: definition of layout hierarchy, area estimation, and aspect ratio assignment for each block; pin location assignments; block placement; and block routing. Some of these will be discussed later. In this subsection we briefly present the Proud placement program developed by Tsay at Berkeley [13]. The program is to be used either for a partitioned block of a chip or a chip itself if the gate count is not excessive. The constructive placement is based on a resistive network analogy which takes advantage of the sparsity of the net list specification. As we know, in circuit simulation sparse matrix algorithms have proven to be effective in handling circuits with many thousands of nodes.

Consider the electric network analogy of the placement problem. The objective function  $x^T Bx$  can be interpreted as the power dissipation of an n-node linear resistive network, with x corresponding to an n-vector whose components represent the voltages at the nodes. The modified connectivity matrix B is exactly the indefinite admittance matrix of the *n*-node resistive network with  $-b_{ii}$  equal to the conductance between node i and node j. The placement problem is then equivalent to that of choosing the node voltages of the n-node network for which the power dissipation is a minimum. In electric network theory it is well known that minimum power dissipation is implied by the two Kirchhoff laws. Thus we can reformulate our linear placement problem in terms of a linear resistive network problem provided that we include the I/O pad specifications. This allows us to model the I/O pads as fixed voltage sources applied to the network. The coordinates of the movable modules are then the node voltages to be determined. Therefore only sparse linear equations need to be solved. In the program Proud, the successive over-relaxation method is used to compute x.

The result of the global placement gives the optimal solution in terms of the original objective function L(x, y). This is because it is a convex quadratic function, so there exists a unique global minimum. In the real situation, modules occupy finite non-zero area and their shapes vary. While the slot constraint is not pertinent to the global placement problem, replacing the point modules with real modules may cause module overlaps at this step. We will specifically address the overlap problem and propose an efficient partitioning method with iterations to improve the initial solution. The key feature is that we again resort to solving linear sparse equations. We repeat the process in a top-down hierarchy to obtain the final solution. At each hierarchy, the placement interactions between the two partitioned parts will be handled by the block Gauss-Seidel (BGS) iteration method to obtain a solution which is close to the global one. In the following, we will first elaborate the partitioning

As shown in Fig. 3, we introduce a vertical cut line to par-

Fig. 3. Projecting modules from right half of plane to center line to determine left plane placement.

tition the chip into two. The location of the cut is determined by the area consideration based on the positions of the modules obtained from the initial global placement. We sort the modules from left to right and add up the module areas until roughly half of the total module area is reached. The cut is then made. If the cut line happens to coincide with the center line, we proceed to the next hierarchy level by performing horizontal cuts on each half. If not, we must move the cut line to the center in order to satisfy the area usage requirement. This calls for a modification of the placement in both halves. To achieve this, we introduce a simple heuristic, as follows.

Assume without loss of generality that the cut line is to the right of the center, as shown in Fig. 3. All modules to the right of the center line are projected horizontally on the center line as shown. We then solve the global placement problem in the left half-plane by the method outlined in the aforementioned. Note that, among the projected modules, only those modules which lie between the cut line and the center line will be included in the set of movable modules, whereas the others will be grouped with the fixed modules. We next repeat the placement algorithm for the right halfregion. However, before that, a temporary top-bottom twoway partition on the left half-plane is determined. These modules are then projected on the center line as fixed modules to solve the right half-plane problem. This process is repeated two or more times before the partition becomes fixed. We then reach the next hierarchy and proceed to find the global placements of the top and bottom quarters of each half. Eventually, after repeated partitioning, each block contains one and only one module with a legal location to which the module will be assigned. Since the partitioning scheme takes into account the available area, the resulting placement will usually have no overlaps.

The preceding concludes the constructive placement phase of the sea-of-gates Proud program. For iterative improvement, we consider actual pin position in evaluating an objective function based on the half-perimeter net length. Pairwise interchange and module insertion are used, but they are limited to within a window which covers only a portion of the entire chip. The size of the window is determined by a compromise between computation time and the quality of the final result.

For an experimental chip with 100K gates, the computation time of the Proud program on a VAX 8650 (a 6 MIPs machine) for the constructive placement phase is 50 minutes, and for the iterative improvement phase is about three hours. The proud program also contains features to place macros combined with basic cells. An algorithm has been developed to place the macros first. The pins of the macros must be considered and are treated like the I/O pads to

obtain a global solution. The hierarchical partitioning scheme must be modified to take into account the locations of the boundaries of the macros.

## B. Building-Block Placement and Floorplanning

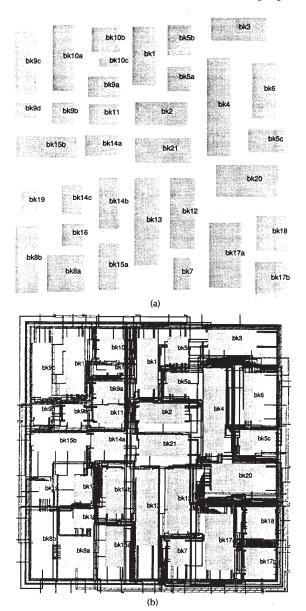

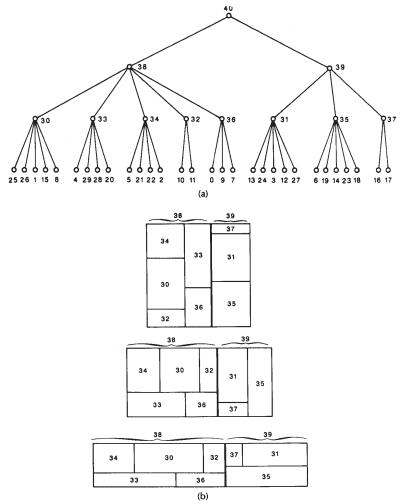

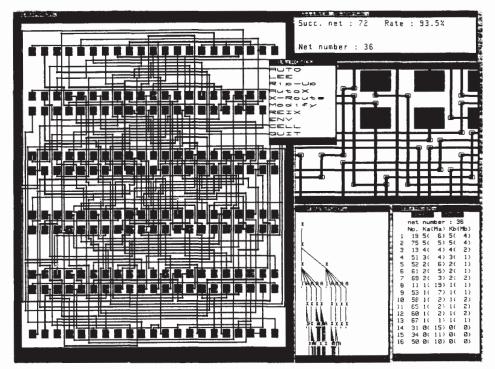

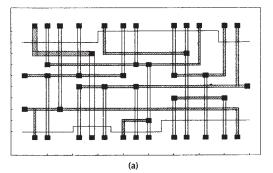

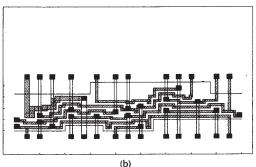

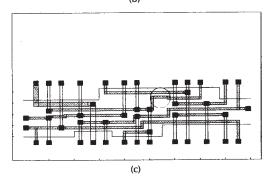

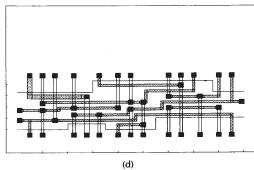

In Fig. 4 we show the result of placement and routing for a 33-block industrial chip done by the BEAR program, which was recently completed at Berkeley [14]. The placement part took 762 seconds on a VAX 8800. Note that in Fig. 4(a) routing space is provided based on a hierarchical wiring area estimation program. Crucial to building-block placement is the allocation of routing space on the routing plane between blocks. As a matter of fact, the problem of routing region

Fig. 4. Output of BEAR building-block layout system of industrial example, primBBL2, with 33 blocks and 123 nets. (a) Placement with routing area estimation. (b) Routing.

definition and ordering is an important aspect of buildingblock layout [15]. Furthermore, when the chip is routed, modules will be moved to accommodate the routing space required. Thus placement and routing interact; it is much more difficult to measure the quality of a placement alone, as in the case of the point-module placement. What really counts is the final total area after a chip is routed. We believe that wiring area estimation is an important part of placement and floorplanning using macrocells. Unfortunately, most published work ignores this important aspect. There has been, however, recent interest in wiring area estimation for layout design [16], [174], [175].

We will briefly review some pertinent work in floorplanning and placement; for example, the slicing structure, the top-down partitioning min-cut method, the polar graph representation, the shape function, the method of rectangular dualization, and the macrocell placement approach based on optimization. As indicated earlier, simulated annealing will not be included; however, it should be noted that programs like Mosaico [176] and others [177]–[179] have shown promise. We will briefly describe our own work used in the BEAR system, which combines bottom-up clustering with top-down partitioning. In BEAR, the problems of floorplanning and placement are treated in a uniform way, in hierarchical fashion, with only slight differences at the bottom hierarchy or the leaf level, where all hard modules must be used for placement.

The macrocell placement problem can be formulated as a nonlinear programming problem. Instead of using point modules, Sha and Dutton [17] introduced a line-segment representation of a rectangular macro to approximately depict its geometry. They used an objective function in terms of the squared wire length, and carried out the optimization subject to the nonoverlap constraints of the macros. The nonoverlap constraints are inequalities derived from the line-segment model. Rotation and mirroring of modules can be taken into account. A penalty function method and a sequential quadratic programming method have been proposed to find a solution. However, neither method guarantees a global minimum solution. Furthermore, because the nonoverlap constraints are based on a line-segment approximate representation, the method may even fail to ensure module nonoverlap. The required computation time is of the same order of magnitude as that of simulated annealing. Also, there is no routing-area estimation.

Placement based on min-cut partitioning [18] has been shown to be useful in standard-cell, gate-array, and building-block layout. Lauther [19] first demonstrated the effectiveness of min-cut partitioning in macrocell placement and, by introducing a graph representation, he established a close tie between the placement problem and floorplanning for the slicing structure. The basic idea is to group together those modules that are tightly connected and separate those that are minimally connected. This is accomplished by successive min-cut bipartitioning (two-way partitioning) in alternate vertical and horizontal directions. A modified Kernighan-Lin algorithm [20] is used. However, one key aspect of Lauther's method is to compute the sum of the areas of the macros of the two partitioned sets and make sure that the area difference between the two does not exceed a predefined threshold value. This criterion ensures that the min-cut partition will not lead to trivial

results, e.g., a single macro separated from the rest, and thus a uniform distribution of macros can be obtained. The same idea is used in the Mason floorplanner [21] developed at Carnegie-Mellon University. However, they introduce an additional feature called "in-place partitioning," which considers module connectivity in terms of terminal locations. At the end of the successive min-cut partitioning process, all modules are assigned to rectangular blocks which satisfy the area specification of each macro. Lauther's method contains a second phase which adjusts the shapes of the blocks to satisfy the aspect ratio of each macro and meanwhile does further optimization to reduce the total wire length by incorporating rotation and mirroring of the macros.

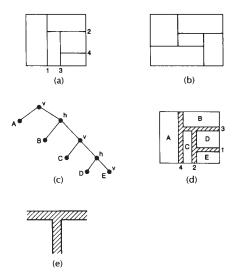

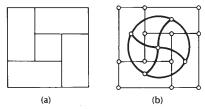

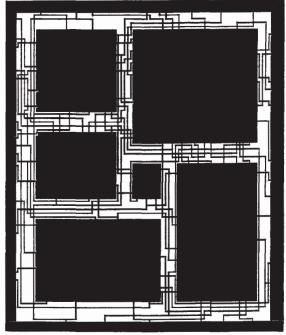

Clearly the first phase of Lauther's method is well suited to slicing-structure floorplanning since the area but not the dimensions of macros are considered in each min-cut bipartitioning. The use of slicing structure for floorplanning was first proposed by Otten and Szepieniec [22]. By slicing structure, we mean a floorplan which can be obtained by a successive slicing process. Fig. 5(a) illustrates

**Fig. 5.** Floorplanning for building-block layout. (a) Slicing structure with order of slicing indicated. (b) Nonslicing structure. (c) Tree representation of slicing structure. (d) Order of channel routing. (e) T-junction at two channels.

a slicing floorplan with 1, 2, 3, and 4 indicating the slicing sequence, while Fig. 5(b) gives the simplest structure, which is nonslicing. To be more precise, we start with a rectangular chip and cut it by  $k \ge 1$  parallel line segments into k+1 rectangles. The direction of cut may be either vertical or horizontal. The resulting k+1 rectangles can then be cut again by parallel line segments in the perpendicular direction from the first. The process continues until, in the end, each rectangular block, sometimes referred to as a room, is fitted by a macrocell. Note that in the nonslicing example of Fig. 5(b), slicing cannot be done at the outset.

It is useful to represent a slicing structure by a slicing rooted tree. Fig. 5(c) gives the slicing tree representation of the slicing floorplan in Fig. 5(a). The root of the tree represents the whole chip. The set of nodes at the next level

represents the resulting rectangles after the first stage of slicing. In the example in Fig. 5(a), it is done in the vertical direction. A marker h or v is used on each level of the slicing tree to depict the direction of slicing. Thus Lauther's method of min-cut bipartitioning always leads to a binary tree.

The slicing floorplan has a distinct advantage in that routing of the entire chip can be completed by using only a channel router. Furthermore, it is easy to demonstrate that the routing order turns out to be the reverse order of the slicing. For the example of the slicing floorplan in Fig. 5(a) its routing order is shown in Fig. 5(d). The essence of channel ordering is illustrated by a T-junction of two channels shown in Fig. 5(e). Clearly the vertical base channel must be routed first; its result, i.e., the width and floating terminal information, is needed to route the horizontal bar channel. In the case of a nonslicing floorplan, as in Fig. 5(b), channels cannot be defined unambiguously; there is always a cyclic conflict, and a channel router alone cannot complete the routing [15], [180].

A floorplan, whether of the slicing or nonslicing structure, can be represented by a pair of dual graphs, the vertical polar digraph and the horizontal polar digraph. The polar graph originated in the early 1940's in the problem of dissection of rectangles into squares [23]. Its use in IC design was first introduced by Ohtsuki, Suziyama, and Kawanishi [24]. Fig. 6 shows the vertical and horizontal polar digraphs

Fig. 6. Polar digraph representations of slicing structure.

of the floorplan in Fig. 5(a). In the vertical polar digraph, the top boundary of the rectangular chip is represented by a source and the bottom boundary of the chip is represented by a sink. Each slice in the horizontal direction is represented by a node. A directed edge exists between two nodes if there exists a block whose top boundary represents one node and whose bottom boundary represents the other node. The direction of the edge is from the node representing the top boundary to the node representing the bottom. The horizontal digraph is similarly defined, with the source representing the left boundary of the chip and the sink the right boundary. The edge direction is then from left to right. It is clear that both digraphs are acyclic and dual to each other. Furthermore, for a slicing floorplan, the digraphs are series-parallel graphs.

The floorplanning problem, as discussed in many published works, assumes a floorplan structure as represented by, for example, the polar digraphs. In other words, the relative placement is given. The objective is to find the minimum chip area subject to the constraint that each macro is specified by its area and perhaps a given shape function.

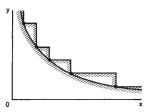

Fig. 7. Shape functions with continuous aspect ratio (parabola) and discrete aspect ratio (staircase).

For a given macro, if the area is fixed, its x-y dimensions can be plotted as a point on a parabola, as shown in Fig. 7. The function  $f(\cdot)$ , where y = f(x) is called the shape function. If, in addition, the aspect ratio is specified by discrete numbers, as in standard-cell design, the parabola is replaced by a staircase shape function as shown in the figure superimposed on the parabola. Obviously, the shape function gives the lower bound of a final floorplan design. If in the final design every rectangular block has an aspect ratio which sits on the parabola of the shape function, the design is then optimum. To find the optimum solution is, in general, difficult; Stockmeyer showed that the problem is NP complete [25]. In the polar graph representation, the edges can be assigned a weight which is equal to the area of the macro. In their recent work, Wimer, Koren, and Cederbaum [26] used polar graphs to prove that if the shape function of the macros is continuous, there exists a unique optimum floorplan, and they give its necessary and sufficient conditions. This implies that there is always a minimum area floorplan, and thus, ideally speaking, it is possible to have no wasted area in floorplanning.

For the discrete aspect ratio situation, i.e., macros with a staircase-shape function, a branch and bound method has been proposed to find the optimum solution [27]. Earlier, Ohtsuki, Suziyama, and Kawanishi used a mathematical programming formulation based on the electric network analogy to solve the same problem [24]. A similar approach was used by Ziebert and Saal [28]. In the electric network analogy, each macro is represented by a linear resistor. The height and width of the macro are then the branch voltage and current, respectively. Thus the aspect ratio gives the resistance value, and the area represents the power dissipation. The whole chip corresponds to a resistive network whose power is to be minimized with respect to the resistances in the network.

For the special case of slicing structure, polynomial time algorithms have been proposed by Stockmeyer [25] and Otten [29]. In the slicing structure, it is easy to combine the shape functions of the macros by traversing the slicing tree, similar to the series and parallel combinations of resistors. It is simple to show that by traversing through the slicing tree from the bottom up, we can obtain the combined shape function for the whole chip. Then, using the information on the desired aspect ratio of the chip, we can then traverse the slicing tree from the top down to determine the aspect ratio for each macro. This is essentially the method used in the Mason floorplanner [21]. The Mason floorplanner also contains the important feature of routing area estimation, done by performing a global routing after preliminary floorplanning. The tree traversing algorithm is then repeated to divide the routing areas into blocks.

Up to now the discussion of floorplanning has assumed that the structure of the floorplan is known and that the only purpose is to minimize the chip area by determining the aspect ratio of the macros. One way to obtain a slicing structure placement is to use the bipartition process proposed by Lauther. Other methods can lead to a general structure. In the following we will briefly review the method of rectangular dualization which can incorporate the adjacent relations of functional and logic blocks into floorplanning. The objective is to find a relative placement of the modules which is compatible with the overall topological relations of the functional blocks to be realized in a chip. For example, module interconnection by abutting is attractive because no routing space is required. Thus in floorplanning it is desirable to keep track of the adjacency relations of the functional and logical blocks. This could also influence the module designers to assign pin locations to facilitate abutting.

A rectangular floorplan as represented by its dissection D is shown in the examples Fig. 5(a) and Fig. 5(b). It can be characterized in terms of a graph. For simplicity, we assume that the line intersections, with the exception of the four corners, are T-shaped. A "+" type intersection can be decomposed into two T-shaped intersections. A rectangular dissection D can be represented by a planar graph, called the floorplan graph: G = (V, E), where V is a set of vertices representing the line intersections of D, and there exists an edge  $(v_i, v_i)$  in E if and only if the intersections corresponding to  $v_i$  and to  $v_i$  are adjacent. The inner faces of G are called rooms. To represent the adjacency relations between rooms of G, we construct the inner dual graph of  $G: G^* = (V^*, E^*)$ , where  $V^*$  is a set of vertices representing rooms of G, and there exists an edge  $(v_i^*, v_i^*)$  in  $E^*$  if and only if the rooms corresponding to  $v_i^*$  and to  $v_i^*$  have a common wall. The floorplan graph of Fig. 5(b) and its inner dual are shown in Fig. 8. The inner dual graph of a floorplan graph

Fig. 8. Floorplan graph. (a) Inner dual graph. (b) Nonslicing structure.

is a plane triangular graph, i.e., a graph which can be embedded in a plane and every face of which is a triangle. A plane triangular graph has a rectangular dual if it is the inner dual graph of a floorplan graph representing a rectangular dissection. The application of dual graphs to IC layout was first introduced by Suziyama, Nemoto, Kani, Ohtsuki, and Watanabe in 1970 [30]. The use of rectangular dualization originated in architectural design in 1971 [31]. Its application to IC floorplanning was first developed by Heller in 1979 [32]. Since then a number of publications have appeared [33], [34], mainly due to its graph theoretical interest. To apply the method to floorplanning, several steps are necessary. First, the block diagram which depicts the global

functional and logic interconnections must be converted to a planar graph. Next, the planar graph must be reduced to a plane triangular graph. To guarantee that it has a dual floorplan graph, the plane triangular graph must not contain complex triangles [35]. In the aforementioned processes, edge deletion and node insertion may be necessary; furthermore, for a given proper plane triangulated graph there exist many rectangular duals. Thus for a large network, the complexity is too high to be appealing. Nonetheless, the method can be used as a guide in floorplanning for simple designs.

In the following we describe briefly the floorplanner used in the BEAR layout system [36]–[38]. The same method is also used for placement with only minor modifications. The method has several advantages and has proven to yield good building-block layouts on several real examples. It is general in that it includes the nonslicing structure. The method depends on bottom-up hierarchical clustering to obtain a clustering tree. A top-down planning is next performed. The method includes hierarchical wiring area estimation and other look-ahead features.

The placement and floorplanning method used in BEAR can be viewed as a generalization of Lauther's mincut bipartitioning algorithm; however, the number of parts resulting per partition is not limited to two. With a larger degree of freedom to group elements together, an artificial separation of related macros is less likely. In mincut bipartitioning a binary tree is generated by a top-down process, whereas BEAR uses a data-driven bottom-up clustering and thus preserves a natural cluster of macros as much as possible. This is not the case in mincut bipartitioning because a binary tree determines the eventual placement of some macros to a great extent at the very outset. For the final placement it is also crucial that at the very end of bipartitioning the shape of the rooms should match the shape of the macros as much as possible. Since this is very difficult to achieve, an iterative step [39] or restructuring of the tree is necessary [40].

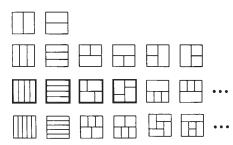

BEAR employs a clustering algorithm based on graph partition using a combined criterion of connectivity and geometry. The latter is heuristic in that blocks in pairs are forbidden if their areas or if the lengths of their longer sides differ significantly. We allow the maximum size of a cluster to equal five at each step. The step is recursively repeated and thus produces the different hierarchical levels in a bottom-up fashion of the cluster tree. We limit the size of each cluster to five because: i) with five or less blocks, a simple pattern enumeration followed by an exhaustive search is feasible, and ii) a general nonslicing structure floorplan is included in our treatment.

Next the method proceeds top-down from the root of the tree, which represents the whole chip, with the chip's specified aspect ratio and possibly I/O goals. The known information at this stage is represented by the clusters of blocks at the next level, which includes area and possibly shape information passed on from the leaves towards the root of the tree. The floorplanner then searches a library of floorplan templates and considers all possible room assignments which meet the combined goals of aspect ratio and I/O pads. The library of templates for two to five rooms is illustrated in Fig. 9. Note that only in the five-room situation does a nonslicing structure exist. The cost function is again given by a combined criterion of connectivity and geom-

Fig. 9. Floorplan templates for two-room, three-room, four-room, and five-room configurations.

etry. Fig. 10 illustrates a cluster tree with three possible floor plans whose chip aspect ratios equal 1:1, 2:1, and 4:1. The algorithms used at the leaf level and the nonleaf level are slightly different. The details are given in [38].

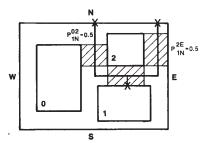

An important feature included is wiring area estimation. A simple top-down hierarchical method is used. Fig. 11 shows a three-block cluster with elements (0, 1, and 2) and I/O's (N, E, S, and W), where the shaded areas are called bottlenecks [41]. Each bottleneck has an estimated channel width which is calculated by the sum of possible nets going through the channel according to a probability measure. Consider the bottleneck between block 1 and block 2. The channel width is given by

$$w_{12} = t_{12} \sum_{i,j} p_{ij}^{12} C_{ij}$$

where  $C_{ij}$  is the connectivity between element i and element j,  $p_{ij}^{12}$  is the probability that the i-j connection goes through the bottleneck 1–2, and  $t_{12}$  is a heuristic weight factor which takes into account track sharing. The probability factors  $p_{1N}^{02}$  and  $p_{1N}^{12}$ , for example, are each equal to 0.5.

The preceding estimation takes advantage of all the information gathered about the position and connectivity of clusters of blocks up to that level. Earlier in the top-down process space for global connections between different clusters has been provided. Later on, in the successive levels, internal connections within the clusters become visible. Because the path information is precomputed for the finite number of topologies, the wiring area estimation can be done efficiently and simultaneously with the template evaluation process. Routing area can be treated in the same way as the block area in the objective function, to obtain an optimal floorplan/placement with routing.

There is an additional feature of floorplanning in BEAR which is used after global routing. It is called the global shape optimizer, and is similar in philosophy to a chip-level compactor. The optimizer assumes that module orientations and the relative pin locations are fixed. Given the initial placement and a set of constraints on module shapes for each module, the shape optimizer alters the location of modules and the aspect ratio of the soft modules to further reduce the chip area. The algorithm performs X- and Y-axis optimization in one pass. It iteratively reduces the longest path by picking up a modulelying on a critical path (in either direction) and resizing it so that the module dimension along the critical path is reduced. The process terminates when no significant improvement in the layout area can be achieved.

**Fig. 10.** Example of hierarchical floorplan enumeration. (a) Cluster tree. (b) Floorplanning with overall aspect ratio goals 1:1, 2:1, and 4:1.

Fig. 11. Hierarchical routing area allocation.

## III. ROUTING

After modules are placed, the remaining task in layout design is to make all the necessary interconnections. This means that pins of modules must be tied together by nets according to the net list specification, meanwhile satisfying both the physical constraints and design rules. The prob-

lem is usually referred to as *routing*. In the sea-of-gates design it entails the connection of many thousands of nets competing for the space throughout the chip that is left over from cell design. The principal requirement is to make 100-percent interconnection. In building-block layout, routing regions are defined after placement [15], though the areas of those regions are not yet fixed. The objective is to devise a method of routing which, when it is completed, minimizes the total chip area. Since the problem is complex, routing is done in two stages: global routing and detailed routing.

Global routing (sometimes called loose routing) calls for a routing plan in which each net is assigned to a particular routing region. The aim is not only to make 100-percent assignments but also to minimize the total wire length. Between neighboring regions, pseudo-pins are used to indicate the intersections of global paths with the boundaries of the local regions. These pins are sometimes called "floating," to imply that their precise coordinates on the boundary may not be fixed. Detailed routing takes over after

KUH AND OHTSUKI: RECENT ADVANCES IN VLSI LAYOUT

global routing and gives the precise recipe of net interconnections for each region in terms of net, via, and track assignments. Although detailed routing is sometimes done using only one layer, as in river routing [42], in most current practice two layers are used. As technology advances, routing on three or more layers will become important. Even now, multilayer interconnect is of real interest in packaging design.

The simplest approach to both global routing and detailed routing is sequential routing, i.e., to route one net at a time and to choose the shortest path whenever possible. The Lee-Moore grid expansion algorithm [43] and many of its modified versions have been widely used. The problem of finding the shortest connection for an *n*-terminal net is called the Steiner problem. It is related to the shortest spanning tree problem but it allows, in addition to the n given terminals, intermediate connecting points called the Steiner points. Unfortunately, the Steiner problem is NP complete. There exist simple heuristic algorithms, however, and for  $n \le 5$  the rectilinear Steiner tree is easily found [44]. Also, for global routing it is useful to consider the Steiner problem on a weighted graph [45]. For special graphs, such as the  $2 \times N$  grid graphs and the partial two-trees [46] and plane-triangular partial three-trees [47], there are linear time algorithms. These graphs have been found useful in hierarchical routing and in combining floorplanning with global routing [36], [48].

The objective of routing is to make 100-percent connection that minimizes the chip area. Clearly it is not generally possible to route all the nets with shortest connection paths because they compete with each other for paths. The sequential approach updates the available routing space after completing each net, as in the Lee-Moore router. The routing order becomes crucial. There are arguments for routing the shortest nets first; there are also arguments for routing nets with the most terminals first. It is almost impossible to devise a general procedure which works the best in all situations. The other approach is to route all nets independently, and if some routing space becomes overcrowded, reroute the nets which cause congestion. This sometimes can be accomplished by rip-up and rerouting, which will be discussed in section III-C. Often the information obtained from independent net routing can be used to help in implementing a totally different routing strategy based on the global view it presents. We will discuss global routing in section III-A and detailed routing in section III-B.

#### A. Global Routing

Although the aim of global routing is to minimize the total wire length, the approaches used differ somewhat according to the layout design styles [49]. For gate-array design there are methods based on deterministic optimization, simulated annealing, hierarchical top-down and bottom-up schemes, and strictly constructive methods [49]-[52]. In standard-cell design, feedthroughs must be used to interconnect cell rows. Global routing can be treated as a multichannel optimization problem using spanning-tree or Steiner-tree algorithms to reduce the total number of routing tracks [53]. For building-block layout, a graph is usually used to represent the topology of the placement, and sequential routing is done on the graph. The edge weight

of the graph, which depicts routing congestion, is updated after each net is routed [41].

In the following we will briefly discuss a method which is based on successive top-down cuts on a plane. The method was discovered independently by Marek-Sadowska for building-block layout [54] and by Lauther for sea-of-gates design [55]. Its special feature is that it is order-independent, and at each hierarchy, it attempts to simultaneously assign optimum net crossings at a cut-line. We have implemented the method in the BEAR program for building-block layout and in the Proud program for sea-of-gates design. We believe that the results are superior to any other available methods in terms of quality and computation time.

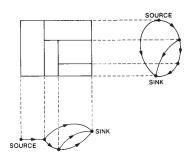

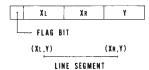

The essence of the method will be illustrated first with the sea-of-gates problem. We will assume that the routing capacity is uniform across the chip. The whole chip is divided into rectangular regions; at the boundaries of each region the capacity for net crossing is uniform. The end result of global routing is a specification for each region of the net list for detailed routing in terms of pseudo-pins and cell terminals. Clearly, with no overflow the number of net crossings must not be larger than the capacity at each boundary.

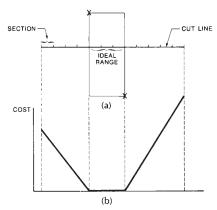

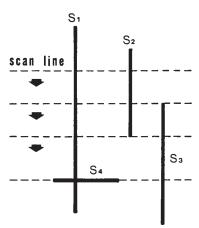

To illustrate, a horizontal cut is first made. There are altogether *M* sections evenly spaced on the cut-line, as shown in Fig. 12(a). We assume that there are *N* two-terminal nets

**Fig. 12.** (a) Illustrating cut-line, sections, enclosing rectangle of two-terminal net, and ideal range. (b) Cost function defined for net.

which must cross the cut-line from the top to the bottom. For simplicity, let us also assume that the capacity for each section is one and  $N \le M$ . It is thus possible to assign one net to a specific section in such a way that some measure of wire length is minimized. Specifically, we want to consider the incremental length, i.e., the length exceeding the shortest route for each net. A cost function must be introduced for each net with respect to the sections of the cut-line. Let us draw the bounding box of each net. Clearly, if the sections are within the bounding box of a net, the cost is zero. We say that these sections are in the ideal range. For sections outside the bounding box, the cost is proportional to the horizontal distance away from the ideal range, as shown in Fig. 12(b) by finite-slope straight lines. The slopes in the cost function may be defined according

to the vertical distance from the terminal to the cut-line. Nets compete for sections in their ideal ranges; some nets must take detours and thus there is a higher cost. For terminals very near the cut-line, the net should not be routed with a long detour away from the ideal range. Other criteria can also be used; for example, in routing critical nets. With the cost functions specified, the problem can be solved by standard linear assignment algorithms. As mentioned earlier, net assignment is done all at once without net ordering. After the initial cut, we proceed to the next hierarchy in the upper plane and lower plane. The process is repeated for each half-plane with vertical cuts. It is terminated when we reach to lowest level of hierarchy, i.e., when we attain the regions for detailed routing.

In the preceding we have assumed that all nets are twoterminal nets and each net is to cross the cut-line exactly once. For multiterminal nets, some preprocessing must be done to decompose the net into subnets. The best way is to find the minimum Steiner tree or an approximate minimum Steiner tree for each net. A subnet denotes a subtree which crosses the cut-line only once.

The location of the cut-line affects the overall result of global routing. What seems to count is net congestion. We have found that the best result can be obtained if the cut is made in the most congested area. Thus we propose to first obtain a density profile after placement. This entails finding all the Steiner trees of nets independently. The order of cuts is then determined according to the density profile with the most congested area cut first. Cuts need not be done at the center in each hierarchy; neither is an alternative horizontal/vertical cut required.

The preceding discussion must be elaborated to fit the real design situations in both sea-of-gates and buildingblock layout. The sections on each cut-line have routing capacity specifications. Let us use building-block layout to illustrate first. When a cut-line is made it intersects both the macrocells and the routing regions. The sections are defined accordingly. If we assume that no over-the-cell routing is allowed, then the sections defined by macrocells will have zero porosity, i.e., the capacity is zero. The capacity of sections defined by the routing regions depends on the number of tracks predetermined by placement with routing area estimation. If over-the-cell routing is allowed on one layer in some locations, the routing capacity for those sections must be calculated. In sea-of-gates design, the capacity specification must include information on whether two or three layers are used for routing and on where layer commitments have already been made in cell design. Once the capacity is specified and cost functions are given, the global routing problem can be described as follows. For each cut, we have sections  $j = 1, 2, \cdots M$ , each with a capacity  $C_i$ . There are nets/subnets crossing the cut-line,  $i = 1, 2, \cdots$ N. The cost is defined by an  $N \times M$  matrix  $W = [w_{ij}]$ , where  $w_{ii}$  is the cost of ith net assigned to the jth section. Let  $x_{ii}$ be a 0-1 variable, then we are seeking an assignment of nets to sections to minimize the total cost function F:

$$F = \sum_{i=1}^{N} \sum_{j=1}^{M} w_{ij} x_{ij}$$

$$\sum_{j=1}^{N} x_{i,j} \leq C_{j}$$

subject to

$$\sum_{i,j}^{N} x_{i,j} \leq C_{j}$$

and

$$\sum_{i=1}^{M} x_{i,j} = 1.$$

That the variable  $x_{ij}$  is zero implies that net i is not assigned to section j. It is equal to one if net i is assigned to section j. This is a familiar network flow problem in which the integer min-cut maximal flow solution can be obtained by standard methods [56]. The time complexity is, on the average, of  $O(M \times N)$ . For a building-block layout example with 77 macros and 500 nets, it takes 20 seconds CPU time on a VAX 11/780 to find a solution.

## B. Detailed Routing

In detailed routing a net list is given together with a specified routing region and available routing layers. For simplicity we assume that pins are accessible in any layer unless they are precisely specified. The primary requirement is to make 100-percent interconnection from the given net list using the space available. There are often additional objectives such as minimizing the total wire length or the total routing area if the routing region has flexible boundaries. Others may be imposed: minimizing the number of vias, considering prerouted nets such as power, ground, and bus lines, or treating critical nets specially, for instance.

The problem of detailed routing can be classified in terms of the number of available routing layers. For one-layer routing, the key constraint is planarity. There are wellestablished problems like river routing and single-row routing [57], [58]. For two-layer routing, a key strategy often employed, called H/V routing, is to route one layer with only horizontal wires and the other with only vertical wires. The connections between the two layers are made at vias. There exist numerous well-known algorithms for H/V routing. What is perhaps not so well-known is the concept of collapsed routing [59], which is a planar representation of twolayer routing. If knock-knee connections are excluded, the collapsed routing can easily be transformed to an H/V routing by inserting a via at every intersection. Horizontal connections can be routed all on one layer and vertical connections on the other. Well-known via-minimization algorithms can reduce the number of vias [60]-[64]. The result will have horizontal and vertical wires mixed on the two layers. The concept of collapsed routing is appealing because it initially disregards layers. We believe that this approach should be researched further to develop new routing algorithms.

The problem of via minimization has received considerable attention. It has both theoretical interest and practical significance. The problem can be classified into two: the constrained via minimization and the unconstrained, also called topological, via minimization. In the former, routing has already been done either on two layers or in the collapsed form. Via minimization then follows as a postprocessor. Algorithms based on graph representation and clustering have been reported which show that via reduction of 20 percent or more from an initial routing can often be achieved. The unconstrained via minimization problem was first introduced by Hsu in 1983 [65]. The aim is to minimize the number of vias based on the net list information without considering either the geometry of the region or design rules. It is an NP complete problem [66], but there

247

are heuristic algorithms which find a topological routing [67], [68]. The conversion of topological routing to geometric routing, however, is difficult. The problem lies in mapping topological routes onto routing tracks to fit the space and boundaries of the given routing region. Much more research is needed before topological routing becomes useful in real layout design.

Detailed routing can also be classified according to whether the routing region is a channel or a general twodimensional region. An ordinary channel is a rectangle with open ends on two opposite sides. There are pins on the other two opposite boundaries of the rectangle. Nets leave the channel through the open ends and are connected to other parts of the chip. In building-block layout, when four channels meet at a "+" (cross) intersection, the region of the intersection defines a rectangular routing region called a switch box. As far as the switch box is concerned, pins and pseudo-terminals exist on all four sides of the rectangle. The major difference between a channel and a switch box is that a channel is an open region and its width can be expanded or reduced according to the space required by a channel router. A switch box, on the other hand, is a closed region whose routing space is fixed. In channel routing, 100-percent completion is guaranteed and the main aim is usually to minimize the channel width. In switch box routing, though, the main aim is to make 100-percent connection. If, for a given net list, routing cannot be completed, the problem is said to be not realizable.

There are generalized versions which include rectilinear boundaries of both the channel routing problem and the switch-box routing problem. The channel can be L-shaped or Z-shaped [69]; the switch box becomes a two-dimensional closed region with a rectilinear boundary which may contain obstructions or rectilinear blocks. These generalizations are important in the detailed routing for both sea-of-gates design and building-block layout. In the following we will give a brief review of switch-box routing and its generalizations. We assume that vertical and horizontal routing grids are given in a closed two-dimensional region and design rules are automatically satisfied. The problem is to make 100-percent interconnection of the pins according to the specified net list.

Of course sequential routing in the form of either maze running or line search [70], [71] may be used. This should be combined, however, with other strategies such as a breadth-first search and minimum change in routing directions [72].

The hierarchical method developed by Burstein [73] can be used both for ordinary channels and switch boxes. It employs a divide-and-conquer technique and leads to excellent results for channel routing, but fails to complete the "Burstein difficult switchbox." Since the publication of the particular example in 1983, several routers have been developed which succeed in routing Burstein's difficult example.

The method introduced by Marek-Sadowska [59] is rule-based. It uses the collapsed routing strategy and conducts routing from the boundary of the region inwards. One key idea is to detect patterns of partial routing which call for a unique solution. A more elaborate rule-based router is Weaver [74], which is a knowledge-based expert systems router. Weaver produces excellent routing results, but takes an enormous amount of time even for simple problems.

The Mighty router [75] is based on an incremental routing strategy. It employs maze running but has the special feature of modifying the already-routed nets. The cost function penalizes long paths and those which require vias. Ripup and rerouting may be necessary to complete the routing.

Another recently developed heuristic router, Beaver [76], has yielded excellent results. The algorithm consists of three successive parts: corner routing, line-sweep routing, and maze routing. It uses priority queues to determine net ordering. In addition, an important feature of track control is employed to prevent routing conflicts. At the beginning, a net is given control of the tracks that extend out part of the way from its terminals. A portion of the tracks is reserved for other nets, so controlled sections may overlap and routing is done on a first-come-first-served basis. This method tends to give a more global view and serves as a guide to the heuristic routing process.

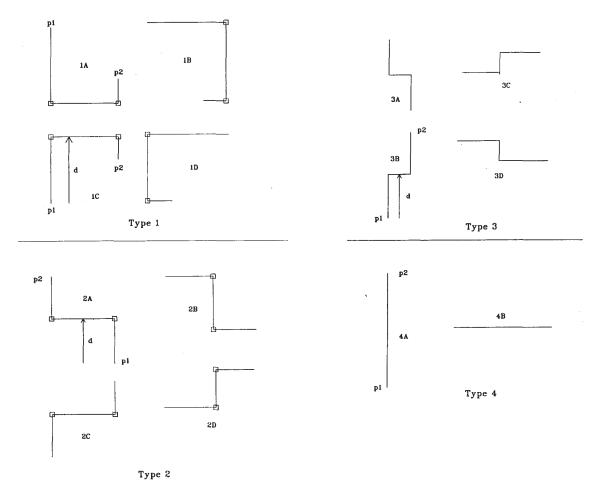

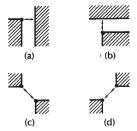

An earlier routing approach proposed for printed circuit board design, called a pattern router [77], [78], is useful in two-dimensional routing. The idea is to enumerate all possible patterns according to cost functions to determine the best path for a two-terminal net. This and various other strategies have been combined recently in the development of a template-based router [79], [80]. As shown in Fig. 13, only four basic types of template are needed. Within each type there are four different configurations depending on the orientation of the templates. For the three-segment template, the span of the central segment depends on the spacing of a given net. The end sections can be characterized in terms of a single number d, which depicts the relative dimension of the sections. If d = 0, the three-segment template is reduced to an L-shaped pattern.

Routing is done sequentially, with the longest half-perimeter net routed first in the present implementation. A control structure similar to that in Beaver is used. Terminals control a specified percentage of the length of the tracks they face. For terminals on the edge of a routing region, the distance is set to a fraction f of the available length of the track perpendicular to the boundary where the terminal lies. Whenever a net is completed, it releases control of all the grid points which it controls. Terminals are also allowed in the interior of the routing region. For these terminals, the reserved track extends in a preferred routing direction on both sides of the terminal, with a distance equal to f/2 of the distance to the boundary. It is easy to see that due to the control structure a deadlock situation can occur where one net does not permit another net to be routed. A special feature in the algorithm is the dynamic updating of the control structure with automatic decrease of the control region. Having uncompleted nets after one pass through the routing will lead to an automatic decrease of the extent of control for the remaining unconnected nets by a fixed amount until the control reaches zero toward the end of the routing process, when maximum congestion starts occurring.

To select a template to be used for routing a net, a set of costs is defined. In the formulation, we assume that obstruction may exist within the routing region. The following defines the various costs.

- C<sub>b</sub> Cost of routing on a grid that is blocked.

- C<sub>c</sub> Cost of routing on a grid point controlled by a net other than itself.

- C<sub>v</sub> Cost of a via.

PROCEEDINGS OF THE IEEE, VOL. 78, NO. 2, FEBRUARY 1990

Fig. 13. Routing templates for template-based two-dimensional router.

- C<sub>f</sub> Cost of routing over an uncontrolled grid point.

- C<sub>s</sub> Cost of routing on a grid point controlled by itself.

Then  $C_b$  is set to be infinity, and  $C_c \gg C_v > C_f > C_s$ . The costs of various templates are evaluated for each net to be routed between two terminals. The template with the minimum cost is selected if its cost is less than  $C_c$ . The connection between the two points is uniquely identified by the template chosen and the characteristic dimension number d. These parameters are stored in the memory, so that if, at a later stage in the routing process, a certain connection needs to be ripped, only the template number and its characteristic dimension needs to be retrieved.

If there are no templates that have a cost less than  $C_{cr}$  then either blockage has been encountered or a template passes over a grid that is being controlled by another net. A special strategy is needed, depending on the nature of the conflict, to find a successful path [80].

Multiterminal nets must first be decomposed into twoterminal subnets. Because the router allows terminals inside the routing region, a minimum Steiner tree can be used to define the subnets. In the present implementation, the minimum spanning tree is used. In summary, the templatebased router has several salient features. It is also very flexible in that if rip-up and rerouting is needed, it can easily be done because of the simplicity of the template's representation. Preliminary tests indicate that the router yields high-quality results in that most nets are routed with shortest paths. It is also extremely fast.

For the Burstein more-difficult switchbox example, the initial template-based routing completes 23 of the 24 nets, all with minimum wire length. The last net is completed by maze routing. The total wire length is 542 units and the number of vias used is 35, which is comparable to that of Mighty and Beaver [76]. The router has an additional special feature: it allows terminals to be prespecified on a particular layer

The problem of general two-dimensional routing is clearly more difficult than channel routing. There are no theoretical results, such as those in channel routing, obtained from a graph theoretical approach. However, in special situations, there are some intersting results. Nishizeki, Saito, and Suzuki [81] considered routing in a two-dimensional region with convex grids that include knock-knee intersections on one or two layers. They proposed an exact solution with a linear time algorithm if all nets are two-terminal and pins are restricted to the boundary. The agorithm is based on planar multicommodity flows and finds edge-disjoint paths

when they exist. Onaga [82] researched the switchbox problem and found a method for multiterminal nets which obtained similar results.

## C. Rip-Up and Rerouting

The primary goal of detailed routing is to achieve 100-percent interconnection using the space available. The conventional incremental routing algorithms suffer from a fatal disadvantage in that they provide no feedback or anticipation to avoid conflict between nets. Because of this blindness such autorouters often fail to connect all the nets and must be followed by manual rework to connect the remaining nets (usually less than 5 percent). What is typically done by designers for connecting the remaining few nets is to detect existing connections causing "blockages" and to rip up and reroute them so as to provide room for the blocked nets. The basic idea behind the recent rip-up and rerouting techiques is to simulate the human way of doing this. The goal of routing tools having the rip-up and rerouting ability is to achieve 100-percent interconnection as successfully as a human expert with shorter design turn-around time, by either improving existing autorouters or using interactive

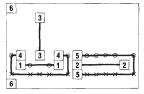

Recently, several CAD vendors have provided routers with rip-up and rerouting features, which achieves better performance. Until now, a few published papers [75], [83]-[85], [181] have reported rip-up and rerouting schemes, but they only ambiguously describe key strategies on deciding which existing nets should be ripped up and how their routes should be modified in order to complete the interconnection under consideration. Roughly speaking, these are the commonly used strategies: pay special attention to the neighborhood of the pins for subsequent interconnections [83]; push aside nearby existing nets so as to make room for a blocked net [75], [84]; remove some existing interconnections so as to connect the blocked net earlier [75], [83]; etc. The template-based router discussed in the last subsection uses a combination of the aforementioned schemes for rip-up and rerouting. In the following we will briefly discuss a graph-theoretic approach to rip-up and rerouting [86], [87] and its implementation on an interactive routing system, called WIRES [88], developed at Waseda University.

When a particular interconnection fails at an intermediate stage of incremental routing, it implies that some already-routed nets have blocked the pin pair. Such a blockage can be well characterized by the graph-theoretic term "minimal separator." The example shown in Fig. 14 will help an understanding of this term, where nets 1, 2, --- , 5 have been routed and net 6 has been blocked. The essential minimal separators for our purpose are those consisting only of the cells occupied by existing interconnections. Among them, two particular ones,  $S_A$  (reachable from a pin of the

Fig. 14. Minimal separators blocking net 6.

blocked net 6) and  $S_B$  (reachable from the other pin) can be found by means of exhaustive wave propagation, i.e., an obvious modification of the Lee algorithm. Those cells in  $S_A$  and  $S_B$  are marked with O and X, respectively.

In order to indicate the likelihood of rerouting particular nets to succeed, the following measure [86], [87] is derived from these two minimal separators. For each already-routed net W, let  $N_A(W)$  and  $N_B(W)$  be the number of cells of W contained in  $S_A$  and  $S_B$ , respectively. Then

$$P(W) = \min \{ N_A(W) - L_A(W), N_B(W) - L_B(W) \}$$

is called the "reroute effect index" for W, where  $L_A(W) = 1$ , if the pin pair of W lies in the opposite sides of  $S_A$ , otherwise it is equal to zero.  $L_B(W)$  is similarly defined. It should be stressed here that rerouting of W successfully makes room for the blocked net only if

$$P(W) \ge 1$$

.

In this particular example, we know that only net 4, with P(W) = 2, and net 5, with P(W) = 5, are worth trying for ripup and rerouting. Although rerouting of net 4 alone is actually successful in this example, the reroute effect index is useful to narrow the range of trial and error. It is desirable to improve this index because a larger value means it is more likely to succeed. An approach in this direction is reported in [88].

Very often we encounter a case where a simple rip-up and rerouting is of no help. Fig. 15(a) is such an example; net

**Fig. 15.** Example in which *X* router is effective.

2 has been blocked by the already-routed net 1. If we connect net 2 by means of a shortest path after removing net 1, as shown in Fig. 15(b), then net 1 is blocked as well. Thus the partial reordering does not work. In such a case, the "X router" implemented in the WIRES system [88] is of great help to find an optimal rerouting path. The cells marked with X in Fig. 15(c), called "X cells," indicate the essential part of the existing interconnection which blocks the unconnected net. Then the X router tries to find a path for the removed net 1 without using X cells so as to make room for the blocked net 2. Note that those X cells can be found

PROCEEDINGS OF THE IEEE, VOL. 78, NO. 2, FEBRUARY 1990

Fig. 16. Multiwindow display in WIRES system.

by means of a slight modification of the wave propagation search for obtaining the minimal separators [87], [88].

The sophisticated rip-up and rerouting is more suitable to implementation in a standalone interactive system than in an autorouter; the former has more flexibility to exploit expert designers' control. On the other hand, the interactive system must provide a pertinent set of commands that are executed very fast so as not to make the interactive operations tedious. The WIRES system has a backup hardware router to accelerate the execution of key commands, which will be briefly described in section V. The WIRES system, in addition to the ordinary incremental router, accommodates the commands for finding minimal separators, calculating reroute effect indices, temporarily removing an existing interconnection, generating X cells, invoking X router, etc. Fig. 16 shows an example of multiwindow display in WIRES. In this example the display consists of the whole wiring space, its partial zoom, command menu, reroute effect indices of blocking nets, and a managing tree representing a sequence of rip-up and rerouting trial.

Fig. 17 shows an example of two-layer wiring done by a graduate student using WIRES. There are 56 nets to be connected, but an incremental router left eight of them unconnected. The interconnection of the remaining nets was completed in 8 minutes (turn-around-time), where exhaustive wave propagation search, ordinary two-pin router, and X router were invoked 4, 14, and 6 times, respectively.

The rip-up and rerouting techniques are useful and promising for improvement of existing detailed routers. However, in order to solve large-scale problems in shorter time, research on faster backup accelerators and on rip-up and rerouting strategies based on gridless routing will be needed.

Fig. 17. Two-layer routing problem.

## IV. COMPUTATIONAL GEOMETRY IN VLSI LAYOUT

Theoretical computational geometry has advanced, aiming at applications such as geographic information processing, computer graphics, structural databases, etc. [89].

251

KUH AND OHTSUKI: RECENT ADVANCES IN VLSI LAYOUT

In the past several years, applications of computational geometry to VLSI layout have also become popular [94]–[110], [114]–[118]. Some of these contributions are summarized in a review article [90]. In this paper we will discuss some more recent results on design rule checking, gridless routing, and layout compaction, after briefly reviewing basic algorithmic techniques and data structures relevant to VLSI layout.

The geometrical patterns encountered in VLSI design are usually simple, i.e., polygons in the mask planes, although we have to deal with extremely large-scale problems. Many of the relevant geometric search problems can be characterized as intersection problems in which layout objects such as rectangles, line segments, points, etc., lying on the digitized plane, are under consideration. These intersection problems are classified into two categories. One of them, called "batched mode," is to report all the intersecting pairs among a given set D of objects. The other, called "on-line mode," is to report items of D that intersect a particular query object. The on-line mode problems are further divided into two classes: static problems, in which the underlying set D is not changed, and dynamic problems, in which D is updated by intersections and deletions.