Note that under these conditions, in which  $V_{\rm Ch}$  and  $I_{\rm D}$  are small, the channel behavior is ohmic and  $R_{\rm Ch} = {\rm d}V_{\rm Ch}/{\rm d}I_{\rm D} \propto (V_{\rm GS}-V_{\rm T})^{-1}$ .

At higher values of  $V_{\rm Ch}$  and  $I_{\rm D}$  the free-electron surface charge density  $Q_{\rm H}$  and the electric field  $E_{\rm y}$  both vary along the channel, as shown in Figure 3.3c. At y=0, the source end,  $Q_{\rm H}$  is unchanged:

$$Q_{1L}(0) = C_{ox}(V_{GS} - V_{T})$$

(3.7)

But at the drain end, it is reduced as a consequence of the voltage dropped along the channel:

$$Q_{\rm TL}(l) = C_{\rm ox}(V_{\rm OS} - V_{\rm T} - V_{\rm Ch})$$

(3.8)

If we take  $C_{\rm ox}(V_{\rm GS}-V_{\rm T}-\frac{1}{2}V_{\rm Ch})$  to be the average surface charge density, the total free-electron charge in the channel is reduced to

$$q_{\rm e} = C_{\rm ox} w l(V_{\rm GS} - V_{\rm T} - \frac{1}{2} V_{\rm Ch})$$

(3.9)

The average drift velocity remains  $v_d = \mu_e V_{Ch}/l$ , so the transit time is still given by Equation (3.5). The drain current is thus

$$I_{\rm D} = \frac{q_{\rm e}}{t_{\rm tr}} = \mu_{\rm e} \frac{w}{l} C_{\rm ox} [(V_{\rm GS} - V_{\rm T}) V_{\rm Ch} - \frac{1}{2} V_{\rm Ch}^2]$$

$$= k [(V_{\rm GS} - V_{\rm T}) V_{\rm Ch} - \frac{1}{2} V_{\rm Ch}^2]$$

(3.10)

The coefficient  $k = \mu_c(w/l)C_{ox}$ , is often referred to as the device transconductance parameter.

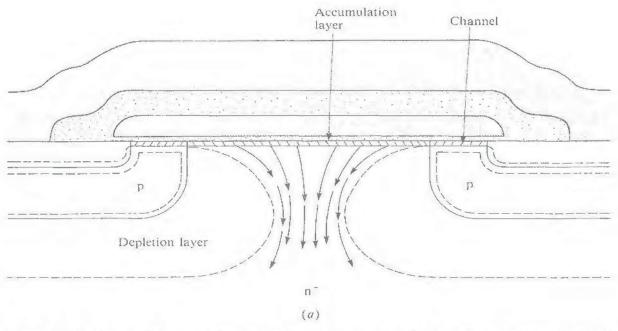

When  $V_{\rm Ch}$  is increased to the value  $V_{\rm GS}-V_{\rm T}$ ,  $Q_{\rm HL}(l)$  becomes zero. The channel then pinches off, and the inversion layer no longer continues through to the drain end. There a depletion layer forms. The situation is illustrated schematically in Figure 3.3d. Further increases in  $V_{\rm DS}$  do not change  $V_{\rm Ch}$  or  $I_{\rm D}$  but merely serve to expand the depletion layer at the pn junction. The increased voltage appears as the voltage  $V_{\rm SCL}$  shown in Figure 3.2, which is dropped across this depletion layer. We discussed in Appendix 1 how heavier doping of the p region than the n<sup>-</sup> region minimizes any reduction of the channel length caused by the expansion of the depletion layer. As a result, the conditions in the channel are little affected by increases in  $V_{\rm DS}$ . The drain current and channel voltage remain sensibly constant. Substituting  $V_{\rm Ch} = V_{\rm GS} - V_{\rm T}$  into Equation (3.10) gives

$$I_{\rm D} = I_{\rm D(Sat)} = \frac{1}{2} \mu_{\rm e} \frac{w}{l} C_{\rm ox} (V_{\rm GS} - V_{\rm f})^2$$

$$= \frac{1}{2} k (V_{\rm GS} - V_{\rm f})^2 \tag{3.11}$$

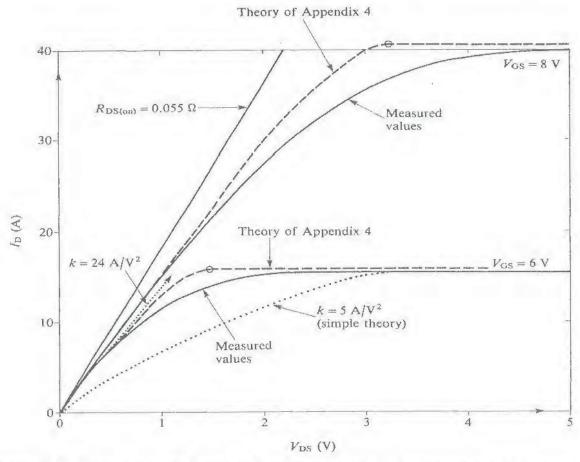

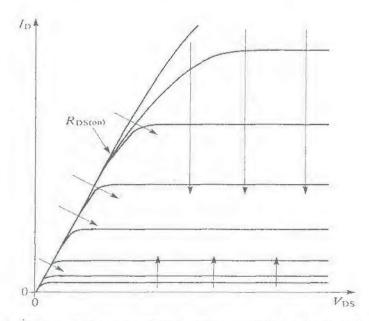

The characteristics shown in Figure 3.1 make it clear that for VDMOS FETS,  $I_{\rm D(Sat)}$  remains quite independent of  $V_{\rm DS}$  beyond pinch-off. In other types of MOSFET, where a small increase in  $I_{\rm D(Sat)}$  does occur, this can best be represented by

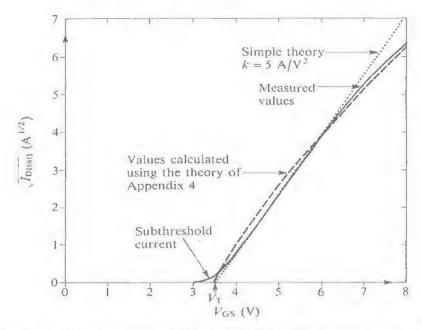

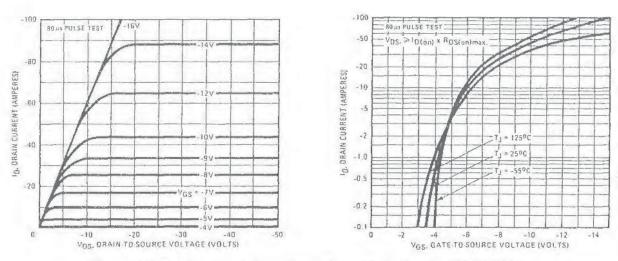

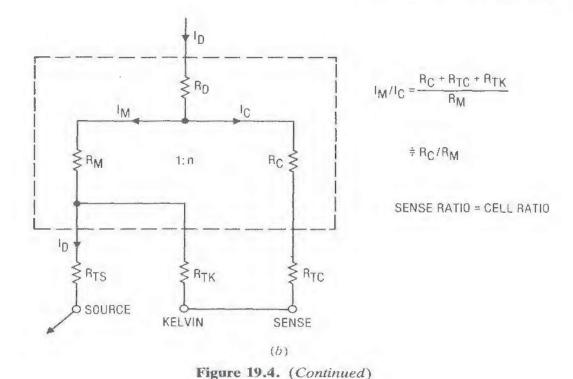

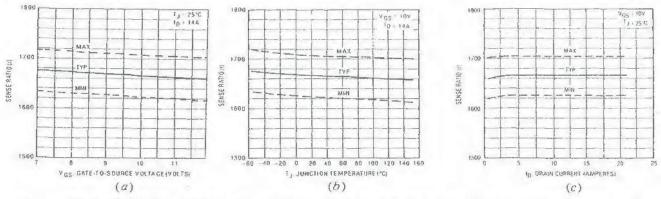

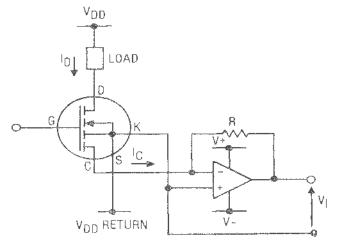

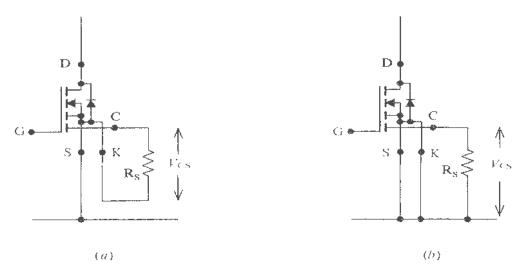

Figure 3.4. A plot of the square root of the saturated drain current versus the gate-source voltage. The data are taken from characteristics like those of Figure 3.1. They show that the behavior of this IRF 540 sample can be represented by  $V_T = 3.5 \text{ V}$ , and  $k = 5 \text{ A/V}^2$  for a range of drain currents between 0.2 and 16 A. Deviations occur at higher and lower currents.

introducing a channel-length modulation parameter,  $\lambda$ . Then

$$I_{\rm D} = I_{\rm D(Sat)}(1 + \lambda V_{\rm DS}) \tag{3.12}$$

where  $I_{D(Sat)}$  is given by Equation (3.11). For VDMOS devices  $\lambda \approx 0$ .

In Figure 3.4 a plot of  $VI_{D(Sat)}$  versus  $V_{GS}$ , taken in part from the curves of Figure 3.1, demonstrates the applicability of Equation (3.11) over a limited range of values. The measured value of k for this device, the IRF 540, is  $5 \text{ A/V}^2$ . If we assume that  $t_{ox} = 100 \text{ nm}$ , so that  $C_{ox} = 3.45 \times 10^{-4} \text{ F/m}^2$ , that the gate width is about 1 m, and that the electron mobility is  $0.05 \text{ m}^2/\text{V}$  s, this value of k implies a channel length in the region of 3.5  $\mu$ m. This is several times longer than we would expect. Furthermore, the characteristics shown in Figure 3.1 are much steeper near the origin than Equation (3.10) predicts, and they approach the constant-current condition more sharply.

Differentiation of Equation (3.10) with respect to  $V_{\rm GS}$  shows that in the linear region, the transconductance  $\partial I_{\rm D}/\partial V_{\rm GS}$  (with  $V_{\rm Ch}$  kept constant) should be  $kV_{\rm Ch}$ . Differentiating with respect to  $V_{\rm Ch}$  (with  $V_{\rm GS}$  kept constant) shows that the slope of the  $I_{\rm D}$  versus  $V_{\rm Ch}$  characteristics at the origin should be  $k(V_{\rm GS}-V_{\rm T})$ . When allowance is made for  $R_{\rm DS(on)}$ , the curves of Figure 3.1 indicate a value of k, on this basis, of approximately 24 A/V<sup>2</sup>. This implies that the effective channel length is less than 1  $\mu$ m, which is rather shorter than we would expect.

These discrepancies are not surprising, because there are several assumptions in the simple theory that do not bear close examination. These are discussed in Appendix 4. There it is shown that a physically more self-consistent theory

predicts values for  $I_D$  and  $I_{D(Sat)}$  that fit the measured device characteristics over a much wider range of values of  $V_{GS}$  and  $V_{DS}$ . We return to these results shortly, but first we consider what happens when higher gate voltages are applied.

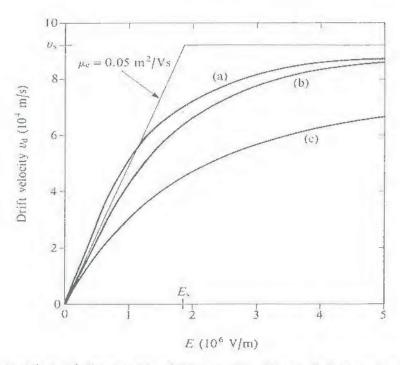

The predicted square-law relationship between  $I_{\rm D(Sat)}$  and  $V_{\rm GS}-V_{\rm T}$  comes about because first the total quantity of free-electron charge in the pinched-off channel is proportional to  $V_{\rm GS}-V_{\rm T}$ , and secondly the average longitudinal electric field in the channel is proporitional to  $V_{\rm Ch}=V_{\rm GS}-V_{\rm T}$  and thus so too is the carrier drift velocity. With the very short channels used in vDMOS FETS this is something that changes at higher values of  $V_{\rm GS}-V_{\rm T}$  and  $I_{\rm D(Sat)}$ . The electric field along the channel, whose average value is  $V_{\rm Ch}/l$ , becomes so large that it causes the electron drift velocity to saturate. This phenomenon is illustrated in Figure 3.5. Only for electric-field strengths less than about  $5\times 10^5\,{\rm V/m}~(0.5\,{\rm V/\mu m})$  is there a well-defined, constant electron mobility  $(v_{\rm d}\propto E)$ . At higher field strengths the drift velocity increases more slowly until, for fields exceeding about  $5\times 10^6\,{\rm V/m}~(5\,{\rm V/\mu m})$ ,  $v_{\rm d}$  becomes constant at the saturated drift velocity,  $v_{\rm s} \approx 9.2\times 10^4\,{\rm m/s}$ . Unlike the electron mobility,  $v_{\rm s}$  does not appear to depend on the normal electric field  $E_x$  at the semiconductor surface [3], but it is expected to decrease with increasing temperature.

For  $V_{\rm GS}-V_{\rm T}>E_s l$ , where  $E_s=v_s/\mu_{\rm c}$ , the carrier drift velocity approaches  $v_s$  over an appreciable proportion of the length of the channel before pinchoff occurs. Remember that pinchoff is defined as the point when  $Q_{\rm IL}(l)=0$ . The transit time then approaches the limiting value

$$t_{\rm tr} = l/v_{\rm s} \tag{3.13}$$

Figure 3.5. Saturation of the carrier drift velocity. Curve (a) shows experimental data based on the results of Ref. 3. Curves (b) and (c) are plots of Equation (A4.22) with  $\mu_{\rm e}=0.05~{\rm m}^2/{\rm V}$  s,  $v_{\rm s}=92{,}300~{\rm m/s}$ , and  $\alpha=2$  and 1, respectively.

At pinchoff,  $V_{Cb} = V_{GS} - V_{T}$ , so that combining Equations (3.9) and (3.13) gives

$$I_{D(Sat)} = q_c/t_{tr} = \frac{1}{2}C_{ox}w(V_{GS} - V_T)v_s$$

(3.14)

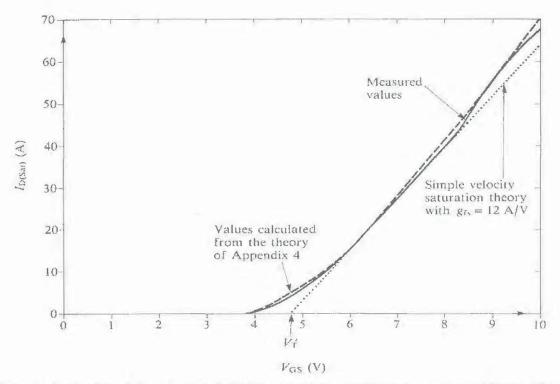

At the higher levels of drain current, these effects cause a more even spacing of the  $I_{\rm D}$ -versus- $V_{\rm DS}$  characteristics. This can be seen in the departure from the straight-line relationship in Figure 3.4 at high current levels. When these data are extended and plotted as  $I_{\rm D(Sat)}$  versus  $V_{\rm GS}$ , the linear relationship expected under velocity saturation conditions is obtained. This is shown in Figure 3.6. Equation (3.14) predicts the gradient of the curve to be  $g_{\rm fs} = \frac{1}{2}C_{\rm ox}wv_{\rm s}$ . Putting  $v_{\rm s} = 9.2 \times 10^4$  m/s, and using the values suggested previously as appropriate for the IRF 540 (namely  $C_{\rm ox} = 3.45 \times 10^{-4}$  F/m<sup>2</sup> and w = 1 m), we should expect this slope to be about 16 S. It can be seen in Figure 3.6 that the measured value is 12 S. Thus, once again, the simple theory predicts the general form of the device characteristics quite well, but not the transition to velocity saturation, nor the absolute value of  $g_{\rm fs}$  once this is established.

Taking  $l \approx 1 \,\mu\text{m}$ , we expect velocity saturation effects to become apparent over the range  $0.5 \,\text{V} < V_{\text{GS}} - V_{\text{T}} < 5 \,\text{V}$ . In fact they are seen in Figure 3.6 to be fully established at a gate voltage of 6 V and a drain current of 16 A. This corresponds to  $V_{\text{GS}} - V_{\text{T}} = 2.5 \,\text{V}$ , and the current is well within the maximum continuous current rating of the IRF 540, which is 27 A.

Figure 3.6. A plot of the saturated drain current versus the gate-source voltage. The data are taken from characteristics like those of Figure 3.1. They show that the behavior of this IRF 540 sample can be represented by  $g_{\rm fs} = 12 \, {\rm S}$  and  $V_{\rm T}' = 4.7 \, {\rm V}$  over the current range 10 to 45 A. Deviations occur at higher and lower currents.

It should be noted that the effective value of the threshold voltage in the velocity saturation region, which we call  $V_{\rm T}'$ , is higher than the effective value,  $V_{\rm T}$ , that applies when the square law [Equation (3.11)] relates  $I_{\rm D}$  and  $V_{\rm GS}$ . This can be seen by projecting back the linear parts of the graphs in Figures 3.4 and 3.6 to  $I_{\rm D(SAT)}=0$ . This type of behavior would be expected in a more detailed theory, because of the gradual onset of velocity saturation. For purposes of device modelling,  $V_{\rm T}'$  should be used in Equation (3.14), rather than  $V_{\rm T}$ .

Velocity saturation can be a valuable feature of power mosfers, even though it causes the drain current to become limited at much lower levels than would otherwise occur. It gives rise to a linear transfer characteristic ( $g_{\rm fs} = {\rm constant}$ ) that is beneficial in linear-amplifier applications.

It has become customary to refer to velocity saturation in power mos devices as a "short-channel" effect. This is unfortunate because to a visi engineer, who is designing small mosfet devices for very large-scale integration, the short-channel effect is something quite different and wholly bad. When channel lengths are reduced in the quest for smaller devices, basic device characteristics can be preserved, as long as all linear dimensions and all voltages are scaled in direct proportion and doping densities are varied in inverse proportion [4]. If this is not done,  $V_{\rm DS}$  may modulate the channel length, making  $\lambda$  large. It may even cause variations in the height of the potential barrier at the source end of the channel, thereby preventing effective cutoff at the threshold voltage. Clearly, velocity saturation gives rise to a very different kind of short-channel effect in power mos devices.

When devices are operated at high current levels, two effects may act to reduce the electron mobility and hence the drain current. This may occur either in normal use, or when device characteristics like those of Figure 3.1 are being measured. The first is simply the rise in junction temperature that results from the dissipation. Unless very short pulses at low duty cycle are used, this can cause an apparent negative differential resistance, with the drain current falling as  $V_{\rm DS}$  is increased. The second is the increased electric field normal to the surface,  $E_x$ , that results from the higher values of  $V_{\rm GS}$  required. This is expected to reduce  $\mu_{\rm e}$ , but not  $v_s$ . The average value of  $E_x$  in the inversion layer may be taken to be  $(Q_{\rm D} + \frac{1}{2}Q_{\rm IL})/\epsilon_0\epsilon_{\rm Si}$ . It thus varies from about 15 V/ $\mu$ m at threshold to over  $40 \text{ V}/\mu\text{m}$  when  $V_{\text{GS}} = 20 \text{ V}$ . For device modeling the variation of  $\mu_{\text{e}}$  is usually approximated by putting  $\mu_e = \mu_{e0}/[1 + \theta(V_{GS} - V_T)]$ . Values of  $\mu_{e0}$  and  $\theta$  may be expected to depend on the doping level and the surface conditions. The values normally used for a typical power vDMOs FET are  $0.05 \,\mathrm{m}^2/\mathrm{V}\,\mathrm{s}$  and  $0.1 \,\mathrm{V}^{-1}$ , respectively. Such a large value for  $\theta$  includes effects associated with higher gate voltages in addition to the direct effect on the mobility through the normal field  $E_x$ .

The more complete theory for the drain-current characteristics presented in Appendix 4 takes into account several effects neglected in the simple theory. These include:

- 1. the extra charge contained in the depletion layer at the drain end of the channel because of the higher voltage dropped across it;

- 2, the reduced electron mobility and eventual velocity saturation at high longitudinal field strengths  $E_y$ .

Neither of these alters the predicted drain current at very low levels. Both cause  $I_D$  to increase more slowly as  $V_{Ch}$  rises and the constant-current condition is approached. It is this that gives rise to the discrepancy between the simple theory of Equations (3.10) and (3.11) and the device characteristics.

There remains one more important effect that is neglected in the theory. That is the gradual reduction in the doping concentration of the channel towards the drain end. This leads to a reduction in the charge density in the depletion layer  $(Q_D \text{ reduced})$ , and hence to an increase in the inversion-layer charge  $(Q_{IL})$ . As a result, the longitudinal electric field needed to maintain any given drain current is reduced, and the saturation drain current  $I_{D(Sat)}$  is increased. It is this that accounts for the unexpectedly low effective channel lengths implied by the characteristics.

The variation of  $v_d$  with  $E_y$  assumed in the theory of Appendix 4 takes the

Figure 3.7. Comparison of theoretical and experimental characteristics. Full curves are taken from the experimental characteristics for the IRF 540 shown in Figure 3.1. The dotted curves are plots of Equation (3.10) for k=5 and  $24 \text{ A/V}^2$ . The lower value fits the constant current region with  $V_{\rm GS}=6 \text{ V}$ ; the higher value fits the observed gradient at the origin. The dashed curves are plots of Equation (A4.34), and represent the results of the more sophisticated theory set out in Appendix 4. It can be seen that this theory predicts a sharper approach to the constant-current condition than occurs in practice. In each case, in calculating  $V_{\rm DS}$ , a value of 0.055  $\Omega$  has been assumed for  $R_{\rm DS(on)}$ .

form  $v_{\rm d} = \mu_{\rm e} E_{\rm y}/(1+E_{\rm y}/E_{\rm s})$ , with  $\mu_{\rm e}$  being a function of the gate-source voltage, as has just been mentioned. Then  $E_{\rm s} = v_{\rm s}/\mu_{\rm e}$ , with  $v_{\rm s} = 9.23 \times 10^4$  m/s. The effect on the theoretical characteristics is simply to increase the effective channel length by  $V_{\rm Ch}/E_{\rm s}$ . Thus k decreases as  $V_{\rm Ch}$  and  $I_{\rm D}$  increase. It can be seen in Figure 3.5 that this assumed form for  $v_{\rm d}(E_{\rm y})$  underestimates the true drift velocity at any given field.

Results obtained using the theory of Appendix 4 are included in Figures 3.4 and 3.6. The device parameters used previously are assumed:  $n_{\rm A}=1\times 10^{23}\,{\rm m}^{-3}$ ,  $n_{\rm D}=1\times 10^{26}\,{\rm m}^{-3}$ ,  $t_{\rm ox}=100\,{\rm nm}$ ,  $Q_{\rm SS}=4\times 10^{-4}\,{\rm C/m^2}$ ,  $w=1\,{\rm m}$ . The effective channel length is taken to be  $l=0.7\,\mu{\rm m}$ , and the mobility parameters used are  $\mu_{\rm e0}=0.06\,{\rm m^2/V}\,{\rm s}$  and  $\theta=0.02\,{\rm V}^{-1}$ .

Equation (3.10) predicts a parabolic variation of  $I_D$  with  $V_{Ch}$ , with the drain current remaining constant once it reaches its maximum value. In Figure 3.7, the results of this simple theory and the theory developed in Appendix 4 are each compared with two of the experimental characteristics taken from Figure 3.1. In estimating  $V_{DS}$ , a value of 0.055  $\Omega$  has been assumed for  $R_{DS(on)}$ . This is a typical value for the IRF 540. It is clear that neither theory provides a close fit to the experimental curves. The simple theory, with a value of k that matches the observed constant current, predicts an initial rise of drain current that is much too low, and a channel length that is much too long. The full theory approaches constant current rather too abruptly, but makes no arbitrary assumptions. All the input parameters can be related in some way to the construction of the device.

### 3.3. THE SUBTHRESHOLD REGION

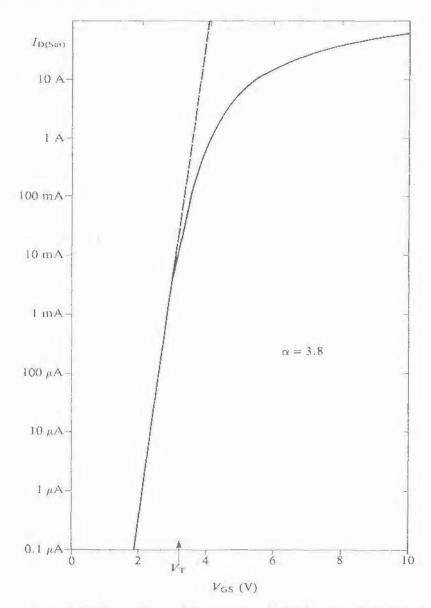

Figure 3.4 shows that  $I_{D(Sat)}$  departs from the square-law relationship with  $V_{GS} - V_T$  at low as well as at high currents. It is clear that  $I_{D(sat)}$  does not fall to zero as  $V_{GS}$  approaches the threshold voltage in the way predicted by Equation (3.11). The threshold is in fact quite "soft", and a significant current flows even when  $V_{GS}$  is less than  $V_T$ . This is called the *subthreshold* current. A log-linear plot of  $I_{D(Sat)}$  versus  $V_{GS}$  shows that in the subthreshold region the drain current varies exponentially with  $V_{GS}$ . This can be seen in Figure 3.8, which shows the results of measurements made on an IRF 540. The exponential variation is maintained over more than five decades.

In Section 2.5 we discuss how the drain current in the region of threshold is governed by the height of the potential barrier facing the electrons in the source. This is illustrated in Figure 2.13. It is therefore only to be expected that the transition from the blocking to the conducting state should occur over a range of values of  $V_{\rm GS}$ , the drain current varying exponentially with the barrier height. In Appendix 3, Figure A3.2 shows that the inversion-layer surface charge density  $Q_{\rm IL}$  does indeed vary exponentially with the surface potential, right through the threshold region.

Because of the very wide gate used in power MOSFETS, the subthreshold current is considerable. On all power-MOS data sheets the threshold voltage is specified at a saturated drain current (with  $V_{\rm GS} = V_{\rm DS}$ ) of 0.25 or 1 mA. This puts it well into the subthreshold region for most devices. Threshold voltages defined in this way

Figure 3.8. A plot of the logarithm of the saturated drain current versus the gate voltage. The data are derived from measured IRF 540 characteristics, including those of Figure 3.1. They demonstrate the exponential variation of the subthreshold current with the gate-source voltage, with  $\alpha = 3.8$ .

are thus lower than the theoretical values that we define in Chapter 2 and those that are measured from graphs such as Figure 3.4.

It is interesting to estimate the expected saturation drain current,  $I_{\rm D(Sat)}$ , at threshold. In Appendix 3, it is shown that at threshold,  $Q_{\rm IL}\approx 0.1Q_0$ , where  $Q_0=(n_{\rm A}kT\epsilon_0\epsilon_{\rm Si})^{1/2}$ . Following the discussion of the last section, let us assume that the average inversion-layer charge density along the channel at pinchoff is half this value. Pinchoff occurs at a channel voltage which is sufficient to reduce  $Q_{\rm IL}$  to zero at the drain end of the channel. This requires  $V_{\rm Ch}=Q_{\rm IL}/C_{\rm ox}=0.12$

$0.1Q_0/C_{\rm ox}$ . Thus, at threshold,

$$I_{D(Sat)} = \frac{q_c}{t_{tr}} = \frac{1}{2} \times 0.1 Q_0 \frac{w}{l} \mu_e V_{Ch} = \frac{1}{2} \mu_e \frac{w}{l} \frac{(0.1 Q_0)^2}{C_{ox}}$$

(3.15)

As an example, assume parameter values based on the IRF 540, for comparison with Figure 3.8. Let  $n_{\rm A}=1\times10^{23}\,{\rm m}^{-3}$ , so that  $Q_0=2.08\times10^{-4}\,{\rm C/m^2}$ . Let  $w=1\,{\rm m},\ l=1\,\mu{\rm m},\ {\rm and}\ C_{\rm ox}=3.45\times10^{-4}\,{\rm m}^{-2},\ {\rm and}\ {\rm take}\ \mu_{\rm c}=0.05\,{\rm m^2/V\,s}$ . Then, at "threshold",  $V_{\rm Ch}=0.06\,{\rm V}$  and  $I_{\rm D(Sat)}=30\,{\rm mA}$ . It can be seen in Figure 3.8 that the corresponding gate voltage is 3.25 V. This is a little lower (0.25 V) than the value of  $V_{\rm T}$  indicated in Figure 3.4.

With  $V_{\rm GS} < V_{\rm T}$ , we expect an exponential variation of the drain current with the barrier height, and hence, as observed, with the gate-source voltage. Thus

$$I_{\mathrm{D(Sat)}} \propto \exp\left(\frac{e \Delta V}{kT}\right) \propto \exp\left(\frac{eV_{\mathrm{GS}}}{\alpha kT}\right)$$

The coefficient  $\alpha$  relates  $V_{GS}$  to the surface potential  $\Delta V$  at the source end of the channel, where the potential minimum occurs. Its theoretical value can be obtained by applying Equation (2.7):

$$V_{\rm GB} = V_{\rm GS} = V_{\rm ox} + \Delta V - V_{\rm CP} \tag{2.5}$$

$$= \frac{(2e\epsilon_0\epsilon_{\rm Si}n_{\rm A}\Delta V)^{1/2} - Q_{\rm SS}}{C_{\rm ox}} + \Delta V - V_{\rm CP}$$

(3.16)

where we have substituted for  $V_{ox}$  using Equations (A2.6) and (A2.7). Thus,

$$\alpha = \frac{\mathrm{d}V_{\mathrm{GS}}}{\mathrm{d}(\Delta V)} = \frac{\left(e\epsilon_0\epsilon_{\mathrm{Si}}n_{\mathrm{A}}/2\Delta V\right)^{1/2}}{C_{\mathrm{ox}}} + 1$$

$$= \frac{C_{\mathrm{D}}}{C_{\mathrm{ox}}} + 1 \tag{3.17}$$

Here,  $C_D$  may be thought of as the depletion-layer capacitance,

$$C_{\rm D} = \frac{\mathrm{d}Q_{\rm D}}{\mathrm{d}(\Delta V)} = \left(\frac{e\epsilon_0 \epsilon_{\rm Si} n_{\rm A}}{2\,\Delta \mathrm{V}}\right)^{1/2} \tag{3.18}$$

With  $n_A = 1 \times 10^{23} \,\mathrm{m}^{-3}$ , we have  $\Delta V \approx \Delta V_{\mathrm{Th}} \approx 0.81 \,\mathrm{V}$  and  $C_D = 10.2 \times 10^{-4} \,\mathrm{F/m^2}$ . With  $t_{\mathrm{ox}} = 100 \,\mathrm{nm}$ ,  $C_{\mathrm{ox}} = 3.45 \times 10^{-4} \,\mathrm{F/m^2}$ . Together these give  $\alpha = 4.0$ .

The simplest way of measuring  $\alpha$  is to take the change in  $V_{\rm OS}$  required to cause a factor-of-ten change in  $I_{\rm D(Sat)}$ . Call this  $(\Delta V_{\rm OS})_{\rm Dec}$ . Then, at room temperature,

$$\alpha = \frac{(\Delta V_{GS})_{Dec}}{(kT/e) \ln 10} = 16.9(\Delta V_{GS})_{Dec}$$

(3.19)

The graph of Figure 3.8 shows that  $(\Delta V_{\rm GS})_{\rm Dec} = 0.225 \, \rm V$ , so the measured value of  $\alpha$  is 3.8. This implies an effective doping concentration at the source end of the channel of  $0.9 \times 10^{23} \, \rm m^{-3}$ . However, in some instances the presence of interface trapping levels may cause  $Q_{\rm SS}$  to be a function of  $\Delta V$ . This would modify the value of  $\alpha$  slightly, but the measured value justifies our estimate of  $n_{\rm A}$  very precisely.

The departure from the exponential variation of  $I_D$  with  $V_{GS}$ , shown in Figure 3.8, starts at  $10 \,\mathrm{mA}$ , when  $V_{GS} = 3.05 \,\mathrm{V}$ . This is the point at which the inversion-layer charge density becomes big enough to influence the potential at the semiconductor surface significantly.

### 3.4. DEVICE TRANSCONDUCTANCE

A device parameter of great importance is the transconductance  $g_{fs}$  which is defined as:

$$g_{\rm fs} = \left(\frac{\partial I_{\rm D}}{\partial V_{\rm GS}}\right)_{V_{\rm DS} = {\rm constant}} \tag{3.20}$$

This measures the sensitivity of the drain current to changes in the gate-source voltage. It determines the current-carrying capacity of the device.

According to the theory of Section 3.2 we should expect  $g_{fs}$  to take on values as follows:

1. Below pinchoff, when  $V_{\rm Ch} < V_{\rm GS} - V_{\rm T}$ , differentiation of Equation (3.6) yields

$$g_{\rm fs} = \mu_{\rm e} \frac{w}{l} C_{\rm ox} V_{\rm Ch} = k V_{\rm Ch}$$

(3.21)

2. Above pinchoff but hefore velocity saturation, that is, for  $E_s l > V_{\rm Ch} \approx V_{\rm GS} - V_{\rm T}$ , Equation (3.11) leads to

$$g_{\rm fs} = \mu_{\rm e} \frac{w}{l} C_{\rm ox} (V_{\rm GS} - V_{\rm T}) = k (V_{\rm GS} - V_{\rm T})$$

(3.22)

3. After velocity saturation,  $V_{\rm Ch} > E_{\rm s} l$ , Equation (3.14) applies and

$$g_{\rm fs} = \frac{1}{2} w C_{\rm ox} v_{\rm s} \tag{3.23}$$

For practical purposes the specification of  $g_{\rm fs}$  for a given device, as on the device data sheet, requires that certain prescribed values of  $V_{\rm GS}$  and  $V_{\rm DS}$  must be chosen. Usually,  $V_{\rm DS}$  is large enough to ensure that the drain current is in the constant-current region,  $I_{\rm D(Sat)}$ . The choice of  $V_{\rm GS}$  usually eusures that this value of  $I_{\rm D(Sat)}$  is about half the maximum current rating of the device. Data sheets also display graphs of  $g_{\rm fs}$  versus  $I_{\rm D}$ . A typical plot is shown in Figure 6 of the data

sheet presented in Appendix 7. These curves demonstrate the increase of  $g_{\rm fs}$  with  $I_{\rm D}$  at low values, and its independence of  $I_{\rm D}$  once velocity saturation is established.

For a given value of  $V_{\rm GS}$ , the three factors that influence  $g_{\rm fs}$  are the gate width w, the channel length l, and the gate oxide thickness  $t_{\rm ox}$ . In saying this we are presuming that by choosing silicon as the semiconductor and silicon dioxide as the gate insulator, the values of  $\mu_{\rm c}$  (or  $v_{\rm s}$ ) and  $\epsilon_{\rm ox}$  are prescribed.

Decreasing  $t_{\rm ox}$  increases  $g_{\rm fs}$  through its effect on  $C_{\rm ox}$ . The limit is set by the need to preserve the uniformity and integrity of the gate oxide, and for it to support the rated voltage  $V_{\rm GS}$ , which is usually  $\pm 20$  V. The design of the transistor has to ensure that no greater voltage appears across the gate oxide in any permitted operating condition. With  $t_{\rm ox} = 100$  nm (1000 Å), the breakdown voltage of good-quality gate oxide averages about 55 V. Technological improvements have reduced the spread around this value, thereby increasing the margin for reliability.

Decreasing l also increases  $g_{\rm fs}$ . The minimum value of l is set by the level of technology, in this case the ability to control the double-diffusion process that determines l. What matters is not what can be achieved in ideal circumstances, but the manufacturability of the device with a reasonable yield within the parameter tolerances specified. This becomes increasingly difficult with  $l < 2 \, \mu \rm m$ .

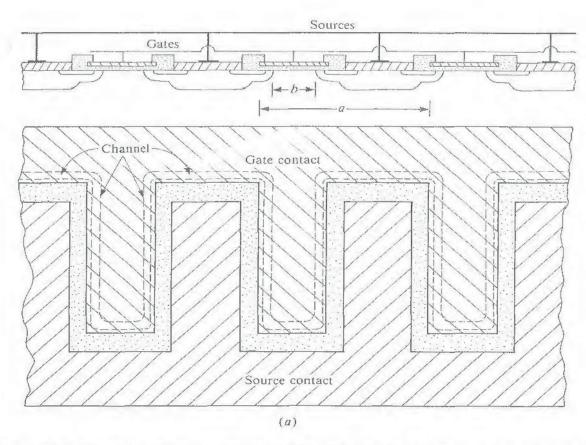

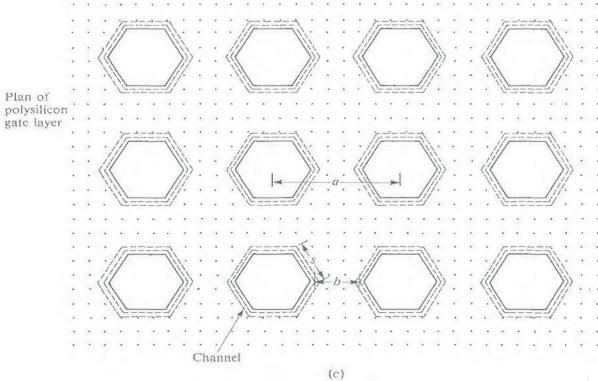

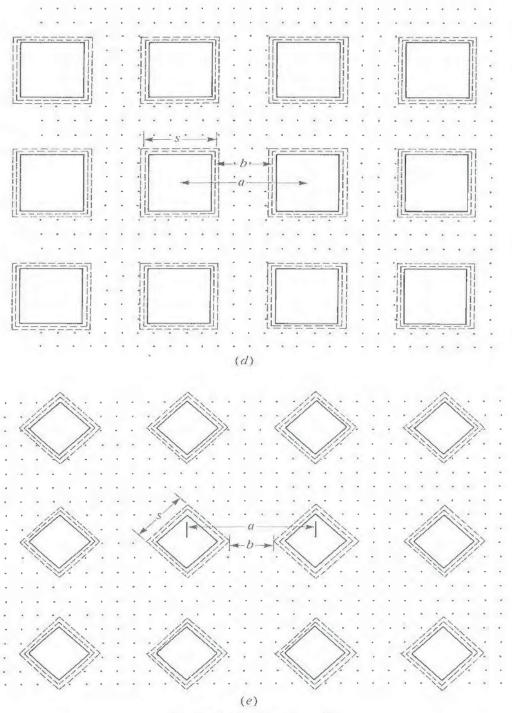

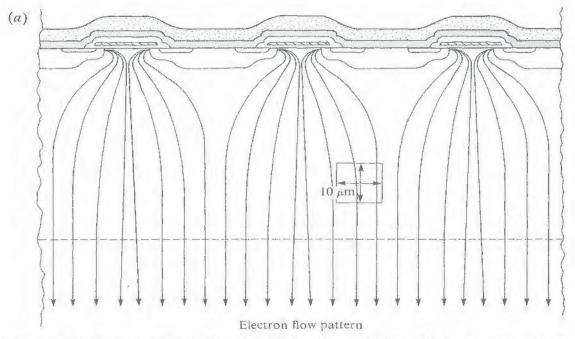

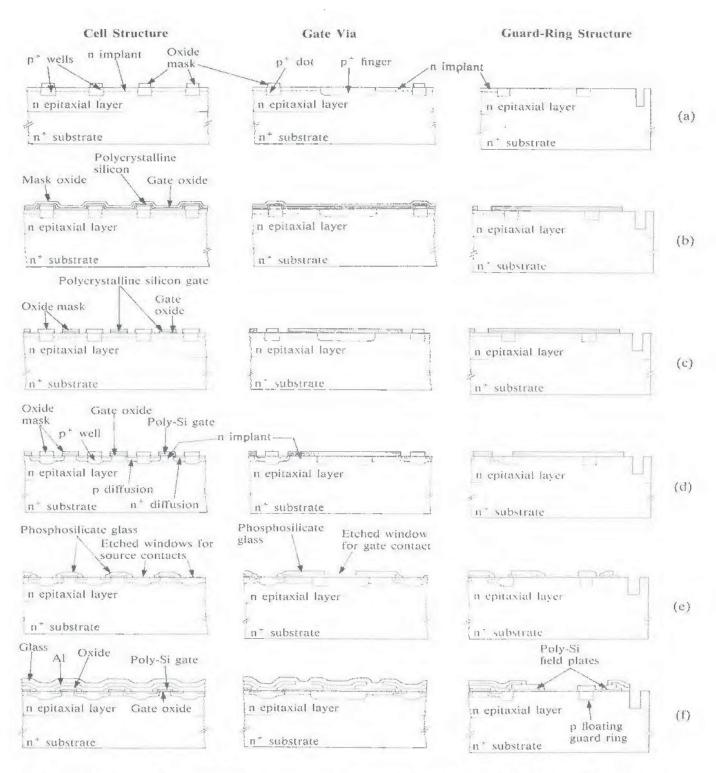

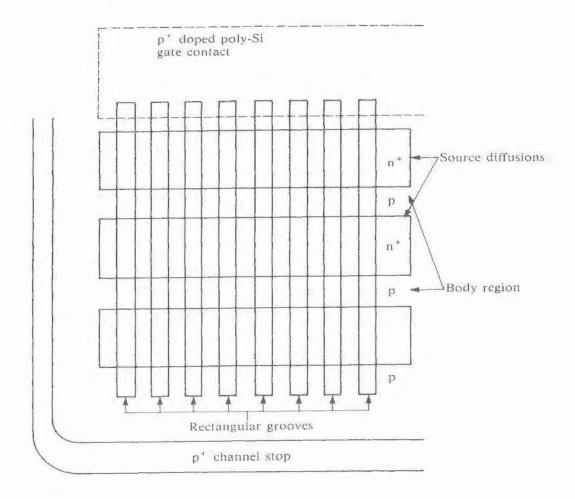

There is greater scope for increasing  $g_{\rm fs}$  by increasing the gate width w, because w varies in direct proportion with the active device area. The parameter determined by technology is the gate width per unit area, w/A. There is an advantage in using a cellular rather than a linear pattern, and several different cellular designs have been proposed and used. Some are illustrated in Figure 3.9. The quantitative theoretical advantages of one pattern over those of another are marginal. They are discussed in Appendix 5. They have been the subject of a number of theoretical studies (e.g. [5]) involving a consideration of the on-state resistance  $R_{\rm DS(on)}$ , as well as the transconductance  $g_{\rm fs}$ . It has recently been shown [6] that a circular cell geometry offers the best compromise, provided that the full bulk breakdown voltage is realized. The hexagonal structure shown in Figure 3.9b approximates this optimum design most closely. Again, though, what really matters is the manufacturability and robustness of the device made by a particular process.

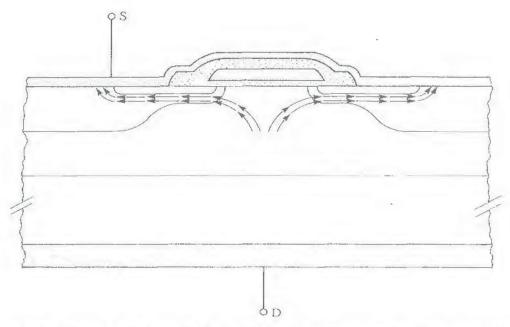

What is clear from theory is that w/A increases as the cell lattice spacing decreases. The limit to this is set in two ways: again by the level of technology, but also by the need to maintain a minimum spacing b between the channel diffusions. This region,  $\bigcirc$  in Figure 2.1, acts as a throat which constricts the drain current. The limit on b results from the need to minimize the contribution of this region to  $R_{DS(on)}$ , bearing in mind that the current density is higher here than in the rest of the drain region. This is discussed in the next section. The problem is exacerbated by the presence here of a parasitic JFET, a matter that is taken up in Section 3.6.

In higher-voltage devices the epitaxial layer is more lightly doped and so has a higher resistivity. This not only increases the resistance of the epilayer, but also causes the channel depletion layers to expand further into the drain drift region, thereby enhancing the JFET action. This can be offset to some extent by increasing

the drain doping concentration towards the surface, but the minimum acceptable value of b remains higher in high-voltage devices.

The technological limit is determined by the line width and registration tolerances of the photolithographic processing steps. A key factor is the need to obtain a low-resistance metal contact to the source. The contact area must be sufficient to ensure this after making provision for registration tolerances in the masking processes, which may cause the metal contact to be offset from the center of the cell. The chip area can most readily be filled by a regularly repeated lattice of square or hexagonal cells. Such patterns dominate in commercial devices.

Another limiting factor is the need to radius the channel at each cell apex in order to maintain its length l constant. The more acute the angle of the apex, the more difficult this is, which confers another benefit on the hexagonal cell.

The first range of devices to become widely established commercially in the early 1980s used a cell lattice spacing of  $38 \,\mu\text{m}$ , giving over 500,000 cells per square inch (approximately 800 per mm<sup>2</sup>). The resulting value of w/A is about

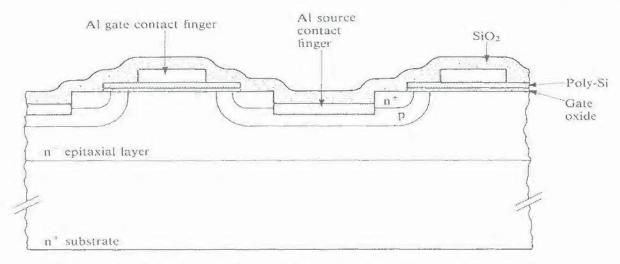

Figure 3.9. Examples of gate patterns: (a) Interdigitated. (b) Hexagons on hexagonal lattice. The plan view of the poly-Si layer shows the channel positions and the source contact areas. A section through the active region is also given. (c) Hexagons on a square lattice. (d) Squares on a square lattice. (e) Squares on an offset square lattice. (f) Squares on a hexagonal lattice. (g) Triangles on a hexagonal lattice.

Figure 3.9. (Continued)

Figure 3.9. (Continued)

$0.07 \,\mathrm{m/mm^2}$ . This remains a perfectly satisfactory standard for higher-voltage devices. However, low-voltage mosfets have benefited from progressive reductions in the cell lattice spacing to  $20 \,\mu\mathrm{m}$  and below, with cell densities increasing first to 1,600,000 and more recently to 3,500,000 per square inch (approximately 2500 and 5400 per  $\mathrm{mm^2}$ , respectively). Corresponding values of w/A are in the

Figure 3.9. (Continued)

region of 0.12 and 0.17 m/mm<sup>2</sup>, respectively. As a result, these devices can support a given current rating on a chip of smaller area. Since the silicon area required is a major element in the cost of a component, obtaining the maximum performance from a given size of chip is extremely important.

Even so, the proportion of the chip available as active device area  $A_{\rm A}$  may be less than 50% of the total area  $A_{\rm Ch}$ . For reasons of reliability the source and gate bonding pads are not often laid over active material. The gate vias that distribute the gate current over the area of polysilicon and the field rings used around the edge of the chip to prevent peripheral voltage breakdow, all diminish the area

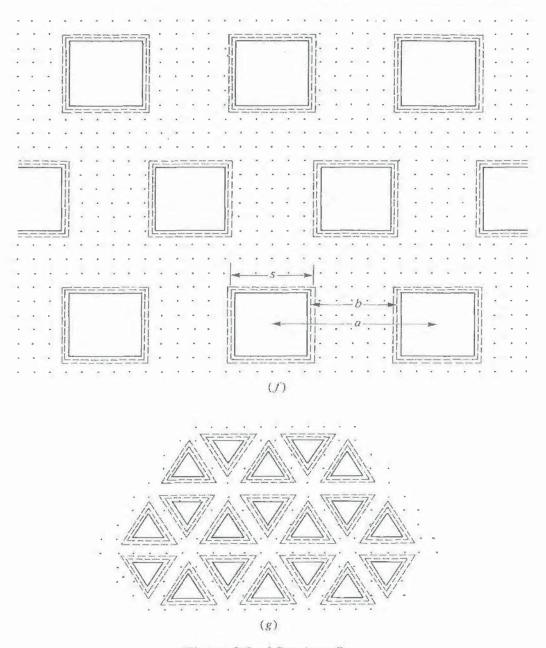

Figure 3.10. Photographs of HEXFET<sup>TM</sup> chips. (a) Earlier design, HEXFET<sup>TM</sup> I; (b) more recent design, HEXFET<sup>TM</sup> III. These plan views show the hexagonal cell pattern, the peripheral field rings, the gate vias, and the bonding pads. In the earlier design, the active area occupies 60% of the total chip area. In the later design, the size of the field rings and the gate bonding pad have been reduced, giving better chip utilization. (Courtesy International Rectifier Corp.)

that can be used for transistor action. The plan views of HEXFET<sup>TM</sup> chips shown in Figure 3.10 illustrate the type of layout used. Approximately 60% of the chip area is active in the earlier design shown in Figure 3.10a. This is increased in the more recent design shown in Figure 3.10b.

### 3.5. THE DRAIN DRIFT REGION

The drain drift region is particularly critical to the design of a power mosfet. Its principal function is to block and support the full forward voltage held off by the transistor in its turned-off state. However, it has also to carry the full forward current in the on state. It is thus most important that its contribution  $R_{\rm EPI}$  to the total on-state resistance  $R_{\rm DS(on)}$  be kept as small as possible. This minimizes dissipation and maximizes the current rating of the device. Thus, the epilayer should be no thicker than it has to be in order to support the maximum blocking

voltage. Values range from about 5  $\mu$ m for a 50-V device to about 50  $\mu$ m for a 1000-V device.

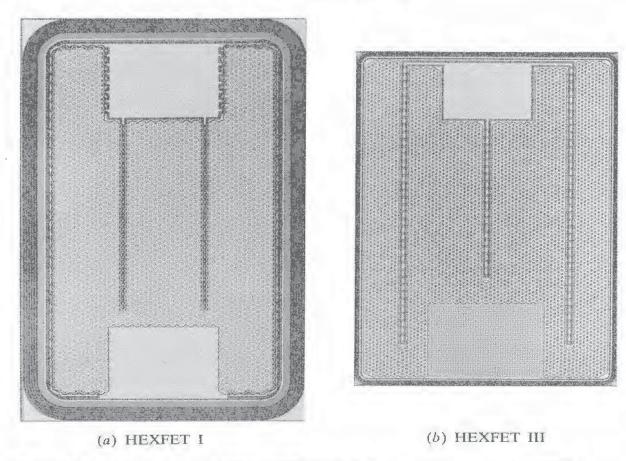

For purposes of discussion we have subdivided the drain drift region into three parts. In Figure 2.1 these are identified as the surface layer B; the part bordered by the source and channel diffusions, C; and the main part below the diffused regions, D. In the on state the current should be evenly distributed all across the epilayer. Clearly, this is not possible in the region between the diffusions, where the electron current emerges from the channel regions. The area between the diffusions is a little less than the gate area. Let it be a fraction g of the total active chip area. The even distribution of current here is assisted by the presence of the accumulation layer in the epilayer immediately under the gate oxide, in the turned-on state, and indeed as long as  $V_{\rm DS} < V_{\rm GS}$ . Under the gate oxide, then, the current density is higher by the factor 1/g. It is further increased by the presence of the depletion layers at the pn junctions. These expand as the local potential increases at high current levels, and give rise to an effect characteristic of a series junction field effect transistor. This has already been mentioned and is discussed again in Section 3.6.

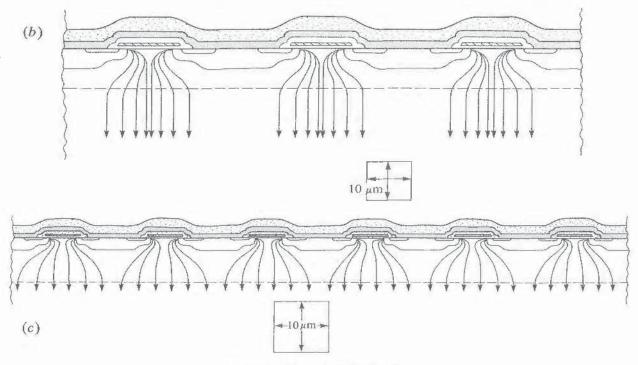

In high-voltage devices the epilayer is sufficiently thick for the current to be able to spread out to cover the whole of the active chip area fairly evenly by the time it enters the substrate. This is shown in Figure 3.11a. With low-voltage devices the chip area can be fully utilized only by further reducing the lateral cell dimensions, as illustrated by Figures 3.11b and c. This gives an additional incentive for a reduction in the cell pitch a, over and above the increase in w/A that results, as discussed in the last section.

When  $R_{\rm EPI}$  is low, as in low-voltage devices, the effect of the other parasitic

Figure 3.11. Current distribution. (a) High-voltage device; (b) low-voltage device with same cell pitch; (c) low-voltage device with reduced cell pitch.

Figure 3.11. (Continued)

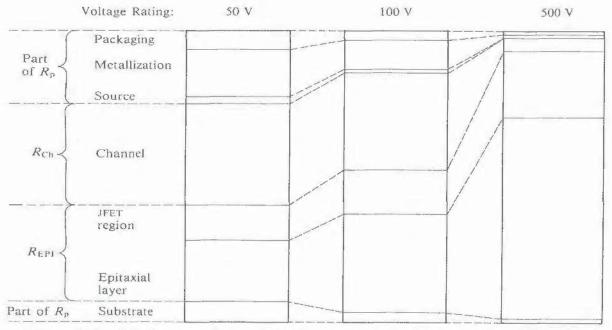

sources of resistance,  $R_{\rm P}$ , is proportionately greater. A schematic illustration of the relative magnitudes of the different factors contributing to  $R_{\rm DS(on)}$  is given in Figure 3.12.

A theory specifying the optimum doping profile and thickness of the epilayer is presented in Appendix 6. It is based on a highly idealized plane-parallel geometry, but it does illustrate the principle of the problem, and it does set into

Figure 3.12. Relative contributions to  $R_{DS(on)}$  in devices of different voltage rating.

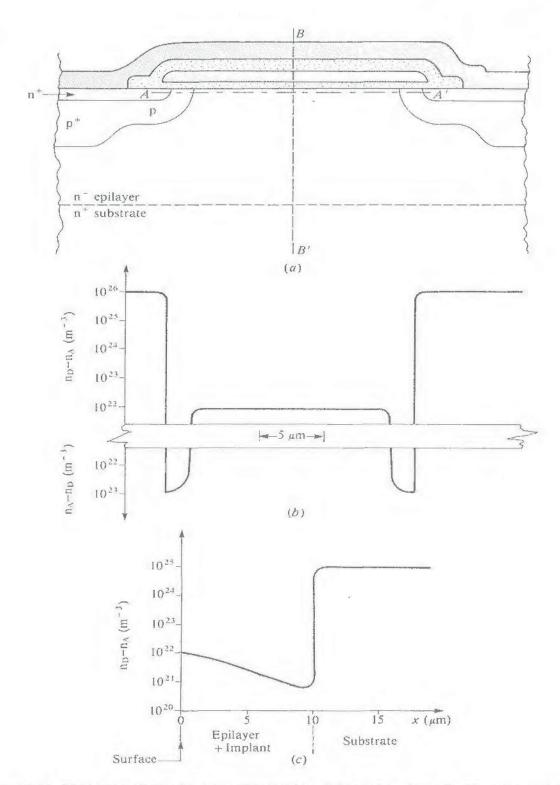

Figure 3.13. Variation of the doping concentration. (a) Section through the active region; (b) variation parallel to the surface along AA'; (c) variation perpendicular to the surface along BB'.

context the much-quoted relationship between the ON resistance and the junction breakdown voltage:

$$R_{\rm DS(on)} \propto V_{\rm B}^{2.6} \tag{3.24}$$

It is the breakdown voltage  $V_{\rm B}$  that partly determines the voltage rating of the device. The resistance calculated in the theory (R in Appendix 6) is the optimum value of the component  $R_{\rm EPI}$  of the on-state resistance when there is a uniform distribution of current. The lateral nonuniformities of the real device mean that the proposed doping profile of Equation (A6.26) is not appropriate in practice.

Ideally [7], the doping level would follow Equation (A6.26) initially, decreasing from the  $n^+n^-$  junction into the epilayer. It would then go through a minimum and increase progressively towards the surface of the chip between the p diffusions. An increase in the epilayer doping concentration in regions B and C is desirable for two reasons. It helps to minimize the extra contribution to  $R_{\text{EPI}}$  caused by the higher current density, and more importantly, it reduces the effect of the parasitic JFET. It is found that the breakdown voltage of a well-designed device is not adversely affected. Most benefit is obtained when the doping concentration has lateral uniformity [8], as in the profile shown in Figure 3.13.

Field enhancement would normally occur at the edges and corners of the channel diffusion in the forward-blocking state. But this is reduced if the depletion layers, expanding from the junctions on either side of the throats in the drain drift region beneath the gate oxide, eventually overlap. The breakdown voltage then approaches that of the plane junction between the epilayer and the p<sup>+</sup> diffusion in the centre of the body region under the source contact. In modern devices this junction is designed to withstand avalanche breakdown in a controlled way. These matters are discussed further in the next section.

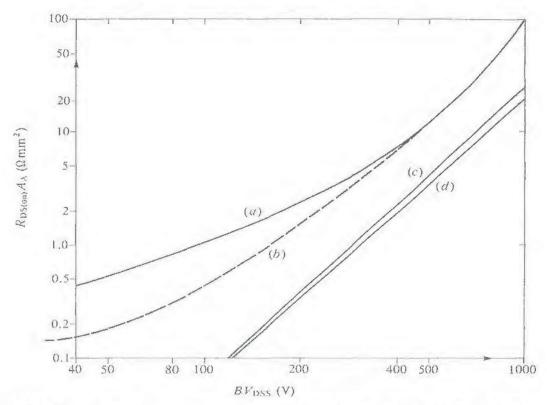

In Figure 3.14, rated values of  $R_{\rm DS(on)}$ , normalized against device active area, are plotted against  $V_{\rm B}$  ( $BV_{\rm DSS}$ ) for some commercially available power MOSFETS. Equations (A6.17) and (A6.28) are also shown. It can be seen that there are significant departures from the theory, especially at low values of  $V_{\rm B}$ . From the earlier discussion this is not surprising, but the reduction of the cell pitch in the more modern designs of low-voltage devices has resulted in their coming nearer to the ideal curves. However, even at the higher values of  $V_{\rm B}$ , the value of  $R_{\rm DS(on)}A_{\rm A}$  is still several times higher than the predicted optimum value RA. One reason is the difficulty of achieving a high fraction of the theoretical value of  $V_{\rm B}$  at the periphery of the chip. Techniques for achieving this are discussed in Chapter 5.

The need to minimize  $R_{\rm DS(on)}$  further emphasizes the importance of minimizing the silicon "real-estate overheads" discussed at the end of the previous section. This inevitably leads to compromises in design. Thus, extending the system of field rings at the periphery may help to ensure higher reliability at high voltage, but this is bought only at the expense of a reduced current-handling capacity and an increase in  $R_{\rm DS(on)}$ . If, in a particular application, this causes the device to run at a higher temperature, its reliability will be degraded.

Some manufacturers have not allowed the bonding pads to overlie active parts of the device. However, an increasing number now have sufficient confidence in

Figure 3.14. Normalized on resistance versus breakdown voltage. Values of  $R_{\rm DS(on)}$  for commercially available devices are compared with the theoretical curves of Appendix 6. Curve (a) shows values typical of standard devices; curve (b) shows values typical of modern low-voltage devices having a high cell density. Curves (c) and (d) represent Equations (A6.17) and (A6.28).

their ability to maintain the integrity of the structure under the bonding pads that they are prepared to extend them over active regions. A final way in which most manufacturers accept an increase in  $R_{\rm DS(on)}$  in exchange for extra reliability in the breakdown performance arises from the fact that in general the depletion layer is not permitted to reach through to the substrate. The epilayer is made thick enough to ensure that the field at the  $n^-n^+$  junction is low. Then, for any given voltage, the peak field occurring at the p-n junction is lower than it would be, were reach-through permitted.

### 3.6. PARASITIC COMPONENTS

#### 3.6.1. Introduction

It will be clear from what has been said already that there are a number of parasitic components inherently associated with the VDMOS FET structure. In addition to the normal resistance of the bulk material and the contacts, the inductance of the leads, and the capacitance of junctions and connections, these parasitic elements include active transistors. Their effects are most pronounced under the transient conditions discussed in Chapter 4. They may severely limit high-frequency operation.

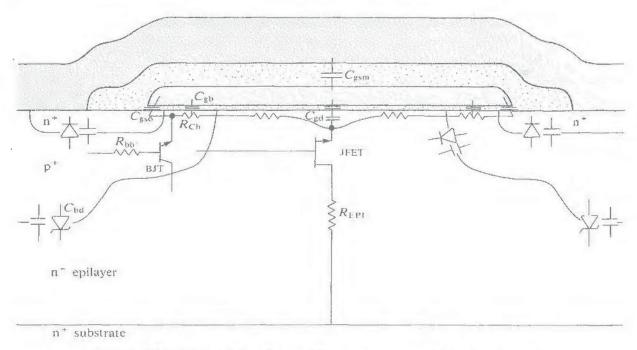

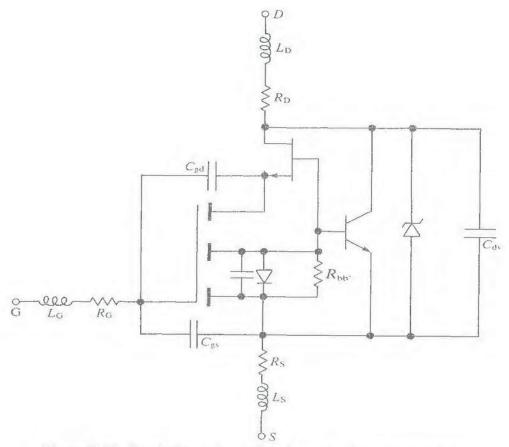

Figure 3.15. The origin of parasitic components within the device.

Figure 3.16. Equivalent circuit showing parasitic components.

In Figure 3.15 the various internal parasitic components of a VDMOS FET are shown, drawn onto the usual section through the active region. An equivalent circuit incorporating these and other parasitic elements is shown in Figure 3.16. Passive components include the following:

- 1. The various resistive elements contributing to  $R_{DS(on)}$ .

- 2. The inductance of each of the pin connections.

- 3. The capacitances between the gate and the source metallization, and between the gate and the source diffusion.

- 4. The capacitances between the gate and the body region, and between the gate and the epilayer.

- 5. The capacitances associated with the various pn junctions.

- 6. The pn junctions show, in addition, their normal diode behavior.

The main active components are:

- 7. The n-channel junction field-effect transistor (JFET) that forms in the epilayer, in between the channel diffusions.

- 8. The npn bipolar junction transistor (BJT) formed between the source, the body, and the drain. Under static conditions the base and emitter of the BJT are shorted, leaving only the body-drain diode effective. However, under transient conditions and in avalanche breakdown, the transistor may be activated, and this can seriously degrade the overall performance of the MOSFET.

We consider each of these groups of parasitic components in turn.

# 3.6.2. Resistance, Inductance and the Parasitic JFET

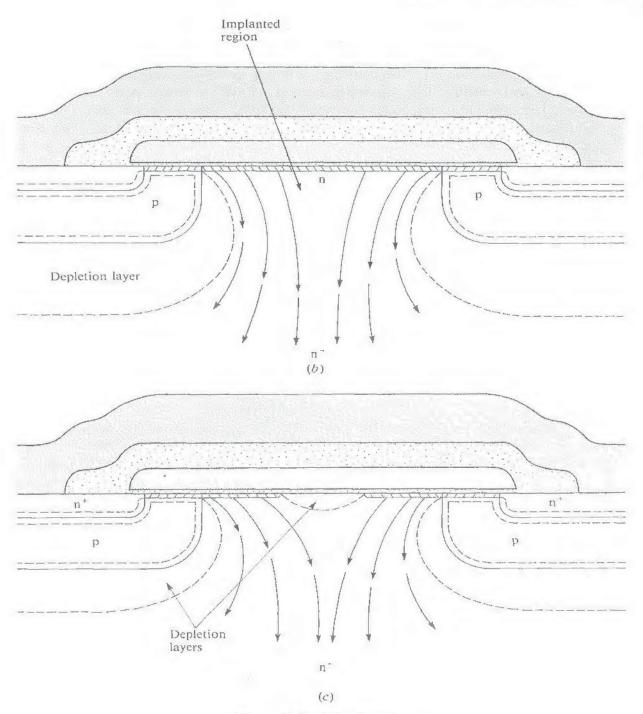

The causes of parasitic resistance in the path of the drain current have been discussed at length already in this chapter. We will not pursue them further, except in so far as they are influenced by the parasitic JFET, which we deal with next. The potential of this component to affect, adversely, many of the MOSFET static characteristics influences a number of design decisions, and has caused us to mention it several times already. The JFET action occurs in the region between the p diffusions. The p-doped body regions act as the gate, and the throat in the n-type drain drift region as the channel. The effect is more severe in high-voltage devices, because the epilayer is more lightly doped and the depletion layers that form at the body-drain junction extend further into the drain.

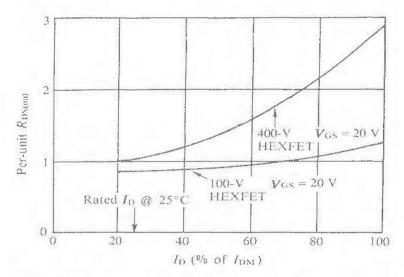

In Figure 3.12 the additional resistance caused by the JFET can be seen to account for 25% of the total  $R_{\rm DS(on)}$  of a high voltage device. At high on-state currents, the increased voltage in the drain drift region causes an expansion of the depletion layers and a further increase in  $R_{\rm DS(on)}$ . This is shown in Figure 3.17. In a poorly designed device, it is possible for pinchoff to occur in the JFET rather than in the MOSFET, under some conditions.

The acceptable spacing b between the channel diffusions is mainly determined by the extent, in the on state, of these depletion layers. As a result, the maximum

Figure 3.17. Increase in  $R_{\rm DS(on)}$  at high drain currents. The current is normalized to  $I_{\rm DM}$ , the maximum rated pulse current, which is higher for the lower-voltage device (e.g. 108 A compared to 40 A). The increase in  $R_{\rm DS(on)}$  at higher currents is mainly the result of JFET action in the throat region as  $V_{\rm DS}$  increases. It can be seen that the increase is much greater in the case of the higher-voltage device, because the epilayer is more lightly doped and the depletion regions expand further into it.

Figure 3.18. Effect of drain implant in reducing IFET action. (a) Depletion layers pinch off the channel through the drain neck region in a uniformly doped epilayer. The MOSFET is fully ON. (b) Depletion-layer thickness is reduced when the doping level under the gate oxide is increased. (c) Under some conditions the potential at the semiconductor surface in the middle of the throat region may exceed  $V_{\rm GS}$ . Then a depletion layer forms there too, further constricting the current path.

Figure 3.18. (Continued)

usable cell density is strictly limited, as discussed in Appendix 5. Increasing the donor doping concentration in the drain throats, as shown in Figure 3.13, has two beneficial effects. The conductivity is improved, and the widths of the depletion layers are reduced, so increasing the cross-sectional area available for conduction. This is illustrated in Figure 3.18. The consequence is that the cell size can be reduced and the resulting benefits of increased  $g_{\rm fs}$  and lower  $R_{\rm DS(on)}$  can be

realized. Of course, the level of the donor concentration in the drain immediately under the gate oxide has to be finely judged. If it is too high, the avalanche breakdown voltage is reduced and channel-length modulation may occur.

Of the lead inductances, that of the gate is not usually significant, but those of the drain, and particularly the source, may have a considerable effect on switching behavior and high-frequency performance. This is discussed in Chapter 4. Values can be minimized by careful encapsulation and design. They lie, typically, in the range 5 to 15 nH.

### 3.6.3. Capacitance

The physical capacitances shown in Figure 3.15 each contribute to the equivalent-circuit capacitances shown in Figure 3.16. We need to relate them to the terminal capacitances,  $C_{\rm iss}$ ,  $C_{\rm oss}$ , and  $C_{\rm rss}$ , that are specified on device data sheets. These are normally measured at 1 MHz, using the circuits shown in Figures A9.4, A9.5, and A9.6 of Appendix 9. Each is a function of the dc drain-source voltage, as shown in Figure 10 of the data sheet of Appendix 7. Values are usually specified for  $V_{\rm DS} = 25$  V and  $V_{\rm GS} = 0$  V. The three capacitances are related as follows:

1. The input capacitance,  $C_{iss}$ , is the parallel sum of  $C_{gd}$  and  $C_{gs}$ . Thus,

$$C_{\rm iss} = C_{\rm gd} + C_{\rm gs} \tag{3.25}$$

2. The output capacitance,  $C_{oss}$ , represents the total capacitance between drain and source with the gate and source shorted together, that is,

$$C_{\rm oss} = C_{\rm ds} + C_{\rm gd} \tag{3.26}$$

On many early data sheets, an incorrect relationship is given, implying that  $C_{\rm oss}$  is the sum of  $C_{\rm ds}$  and the series combination of  $C_{\rm gs}$  and  $C_{\rm gd}$ . The published curves, however, were always obtained using the circuit of Figure A9.5, and are thus correct.

3. The reverse transfer or Miller capacitance,  $C_{rss}$ , is simply the gate-drain capacitance with  $V_{GS} = 0$ . That is,

$$C_{\rm rss} = C_{\rm gd} \tag{3.27}$$

From the discussion in Section 2.4, we can see that  $C_{\rm gd}$  is made up of the series combination of the gate oxide capacitance and the capacitance of the drain depletion layer beneath the gate oxide. This latter component exists only when the potential of the drain surface region B is more positive than that of the gate. When the gate is more positive, an accumulation layer forms at the semiconductor surface and  $C_{\rm gd} \approx C_{\rm ox} A_{\rm G}$ , where  $C_{\rm ox} = \epsilon_0 \epsilon_{\rm ox}/t_{\rm ox}$ , as before, and  $A_{\rm G}$  is the area of the gate. As the drain potential rises above that of the gate, the value of  $C_{\rm gd}$  falls quite sharply. It continues to fall progressively as the depletion layer extends deeper into the epilayer. This is shown in Figure 2.11. Depletion-layer capacitance is discussed in Appendix 1. Its variation with the dc bias voltage is shown to

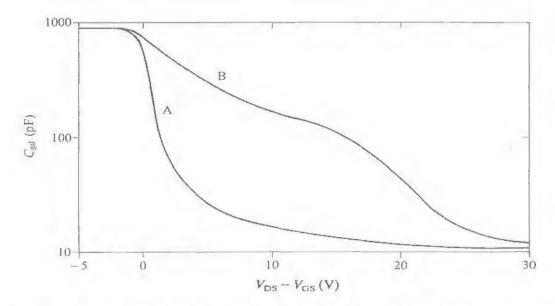

Figure 3.19. Effect of drain implant on the variation of  $C_{\rm gd}$  with  $V_{\rm DS}$ . Curve A represents a device with a uniformly doped epitaxial layer. Curve B is from one in which the conductivity under the gate oxide has been increased by an implant of  $10^{16}$  phosphorus atoms per m<sup>2</sup> ( $10^{12}$  cm<sup>-2</sup>).

be a function of the doping profile. The detailed variation of  $C_{\rm gd}$  with  $V_{\rm DS}$ , given that  $V_{\rm GS}=0$ , is therefore a function of the impurity concentration profile in the epilayer. This can be seen in Figure 3.19. Really we are applying the well-known capacitance-voltage (C-V) profiling technique to the whole device.

Physically, the gate-source capacitance  $C_{\rm gs}$  comprises the overlap capacitance, the gate-channel capacitance, and the capacitance through the field oxide of the source overlay. It is largely independent of bias.

The principal component of  $C_{\rm ds}$  is the capacitance of the junction between the p diffusion and the epilayer. This varies inversely with the square root of the drain-source voltage, as indicated by Equation (A1.18). Thus, at low drain voltages, particularly when  $V_{\rm GS} > V_{\rm DS}$ ,  $C_{\rm oss} = C_{\rm ds} + C_{\rm gd}$  becomes quite large.

Because of their considerable variation with the biasing conditions, knowledge of  $C_{\rm iss}$ ,  $C_{\rm oss}$ , and  $C_{\rm rss}$  at any one state of bias is of limited value to the circuit designer. Graphs of the three capacitances versus  $V_{\rm DS}$  are normally provided, but, unless these are extended to negative values of  $V_{\rm GD}$ , they do not show the full extent of the capacitance variation. To overcome this difficulty, it has become normal practice to specify the total amount of charge needed to change the gate voltage from 0 to 10 V while the device switches a prescribed current. The current chosen is normally somewhat greater than the maximum dc rating. The details and implications of this are discussed further in Chapter 4.

# 3.6.4. The Body-Drain Diode and the Bipolar Junction Transistor

Finally, we come to the bipolar junction transistor structure that is formed by the n<sup>+</sup> source, the p body, and the n<sup>-</sup> epilayer. Under normal, static conditions the

emitter and the base of the BJT (the source and the body region) are shorted, leaving only the effect of the body-drain diode.

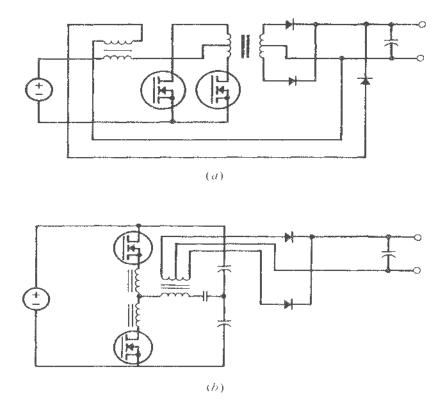

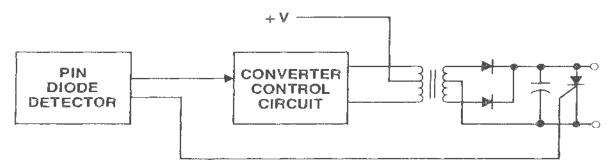

When the MOSFET is reverse biased, the body-drain diode is set into forward conduction. Its current rating is comparable to that of the MOSFET itself. So that this should not lead to excessive dissipation, or to problems in external circuits, its forward voltage  $(V_{\rm SD(on)})$  needs to be kept low. Typical values at the full rated current are from 2 to 2.5 V. This reverse-conduction property is valuable in a power switching device. It is particularly necessary in circuits such as dc-to-ac inverters and dc-to-dc choppers, when they are used in applications such as motor speed control, as discussed in Chapter 12.

As well as a low on-state voltage, the body-drain diode must exhibit a rapid, but not too abrupt, recovery waveform, and low reverse recovered charge  $Q_{\rm RR}$ . Occasionally, heavy-metal doping (gold or platinum) or electron bombardment have been used to speed up the recovery of the body-drain diode. These are normal techniques used with other types of device. They introduce recombination centers by creating trapping levels in the middle of the band gap, and so kill the carrier lifetime. Unfortunately, this increases both  $V_{\rm SD(on)}$  and  $R_{\rm DS(on)}$  at room temperature. At elevated temperatures, the trapping levels are no longer effective, and both the lifetime and the ON resistance revert to their normal values. This means that the temperature coefficient of  $R_{\rm DS(on)}$  is lower than that of a normal device. The effect on  $Q_{\rm RR}$  is discussed in Chapter 13; see Figure 13.22, in particular.

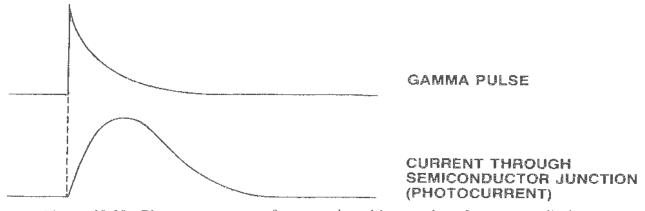

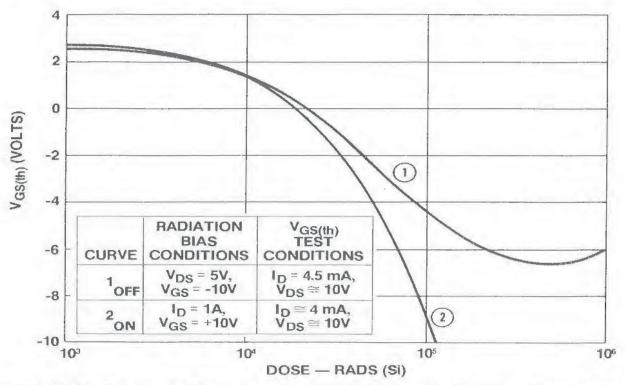

It has been shown [9] that a careful adjustment of the energy and dose of electron irradiation can give valuable reductions in the recovery time and the recovered charge (and so reduce the transient dissipation), without degrading the other parameters significantly. In Ref. 9, 8 Mrad at 3 MeV was reported to be effective. Another adverse effect is a reduction caused to the threshold voltage by the creation of positive charge in the gate oxide. To reduce this charge, it is necessary to anneal the device after irradiation for several hours at about 140°C. This normally restores the threshold voltage to a reasonable value, but leakage currents remain appreciably higher than before irradiation.

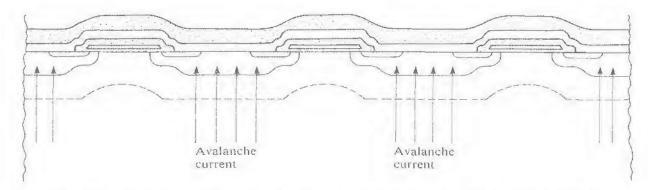

The reverse avalanche-breakdown characteristics of the body-drain diode determine the forward voltage rating of the MOSFET,  $BV_{DSS}$ . In modern devices, the diode junction is designed to withstand the passage of substantial current under conditions of controlled avalanche breakdown. This enables forward transients to be quenched, and inductive energy to be dissipated, without the use of additional, external clamping and snubber components. To achieve this it is necessary for the breakdown to be very evenly distributed over the  $p^+$  region of the junction and, in particular, to be evenly distributed from cell to cell. This is illustrated in Figure 3.20.

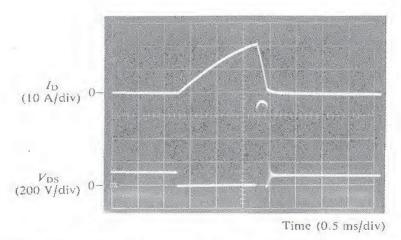

Many devices now have single-shot and repetitive pulsed ratings for the energy (charge  $\times BV_{DSS}$ ) that they can safely dissipate in this way. An example of a device being driven into controlled breakdown by an inductive load is shown in Figure 3.21. The device under test is an IRF 460, rated at 500 V, 24 A. Once the MOSFET is turned on, the current rises approximately linearly with time at a rate determined by the voltage across the inductance (17 A/ms, that is, 100 V across 6 mH). When the transistor is turned off, the voltage across it rises to the breakdown voltage  $V_{\rm B}$ , which is 550 V. This causes the current in the inductance

Figure 3.20. Avalanche breakdown of the body-drain diode. The diagram shows the uniform breakdown of the p<sup>+</sup>n junction required in a good device. The shielding effect of adjacent cells mitigates the field concentration at the edges and corners of the p diffusion.

to fall at the rate (550 V)/(6 mH) = 90 A/ms. Thus the energy stored in the inductance at the moment of turnoff is dissipated in the transistor during the fall of current. In this case it amounts to about 1.2 J.

The body region has a lateral resistance from the contact to the shoulder that is known as the "pinch-base" resistance,  $R_{\rm bb}$ . Current flowing laterally through  $R_{\rm bb}$ , as shown in Figure 3.22, causes an ohmic voltage drop. If this voltage exceeds about 0.6 V, it will initiate transistor action in the parasitic BJT. This is because it forward-biases the source-body junction and causes the injection of electrons from the source into the body region. These then become the emitter and base of the parasitic bipolar transistor.

The value of  $R_{\rm bb}$  is minimized by reducing the length of the shoulder linking the channel region to the p<sup>+</sup> diffusion. The depth of the shoulder is determined by the relative diffusion depths of the body and the source, which in turn determine the channel length. With a channel length of about  $1 \,\mu$ m, the depth of the p diffusion is rather less than  $2 \,\mu$ m. With a maximum boron doping density of about  $1 \times 10^{23} \, {\rm m}^{-3} \, (1 \times 10^{17} \, {\rm cm}^{-3})$ , the body-region resistivity has a minimum value of about  $2 \times 10^{-3} \, \Omega$  m (0.2  $\Omega$  cm). The surface resistance of the shoulder is

Figure 3.21. Example of controlled avalanche breakdown immediately following turn-off.

Figure 3.22. Current flow through the pinch-base resistance. This creates the danger that the parasitic BJT may be activated.

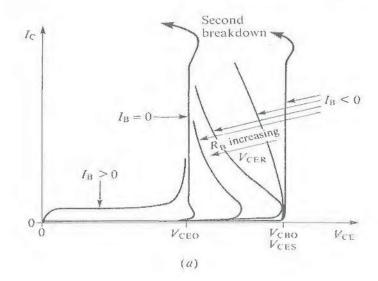

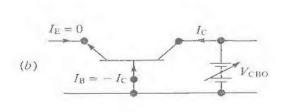

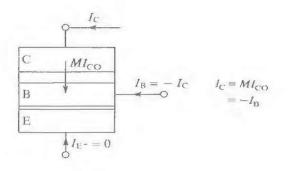

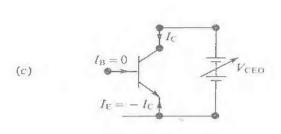

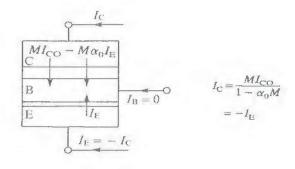

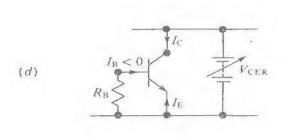

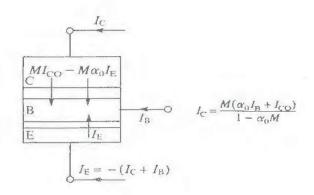

Figure 3.23. The avalanche-breakdown behavior of a bipolar junction transistor. (a) Typical characteristics; (b) common-base configuration  $(V_{CBO})$ ; (c) common-emitter configuration  $(V_{CEO})$ ; (d) emitter and base connected  $(V_{CER})$ . Avalanche breakdown is a regenerative process, because some of the electrons and holes created by impact ionization pass back through the high-field region and themselves create more carriers. The breakdown voltage of a junction,  $V_{\rm B}$ , is the voltage at which the carrier avalanche multiplication factor  $M = \infty$ . As the temperature rises, M decreases, so  $V_B$  increases. In a BIT, the breakdown voltage  $V_{CBO}$ , is that of the collector-base junction with the emitter open-circuited. A similar value is obtained when the base and emitter are shorted, but it is then called  $V_{\rm CES}$ . The breakdown voltage  $V_{\rm CEO}$  is that between the collector and the emitter with the base open-circuited. It is significantly lower than  $V_{\rm CBO}$ , because of a further process of regeneration. When holes created in the multiplication process at the collector junction pass back across the base and enter the emitter, they may cause the injection of further electrons into the base. A proportion of these reach the collector junction, where they in turn suffer multiplication. Let a fraction  $\alpha_0$  of the current crossing the emitter junction be electrons which reach the collector junction and are multiplied. The current in the transistor can increase without limit when  $1 - \alpha_0 M = 0$ , that is, when  $M=1/\alpha_0$ . With  $V_{\rm BE} < 0.6 \, \rm V$ ,  $\alpha_0 \approx 0$ , but the buildup of carriers in the base, once avalanche multiplication becomes appreciable causes the base-emitter junction to become forward biased. Transistor action is initiated and  $\alpha_0$  increases rapidly. The minimum value of  $V_{\text{CEO}}$  corresponds to the maximum value of  $\alpha_0$ , and is known as  $V_{\text{CEO(sus)}}$ . When a finite resistance connects base and emitter, the breakdown curve  $(V_{CER})$  lies between these two extremes. At low currents  $\alpha_0$  is low and  $V_{CER}$  approximates to  $V_{CBO}$ . As the current increases,  $\alpha_0$  increases and  $V_{\text{CER}}$  approaches  $V_{\text{CEO}}$ . Only if the emitter is open-circuited or shorted to the base can  $V_{CBO} = V_{CES}$  be sustained. Further increase in current, if maintained, eventually leads to second breakdown and device destruction.

thus rather more than  $1 \, \mathrm{k}\Omega/\mathrm{square}$ . With the length of the shoulder about  $6 \, \mu \mathrm{m}$  and a gate width of about  $1 \, \mathrm{m}$ , the overall value of  $R_{\mathrm{bb}}$  is in the region of  $6 \, \mathrm{m}\Omega$ , say  $6 \, \mathrm{to} \, 10 \, \mathrm{m}\Omega$ . It would thus require a uniformly distributed current of  $60 \, \mathrm{to} \, 100 \, \mathrm{A}$  to activate the bipolar transistor. However, any mask misalignment that causes the  $\mathrm{p}^+$  diffusion to be displaced also increases the length of the shoulder on one side and so increases  $R_{\mathrm{bb}}$  locally. It is important to understand that it only requires the BJT to be turned on in one part of one cell for this region to hog all the current passing through the device. The rise of temperature caused by the resulting dissipation may induce current crowding and lead on to thermal runaway and second breakdown failure. It is a comment on their design quality and process controllability that manufacturers can now guarantee ratings at which such failures do not occur.

The use of the  $p^+$  diffusion to connect the body region back to the source contact can be seen to be an important part of the VDMOS FET design. It reduces  $R_{bb'}$  and determines the breakdown voltage of the body-drain diode. Its vertical and lateral doping profiles have to be carefully controlled so that no adverse effects on the breakdown voltage or the properties of the channel region occur.

The presence of the parasitic bipolar junction transistor, with its base and emitter connected by  $R_{\rm bb'}$ , lowers the breakdown voltage of the body-source junction. This effect is characteristic of bipolar junction transistors in general. It is illustrated in Figure 3.23. There it can be seen that electrons injected into the base (body) from the emitter (source) give rise to an additional regenerative effect. This is serious because field concentration at the edges and corners of the shoulder of the body region would normally reduce the breakdown voltage there anyway. Fortunately, as was mentioned in the previous section and illustrated in Figure 3.20, the proximity of adjacent cells helps to minimize this field concentration. If, as a result of current flowing through  $R_{\rm bb'}$ , the breakdown voltage is locally reduced to  $V_{\rm CEO}$ , and this is below the supply voltage, the MOSFET will be destroyed.

Under transient conditions, the parasitic BJT may be activated in two further ways. First, changes in the potential difference across the body-drain diode require its self-capacitance to be charged and discharged, and the resulting capacitative currents flow through  $R_{bb'}$ . This could, in principle lead to a forward dV/dt failure. In practice, even taking  $C_{ds} = 1$  nF, which would be typical for  $V_{DS}$ small, the rate of change of  $V_{\rm DS}$  would have to be in the region of 60 to 100 V/ns for  $R_{\rm bb}$ ,  $C_{\rm ds} \, dV_{\rm DS}/dt$  to exceed 0.6 V. This is not a problem with the high degree of cell uniformity achieved in modern devices. The second way of activating the BJT also follows turnoff. Excess carriers left from the previous conduction phase are swept out from the regions either side of the body-drain junction, as the depletion layers expand. This adds greatly to the normal capacitance current. Such carriers are most likely to remain in the region under the gate oxide. From there they are swept into the shoulder of the body region and have to pass the whole of  $R_{\rm bb'}$  to reach the source contact. They are, of course, blocked by the source-body junction, until this becomes forward biased—the effect we are seeking to avoid! Even greater care has to be taken over regions at the periphery of the chip and adjacent to the gate vias. Unless special precautions are taken, carriers tend to build up in these "dead spaces" and remain there longer than in the more confined regions of the active parts of the device. Figure 13.24, in

Section 13.13, shows an IRF 530 turning off in an inductive switching circuit. Following the recovery of the body-drain diode, the device is subjected to a fast forward  $dV_{DS}/dt$  transient. This is safely clamped at 130 V by a controlled breakdown. More detailed discussions of the origin of the waveforms observed during turn-on and turn-off are given in Chapter 4 and in later chapters in the context of specific applications.

### 3.7. TEMPERATURE EFFECTS

In Chapter 2 we showed that the threshold voltage would be expected to decrease with an increase in temperature. Carrier mobility and saturation velocity also decrease as the temperature rises, and in the bulk semiconductor regions the resistivity increases. For a given device, in which  $V_{\rm GS}$  is kept constant, the net consequence of a rise in temperature resulting from these various effects is as follows:

- 1. In the subthreshold region  $(V < V_{\rm T})$  the drain current after pinchoff increases. Before pinchoff the increase in the various parasitic resistances tends to reduce the slope of the  $I_{\rm D}$ -versus- $V_{\rm DS}$  characteristic.

- 2. In the "normal" operating region described by Equations (3.10) and (3.11) in the simple theory, or by their extensions discussed in Appendix 4, the decrease of the carrier mobility more than offsets the consequences of the lowering of  $V_{\rm T}$ . As a result,  $I_{\rm D}$  decreases above and below pinchoff.

- 3. In the velocity saturation region  $I_{\rm D(Sat)}$  again decreases, because of the fall in  $v_{\rm s}$ .

The combination of all these effects on the static characteristics is shown in Figure 3.24. In particular, the transfer characteristics like those of Figure 2 in Appendix 7, which are given in most data sheets, demonstrate how  $I_{D(Sat)}$  increases with temperature below a certain current level and decreases with increasing temperature at higher currents. This is important in the bias stabilization of linear amplifiers, and is discussed further in Section 15.2.2. In practice, the normal operating currents of LDMOS FETS lie much further above the threshold voltage than those of VDMOS FETS. The result is that LDMOS FETS are less sensitive to the variation of  $V_T$ , and the crossover current occurs at a lower level. This is shown in Figure 15.7, in Section 15.2.2.

The effect of temperature on  $g_{\rm fs}$  is shown by Figure 6 of Appendix 7. The reduction in the high-current region, when  $g_{\rm fs}$  is constant, is brought about by the lowering of  $v_{\rm s}$  as the temperature rises. The increase in  $R_{\rm DS(on)}$  with temperature is shown in Figure 9 of Appendix 7. The effect of this is compounded, because the increase in dissipation that results causes a further temperature rise, and so on.

Operating at elevated temperature increases the junction breakdown voltage, by about 1% for each 10°C rise. It also is likely to reduce the expected device lifetime, as described in Chapters 5 and 17. The device capacitances discussed in the previous section are largely unaffected by changes in temperature.

At higher temperatures, a lower forward bias voltage is needed to support a given current flowing across any of the pn junctions. Thus,  $V_{\rm SD(on)}$  is lower.

Figure 3.24. Effect of temperature on device characteristics. Arrows indicate the shift of the different parts of the characteristics with an increase in temperature.

Observation of  $V_{\rm SD(on)}$ ,  $V_{\rm T}$ , or  $R_{\rm DS(on)}$  permits an indication of the temperature in the active parts of the transistor to be obtained, as discussed in Section 17.2.4.

The parasitic bipolar junction transistor is more easily turned on at high temperatures, because the pinch-base resistance  $R_{\rm bb'}$ , is increased, and the voltage needed to forward-bias the emitter-base junction is reduced. At the same time the BJT is more rapidly sent into second breakdown failure.

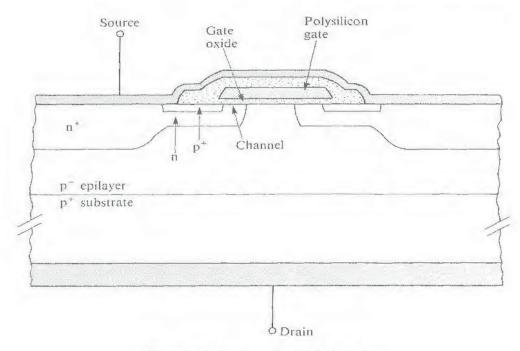

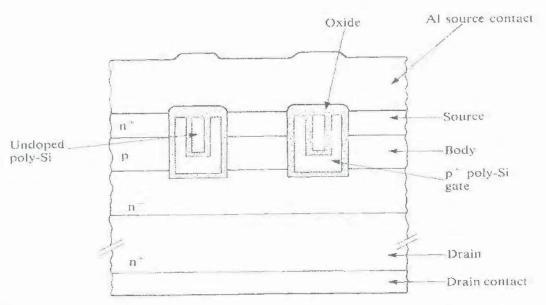

# 3.8. p-CHANNEL AND OTHER DEVICES

Often considerable advantage in circuit simplicity results when complementary p-channel and n-channel devices are both available. This is as true for power devices as it is for CMOS (in comparison with NMOS) integrated circuits. In silicon, holes have lower mobility as well as a lower saturation drift velocity. As a result, p-channel devices show a higher  $R_{\rm DS(on)}$  (about a factor of 2 higher) and a lower value of  $g_{\rm fs}$  than n-channel devices having the same silicon area. These important considerations apart, p-channel devices can be made simply by reversing the dopant types, as illustrated in Figure 3.25. Typical characteristics are shown in Figure 3.26.

One advantage of the p-channel device is that the body region is n-type and so has a lower resistivity for a given doping concentration. The pinch-base resistance,  $R_{\rm bb'}$ , is lower in consequence, and the avalanche characteristics are better because the pnp transistor is less prone to turn on. A further disadvantage, though, is the difficulty of making a good ohmic contact between the source metallization and the body diffusion. Because of the constraints on the body

Figure 3.25. A p-channel device.

region doping levels, this contact normally forms a Schottky diode. Its reverse breakdown voltage is in series with the forward voltage of the body-drain diode when reverse current is conducted, so the drain-source voltage drop under these conditions  $(V_{\rm SD(on)})$  is high, typically 5 to 6 V.

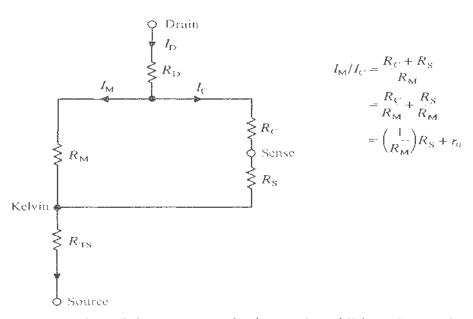

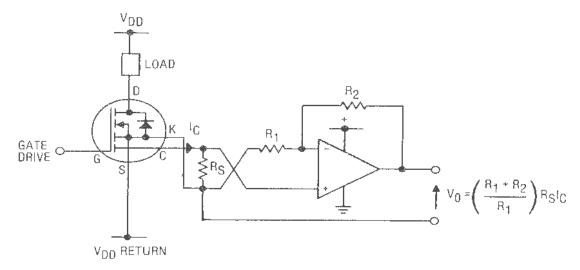

Many variants on the basic VDMOS FET have been devised and are more or less generally available. These include the IGBT mentioned briefly in Section 1.3, and several other MOS/bipolar devices. They are discussed further in Chapter 20. Current-sensing MOSFETS and radiation-hardened devices are discussed in Chapter 19.

Figure 3.26. Characteristics of a p-channel device (an IRF 9540).

### SUMMARY

The total drain-source voltage of the conducting mosfer comprises the ohmic and the nonlinear voltages illustrated in Figure 3.2. For high-voltage devices in the on state, the resistance of the epitaxial layer is dominant, and  $R_{\rm DS(on)}$  varies approximately as  $V_{\rm B}^{2.5}$ . The theory governing these parameters is discussed in Appendix 6. Devices henefit from an increase in the doping level in the drain under the gate oxide. For low-voltage devices it is most important to minimize the contact and lead resistances, and a reduction in the device feature size is beneficial.

A simple charge-control model predicts the following dependence of  $I_{\rm D}$  on  $V_{\rm GS}$  and  $V_{\rm Ch}$ :

For  $V_{\rm GS} > V_{\rm T}$  and  $V_{\rm GS} - V_{\rm T} > V_{\rm Ch}$ ,

$$I_{\rm D} = \mu_{\rm e} \frac{w}{l} C_{\rm ox} [(V_{\rm GS} - V_{\rm T}) V_{\rm Ch} - \frac{1}{2} V_{\rm Ch}^2]$$

(3.10)

For  $V_{\rm GS} > V_{\rm T}$  and  $V_{\rm GS} - V_{\rm T} < V_{\rm Ch}$ ,

$$I_{\rm D} = I_{\rm D(Sat)} = \frac{1}{2} \mu_e \frac{w}{I} C_{\rm ox} (V_{\rm GS} - V_{\rm T})^2$$

(3.11)

At high levels of drain current, electron velocity saturation effects lead to a predicted linear variation of drain current with  $V_{\rm GS}$ ,

$$I_{D(Sat)} = \frac{1}{2}C_{ox}w(V_{GS} - V_{T})v_{s}$$

(3.14)

Close to threshold,  $V_{GS} \approx V_{T}$ , there is an exponential variation of  $I_{D(Sat)}$  with  $V_{GS}$ ,

$$I_{\rm D(Sat)} \propto \exp(eV_{\rm GS}/\alpha kT)$$

(3.15)

This simple theory can be fitted quite closely to the experimental characteristics of devices, but cannot easily be reconciled with their known physical characteristics. On closer examination it is seen to contain a number of self-contradictions. The more sophisticated theory discussed in Appendix 4 avoids these, but without the introduction of a field-dependent mobility, serious discrepancies with the experimental results remain.

Transconductance is maximized by obtaining the maximum gate width from a given area of silicon. This is inversely proportional to feature size, and is aided by the use of a cellular geometry. A discussion of the implications of some of the different cell patterns that have been used or proposed is given in Appendix 5.

A rise of temperature causes an increase in  $R_{\rm DS(on)}$ . In the subthreshold region  $I_{\rm D(Sat)}$  increases with temperature, because of the reduction in the threshold voltage. At higher current levels the reduction in the electron mobility with temperature offsets this, and above a certain value of  $I_{\rm D(Sat)}$ , where the temperature coefficient is zero, it decreases. These effects are illustrated in Figure 3.24.

Holes have a lower mobility and a lower saturation drift velocity than electrons, so p-channel devices have a lower transconductance and a higher  $R_{\rm DS(on)}$  than otherwise similar n-channel devices. Their voltage drop in reverse conduction is higher, but their reverse breakdown performance is better.

Several parasitic components influence the behaviour of power mosfets. As well as the normal parasitic resistance, inductance and capacitance associated with the semiconductor, the leads, and the packaging, several parasitic active components are also inherently present. These include the body-drain diode, the source-body-drain bipolar junction transistor, and a series junction field-effect transistor in the drain drift region. These are illustrated in Figures 3.15 and 3.16. These parasitics limit device performance and set constraints on device design. The body-drain diode is forward biased by any inverse voltage that develops across the transistor and so provides a reverse conduction path. Modern designs of transistors allow the body-drain diode to avalanche safely when reverse biased and so provide a means of dissipating energy stored in inductive switching circuits.

## REFERENCES

- 1. H. C. Pao and C. T. Sah, "Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors." Solid-State Electron. 9, 927-937 (1966).

- 2. R. F. Pierret and J. A. Shields, "Simplified long-channel MOSFET theory." Solid-State Electron. 26, 143-147 (1983).

- 3. J. A. Cooper, Jr. and D. F. Nelson, "High-field drift velocity of electrons at the Si-SiO<sub>2</sub> interface as determined by a time-of-flight technique." J. Appl. Phys. 54, 1445-1456 (1983).

- 4. G. Baccarani, M. R. Wordeman, and R. H. Dennard, "Generalised scaling theory and its application to a 1/4 micrometer Mosfet design." *IEEE Trans. Electron Devices* **ED-31**, 452–462 (1984).

- 5. C. Hu, M.-H. Chi, and V. M. Patel, "Optimum design of power MOSFET's." *IEEE Trans. Electron Devices* **ED-31**, 1693–1700 (1984).

- 6. H.-R. Chang and B. J. Baliga, "Impact of cell breakdown upon power DMOSFET on-resistance." *IEEE Trans. Electron Devices* **ED-34**, 2360 (1987).

- 7. V. A. K. Temple, "Ideal FET doping profile." IEEE Trans. Electron Devices ED-30, 619-626 (1983).

- 8. A. Lidow and T. Herman, "Process for manufacture of high power MOSFET with laterally distributed high carrier density beneath the gate." U.S. Pat. 4,593,302 (1986).

- 9. B. J. Baliga and J. P. Walden, "Improving the reverse recovery of power MOSFET integral diodes by electron irradiation." Solid-State Electron. 26, 1133-1141 (1983).

# Fabrication and Reliability

#### 5.1. FABRICATION

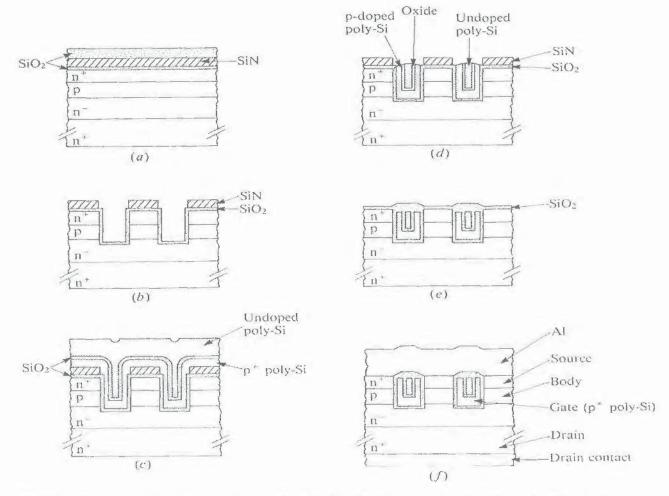

## 5.1.1. A Standard Process for n-Channel Devices

Most vomos fets are fabricated in processes involving several deposition, implantation, and diffusion stages, and some five or six separate masking steps. The photolithography should permit a 2- to 3-\mu minimum line width to be defined. This means that whole-wafer proximity printing may be used, together with chemical (wet) etching methods. A number of more modern device designs utilize a smaller cell size, and so demand a finer geometry. This is particularly true for devices intended for low-voltage applications. For these, the difficulty of maintaining the required definition and registration tolerances over the whole slice is overcome by the use of a step-and-repeat masking process. A mask covering a single device or a few devices only, is projected onto the photoresist, usually with a ×10 reduction, and progressively stepped across the whole wafer. This technique has to be used when larger diameter slices (6 in. rather than 4 in.) are used to increase throughput. Likewise, plasma (dry) etching techniques are then needed in order to avoid undercutting and lateral spread during etching. For a comprehensive review of all aspects of fabrication technology, the reader is referred to Ref. 1.

As was made clear in Chapter 1, VDMOS FETS are fabricated on  $\langle 100 \rangle$ -oriented slices. The slice thickness has to be chosen with some care. Heat dissipated in the active parts of the device has to be removed through the full thickness of the substrate. The thicker the slice, the greater is the thermal resistance of the final device. However, too thin a slice will lead to breakages during manufacture and a lower yield, particularly with larger-diameter slices. Typically, slice thicknesses between 250 and 500  $\mu$ m (10–20 mils) are used. The slice thickness also adds to  $R_{DS(on)}$ . However, heavy doping with phosphorus ensures that the resistivity is low. Typical values exceed  $10^{24}$  atoms/m<sup>3</sup> ( $10^{18}$  cm<sup>-3</sup>), giving  $2 \times 10^{-4}$   $\Omega$  m (0.02  $\Omega$  cm), or less.

After the normal cleaning and polishing routines, the first step is to grow the n-type epitaxial layer in which the device will be formed. Ideally this should be defect-free. Its thickness and doping level are determined by the intended voltage rating of the transistors. For 50-V devices, as little as  $10 \, \mu \text{m}$  of material may be deposited. The resistivity would then typically be about  $0.01 \, \Omega \, \text{m}$  ( $1 \, \Omega \, \text{cm}$ ), corresponding to a phosphorus doping level of about  $5 \times 10^{21} \, \text{m}^{-3}$  ( $5 \times 10^{15} \, \text{cm}^{-3}$ ). The thickness and resistivity of the epitaxial layer increase as the voltage rating

increases. For 500-V devices, the thickness is more likely to be 50  $\mu$ m and the resistivity 0.2  $\Omega$  m (20  $\Omega$  cm). The corresponding phosphorus concentration is  $2 \times 10^{20}$  m<sup>-3</sup> ( $2 \times 10^{14}$  cm<sup>-3</sup>).

The surface is oxidized for the first masking process. This defines the p-type wells that in the final device connect the channel regions back to the source contacts. It also defines the p-type regions that will underlie the gate vias and the bonding pads. Similar p-type regions form the guard rings for the high-voltage structure around the periphery of the chip. Windows are etched through the oxide, and some  $10^{18}$  boron atoms per square meter ( $10^{14}$  cm<sup>-2</sup>) are implanted at low energy ( $<10\,\text{kV}$ ) and then diffused in to form a junction at a depth of about 5  $\mu\text{m}$ . In an optimized process, some compensation has to be made for the doping level of the epilayer. The sheet resistance is typically about 200  $\Omega$ /square. During the high-temperature treatment, some outdiffusion of dopant from the substrate into the epilayer occurs.