# 10 A, 2.4 kV Power DiMOSFETs in 4H-SiC

Sei-Hyung Ryu, *Member, IEEE*, Anant Agarwal, *Member, IEEE*, James Richmond, John Palmour, *Member, IEEE*, Nelson Saks, and John Williams

Abstract—We report the characteristics of large area (3.3 × 3.3 mm²) high-voltage 4H-SiC DiMOSFETs. The MOSFETs show a peak MOS channel mobility of 22 cm²/V·s and a threshold voltage of 8.5 V at room temperature. The DiMOSFETs exhibit an on-resistance of 42 mΩ·cm² at room temperature and 85 mΩ·cm² at 200 °C. Stable avalanche characteristics at approximately 2.4 kV are observed. An on-current of 10 A is measured on a 0.103 cm² device. High switching speed is also demonstrated. This suggests that the devices are capable of high-voltage, high-frequency, low-loss switching applications.

*Index Terms*—Avalanche, fast switching, high voltage, MOSFET, NO anneal, silicon carbide.

#### I. INTRODUCTION

7 ERY HIGH critical field (~2 MV/cm) and good bulk electron mobility (~800 cm<sup>2</sup>/V·s) make 4H-silicon carbide very attractive for high-speed unipolar switching devices for blocking voltages ranging from 600 V to 3000 V [1], [2]. At such high voltages, conventional silicon devices typically utilize conductivity modulation in the drift layer, resulting in slower switching speeds. Several exploratory devices, such as vertical MOSFETs [3]–[7] and vertical JFETs [8], [9] have been demonstrated in SiC. However, none of the devices reported to date demonstrated reasonable current ratings and normally off characteristics. In this letter, we present results from our latest 4H-SiC DiMOSFETs (double-implanted MOSFETs) [3], [10] with active areas of up to 0.103 cm<sup>2</sup>. The 0.103 cm<sup>2</sup> device exhibits a specific on-resistance of 42 m $\Omega$ ·cm<sup>2</sup>, a drain current of 10 A at a forward drop of 7.2 V, and a blocking voltage of around 2.4 kV.

## II. DEVICE DESIGN AND FABRICATION

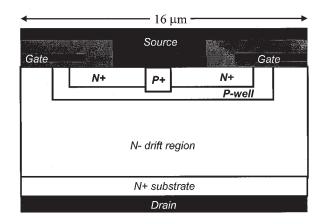

A simplified schematic cross section of a DiMOSFET cell is shown in Fig. 1. The MOS channel length, defined by the p-well and  $n^+$  implants, is 1.5  $\mu$ m. Electrons flow laterally from  $n^+$  source through an MOS channel on the implanted p-well, then flow vertically through the JFET region formed by two adjacent p-well regions, and then through the lightly doped  $n^-$  drift region into the drain. The cell pitch is 16  $\mu$ m, and packing density of the gate periphery is 1250 cm/cm<sup>2</sup>. A 20  $\mu$ m thick

Manuscript received December 18, 2001; revised March 6, 2002. This work was supported by Defense Advanced Research Projects Agency (DARPA) and managed by the Office of Naval Research under Contract N00014-99-C-0377. The review of this letter was arranged by Editor J. Sin.

S.-H. Ryu, A. Agarwal, J. Richmond, and J. Palmour are with Cree, Inc., Durham, NC 27703 USA.

N. Saks is with the Naval Research Laboratory, Washington, DC 20375 USA.

J. Williams is with the Department of Physics, Auburn University, Auburn, AL 36849 USA.

Publisher Item Identifier S 0741-3106(02)05186-8.

Fig. 1. Simplified cross-sectional view of a DiMOSFET cell.

drift layer with a doping concentration of  $2.5 \times 10^{15}$  cm<sup>-3</sup> was chosen for a 2000 V blocking voltage design.

P-wells, with a surface concentration of around  $1 \times 10^{16}$  cm<sup>-3</sup>, were formed by aluminum implantation. N<sup>+</sup> source regions were then formed by a heavy-dose nitrogen implantation. A heavy dose aluminum implantation formed p<sup>+</sup> contacts to the p-wells, as well as the floating guard rings to terminate the edges. All the implants were activated at around 1600 °C in Ar. A 2-μm-thick oxide layer was then deposited and patterned as the field oxide followed by a gate oxidation. 500-Å-thick gate oxide was thermally grown at 1200 °C in dry O2, then annealed in NO at Auburn University, Auburn, AL, as described in [11]. Then, a 0.25  $\mu$ m thick Molybdenum layer was sputtered and patterned as gate metal. The gate was then metallized with a 0.25- $\mu$ m-thick Ni/Au layer to reduce the gate resistance further. The contacts to source, drain, and p<sup>+</sup> regions were formed with alloyed Ni. A PECVD oxide layer was then deposited as an inter-metallic dielectric, and via holes were opened. Finally, a 2- $\mu$ m-thick Ti/Pt/Au layer was e-beam evaporated and lifted off as the final metal layer.

## III. EXPERIMENTAL RESULTS

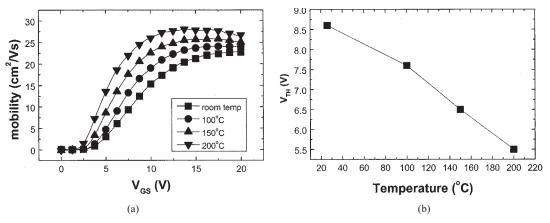

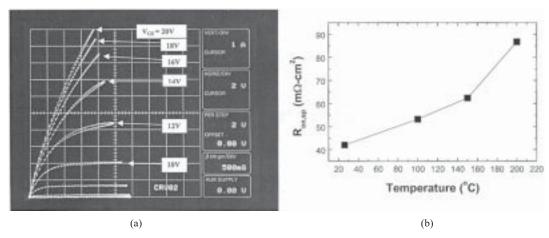

Fig. 2 shows the effective MOS channel mobility ( $\mu_{eff}$ ) and threshold voltage ( $V_{TH}$ ) measured on a lateral test MOSFET with a W/L of 200  $\mu$ m/200  $\mu$ m. A peak mobility of 22 cm²/Vs and a  $V_{TH}$  of 8.5 V are measured at room temperature. At 200 °C, the peak mobility increases to 27 cm²/Vs and the  $V_{TH}$  shifts to 5.5 V. This suggests that the MOS channel is still severely affected by interface traps [12]. Fig. 3(a) shows the on-state characteristics of a 3.3 mm  $\times$  3.3 mm (active area = 0.103 cm²) DiMOSFET at room temperature, measured using a Tektronix 370 curve tracer. The device is normally off, and shows an on-current of 10 A (97 A/cm²)

Fig. 2. (a) Effective MOS channel mobility and (b) threshold voltage extracted from a 200  $\mu$ m/200  $\mu$ m 4H-SiC test MOSFET.  $V_{DS}$  was fixed at 50 mV.

Fig. 3. (a) On-state current-voltage I-V characteristics of a 0.103 cm<sup>2</sup> 4H-SiC DiMOSFET. (b) Specific on-resistance of a 4H-SiC DiMOSFET as a function of temperature.

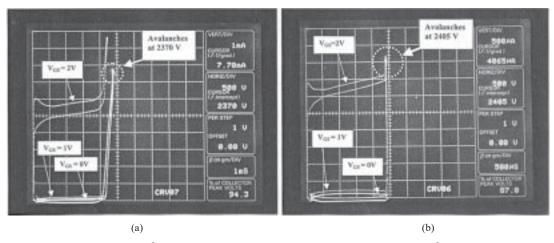

Fig. 4. (a) Blocking characteristics of a 0.103 cm² 4H-SiC DiMOSFET. (b) Blocking characteristics of a 0.0387 cm² 4H-SiC DiMOSFET. Both measurements were done at room temperature, and the devices were immersed in Fluorinert™ oil.

at a forward drop of around 7.2 V. Specific on-resistance,  $R_{on,\,sp}$ , measured with  $V_{GS}=20$  V and  $V_{DS}=1$  V at room temperature, is around 42 m $\Omega$ ·cm<sup>2</sup>. The specific on-resistance is very dependent on the gate bias, and high gate voltages were required to turn the devices fully on, indicating that the on-resistance is dominated by the MOS channel resistance at room temperature. This suggests that further improvement in the  $\mu_{eff}$  is necessary to reduce the on-resistance. A higher  $\mu_{eff}$  is also expected to result in improved long-term reliability

of the device because a lower gate bias (with less stress on the gate dielectric) can be used to fully turn on the device. Fig. 3(b) shows  $R_{on,\,sp}$  as a function of temperature. The  $R_{on,\,sp}$  value increases with temperature despite the increase in  $\mu_{eff}$  and the negative shift in  $V_{TH}$ , due to decrease in electron mobility in the drift layer. This enables easy paralleling of these devices.

Fig. 4(a) shows the blocking capability of the same device at room temperature, measured using a Tektronix 371 curve tracer. The measurement was done in Fluorinert<sup>TM</sup> oil. The

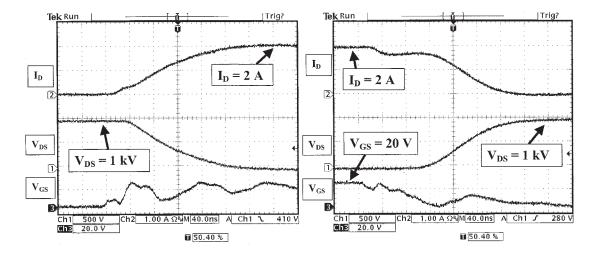

Fig. 5. Room temperature dynamic characteristics of a 0.0387 cm<sup>2</sup> 4H-SiC DiMOSFET. A supply voltage of 1000 V, a 500  $\Omega$  resistive load, and a 50  $\Omega$  gate resistor were used for the measurement. The switching frequency of the gate drive was 100 kHz. (a) Turn-on transients and (b) turn-off transients.

device starts showing some leakage current at a  $V_{DS}$  of 2100 V, then avalanches at a  $V_{DS}$  of 2370 V. This blocking voltage is approximately 75% of the ideal parallel plate blocking voltage of the epilayer (3100 V), assuming a critical electric field  $(E_c)$  of 2 MV/cm. The blocking characteristics of a smaller (0.0387 cm²) device placed adjacent to the device are shown in Fig. 4(b). Since the area of this device is smaller, it contains less material defects, and no significant leakage current is observed until it reaches avalanche conditions. None of the curves  $(V_{GS}=0~{\rm V},1~{\rm V},2~{\rm V})$  in Fig. 4(b) show signs of early breakdown until  $V_{DS}$  reaches 2405 V, at which point the device shows avalanche breakdown. The avalanche was powered up to 4 mA (=0.1 A/cm²), which corresponds to a power density of about 240 W/cm².

Fig. 5 shows dynamic characteristics of a —packaged  $0.0387~\rm cm^2$  device at room temperature. A supply voltage of  $1000~\rm V$ , a  $500~\Omega$  resistive load, a  $50~\Omega$  gate resistor, and a  $100~\rm kHz$  gate pulse were used for this measurement. The device switches 2 A of drain current (about  $52~\rm A/cm^2$ ) with a turn-on delay,  $t_{d(off)}$ , of  $40~\rm ns$ , a rise time,  $t_r$ , of  $140~\rm ns$ , a turn-off delay,  $t_{d(off)}$ , of  $100~\rm ns$ , and a fall time,  $t_f$ , of  $120~\rm ns$ . This shows that these DiMOSFETs are suitable for low loss, high speed power switching applications.

## IV. CONCLUSION

The 2.4 kV DiMOSFETs in 4H-SiC have been successfully fabricated. The devices have an MOS channel mobility of  $22 \text{ cm}^2/\text{V} \cdot \text{s}$  and a threshold voltage of 8.5 V. The DiMOSFETs exhibit an on-resistance of  $42 \text{ m}\Omega \cdot \text{cm}^2$  at  $27 \, ^{\circ}\text{C}$ , which increases with the temperature. The on-resistance is dominated by the MOS channel resistance, which suggests that further improvement in the MOS channel mobility is necessary to improve the device performance. A blocking voltage of around 2.4 kV is observed, and an on-current of 10 A is measured from a 0.103 cm<sup>2</sup> device. Dynamic measurement of these devices showed a turn-on time ( $t_{d(on)} + t_r$ ) of 180 ns and a turn-off time ( $t_{d(off)} + t_f$ ) of 220 ns when controlling a current density of 52 A/cm<sup>2</sup> with a 1000 V supply voltage. The excellent blocking

capability and fast switching speed of the devices suggest that these devices will enable high-voltage, high-frequency, and low-loss power switching applications.

#### REFERENCES

- P. G. Neudeck, "Progress in silicon carbide semiconductor electronics technology," J. Electron. Mater., vol. 24, p. 283, 1995.

- [2] M. Bhatnagar and B. J. Baliga, "Comparison of 6H-SiC, 3C-SiC, and Si for power devices," *IEEE Trans. Electron Devices*, vol. 40, p. 645, Mar. 1993.

- [3] J. N. Shenoy, J. A. Cooper, Jr., and M. R. Melloch, "High-voltage double-implanted power MOSFETs in 6H-SiC," *IEEE Electron Device Lett.*, vol. 18, pp. 93–95, Mar. 1997.

- [4] K. Hara, "Vital issues for SiC power devices," in *Proc. Int. Conf. Silicon Carbide, III-Nitrides and Related Materials*, Stockholm, Sweden, Aug.. 31–Sept. 5, 1997.

- [5] J. Tan, J. A. Cooper, Jr., and M. R. Melloch, "High-voltage accumulation-layer UMOSFETs in 4H-SiC," *IEEE Electron Device Lett.*, vol. 19, pp. 487–489, Dec. 1998.

- [6] S. Ryu, A. K. Agarwal, N. S. Saks, M. K. Das, L. A. Lipkin, R. Singh, and J. W. Palmour, "Design and Process Issues for silicon carbide power DiMOSFETS," in *Proc. Mat. Res. Soc. Symp.*, 2001, vol. 640, pp. H4.5.1–H.4.5.6.

- [7] R. Schorner, P. Friedrichs, D. Peters, H. Mitlehner, B. Weis, and D. Stephani, "Rugged power MOSFETs in 6H-SiC with blocking capability up to 1800 V," in *Trans. Tech. Publications. Mat. Sci. Forum*, vol. 348-342, Switzerland, 2000, pp. 1295–1298.

- [8] K. Asano, Y. Sugawara, S. Ryu, R. Singh, J. Palmour, T. Hayashi, and D. Takayama, "5.5 kV Normally-off low ronS 4H-SiC SEJFET," in *Proc. Int. Symp. Power Semiconductor Devices and ICs*, Osaka, Japan, June 4–7, 2001.

- [9] P. Friedrichs, H. Mitlehner, R. Kalschmidt, U. Weinert, W. Bartsch, C. Hecht, K. O. Dohnke, B. Weis, and D. Stephania, "Static and dynamic characteristics of 4H-SiC JFETs designed for different blocking categories," in *Trans. Tech. Publications. Mat. Sci. Forum*, vol. 348-342, Geneva, Switzerland, 2000, pp. 1243–1246.

- [10] S. Ryu, A. Agarwal, J. Richmond, M. Das, L. Lipkin, J. Palmour, N. Saks, and J. Williams, "Large area (3.3 mm × 3.3 mm) power MOSFETs in 4H-SiC," in *Proc. Int. Conf. Silicon Carbide and Related Materials*, Tsukuba, Japan, Oct. 28–Nov. 2, 2001.

- [11] G. Chung, C. C. Tin, J. R. Williams, J. K. McDonald, M. Di Ventra, S. T. Pantelides, L. C. Feldman, and R. A. Weller, "Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide," *Appl. Phys. Lett.*, vol. 76, pp. 1713–1715, Mar. 2000.

- [12] J. R. Williams, G. Chung, C. C. Tin, K. McDonald, D. Farmer, R. K. Chanana, R. A. Weller, S. T. Pantelides, O. W. Holland, M. K. Das, and L. C. Feldman, "Passivation of the 4H-SiC/SiO2 interface with nitric oxide," in *Int. Conf. Silicon Carbide and Related Materials*, Tsukuba, Japan, Oct. 28–Nov. 2, 2001.