# UNITED STATES PATENT AND TRADEMARK OFFICE PATENT TRIAL AND APPEAL BOARD

SAMSUNG ELECTRONICS CO., LTD.

Petitioner v.

# BISHOP DISPLAY TECH LLC Patent Owner

Case No. IPR2022-00501 Patent No. 7,995,047

# **DECLARATION OF ALEX Z. KATTAMIS, PH.D., P.E.**

# TABLE OF CONTENTS

| I.        | I  | NTRODUCTION                                                          | 8  |

|-----------|----|----------------------------------------------------------------------|----|

| II.       | E  | XPERIENCE AND QUALIFICATIONS                                         | 8  |

| III.      | T  | ASK SUMMARY AND MATERIALS REVIEWED                                   | 10 |

| IV.       | L  | IST OF EXHIBITS                                                      | 11 |

| V.        |    | UMMARY OF CONCLUSIONS AND GROUNDS FOR HALLENGE OF '047 PATENT        | 13 |

| VI.       | U  | NDERSTANDING OF THE GOVERNING LAW                                    | 14 |

|           | A. | Level of Ordinary Skill in the Art                                   | 14 |

|           | B. | Legal Standard for Claim Construction                                | 15 |

|           | C. | Anticipation                                                         | 16 |

|           | D. | Obviousness                                                          | 17 |

| VII.      | O  | VERVIEW OF THE '047 PATENT                                           | 20 |

|           | A. | Priority Date for Claims of the '047 Patent                          | 20 |

|           | B. | The Subject Matter of the '047 Patent                                | 21 |

|           | C. | The Challenged Claims of the '047 Patent                             | 28 |

|           | D. | Prosecution History of the '047 Patent                               | 31 |

|           |    | a. Originally Filed Claims on December 12, 2007                      | 31 |

|           |    | b. USPTO Examiner Issues Office Action on December 8, 2010           | 35 |

|           |    | c. Applicants Respond to Office Action on March 7, 2011              | 35 |

|           |    | d. Notice of Allowance on May 31, 2011                               | 43 |

| VIII      |    | EVEL OF ORDINARY SKILL IN THE ART FOR THE '047 ATENT                 | 44 |

| IX.       |    | LAIM CONSTRUCTION                                                    |    |

| <b>X.</b> | T  | ECHNOLOGY BACKGROUND AND STATE OF THE ART OR THE '047 Patent         |    |

|           | A. | Exemplary References Corroborating the General Engineering Knowledge | 45 |

|           |    | a. Camara Handbook (Ex. 1007)                                        | 45 |

|           |    | b. den Boer Text (Ex. 1008)                                          | 45 |

|      |    | c. Han Article (Ex. 1009)                                                                                                                                                                   | 46 |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | B. | General Display Background                                                                                                                                                                  | 46 |

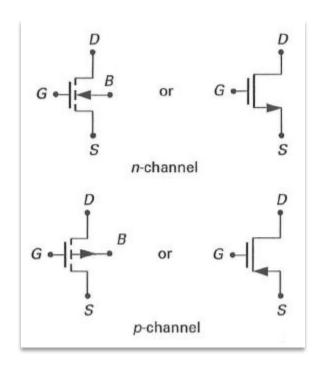

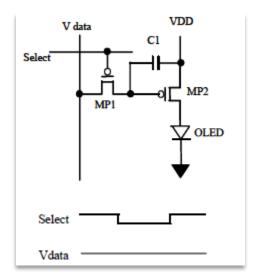

|      | C. | Basic Circuits for Driving Displays                                                                                                                                                         | 49 |

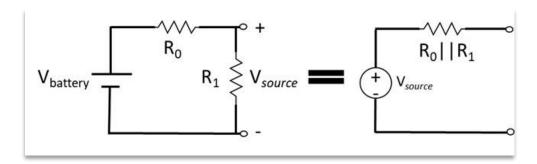

|      |    | a. Voltage supply source / Voltage supply mode                                                                                                                                              | 49 |

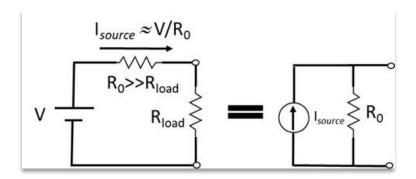

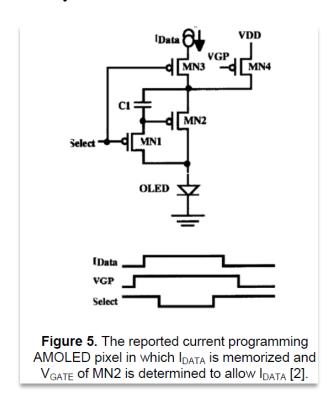

|      |    | b. Current supply source / Current supply mode                                                                                                                                              | 50 |

|      |    | c. Voltage-current converting circuit                                                                                                                                                       | 50 |

|      |    | d. Capacitors                                                                                                                                                                               | 51 |

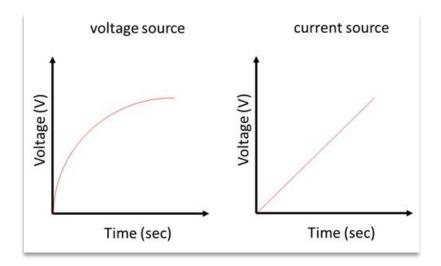

|      |    | e. Voltage and Current Programming                                                                                                                                                          | 53 |

| XI.  | O  | VERVIEW OF THE PRIOR ART TO THE '047 PATENT                                                                                                                                                 | 57 |

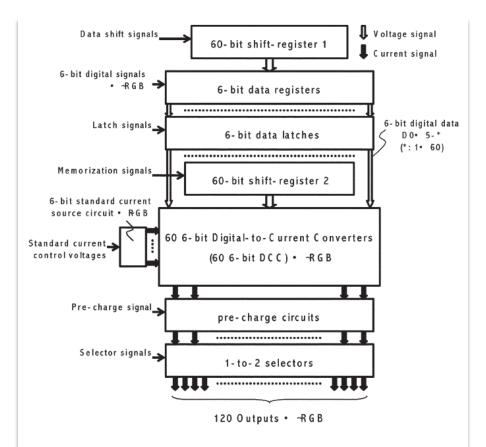

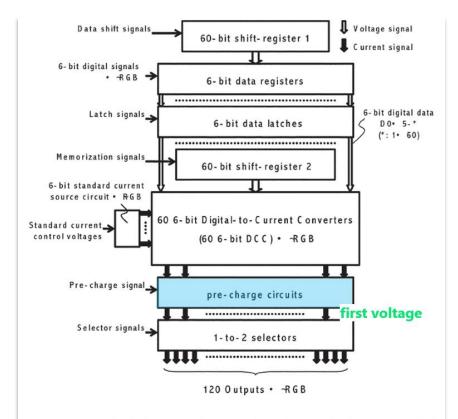

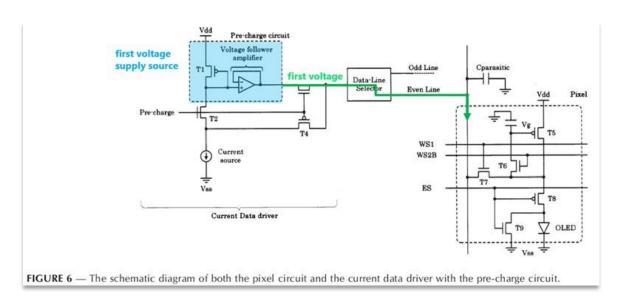

|      | A. | Shimoda (Ex. 1004)                                                                                                                                                                          | 57 |

|      |    | a. Status of Shimoda as Prior Art                                                                                                                                                           | 57 |

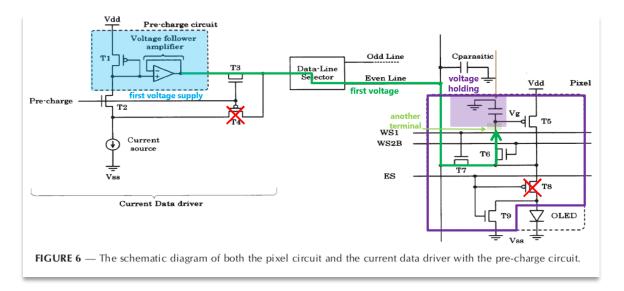

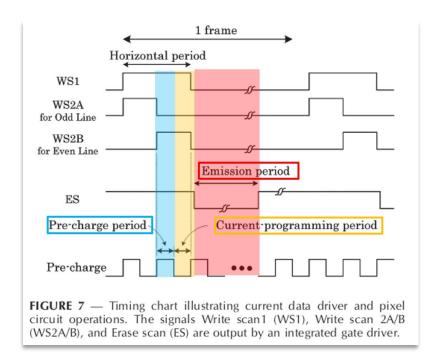

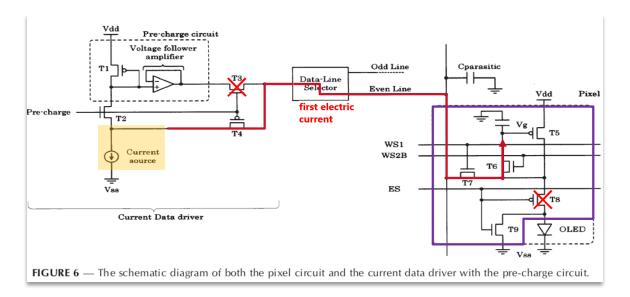

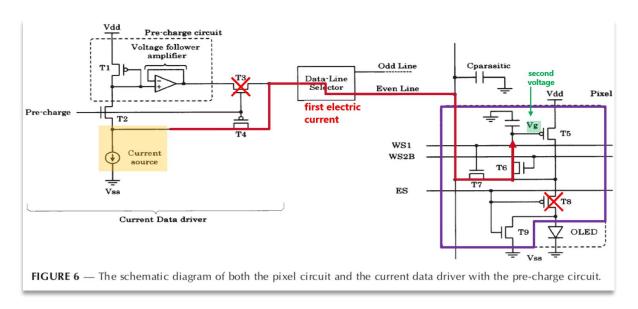

|      |    | b. Overview of the Disclosure of Shimoda                                                                                                                                                    | 59 |

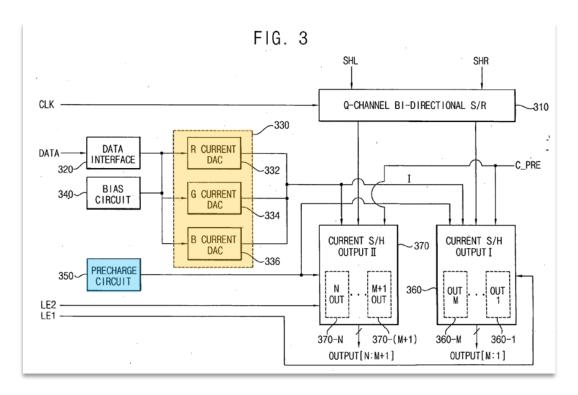

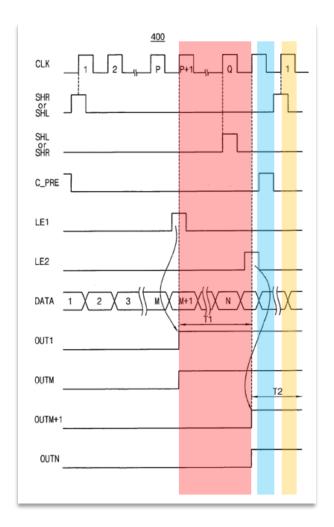

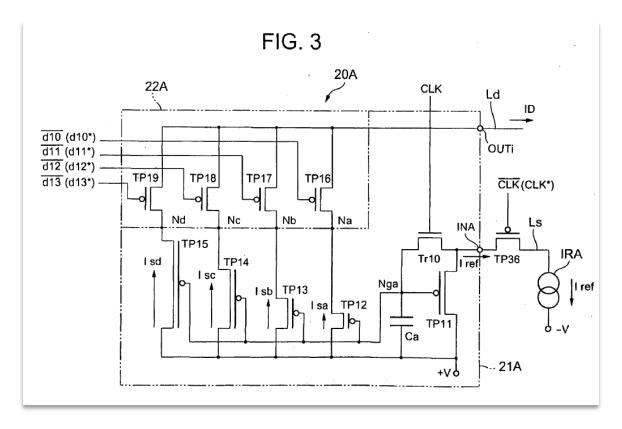

|      | B. | Baek (Ex. 1005)                                                                                                                                                                             | 62 |

|      |    | a. Status of Baek as Prior Art                                                                                                                                                              | 62 |

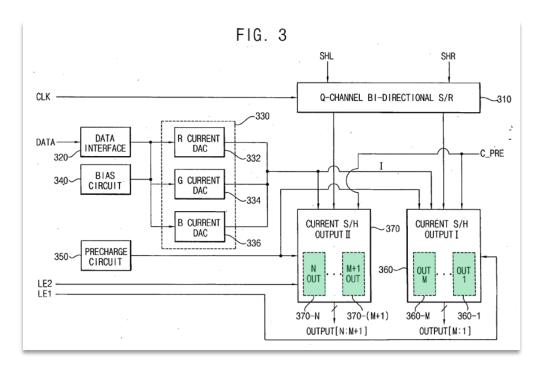

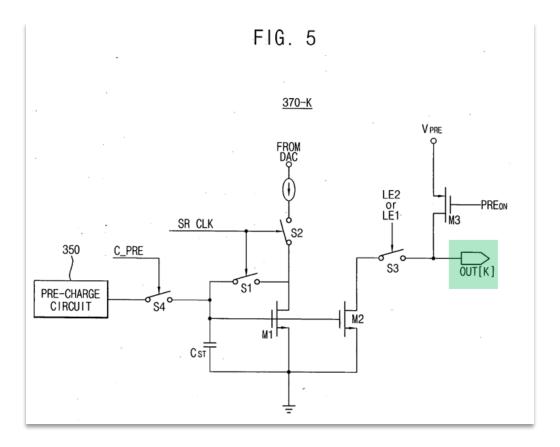

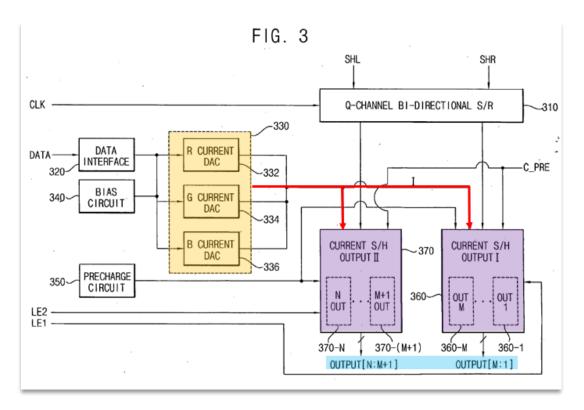

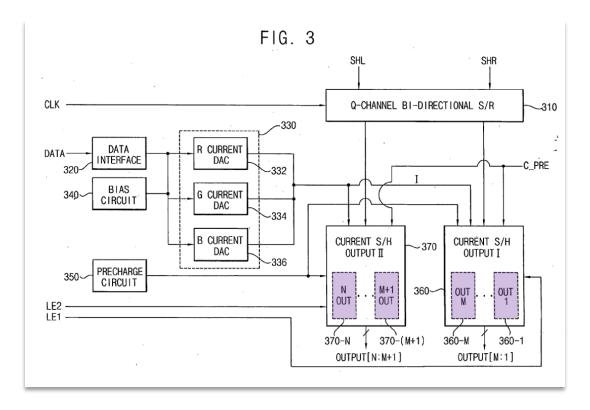

|      |    | b. Overview of the Disclosure of Baek                                                                                                                                                       | 62 |

|      | C. | Sasaki (Ex. 1006)                                                                                                                                                                           | 66 |

|      |    | a. Status of Sasaki as Prior Art                                                                                                                                                            | 66 |

|      |    | b. Overview of the Disclosure of Sasaki                                                                                                                                                     | 67 |

| XII. | G  | ROUNDS 1 & 2: SHIMODA                                                                                                                                                                       | 69 |

|      | A. | Independent Claim 1 of the '047 Patent                                                                                                                                                      | 70 |

|      |    | a. 1(pre): "A current driving device, comprising:"                                                                                                                                          | 70 |

|      |    | b. 1(a): "a first voltage supply source for supplying a first                                                                                                                               |    |

|      |    | voltage;"                                                                                                                                                                                   | 72 |

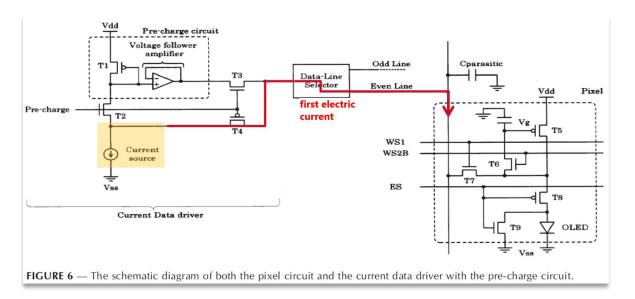

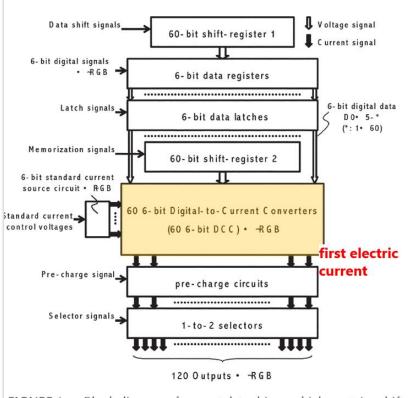

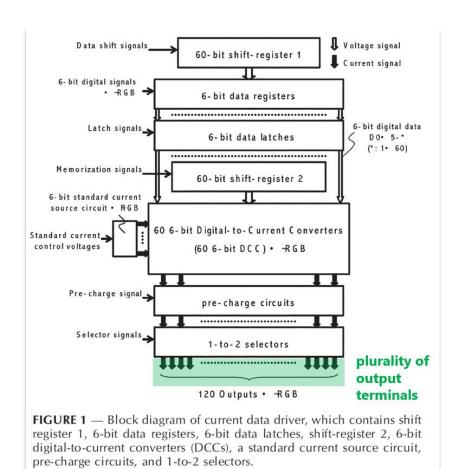

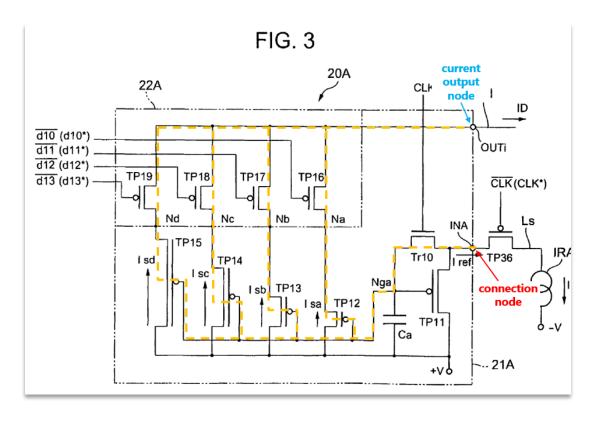

|      |    | c. 1(b): "a first current supply source for supplying a first electric current;"                                                                                                            | 74 |

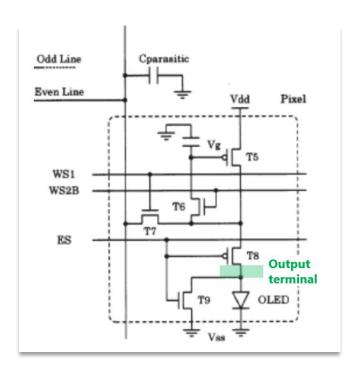

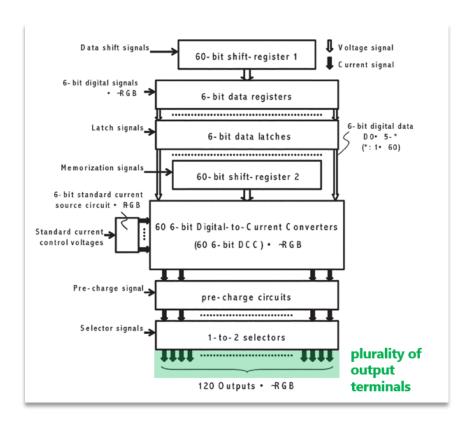

|      |    | d. 1(c): "a plurality of output terminals;"                                                                                                                                                 | 76 |

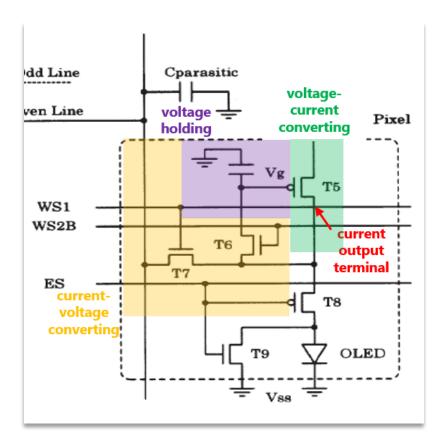

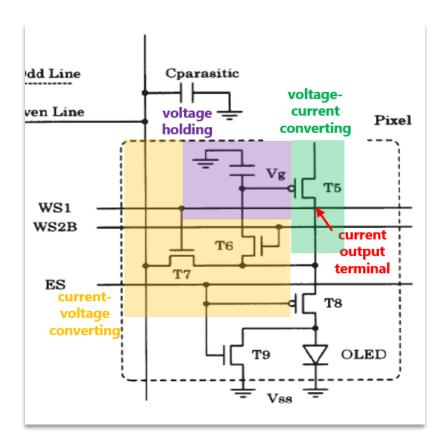

|      |    | e. 1(d)(1): "and a plurality of current output circuits for outputting an electric current in accordance with said first electric current, each of said current output circuits comprising" | 79 |

|      |    | f. 1(d)(2): "a current-voltage converting circuit, a voltage-current converting circuit, a voltage holding circuit having a terminal                                                        |    |

|    |    | voltage, and at least one current output terminal, wherein,"82                                                                                                                                                                                                                                                                                                                 |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

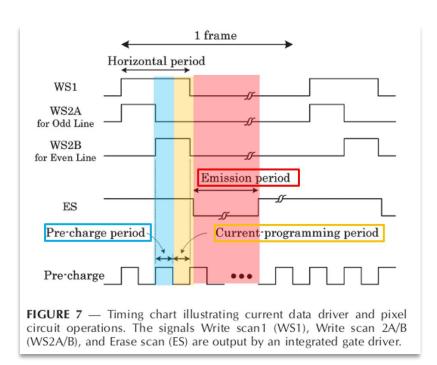

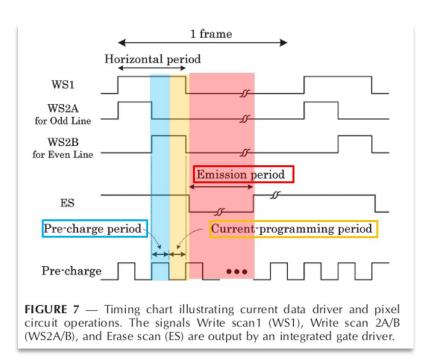

|    | g. | 1(e): "each of said current output circuits operates in three operation modes including a voltage supply mode, a current supply mode, and a current output mode,"                                                                                                                                                                                                              |

|    | h. | 1(f): "under said voltage supply mode, each of said current output circuits receives said first voltage from said first voltage supply source, and the first voltage is supplied to another terminal of said voltage holding circuit,"                                                                                                                                         |

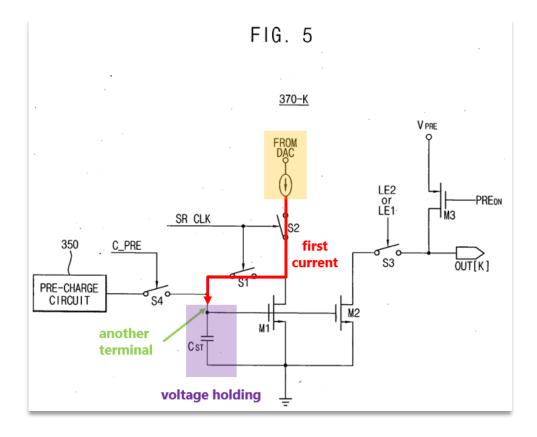

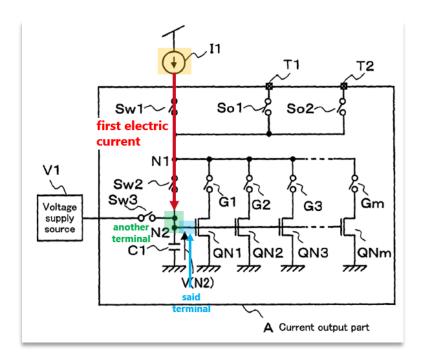

|    | i. | 1(g): "under said current supply mode, each of said current output circuits receives said first current from said first current supply source, and generates a second voltage by said current-voltage converting circuit, and the first current is supplied to said another terminal of said voltage holding circuit, and"96                                                   |

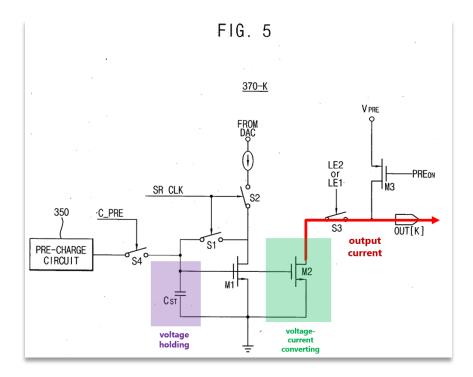

|    | j. | 1(h): "under said current output mode, each of said current output circuits outputs an output current according to said voltage held in said voltage holding circuit by said voltage-current converting circuit."                                                                                                                                                              |

| B. | Cl | aims Depending From Claim 1 of the '047 Patent105                                                                                                                                                                                                                                                                                                                              |

|    | a. | "2. The current driving device according to claim 1, wherein: each of said output terminals is connected to said current output terminals provided to said plurality of said current output circuits, and each of said plurality of current output circuits is connected in parallel to said first current supply source and said first voltage supply source used in common." |

|    | b. | "3. The current driving device according to claim 1, wherein, in each of said current output circuits, said current-voltage converting circuit is actuated under said voltage supply mode."111                                                                                                                                                                                 |

|    | c. | "4. The current driving device according to claim 1, wherein each of said current output circuits is configured to stop said current-voltage converting circuit under said voltage supply mode."                                                                                                                                                                               |

|    | d. | "9. A current-driving-type display device, comprising said current driving device according to claim 1 mounted thereon so as to be driven by said current driving device."                                                                                                                                                                                                     |

| XIII. | G  | ROUNDS 3 & 4: BAEK113                                                                                                                                                                                                                                                                                                                            |

|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | A. | Independent Claim 1 of the '047 Patent                                                                                                                                                                                                                                                                                                           |

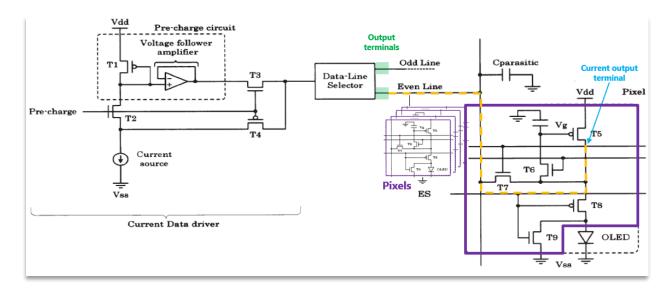

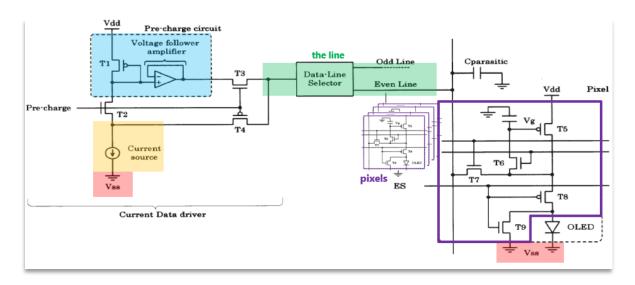

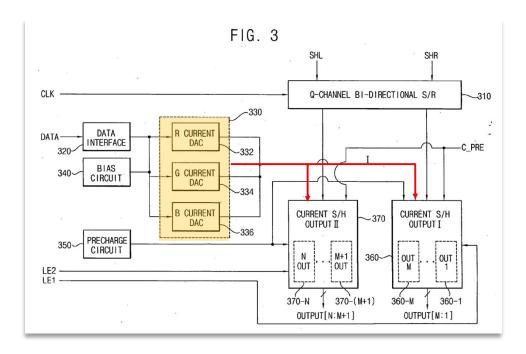

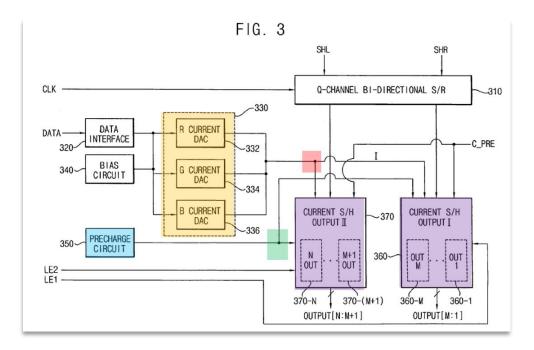

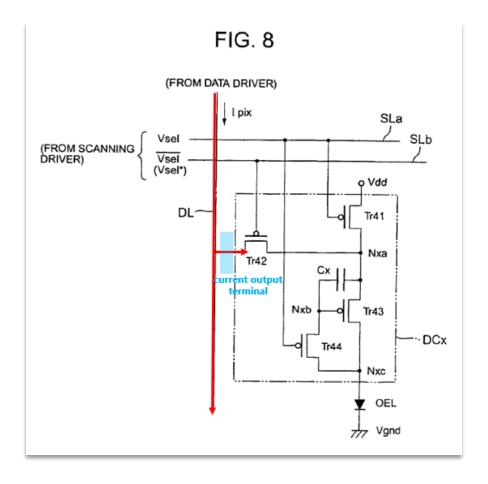

|       |    | a. 1(preamble): "A current driving device, comprising:"114                                                                                                                                                                                                                                                                                       |

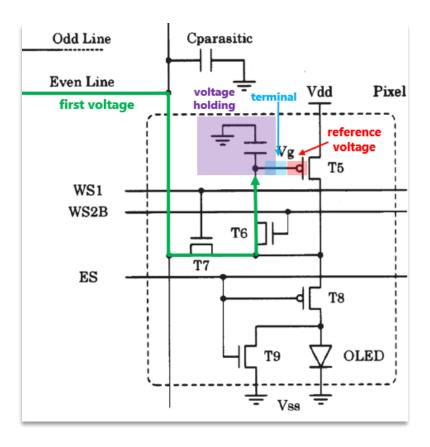

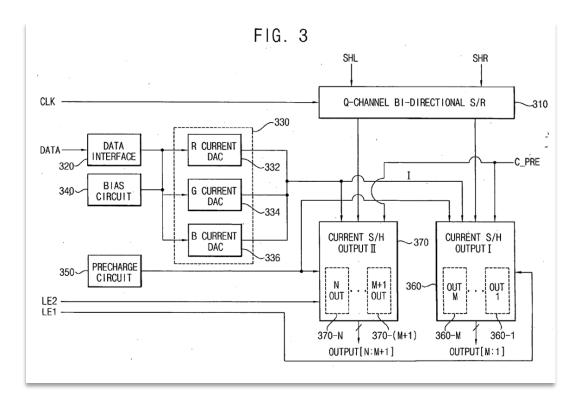

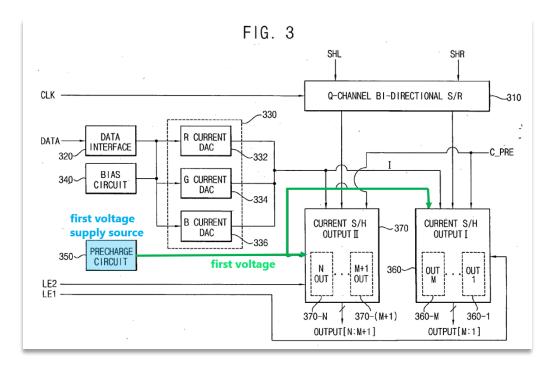

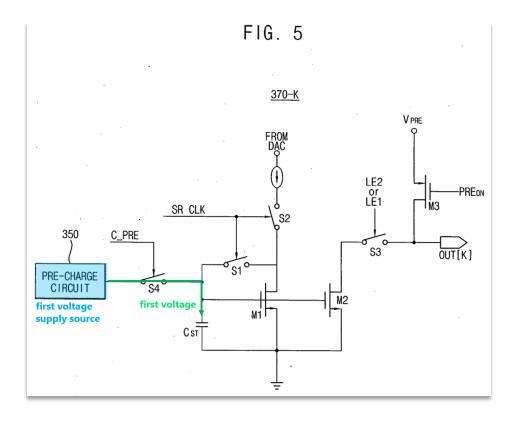

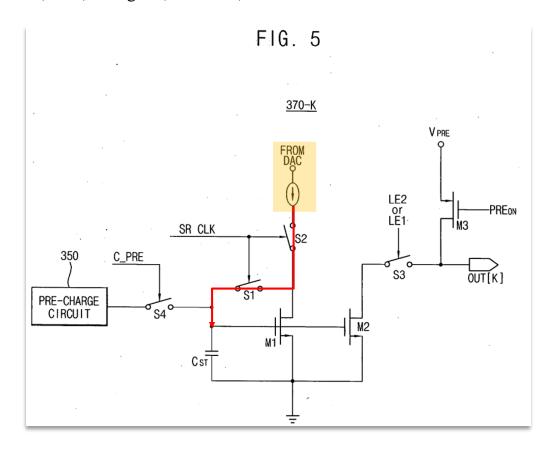

|       |    | b. 1(a): "a first voltage supply source for supplying a first voltage;"                                                                                                                                                                                                                                                                          |

|       |    | c. 1(b): "a first current supply source for supplying a first electric current;"                                                                                                                                                                                                                                                                 |

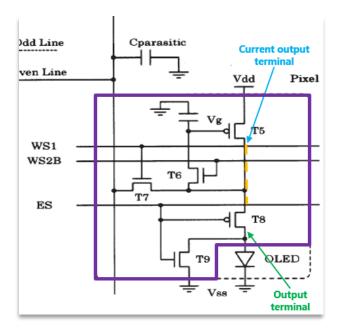

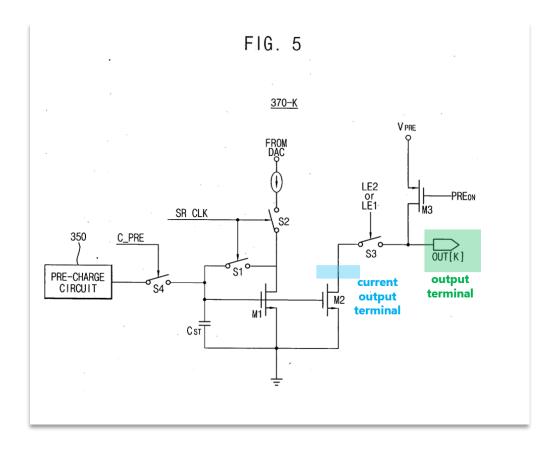

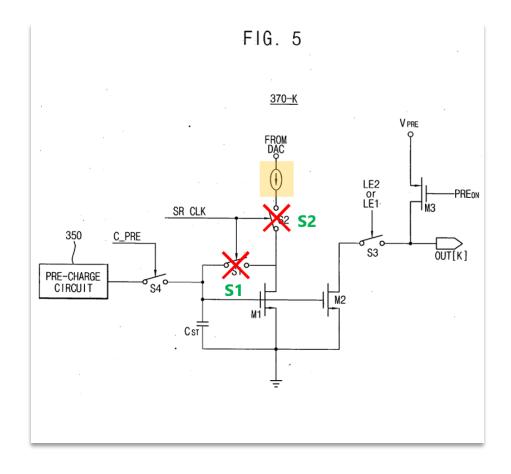

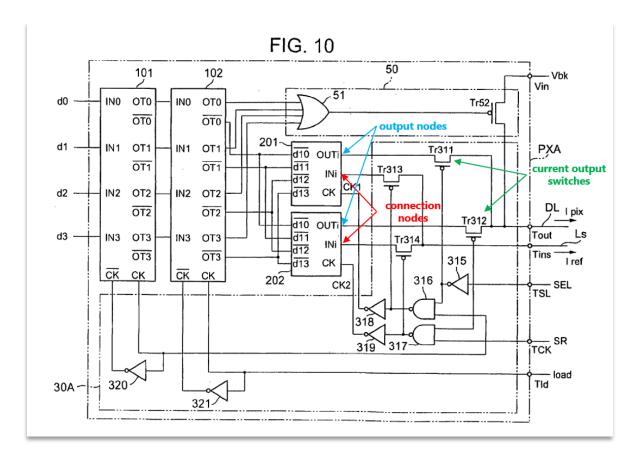

|       |    | d. 1(c): "a plurality of output terminals;"120                                                                                                                                                                                                                                                                                                   |

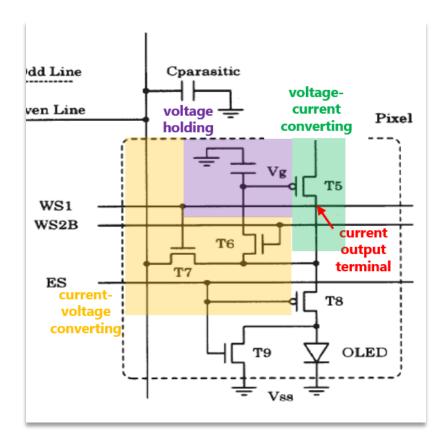

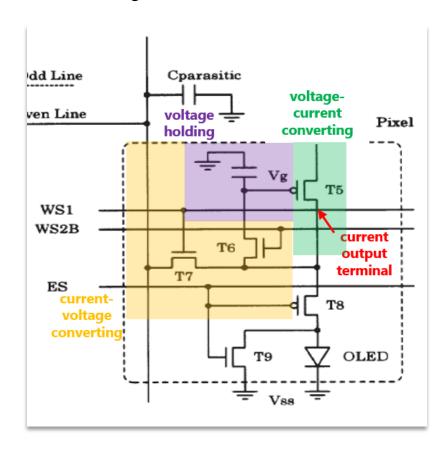

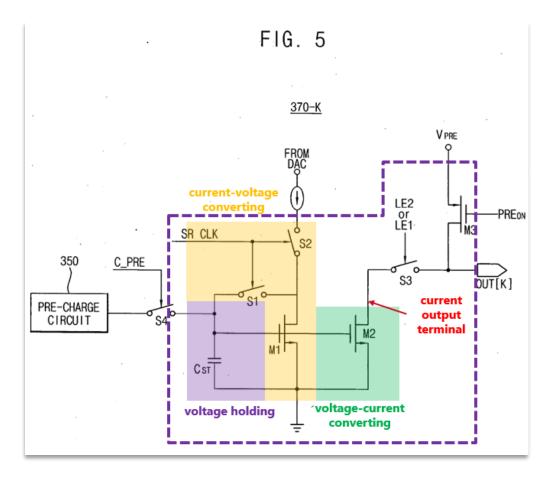

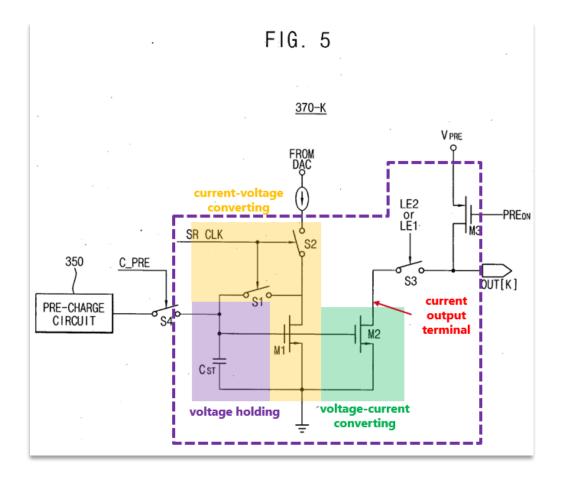

|       |    | e. 1(d)(1): "and a plurality of current output circuits for outputting an electric current in accordance with said first electric current, each of said current output circuits comprising"                                                                                                                                                      |

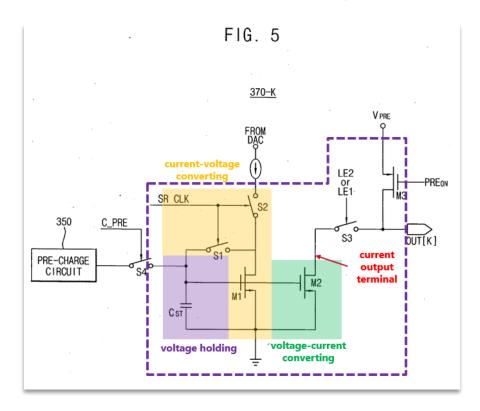

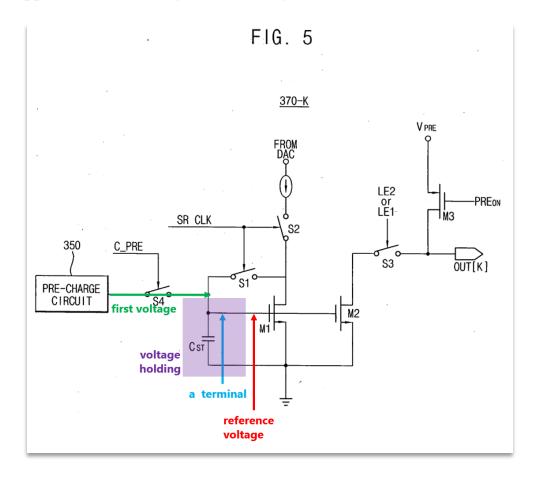

|       |    | f. 1(d)(2) "a current-voltage converting circuit, a voltage-current converting circuit, a voltage holding circuit having a terminal being connected to a reference voltage different from the first voltage, and at least one current output terminal, wherein"                                                                                  |

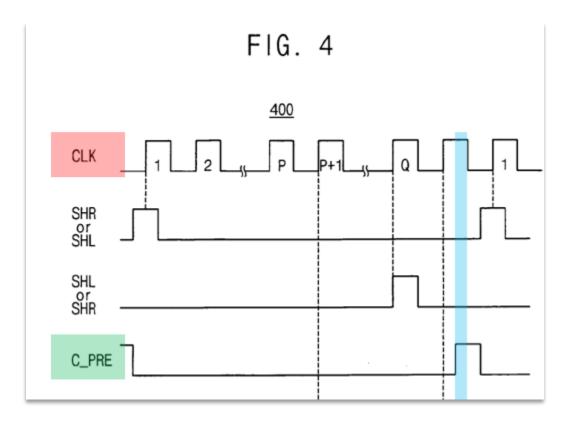

|       |    | <ul> <li>g. 1(e): "each of said current output circuits operates in three operation modes including a voltage supply mode, a current supply mode, and a current output mode,"</li></ul>                                                                                                                                                          |

|       |    | h. 1(f). "under said voltage supply mode, each of said current output circuits receives said first voltage from said first voltage supply source, and the first voltage is supplied to another terminal of said voltage holding circuit,"                                                                                                        |

|       |    | <ul> <li>i. 1(g). "under said current supply mode, each of said current output circuits receives said first current from said first current supply source, and generates a second voltage by said current-voltage converting circuit, and the first current is supplied to said another terminal of said voltage holding circuit, and"</li></ul> |

|       |    | <ul> <li>j. 1(h). "under said current output mode, each of said current output circuits outputs an output current according to said voltage held in said voltage holding circuit by said voltage-current converting circuit."</li> </ul>                                                                                                         |

|       | B. | Claims Depending From Claim 1 of the '047 Patent14                                                                                                                                                                                                                                                                                               |

|       |    | a. "2. The current driving device according to claim 1, wherein: each of said output terminals is connected to said current output                                                                                                                                                                                                               |

|        |    | circuits, and each of said plurality of said current output circuits is connected in parallel to said first current supply source and said first voltage supply source used in common"                                                                                                                                  | 147 |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | b. | "3. The current driving device according to claim 1, wherein, in each of said current output circuits, said current-voltage converting circuit is actuated under said voltage supply mode."                                                                                                                             | 151 |

|        | c. | "4. The current driving device according to claim 1, wherein each of said current output circuits is configured to stop said current-voltage converting circuit under said voltage supply mode."                                                                                                                        | 152 |

|        | d. | "9. A current-driving-type display device, comprising said current driving device according to claim 1 mounted thereon so as to be driven by said current driving device."                                                                                                                                              | 154 |

| XIV. G | R( | OUND 5 & 6: SASAKI                                                                                                                                                                                                                                                                                                      | 155 |

| A.     | In | dependent Claim 10 of the '047 Patent                                                                                                                                                                                                                                                                                   | 155 |

|        | a. | 10(preamble): "A current driving device, comprising:"                                                                                                                                                                                                                                                                   | 155 |

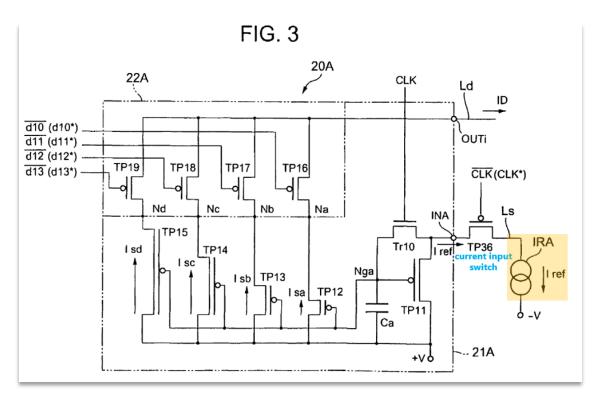

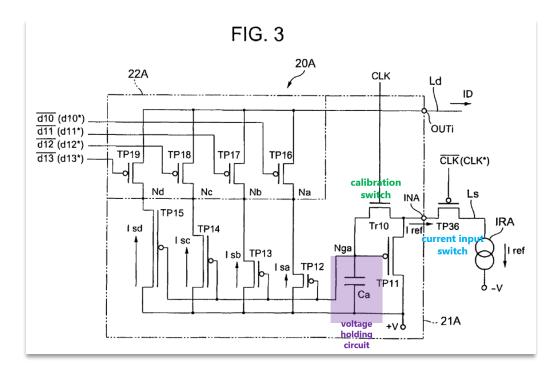

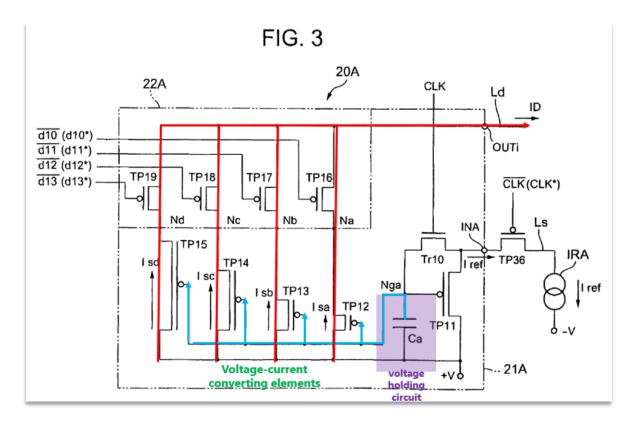

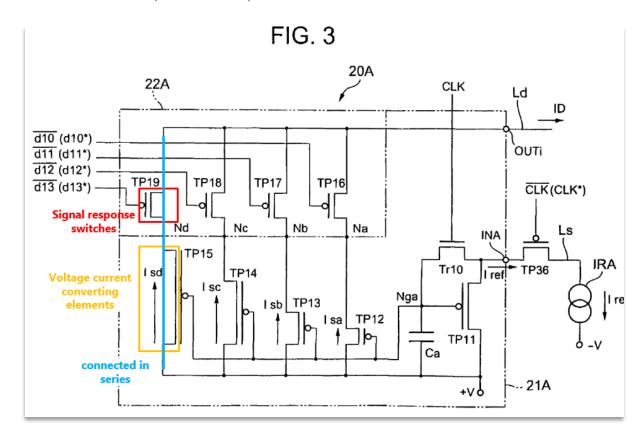

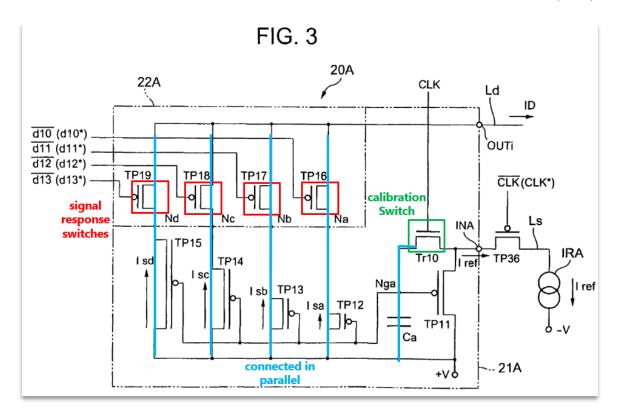

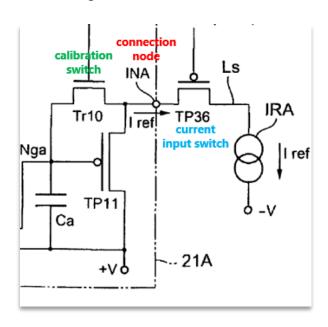

|        | b. | 10(a): "a current input switch for controlling connection/disconnection states with respect to a current supply source;"                                                                                                                                                                                                | 155 |

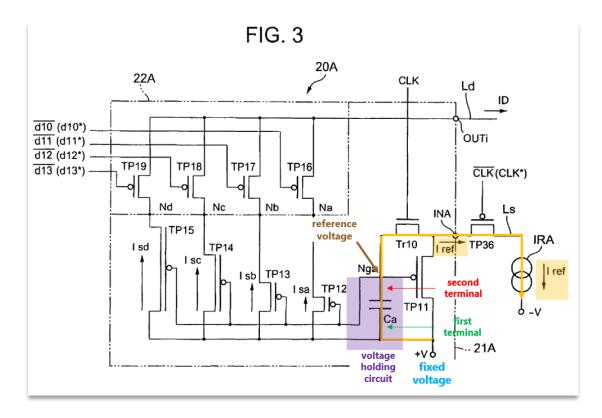

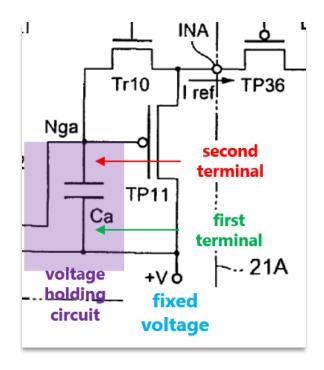

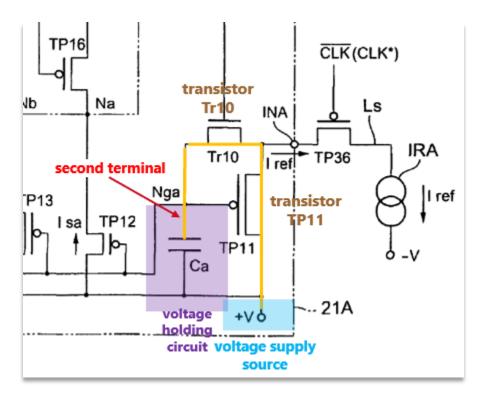

|        | c. | 10(b): "a voltage holding circuit for holding a reference voltage, which is charged by a flown current, the voltage holding circuit having a first terminal and a second terminal, the first terminal being connected to a fixed voltage;"                                                                              | 157 |

|        | d. | 10(c): "a calibration switch interposed between said current input switch and said voltage holding circuit;"                                                                                                                                                                                                            | 160 |

|        | e. | 10(d): "a plurality of voltage-current converting elements for generating an electric current in accordance with said reference voltage held in said voltage holding circuit;"                                                                                                                                          | 162 |

|        | f. | 10(e): "a plurality of signal response switches that are on/off controlled in accordance with inputted signals, each of said response switches being connected in series to a corresponding one of said voltage-current converting elements, and each of which being connected in parallel to said calibration switch;" | 164 |

# Declaration of Dr. Alex Kattamis IPR of USP 7,995,047

| XVI. | CONCLUSION                                                                                                                                                                                                      | 174 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| XV.  | SECONDARY CONSIDERATIONS OF NON-OBVIOUSNESS REGARDING THE CHALLENGED PATENT                                                                                                                                     | 173 |

|      | <ol> <li>10(h): "a high-speed switch for controlling<br/>connection/disconnection states of said voltage supply source<br/>with respect to the second terminal of said voltage holding<br/>circuit."</li> </ol> | 172 |

|      | h. 10(g): "a plurality of current output switches, each being interposed between the connection node and said plurality of current output terminals; and"                                                       | 167 |

|      | g. 10(f): "a connection node provided between said current input switch and said calibration switch;"                                                                                                           | 166 |

#### I. INTRODUCTION

- 1. My name is Alex Kattamis. I make this declaration based upon my own personal knowledge and, if called upon to testify, would testify competently to the matters contained herein.

- 2. I am over the age of 21 and am competent to make this declaration.

- 3. I have been retained by Baker Botts LLP on behalf of Samsung to provide technical assistance in the inter partes review of U.S. Patent No. 7,995,047, which I may abbreviate as "the '047 Patent" or refer to as the "Challenged Patent." This declaration is a statement of my opinions on issues related to the unpatentability of claims of the Challenged Patent.

- 4. I am a salaried employee of Exponent. Exponent charges \$495 per hour for my time plus expenses for work performed in connection with this project. I have received no additional compensation for work in this case, and my compensation does not depend upon the contents of this report, any testimony I may provide, or the ultimate outcome of the case.

# II. EXPERIENCE AND QUALIFICATIONS

5. In formulating my opinions, I have relied upon my knowledge, training, and experience in the relevant art. My qualifications are stated more fully in my curriculum vitae, which has been provided as Appendix A. My CV also lists publications on which I am a named author and identifies parties on behalf of whom

I have previously provided expert testimony within the past four years. Here, I provide a brief summary of my qualifications.

- 6. I am a Senior Managing Engineer in Exponent's Electrical Engineering and Computer Science practice. I received my B.A. in Electrical Engineering from the University of Connecticut in 2002 and an M.A. and Ph.D. in Electrical Engineering from Princeton University in 2004 and 2007 respectively.

- 7. During my time at the University of Connecticut and through a grant from the National Science Foundation I designed and implemented devices for people with disabilities. This included the design and manufacture of analog and digital control systems for devices including go-karts and electronic lifts.

- 8. Before joining Princeton University, I worked as a design engineering intern at General Electric Industrial Systems. There I designed and implemented analog and digital circuits. This work included the implementation of current sense devices for feedback in power supplies

- 9. At Princeton University my research was focused on designing and fabricating pixel circuits on non-conventional substrates for driving liquid-crystal display (LCDs) and active-matrix organic light emitting diode displays (AMOLEDs).

- 10. Throughout my career at Exponent I have worked extensively on AMOLED and LCD displays including driver circuits, and thin-film transistor and pixel architectures.

- 11. I am a licensed Professional Engineer in the State of Connecticut, the State of Georgia, the Commonwealth of Massachusetts, the State of New Jersey, the State of New York, the Commonwealth of Pennsylvania, the State of Rhode Island, and in State of Texas. I am also designated a Model Law Engineer by the National Council of Examiners for Engineering.

- 12. I am a Senior Member of the Institute of Electrical and Electronics Engineers (IEEE), which is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity.

- 13. Therefore, based on my education, professional experience, scholarly books and publications, I am an expert in the relevant field of the Challenged Patent at issue here and have been an expert in this field since before the Challenged Patent was filed with the United States Patent and Trademark Office ("USPTO"). I am familiar with how a person having ordinary skill in the art would have understood and used the terminology found in the Challenged Patent at the time of its filing.

### III. TASK SUMMARY AND MATERIALS REVIEWED

14. I have been asked to review the Challenged Patent and its prosecution history, to provide an understanding of the technology relevant to the Challenged Page 10 of 174

Patent, to review certain prior-art references, and analyze whether or not those references disclose or teach limitations of claims from the Challenged Patent. The opinions stated in this declaration are from the perspective of a person of ordinary skill in the art (POSITA).

#### IV. <u>LIST OF EXHIBITS</u>

15. In forming my opinions, I have reviewed the Challenged Patent, its prosecution history and referenced cited by the Examiner, the materials cited in the List of Exhibits, and the materials cited throughout my declaration.

| Ex.  | Description of Exhibits                                                                                                                                                                                                                                                    |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1001 | U.S. Patent No. 7,995,047 to Makoto Mizuki et al., entitled "Current Driving Device" (filed December 12, 2007 and issued August 9, 2011) ("'047 Patent" or "Challenged Patent")                                                                                            |  |

| 1002 | Declaration of Dr. Alex Kattamis in Support of Petition for <i>Inter Partes</i> Review of U.S. Patent No. 7,995,047, with CV attached as Appendix A ("Kattamis Decl.")                                                                                                     |  |

| 1003 | File History of U.S Patent No. 7,995,047 (App. No. 11/954,659) ("'047 Patent File History")                                                                                                                                                                                |  |

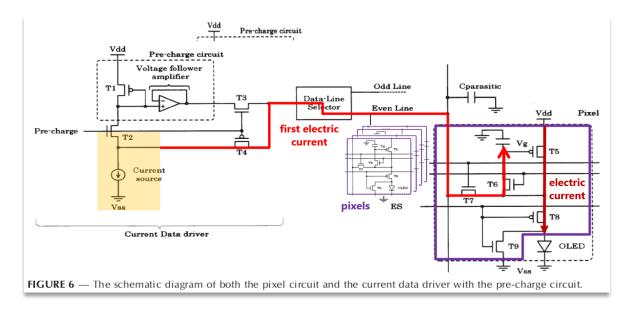

| 1004 | M. Shimoda, K. Abe, H. Haga, H. Asada, H. Hayama, K, Iguchi, D. Iga, H. Imura, and S. Miyano, "An integrated poly-Si TFT current data driver with a data-line pre-charge function," <i>Journal of the Society for Information Display</i> 11/3 (2003): 461-466 ("Shimoda") |  |

| 1005 | U.S. Patent Publication No. 2006/0170629 to Jong-Hak Baek, entitled "Display Driver Circuit, Current Sample/Hold Circuit and Display Driving Method Using the Display Driver Circuit" (filed January 27, 2006 and published August 3, 2006) ("Baek")                       |  |

| 1006          | U.S. Patent Publication No. 2005/0017765 to Kazuhiro Sasaki and Katsuhiko Morosawa, entitled ""Current Generation Supply Circuit and Display Device" (filed July 14, 2004 and published January 27, 2005 ("Sasaki")                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1007          | John A. Camara, ELECTRICAL ENGINEERING REFERENCE MANUAL FOR THE ELECTRICAL AND COMPUTER PE EXAM, 6th ed. (Professional Publications, Inc.: 2002), ISBN: 1-888577-56-8 ("Camara")                                                          |

| 1008          | Willem den Boer, ACTIVE MATRIX LIQUID CRYSTAL DISPLAYS, 1st ed. (Newnes: 2005), ISBN: 0-750678-13-5 ("den Boer")                                                                                                                          |

| 1009          | M.K. Han, "AM backplane for AMOLED," <i>Proc. Of ASID</i> <b>6</b> (Oct. 8-12, 2006): 53-58 ("Han")                                                                                                                                       |

| 1010          | B. Hekmatshoar, A. Kattamis et al., "A Novel TFT-OLED integration for OLED-independent pixel programming in amorphous-Si AMOLED pixels," <i>Journal of the Society for Information Display</i> <b>16/1</b> (2008): 183-188.               |

| 1011          | A. Kattamis et al., "Active-matrix organic light-emitting displays employing two thin-film-transistor a-Si:H pixels on flexible stainless-steel foil," <i>Journal of the Society for Information Display</i> <b>15/7</b> (2007): 433-437. |

| 1012          | About the SID (dated June 16, 2004), available at: <a href="https://web.archive.org/web/20040616180753/http://www.sid.org/about/about.html">https://web.archive.org/web/20040616180753/http://www.sid.org/about/about.html</a>            |

| 1013-<br>1018 | Not Used                                                                                                                                                                                                                                  |

| 1019          | Declaration of Dr. James L. Mullins sponsoring Exhibit 1004 and Exhibits 1020-1027 ("Mullins Decl.")                                                                                                                                      |

| 1020          | Copy of Shimoda owned by the Linda Hall Library                                                                                                                                                                                           |

| 1021          | Copy of Shimoda owned by the United States Library of Congress                                                                                                                                                                            |

| 1022          | WorldCat entry for Journal of the Society for Information Display (Missouri)                                                                                                                                                              |

| 1023          | WorldCat entry for Journal of the Society for Information Display (Washington, DC)                                                                                                                                                        |

| 1024 | OPAC record from Linda Hall Library for Journal of the Society for Information Display                                                                                                       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1025 | OPAC record from United States Library of Congress for Journal of the Society for Information Display                                                                                        |

| 1026 | J.L. Sanford and F.R. Libsch, "V <sub>t</sub> compensated voltage-data a-Si TFT AMOLED pixel circuits," <i>Journal of the Society for Information Display</i> 11/1 (2004): 65-73 ("Sanford") |

| 1027 | YS. Son, SK. Kim, YJ. Jeon et al., "P-40: A Novel Data Driving Method and Circuits for AMOLED Displays," <i>SID Symposium Digest of Technical Papers</i> <b>37</b> (2006): 343-346 ("Son")   |

Other than the prosecution history, Ex. 1003, respectively, all citations to exhibits reference original page numbers found in the underlying document, and unless noted, all emphases have been added.

## V. <u>SUMMARY OF CONCLUSIONS AND GROUNDS FOR</u> CHALLENGE OF '047 PATENT

16. After reviewing the materials identified in the List of Exhibits, I have concluded that each of Claims 1-4, 9, and 10 ("Challenged Claims") of the '047 Patent would have been anticipated and/or obvious to a person of ordinary skill in the art, based on the following grounds.

| Ground | '047 Patent Claims | Basis for Invalidity                           |

|--------|--------------------|------------------------------------------------|

| 1      | 1-4, 9             | Anticipated by Shimoda (Ex. 1004)              |

| 2      | 1-4, 9             | Obvious over Shimoda (Ex. 1004) in view of the |

|        |                    | knowledge of a POSITA                          |

| 3      | 1-4, 9             | Anticipated by Baek (Ex. 1005)                 |

| 4      | 1-4, 9             | Obvious over Baek (Ex. 1005) in view of the    |

|        |                    | knowledge of a POSITA                          |

| 5      | 10                 | Anticipated by Sasaki (Ex. 1006)               |

| Ground | '047 Patent Claims | Basis for Invalidity           |

|--------|--------------------|--------------------------------|

| 6      | 10                 | Obvious over Sasaki (Ex. 1006) |

#### VI. <u>UNDERSTANDING OF THE GOVERNING LAW</u>

#### A. LEVEL OF ORDINARY SKILL IN THE ART

- 17. When analyzing a patent, I understand that it is important to identify the relevant art pertaining to the patent as well as the level of ordinary skill in that art at the time of the claimed invention. The "art" is the field of technology to which the patent is related.

- 18. I have been instructed by counsel that the person of ordinary skill in the art ("POSITA") is a hypothetical person who is presumed to know the relevant prior art. I understand that the actual inventor's skill is not determinative of the level of ordinary skill. I further understand that the factors that may be considered in determining the level of skill include: the types of problems encountered in the art; prior art solutions to those problems; rapidity with which innovations are made; sophistication of the technology; and educational level of active workers in the field. I understand that not all such factors may be present in every case, and one or more of them may predominate.

#### B. LEGAL STANDARD FOR CLAIM CONSTRUCTION

- 19. I understand that the first step in determining whether a patent claim would have been anticipated or obvious is to ascertain how a POSITA would have understood the claim terms.

- 20. I have been instructed by counsel on the law regarding claim construction and patent claims, and I understand that a patent may include two types of claims: independent claims and dependent claims. An independent claim stands alone and includes only the limitations it recites. A dependent claim can depend from an independent claim, or it can further depend from another dependent claim. I understand that a dependent claim includes all the limitations that it recites, in addition to all the limitations recited in the claim(s) from which it depends.

- 21. It is my understanding that in proceedings before the USPTO, the claims of a patent are to be construed under what is referred to as the "Phillips standard." I understand that this means that claim terms of a patent are given the meaning the terms would have to a POSITA, in view of the description provided in the patent itself and the patent's file history.

- 22. I understand that to determine how a person of ordinary skill would understand a claim term, one should look to those sources available that show what a person of skill in the art would have understood the disputed claim language to mean. I understand that, in construing a claim term, one looks primarily to the Page 15 of 174

intrinsic patent evidence, including the words of the claims themselves, the remainder of the patent, and the patent's prosecution history. I understand that extrinsic evidence, which is evidence external to the patent and the prosecution history, may also be useful in interpreting patent claims when the intrinsic evidence itself is insufficient.

- 23. I understand that words or terms should be given their ordinary and accepted meaning unless it appears that the inventors were using them to mean something else. In making this determination, the claims, the remainder of the patent, and the prosecution history are of paramount importance. Additionally, the patent and its prosecution history must be consulted to confirm whether the patentee has acted as its own lexicographer (i.e., provided its own special meaning to any disputed terms), or intentionally disclaimed, disavowed, or surrendered any claim scope.

- 24. In comparing the claims of the Challenged Patent to the prior art, I have considered the Challenged Patent and its file history in light of the understanding of a person of skill at the time of the alleged invention.

## C. ANTICIPATION

25. It is my understanding that the claims of a patent are anticipated by a prior art reference if each and every element of the claim is found either explicitly or inherently in a single prior art reference. I understand that inherency requires a Page 16 of 174

showing that the missing descriptive matter in the claim is necessarily or implicitly present in the allegedly anticipating reference, and that it would have been so recognized by a POSITA. In addition, I understand that an enabling disclosure is a disclosure that allows a POSITA to make the invention without undue experimentation. Although anticipation typically involves the analysis of a single prior art reference, I understand that additional references may be used to show that the primary reference has enabling disclosure, to explain the meaning of a term used in the primary reference, and/or to show that a characteristic is inherent in the primary reference.

#### D. <u>OBVIOUSNESS</u>

26. I understand that the prior art may render a patent claim "obvious." I understand that two or more prior art references (e.g., prior art articles, patents, or publications) that each disclose fewer than all elements of a patent claim may nevertheless be combined to render a patent claim obvious if the combination of the prior art collectively discloses all elements of the claim and one of ordinary skill in the art at the time would have been motivated to combine the prior art in such a way. I understand that this motivation to combine need not be explicit in any of the prior art, but may be inferred from the knowledge of one of ordinary skill in the art at the time the patent was filed. I also understand that one of ordinary skill in the art is not an automaton, but is a person having ordinary creativity. I further understand that

one or more prior art references, articles, patents or publications that disclose fewer than all of the elements of a patent claim may render a patent claim obvious if including the missing element would have been obvious to one of skill in the art (e.g., the missing element represents only an insubstantial difference over the prior art or a reconfiguration of a known system).

- 27. I understand that under the doctrine of obviousness, a claim may be invalid if the differences between the invention and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a POSITA to which the subject matter pertains.

- 28. To assess obviousness, I understand that I am to consider the scope and content of the prior art, the differences between the prior art and the claim, the level of ordinary skill in the art, and any secondary considerations to the extent they exist.

- 29. I understand that any evidence of secondary indicia of non-obviousness should be considered when evaluating whether a claimed invention would have been obvious to one of ordinary skill at the time of invention. These secondary indicia of non-obviousness may include, for example:

- a long felt but unmet need in the prior art that was satisfied by the claimed invention;

- commercial success of processes claimed by the patent;

- unexpected results achieved by the invention;

- praise of the invention by others skilled in the art;

- the taking of licenses under the patent by others; and

- deliberate copying of the invention.

I understand that there must be a nexus between any such secondary indicia and the claimed invention.

- 30. It is also my understanding that there are additional considerations that may be used as further guidance as to when the above factors will result in a finding that a claim is obvious, including the following:

- the claimed subject matter is simply a combination of prior art elements according to known methods to yield predictable results;

- the claimed subject matter is a simple substitution of one known element for another to obtain predictable results;

- the claimed subject matter uses known techniques to improve similar devices or methods in the same way;

- the claimed subject matter applies a known technique to a known device or method that is ready for improvement to yield predictable results;

- the claimed subject matter would have been "obvious to try" choosing from a finite number of identified, predictable solutions, with a reasonable expectation of success;

- there is known work in one field of endeavor that may prompt variations of it for use in either the same field or a different one based on design incentives or other market forces if the variations would have been predictable to a POSITA;

- there existed at the time of the invention a known problem for which there was an obvious solution encompassed by the patent's claims; and

- there is some teaching, suggestion, or motivation in the prior art that would have led a POSITA to modify the prior art reference or to combine prior art reference teachings to arrive at the claimed subject matter.

- 31. Finally, I understand that a claim may be deemed invalid for obviousness in light of a single prior art reference, without the need to combine references, if the elements of the claim that are not found in the reference can be supplied by the knowledge or common sense of one of ordinary skill in the relevant art.

#### VII. OVERVIEW OF THE '047 PATENT

32. I have reviewed U.S. Patent No. 7,995,047 ("the '047 Patent"), which is entitled "Current Driving Device." Ex. 1001.

#### A. PRIORITY DATE FOR CLAIMS OF THE '047 PATENT

33. I understand that the '047 Patent was filed on December 12, 2007, and that it was issued on August 9, 2011. The '047 Patent claims priority to an application filed in Japan on December 13, 2006. I understand that, regardless of whether the priority date of the '047 Patent is December 12, 2007 (corresponding to its U.S. filing date) or December 13, 2006 (corresponding to the filing date of the Japanese application), the references I rely on qualify as prior art.

#### B. THE SUBJECT MATTER OF THE '047 PATENT

- 34. The '047 Patent is directed to a "current driving device" for use as a "driver for displays such as organic EL (Electro-luminescence) panels, LED panels, and the like." Ex. 1001 ('047 Patent) 1:5-7.

- 35. As discussed in the "Background of the Invention" section, the '047 Patent recognizes a known problem in the prior art. For large screen displays with increasing definition, variations in electric currents "due to fabrication processes of each transistor, variations of gate voltages" and the "resistance of power supply wiring" cause non-uniformity in the display image. Ex. 1001 ('047 Patent) 1:17-20. The '047 Patent recognizes that, in order to ensure image uniformity "it is required for display drivers to improve the uniformity in the displayed images qualities through decreasing variations between output electric currents that are outputted from output terminals." Ex. 1001 ('047 Patent) 1:13-16.

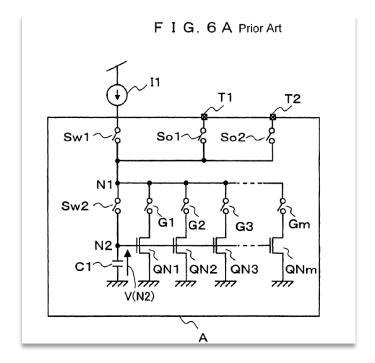

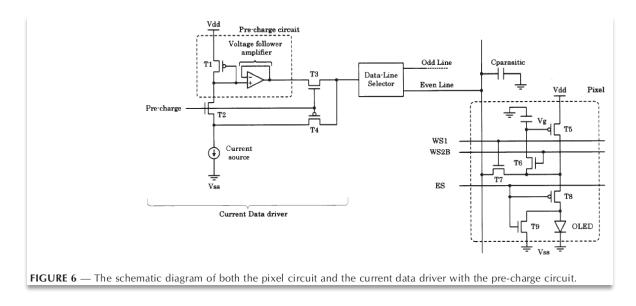

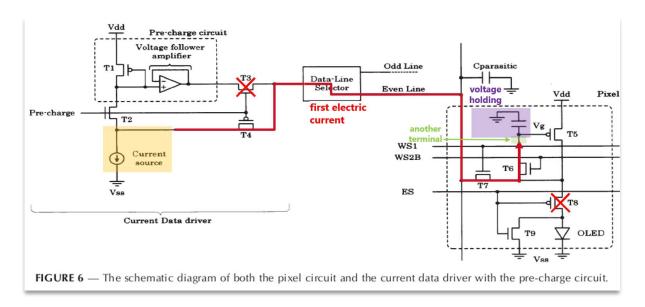

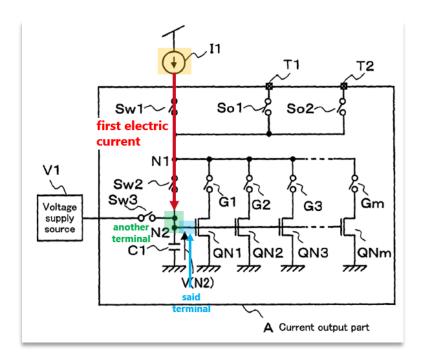

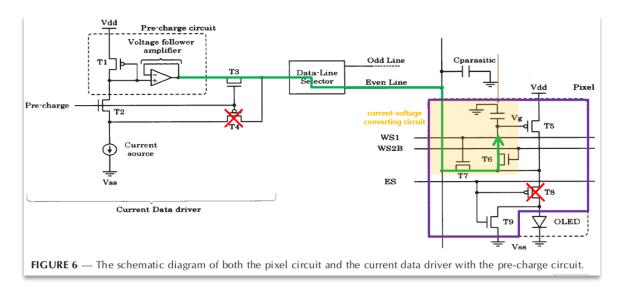

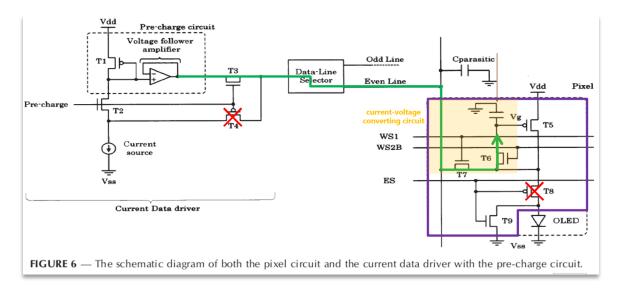

- 36. The '047 Patent discloses a known solution in the prior art for "decreasing such variations," which includes the "current output part" as shown below in Figure 6A, further including "a calibration function and a current output function." Ex. 1001 ('047 Patent) 1:33-39.

As can be seen in the caption of the figures, Figure 6A is labeled with a caption that recognizes that it is "Prior Art."

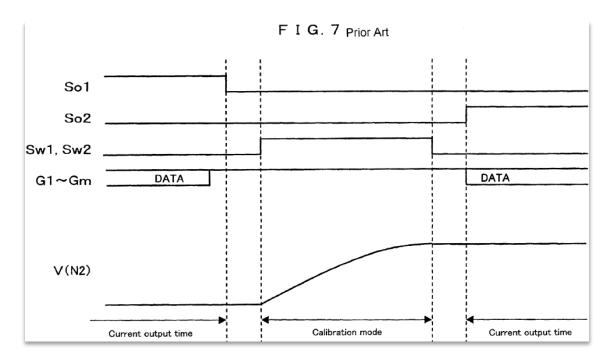

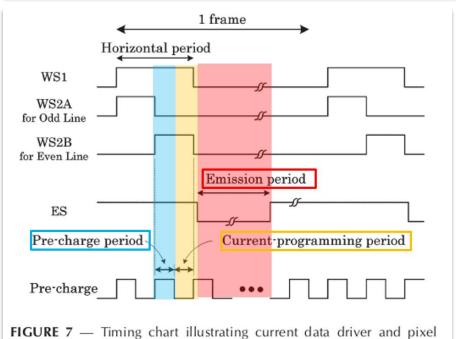

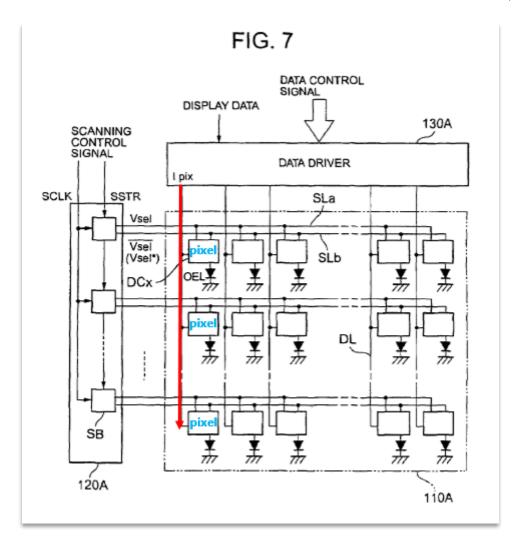

37. As shown in Figure 7, which is also labeled "Prior Art," the '047 Patent acknowledges that it was known in the prior art to have two modes of operation for the device shown in Figure 6A: "calibration mode" and "current output mode."

Ex. 1001 ('047 Patent) at Fig. 7; 2:8-13.

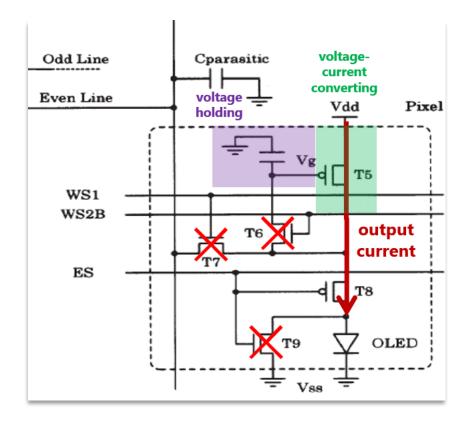

38. During operation of the prior art "calibration mode," the transistors are operated to allow "the electric current from the reference source I1 to flow through the transistors themselves. A voltage holding capacitance element C1 is charged to the above-described gate voltage." Ex. 1001 ('047 Patent) 1:40-51. This calibration mode is comprised of a current supply mode. Ex. 1001 ('047 Patent) 1:37-39, *see also* Fig. 6A. As was known in the art, the '047 Patent recognizes that a purpose of charging a capacitor (e.g., voltage holding capacitance element C1) is to store a voltage to enable each QN1-QNm transistor to stay on while passing a desired amount of current such that combinations of currents from QN1-QNm are used to drive a pixel element.

- 39. During operation of the prior art "current output mode ... [t]he voltage holding capacitance element C1 holds the voltage charged by the calibration ... [and] Nch transistors QN1-QNm output an electric current ... from one (in an [sic] conductive state) of the current output terminals T1 and T2, in accordance with the conduction state of the signal response switches G1-Gm." Ex. 1001 ('047 Patent) 1:60-2:7, *see also id.* Fig. 6A.

- 40. Pixel luminance levels are determined by the bit depth or color depth of a particular display. For example, a display with 8 bits of data for blue sub-pixel has 256 potential luminance levels for the blue sub-pixel. Since the amount of light emitted (or luminance) by an organic electroluminescence diode or OLED is directly proportional to the current flowing through the device, there are 256 current values that are necessary to drive a blue sub-pixel.

- 41. The '047 Patent describes how these 256 current values may be created using combinations of current output from QN1-QNm transistors that each output a set current. Therefore, the QN1-QNm transistors should be accurately set or calibrated by adequately charging C1 within a set amount of time such that they can output a desired current; otherwise, the color output of pixels will vary and reduce the display color quality. The appropriate charging of C1 to a particular voltage affects current flow through each transistor QN1-QNm, because C1 sets the gate voltage on the transistors which controls the current flow through the transistors.

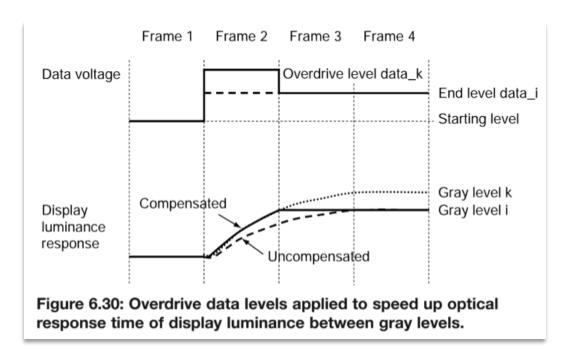

- 42. Still in the "Background of the Invention" section, the '047 Patent describes a known shortcoming with the two modes of operation, in that the ability of a reference current to charge the holding capacitive element "becomes insufficient when the current value of the refence current source I1 is very small." Ex. 1001 ('047 Patent) 3:1-9, *see also* Fig. 6A. This means that it takes longer to charge the holding capacitor, which limits the speed at which the display screen can be refreshed. Furthermore, an incorrect voltage on the holding capacitor will cause the pixels to produce an incorrect luminance and color, because the current driver will output an inaccurate drive current. Overall, the display quality will be low if luminance and color cannot be reproduced accurately across millions of pixels in a flat panel display.

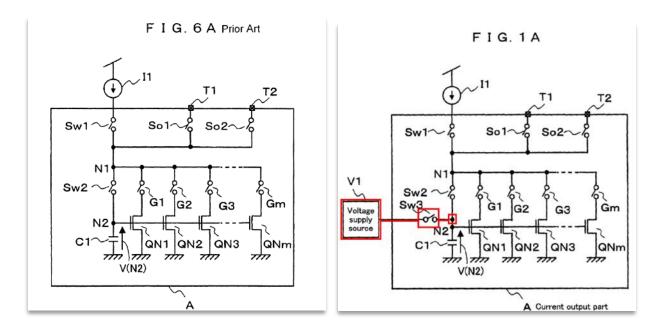

- 43. Thus, the '047 Patent proposes a solution to these known problems, so that "a current driving device ... can perform calibration at a high speed and improve the non-uniformity of the output currents even when a reference current is very small and when there is a change in the reference current." Ex. 1001 ('047 Patent) at 3:16-21. The '047 Patent purports to improve upon the prior art (Fig. 6A) by including a voltage supply source, which was already known in the art a "pre-charge circuit." Figure 6A (admitted prior art) and Figure 1A of the '047 Patent are shown side-by-side, with highlighting added to Figure 1A to show the additional components added.

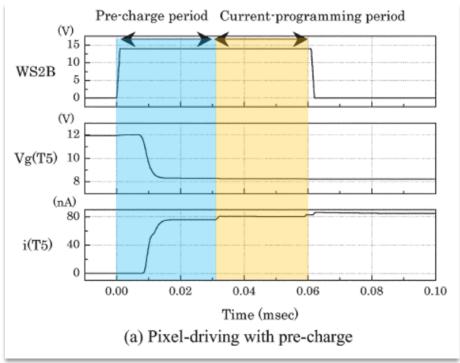

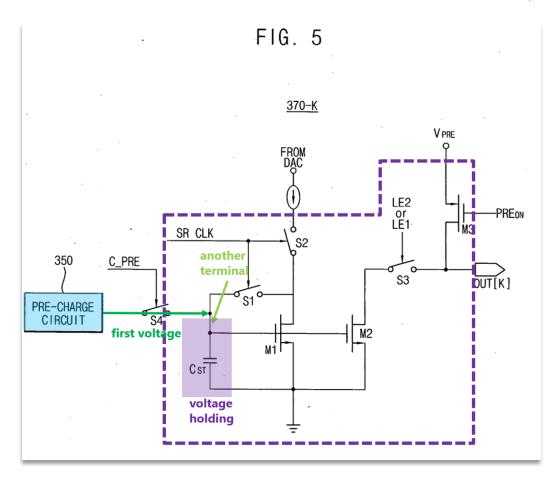

Ex. 1001 ('047 Patent) at Fig. 1, Fig. 6A (annotated). As can be seen, the only addition to the prior art circuit diagram is a voltage supply source (i.e., a pre-charge circuit) and a switch for connecting and disconnecting the voltage-supply source to the circuit (Sw3). As described in the substantive grounds, pre-charge circuits were also known in the prior art and were included in circuits to solve the same known problems discussed in the '047 Patent.

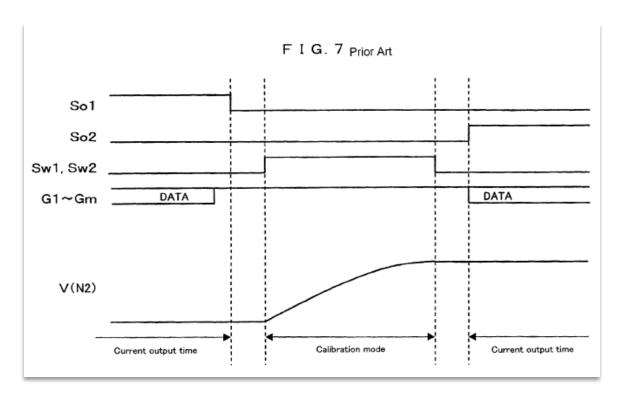

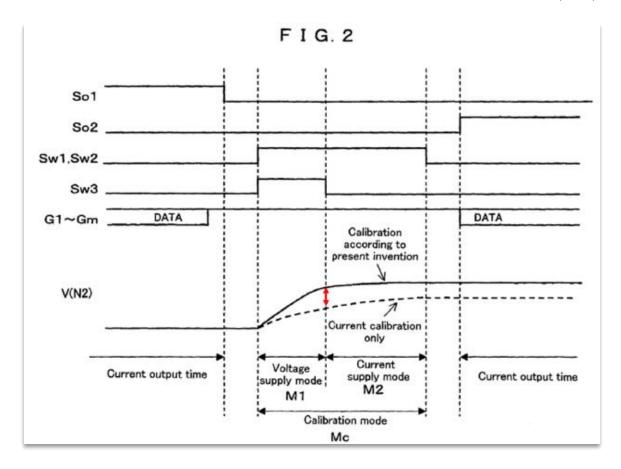

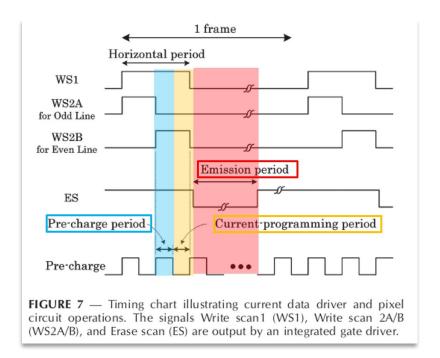

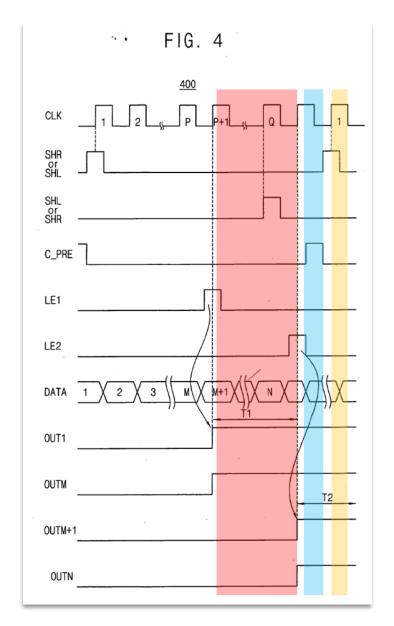

44. Along with the voltage supply source, the '047 Patent discloses an additional mode of operation referred to as a "voltage supply mode." This voltage supply mode occurs prior to a current supply mode, and acts to pre-charge the capacitor (C1) to a certain level. Together the voltage supply mode and the current supply mode constitute the new "calibration mode" disclosed in the '047 Patent. Figure 2 of the '047 Patent discloses "three operation modes (the voltage supply

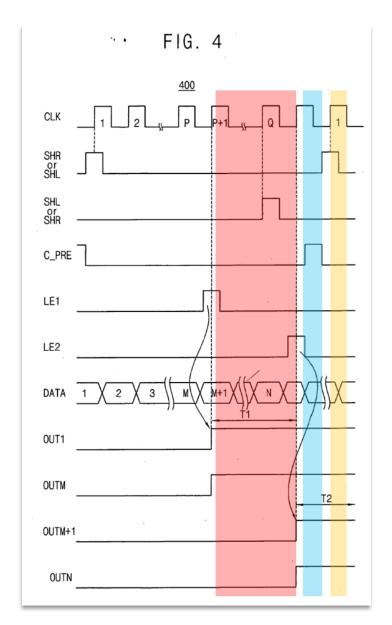

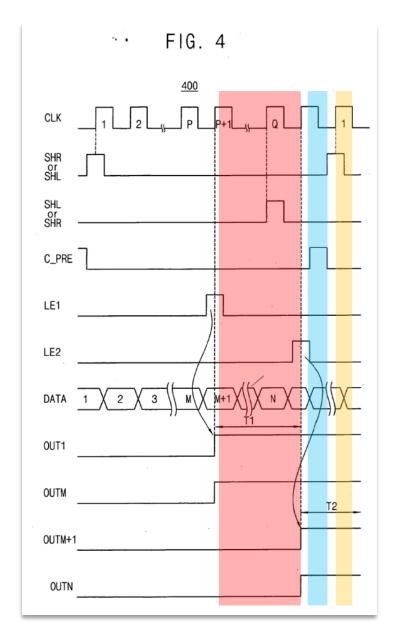

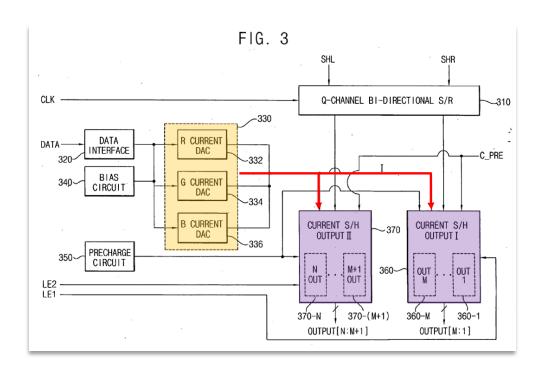

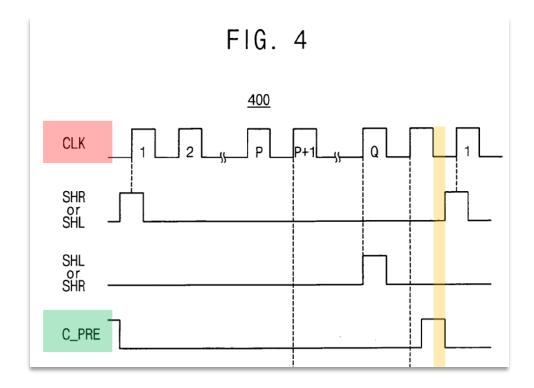

mode M1, the current supply mode M2, and the current output mode M3)." Ex. 1001 ('047 Patent) 9:32-34. This voltage supply mode is a pre-charging mode where a voltage source, as opposed to a current source, is used to charge capacitor C1. Accordingly, the '047 Patent teaches a current driving device with a pre-charge function that reduces the time needed for charging a capacitor and thus "can perform calibration at a high speed and improve the non-uniformity of the output currents even when a reference current is very small." Ex 1001 ('047 Patent) 3:19-22.

45. Figure 7 (admitted prior art) and Figure 2 of the '047 Patent are shown side-by-side, with highlighting added to Figure 2 to show the increased rate at which the capacitor is charged by the voltage supply mode.

Ex. 1001 ('047 Patent) at Fig. 7, 2:8-13. But as I describe in the substantive grounds, charging the capacitor in two phases—voltage supply and current supply—was also known in the prior art.

# C. THE CHALLENGED CLAIMS OF THE '047 PATENT

46. Claims 1-4, 9, and 10 of the '047 Patent ("Challenged Claims") are set forth below. I understand that claims 2, 3 and 9 depend from claim 1 and therefore include all of the limitations from claim 1. In the table below, some of the claim elements have been further sub-divided for ease of reference.

| Claim<br>Element | Claim Language from '047 Patent                                                                                                                                                                                                                                                                                    |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1(pre)           | 1. A current driving device, comprising:                                                                                                                                                                                                                                                                           |  |

| 1(a)             | a first voltage supply source for supplying a first voltage;                                                                                                                                                                                                                                                       |  |

| 1(b)             | a first current supply source for supplying a first electric current;                                                                                                                                                                                                                                              |  |

| 1(c)             | a plurality of output terminals; and                                                                                                                                                                                                                                                                               |  |

| 1(d)(1)          | a plurality of current output circuits for outputting an electric current in accordance with said first electric current, each of said current output circuits comprising                                                                                                                                          |  |

| 1(d)(2)          | a current-voltage converting circuit, a voltage-current converting circuit, a voltage holding circuit having a terminal being connected to a reference voltage different from the first voltage, and at least one current output terminal, wherein:                                                                |  |

| 1(e)             | each of said current output circuits operates in three operation modes including a voltage supply mode, a current supply mode, and a current output mode,                                                                                                                                                          |  |

| 1(f)             | under said voltage supply mode, each of said current output circuits receives said first voltage from said first voltage supply source, and the first voltage is supplied to another terminal of said voltage holding circuit, and                                                                                 |  |

| 1(g)             | under said current supply mode, each of said current output circuits receives said first current from said first current supply source, and generates a second voltage by said current-voltage converting circuit, and the first current is supplied to said another terminal of said voltage holding circuit, and |  |

| 1(h)             | under said current output mode, each of said current output circuits outputs an output current according to said voltage held in said voltage holding circuit by said voltage-current converting circuit.                                                                                                          |  |

| 2                | 2. The current driving device according to claim 1, wherein: each of said output terminals is connected to said current output terminals provided to                                                                                                                                                               |  |

| Claim<br>Element | Claim Language from '047 Patent                                                                                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | said plurality of said current output circuits, and each of said plurality of current output circuits is connected in parallel to said first current supply source and said first voltage supply source used in common                                                                                         |

| 3                | 3. The current driving device according to claim 1, wherein, in each of said current output circuits, said current-voltage converting circuit is actuated under said voltage supply mode.                                                                                                                      |

| 4                | 4. The current driving device according to claim 1, wherein each of said current output circuits is configured to stop said current-voltage converting circuit under said voltage supply mode.                                                                                                                 |

| 9                | 9. A current-driving-type display device, comprising said current driving device according to claim 1 mounted thereon so as to be driven by said current driving device.                                                                                                                                       |

| 10(pre)          | 10. A current driving device, comprising:                                                                                                                                                                                                                                                                      |

| 10(a)            | a current input switch for controlling connection/disconnection states with respect to a current supply source;                                                                                                                                                                                                |

| 10(b)            | a voltage holding circuit for holding a reference voltage, which is charged<br>by a flown current, the voltage holding circuit having a first terminal and a<br>second terminal, the first terminal being connected to a fixed voltage;                                                                        |

| 10(c)            | a calibration switch interposed between said current input switch and said voltage holding circuit;                                                                                                                                                                                                            |

| 10(d)            | a plurality of voltage-current converting elements for generating an electric current in accordance with said reference voltage held in said voltage holding circuit;                                                                                                                                          |

| 10(e)            | a plurality of signal response switches that are on/off controlled in accordance with inputted signals, each of said response switches being connected in series to a corresponding one of said voltage-current converting elements, and each of which being connected in parallel to said calibration switch; |

| Claim<br>Element | Claim Language from '047 Patent                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10(f)            | a connection node provided between said current input switch and said calibration switch;                                                                              |

| 10(g)            | a plurality of current output switches, each being interposed between the connection node and said plurality of current output terminals; and                          |

| 10(h)            | a high-speed switch for controlling connection/disconnection states of said voltage supply source with respect to the second terminal of said voltage holding circuit. |

#### D. PROSECUTION HISTORY OF THE '047 PATENT

#### a. Originally Filed Claims on December 12, 2007

- 47. What ultimately issued as the '047 Patent was filed on December 12, 2007 in the USPTO as Application No. 11/954,659. The application was originally filed with ten claims: independent claim 1, dependent claims 2-9 (depending from claim 1), and independent claim 10. The text of the claims is copied below:

- A current driving device, comprising:

a first voltage supply part for supplying a first voltage;

a first current supply part for supplying a first electric current;

- a plurality of output terminals; and

- a plurality of current output parts for outputting an electric current in accordance with said first electric current, each of said current output parts comprising a current-voltage converting function, a voltage-current converting function, a voltage holding part, and at least one current output terminal, wherein

said current output part takes three operation modes, i.e. a voltage supply mode, a current supply mode, and a current output mode,

under said voltage supply mode, said current output part receives said first voltage from said first voltage supply part and holds said voltage in said voltage holding part,

under said current supply mode, said current output part receives said first current from said first current supply part, and generates a second voltage by said current-voltage converting function and holds said voltage in said voltage holding part, and

under said current output mode, said current output part outputs an output current according to said voltage held in said voltage holding part by said voltage-current converting function.

- 2. The current driving device according to claim 1, wherein each of said output terminals is connected to said current output terminals provided to said plurality of said current output parts, and each of said plurality of current output parts is connected in parallel to said first current supply part and said first voltage supply part used in common.

- 3. The current driving device according to claim 1, wherein each of said current output parts actuates said current-voltage converting function under said voltage supply mode.

- 4. The current driving device according to claim 1, wherein each of said current output parts comprises a function of stopping said current-voltage converting function under said voltage supply mode.

- The current driving device according to claims 1, further comprising

- a second current supply part for supplying a second electric current that is proportional to said first electric current, and

- a current-voltage converting part for generating said first voltage by receiving said second electric current, wherein

said first voltage supply part controls supplies of said first voltage generated by said current-voltage converting part to said current output parts.

- 6. The current driving device according to claim 5, wherein said current-voltage converting part comprises a switching part for short-circuiting a node at which said first voltage emerges to a reference voltage node.

- 7. The current driving device according to claims 1, further comprising a second voltage supply part with a larger voltage supply capacity than that of said first voltage supply part, wherein

the use of said first voltage supply part and the use of said second voltage supply part are switched in accordance with the number of said current output parts that take said voltage supply mode among said plurality of current output parts.

The current driving device according to claims 1, wherein

said first voltage supply part is constituted to be capable of changing its voltage supply capacity in accordance with the number of said current output parts that take said voltage supply mode among said plurality of current output parts.

- 9. A current-driving-type display device, comprising said current driving device according to claims 1 mounted thereon so as to be driven by said current driving device.

- 10. A current driving device, comprising:

- a current input switch for controlling connection/

disconnection states with respect to a current supply part;

- a voltage holding part for holding a reference voltage, which is charged by a flown current;

- a calibration switch interposed between said current input switch and said voltage holding part;

- a plurality of voltage-current converting elements for generating an electric current in accordance with said reference voltage held in said voltage holding part;

- a plurality of signal response switches that are on/off controlled in accordance with inputted signals, said response switches being connected in series to each of said voltage-current converting elements, and each of which being connected in parallel to said calibration switch;

- a plurality of current output switches, each being interposed between a connection node, which is provided between said current input switch and said calibration switch, and said plurality of current output terminals; and

- a high-speeding switch for controlling connection/ disconnection states of said voltage supply part with respect to said voltage holding part.

Ex. 1003 ('047 Patent File History, 12/12/2007 Original Claims) at 139-144.

#### b. USPTO Examiner Issues Office Action on December 8, 2010

48. The USPTO Examiner issued an office action on December 8, 2010. In that Office Action, the Examiner requested that corrected drawings be presented in which "Figures 6A, 6B, and 7-9 should be designated by a legend such as—Prior Art—because only that which is old is illustrated." Ex. 1003 ('047 Patent File History, 12/8/2010 Office Action) at 49. The Examiner rejected claims 1-10 as anticipated by Date, U.S. Patent No. 7,466,166. The Examiner also rejected claims 1-10 as anticipated by Hashido, U.S. Patent No. 7,221,349.

#### c. Applicants Respond to Office Action on March 7, 2011

49. On March 7, 2011, the Applicants responded to the Examiner by agreeing that Figs. 6A, 6B, and 7-9 were in the prior art and changing the labels on those figures. Ex. 1003 ('047 Patent File History, 3/7/2011 Resp. to Office Action) at 35. The applicants amended the claims as follows:

- 1. (Currently Amended) A current driving device, comprising:

- a first voltage supply [[part]] source for supplying a first voltage;

- a first current supply [[part]] source for supplying a first electric current;

- a plurality of output terminals; and

- a plurality of current output [[parts]] <u>circuits</u> for outputting an electric current in accordance with said first electric current, each of said current output [[parts]] <u>circuits</u> comprising a current-voltage converting <u>function</u> <u>circuit</u>, a voltage-current converting <u>function</u> <u>circuit</u>, a voltage holding [[part]] <u>circuit having a terminal being connected to a reference voltage different from the first voltage</u>, and at least one current output terminal, wherein:

<u>each of said current output part takes circuits operates in three operation modes [[, i.e.]]</u>

<u>including a voltage supply mode, a current supply mode, and a current output mode,</u>

under said voltage supply mode, <u>each of</u> said current output [[part]] <u>circuits</u> receives said first voltage from said first voltage supply [[part]] <u>source</u>, and <u>holds said voltage in the first voltage</u> <u>is supplied to another terminal of</u> said voltage holding [[part]] <u>circuit</u>,

under said current supply mode, <u>each of</u> said current output [[part]] <u>circuits</u> receives said first current from said first current supply [[part]] <u>source</u>, and generates a second voltage by said current-voltage converting <u>function circuit</u>, and <u>holds said voltage in the first current is supplied to said another terminal of said voltage holding [[part]] <u>circuit</u>, and</u>

under said current output mode, <u>each of</u> said current output [[part]] <u>circuits</u> outputs an output current according to said voltage held in said voltage holding [[part]] <u>circuit</u> by said voltage-current converting <u>function</u> <u>circuit</u>.

2. (Currently Amended) The current driving device according to claim 1, wherein: each of said output terminals is connected to said current output terminals provided to said plurality of said current output [[parts]] circuits, and

each of said plurality of current output [[parts]] <u>circuits</u> is connected in parallel to said first current supply [[part]] <u>source</u> and said first voltage supply [[part]] <u>source</u> used in common.

- 3. (Currently Amended) The current driving device according to claim 1, wherein, in each of said current output [[parts]] circuits, actuates said current-voltage converting function circuit is actuated under said voltage supply mode.

- 4. (Currently Amended) The current driving device according to claim 1, wherein each of said current output [[parts]] <u>circuits is configured to stop emprises a function of stopping</u> said current-voltage converting <u>function circuit</u> under said voltage supply mode.

- 5. (Currently Amended) The current driving device according to [[claims]] <u>claim</u> 1, further comprising:

a second current supply [[part]] <u>source</u> for supplying a second electric current that is proportional to said first electric current; [[,]] and

a <u>second</u> current-voltage converting [[part]] <u>circuit</u> for generating said first voltage by receiving said second electric current, wherein

said first voltage supply [[part]] <u>source</u> controls supplies of said first voltage generated by said <u>second</u> current-voltage converting [[part]] <u>circuit</u> to said current output [[parts]] <u>circuits</u>.

6. (Currently Amended) The current driving device according to claim 5, wherein said second current-voltage converting [[part]] circuit comprises a switching part for short-circuiting a node at which said first voltage emerges to a reference voltage node.

7. (Currently Amended) The current driving device according to [[claims]] <u>claim</u> 1, further comprising a second voltage supply [[part]] <u>source</u> with a larger voltage supply capacity than that of said first voltage supply [[part]] <u>source</u>, wherein

the use of said first voltage supply [[part]]source and the use of said second voltage supply [[part]] source are switched in accordance with the number of said current output [[parts]] circuits that [[take]] operate in said voltage supply mode among said plurality of current output [[parts]] circuits.

- 8. (Currently Amended) The current driving device according to [[claims]] <a href="claim">claim</a> 1, wherein said first voltage supply [[part]] <a href="source">source</a> is <a href="configured to change eonstituted to be capable of ehanging its voltage supply capacity in accordance with the number of said current output [[parts]] <a href="circuits">circuits</a> that [[take]] <a href="operate in">operate in</a> said voltage supply mode among said plurality of current output [[parts]] <a href="circuits">circuits</a>.

- 9. (Currently Amended) A current-driving-type display device, comprising said current driving device according to [[claims]] <u>claim</u> 1 mounted thereon so as to be driven by said current driving device.

- 10. (Currently Amended) A current driving device, comprising:

- a current input switch for controlling connection/disconnection states with respect to a current supply [[part]] source;

- a voltage holding [[part]] <u>circuit</u> for holding a reference voltage, which is charged by a flown current, the voltage holding circuit having a first terminal and a second terminal, the first terminal being connected to a fixed voltage;

a calibration switch interposed between said current input switch and said voltage holding

[[part]] circuit;

a plurality of voltage-current converting elements for generating an electric current in accordance with said reference voltage held in said voltage holding [[part]] <u>circuit</u>;

a plurality of signal response switches that are on/off controlled in accordance with inputted signals, <u>each of</u> said response switches being connected in series to <u>a corresponding one</u> [[each]] of said voltage-current converting elements, and each of which being connected in parallel to said calibration switch;

a connection node provided between said current input switch and said calibration switch; a plurality of current output switches, each being interposed between [[a]] the connection node, which is provided between said current input switch and said calibration switch, and said plurality of current output terminals; and

a high-speeding high-speed switch for controlling connection/disconnection states of said voltage supply [[part]] source with respect to the second terminal of said voltage holding [[part]] circuit.

Ex. 1003 ('047 Patent File History, 3/7/2011 Resp. to Office Action) at 31-34. The Applicants also argued that the amended claims were different than what was disclosed in the prior art.

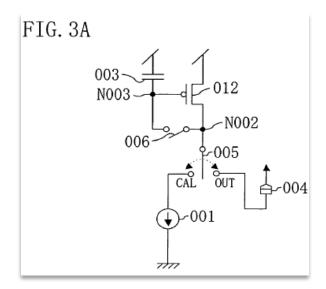

50. Regarding the Date reference, Applicants distinguished the claims from Figure 3A of Date, copied below:

U.S. Patent No. 7,466,166 (Date) at Fig. 3. Applicants argued regarding Claim 1 that Date "fails to disclose that a voltage holding circuit has a terminal being connected to a reference voltage different from the first voltage, and under the voltage supply mode, the first voltage is supplied to another terminal of the voltage holding circuit." In explaining Figure 3A of Date, Applicants argued that "the Examiner asserts that FIG. 3A of Date discloses the claimed first voltage supply part (source). It appears that the Examiner considers Vcc connected to capacitor 0003 as the claimed voltage holding part (circuit). However, it is clear that FIG. 3A fails to disclose that a voltage holding circuit (0003) has a terminal being connected to a reference voltage different from the first voltage (Vcc)." Regarding claim 10, Applicants argued "Date fails to disclose that the voltage holding circuit has a first terminal and a second terminal, the first terminal being connected to a fixed voltage, and the current driving device includes a high-speed switch for controlling

connection/disconnection states of **said voltage supply source with respect to the second terminal of said voltage holding circuit**." Ex. 1003 ('047 Patent File History, 3/7/2011 Resp. to Office Action) at 37 (emphasis in original).

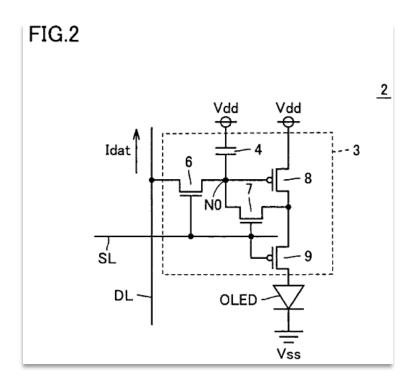

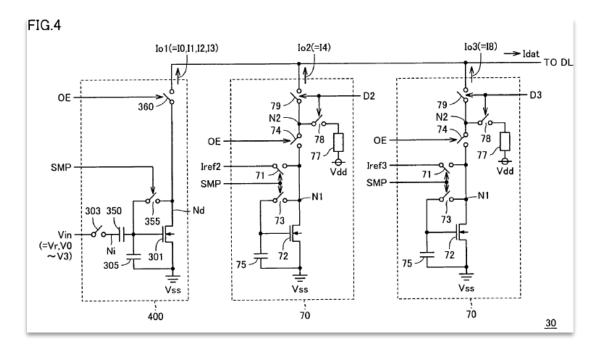

51. The Applicants distinguished the claims from Figure 2 and Figure 4 of Hashido, which are copied below: