### (19)日本国特許庁 (JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号 特開2000-22283 (P2000-22283A)

(43)公開日 平成12年1月21日(2000.1.21)

| (51) Int.Cl.7 |       | 識別記号 | FΙ            |   | テーマコード( <i>参考)</i> |

|---------------|-------|------|---------------|---|--------------------|

| H01S          | 5/30  |      | H 0 1 S 3/18  |   | 5 F 0 4 1          |

| H01L          | 33/00 |      | H 0 1 L 33/00 | С | 5 F O 7 3          |

## 審査請求 未請求 請求項の数14 〇L (全 10 頁)

| (21)出願番号 | 特願平10-190059        | (71) 出願人 000005821    |

|----------|---------------------|-----------------------|

|          |                     | 松下電器産業株式会社            |

| (22)出願日  | 平成10年7月6日(1998.7.6) | 大阪府門真市大字門真1006番地      |

|          |                     | (72)発明者 让村 歩          |

|          |                     | 大阪府門真市大字門真1006番地 松下電器 |

|          |                     | 産業株式会社内               |

|          |                     | (7%)発明者 長谷川 義晃        |

|          |                     | 大阪府門真市大字門真1006番地 松下電器 |

|          |                     | 産業株式会社内               |

|          |                     | (74)代理人 100078204     |

|          |                     | 弁理士 滝本 智之 (外1名)       |

|          |                     |                       |

|          |                     |                       |

|          |                     | 最終頁に続く                |

### (54) 【発明の名称】 半導体素子、半導体素子の製造方法及び半導体基板の製造方法

### (57)【要約】

【課題】 Nを含む I I I - V族半導体素子の熱応力に 起因する反りを抑制し、素子層における結晶欠陥やクラックの発生を防止できる半導体素子を提供することを目 的とする。

【解決手段】  $A1_2O_3$ 基板11の一方の主面上に、GaNバッファ層12、n型GaNコンタクト層13、n型A1GaNクラッド層14、GaN光ガイド層15、GaInN量子井戸活性層16、p型A1GaNクラッド層17、n型GaN電流ブロック層18、p型GaNコンタクト層19等のIII-V族化合物半導体層を形成する一方で、基板11の他方の主面上にZnO層112を形成する。上記のIII-V族化合物半導体層及UZnO0層112はともに基板よりも熱膨張係数が小さいため、半導体層形成後の冷却時に反りが発生するのを防止できる。

Lite-On Ex. 1005 p. 0001

#### 【特許請求の範囲】

【請求項1】基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIII-V族化合物半導体層と、前記基板の他方の主面上に形成された1層以上の裏面層とを有する半導体素子であって、前記III-V族化合物半導体層及び前記裏面層の熱膨張係数が、前記基板の熱膨張係数より小さいことを特徴とする半導体素子。

【請求項2】基板が $A 1_2 O_3$ であり、裏面層が少なくともGaN層、ZnO層、 $Si_3N_4$ 層または $SiO_2$ 層を含むことを特徴とする請求項1に記載の半導体素子。

【請求項3】基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIII-V族化合物半導体層と、前記基板の他方の主面上に形成された1層以上の裏面層とを有する半導体素子であって、前記III-V族化合物半導体層及び前記裏面層の熱膨張係数が、前記基板の熱膨張係数より大きいことを特徴とする半導体素子。

【請求項4】基板がSiCであり、裏面層が金属層を含むことを特徴とする請求項3に記載の半導体素子。

【請求項5】金属層が少なくともNi、Au、Al、InまたはGaを含むことを特徴とする請求項4に記載の 半導体素子。

【請求項6】基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIII-V族化合物半導体層を有する半導体素子であって、前記基板の他方の主面側において、前記基板の厚さが他の部分に比べて薄い部分を有することを特徴とする半導体素子。

【請求項7】基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIII-V族化合物半導体層を有する半導体素子であって、前記基板の他方の主面側に加工損傷層を有することを特徴とする半導体素子。

【請求項8】基板の一方の主面上に熱膨張係数が前記基板の熱膨張係数よりも小さい材料からなる裏面層を少なくとも1層以上形成する工程と、前記基板の他方の主面上に1層以上の少なくともNを含み、かつ前記基板より熱膨張係数が小さいIII-V族化合物半導体層を形成する工程と、基板裏面層及び前記基板を除去して前記III-V族化合物半導体層からなる半導体基板を得る工程とを有する半導体基板の製造方法。

【請求項9】基板が $A1_2O_3$ であり、裏面層が少なくともZnO層、 $Si_3N_4$ 層または $SiO_2$ 層を含むことを特徴とする請求項8に記載の半導体基板の造方法。

【請求項10】基板の一方の主面上に熱膨張係数が前記基板の熱膨張係数よりも大きい材料からなる裏面層を少なくとも1層以上形成する工程と、前記基板の他方の主面上に1層以上の少なくともNを含み、かつ前記基板より熱膨張係数が大きいIII-V族化合物半導体層を形成する工程と、基板裏面層及び前記基板を除去して前記II

I-V族化合物半導体層からなる半導体基板を得る工程とを有する半導体基板の製造方法。

【請求項11】基板がSiCであり、裏面層が金属層を含むことを特徴とする請求項10に記載の半導体基板の製造方法。

【請求項12】金属が少なくともNi、Au、Al、InまたはGaを含むことを特徴とする請求項11に記載の半導体基板の製造方法。

【請求項13】基板の一方の主面上に熱膨張係数が前記基板の熱膨張係数よりも小さい材料からなる裏面層を少なくとも1層以上形成する工程と、前記基板の他方の主面上に1層以上の少なくともNを含み、かつ前記基板より熱膨張係数が小さいIII-V族化合物半導体層を形成する工程と、前記裏面層及び前記基板を除去して前記II-V族化合物半導体層からなる半導体基板を得る工程と、前記半導体基板上に1層以上の少なくともNを含むIII-V族化合物半導体からなる素子層を形成する工程とを有することを特徴とする半導体素子の製造方法。

【請求項14】基板の一方の主面上に熱膨張係数が前記基板の熱膨張係数よりも大きい材料からなる裏面層を少なくとも1層以上形成する工程と、前記基板の他方の主面上に1層以上の少なくともNを含み、かつ前記基板より熱膨張係数が大きいIII-V族化合物半導体層を形成する工程と、前記裏面層及び前記基板を除去して前記II-V族化合物半導体層からなる半導体基板を得る工程と、前記半導体基板上に1層以上の少なくともNを含むIII-V族化合物半導体からなる素子層を形成する工程とを有することを特徴とする半導体素子の製造方法。

## 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は半導体素子、半導体基板および素子の製造方法に関するもので、特に紫外領域から青色領域の光を放出する発光素子や電子素子等に用いられるNを含むIII-V族半導体素子、半導体基板および素子の製造方法に関する。

[0002]

【従来の技術】光ディスクの記録密度向上あるいはレーザプリンタの解像度向上あるいは光計測機器、医療機器、ディスプレイ装置、照明装置等への応用を図るため、紫外領域から青色領域での発光が可能な半導体発光素子、特に半導体レーザの研究開発が盛んに行われている。このような短波長領域での発光が可能な材料として、A1GaInN系等のNを含むIII-V族化合物半導体を挙げることができる。例えばApp1ied Physics Letters第72巻(1998)211~213頁には、 $A1_2O_3$ 基板を用い、 $SiO_2$ マスク上にラテラル成長させたGaN層の上に変調ドープA1GaN/GaN歪超格子クラッド層およびInGaN多重量子井戸活性層を有する半導体レーザ素子を作製したことが記載されている。この素子は波長39

7 nm付近において室温連続発振し、出力2mWで11 50時間以上の動作寿命があると記されている。

【0003】高品質かつ高信頼性が要求される半導体素子の基板としては、格子定数および熱膨張係数が素子層とほぼ一致することが好ましいため、素子層と同じ材料を用いるのが理想的であるが、実際には、基板として必要な大面積のA1GaInN系半導体単結晶を得ることは、Nの平衡蒸気圧が非常に高く極めて困難である。そこで、結晶成長時の安定性の観点から、一般に $A1_2O_3$ やSiC等が基板として用いられている。

【0004】また素子層の形成には、一般に有機金属気相エピタキシー法(以下、MOVPE法と略す)や分子線エピタキシー法(以下、MBE法と略す)が用いられ、半導体結晶がエピタキシャル成長されている。

【発明が解決しようとする課題】しかしながら、上記のような素子層とは異なる材料系の基板を用いた場合、800~1100℃程度の高温でのエピタキシャル成長終了後、室温まで冷却する過程において、基板とA1GaInN系半導体との熱膨張係数差に比例する熱応力が発生する。これに起因して、基板と半導体素子層は反り、結晶欠陥やクラックの発生を引き起こしてしまう。

【0006】従って、A1GaInN系半導体レーザの素子特性や信頼性を実用レベルまで向上させるには、素子層における結晶欠陥やクラックの発生を防ぐことが不可欠である。そこで本発明は、基板の反りを抑制して結晶欠陥やクラックの発生を防いだ半導体素子(半導体発光素子)を提供することを主たる目的とする。

### [0007]

【0005】

【課題を解決するための手段】上記の目的を達成するために本発明の半導体素子は、基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIIIーV族化合物半導体層と、前記基板の他方の主面上に形成された1層以上の裏面層とを有する半導体素子であって、前記IIIーV族化合物半導体層及び前記裏面層の熱膨張係数が、前記基板の熱膨張係数より小さいことを特徴とする構成、または、基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIIIーV族化合物半導体層と、前記基板の他方の主面上に形成された1層以上の裏面層とを有する半導体素子であって、前記IIIーV族化合物半導体層及び前記裏面層の熱膨張係数が、前記基板の熱膨張係数より大きいことを特徴とする構成となっている。

【0008】この構成によれば、半導体素子層を形成した後の冷却時に発生する反りの発生を防止することができる

【0009】また、基板と、前記基板の一方の主面上に 形成された1層以上の少なくともNを含むIII-V族化 合物半導体層を有する半導体素子であって、前記基板の 他方の主面側において、前記基板の厚さが他の部分に比 べて薄い部分を有するか、または、基板と、前記基板の一方の主面上に形成された1層以上の少なくともNを含むIII-V族化合物半導体層を有する半導体素子であって、前記基板の他方の主面側に加工損傷層を有する構成によっても上記と同様に反りの発生を防止することができる。

【0010】また本発明の半導体基板の製造方法は、基 板の一方の主面上に熱膨張係数が前記基板の熱膨張係数 よりも小さい材料からなる裏面層を少なくとも1層以上 形成する工程と、前記基板の他方の主面上に1層以上の 少なくともNを含み、かつ前記基板より熱膨張係数が小 さいIII-V族化合物半導体層を形成する工程と、基板 裏面層及び前記基板を除去して前記III-V族化合物半 導体層からなる半導体基板を得る工程とを有するか、ま たは、基板の一方の主面上に熱膨張係数が前記基板の熱 膨張係数よりも大きい材料からなる裏面層を少なくとも 1層以上形成する工程と、前記基板の他方の主面上に1 層以上の少なくともNを含み、かつ前記基板より熱膨張 係数が大きいIII-V族化合物半導体層を形成する工程 と、基板裏面層及び前記基板を除去して前記III-V族 化合物半導体層からなる半導体基板を得る工程とを有す る構成となっている。

【0011】この構成によれば、基板となるIII-V族化合物半導体層に、反りに基づく欠陥が入るのを防止することができる。また、上記のようにして形成した半導体基板に対して、III-V族化合物半導体層を形成すると、品質のよい半導体素子を得ることができる。

#### [0012]

【発明の実施の形態】以下本発明の実施の形態における 半導体素子、半導体素子の製造方法及び半導体基板の製 造方法について図面を参照しながら詳細に説明する。な お、以下に示す例では、半導体素子として、半導体発光 素子の1つである半導体レーザを例に挙げて説明を行う が、本発明は半導体発光素子に限らず、Nを含有しIII -V族化合物半導体層を有する様々な半導体素子に適用 することができる。

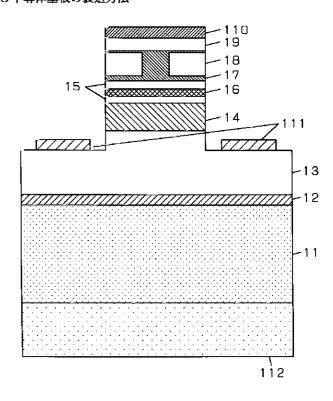

【0013】 (実施の形態1)図1に本発明の実施の形態1における半導体レーザ素子の構造を示す断面図を示す。図1において、11は $A1_2O_3$ 基板(厚さ150 $\mu$ m)、12はGaNバッファ層(膜厚40nm)、13はn型GaN3)、14はn型A1GaN9)。ド層(膜厚500nm、キャリア密度5×10<sup>17</sup> cm<sup>-3</sup>)、15はGaN光ガイド層(膜厚100nm)、16はGaInN量子井戸活性層、17はP型A1GaN9)、ド層(膜厚500nm、キャリア密度3×10<sup>17</sup> cm<sup>-3</sup>)、18はn2P2P3 に n3 に n3 に n3 に n4 に n5 に n5 に n5 に n6 に n6 に n7 に n7 に n7 に n8 に n9 に n

である。そして基板の裏面にはZ n O 層 1 1 2 ( 膜厚 2  $\mu$  m ) が形成されている。

【0014】基板の導電型については、n型、p型あるいは絶縁性であってもよい。また、GaNバッファ層12は、格子定数がA1GaInN系半導体結晶と大きく異なる $A1_2O_3$ 基板上にA1GaInN系半導体結晶を2次元成長させるために設けられるものであり、GaN以外にA1NあるいはA1GaNを用いることもできる。

【0015】n型GaNコンタクト層13の膜厚は、基板が絶縁性でp、n電極間でラテラル方向に電流を流さねばならないため、 $1\mu m$ 程度以上、好ましくは $3\mu m$ 程度必要である。

【0016】A1GaNクラッド層14、17のA1混晶比は、例えば8%である。なお、A1混晶においては、A1混晶比の増加、膜厚および不純物密度の増加に伴ってクラックが発生しやすくなるので、適当なA1混晶比、膜厚および不純物密度を選ぶ必要がある。

【0017】GaInN量子井戸活性層16の構造は、例えば膜厚5nm、In混晶比3%の障壁層4層と膜厚2.5nm、In混晶比13%の井戸層3層とが交互に積層されており、一番上の障壁層の上には膜厚5nm、A1混晶比15%のA1GaN層が備わる。このA1GaN層はGaInN層の分解を防ぐためである。

【0018】上記の図1に示したA1GaInN系半導体素子層の製造にあたっては、MOVPE法あるいはMBE法等の気相成長法を用いることができる。MOVPE法では速い成長速度で高品質な結晶を得ることができ、MBE法では高真空中で原子層レベルでのその場観察により高精度な成長制御を行うことができる。

【0019】MOVPE法では、Ga源としてはトリメチルガリウム(以下、TMGと略す)、トリエチルガリウム(以下、TEGと略す)、A1源としてはトリメチルアルミニウム(以下、TMAと略す)、トリエチルアルミニウム(以下、TEAと略す)、In源としてはトリメチルインジウム(以下、TMIと略す)、トリエチルインジウム(以下、TEIと略す)等のトリアルキル 金属化合物が用いられ、N源としてはアンモニア、ジメチルヒドラジン等のヒドラジン誘導体が用いられる。また n型不純物のSi源としてはシラン等、p型不純物のMgとしてはビスシクロペンタジエニルマグネシウム(以下、Cp2Mgと略す)等が用いられる。これらの原料ガスが水素、窒素あるいはアルゴン等をキャリアガスとして供給される。

【0020】一方MBE法では、III族源、不純物源としてはそれぞれ金属Ga、A1、In、SiおよびMgが用いられ、N源としては窒素、アンモニア等のガスが高周波プラズマ等で励起されて用いられる。一般にMBE法ではMOVPE法に比べて成長温度を低くすることができ、非平衡状態での成長を行えるが、A1GaIn

N系半導体結晶の場合は、ホール移動度等の結晶品質の 観点から、MBE法においてもできるだけ高温で成長を 行うことが好ましい。

【0021】上記のように構成された半導体レーザにつ いて考察する。基板である $A 1_2 O_3$ の熱膨張係数は8. O×1 O<sup>-6</sup> / K、III − V族化合物半導体層である A 1 GaInN系半導体の熱膨張係数は4.0~5.5×1 O-6/Kであるため(III-V族化合物半導体層の熱膨 張係数が基板の熱膨張係数よりも小さい)、通常、高温 でのIII-V族化合物半導体層のエピタキシャル成長終 了後、室温まで冷却する過程において、III-V族化合 物半導体層には圧縮応力が働き、III-V族化合物半導 体層表面側が上に凸になるように反ってしまう。しかし ながら、図1に示す構成では、III-V族化合物半導体 層が形成されていない側の基板裏面に、基板のA 12O3 より熱膨張係数の小さい物質、例えばZnO(熱膨張係 数2.9×10<sup>-6</sup>/K )で裏面層112を形成し、膜 厚、構造、成膜温度を制御することにより、熱応力を低 減し、半導体素子の反りを抑制することができる。その 結果、半導体素子層における結晶欠陥やクラックの発生 を防ぐことができ、素子特性や信頼性が向上する。な お、A12O3基板の裏面層に用いることのできる最適の 物質は、ZnO以外にSigN4、SiOg、GaN等が 挙げられる。

【0022】次に以下では、図1に示した半導体レーザ素子を製造方法について説明する。基板11には、(0001)面を主面とし、両面を鏡面研磨した単結晶A1203を用い、まず基板裏面にZnO層112を形成する。ZnO膜の製造方法には、大別して化学輸送法、MOVPE法あるいはMBE法等によるエピタキシャル成長と、スパッタリング法による多結晶膜成長とがある。例えばMOVPE法では、ジエチル亜鉛とNO2を原料としてエキシマレーザ(波長248nm)を照射して500℃でエピタキシャル膜が得られる。ここでは、レーザアブレーション法を用いる。

【0023】次に脱脂、洗浄したA1203基板11を高真空成長室に入れ、酸素分圧3×10-6Torrの雰囲気中750℃で10分間加熱し、基板裏面のクリーニングを行う。続いて基板温度を600℃にしてZnO焼結ターゲットにエキシマレーザを照射し、原料を蒸発させて基板へ2μm堆積させる。その後、成長室の雰囲気を酸素1気圧とし、500℃でアニールしてZnO層112を形成する。

【0024】次にMOVPE法を用いて $A1_2O_3$ 基板11の表面側に半導体レーザ素子層を成長させる工程に移

【0025】反応室内のサセプタ上に載置し、300T orrの水素雰囲気中1120℃で10分間加熱し、基 板表面のクリーニングを行う。続いて基板温度を500 ℃まで下げ、キャリアガスに水素、原料ガスにTMGと アンモニアとを用い、V族/III族供給モル比(以下、V/III比と略す)を5000として、基板11上にGaNバッファ層12を40nm堆積させる。次に、TMGのみ供給を止めて1000℃まで昇温する。1000℃に到達後、再びTMGを供給し、V/III比を2500として、段階的に昇温しながら最終的に1060℃でシランを加えてn型GaNコンタクト層13を成長させ、膜厚を3μmとする。続いてTMAを加えてn型A1GaNクラッド層14を500nm成長させる。TMGに対するTMAの気相比は10%である。さらに、TMAおよびシランの供給を止めてGaN光ガイド層15を100nm成長させる。

【0026】GaN光ガイド層15の成長後、TMGの供給も止めて810℃まで降温する。810℃に到達後、キャリアガスをArに切り替えて、井戸層においてはTEGとTMIをTMIの気相比が85%、V/III比が1000となるよう、また障壁層においてはTMIの気相比が15%、V/III比が6000となるよう供給して、GaInN量子井戸活性層16を形成する。【0027】次に、基板温度を1030℃まで昇温し、キャリアガスを再び水素に切り替えて、TMGとアンモニアを用いてGaN光ガイド層15を100nm成長させる。引き続き、TMAとCp2Mgを加えてp型AIGaNクラッド層17を500nm成長させた後、原料ガスの供給を止めて室温まで冷却する。

【0028】以上のようにしてIII-V族化合物半導体層を形成することができる。なお、上述の半導体レーザ素子層を製造する他の方法としてはMBE法が挙げられる。また、MOVPE法とMBE法を組み合わせて、基板側のn型層をMOVPE法で成長し、活性層およびp型層をMBE法で成長してもよい。MBE法では水素パッシベーションが起こらないので、熱処理せずにp型伝導が得られる。

【0029】以上の結晶成長工程で得られたウェハの反りを測定したところ、曲率半径は31.1mであり、基板裏面にZnO層112を設けない従来素子構造の場合の8.6mと比較すると、反りがほとんど無くなっていることがわかる。これは、成長温度から室温までの冷却過程でレーザ素子層に作用する圧縮応力が、基板裏面のZnO層に作用する圧縮応力に打ち消されるためと考えられる。

【0030】このウェハを単一モードレーザ素子に加工する。すなわち、フォトリソグラフィー、ドライエッチング、埋め込み再成長、電極蒸着等のプロセスを用いる。まず、幅3 $\mu$ mのストライプ状SiO2を形成する。これをマスクとして、p型A1GaNクラッド層17をリッジ状に深さ400nmドライエッチングする。次にMOVPE法によりn型GaN電流ブロック層18を400nm選択成長させる。その後、SiO2マスクを除去し、再びMOVPE法によりp型GaNコンタク

ト層 198400 n m成長させる。さらに、n 型電極 118 形成するため、p 型 G a N コンタクト層 19 から n 型 A 1 G a N クラッド層 14 までをドライエッチング し、n 型 G a N コンタクト層 138 を露出させる。

【0031】Mgアクセプタ活性化のための熱処理は、成長終了後に反応室内で行ってもよいし、いったん取り出して熱処理炉で行ってもよいし、あるいは電極蒸着のシンタリングと同時に行ってもよい。熱処理条件は、例えば窒素雰囲気中で600℃、20分間である。

【0032】最後に、電極蒸着およびシンタリングを行う。p型電極110には、例えばMg膜とAu膜が順次積層されたMg/Au電極が用いられる。またn型電極111にはTi/Mo/Pt/Au電極が形成される。【0033】このウェハを劈開して共振器長を例えば0.7μmとし、両端面とも適当なコーティングを施した後、レーザ素子に分離して、ヒートシンクにジャンクションダウンで実装する。室温での動作特性を評価したところ、発振波長は404nm、しきい値電流は94mA、外部微分量子効率は70%、レーザ発振開始時の印加電圧は5.9Vであった。

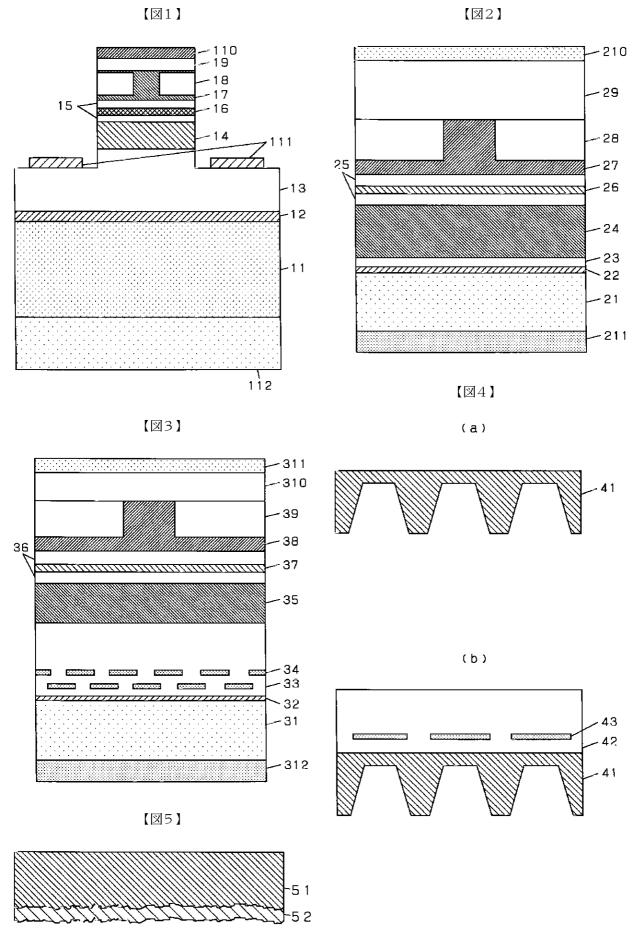

【0034】(実施の形態2)図2に本発明の実施の形 態2における半導体レーザ素子の構造を示す断面図を示 す。図2において、21はn型6H-SiC基板(厚さ 150μm、キャリア密度2×10<sup>18</sup> cm<sup>-3</sup>)、22は A1Nバッファ層(膜厚10nm)、23はA1GaI nNバッファ層 (膜厚20nm)、24はn型A1Ga Nクラッド層(膜厚500nm、キャリア密度5×10 17 c m<sup>-3</sup>)、25はGaN光ガイド層(膜厚100 n m)、26はGaInN量子井戸活性層、27はp型A 1GaNクラッド層(膜厚500nm、キャリア密度3 ×10<sup>17</sup>cm<sup>-3</sup>)、28はn型GaN電流ブロック層 (膜厚400nm、キャリア密度5×10<sup>17</sup>cm<sup>-3</sup>)、 29はp型GaNコンタクト層(膜厚400nm、キャ リア密度8×10<sup>17</sup> c m<sup>-3</sup>)、210はp型電極であ る。そして基板の裏面には金属層であるNi/Au層2 11 (膜厚400nm)が形成されている。

【0035】なお、基板の導電型については、n型、p型あるいは絶縁性であってもよく、また、基板面方位については低指数面だけでなく、ある方向へ傾斜させた基板を用いてもよい。例えば、4H-SiCの(0001)面から[11-20]方向へ3度傾斜させた基板を用いることもできる。

【0036】上記のように構成された半導体レーザについて考察する。基板であるSiCの熱膨張係数は4.2×10-6/K、GaN系半導体の熱膨張係数は5.5×10-6/Kであるため(III-V族化合物半導体層の熱膨張係数が基板の熱膨張係数よりも大きい)、通常、高温でのエピタキシャル成長終了後室温まで冷却する過程で、III-V族化合物半導体層には引張り応力が働き、III-V族化合物半導体層表面側が下に凸になるように反

る。しかしながら、図2に示す構成では、III-V族化合物半導体層が形成されていない側の基板裏面に、基板のSiCより熱膨張係数の大きい金属等の物質で裏面層211を形成し、膜厚、構造、成膜温度を制御することにより、熱応力を低減し、半導体素子層における結晶欠により、熱応力を低減し、半導体素子層における結晶欠陥やクラックの発生を防ぐことができ、素子特性や信頼性が向上する。なお、SiC基板の裏面層に用いることのできる最適の物質は、NiやAu以外にA1、In、Ga等が挙げられる。

【0037】以下、上記の実施の形態1と異なる点について、図2に示した半導体レーザ素子を製造する工程に即して説明する。

【0038】基板21には、(0001) Si面を主面とし、両面を鏡面研磨した単結晶n型6H-SiCを用い、まず基板裏面にNi/Au層211を通常の真空蒸着法により形成する。脱脂、洗浄した基板21を真空蒸着槽に入れ、基板温度は350 Cとして真空度 $5\times10$  -7Torr以下でNiを10nm、Auを390nm順次蒸着する。Niは基板とAuの密着性を高めるために用いる。なお、熱膨張係数はNiが $38\times10^{-6}/K$ 、Auが $43\times10^{-6}/K$ である。

【0039】次にMOVPE法を用いてSiC基板21 の表面側に半導体レーザ素子層を成長させる。反応室内 のサセプタ上に載置し、300Torrの水素雰囲気中 1120℃で10分間加熱し、基板表面のクリーニング を行う。このときに、裏面のNi/Au層211は融点 を超えて流動性が高まり、基板21との間の熱応力に起 因する歪は解放される。続いて基板温度を1000℃ま で下げ、キャリアガスに水素、原料ガスにTMAとアン モニアとを用い、基板21上にA1Nバッファ層22を 10nm堆積させ、TMAの供給を止める。さらに基板 温度を910℃まで下げ、TMA、TMG、TMIを供 給して、A1GaInNバッファ層23を20nm成長 させる。この層は、レーザ構造各層間に存在する歪に起 因するクラックの発生を抑制する効果がある。 n型A1 GaNクラッド層24以降の成長工程は実施の形態1で 説明した通りである。

【0040】結晶成長工程で得られたウェハの反りを測定したところ、曲率半径は24.8mであり、基板裏面にNi/Au層211を設けない従来素子構造の場合の13.5mと比較すると、反りが抑制されていることがわかる。また、従来構造では素子層にクラックの発生が観察されるが、本実施の形態の構造では観察されなかった。これは、成長温度から室温までの冷却過程でレーザ素子層に作用する引張り応力が、基板裏面のNi/Au層に作用する引張り応力に打ち消されるためと考えられる。

【0041】なお、基板裏面のNi/Au層211はレーザ素子層成長時に十分合金化され、n型SiCに対す

るオーミック電極となるので、図2の素子構造において はn型電極をも兼ねる。

【0042】(実施の形態3)図3に本発明の実施の形 態3における半導体レーザ素子の構造を示す断面図を示 す。図3において、31はn型6H-SiC基板(厚さ 150μm、キャリア密度2×10<sup>18</sup> cm<sup>-3</sup>)、32は A1Nバッファ層(膜厚10nm)、33はn型GaN 層(膜厚16μm、キャリア密度7×10<sup>17</sup> c m<sup>-3</sup>)、 34はSiO2マスク層、35はn型A1GaNクラッ ド層(膜厚500nm、キャリア密度5×10<sup>17</sup> c m<sup>-3</sup>)、36はGaN光ガイド層(膜厚100nm)、 37はGaInN量子井戸活性層、38はp型A1Ga Nクラッド層(膜厚500nm、キャリア密度3×10 <sup>17</sup> c m<sup>-3</sup>) 、39はn型GaN電流ブロック層 (膜厚4 00nm、キャリア密度5×10<sup>17</sup>cm<sup>-3</sup>)、310は p型GaNコンタクト層(膜厚400nm、キャリア密 度8×10<sup>17</sup> c m<sup>-3</sup>)、311はp型電極である。そし て基板の裏面にはNi/Au層312(膜厚500n m)が形成されている。

【0043】本実施の形態は、基本的には、上記の実施の形態2と類似しており、基板上のIII-V族化合物半導体層中にストライプ状に $SiO_2$ が埋め込まれている点が異なっている。なお、本実施の形態では、上記のような構成で説明を行うが、 $SiO_2$ 以外に $Si_3N_4$ を用いてもよく、また、必ずしもストライプ状に形成されている必要性はなく、不連続に埋め込まれていればよい。【0044】以下、実施の形態2と異なる点について、図3に示した半導体レーザ素子を製造する工程に即して説明する。すなわち、実施の形態2と同様、基板裏面にNi/Au層312を通常の真空蒸着法により形成した後、MOVPE法を用いて基板表面側に半導体レーザ素子層を成長させる。

【0045】まずA1Nバッファ層32の成長に引き続き、厚さ $2\mu$ mのn型GaN層33を成長させる。次にプラズマCVD法等により $SiO_2$ マスク層34(厚さ100nm)を形成し、フォトリソグラフィー、ドライエッチングプロセスにより、GaNの[1-100]方向に $4\mu$ mピッチで $1.5\mu$ m幅のストライプ状開口部を設ける。

【0046】再びMOVPE反応室内のサセプタ上に載置し、n型GaN層33を選択成長させる。この過程でマスク上への多結晶GaN堆積は起こらず、開口部からGaNがラテラル成長し、マスク中央部で合体し、厚さ約 $4\mu$ mの成長で(0001)平坦面が得られる。次に再びプラズマCVD法等により2層目のストライプ状 $SiO_2$ マスク層34(厚さ100nm)をさきほどと同じ方向に形成する。このとき、マスクの開口部が1層目のマスクの上方に来るように2層目のマスクを形成する

【0047】そしてMOVPE反応室内のサセプタ上に

【0048】基板裏面にNi/Au層312を設けない従来素子構造ではn型GaN層33のラテラル成長でクラックが発生し、その上にレーザ素子層を形成することができなかったが、本実施の形態の構造ではクラックは発生せず、転位密度105cm<sup>-2</sup>台程度の高品質なレーザ素子層を形成することができる。

【0049】(実施の形態4)図4に本発明の実施の形態4における半導体レーザ素子に用いる基板の構造を示す断面図を示す。本実施の形態も、上記の実施の形態1や2と同様に、基板の一方の主面上にNを含有するIIIーV族化合物半導体層を有する構造となっているが、この部分については同様であるため、説明を省略し、IIIーV族化合物半導体層を結晶成長させた後の冷却工程において生じる反りの防止を行うための、基板側の特徴点について説明することとする。

【0050】図4 (a)は例えば (0001) Si面を主面とするn型6 H-SiC基板 (厚さ150 $\mu$ m、キャリア密度 $2\times10^{18}$  cm $^{-3}$ )であって、裏面側には、例えば [1-100]方向に延びる深さ110 $\mu$ m、幅150 $\mu$ mの溝が150 $\mu$ m間隔で設けられている。このような、基板の厚さが他の部分に比べて薄い部分を有する形状を有する基板の製造には、フォトリソグラフィ、ドライエッチングおよび、またはウェットエッチングが用いられる。

【0051】基板41の表面に、実施の形態2で説明したようなA1 G a I n N 系半導体レーザ素子を形成したときのウェハの反りは、厚さの均一な基板上に素子を形成したときと比較して大きな差はなかった。しかし、断面を透過電子顕微鏡で観察すると、溝のない厚い基板部分に形成した素子層では、貫通転位の密度が $10^7 \sim 1$   $0^8$  c m $^{-2}$ 程度に達するが、溝のある薄い基板部分に形成した素子層では、 $10^6$  c m $^{-2}$ 以下に抑えられている一方、薄い基板部分に欠陥やクラックの発生する傾向が観察された。つまり、基板に溝を設けて薄くしたことにより、強度の低下した基板側に欠陥等が発生し、その部分の歪が緩和されるので、その上の素子層では高品質な結晶が得られる。

【0052】なお、基板裏面の溝は素子を分離する、あるいは劈開するための溝として利用してもよい。また、 本実施の形態ではストライプ状に溝を設けているが、こ れ以外には例えば、格子状に溝を設けてもよい。

【0053】さらに、図4(b)に示すように基板上に n型GaN層42を成長させ、 $SiO_2$ マスク層43上に GaNをラテラル成長させて平坦な n型GaN層42 を形成した後、その上にAlGaInN系半導体レーザ素子を形成してもよい。 $SiO_2$ マスク層43の形状は、例えば GaN[1-100] 方向に延びるストライプ状で、 $10\mu$ mピッチで  $5\mu$ m幅のストライプ状開口部を設けてある。

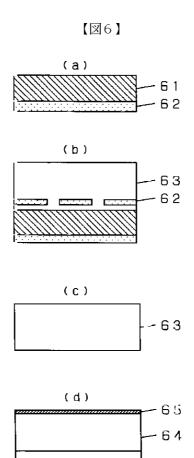

【0054】(実施の形態5)図5に本発明の実施の形態5における半導体レーザ素子に用いる基板の構造を示す断面図を示す。本実施の形態も、上記の実施の形態1や2と同様に、基板の一方の主面上にNを含有するIII-V族化合物半導体層を有する構造となっているが、この部分については同様であるため、説明を省略し、III-V族化合物半導体層を結晶成長させた後の冷却工程において生じる反りの防止を行うための、基板側の特徴点について説明することとする。

【0055】図5において、基板の材質は例えば $A1_2$ O $_3$ であり、52は $A1_2$ O $_3$ 基板51裏面の加工損傷層を示す。基板は、例えば、インゴットから切り出して表面側は鏡面研磨するが、裏面側は切り出したときのままの状態、あるいはラップエッチングを施した状態とする。加工による基板へのグメージが残っているため、この上にA1GaInN系半導体素子を形成すると歪のかかり方が変化し、通常、半導体素子層には圧縮応力が働いて表面側が上に凸になるように反るのに対して、この場合はそれを打ち消す方向に働き、ほぼ平坦とすることができる。

【0056】なお、基板と半導体素子層の熱膨張係数差が大きいときに、基板の反りを防止し、あるいは素子層への結晶欠陥・クラック発生を抑制するためには、これまで説明してきた実施の形態以外に、他の手段を用いることもできる。例えば、基板裏面側を多孔質状にすること、基板裏面にハニカム状層を設けること、あるいは基板裏面に微粒子層を設けること等が挙げられる。

【0057】(実施の形態6)図6に本発明の実施の形態6における半導体レーザ素子の製造工程断面図を示す。図6において、61は $A1_2O_3$ 基板、62は $SiO_2$ 層、63はn型GaN層、64はA1GaInN系レーザ素子層、65はp型電極、66はn型電極を示している。

【0058】以下図6を参照しながら、本発明の実施の 形態における半導体レーザ素子の製造方法とともに、半 導体基板の製造方法についても説明する。

【0059】 $A1_2O_3$ 基板61には、(0001) 面を主面とし、両面を鏡面研磨した単結晶 $A1_2O_3$ (厚さ $150\mu$ m)を用い、まず基板裏面に熱膨張係数が基板の熱膨張係数よりも小さい材料である $SiO_2$ 層62(厚さ $2\mu$ m)を裏面層としてプラズマCVD法等により形

成する。

【0060】次にMOVPE法を用いて基板表面側に厚さ $2\mu$ mのGaN層63を成長させる。そして $SiO_2$ マスク層62(厚さ100nm)を形成し、フォトリソグラフィー、ドライエッチングプロセスにより、GaNの[1-100]方向に $8\mu$ mピッチで $3\mu$ m幅のストライプ状開口部を設ける。

【0061】再びMOVPE反応室内のサセプタ上に載置し、n型GaN層(キャリア密度 $1\times10^{18}$  c m $^{-3}$ )63を選択成長させる。この過程でマスク上への多結晶 GaN堆積は起こらず、開口部からGaNがラテラル成長し、マスク中央部で合体し、厚さ約 $6\mu$ mの成長で(0001)平坦面が得られるが、厚さ約 $100\mu$ m以上になるまでそのまま成長を続ける。これにより、 $A1_2O_3$ 基板61との界面から発生して上方に延びる貫通転位(界面付近の密度は $2\times10^{10}$  c m $^{-2}$ )は $SiO_2$ マスク層で消失し、またラテラル方向にはほとんど屈曲しないので、n型GaN層63の最上部で貫通転位の密度は $10^4$  c m $^{-2}$ 台に減少する。

【0062】ここではGaN厚膜をMOVPE法により 形成したが、他の方法としてハイドライドVPE法を用 いて形成してもよい。この方法はMOVPE法に比べて 格段に成長速度が速く、厚膜成長に適している。

【0063】以上の工程により、基板の裏面層が形成された側とは反対側の主面に熱膨張係数が基板よりも小さいIII-V族化合物半導体層が形成されたことになる。

【0064】GaN厚膜成長を終えて室温まで冷却した時点で、基板の反りはほぼ抑制されている。この状態で  $A1_2O_3$ 基板61の裏面側から $SiO_2$ 層62、 $A1_2O_3$ 基板61および $SiO_2$ マスク層62を研磨によって除去することにより、厚さ約 $100\mu$ mのn型GaN基板 63を得ることができる。

【0065】この基板上に、MOVPE法を用いて実施の形態3で説明したように、A1GaInN系レーザ素子層64を形成し、表面のp型コンタクト層上にp型電極65を、基板裏面にn型電極66をそれぞれ形成することにより、半導体レーザ素子が得られる。

【0066】なお、本実施の形態では、裏面層として $SiO_2$ を用いたが、ZnO層や、 $Si_3N_4$ 層を用いてもよい。また、例えば基板にSiCを用い、裏面層を金属層(Ni、Au、Al、In またはGaを含む)とすることにより、基板の一方の主面上に熱膨張係数が基板の熱膨張係数よりも大きい材料からなる裏面層を形成し、基板の他方の主面上に基板より熱膨張係数が大きいIII -V族化合物半導体層を形成した後、基板裏面層及び基板を除去し半導体基板を得てもよい。

【0067】以上本発明について、その実施の形態とと

もに説明を行い、上記の実施の形態においては半導体レーザ素子について説明したが、発光ダイオード、フォトダイオード、電界効果トランジスタやその他の半導体素子にも適用することができる。

#### [0068]

【発明の効果】以上のように本発明によれば、N含むII I-V族半導体結晶と基板との熱膨張係数差に比例する 熱応力を低減させることができ、半導体結晶の反りを抑 制して結晶欠陥やクラックの発生を防げるので、これを 用いた半導体素子の特性や信頼性を向上させるという顕 著な効果が得られる。

### 【図面の簡単な説明】

【図1】本発明の実施の形態1における半導体レーザ素 子の構造を示す断面図

【図2】本発明の実施の形態2における半導体レーザ素 子の構造を示す断面図

【図3】本発明の実施の形態3における半導体レーザ素 子の構造を示す断面図

【図4】本発明の実施の形態4における半導体レーザ素 子に用いる基板の構造を示す断面図

【図5】本発明の実施の形態5における半導体レーザ素 子に用いる基板の構造を示す断面図

【図6】本発明の実施の形態6における半導体レーザ素 子の製造工程断面図

#### 【符号の説明】

11,51,61 Al<sub>2</sub>O<sub>3</sub>基板

12 GaNバッファ層

13 n型GaNコンタクト層

14, 24, 35 n型AlGaNクラッド層

15, 25, 36 GaN光ガイド層

16, 26, 37 GaInN量子井戸活性層

17, 27, 38 p型A1GaNクラッド層

18, 28, 39 n型GaN電流ブロック層

19,29,310 p型GaNコンタクト層

110, 210, 311, 65 p型電極

111,66 n型電極

112 ZnO層

21,31,41 n型6H-SiC基板

22,32 A1Nバッファ層

23 AlGaInNバッファ層

211,312 Ni/Au層

33,42,63 n型GaN層

34,43 SiO<sub>2</sub>マスク層

52 加工損傷層

62 SiO<sub>2</sub>層

64 AlGaInN系レーザ素子層

Lite-On Ex. 1005 p. 0009

フロントページの続き

(72)発明者 石橋 明彦

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(72)発明者 木戸口 勲

大阪府門真市大字門真1006番地 松下電器 産業株式会社内 (72)発明者 伴 雄三郎

-63 -66

> 大阪府門真市大字門真1006番地 松下電器 産業株式会社内

Fターム(参考) 5F041 AA40 CA04 CA05 CA14 CA33

CA34 CA40 CA46 CA65

5F073 AA45 AA51 AA73 BA06 BA07

CA07 CB04 CB05 DA05 EA27

EA29

### (54) [Title of the Invention]

Semiconductor device, manufacturing method of semiconductor device, and manufacturing method of semiconductor substrate

### (57) [Abstract]

[Problem to be Solved] It is a primary objective of the present invention to provide a semiconductor device capable of suppressing warpages of N-containing group III-V compound semiconductor devices caused by thermal stress and preventing crystal defects or cracks occurred in device layers.

[Solution to the Problem] Group III-V compound semiconductor layers including the gallium nitride (GaN) buffer layer 12, n-type GaN contact layer 13, n-type AlGaN cladding layer 14, GaN light guide layer 15, GaInN quantum well active layer 16, p-type AlGaN cladding layer 17, n-type GaN current blocking layer 18, and p-type GaN contact layer 19 are formed on a main surface on one side of a sapphire (Al<sub>2</sub>O<sub>3</sub>) substrate 11. On the other hand, a ZnO layer 112 is formed on a main surface on the other side of the substrate 11. Since the aforementioned group III-V compound semiconductor layers and ZnO layer 112 have a coefficient of thermal expansion smaller than that of the substrate, therefore the occurrence of warpage can be prevented after the formed semiconductor layers are cooled.

## [What is claimed is:]

[Claim 1]

A semiconductor device, comprising:

a substrate;

at least one group III-V compound semiconductor layer, containing nitrogen (N), and formed on a main surface on a side of the substrate; and at least one back layer, formed on a main surface on the other side of the substrate, wherein both of the group III-V compound semiconductor layer and the back layer have a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate.

#### [Claim 2]

The semiconductor device according to claim 1, wherein the substrate is made of Al<sub>2</sub>O<sub>3</sub>, and the back layer comprises a GaN layer, a ZnO layer, a Si<sub>3</sub>N<sub>4</sub> layer or a SiO<sub>2</sub> layer.

## [Claim 3]

A semiconductor device, comprising: a substrate; at least one group III-V compound semiconductor layer, at least containing nitrogen (N), and formed on a main surface on a side of the substrate; and at least one back layer, formed on a main surface of the other side of the substrate, wherein both of the group III-V compound semiconductor layer and the back layer have a coefficient of thermal expansion greater than the coefficient of thermal expansion of the substrate.

#### [Claim 4]

The semiconductor device according to claim 3, wherein the substrate is made of SiC, and the back layer comprises a metal layer.

### [Claim 5]

The semiconductor device according to claim 4, wherein the metal layer comprises Ni, Au, Al, In or Ga.

### [Claim 6]

A semiconductor device, comprising: a substrate; and at least one group III-V compound semiconductor layer, containing nitrogen (N), and formed on a main surface on a side of the substrate, wherein a main surface on the other side of the substrate has a thin part with a thickness of the substrate smaller than the thickness of other parts of the substrate.

#### [Claim 7]

A semiconductor device, comprising:

a substrate; and at least one group III-V compound semiconductor layer, containing nitrogen (N), and formed on a main surface of a side of the substrate, wherein a main surface on the other side of the substrate has a manufacture damaged layer.

### [Claim 8]

A manufacturing method of a semiconductor substrate, comprising: a back layer formation process, for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process, for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer contains nitrogen (N) and has a coefficient of thermal expansion smaller than that of the substrate; and a

semiconductor substrate obtaining process, for removing the back layer of the substrate and the substrate to obtain a semiconductor substrate formed by the group III-V compound semiconductor layer.

### [Claim 9]

The manufacturing method of a semiconductor substrate according to claim 8, wherein the substrate is made of Al<sub>2</sub>O<sub>3</sub>, and the back layer comprises a ZnO layer, a Si<sub>3</sub>N<sub>4</sub> layer or a SiO<sub>2</sub> layer.

### [Claim 10]

A manufacturing method of a semiconductor substrate, comprising: a back layer formation process, for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion greater than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process, for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer contains nitrogen (N) and has a coefficient of thermal expansion greater than that of the substrate; and a semiconductor substrate obtaining process, for removing the back layer of the substrate and the substrate to obtain a semiconductor substrate formed by the group III-V compound semiconductor layer.

### [Claim 11]

The manufacturing method of a semiconductor substrate according to claim 10, wherein the substrate is made of SiC, and the back layer comprises a metal layer.

### [Claim 12]

The manufacturing method of a semiconductor substrate according to claim 11, wherein the metal layer comprises Ni, Au, Al, In or Ga.

#### [Claim 13]

A manufacturing method of a semiconductor substrate, comprising: a back layer formation process, for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process, for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer contains nitrogen (N) and has a

coefficient of thermal expansion smaller than that of the substrate; a semiconductor substrate obtaining process, for removing the back layer of the substrate and the substrate to obtain a semiconductor substrate formed by the group III-V compound semiconductor layer; and a device layer formation process, for forming at least one device layer on the semiconductor substrate, wherein the device layer is comprised of an N-containing group III-V compound semiconductor.

## [Claim 14]

A manufacturing method of a semiconductor device, comprising: a back layer formation process, for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion greater than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process, for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer contains nitrogen (N) and has a coefficient of thermal expansion greater than that of the substrate; a semiconductor substrate obtaining process, for removing the back layer and the substrate to obtain a semiconductor substrate comprised of the group III-V compound semiconductor layer; and a device layer formation process, for forming at least one device layer on the semiconductor substrate, wherein the device layer is comprised of an N-containing group III-V compound semiconductor.

[Detailed Description of the Invention] [0001]

[Technical Field of the Invention]

The present invention relates to a semiconductor device, a semiconductor substrate and a manufacturing method of the semiconductor device, and more particularly to an N-containing group III-V compound semiconductor device, a semiconductor substrate and a manufacturing method of the semiconductor device used in a light emitting element or an electronic device for transmitting light from an ultraviolet region to a blue region.

[0002]

[Background of the Invention]

In order to increase the recording density of an optical disk or the resolution of a laser printer, apply these results to an optical measuring device, a medical device, a display device, a lighting device, and the like, the research and development of semiconductor light emitting elements, particularly semiconductor lasers, which can emit light from an ultraviolet region and a blue region, have been actively conducted. As a material capable of emitting light in such a short wavelength region, a Group III-V compound semiconductor such as an AlGaInN group can be cited. For example, Applied Physics Letters, Volume 72 (1998), Pages 211 to 213, have pointed out that a semiconductor laser device can be fabricated by using an Al<sub>2</sub>O<sub>3</sub> substrate which is horizontally grown on a GaN layer on a SiO<sub>2</sub> mask, and the semiconductor laser device has a modulation doped AlGaN/GaN strained layer superlattice cladding layer and an InGaN multiple quantum well active layer. It is described that this device has a wavelength of approximately 397nm under a continuous oscillation at room temperature, and a service life of over 1150 hours at the output power of 2mW.

## [0003]

For a substrate of a high-quality and reliable semiconductor device, the lattice constant, the coefficient of thermal expansion, and the device layer are all consistently good, and thus it is ideal to use the same material as that of the device layer for the substrate. Actually, it is very difficult to obtain the single crystal of the AlGaInN-based semiconductor for the large area required by the substrate, because the equilibrium vapor pressure of nitrogen (N) is very high. Therefore, from the point of view of stability at the crystal growth time, Al<sub>2</sub>O<sub>3</sub> or SiC is generally used for making a substrate.

#### [0004]

In addition, the formation of device layers generally adopt an organic metal vapor phase epitaxy (hereinafter referred to as "MOVPE") or molecular beam epitaxy (hereinafter referred to as "MBE") method to epitaxially grow the semiconductor crystals.

#### [0005]

#### [Problem to be Solved]

However, when a substrate made of a material different from that of the device layer is used, a thermal stress proportional to the difference of the coefficients of thermal expansion between the substrate and the AlGaInN semiconductor is generated during the process of cooling the substrate to room temperature after the completion of epitaxial growth at a high temperature within a range of 800 to 1100 ° C. As a result, the substrate and the semiconductor device layer may have warpage, crystal defects, and cracks for the above reasons.

## [0006]

To improve the property and reliability of the AlGaInN based semiconductor laser to a practical level, it is essential to prevent the occurrence of crystal defects and cracks in the device layer. Therefore, it is a primary objective of the present invention to provide a semiconductor device (or a semiconductor light emitting device) capable of suppressing the warpage of a substrate to prevent the occurrence of crystal defects and cracks.

### [0007]

#### [Solution]

To achieve the aforementioned objective, the present invention provides a semiconductor device comprising a substrate, at least one group III-V compound semiconductor layer, containing nitrogen (N), and formed on a main surface on a side of the substrate; and at least one back layer, formed on a main surface on the other side of the substrate, wherein both of the group III-V compound semiconductor layer and the back layer have a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate.

## [8000]

According to this structure it is possible to prevent the occurrence of warpage occurred at the time of cooling after forming the semiconductor device layer.

#### [0009]

This invention also provides a semiconductor device comprising a substrate; and at least one group III-V compound semiconductor layer, containing nitrogen (N), and formed on a main surface on a side of the substrate, wherein a main surface on the other side of the substrate has a thin part with a thickness of the substrate smaller than the thickness of other parts of the substrate.

### [0010]

This invention further provides a manufacturing method of a semiconductor substrate comprising: a back layer formation process for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer

contains nitrogen (N) and has a coefficient of thermal expansion smaller than that of the substrate; and a semiconductor substrate obtaining process for removing the back layer of the substrate and the substrate to obtain a semiconductor substrate comprised of the group III-V compound semiconductor layer. Alternatively, the method comprises a back layer formation process, for forming at least one back layer on a main surface on a side of a substrate, wherein the back layer is made of a material with a coefficient of thermal expansion greater than the coefficient of thermal expansion of the substrate; a group III-V compound semiconductor layer formation process, for forming at least one group III-V compound semiconductor layer on the other side of the substrate, wherein the group III-V compound semiconductor layer contains nitrogen (N) and has a coefficient of thermal expansion greater than that of the substrate; and a semiconductor substrate obtaining process, for removing the back layer of the substrate and the substrate to obtain a semiconductor substrate comprised of the group III-V compound semiconductor layer.

## [0011]

Based on the aforementioned structure, the group III-V compound semiconductor layer serving as the substrate can prevent the occurrence of defects caused by warpage. In addition, a high-quality semiconductor device can be obtained by forming the group III-V compound semiconductor layer on the aforementioned semiconductor substrate.

#### [0012]

#### [Embodiments of the Invention]

The semiconductor device, manufacturing method of the semiconductor device, and manufacturing method of a semiconductor substrate of the present invention will be described in detail with reference to the accompanying drawings. In the following embodiments, a laser semiconductor is taken as an example of one of the semiconductor light emitting elements, but the present invention is not limited to the semiconductor light emitting element only, and the invention can be applied to various semiconductor elements having the Group III-V compound semiconductor layer.

[0013] With reference to FIG. 1 for a cross-sectional view showing the structure of a semiconductor laser device in accordance with the first embodiment of the present invention, the numerals used in the figure are described in below: 11 is an Al<sub>2</sub>O<sub>3</sub> substrate (with a thickness of 150µm), 12 is a GaN buffer layer (with a film thickness

of 40nm), 13 is an n-type GaN contact layer (with a film thickness of 3μm, a carrier density of 1×1018cm<sup>-3</sup>), 14 is an n-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 5×1017cm<sup>-3</sup>), 15 is a GaN light guide layer (with a film thickness of 100nm), 16 is a GaInN quantum well active layer, 17 is a p-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 3×1017cm<sup>-3</sup>), 18 is an n-type GaN current blocking layer (with a film thickness of 400nm and a carrier density of 5×1017cm<sup>-3</sup>), 19 is a p-type GaN contact layer (with a film thickness of 400nm and a carrier density of 8×1017cm<sup>-3</sup>), 110 is an n-type electrode, and 111 is a p-type electrode. In addition, a ZnO layer 112 (with a film thickness of 2μm) is formed on the back surface of a substrate.

## [0014]

The conductivity type of the substrate may be n-type, p-type or insulating. Further, the GaN buffer layer 12 is provided for the two-dimensional growth of an AlGaInN based semiconductor crystal on an Al<sub>2</sub>O<sub>3</sub> substrate having a lattice constant different from that of an AlGaInN based semiconductor, and AlN or AlGaN may be used other than GaN.

## [0015]

Since the substrate is insulating, the current must circulate in a horizontal direction between the p-type and n-type electrodes, so that the film thickness of the n-type GaN contact layer 13 must be  $1\mu m$  or above, preferably  $3\mu m$ .

#### [0016]

The Al crystal mixing ratio of the AlGaN cladding layer 14, 17 is, for example, 8%. As the Al crystal mixing ratio increases, the film thickness and impurity concentration increase accordingly, so that cracks are prone to occur, and it is necessary to choose an appropriate Al crystal mixing ratio, film thickness and impurity concentration.

### [0017]

In the structure of the GaInN quantum well active layer 16, for example, is formed by four barrier layers with a film thickness of 5nm and an In crystal mixing ratio of 3%, and a three well layers with a film thickness of 2.5nm and an In crystal mixing ratio of 13% which are alternately stacked with one another, and the barrier layer (which is the uppermost layer) has an AlGaN layer with a film thickness of 5nm and an Al crystal mixing ratio of 15% and is provided for preventing the decomposition of the AlGaN layer.

## [0018]

In the manufacturing of the AlGaInN-based semiconductor device layer as shown in FIG. 1, a vapor deposition method such as a MOVPE or MBE method can be used. The MOVPE method can be used to obtain high-quality crystals at high growth rate, and the MBE method provides site observations according to the atomic layer level under high vacuum for a high-precision growth control.

#### [0019]

In the MOVPE method, trimethylgallium (hereinafter abbreviated as TMG), triethylgallium (hereinafter abbreviated as TEG), and trimethylaluminum (hereinafter abbreviated as TMA) can be used as an Al source are used as sources. A trialkyl metal compound such as trimethylindium (hereinafter abbreviated as TMI) or triethylindium (hereinafter abbreviated as TEI) can be used as an In source. A hydrazine derivative such as ammonia or dimethyl hydrazine is used as an N source. In addition, silane can be used as a Si source of an n-type impurity, and biscyclopentadienyl magnesium (hereinafter abbreviated as Cp2Mg) can be used as a Mg source of a p-type impurity. These source gases are hydrogen, nitrogen or argon used as a carrier gas for supply.

## [0020]

On the other hand, in the MBE method, a metal Ga, Al, In, Si or Mg can be used as a Group III source and an impurity source respectively, and a gas such as nitrogen and ammonia can be used as an N source which is excited by high-frequency plasma or the like. In general, the MBE method can lower the growth temperature when compared with the MOVPE method, and can perform the growth in a non-equilibrium state, but in the case of AlGaInN-based semiconductor crystals, the crystal quality such as hole mobility can be observed. In the MBE method, the growth is preferably performed at a high temperature as much as possible..

## [0021]

The semiconductor laser so constructed will be studied. Since the coefficient of thermal expansion Al<sub>2</sub>O<sub>3</sub> used as the substrate is  $8.0 \times 10^{-6}$ /K, and the coefficient of thermal expansion of the AlGaInN-based semiconductor used as the group III-V compound semiconductor layer is  $4.0 \sim 5.5 \times 10^{-6}$ /Km (i.e. the coefficient of thermal expansion of the group III-V compound semiconductor layer is smaller than the coefficient of thermal expansion of the substrate), therefore after the epitaxial growth of the group III-V compound semiconductor layer performed at high temperature is

completed, a compressive stress is acted on a surface of the group III-V compound semiconductor layer to warp the surface of the group III-V compound semiconductor layer during the process of cooling the group III-V compound semiconductor layer to room temperature. However, a back layer 112 is formed on the back surface of the substrate which is the side without the group III-V compound semiconductor layer and made of a material with a coefficient of thermal expansion smaller than that of the Al<sub>2</sub>O<sub>3</sub> substrate such as ZnO (with a coefficient of thermal expansion equal to 2.9×10<sup>-6</sup>/K). By controlling the film thickness, structure, and film formation temperature, the thermal stress can be reduced to suppress the warpage of the semiconductor device. As a result, this invention can prevent crystal defects or cracks occurred in the semiconductor device layer to improve the property or reliability of the device. In addition, the back layer of the Al<sub>2</sub>O<sub>3</sub> substrate is preferably made of Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, or GaN in addition to ZnO.

## [0022]

With reference to FIG. 1 for the manufacturing method of the semiconductor laser device, the plane (0001) is used as a main surface, and a double-sided polished monocrystalline Al<sub>2</sub>O<sub>3</sub> mirror is used as the substrate 11, and a ZnO layer 112 is first formed on the back surface of the substrate. In the method of manufacturing the ZnO film, there are chemical vapor transport, MOVPE or MBE method used for epitaxial growth, and a sputtering method for polycrystalline film growth. For example, in the MOVPE method, an excimer laser (wavelength of 248 nm) is irradiated using diethyl zinc and NO 2 as a raw material to obtain an epitaxial film at 500 ° C, wherein a laser ablation method is used).

## [0023]

Secondly, the degreased and cleaned Al<sub>2</sub>O<sub>3</sub> substrate 11 is placed in a high vacuum growth chamber heated at 750° C for 10 min. in the atmosphere having an oxygen partial pressure of  $3\times10^{-6}$ Torr, and the back surface of the substrate back is cleaned. Subsequently, the substrate temperature is brought to  $600^{\circ}$  C, and an excimer laser is irradiated on the ZnO sintered target, and the raw material is evaporated to a thickness of 2  $\mu$  m on the substrate. Thereafter, an atmosphere of the growth chamber is set to 1 atm of oxygen and annealed at 500 ° C. to form a ZnO layer 112.

#### [0024]

Further, the process proceeds to a step of growing a semiconductor laser element layer on the surface side of the Al<sub>2</sub>O<sub>3</sub> substrate 11 using the MOVPE method.

### [0025]

The substrate is placed on a susceptor in a reaction chamber and heated at  $1120 \,^{\circ}$  C. for 10 minutes in a hydrogen atmosphere of 300 Torr to clean the surface of the substrate. Subsequently, the substrate temperature is lowered to 500  $^{\circ}$  C and hydrogen and TMG are added to the carrier gas and TMG, respectively.

By using hydrogen as a carrier gas, and TMG and ammonia as source gases, a GaN buffer layer 12 is deposited to a thickness of 40 nm on a substrate 11 which is a group V/III semiconductor substrate supplied with a molar ratio (hereinafter abbreviated as V/III ratio) of 5000. Secondly, only the supply of TMG is stopped, and the temperature is raised to  $1000^{\circ}$  C. After the temperature reaches  $1000^{\circ}$  C, the supply of TMG is resumed, and the V/III ratio is set to 2500, while increasing the temperature gradually. Finally, silane is added at  $1060^{\circ}$  C to grow an n-type GaN contact layer 13 with a film thickness of  $3\mu m$ , and then TMA is added to grow the n-type AlGaN cladding layer 14 to 500nm. The vapor phase ratio of TMA to TMG is 10%. Further, the supply of TMA and silane is stopped to grow the GaN light guide layer 15 to 100 nm.

### [0026]

After the growth of the GaN light guide layer 15, the supply of TMG is stopped and the temperature is lowered to 810°C. After the temperature reaches 810°C, the carrier gas is switched to argon (Ar), and in the well layer, the TEG and TMI are supplied so that the gas phase ratio of TMI is 85% and the V / III ratio is 10000. In addition, the GaInN quantum well active layer 16 is formed while the gas phase ratio of TMI is set to 15% and the V / III ratio is set to 6000 in the barrier layer.

## [0027]

Next, the substrate temperature is raised to 1030°C, and the carrier gas is again switched to hydrogen, and TMG and ammonia are used to grow the GaN light guide layer 15 to 100nm. Subsequently, TMA and Cp2Mg are added to grow the p-type AlGaN cladding layer 17 to 500nm, and then the supply of the source gas is stopped and the temperature is cooled down to room temperature.

### [0028]

Therefore, a group III-V compound semiconductor layer can be formed. As another method of manufacturing the aforementioned semiconductor laser device layer, an MBE method can be used. In addition, this method can be combined with the MOVPE method and the MBE method, wherein the n-type layer is grown on a side of

the substrate by the MOVPE method, and the active layer and the p-type layer are grown by the MBE method. In the MBE, no hydrogen passivation occurs, so that the p-type conduction can be achieved without heat treatment.

### [0029]

When the warpage of the wafer obtained in the above crystal growth step is measured, it is found that the curvature radius is 31.1 m. As compared with 8.6 m in the case of the conventional device structure in which the ZnO layer 112 is not provided on the back surface of the substrate, the warpage is almost eliminated. This is considered due to the compressive stress acting on the laser device layer during the cooling process from the growth temperature to the room temperature is offset by the compressive stress acting on the ZnO layer on the back surface of the substrate.

## [0030]

This wafer is processed into a single mode laser device, wherein processes such as photolithography, dry etching, buried regrowth, electrode evaporation are used. Firstly, stripe SiO<sub>2</sub> with a width of 3 µm is formed and used as a mask to dry-etch the p-type AlGaN cladding layer 17 into a ridge shape with a depth of 400 nm. Secondly, an n-type GaN current blocking layer 18 is selectively grown to 400 nm by the MOVPE method. After that, the SiO<sub>2</sub> mask is removed, and the p-type GaN contact is formed by the MOVPE method, so as to grow the p-type GaN contact layer 19 to 400nm. Further, in order to form the n-type electrode 111, the p-type GaN contact layer 19 is dry-etched from the p-type GaN contact layer 14 to the n-type AlGaN cladding layer 13 to expose the n-type GaN contact layer.

## [0031]

The heat treatment for the activation of the Mg acceptor may be performed in the reaction chamber after the completion of the growth, or performed in a heat treatment furnace once the Mg acceptor is taken out, or performed simultaneously with the sintering of the electrode evaporation. The heat treatment conditions, for example, are set at 600°C for 20 minutes in a nitrogen atmosphere.

### [0032]

Finally, the electrode deposition and sintering are performed. For example, an Mg/Au electrode in which an Mg film and an Au film are sequentially stacked is used as the p-type electrode 110. An Ti/Mo/Pt/Au electrode is formed on the n-type electrode 111.

## [0033]

The wafer is cleaved to have a resonator length such as 0.7μm, and both end surfaces of the cover are applied with an appropriate coating and then separated into a laser device and mounted on a heat sink in a junction-down manner. When the operating characteristics at room temperature were evaluated, the oscillation wavelength was 404 nm, the threshold current was 94 mA, the external differential quantum efficiency was 70%, and the applied voltage at the start of laser oscillation was 5.9 V.

## [0034]

#### (Second Embodiment)

With reference to FIG. 2 for the cross-sectional view showing the structure of a semiconductor laser device in accordance with the second embodiment of the present invention, the numerals used in the figure are described below: 21 is an n-type 6H-SiC substrate (with a thickness of 150μm and a carrier density of 2×10<sup>18</sup>cm<sup>-3</sup>), 22 is an AlN buffer layer (with a film thickness of 10nm), 23 is an AlGaInN buffer layer (with a film thickness of 20nm), 24 is an n-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 5×10<sup>17</sup>cm<sup>-3</sup>), 25 is a GaN light guide layer (with a film thickness of 100nm), 26 is a GaInN quantum well active layer, 27 is a p-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 3×10<sup>17</sup>cm<sup>-3</sup>), 28 is an n-type GaN current blocking layer (with a film thickness of 400nm and a carrier density of 5×10<sup>17</sup>cm<sup>-3</sup>), 29 is a p-type GaN contact layer (with a film thickness of 400nm and a carrier density of 8×10<sup>17</sup>cm<sup>-3</sup>), 210 is a p-type electrode. In addition, a Ni/Au layer 211 (with a film thickness of 400nm) is formed on the back surface of the substrate to serve as the metal layer.

### [0035]

It is noteworthy that the conductivity type of the substrate may be an n-type, a p-type, or an insulating. In addition, a substrate inclined in a certain direction as well as a low index surface may be used as the substrate surface orientation. For example, a substrate tilted at 3 degrees from the (0001) plane of 4H- SiC in the [11-20] direction may be used.

## [0036]

The semiconductor laser device constructed as described above will be studied. Since the coefficient of thermal expansion of SiC used as a substrate is  $4.2 \times 10^{-6}$ /K and the coefficient of thermal expansion of a GaN-based semiconductor is  $5.5 \times 10^{-6}$ /K (i.e. the coefficient of thermal expansion of the Group III-V compound semiconductor

layer is greater than that of the substrate), tensile stress normally acts on the group III-V compound semiconductor layer, and the surface of the group III-V compound semiconductor layer may be warped downwardly during the process of cooling to room temperature after completion of epitaxial growth at high temperature. For example, a metal substance such as SiC with a coefficient of thermal expansion greater than that of the substrate can be used to form the back layer 112, so that the thermal stress can be reduced by controlling the film thickness, structure, and film formation temperature to suppress the warpage of the semiconductor device. As a result, the crystal defects and cracks occurred in the semiconductor device layer can be prevented to improve the property and reliability of the semiconductor device. Further, examples of suitable materials that can be used for the back layer of the SiC substrate include Al in addition to Ni and Au.

# [0037]

The differences between this embodiment and the first embodiment are described based on the manufacturing process of the semiconductor laser device as shown in FIG. 2.

## [0038]

In the substrate 21, monocrystalline n-type 6H-SiC with a Si surface (0001) serving as a main surface and a polished double-sided mirror is used. Firstly, a Ni/Au layer 211 is formed on the back surface of the substrate a normal vacuum evaporation method. The degreased and cleaned substrate 21 is placed into a vacuum deposition tank, and the substrate temperature is set to 350°C, and the Ni (10nm) and Au (390nm) are sequentially deposited by evaporation in the vacuum below 5×10<sup>-7</sup>Torr. Ni is used to enhance adhesion between the substrate and Au. It is noteworthy that the coefficient of thermal expansion of Ni is  $38\times10^{-6}$ /K, and the coefficient of thermal expansion of Au is  $43\times10^{-6}$ /K.

## [0039]

Subsequently, a semiconductor laser device layer is grown on the surface of the SiC substrate 21 by using the MOVPE method. The substrate is placed on a susceptor in a reaction chamber and heated at 1120 ° C. for 10 minutes in a hydrogen atmosphere of 300 Torr to clean the surface of the substrate. At this time, the Ni/Au layer 211 on the back surface with a temperature exceeding the melting point improves the fluidity, and the effect of the thermal stress between the substrate 21 and the Ni/Au layer can be released. Subsequently, the substrate temperature is lowered to 1000 ° C., and

hydrogen is used as a carrier gas, and TMA and ammonia are used as the source gases and the TMA and ammonia are deposited on the substrate 21, and an AlN buffer layer 22 is deposited to a thickness of 10 nm, and then the supply of TMA is stopped. Further, the substrate temperature is lowered to 910 ° C., and TMA, TMG, and TMI are supplied to grow the AlGaInN buffer layer 23 to 20 nm. This layer has an effect of suppressing the occurrence of cracks due to the effect existing between the respective layers of the laser structure. The growth step after the n-type AlGaN cladding layer 24 is the same as the description given in the first embodiment.

[0040]After the warpage of the wafer resulted from the crystal growth process is measured, it is found that the radius of curvature is 24.8m. Compared with the value 13.5 m for the back surface of the substrate of the conventional device structure without having the Ni/Au layer 211, warpage has been suppressed. Although cracks are observed in the device layer of the conventional structure, the cracks are not observed in the structure of this embodiment. This is considered due to the phenomenon of the tensile stress acting on the laser element layer during the cooling process from the growth temperature to the room temperature is offset by the tensile stress acting on the Ni/Au layer on the back surface of the substrate.

[0041]The Ni/Au layer 211 on the back surface of the substrate is sufficiently alloyed relative to the n-type SiC (which is considered as an ohmic electrode) during the growth of the laser device layer, so that it also acts as the n-type electrode in the device structure as shown in FIG. 2.

#### [0042]

### (Third Embodiment)

With FIG. 3 for the cross-sectional view showing the structure of a semiconductor laser device in accordance with the third embodiment of the present invention, the numerals used in the figure are described below: 31 is an n-type 6H-SiC substrate (with a thickness 150μm of a carrier density of 2×10<sup>18</sup>cm<sup>-3</sup>), 32 is an AlN buffer layer (with a film thickness of 10nm), 33 is an n-type GaN layer (with a film thickness of 16μm and a carrier density of 7×10<sup>17</sup>cm<sup>-3</sup>), 34 is a SiO<sub>2</sub> mask layer, 35 is an n-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 5×10<sup>17</sup>cm<sup>-3</sup>), 36 is a GaN light guide layer (with a film thickness of 100nm), 37 is a GaInN quantum well active layer, 38 is a p-type AlGaN cladding layer (with a film thickness of 500nm and a carrier density of 3×10<sup>17</sup>cm<sup>-3</sup>), 39 is an n-type GaN current blocking layer (with a film thickness of 400nm and a carrier density of 5×10<sup>17</sup>cm<sup>-3</sup>), 310 is a p-type GaN contact layer (with a film thickness of 400nm and a carrier density of 8×10<sup>17</sup>cm<sup>-3</sup>), and 311 is a p-type electrode. In addition, a Ni/Au layer 312 (with a film thickness of 500nm) is formed on the back surface of the substrate.

### [0043]

This embodiment is substantially the same as the second embodiment, but SiO<sub>2</sub> is embedded in a stripe shape in the group III-V compound semiconductor layer on the substrate. In this embodiment, Si<sub>3</sub>N<sub>4</sub> can also be used, in addition to the use of SiO<sub>2</sub>, and there is no necessity of being formed in the stripe shape. The same works as long as the SiO<sub>2</sub> is not embedded continuously.

#### [0044]

Aiming at the difference between this embodiment and the second embodiment, it is described based on the manufacturing process of the semiconductor laser device as shown in FIG. 3. Same as the second embodiment, a Ni/Au layer 312 is formed on the back surface of the substrate by a normal vacuum evaporation method, and then a semiconductor laser device layer is grown on the front surface of the substrate by the MOVPE method.

## [0045]

After the growth of the AlN buffer layer 32, an n-type GaN layer 33 having a thickness of 2  $\mu$ m is grown, and then a SiO<sub>2</sub> mask layer 34 (having a thickness of 100 nm) is formed by plasma CVD or the like, and a striped opening with a pitch of 4 $\mu$ m and a width of 1.5 $\mu$ m is formed in the [1-100] direction of the GaN by the photolithography and dry etching processes.

#### [0046]

Once again, the substrate is placed on a susceptor in the MOVPE reaction chamber to selectively grow the n-type GaN layer 33. In this process, no deposition of polycrystalline GaN on the mask takes place, the GaN is grown laterally from the opening and combined at the central part of the mask, and a flat surface (0001) is obtained at the growth of approximately 4µm in thickness. Secondly, the stripe shaped SiO<sub>2</sub> mask layer 34 (with a thickness of 100nm) of the second layer is formed in the same direction as above by the plasma CVD method or the like. At this time, the opening of the mask is shifted to the mask of the first layer to form the mask of the second layer.

[0047] In addition, the substrate is placed on the susceptor in the MOVPE reaction chamber, so that a flat surface (0001) deposited on the n-type GaN layer 33 and grown laterally to form a laser device layer having a thickness of about 10  $\mu$ m can be obtained. By means of the second lateral growth, a threading dislocation occurred at

the junction of the SiC substrate 31 and extending to the top (the density near the junction is  $1\times10^8$ cm<sup>-2</sup>) will disappear from the SiO<sub>2</sub> mask layer. Since it can hardly bend in a lateral direction, the density of the threading dislocation at the uppermost part of the n-type GaN layer 33 is reduced to  $5\times10^5$ cm<sup>-2</sup>. The subsequent growth process of the n-type AlGaN cladding layer 35 is the same as described in the first embodiment.

#### [0048]

In the conventional device structure of which the Ni/Au layer 312 is not provided on the back surface of the substrate, cracks occur in the lateral growth of the n-type GaN layer 33, and a laser device layer cannot be formed on the substrate, but in the structure of this embodiment, cracks do not occur and a high-quality laser device layer with a dislocation density around 10<sup>5</sup>cm<sup>-2</sup> can be formed.

## [0049]

## (Fourth Embodiment)

With reference to FIG. 4 for the cross-sectional view showing the structure of a substrate of a semiconductor laser device in accordance with the fourth embodiment of the present invention, this embodiment similar to the first and second embodiments has the N-containing group III-V compound semiconductor layer formed on a main surface on a side of the substrate, and thus the description of the similarity will not be repeated, and only the technical characteristics of the substrate are described. In this embodiment, the warpage occurred on this side of the substrate during the cooling process after the crystal growth of the group III-V compound semiconductor layer can be prevented.

#### [0050]

In the fourth embodiment as shown in FIG. 4(a), an n-type 6H-SiC substrate (with a thickness of 150 $\mu$ m and a carrier density of  $2\times10^{18} \text{cm}^{-3}$ ) having a Si surface (0001) is provided to serve as a main surface. For example, a groove (with a width of 150 $\mu$ m and a depth of 110 $\mu$ m) extending in the [1-100] direction is formed at a distance of 150 $\mu$ m on the back surface, so that a substrate having a portion with a thinner thickness than other portions can be manufactured by photolithography, dry etching and/or wet etching.

### [0051]

In the case of forming the AlGaInN based semiconductor laser device as described in

the second embodiment on the surface of the substrate 41, there was no large difference in the warpage of the wafer when the device was formed on a substrate having uniform thickness. However, when the cross section is observed with a transmission electron microscope, no groove was formed in a device layer on the substrate, and the density of threading dislocation reaches  $10^7 \sim 10^8 \text{cm}^{-2}$ , but grooves formed on a device layer of the thinner portion of the substrate were suppressed to  $10^6 \text{cm}^{-2}$  or below. Obviously, there is a tendency for the thinner portions of the substrate to have defects or cracks. In other words, some of the stress can be relaxed by forming grooves on the substrate and thinning the substrate, since the defects usually occur on a side of the substrate where the strength is lowered. Therefore, a high-quality crystal on the device layer can be obtained.

### [0052]

In addition, the grooves on the back surface of the substrate may be used for separating or cleaving the devices, wherein the grooves of this embodiment are formed in the stripe shape. Of course, the grooves are not limited to the stripe shape, but they can be in a lattice form.

## [0053]

Further, as shown in FIG. 4(b), an n-type GaN layer 42 may be grown on a substrate, GaN may be laterally grown on the  $SiO_2$  mask layer 43 to form a flat n-type GaN layer 42, and then an AlGaInN-based semiconductor laser device may be formed thereon. The shape of the  $SiO_2$  mask layer 43 is, for example, in a stripe shape extending in the GaN [1 - 100] direction, and a striped opening with a width of 5  $\mu$ m is provided at a pitch of 10  $\mu$ m.

#### [0054]

### (Fifth Embodiment)

With reference to FIG. 5 for the cross-sectional view showing the structure of a semiconductor laser device in accordance with the fifth embodiment of the present invention, this embodiment similar to the first and second embodiments has the N-containing group III-V compound semiconductor layer formed on a main surface on a side of the substrate, and thus the description of the similarity will not be repeated, and only the technical characteristics of the substrate are described. In this embodiment, the warpage occurred on this side of the substrate during the cooling process after the crystal growth of the group III-V compound semiconductor layer can be prevented.

## [0055]

In FIG. 5, the material of the substrate is, for example, Al<sub>2</sub>O<sub>3</sub>, and the numeral 52 represents a manufacture damaged layer disposed on the back surface of the Al<sub>2</sub>O<sub>3</sub> substrate 51. For example, a substrate is cut out from an ingot, and a surface side is mirror-polished, but the back surface is remained in a state as is or kept in a state after the wrap etching has been applied. Since there are damages of the substrate remained from the manufacture, the way of applying the stress has changed when the substrate is formed on the AlGaInN-based semiconductor device. In the semiconductor device layer, a compressive stress usually acts on the semiconductor device to warp a surface of the semiconductor device upward. When a force is applied in a direction against the warpage, a substantially flat surface can be achieved.

## [0056]

In order to prevent warpage of the substrate or suppress the occurrence of crystal defects and cracks in the device layer when the difference of the coefficients of the thermal expansion between the substrate and the semiconductor device layer is large, means other than those described above may be used. For example, the back surface of the substrate is made porous, or a honeycomb layer is provided on the back surface of the substrate, or a fine particle layer is provided on the back surface of the substrate.

### [0057]

#### (Sixth Embodiment)

With reference to FIG. 6 for the cross-sectional view of a manufacturing process of a semiconductor laser device in accordance with the sixth embodiment of the present invention, the numerals used in FIG. 6 are described below: 61 is an Al<sub>2</sub>O<sub>3</sub> substrate, 62 is a SiO<sub>2</sub> layer, 63 is an n-type GaN layer, 64 is an AlGaInN-based laser device layer, 65 is a p-type electrode, and 66 is an n-type electrode.

#### [0058]

The manufacturing method of a semiconductor laser device and the manufacturing method of a semiconductor substrate in accordance with an embodiment of the present invention will be described in conjunction with the illustration by FIG. 6a below.

#### [0059]

In the Al<sub>2</sub>O<sub>3</sub> substrate 61, the monocrystalline Al<sub>2</sub>O<sub>3</sub> plane (0001) (with a thickness of 150µm) is used as a main surface and polished by double-sided mirror polishing.

Firstly, a SiO<sub>2</sub> layer 62 (with a thickness of 2µm) is formed on the back surface of the substrate by a plasma CVD method or the like to serve as the back layer, and the material of SiO<sub>2</sub> layer 62 has a coefficient of thermal expansion smaller than the coefficient of thermal expansion of the substrate.

### [0060]

Secondly, the MOVPE method is used to grow a GaN layer 63 (with a thickness of  $2\mu m$ ) on the substrate surface side, and a SiO<sub>2</sub> mask layer 62 (with a thickness of 100nm) is formed, and a striped opening having a width of 3  $\mu m$  is provided in the [1-100] direction of GaN with a pitch of 8  $\mu m$  by photolithography and dry etching process.

### [0061]

The substrate is placed on a susceptor in an MOVPE reaction chamber, and an n-type GaN layer 63 (with a carrier density of  $1\times10^{18} \text{cm}^{-3}$ ) is selectively grown. During this process, there is no deposition of polycrystalline GaN on the mask occurs, and GaN grows laterally from the opening and combines at the center of the mask, resulting in a flat surface (0001) at a growth of about 6  $\mu$ m thick and continues to grow until a thickness reaches about 100  $\mu$ m or above.

As a result, a threading dislocation (wherein its density near the junction is  $2\times10^{10}$ cm<sup>-2</sup>) occurred at the junction between the Al<sub>2</sub>O<sub>3</sub> substrate 61 and extending upward will disappear from the SiO<sub>2</sub> mask layer and hardly bent in a lateral direction, so that the density of threading dislocations is reduced to about  $10^4$ cm<sup>-2</sup> at the uppermost portion of the n-type GaN layer 63.

### [0062]

Although the GaN thick film can be formed by the MOVPE method, the hydride vapor phase epitaxy (HVPE) method can also be used as another method. Compared with the MOVPE method, the HVPE method has a higher growth rate which is suitable for thick film growth.

#### [0063]

According to the aforementioned steps, a group III-V compound semiconductor layer having a thermal expansion coefficient smaller than that of the substrate is formed on a main surface of the substrate opposite to the side on which the back layer is formed.

### [0064]

When the growth of GaN thick film is completed and the film is cooled to room temperature, the warpage of the substrate can be substantially suppressed. In this

state, an n-type GaN substrate 63 having a thickness of about 100 μm can be obtained by removing the SiO<sub>2</sub> layer 62, the Al<sub>2</sub>O<sub>3</sub> substrate layer 61 and the SiO<sub>2</sub> mask layer 62.

## [0065]

As described in the third embodiment, an AlGaInN-based laser device layer 64 is formed on this substrate, and a p-type electrode 65 is formed on the p-type contact layer of the front surface of the substrate and an n-type electrode 66 is formed on the back surface of the substrate.

#### [0066]

Although SiO<sub>2</sub> is used as the back layer in this embodiment, a ZnO layer or a Si<sub>3</sub>N<sub>4</sub> layer can also be used as the back layer. For example, SiC can be used for the substrate, and a metal layer (including Ni, Au, Al, In or Ga) is used as the back layer. After a back layer made of a material having a coefficient of thermal expansion greater than the coefficient of thermal expansion of the substrate can be formed on a main surface on a side of the substrate, and a group III-V compound semiconductor layer made of a material having a coefficient of thermal expansion greater than substrate is formed on a main surface on the other side of the substrate, the back layer of the substrate and the substrate are removed to obtain a semiconductor substrate.

## [0067]

As described above, the present invention is described in conjunction with its embodiments. Although the description of these embodiments is directed to a semiconductor laser device, it can also be applied to light-emitting diodes, photodiodes, field-effect transistors or other semiconductor devices.

## [0068]

#### [Effect of the Invention]

In summation of the description above, the present invention can reduce the thermal stress proportional to the difference in the coefficient of thermal expansion between the III-V semiconductor crystal and the substrate, to achieve the effects of preventing the occurrence of crystal defects or cracks and improving the property or reliability of the semiconductor device.

#### [Brief Description of the Drawings]

FIG. 1 is a cross-sectional view showing the structure of a semiconductor laser device

in accordance with a first embodiment of the present invention.

- FIG. 2 is a cross-sectional view showing the structure of a semiconductor laser device in accordance with a second embodiment of the present invention.

- FIG. 3 is a cross-sectional view showing the structure of a semiconductor laser device in accordance with a third embodiment of the present invention.

- FIG. 4 is a cross-sectional view showing the structure of a semiconductor laser device in accordance with a fourth embodiment of the present invention.

- FIG. 5 is a cross-sectional view showing the structure of a semiconductor laser device in accordance with a fifth embodiment of the present invention.

- FIG. 6 is a cross-sectional view showing the structure of a semiconductor laser device in accordance with a sixth embodiment of the present invention.

## [Description of numerals]

- 11, 51, 61 Al<sub>2</sub>O<sub>3</sub> substrate

- 12 GaN buffer layer

- 13 n-type GaN contact layer

- 14, 24, 35 n-type AlGaN cladding layer

- 15, 25, 36 GaN light guide layer

- 16, 26, 37 GaInN quantum well active layer

- 17, 27, 38 p-type AlGaN cladding layer

- 18, 28, 39 n-type GaN current blocking layer

- 19, 29, 310 p-type GaN contact layer

- 110, 210, 311, 65 p-type electrode

- 111, 66 n-type electrode

- 112 ZnO layer

- 21, 31, 41 n-type 6H-SiC substrate

- 22, 32 AlN buffer layer

- 23 AlGaInN buffer layer

- 211, 312 Ni/Au layer

- 33, 42, 63 n-type GaN layer

- 34, 43 SiO<sub>2</sub> mask layer

- 52 manufacture damaged layer

- 62 SiO<sub>2</sub> layer

- 64 AlGaInN-based laser device layer

#### Translator's Declaration

# I Joanna Wang, hereby declare:

I possess advanced knowledge of the Japanese and English languages. My qualifications are as follows:

I currently work for Central Translation Service, dealing with translation projects.

I hereby certify that I translated "Ban JP2000022283A," from Japanese to English and that, to the best of my ability, my English translation, attached hereto, is a true and correct translation.

I further certify and I am competent in both English and Japanese to render and certify such translation. I understand that willful false statements and the like are punishable by a fine or imprisonment or both (18 U.S.C. 1001). I declare under penalty of perjury under the laws of the United States of America that all statements made on information and belief are believed to be true.

If called upon to testify at a deposition in connection to this translation, I will make myself available.

Date:

MAR 09 2022