# IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

TQ DELTA, LLC,

Plaintiff,

V.

2WIRE, INC.

Defendant.

Civil Action No. 13-cv-1835-RGA

# OPENING EXPERT REPORT ON INVALIDITY OF DR. KRISTA S. JACOBSEN FOR FAMILY 3 PATENTS

TQ Delta Exhibit 2009 COMMSCOPE, INC. v. TQ DELTA LLC IPR2023-00064

## **Table of Contents**

|      |                                                  | Page |

|------|--------------------------------------------------|------|

| I. I | Introduction                                     | 1    |

| II.  | Background and Qualifications                    | 1    |

| III. | Compensation                                     | 3    |

| IV.  | Documents and Other Materials Relied Upon        | 3    |

| V.   | Legal Principles                                 | 4    |

| A.   | Anticipation Under 35 U.S.C. § 102               | 4    |

| B.   | Obviousness Under 35 U.S.C. § 103                | 5    |

| C.   | Indefiniteness Under 35 U.S.C. § 112, ¶ 2        | 12   |

| D.   | Written Description Under 35 U.S.C. § 112, ¶ 1   | 13   |

| E.   | Enablement Under 35 U.S.C. § 112, ¶ 1            | 13   |

| VI.  | Level of Skill in the Art                        | 13   |

| VII. | Background of the Technology                     | 14   |

| A.   | Forward Error Correction and Reed Solomon Coding | 14   |

| B.   | Interleaving and Deinterleaving                  | 16   |

| C.   | Shared Memory                                    | 21   |

| D.   | Latency Paths                                    | 24   |

| E.   | Overview of DSL Standards Groups                 | 25   |

| 1    | 1. T1E1.4                                        | 25   |

| 2    | 2. ITU-T Study Group 15, Question 4              | 26   |

| 3    | 3. Operation of DSL Standards Meetings           | 28   |

| F.   | Interleaving and FEC in DSL Standards            | 29   |

| 1    | 1. Nomenclature                                  | 30   |

| 2    | 2. G.992.1 (1999)                                | 31   |

| 3    | 3. G.992.2 (1999)                                | 35   |

| 4    | 4. G.993.1 (2004)                                | 38   |

| G.   | The Family 3 Patents                             | 42   |

| 1    | 1. Asserted Claims Family 3 Patents              | 45   |

| 2    | 2. Provisional Application                       | 48   |

| 3    | 3. File History                                  | 50   |

| 4    | 4. Claim Construction                            | 54   |

| VIII.     | Analysis of Invalidity Under 35 U.S.C. § 112                                                   | 56    |

|-----------|------------------------------------------------------------------------------------------------|-------|

| A.        | 35 U.S.C. § 112, ¶ 2 – Indefiniteness                                                          | 56    |

| B.        | 35 U.S.C. § 112, ¶ 1 – Written Description and Enablement                                      | 57    |

| C.        | Certificates of Correction                                                                     | 58    |

| IX.       | Analysis of the Prior Art                                                                      | 60    |

| A.        | The Asserted Claims Are Obvious Over LB-031                                                    | 60    |

| 1.        | Public Availability of LB-031                                                                  | 60    |

| 2.        | Brief Description of LB-031                                                                    | 62    |

| 3.        | Claim 1 of the '048 Patent                                                                     | 66    |

| 4.        | Claim 5 of the '381 Patent                                                                     | 76    |

| 5.        | Claim 13 of the '882 Patent                                                                    | 81    |

| 6.        | Claim 19 of the '473 Patent                                                                    | 82    |

| B.        | The Asserted Claims Are Obvious Over the Combination of LB-031 and Mazzon                      | ıi 86 |

| 1.        | Brief Description of LB-031                                                                    | 87    |

| 2.        | Brief Description of Mazzoni                                                                   | 87    |

| 3.        | Claim 1 of the '048 Patent                                                                     | 91    |

| 4.        | Claim 5 of the '381 Patent                                                                     | 103   |

| 5.        | Claim 13 of the '882 patent                                                                    | 108   |

| 6.        | Claim 19 of the '473 Patent                                                                    | 109   |

| 7.        | Motivation to Combine LB-031 and Mazzoni                                                       | 117   |

| C.<br>Rec | The Asserted Claims Are Obvious Over Fadavi-Ardekani in Combination With I ommendation G.993.1 |       |

| 1.        | Brief Description of Fadavi-Ardekani                                                           | 119   |

| 2.        | Brief Description of G.993.1.                                                                  | 124   |

| 3.        | Claim 1 of the '048 Patent                                                                     | 124   |

| 4.        | Claim 5 of the '381 Patent                                                                     | 140   |

| 5.        | Claim 13 of the '882 patent                                                                    | 146   |

| 6.        | Claim 19 of the '473 Patent                                                                    | 147   |

| 7.        | Motivation to Combine Fadavi-Ardekani and G.993.1                                              | 156   |

| D.        | The Asserted Claims Are Obvious Over Fadavi-Ardekani in Combination with 92.2                  | 159   |

| 1.9       |                                                                                                |       |

| 2.        | *                                                                                              |       |

| 3.        |                                                                                                |       |

| 1         | Claim 13 of the '882 Patent                                                                    | 172   |

| 5.                                                                                                                                     | Claim 19 of the '473 Patent                                                   | 173 |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|

| 6.                                                                                                                                     | Motivation to Combine Fadavi-Ardekani and G.992.2                             | 177 |

| E.                                                                                                                                     | Claim 19 of the '473 Patent Is Obvious Over Voith in Combination with LB-031. | 180 |

| 1.                                                                                                                                     | Brief Description of Voith                                                    | 181 |

| 2.                                                                                                                                     | Claim 19 of the '473 Patent                                                   | 184 |

| 3.                                                                                                                                     | Motivation to Combine Voith and LB-031                                        | 191 |

| F. <b>(</b>                                                                                                                            | Claim 19 of the '473 Patent is Obvious In View of Mazzoni and G.993.1         | 193 |

| 1.                                                                                                                                     | Brief Description of Mazzoni                                                  | 193 |

| 2.                                                                                                                                     | Brief Description of G.993.1                                                  | 193 |

| 3.                                                                                                                                     | Claim 19 of the '473 Patent                                                   | 193 |

| 4.                                                                                                                                     | Motivation to Combine Mazzoni and G.993.1                                     | 197 |

| G. Claim 19 of the '473 Patent is Obvious In View of Voith and G.993.1, or, In the Alternative, In View of Voith, G.993.1 and Mazzoni. |                                                                               | 199 |

| 1.                                                                                                                                     | Brief Descriptions of Voith, G.993.1, and Mazzoni.                            | 199 |

| 2.                                                                                                                                     | Claim 19 of the '473 Patent                                                   | 199 |

| 3.                                                                                                                                     | Motivation to Combine Voith and G.993.1                                       | 202 |

| 4.                                                                                                                                     | Mazzoni Supplies Any Disclosure Missing from G.993.1 and Voith                | 204 |

| 5.                                                                                                                                     | Motivation to Combine Mazzoni with Voith and G.993.1.                         | 205 |

| X. S                                                                                                                                   | Secondary Considerations of Non-Obviousness                                   | 206 |

| XI. (                                                                                                                                  | Conclusion                                                                    | 207 |

#### I. INTRODUCTION

1. My name is Krista S. Jacobsen. I have been asked by Defendant 2Wire, Inc. to provide this report in connection with the above-captioned District Court action. Specifically, I have been asked to opine on the validity of claim 1 of U.S. Patent No. 8,276,048 ("the '048 patent"), claim 5 of U.S. Patent No. 7,836,381 ("the '381 patent"), claim 13 of U.S. Patent No. 7,844,882 ("the '882 patent"), and claim 19 of U.S. Patent No. 8,495,473 ("the '473 patent"). I understand that plaintiff TQ Delta, LLC has alleged that certain 2Wire products infringe these claims. I further understand that these patents are referred to in this action as being part of "Family 3."

#### II. BACKGROUND AND QUALIFICATIONS

- 2. I was awarded a Ph.D. in Electrical Engineering from Stanford University in 1996, and a Master's Degree in Electrical Engineering in 1993, also from Stanford University. I held a National Science Foundation Graduate Fellowship from 1991-94 and an IBM Graduate Fellowship from 1994-95. In 1993, I was awarded an IEEE Communications Society Scholarship.

- 3. I hold a Bachelor of Science Degree in Electrical Engineering, summa cum laude, from the University of Denver, which I received in 1991. From 1986-91, I held a University of Denver Honors Scholarship, and from 1987-91, I held a Colorado Scholars Scholarship. I was elected to Phi Beta Kappa in 1988, and I received the University of Denver's Distinguished Senior Woman Award in 1990 and the University of Denver Pioneer Award in 1991. I won the Denver Section of the IEEE Student Paper Contest in 1991.

- 4. At Stanford, my Ph.D. research focused on technology for digital communications, including multicarrier modulation, discrete multi-tone (DMT) modulation, and orthogonal frequency division multiplexing (OFDM). My doctoral thesis topic was "Discrete

Multi-Tone-Based Communications in the Reverse Channel of Hybrid Fiber-Coax Networks." My research adviser was Dr. John M. Cioffi, who is known as the "father of digital subscriber lines (DSL)" and whose pioneering research in DSL earned him the Marconi Prize in 2006.

- 5. From 1996 to 2004, I worked as an engineer at Amati Communications

Corporation, which was acquired by Texas Instruments (TI) in 1998. I was part of the team that developed the world's first operational DMT-based VDSL transceivers. From 2004 to 2006, as a consultant, I assisted clients to determine and execute DSL standardization and product strategies, wrote computer simulations of multicarrier systems, and generated and presented technical tutorials.

- 6. From 1996 through 2006, I participated in several standards-setting organizations that standardized DSL systems, including ATIS T1E1.4 (later renamed NIPP-NAI), ETSI TM6, ITU-T Study Group 15, Question 4, and IEEE 802.3ah (Ethernet in the First Mile). I wrote and/or presented many dozens of technical contributions to these organizations.

- 7. I am a co-editor of two books on DSL technology and the author of several book chapters on multicarrier modulation, DSL technology, and DSL standardization. In addition, I have authored or co-authored numerous technical papers and magazine articles on multicarrier communications, and, in 2001-02, I co-edited an issue of the IEEE Journal on Selected Areas in Communication focused on twisted pair transmission.

- 8. I have over ten years of experience working in the development and standardization of DSL technologies, including those embodied in the ITU-T Recommendations involved in the above-captioned District Court actions. I am an inventor named on eleven patents solving issues presented by or related to multicarrier modulation. My experience

includes work in DSL technologies and the DSL industry both before and after the purported priority date of the Family 2 patents.

- 9. I am also licensed to practice before the Patent and Trademark Office. I am currently an attorney who serves as an expert consultant and witness for patent litigation, and I provide patent prosecution and counseling services in multiple areas, including telecommunications.

- 10. A detailed curriculum vitae showing more of my credentials is attached to this report as Appendix A.

#### III. <u>COMPENSATION</u>

11. I am being compensated for my time at the rate of \$400 per hour. This compensation is not contingent on my performance, the outcome of this matter, or any issues involved in or relating to this matter.

### IV. DOCUMENTS AND OTHER MATERIALS RELIED UPON

- 12. In forming the opinions set forth in this declaration, I have reviewed each of the Family 3 patents that were asserted by TQ Delta in this action U.S. Patent No. 7,831,890 ("the '890 Patent"), along with the '048, '381, '882, and '473 patents. Additionally, I have considered my own experience and expertise concerning the knowledge of a person having ordinary skill in the relevant art during the timeframe of the claimed priority date of the Family 3 patents. I have reviewed information generally available to, and relied upon by, a person having ordinary skill at the time of the alleged invention. I have also reviewed the parties' claim construction briefing and the Court's order on the same.

- 13. In addition, I have reviewed the materials listed in <u>Appendix B</u>.

- 14. I was told to assume that the earliest possible time of the alleged invention for each of the Family 3 patents is October 12, 2004, the date on which Provisional Application No.

60/618,269, was filed. I disagree, however, that the Family 3 patents are entitled to the priority date of the provisional application, as I explain below in Section VII.G.2. I am also informed, however, that once an accused infringer has introduced sufficient evidence to put at issue whether there is prior art alleged to anticipate the claims being asserted, and that prior art is dated earlier than the apparent effective date of the asserted patent claim, the patentee has the burden of going forward with evidence and argument to the contrary.

#### V. <u>LEGAL PRINCIPLES</u>

15. Although I am licensed to practice law, I am not offering any legal opinions in this Report. My opinions are based on the Court's constructions and, where the Court did not construe a term, the meaning that term would have had to a person having ordinary skill in the art in light of the specification and the prosecution history at the time of the filing of the earliest priority application.

#### A. Anticipation Under 35 U.S.C. § 102

16. I am informed and understand that to anticipate a patent claim under 35 U.S.C. §

102, a single asserted prior art reference must disclose each and every element of the claimed invention, either explicitly, implicitly, or inherently, to a person of ordinary skill in the art.

There must be no difference between the claimed invention and the disclosure of the alleged prior art reference as viewed from the perspective of the person of ordinary skill in the art.

Also, I understand that in order for a reference to be an anticipating reference, it must describe the claimed subject matter with sufficient clarity to establish that the subject matter existed and that its existence was recognized by persons of ordinary skill in the field of the invention. In addition, I am informed and understand that in order to establish that an element of a claim is "inherent" in the disclosure of an asserted prior art reference, extrinsic evidence (or the evidence outside the four corners of the asserted prior art reference) must make clear that the missing

element is necessarily found in the prior art, and that it would be recognized as necessarily present by persons of ordinary skill in the relevant field.

17. In my opinions below, when I say that a person of ordinary skill would understand, readily understand, or recognize that an element or aspect of a claim is disclosed by a reference, I mean that the element or aspect of the claim is disclosed explicitly to a person of ordinary skill in the art.

#### B. Obviousness Under 35 U.S.C. § 103

- 18. I am informed and understand that obviousness is a determination of law based on various underlying determinations of fact. In particular, these underlying factual determinations include (1) the scope and content of the prior art; (2) the level of ordinary skill in the art at the time the claimed invention was made; (3) the differences between the claimed invention and the prior art; and (4) the extent of any proffered objective indicia of nonobviousness. I understand that the objective indicia that may be considered in such an analysis include commercial success of the patented invention (including evidence of industry recognition or awards), whether the invention fills a long-felt but unsolved need in the field, the failure of others to arrive at the invention, industry acquiescence and recognition, initial skepticism of others in the field, whether the inventors proceeded in a direction contrary to the accepted wisdom of those of ordinary skill in the art, and the taking of licenses under the patent by others, among other factors.

- 19. To ascertain the scope and content of the prior art, it is necessary to first examine the field of the inventor's endeavor and the particular problem for which the invention was made. The relevant prior art includes prior art in the field of the invention, and also prior art from other fields that a person of ordinary skill in the art would look to when attempting to solve the problem.

- 20. I understand that a claim may be rendered obvious if a person having ordinary skill in the art would understand the claimed invention as a predictable variation of a known reference.

- 21. I am informed and understand that an obviousness evaluation can be made using either a single reference or a combination of several prior art references. An obviousness analysis involving two or more references generally requires a reason why a person having ordinary skill in the relevant field would have combined aspects of those references in the way the asserted patent claims do. I understand that the prior art references themselves may provide a suggestion, motivation, or reason to combine, but other times the link may simply be common sense. An obviousness analysis can recognize that market demand, rather than scientific literature, often drives innovation, and that is sufficient motivation to combine references.

- 22. I understand that a particular combination of prior art references may be made by merely showing that it was obvious to try the combination. For example, common sense is a good reason for a person having ordinary skill to pursue known options when there is a design need or market pressure to solve a problem, and there are a finite number of identified, predictable solutions.

- 23. I am informed and understand that a determination of obviousness cannot be based on the hindsight combination of components selectively culled from the prior art to fit the parameters of the patented invention. Instead, it is my understanding that in order to render a patent claim invalid as being obvious from a combination of references, there must be some evidence within the prior art as a whole to suggest the desirability, and thus the obviousness, of making the combination in a way that would produce the patented invention.

- 24. I am further informed and understand that a proper obviousness analysis focuses on what was known or obvious to a person having ordinary skill in the art, not just the patentee. Therefore, in an obviousness analysis, neither the motivation nor the purpose of the patentee is controlling. What is important is whether there existed at the time of the invention a known problem for which there was an obvious solution encompassed by the patent's claims. For example, any need or known problem in the field at the time of the alleged invention that is supposedly addressed by the patent can provide a reason for combining the limitations in the manner claimed if a combination of prior art would address the same.

- 25. In addition, it is my understanding that in order to find a patent claim invalid for obviousness, there must be a finding that each element in each limitation of the patent claim is disclosed, taught, or suggested by the asserted combination of prior art references or elsewhere in the relevant prior art. I understand, however, that a patent claim composed of several elements is not proved obvious merely by demonstrating that each of its elements was, independently, known in the prior art. But multiple prior art references or elements may, in some circumstances, be combined to render a patent claim obvious. I understand that I should consider whether there is an "apparent reason" or motivation to combine the prior art references or elements in the way the patent claims. To determine whether such an "apparent reason" or motivation to combine the prior art references or elements in the way a patent claims exists, it will often be necessary to look to the interrelated teaching of multiple prior art references, to the effects of demands known to the design community or present in the marketplace, and to the background knowledge possessed by a person of ordinary skill in the art.

- 26. I am further informed and understand that when an element is available in one field of endeavor, design incentives and other market forces can prompt variations of it, either

in the same field or a different one. If a person of ordinary skill in the art can implement a predictable variation of that available element, Section 103 likely renders the invention obvious. For the same reason, I am informed and understand that if a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that such technique would improve similar devices in the same way, using the technique is obvious unless its actual application is beyond his or her skill. Following these principles often requires one to look to interrelated teachings of multiple patents; the effects of demands known to the design community present in the marketplace; and the background knowledge possessed by a person having ordinary skill in the art, all in order to determine whether there was an apparent reason to combine the known element in the manner claimed by the patent at issue. I am further informed and understand that the analysis need not seek out precise teachings directed to the specific subject matter of the challenged claim, because one can take account of the inferences and creative steps that a person of ordinary skill in the art would employ.

27. I am further informed and understand that although the use of the "teaching, suggestion or motivation" test for combining references has not been completely rejected, the obviousness analysis cannot be confined by a formalistic conception of the words teaching, suggestion, and motivation, or by overemphasis on the importance of published articles and the explicit content of issued patents. I am informed and understand that in many fields there is little discussion of obvious techniques or combinations, and it is often the case that market demand, rather than scientific literature, drives design trends. Under the correct analysis, any need or problem known in the field of endeavor at the time of the invention and addressed by the patent can provide a reason for combining the elements in the manner claimed. Finally, I am informed and understand that common sense teaches that familiar items may have obvious

uses beyond their primary purposes and, in many cases, a person of ordinary skill in the art will be able to fit the teachings of multiple patents together like pieces of a puzzle.

- 28. I am also informed and understand that even though a prior art reference does not fully anticipate a claim of a patent, a claim may, nonetheless, be rendered obvious to one of ordinary skill in the art if the differences between the subject matter set forth in the patent claim and the prior art are such that the subject matter as a whole of the claim would have been obvious at the time the claimed invention was made.

- 29. I further am informed that in determining whether the claimed subject matter is obvious, one must also examine any objective indicia of nonobviousness (also called secondary considerations). I also have been informed that secondary considerations cannot overcome a strong showing of obviousness. In that regard, I am informed that secondary considerations must be commensurate in scope (proportional) with respect to the claims for which the evidence is offered to support. I have been informed that evidence of secondary considerations is not commensurate in scope if the claims are broader than the scope of such evidence. Relatedly, I have been informed that a nexus or connection between the merits of the claimed invention and the alleged evidence of secondary considerations is necessary. Specifically, I have been informed that the secondary considerations must be tied to purported novel or new elements of the claimed invention.

- 30. I also am informed that secondary considerations of nonobviousness include (1) whether the claimed subject matter achieved unexpected results or benefits, (2) whether the claimed subject matter satisfied a long-felt but unmet need, (3) whether the claimed subject matter was commercially successful as a result of the merits of a claimed subject matter (rather than the result of design needs, market pressure, advertising, or similar activities), (4) whether

other skilled artisans failed in their attempts to solve the same problems addressed by the invention, (5) whether others copied the claimed subject matter, and (6) whether others in the field praised claimed the subject matter.

- 31. Specifically, I am informed that evidence that other skilled artisans failed in their attempts to solve the same problems addressed by claimed invention is potential evidence of nonobviousness. To demonstrate failure of others, I am informed that plaintiff must establish that others skilled in the art tried and failed to find a solution for the problem allegedly solved by the invention claimed by the asserted patents. I further understand that for such evidence of failure to be relevant as an objective indicia of nonobviousness, these prior unsuccessful attempts must have failed because they lacked the claimed features of the asserted inventions. Purported failures unrelated to the patented invention are not relevant secondary considerations of nonobviousness.

- 32. I also am informed that evidence of a long-felt unmet need for the claimed invention is one factor courts may consider when assessing the obviousness of that invention. The underlying rationale for accepting evidence of a long-felt unmet need as evidence of nonobviousness, as I understand it, is based on the assumption that if an unmet need persists for a long time despite commercial incentives to offer a solution, the resolution of the problem may not be obvious. I also understand that the long-felt unmet need must be directly related to the subject matter of the claimed invention and must actually provide a result that meets the claimed need. I further am informed that the length of time that must pass to constitute a "long felt" need is to be determined in the light of the speed of innovation in the relevant industry. I also have been informed that long-felt, unmet need should be based upon alleged inadequacies in the technical knowledge of those skilled in the art, not due to business-driven market forces.

Lastly, I have been informed that any evidence of a need that post-dates the filing date of a challenged patent is irrelevant to the determination of nonobviousness.

- 33. I am further informed that "commercial success" is a legal construct that has been established through case law. I have been informed that analysis of commercial success is premised on the concept that if a product is economically successful, it may provide objective evidence of nonobviousness. I further understand that any purported commercial success of the product must be attributable to the alleged novel features of the claimed invention. I understand this to mean that, to support a finding of nonobviousness, any alleged commercial success must be driven by and attributable to the purported merits of the patented invention, and not by other factors unrelated to the allegedly novel features of the claimed invention. In other words, there must be a causal correlation, or "nexus," between the unique merit of the claimed invention and the success of the product. I also understand that if purported commercial success is due to an element in the prior art, no nexus exists.

- 34. I additionally understand that an alleged infringer's copying of a claimed invention rather than one that is in the public domain can support a finding of nonobviousness. Likewise, I am informed that to support a finding of nonobviousness, alleged industry praise must be linked to the patented invention. In other words, a patentee must show that any industry praise is attributable to material differences between the prior art and the patented invention. I have been informed that a patentee's statements that are intended to generate interest in a product are not evidence of industry praise. Similarly, publications authored or sponsored by or on behalf of a patentee fail to demonstrate true industry praise.

- 35. I further understand that the near simultaneous invention by two or more equally talented inventors working independently may or may not be an indication of obviousness. In

other words, the fact that another person simultaneously and independently created the same invention claimed in the patent-in-suit can serve as an indication that the invention was obvious.

## C. <u>Indefiniteness Under 35 U.S.C. § 112, ¶ 2</u>

- 36. I have been informed that that 35 U.S.C. § 112, second paragraph, requires that a patent specification include claims particularly pointing out and distinctly claiming the subject matter which the inventor regards as his invention. I further understand that in order to comply with this requirement, a patent's claims, viewed in light of the specification and prosecution history, must inform those skilled in the art about the scope of the invention with reasonable certainty. Otherwise, the patent claims are invalid as indefinite.

- 37. I further have been informed that under this "reasonable certainty" standard, an undefined claim term renders a claim indefinite when it results in the existence of multiple methods leading to different results without guidance in the patent or the prosecution history. I also understand that this indefiniteness problem will persist even if someone skilled in the art could determine which method was the most appropriate.

- as. I also understand that a claim may be indefinite where it employs a narrow numerical range that falls within a broader range, at least when the boundaries of the claim are not discernible. Likewise, I understand that claim language employing terms of degree may be indefinite where the language does not provide enough certainty to one of skill in the art when read in the context of the specification for instance, where the term of degree is highly subjective and, on its face, provides little guidance to one of skill in the art such that, when combined with intrinsic evidence, the subjectivity does not provide a definition or boundaries for the term and/or does not provide any reference point for comparison.

#### D. Written Description Under 35 U.S.C. § 112, ¶ 1

39. I have been informed that the standard for satisfying written description with respect to a patent is that the patent specification reasonably conveys to a person having ordinary skill in the art that the inventor had possession of the subject matter of the claims as of the effective filing date.

## E. Enablement Under 35 U.S.C. § 112, ¶ 1

- 40. I have been informed that to satisfy the enablement requirement with respect to a patent, the specification must describe the manner and process of making and using the claimed invention so as to enable the full scope of the claims, such that the public is enriched by the patent specification at least commensurate with the scope of those claims.

- 41. Furthermore, I understand that a patent specification that does not allow a person having ordinary skill in the art to practice the invention without undue experimentation is not enabled. I have been informed that certain factors are typically considered when evaluating the level of experimentation, such as the quantity of experimentation necessary to make or use the invention based on the content of the disclosure, the amount of direction or guidance presented by the inventor, the presence or absence of working examples, the breadth of the claims, the nature of the invention, the level of one of ordinary skill and the predictability or unpredictability of the art.

- 42. Therefore, I will analyze the prior art and other issues using this framework.

## VI. <u>LEVEL OF SKILL IN THE ART</u>

43. I am informed and understand that the claims of a patent are judged from the perspective of a hypothetical construct involving a "person of ordinary skill in the art." The "art" is the field of technology to which the patent is related. I understand that the purpose of using the viewpoint of a person of ordinary skill in the art is for objectivity. I understand that a

person of ordinary skill in the art is presumed to know and be familiar with all of the relevant art in the field at the time of invention.

- 44. I was also asked to provide an opinion regarding the skill level of a person of ordinary skill in the art of the Family 3 patents. I considered several factors, including the types of problems encountered in the art, the solutions to those problems, the pace of innovation in the field, the sophistication of the technology, my experience as a person who worked in the art on the Family 3 patents' priority date, and the education level of active workers in the field.

- 45. In my opinion, at the time of the alleged invention, a person having ordinary skill in the art would have had a bachelor's degree in electrical engineering or computer engineering and 5 years of experience in digital communications, a Master's degree in electrical engineering and 2-3 years of experience in digital communications, or a Ph.D. in electrical engineering with 1-2 years of experience in digital communications.

- 46. I am qualified as a person of at least ordinary skill in the art, and my qualifications enable me to provide opinions regarding the Family 3 patents from the perspective of one of ordinary skill in the art.

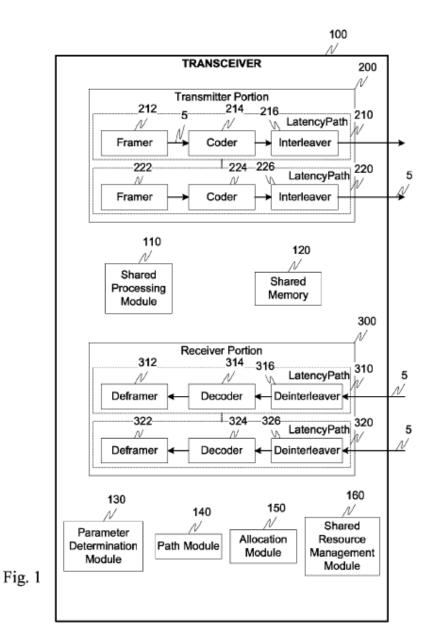

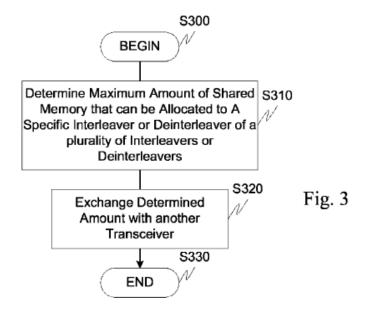

#### VII. BACKGROUND OF THE TECHNOLOGY

47. The Family 3 patents share a common specification.<sup>1</sup> The Family 3 patents are generally directed to methods, systems, and apparatuses for allocating shared memory between interleavers and deinterleavers.

## A. Forward Error Correction and Reed Solomon Coding

48. In a digital communication system, a transmitter transmits data to a receiver over a channel. The channel attenuates and adds noise to the transmitted signal. As a result,

<sup>&</sup>lt;sup>1</sup> Accordingly, citations are to U.S. Patent No. 7,844,882 ("the '882 patent") unless otherwise noted.

sometimes the bits detected by the receiver do not match the bits represented by the transmitted signal sent by the transmitter. Consequently, digital communication systems often employ certain well-known techniques to detect, and sometimes correct, errors in the received bit stream.

- 49. Error correction techniques enable a receiver to detect the presence of errors and also correct at least some of those errors. To apply an error correction technique, the transmitter adds redundant information to a message to be transmitted. The receiver then uses the redundant information to detect a limited number of errors that may occur anywhere in the message, and often to correct those errors. When the communication system uses an error correction technique, the receiver can correct at least some errors in the received data, which reduces and could eliminate entirely any need for the receiver to request retransmission of corrupted messages.

- FEC). One type of FEC is block codes. To apply a block code, the transmitter partitions the data to be transmitted into blocks and adds redundancy to each block to form a *codeword*. The transmitter appends r redundancy symbols to each block of k symbols, without altering the original k symbols, to form codewords having k + r symbols. The receiver then uses the information in the r redundancy symbols to automatically detect and correct errors in the data portion of the codeword. A well-known example of a block code is the Reed-Solomon coding used in ADSL and VDSL.

- 51. Many communication systems, including ADSL and VDSL, are byte-oriented systems, and each Reed-Solomon-encoded data block contains an integer number of bytes. The bytes in each Reed-Solomon codeword include K data bytes (i.e., the data to be transmitted in

the block) and R redundancy bytes that result from the Reed-Solomon code calculation. Thus, the size of each Reed-Solomon codeword is N = K + R bytes long.

- 52. The mathematics of Reed-Solomon codes are complicated, but the essential property is that the maximum number of data elements with any number of errors that can be corrected is equal to half of the number of redundancy elements. In other words, a byte-oriented Reed-Solomon code can correct as many as R/2 errored data bytes, regardless of how many individual errors are within those data bytes.

- 53. As a simple example, if R = 16, up to 8 erroneous bytes can be corrected, regardless of how many bits of each errored byte are in error. Reed-Solomon codes are particularly helpful for use in environments that suffer from noise bursts because any erroneous element counts as a single error regardless of how many bits of that element are in error.

## B. <u>Interleaving and Deinterleaving</u>

- 54. Interleaving is a technique used in ADSL and VDSL to improve the performance of Reed-Solomon coding in the presence of *impulse noise*, by which I mean intermittent and unpredictable bursts of noise that can temporarily overwhelm the data-carrying signal over several consecutive symbol periods. Deinterleaving is the complementary process that "undoes" interleaving. Interleaving—and, therefore, deinterleaving—have been specified in ADSL since the first T1.413 Issue 1 standard was published in 1995.

- 55. To apply interleaving, the transmitter shuffles consecutive bytes of the data stream in a known and systematic way before transmitting them to the receiver. As a result of the interleaving process, bytes that are adjacent in the data sequence are transmitted non-consecutively, spread out over a time interval. The receiver knows how the transmitter interleaved the bytes and reorders them before performing Reed-Solomon decoding to detect, and ideally correct, errors within the codewords.

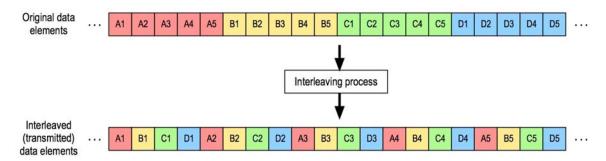

56. Figure 1 below illustrates how the interleaving process works using a simple interleaving procedure. The transmitter separates the data elements into a number of blocks of five elements each (i.e., A1, A2, A3, A4, A5; B1, B2, B3, B4, B5; etc.). Elements from four blocks are then interleaved and transmitted in turn to create a sequence AxBxCxDx.

Figure 1: Interleaving example

- 57. Note that the interleaving process significantly increases the time interval over which the data elements from each of the individual data blocks are transmitted. Following the interleaving process in this simple example, the first and last data elements of each block are separated by 15 other data elements, and consecutive data elements of each block are separated by three other data elements. In real systems, the separation after interleaving will normally be hundreds or even thousands of bytes.

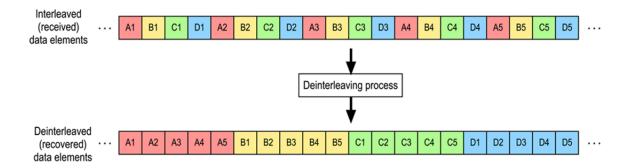

- 58. The receiver knows how the transmitter interleaved the data elements and can reverse the interleaving process by collecting all of the interleaved data elements and using a complementary deinterleaving process. The deinterleaving process results in the data elements being reordered into their original sequence, as shown in Figure 2 below.

Figure 2: Deinterleaving example

- 59. DSL systems often use interleaving to improve the performance of the Reed-Solomon code. Errors in the received data caused by impulse noise tend to occur in bursts. Without interleaving, impulse noise causes errors that are concentrated within one or more consecutive Reed-Solomon codewords. As I explained above, a Reed-Solomon code can correct up to R/2 errored data elements in a codeword, where R is the number of redundancy bytes. If a single codeword has more than R/2 data bytes with errors, the Reed-Solomon code cannot correct all of the errors. Without interleaving, impulse noise can readily cause errors in more than R/2 of the bytes within a single Reed-Solomon codeword, which means the Reed-Solomon code (probably) cannot correct all of those errors.

- 60. If the transmitter interleaves the bytes prior to transmission, however, the effects of bursts of errors are spread out over multiple Reed-Solomon codewords when the bytes are reordered by the receiver, instead of being concentrated in a fewer number of Reed-Solomon codewords. After deinterleaving, the code can correct all of the errors as long as none of the reordered blocks of data bytes has more than R/2 bytes with errors.

where the subscripts are the byte indices within a codeword, and the superscripts are the codeword indices. The vertical lines show the codeword boundaries. Assume impulse noise corrupts five consecutive bytes as shown below by Xs:

$$\begin{bmatrix} \mathbf{g}_1^1 & \mathbf{g}_1^1 & \mathbf{g}_2^1 & \mathbf{g}_3^1 & \mathbf{g}_4^1 & \mathbf{g}_5^1 & \mathbf{g}_6^1 & \mathbf{g}_7^2 & \mathbf{g}_7^2 & \mathbf{g}_5^2 & \mathbf{X} & \mathbf{X} & \mathbf{X} & \mathbf{X} & \mathbf{g}_2^3 & \mathbf{g}_3^3 & \mathbf{g}_4^3 & \mathbf{g}_5^3 & \mathbf{g}_6^3 & \mathbf{g}_6^3 & \mathbf{g}_6^3 & \mathbf{g}_9^3 & \mathbf$$

Assuming R/2 is 2, the Reed-Solomon code can correct the two errored bytes in the third codeword, but it cannot correct each of the three errored bytes in the second codeword.

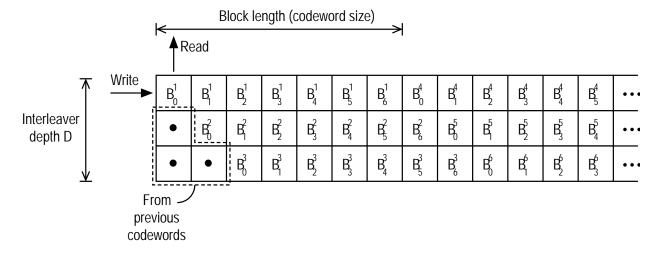

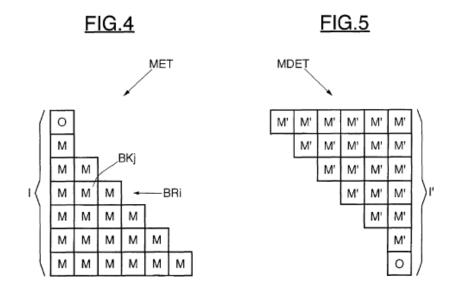

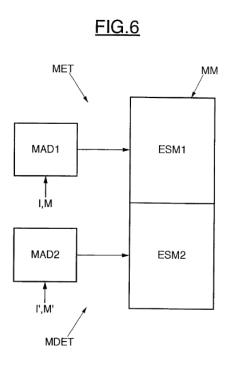

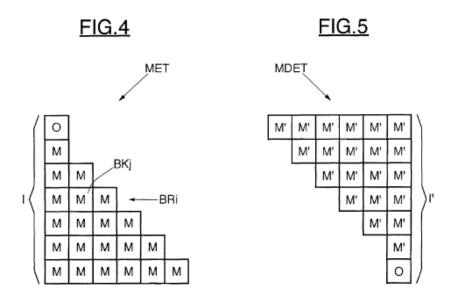

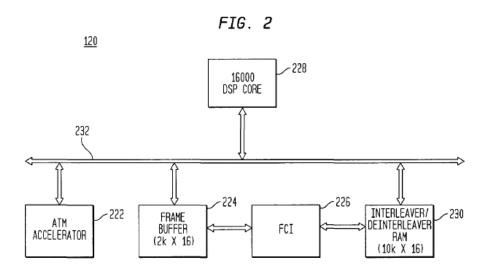

62. ADSL and VDSL use a particular kind of interleaving called *convolutional interleaving*. Figure 3 below is an example illustrating how a transmitter performs convolutional interleaving. Visualizing the interleaver memory as a matrix, codewords are written into the rows and read out of the columns of the matrix to create the interleaved stream of bytes. In convolutional interleaving, the first bytes of the D codewords in different rows are in different columns (i.e., subsequent codewords are shifted to the right by one column when written into the rows). The deinterleaver operates similarly to the interleaver, except that the received bytes are written into the columns of the matrix and read out row by row.

Figure 3: Convolutional interleaver with 7-byte codeword length and depth D=3

- 63. In the example of Figure 3, the interleaver depth D is 3 bytes, and the codeword size I is 7 bytes. The large dots within the squares at the left-hand side of the figure represent bytes from previous codewords. To help with visualization of how convolutional interleaving works, the rows are depicted as never ending so that additional codewords can be added to each of the rows in sequence.

- 64. In order of left to right, the interleaved stream for the example convolutional interleaver shown in Figure 3 is

The bytes that were adjacent in the original data stream are separated by 3 bytes (the interleaver depth D) after interleaving.

65. Now if impulse noise corrupts the five consecutive bytes in the same location as shown above, the resulting interleaved stream of bytes is:

When the bytes are deinterleaved, the resulting stream of codewords is:

After the bytes have been returned to their original order, no codeword includes more than two bytes in error, and the Reed-Solomon code can correct all of the errors.

66. The process of interleaving in the transmitter and deinterleaving in the receiver introduces delay (or latency) because bytes are stored for a period of time after they are written to the interleaver or deinterleaver memory but before they are read out. All bytes have the same total delay between the input to the interleaver and the output of the deinterleaver, which is typically referred to as the *end-to-end interleaver delay* (with the understanding that the delay contributed by the deinterleaving process is included, too). In units of time, the end-to-end

over the communication channel in the downstream direction, because that rate determines how quickly the transmitter processes the bytes for transmission.

- 67. The amount of memory needed for convolutional interleaving depends on how the interleaver and deinterleaver are implemented. The minimum amount of memory required for a convolutional interleaver and deinterleaver pair is  $(D-1) \times (I-1)$  bytes.

- 68. The primary penalties for including interleaving in a communication system are increased latency (due to the end-to-end interleaver delay) and a requirement for additional memory in both the transmitter and receiver. The end-to-end interleaver delay increases with the interleaver depth. Therefore, there is a fundamental trade-off between latency and improved Reed-Solomon performance. A larger interleaver depth offers better potential to improve the performance of the Reed-Solomon coding but also increases latency.

#### C. Shared Memory

- 69. As I explain further in the prior art discussion below, the idea of a transceiver sharing a common memory for interleaving and deinterleaving was well known as of the Family 3 patents' priority date.

- 70. For convenience, I will sometimes distinguish in this report between a "near-end" transceiver and the "far-end" transceiver that is on the other side of a communication channel from the near-end transceiver. When the transmitter of a near-end transceiver performs interleaving, the transmitter needs to have access to an amount of memory sufficient for the transmitter to perform the interleaving procedure. Likewise, when the transmitter in the far-end transceiver performs interleaving, the near-end transceiver's receiver must have access to an amount of memory sufficient to enable it to deinterleave the data interleaved by the far-end transceiver's transmitter. And, of course, the far-end transceiver needs sufficient memory to

deinterleave the data transmitted by the near-end transmitter and to interleave the data it is transmitting to the near-end receiver.

- 71. There are two ways to provide the memory needed for a transceiver's interleaving and deinterleaving procedures. The first way is to provide a specified amount of dedicated interleaver memory and a specified amount of dedicated deinterleaver memory. The transmitter has exclusive access to the interleaver memory and can, at least in theory, use as much as all of the interleaver memory for interleaving. Similarly, the receiver has exclusive access to the deinterleaver memory and can, at least in theory, use as much as all of the deinterleaver memory for deinterleaving.

- 72. The second way to meet the transceiver's memory requirements for interleaving and deinterleaving is to provide shared memory that the transceiver can partition between its interleaver and deinterleaver on a per-connection basis. Use of a shared memory for interleaving and deinterleaving, including in DSL, was well known before the priority date of the Family 3 patents. *See, e.g.*, U.S. Patent Pub. No. 2005/0034046 by Berkmann *et al.* at Abstract (disclosing a "combined interleaving and deinterleaving circuit" with "data memory (RAM) for temporary storage of the data to be interleaved and deinterleaved"); U.S. Patent No. 6,707,822 to Fadavi-Ardekani *et al.* at Abstract (disclosing an "Interleave/De-Interleave Memory" that "is shared by multiple ADSL sessions and by the transmit and receive processes within an individual session"); U.S. Patent No. 6,381,728 to Kang at col. 5:35-38 (disclosing "double buffering [that] allows the channel interleaver memory to be used, along with the app memory, as the turbo deinterleaver memory"); U.S. Patent No. 7,269,208 to Mazzoni *et al.* at Abstract (disclosing memory having "a first memory space assigned to the interleaver and a second memory space assigned to the deinterleaver"); *id.* at col. 1:19-22 ("The present

invention may advantageously be applied to a very high rate digital subscriber line (VDSL) environment or system. . . . "); U.S. Patent No. 5,751,741 to Voith *et al.* at col. 4:47-50 (disclosing external interleave/deinterleave memory used by both transmitter for interleaving and receiver for deinterleaving); *id.* at col. 2:61-64 ("Generally, the present invention provides an ADSL transceiver. . . .").

- 73. Once the shared memory has been partitioned between the transmitter's interleaver and the receiver's deinterleaver for a connection, the transmitter has exclusive access to the portion of the shared memory allocated for interleaving and can, at least in theory, use as much as all of that portion of the shared memory for interleaving. Similarly, the receiver has exclusive access to the portion of the shared memory allocated for deinterleaving and can, at least in theory, use as much as all of that portion of the shared memory for deinterleaving. When the connection terminates, the shared memory can thereafter be repartitioned, possibly differently, when new connections are established.

- 74. Because the interleaving procedure is performed by one transceiver, and the corresponding deinterleaving procedure is performed by a different transceiver, it is necessary for at least one of the transceivers to know the capabilities or requirements of the other transceiver in order to configure the interleaver (or deinterleaver). Otherwise, for example, the transceiver performing the interleaving procedure could use an interleave depth that requires more memory than is available to the transceiver performing the deinterleaving procedure.

- 75. For example, before the near-end transceiver can configure its interleaver, which establishes how much of the memory available for interleaving (in either a dedicated memory or shared memory) the transmitter will use, it needs to know something about the far-end transceiver's deinterleaving capabilities; otherwise, the near-end transmitter could perform an

interleaving procedure that the far-end receiver is incapable of reversing (e.g., because it does not have sufficient memory). In addition, before the near-end transceiver can configure its deinterleaver, which establishes how much of the memory available for deinterleaving (in either a dedicated memory or shared memory) the receiver will use, it needs to know how the far-end transceiver will be interleaving the data; otherwise, the near-end receiver will be unable to perform the corresponding deinterleaving procedure.

76. As discussed below, since 1995, the ADSL and VDSL standards have provided for the near-end and far-end transceivers to communicate their interleaving requirements and/or capabilities to each other during an initialization procedure.

### D. <u>Latency Paths</u>

- 77. Different types of data have different levels of sensitivity to delays that occur during transmission. For example, real-time voice data, such as from a telephone call, cannot tolerate large delays because delays in conversations are very annoying for the participants. In contrast, a pre-stored (i.e., non-real-time) video transmitted to a receiver (e.g., via YouTube, Netflix, HBO Go, etc.) can tolerate a substantial amount of delay because the local video playback device typically buffers at least some of the video before playing it.

- 78. To enable the transmission of both delay-sensitive and delay-tolerant data over the same subscriber line, the ADSL and VDSL standards, discussed below, define multiple *latency paths* that allow a single DSL connection to transfer multiple types of data having different latency requirements (or delay tolerances) at the same time. Each latency path is characterized by a distinct delay (or latency), which may be the same as or different from the delay(s) of other latency paths. For example, one latency path may be characterized by a relatively large delay because of interleaving in the transmitter and deinterleaving in the

receiver, whereas another latency path may be characterized by a relatively small delay because of little or no interleaving.

79. The delay of a particular latency path depends on the FEC and interleaving used in that path. For example, when a latency path includes both FEC and interleaving, the delay depends on the codeword size and the interleave depth.

## E. Overview of DSL Standards Groups

80. Many of the aspects of ADSL and VDSL have been standardized by standard-setting organizations (SSOs), such as the Alliance for Telecommunications Industry Solutions (ATIS) and the International Telecommunications Union (ITU). This section introduces two of the working groups and the standards they produced that are relevant to the subject matter of this case and pre-date the priority date of the Family 3 patents. It also provides a brief overview of how the work in the responsible working groups is conducted.

#### 1. <u>T1E1.4</u>

- 81. The earliest standardization work in ADSL was undertaken in the United States by the T1E1.4 technical subcommittee of Committee T1, a telecommunications standards body sponsored by ATIS and accredited by the American National Standards Institute (ANSI).

- 82. In 1995, ATIS published the world's first ADSL standard, T1.413. I will refer to the first version of the T1.413 standard herein as "T1.413 Issue 1." In 1998, ATIS published a revision of T1.413, which I will refer to as "T1.413 Issue 2." Both T1.413 Issue 1 and T1.413 Issue 2 specify the required operations of ADSL transceivers (referred to as the "ATU-C" and "ATU-R").

- 83. After releasing T1.413 Issue 2 ADSL, T1E1.4 focused less on developing standalone transceiver standards and more on providing inputs to the ITU-T, discussed below, regarding North American requirements and preferences for emerging DSL standards.

#### 2. ITU-T Study Group 15, Question 4

- 84. In 1997, the Telecommunications Sector of the ITU, known as the ITU-T, also began working on ADSL standardization. The ITU-T generates standards called "Recommendations" for all fields of telecommunications. Recommendations are the result of work by members of the ITU-T, which include Member States (e.g., the United States and other members of the United Nations), Sector Members, and Associates. Sector Members and Associates are generally companies and other organizations.

- 85. DSL standardization is carried out by Study Group 15 of the ITU-T. The work of Study Group 15 is partitioned into work areas known as "Questions." DSL standardization work takes place within Study Group 15, Question 4 (abbreviated herein as "SG15/Q4"). SG15/Q4 became the primary group responsible for defining DSL transceiver standards after T1E1.4 completed T1.413 Issue 2.

- and optional functions of DSL transceivers. In 1997, among other projects, SG15/Q4 established the projects known as "G.dmt" and "G.lite." At that time, T1.413 Issue 1 was in force, and T1E1.4 was developing what eventually became T1.413 Issue 2 ADSL. G.dmt was expected essentially to adopt T1.413 Issue 2 and add annexes addressing country-specific requirements. The work in G.dmt was eventually released in 1999 as ITU-T Recommendation G.992.1, entitled "Asymmetric digital subscriber line (ADSL) transceivers," much of which is identical to T1.413 Issue 2. G.992.1 specifies requirements for both the ATU-C and the ATU-R to enable connections that support at least 6.144 Mbit/s in the downstream direction (i.e., toward the subscriber, from the ATU-C to the ATU-R) and at least 640 kbit/s in the upstream direction (i.e., away from the subscriber, from the ATU-R to the ATU-C) without interfering with "plain old telephone signals" (POTS) on the same subscriber line.

- 87. G.lite was intended to be a lower-speed version of ADSL. The work in G.lite was eventually released, also in 1999, as ITU-T Recommendation G.992.2, entitled "Splitterless asymmetric digital subscriber line (ADSL) transceivers." Unlike G.992.1, which was designed to maximize performance, G.992.2 was designed to provide lower bit rates (i.e., a maximum of 1.536 Mbit/s downstream and 512 kbit/s upstream) by simplifying various aspects of the ATU-C and ATU-R.

- 88. After completing G.992.1, SG15/Q4 almost immediately began work on a revision, standardized in Recommendation G.992.3, entitled "Asymmetric digital subscriber line transceivers 2 (ADSL2)," the first version of which was approved in 2002. G.992.3 builds on many of the aspects of G.992.1 to enable connections that support at least 8 Mbit/s downstream and at least 800 kbit/s upstream.

- 89. In parallel with the work on ADSL2, SG15/Q4 also worked on a higher speed version of ADSL, known as ADSL2+. Recommendation G.992.5, entitled "Asymmetric Digital Subscriber Line (ADSL) transceivers Extended bandwidth ADSL2 (ADSL2+)," was first approved in 2003. It specifies the physical layer characteristics of an ADSL transceiver that transmits over a wider bandwidth than an ADSL2 transceiver. G.992.5 is defined in a "delta document" to G.992.3, meaning that it incorporates the content of G.992.3 and specifies only changes and additions to that document. As compared to G.992.3, G.992.5 enables transceivers to transmit using twice as much bandwidth in the downstream direction to provide at least 16 Mbit/s in the downstream direction and at least 800 kbit/s in the upstream direction.

- 90. In June of 2004, the ITU-T's first VDSL Recommendation, G.993.1, entitled "Very high speed digital subscriber line transceivers," was approved. It specifies transceiver

requirements to support the transmission of asymmetric and symmetric aggregate data rates up to tens of Mbit/s on twisted pairs.

#### 3. Operation of DSL Standards Meetings

- 91. Both T1E1.4 and SG15/Q4 met regularly, typically 4 to 6 times per year, to begin work on new DSL standards, to discuss and improve the draft standards being developed at the time, and eventually to submit the standards for formal approval. In order to develop and improve the standards, T1E1.4 and SG15/Q4 participants submitted documents, referred to as "contributions." A contribution might identify a problem with an in-force standard and propose a solution for incorporation in a revision of that standard, or it might propose a new feature for a standard being developed, or it might propose to begin work on a new standard.

- 92. Each T1E1.4 contribution was assigned a unique identifier of the form "T1E1.4/YY-NNN" or "T1E1.4/YYY-NNN," where "YY" or "YYYY" indicates the year, and "NNN" is a unique 3-digit number. The unique 3-digit number would reset to 001 at the beginning of each year. Each SG15/Q4 contribution is assigned a unique identifier of the form "MM-NNN," where "MM" is a 2-letter designator reflecting the location of the meeting (e.g., "DC" stands for "Durango, Colorado," "LB" stands for "Leuven, Belgium," etc.), and "NNN" is a unique 3-digit number. The unique 3-digit number resets to 001 for each SG15/Q4 meeting.

- 93. One unique aspect of T1E1.4, relative to many other SSO working groups, was that prior to 2004, its meetings were open to members of the public, and the contributions distributed to meeting participants and/or posted on Committee T1's website were freely available to the public without any distribution restrictions. Thus, any member of the public could attend T1E1.4 meetings free of charge and obtain copies of the contributions submitted to that meeting. Members of the public could also download contributions from Committee T1's website. Meetings of T1E1.4 were typically held in the United States.

94. SG15/Q4 meetings were (and are) open to and attended by members of the ITU-T. ITU-T membership was (and is) available to interested companies and organizations for an annual fee that, as of June of 2004, was 10,500 Swiss francs.<sup>2</sup> I personally attended SG15/Q4 meetings starting in 2000,<sup>3</sup> and I recall the meetings being attended by most of the companies developing DSL chips and transceivers, as well as the service providers deploying DSL.<sup>4</sup>

## F. <u>Interleaving and FEC in DSL Standards</u>

95. As explained above, interleaving and FEC, and specifically the use of Reed-Solomon coding, have been specified for ADSL since the first ADSL standard, T1.413 Issue 1, was completed in 1995. Each of the subsequent ADSL and VDSL standards released before the Family 3 patents' priority date also specifies interleaving, FEC, and protocols to enable the near-end and far-end transceivers to inform each other of their capabilities and/or requirements during the initialization procedure.

https://web.archive.org/web/20001206175700/http://www.itu.int:80/cgi-

bin/htsh/mm/scripts/mm.list?\_search=SEC%26\_languageid=1 (last visited November 16, 2018).

<sup>&</sup>lt;sup>2</sup> See https://web.archive.org/web/20040603123217/http://www.itu.int:80/ITU-

T/membership/associates.html (last visited November 16, 2018).

<sup>&</sup>lt;sup>3</sup> I attended SG15/Q4 on behalf of Texas Instruments until May of 2004 and on behalf of 2Wire from August of 2004 through June of 2006.

<sup>&</sup>lt;sup>4</sup> According to the Internet Archive, as of December 6, 2000 the ITU-T members included, among others: 3Com, ADTRAN, Alcatel, Analog Devices, AT&T, Aware, Bell Atlantic, Bell Canada, Bell South, Broadcom, British Telecom, Burr-Brown Corporation, Catena Networks, Centillium Communications, Cisco Systems, Conexant Systems, Copper Mountain Networks, Covad Communications, Element 14, Ericsson, Excess Bandwidth Corporation, France Telecom, Fujitsu, Globespan, Infineon, Italtel, Legerity, Level One, LG Electronics, Lucent, Marconi Communications, Matsushita, Metalink, Mitel Corporation, Mitsubishi, Motorola, NEC, Next Level Communications, Nokia, Nortel Networks, NTT, PairGain, Paradyne Corporation, Philips, PMC-Sierra, Qwest, Sagem, Sasken, SBC Communications, Siemens, Sprint, STMicroelectronics, Sumitomo, Swisscom, Telcordia, Telecom Italia, Telenor, Telesis Technologies Laboratory, Telia, Tellabs, Texas Instruments, VDSL Systems, Verizon, Velocity Communication (later renamed Ikanos), and Virata. *See*

#### 1. Nomenclature

- 96. In ADSL, one transceiver is located on the service provider's side of the subscriber line, often in the service provider's central office (CO), and the other transceiver is located on the customer's side of the subscriber line. The ADSL transceiver located on the service provider's side of the subscriber line is referred to as the "ATU-C," and the ADSL transceiver located on the customer's side of the subscriber line is referred to as the "ATU-R."

- 97. In VDSL, one transceiver is located on the service provider's side of the subscriber line, potentially in an optical network unit (ONU), and the other transceiver is located on the customer's side of the subscriber line. The VDSL transceiver located on the service provider's side of the subscriber line is referred to as the "VTU-O," and the VDSL transceiver located on the customer's side of the subscriber line is referred to as the "VTU-R."

- 98. The direction of transmission from the ATU-C (or VTU-O) to the ATU-R (or VTU-R) is the *downstream* direction, and the direction of transmission from the ATU-R (or VTU-R) to the ATU-C (or VTU-O) is the *upstream* direction.

- 99. If interleaving is used in both the upstream and downstream directions in ADSL, both the ATU-C and ATU-R use both an interleaver and a deinterleaver. The ATU-R interleaves upstream data (for transmission to the ATU-C) and deinterleaves downstream data (interleaved by and received from the ATU-C). Conversely, the ATU-C interleaves downstream data (for transmission to the ATU-R) and deinterleaves upstream data (interleaved by and received from the ATU-R).

- 100. Similarly, in VDSL, if interleaving is used in both the upstream and downstream directions, both the VTU-O and VTU-R use both an interleaver and a deinterleaver. The VTU-R interleaves upstream data (for transmission to the VTU-O) and deinterleaves downstream data (interleaved by and received from the VTU-O). Conversely, the VTU-O interleaves

downstream data (for transmission to the VTU-R) and deinterleaves upstream data (interleaved by and received from the VTU-R).

#### 2. <u>G.992.1 (1999)</u>

- 101. G.992.1 specifies dual-latency configurations using two independent data paths in both the downstream and upstream directions. G.992.1 also supports a single-latency configuration, which may include interleaving.

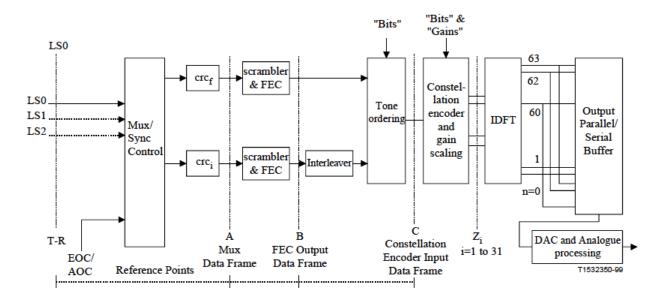

- 102. Figure 5-1 of G.992.1, copied below, is a reference diagram for the ATU-C, and Figure 5-3 of G.992.1, also copied below, is a reference diagram for the ATU-R.

NOTE – Solid versus dashed lines are used to indicate required versus optional capabilities respectively. This figure is not intended to be complete in this respect, see clauses 6 and 7 for specific details.

Figure 5-1/G.992.1 – ATU-C transmitter reference model for STM transport

NOTE – Solid versus dashed lines are used to indicate required versus optional capabilities respectively. This figure is not intended to be complete in this respect, see clauses 6 and 8 for specific details.

Figure 5-3/G.992.1 – ATU-R transmitter reference model for STM transport

In the downstream direction, there are up to two latency paths (fast and interleaved), and in the upstream direction there are also up to two latency paths (fast and interleaved), resulting in a total of four possible latency paths overall. When a single latency path is supported in one of the directions of transmission, it may use either the fast or interleaved path.

- 103. The key difference between the fast and interleaved paths in G.992.1 is that data in the interleaved path is both FEC encoded (using Reed-Solomon coding) and interleaved, as described previously, to improve the effectiveness of the FEC code in the presence of impulse noise. In contrast, the fast path includes FEC coding, but does not include interleaving. Therefore, the fast path has lower latency than the interleaved path, but it is also more likely to suffer from a higher error rate in the presence of impulse noise.

- 104. Each FEC codeword has a length of some number of bytes (i.e., N, K, and R all have units of bytes), which can be different for the fast and interleaved paths and in the downstream and upstream directions. The value of K depends on the transmitted bit rate (i.e.,

the rate at which the transmitter sends bits to the receiver on the other side of the subscriber line). The values of N, K, and R are set during the initialization procedure (with N = K + R).

- 105. G.992.1 specifies the interleave depth for the interleaved path as a number of FEC codewords.

- ates and formats to the ATU-R using a signal known as "C-RATES1." Each of the options includes downstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleaving the ATU-C proposes to do for each option) and upstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleaving the ATU-R will need to do for each of the options). G.992.1 at § 10.6.2. The ATU-R responds by transmitting a signal known as "R-RATES1," in which the ATU-R echoes the four options in the order in which the ATU-R prefers them. G.992.1 at § 10.7.4.

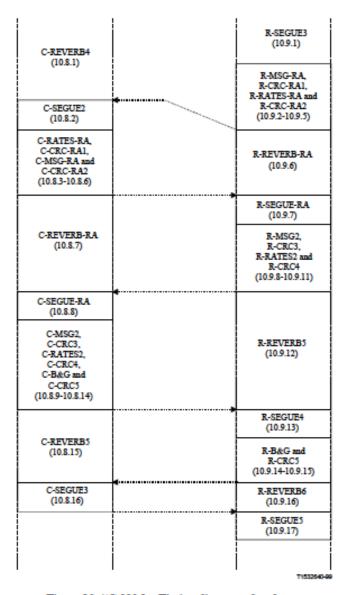

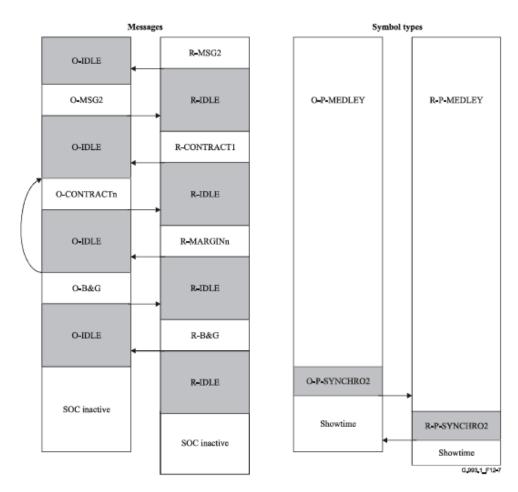

- 107. Figure 10-4 of G.992.1, copied below, shows the timing of the messages transmitted by the ATU-C and ATU-R during the "exchange" phase of initialization, which follows the transmission of the C-RATES1 and R-RATES1 messages.

Figure 10-4/G.992.1 - Timing diagram of exchange

108. After transmitting R-RATES1 and measuring the signal-to-noise ratio (SNR) of the downstream channel, the ATU-R transmits a signal called "R-MSG-RA," which tells the ATU-C, among other things, the maximum interleave depth the ATU-R can support. G.992.1 at §§ 10.9.2, 10.9.2.7. The ATU-R also transmits a signal called "R-RATES-RA," which indicates either (a) the option number of the highest data rate from C-RATES1 that can be supported based on the measured SNR in the downstream direction, (b) no option selection was made but will be made later based on information in the C-RATES-RA signal the ATU-C will

transmit, or (c) the ATU-R cannot implement any of the options received in C-RATES1. G.992.1 at § 10.9.4.

- alled "C-RATES-RA," which sends four new options for data rates and formats for both upstream and downstream transmission. G.992.1 at § 10.8.3. As in C-RATES1, each of the options includes downstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleave depth in FEC codewords (i.e., to option) and upstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleaving the ATU-R will need to do for each of the options). G.992.1 at § 10.8.3.

- only the number of the option with the highest data rate that can be supported in the downstream direction based on the ATU-R's measurements of the channel. G.992.1 at § 10.9.10. The ATU-C then transmits C-RATES2, which indicates the final decision on the downstream and upstream options that will be used for the connection. G.992.1 at § 10.8.11. The ATU-C's decision combines the downstream option selected by the ATU-R with the option number with the highest upstream data rate that can be supported based on the ATU-C's measurements of the channel. G.992.1 at § 10.8.11.

# 3. <u>G.992.2 (1999)</u>

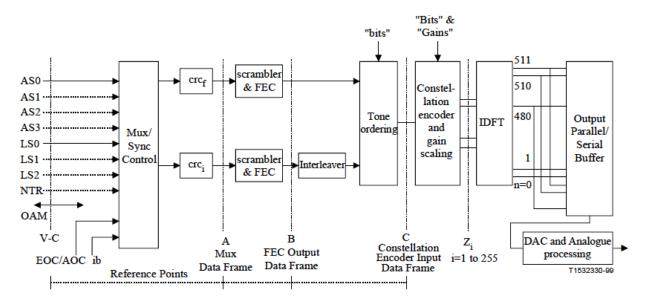

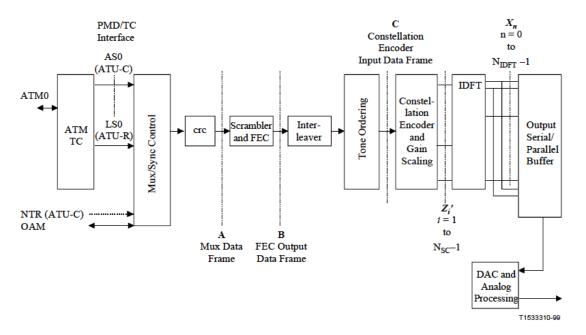

operate without the splitter filters required in G.992.1 to isolate ADSL signals from telephony signals on the same subscriber line. G.992.2 at Summary. Figure 2 of G.992.2, copied below, is the reference model for G.992.2 transmitters (both ATU-C and ATU-R).

Figure 2/G.992.2 – ATU reference transmitter model

- of FEC and interleaver settings during the initialization procedure. The ATU-C transmits C-RATES1, which contains four options, in order of decreasing preference, for downstream and upstream data rates and formats. G.992.2 at § 11.9.2. Each option contains Reed-Solomon FEC and interleaver parameters, such as the downstream interleave depth in codewords. G.992.2 at § 11.9.2. The ATU-R responds by sending R-RATES1, in which the ATU-R echoes the four options received from the ATU-C in order of decreasing preference. G.992.2 at § 11.10.4.

- 113. Figure 26 of G.992.2, copied below, shows the "exchange" phase of initialization, which takes place after the ATU-C and ATU-R have transmitted, respectively, C-RATES1 and R-RATES1.

Figure 26/G.992.2 - Timing diagram of exchange

114. After assessing the channel, the ATU-R sends R-MSG-RA, which includes, among other things, a number of Reed-Solomon overhead bytes (R) and a number of Reed-Solomon payload bytes (K). G.992.2 at § 11.12.2. The ATU-R also sends R-RATES-RA, which indicates either (a) the option number of the highest data rate sent in C-RATES1 that can be supported based on the measured SNR in the downstream direction, (b) no option selection

was made but will be made later based on information in the C-RATES-RA signal the ATU-C will transmit, or (c) the ATU-R cannot implement any of the options received in C-RATES1.

G.992.2 at § 11.12.4.

- 115. The ATU-C then transmits C-RATES-RA, which contains four new options for data rates and formats for both upstream and downstream transmission. G.992.2 at § 11.11.3. As in C-RATES1, each of the options includes downstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleaving the ATU-C proposes to do for each option) and upstream FEC settings and an interleave depth in FEC codewords (i.e., to notify the ATU-R of the FEC coding and interleaving the ATU-R will need to do for each of the options). G.992.2 at § 11.11.3.

- only the number of the option with the highest data rate that can be supported in the downstream direction based on the ATU-R's measurements of the channel. G.992.2 at § 11.12.10. The ATU-C then transmits C-RATES2, which indicates the final decision on the downstream and upstream options that will be used for the connection. G.992.2 at § 11.11.11. The ATU-C's decision combines the downstream option selected by the ATU-R with the option number with the highest upstream data rate that can be supported based on the ATU-C's measurements of the channel. G.992.2 at § 11.11.11.

# 4. <u>G.993.1 (2004)</u>

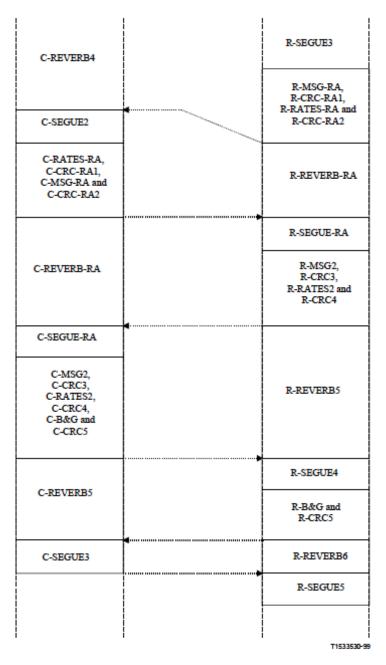

117. ITU-T Recommendation G.993.1 specifies aspects of very high-speed digital subscriber lines (VDSL) to permit the transmission of asymmetric and symmetric aggregate data rates up to tens of Mbit/s on twisted pairs. G.993.1 provides for use of a wider bandwidth than is used in ADSL, namely, up to 12 MHz. G.993.1 at § 1.

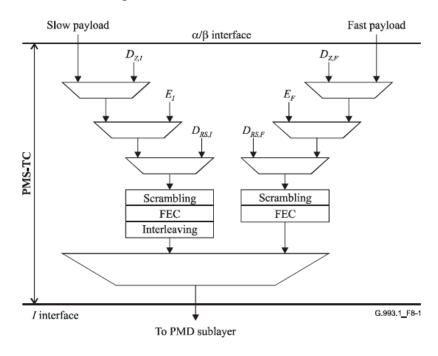

118. Among other things, G.993.1 specifies the use of FEC and interleaving in the transmitter. Figure 8-1 of G.993.1, copied below, illustrates the defined "slow" and "fast" paths. As shown, the "slow" path includes both FEC and interleaving, whereas the "fast" path includes FEC but not interleaving.

Figure 8-1/G.993.1 – Diagram of PMS-TC sublayer

provide protection against random and burst errors" (G.993.1 at § 8.3) and interleaving "to protect the data against bursts of errors by spreading the errors over a number of Reed-Solomon codewords." G.993.1 at § 8.4.1. Specifically, "the codewords shall be interleaved before transmission to increase the immunity of RS [Reed-Solomon] codewords to bursts of errors." G.993.1 at § 8.4.1. The interleave depth is programmable up to a maximum depth of 64 codewords when the codeword length is 255 bytes. *Id.* When the codeword is shorter than 255 bytes, the interleave depth can be larger than 64 codewords. *Id.*

- 120. G.993.1 specifies that "[i]t shall be possible to adjust the interleave depth via the management system to meet latency requirements." *Id.* The interleaver "uses a memory in which a block of I octets is written while an (interleaved) block of I octets is read." *Id.* G.993.1 teaches that the receiver requires the same size of memory for deinterleaving as the transmitter uses for interleaving. *Id.*