# UNITED STATES DISTRICT COURT DISTRICT OF DELAWARE

|                                                                                                  | 1                                      |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| TQ Delta, LLC,                                                                                   |                                        |  |  |  |

| Plaintiff,                                                                                       | Case No. C.A. No. 1:13-cv-01835-RGA    |  |  |  |

| v.                                                                                               | Jury Trial Demanded                    |  |  |  |

| 2Wire, Inc.                                                                                      |                                        |  |  |  |

| Defendant.                                                                                       |                                        |  |  |  |

| CORRECTED REBUTTAL EXPERT REPORT OF DR. TODOR COOKLEV REGARDING VALIDITY OF THE FAMILY 3 PATENTS |                                        |  |  |  |

| CONFIDENTIAL - ATTORNEYS' EYES ONLY                                                              |                                        |  |  |  |

| I declare under penalty of perjury tl                                                            | nat the following is true and correct. |  |  |  |

| JANUARY 4, 2019                                                                                  | J Coo                                  |  |  |  |

DATE

TQ Delta Exhibit 2010 COMMSCOPE, INC. v. TQ DELTA LLC IPR2023-00064

Todor Cooklev, Ph.D.

| I.       | IN        | FRODUCTION                                                                                                     | 1    |

|----------|-----------|----------------------------------------------------------------------------------------------------------------|------|

| II.      | AP        | PLICABLE LEGAL PRINCIPLES                                                                                      | 3    |

| A        |           | Presumption of Validity                                                                                        | 4    |

| В        | •         | Anticipation                                                                                                   | 4    |

| C.       |           | Obviousness                                                                                                    | 5    |

| D        |           | Written Description                                                                                            | 9    |

| E.       |           | Definiteness and Enablement                                                                                    | 9    |

| F.       |           | Claiming Priority to A Provisional Application                                                                 | . 11 |

| III.     |           | RSON OF ORDINARY SKILL IN THE ART                                                                              |      |

| IV.      | BA        | CKGROUND OF DSL TECHNOLOGY AND INVENTION                                                                       | . 11 |

| A        |           | Interleaver Memory and Deinterleaver Memory in Prior Art Systems                                               | . 11 |

| В.       | •         | Shared Interleaver and Deinterleaver Memory in the Family 3 Patent Inventions                                  | . 13 |

| C.<br>th |           | References Cited in Jacobsen Report are Consistent with Implementations that Preceventions of Family 3 Patents |      |

| V.       | TH        | E ASSERTED CLAIMS OF THE FAMILY 3 PATENTS ARE VALID                                                            | . 21 |

| A        |           | Claim 19 of the '473 patent is valid under 35 U.S.C. § 112, ¶2                                                 | . 21 |

| В        | •         | Written Description and/or Enablement under 35 U.S.C. § 112, ¶1                                                | . 24 |

| C.       |           | Certificate of Correction                                                                                      | . 28 |

| VI.      | AN        | IALYSIS OF THE CITED REFERENCES                                                                                | . 30 |

| A        |           | The Asserted Claims Are Not Obvious Over LB-031                                                                | . 30 |

|          | 1.        | Overview of LB-031                                                                                             | . 30 |

|          | 2.        | LB-031 Does Not Render Claim 1 of the '048 Patent Obvious                                                      | . 32 |

|          | 3.        | LB-031 Does Not Render Claim 5 of the '381 Patent Obvious                                                      | . 44 |

|          | 4.        | LB-031 Does Not Render Claim 13 of the '882 Patent Obvious                                                     | . 50 |

|          | 5.        | LB-031 Does Not Render Claim 19 of the '473 Patent Obvious                                                     | . 51 |

| В        | •         | The Asserted Claims Are Not Obvious Over the Combination of LB-031 and Mazzo 62                                | ni   |

|          | 1.        | Overview of Mazzoni                                                                                            | . 63 |

|          | 2.        | A Person of Ordinary Skill in the Art Would Not Combine the Teachings of LB-03 the Teachings of Mazzoni        |      |

|          | 3.<br>Pat | The Combination of LB-031 and Mazzoni Does Not Render Claim 1 of the '048 ent Obvious                          | . 72 |

|          | 4.        | The Combination of LB-031 and Mazzoni Does Not Render Claim 5 of the '381                                      | 70   |

|          | 5. Patent    | t Obvious                                                                                                                                                                                                                                                                |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 6.<br>Patent | The Combination of LB-031 and Mazzoni Does Not Render Claim 19 of the '473 t Obvious                                                                                                                                                                                     |

| C.<br>IT |              | he Asserted Claims Are Not Obvious Over Fadavi-Ardekani in Combination with decommendation G.993.193                                                                                                                                                                     |

|          | 1.           | Overview of Fadavi-Ardekani 93                                                                                                                                                                                                                                           |

|          |              | Fadavi-Ardekani in combination with G.993.1 does not disclose all the limitations of 1 of the '048 patent                                                                                                                                                                |

|          | 3. claim     | Fadavi-Ardekani in combination with G.993.1 does not disclose all the limitations of 5 of the '381 patent                                                                                                                                                                |

|          |              | Fadavi-Ardekani in combination with G.993.1 does not disclose all the limitations of 13 of the '882 patent                                                                                                                                                               |

|          | 5.<br>claim  | Fadavi-Ardekani in combination with G.993.1 does not disclose all the limitations of 19 of the '473 patent                                                                                                                                                               |

|          | 6.           | A POSITA would not have been motivated to combine Fadavi-Ardekani and G.993.1 108                                                                                                                                                                                        |

| D.<br>IT |              | he Asserted Claims Are Not Obvious Over Fadavi-Ardekani in Combination with decommendation G.992.2                                                                                                                                                                       |

|          | 1.<br>claim  | Fadavi-Ardekani in combination with G.992.1 does not disclose all the limitations of 1 of the '048 patent                                                                                                                                                                |

|          | 2.<br>claim  | Fadavi-Ardekani in combination with G.992.2 does not disclose all the limitations of 5 of the '381 patent                                                                                                                                                                |

|          | 3. claim     | Fadavi-Ardekani in combination with G.992.2 does not disclose all the limitation of 13 of the '882 patent                                                                                                                                                                |

|          |              | Fadavi-Ardekani in combination with G.992.2 does not disclose all the limitation of 19 of the '473 patent                                                                                                                                                                |

|          | 5.           | A POSITA would not have been motivated to combine Fadavi-Ardekani and G.992.2                                                                                                                                                                                            |

| E.       |              | laim 19 of the '473 Patent Is Not Obvious Over Voith in Combination with LB-031                                                                                                                                                                                          |

|          | functi       | Neither Voith nor LB-031 discloses a multicarrier communications transceiver ated with a memory "wherein the memory is allocated between the interleaving on and the deinterleaving function in accordance with a message received during an ization of the transceiver" |

|          | interle      | Neither Voith nor LB-031 discloses a multicarrier communications transceiver ated with a memory "wherein at least a portion of the memory may be allocated to the eaving function or the deinterleaving function at any one particular time depending on essage"         |

|          | 3.           | No Motivation to Combine Voith with LB-031                                                                                                                                                                                                                               |

| F.       | Clai         | m 19 of the '473 Patent Is Not Obvious Over Mazzoni and G.993.1                                                                                                                                                                                                            |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.<br>with t | A Person of Ordinary Skill in the Art Would Not Combine the Teachings of Mazzoni he Teachings of G.993.1                                                                                                                                                                   |

|          | 2.<br>Patent | The Combination of Mazzoni and G.993.1 Does Not Render Claim 19 of the '473 t Obvious                                                                                                                                                                                      |

| G.<br>Al |              | laim 19 of the '473 Patent Is Not Obvious Over Voith and G.993.1, or, In the ive, In View of Voith, G.993.1 and Mazzoni                                                                                                                                                    |

|          | functi       | Neither Voith nor G.993.1 discloses a multicarrier communications transceiver lated with a memory "wherein the memory is allocated between the interleaving on and the deinterleaving function in accordance with a message received during an ization of the transceiver" |

|          | interle      | Neither Voith nor G.993.1 discloses a multicarrier communications transceiver lated with a memory "wherein at least a portion of the memory may be allocated to the eaving function or the deinterleaving function at any one particular time depending on essage"         |

|          | 3.           | No Motivation to Combine Voith with G.993.1                                                                                                                                                                                                                                |

|          | 4.           | Mazzoni does not Supply the Disclosure Missing from G.993.1 and Voith 141                                                                                                                                                                                                  |

|          | 5.           | A POSITA would not be Motivated to Combine Mazzoni with Voith and G.993.1 142                                                                                                                                                                                              |

| VII.     | CON          | CLUSION                                                                                                                                                                                                                                                                    |

### I. INTRODUCTION

- 1. My name is Dr. Todor Cooklev, and I have been retained by TQ Delta LLC ("TQ Delta").

- 2. I have been asked to prepare this report ("Rebuttal Report") in connection with the above captioned District Court action between TQ Delta LLC and 2Wire, Inc. ("Defendant"). I have reviewed the report by Dr. Krista Jacobsen ("the Jacobsen Report") submitted in this litigation on November 28, 2018. I address the Jacobsen Report in detail below. Specifically, I have been asked to opine on Dr. Jacobsen's allegations that claim 1 of U.S. Patent No. 8,276,048 ("the '048 patent"), claim 5 of U.S. Patent No. 7,836,381 ("the '381 patent"), claim 13 of U.S. Patent No. 7,844,882 ("the '882 patent"), and claim 19 of U.S. Patent No. 8,495,473 ("the '473 patent") are invalid. I will be referring to the above-mentioned claims, collectively, as the Asserted Claims, and to the above-mentioned patents, collectively, as the Asserted Patents or the Family 3 Patents.

- 3. My qualifications were described in detail in Section II of my opening report on the infringement of the Family 3 Patents submitted on November 28, 2018 ("Cooklev Inf. Report"), as well as in my curriculum vitae, which was attached to that Report as Exhibit 1.

- 4. I also incorporate my discussion of the Asserted Claims and claim constructions from my opening report. *See, e.g.*, Cooklev Inf. Report at §§ VII.D-F, X.

- 5. In coming to my conclusions, I reviewed the materials identified in Exhibit1 to this Report, as well as all materials referenced in this Report.

- 6. As detailed below, based upon my personal knowledge, expertise, and the review and analysis I have performed to date, I have formed the following opinions:

- 7. Claim 1 of the '048 patent is valid. The claim covers patentable subject matter, is not obvious in view of the prior art as applied by Dr. Jacobson. The claim is supported by the specification's written description, enabled, and definite.

- 8. Claim 5 of the '381 patent is valid. The claim covers patentable subject matter, is not obvious in view of the prior art as applied by Dr. Jacobson. The claim is supported by the specification's written description, enabled, and definite.

- 9. Claim 13 of the '882 patent is valid. The claim covers patentable subject matter, is not obvious in view of the prior art as applied by Dr. Jacobson. The claim is supported by the specification's written description, enabled, and definite.

- 10. Claim 19 of the '473 patent is valid. The claim covers patentable subject matter, is not obvious in view of the prior art as applied by Dr. Jacobson. The claim is supported by the specification's written description, enabled, and definite.

- 11. I set forth below the bases and reasoning for these opinions. Specifically, I explain why Dr. Jacobson's opinions fail to invalidate the Asserted Claims on any basis. In doing so, I explain why each alleged prior art reference does not invalidate the Asserted Claims, by obviousness, and why the Asserted Claims are not invalid for lack of written description or enablement, or for indefiniteness.

- 12. I based this Report on information currently available to me. I reserve the right to expand, modify, or supplement my Report based on additional information, to the extent that information was not provided to me before this Report is due. I further

reserve the right to expand, modify, and/or supplement this Report and my opinions in response to matters raised by Defendant and/or Defendant's expert(s), opinions provided by other defendants and/or their expert(s) in related matters, or in view of relevant orders and findings by the Court.

- 13. In this Report, I cite to various documents and testimony. These citations are meant to be exemplary, and not exhaustive. Citations to documents or testimony are not intended to signify that my conclusions or opinions are limited to the cited sources, or supported by the cited sources only.

- 14. I expect to be available for deposition and to testify at trial in the above captioned actions. I reserve the right to perform demonstrations and use animations, demonstratives, and/or other physical evidence at trial. I expressly reserve the right to offer opinions at trial and/or in one or more supplemental reports on subjects raised in my deposition, as well as on matters raised by Dr. Jacobsen or by Defendant(s) in any subsequent report, at deposition, or at trial.

- 15. I am being compensated at \$400 per hour, which is my standard hourly consulting rate, plus reasonable expenses. I have not received any additional compensation for my work on this case, and no part of my compensation is dependent on my conclusions or on the outcome of the above captioned actions.

### II. APPLICABLE LEGAL PRINCIPLES

16. I have reviewed Dr. Jacobsen's statements of legal standards that Dr. Jacobsen purportedly applied in forming her opinions. While I generally agree with the statements on the law, the summarizations overlook several important points that result

in misleading opinions. I have been informed by TQ Delta's counsel about the legal principles that I understand control the issues that Dr. Jacobsen opined on and which I rebut. I have applied these legal standards to the facts, circumstances, and materials considered, along with my experience, in reaching the conclusions and opinions expressed in this Report.

## A. Presumption of Validity

- 17. It is my understanding that the claims of an issued U.S. patent are presumed valid. I further understand that the party challenging a patent claim's validity bears the burden of proving that claim invalid by clear and convincing evidence.

- 18. I understand that the standard for clear and convincing evidence is higher than the preponderance-of-evidence standard that is used to determine infringement. I am informed that the clear-and-convincing evidence standard requires an abiding conviction that the truth of a fact is highly probable.

- 19. I understand that this burden may be more difficult for a Defendant to meet if prior art was considered by the Examiner during the original prosecution of an Asserted Patent.

## B. Anticipation

20. I understand the following principles apply for determining anticipation under 35 U.S.C. § 102. A patent claim is anticipated by prior art when each element of the claim is present within a single prior art reference. In addition, each element of the claim must be arranged in the prior art as it is in the claim. An element may be either

expressly disclosed or inherent in the prior art. A claim element is only inherent if it is necessarily present in the reference. I further understand that the possibility, even if probable, that an element may result from a certain set of circumstances – that is, an element *might* be present – is not sufficient to establish inherency.

21. I have been informed that, although anticipation cannot be established through a combination of references, additional references may be used to interpret the allegedly anticipating reference by, for example, indicating what the allegedly anticipating reference would have meant to one of ordinary skill in the art. For the claim to be anticipated, however, these other references must make clear that the missing descriptive matter in the patent claim is necessarily or implicitly present in the allegedly anticipating reference, and that it would be so recognized by one of ordinary skill in the art.

## C. Obviousness

22. I understand the following principles apply for determining obviousness under 35 U.S.C. § 103. A claim may be invalid as obvious if the difference between the claimed subject matter and one or more prior art references are such that the subject matter as a whole would have been obvious at the time the invention was made to a person of ordinary skill in the art ("POSITA"). The following factors must be found and considered in determining obviousness: (1) the scope and content of the prior art; (2) the differences between the art and the claims at issue; (3) the level of ordinary skill in the art; and, (4) objective evidence of non-obviousness, which is also referred to as secondary considerations.

- 23. It is not enough that the prior art references can be combined; there must be a motivation to one of ordinary skill in the art to arrive at the claimed invention. But I also understand that motivation may not be gleaned from impermissible hindsight reasoning. That is, the reason to combine the prior art to arrive at the claimed invention cannot be based in whole or in part on the inventors' own disclosure.

- 24. I understand that assessing which prior art references to combine and how they may be combined to match the asserted claim may not be based on hindsight reconstruction. Hindsight reconstruction is using the patent itself as a road map for recreating the invention. In assessing obviousness, only what was known before the invention was made can be considered. I also understand that one important guard against such hindsight reconstruction is a determination whether a person of ordinary skill in the art would have been motivated, taught, or suggested to combine the relevant techniques of the prior art to duplicate the patent claims at the time of the patented invention.

- 25. I understand that obviousness cannot be predicated on the mere identification in the prior art of individual components of claimed limitations. It is not appropriate to pick and choose among the individual elements of assorted prior art references to recreate the claimed invention, but rather, there must be some teaching or suggestion in the references to support their use in the particular claimed combination.

- 26. I understand that it is the Defendant's burden to prove that a person of ordinary skill in the art would have been motivated to combine the prior art references.

I understand that the motivation to combine must be supported by evidence and

articulated explanation. When considering obviousness, I understand that it is insufficient to simply say that a skilled artisan, once presented with a combination of references, would have understood that they could be combined.

- 27. Rather, the Defendant must show that the skilled artisan would have been motivated to make the combinations or modification of prior art to arrive at the claimed invention. Conclusory statements alone are insufficient, and any obviousness analysis must be supported by a reasoned explanation as to why a person of ordinary skill in the art would have been motivated to combine the prior art. For example, "common sense" or "intuition" alone cannot support a motivation to combine without explaining why they would lead a skilled artisan to solve the problem at hand with the particular elements of the claimed invention.

- 28. I understand that, to determine the scope and content of the prior art, I must consider whether the prior art was reasonably relevant to the particular problem the inventors faced in making the claimed invention.

- 29. To determine whether any material differences existed between the scope and content of the prior art and each asserted claim, I must consider the claimed invention as a whole to determine whether or not the claim would have been obvious in light of the prior art. If the prior art discloses all the elements in separate references, I must consider whether it would have been obvious to combine those references. I understand that a claim is not obvious just because all elements of a claim already existed.

- 30. I understand that a motivation to conduct further testing or research that may lead to the claimed invention does not necessarily render a claim obvious. I further understand that an invention is not necessarily rendered obvious simply because it was obvious to try a certain combination.

- 31. Secondary considerations may also impact a determination of obviousness, provided that there is some nexus or link between the claimed invention and the secondary factors considered. I further understand that any secondary factors that may prove instructive in determining non-obviousness should be considered. The following are examples:

- (1) a long-felt, but unmet need for the invention;

- (2) prior art teaching away from the invention;

- (3) failure of others to make the invention;

- (4) praise for the invention;

- (5) commercial success;

- (6) copying of the invention;

- (7) initial skepticism for the invention;

- (8) licensing;

- (9) whether the invention proceeded in a direction contrary to accepted wisdom in the field.

- 32. I understand that the inquiry into secondary considerations is a means to check hindsight analysis. I am informed that it is impermissible to use hindsight and that it is improper to focus on just one portion or element of the invention, as opposed to the invention as a whole.

33. I also understand that when prior art teaches away from combining prior art references, the discovery of a successful way to combine them is unlikely to be obvious. Prior art teaches away from an invention when a person of ordinary skill would be discouraged or diverted from following the path leading to the invention because of the prior art. I also understand that if a proposed combination would require modification of prior art and that modification would render the prior art unsatisfactory for its intended purpose, then there is no suggestion or motivation to make the proposed combination and modification.

## D. Written Description

34. I understand the following legal principles apply to assessing whether a patent is invalid for not meeting the written description requirement in 35 U.S.C. § 112, ¶ 1. The written description requirement evaluates whether the patent applicant had possession of the full scope of the claimed invention at the time the patent application was filed. This evaluation is made from the perspective of one of ordinary skill in the art. Claims may be broader than the embodiment or embodiments identified in the specification, and the specification may contain adequate written description of a broadly claimed invention without expressly describing every embodiment the claim encompasses.

### E. Definiteness and Enablement

35. I also understand that claims must be particular and distinct, which is also referred to as a definiteness requirement in 35 U.S.C.  $\S$  112,  $\P$  2. This definiteness requirement provides that a patent applicant must particularly point out and distinctly

claim the subject matter that the applicant regards as the invention. The definiteness standard is one of reasonableness under the circumstances. In other words, in light of the teachings of the prior art and of the particular invention, the definiteness inquiry is whether the claims inform those skilled in the art about the scope of the invention with reasonable certainty.

- 36. The enablement requirement requires the inventor to describe his or her invention in a manner that would allow others in the industry to make and use the invention. To analyze enablement, one needs to take into account the knowledge of a POSITA.

- 37. I understand that a patent need not teach, and preferably omits, what is well known in the art. I also understand that resort to material outside of the specification in order to satisfy the enablement requirement is permissible because it makes no sense to encumber the specification of a patent with all the knowledge of the past concerning how to make and use the claimed invention. I further understand that the fact that some experimentation is necessary does not preclude enablement, but that any required experimentation must be reasonable. Some trial and error is permissible.

- 38. Further, I have been informed that enablement does not require the inventor to foresee every means of implementing an invention. Finally, I am informed that the specification need not necessarily describe how to make and use every possible variant of the claimed invention, for the artisan's knowledge of the prior art and routine experimentation can fill in any gaps, interpolate between embodiments, and even extrapolate beyond the disclosed embodiments.

## F. Claiming Priority to A Provisional Application

39. I understand that a patent may be given the prior art date of the patent's provisional application. I am informed that a reference patent is entitled to claim the benefit of the filing date of its provisional application if the disclosure of the provisional application provides support for the claims in the reference patent.

### III. PERSON OF ORDINARY SKILL IN THE ART

40. I defined a person of ordinary skill in the art with respect to the subject matter of the Family 3 Patents in Section VI.A of my Opening Infringement Report. I incorporate that definition by reference. *See* Cooklev Inf. Report at § VI.A.

### IV. BACKGROUND OF DSL TECHNOLOGY AND INVENTION

41. I set forth a background of DSL communications, error correction, interleaver and deinterleaver memory, and the inventions of the Asserted Patents alongside with their befits in Sections VII.A-F of my Opening Infringement Report. *See* Cooklev Inf. Report at §§ VII.A-F. I incorporate those sections by reference.

## A. Interleaver Memory and Deinterleaver Memory in Prior Art Systems

42. DSL systems, such as, for example, ADSL2/2+ standards known at the time of the inventions, specify dedicated interleaving memory requirements in each transceiver separately for upstream and downstream transmission (i.e., in each direction separately). More specifically, an ADSL2/2+ ATU-C is required to have a specified amount of dedicated interleaving memory for downstream data transmission and separately and independently have a specified amount of dedicated interleaving memory for upstream data reception. ADSL2/2+ specifies that the ATU-C must have

enough dedicated memory for <u>downstream</u> interleaving to interleave codewords sizes of Nfec= 255 bytes with an interleaver depth of D=64. This corresponds to Nfec  $\times$  D=255  $\times$  64 = 16,320 octets of dedicated interleaving memory for downstream. Likewise, ADSL2/2+ specifies that the ATU-C must separately have enough dedicated memory for <u>upstream</u> deinterleaving to deinterleave codewords sizes of Nfec= 255 bytes with an deinterleaver depth of D=8. This corresponds to Nfec  $\times$  D=255  $\times$  8 = 2,048 octets of dedicated deinterleaving memory for upstream. The total interleaving + deinterleaving memory requirement for an ATU-C is therefore approximately 16K + 2K = 20K. These requirements are specified (or derived from values provided) in Tables 7-7, 7-8, 7-9 and 7-10 of G.992.3/2002.

43. In the same manner, an ADSL2/2+ ATU-R is required to have a specific amount of dedicated interleaving memory for downstream data reception and separately have a specific amount of dedicated interleaving memory for upstream data transmission. Like the ATU-C, ADSL2/2+ specifies that the ATU-R must have enough dedicated memory for downstream deinterleaving to deinterleave codewords sizes of Nfec= 255 bytes with an deinterleaver depth of D=64. This corresponds to Nfec x D=255 x 64 = 16,320 octets of dedicated deinterleaving memory for downstream. Like the ATU-C, ADSL2/2+ specifies that the ATU-R must have enough memory for upstream interleaving to interleave codewords sizes of Nfec= 255 bytes with an interleaver depth of D=8 for upstream. This corresponds to Nfec x D=255 x 8 = 2,048 octets of dedicated interleaving memory. The total deinterleaving + interleaving memory requirement for

an ATU-R is therefore approximately 16,320 + 2,048 = 18,368 octets. These requirements are specified in Tables 7-7, 7-8, 7-9 and 7-10 of G.992.3/2002.

- 44. The ADSL2/2+ standards do not specify or enable memory sharing between the interleaver and the deinterleaver in a single transceiver. Furthermore, since ADSL2/2+ specify that the ATU-C downstream interleaver and the ATU-R downstream deinterleaver have the same amount of memory (i.e., ~16K octets) there are no messages specified (or ever needed) to negotiate the amount of memory to be allocated to the interleaver (in the ATU-C) or to the deinterleaver (in the ATU-R). Likewise, since ADSL2/2+ specify that the ATU-R upstream interleaver and the ATU-C upstream deinterleaver have the same amount of memory (i.e. ~2K octets) there are no messages specified (or ever needed) to negotiate the amount of memory to be allocated to the interleaver (in the ATU-R) or to the deinterleaver (in the ATU-C).

- 45. Prior to the inventions disclosed in the Family 3 patents, an amount of memory available to an interleaver was predetermined and an amount of memory available to a deinterleaver was predetermined. Those systems were incapable of sharing memory between an interleaving and deinterleaving function based on a message.

## B. Shared Interleaver and Deinterleaver Memory in the Family 3 Patent Inventions

46. The below examples illustrate how, even if one of the transceivers provided more memory than the minimum specified by a standard, the interleaver memory and the deinterleaver memory in a single transceiver had been implemented in

prior art systems before the inventions of the Family 3 patents in comparison with how the shared memory can be allocated to an interleaver and a deinterleaver according to the inventions of the Family 3 patents.

- 47. Generally, a transceiver (e.g., VTU-R) with a larger dedicated deinterleaver memory than is required could at most determine whether a transceiver (e.g., VTU-0) at the other line of the line can also support a larger amount. But, if the VTU-O does not support a larger amount than is required, however, the extra deinterleaver memory of the VTU-R is simply not used. For example, it is not available to be used for the upstream interleaver function. The examples described below illustrate this concept.

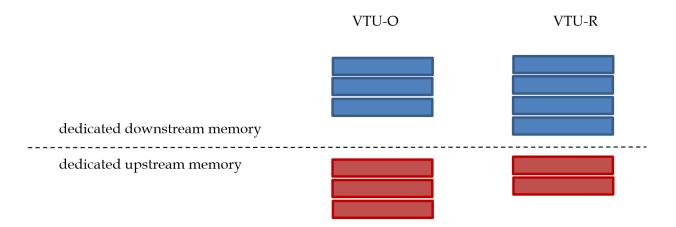

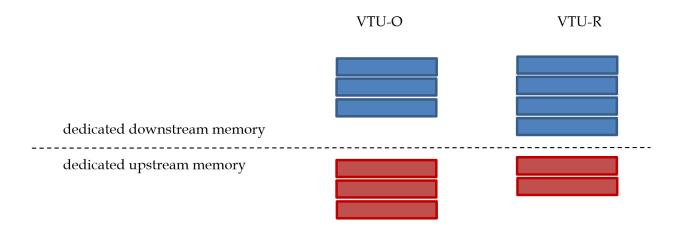

- 48. Example 1 (Prior Art Systems). VTU-O (30,000 octets of dedicated downstream interleaver memory; 30,000 octets of dedicated upstream deinterleaver memory). VTU-R (40,000 octets of dedicated downstream deinterleaver memory; 20,000 octets of dedicated upstream interleaver memory).

Legend:

dedicated downstream memory (interleaver memory for VTU-O, deinterleaver memory for VTU-R)

dedicated upstream memory (interleaver memory for VTU-R, deinterleaver memory for VTU-O)

Each rectangle represents 10,000 octets of memory.

49. Capabilities (maximum memory supported):

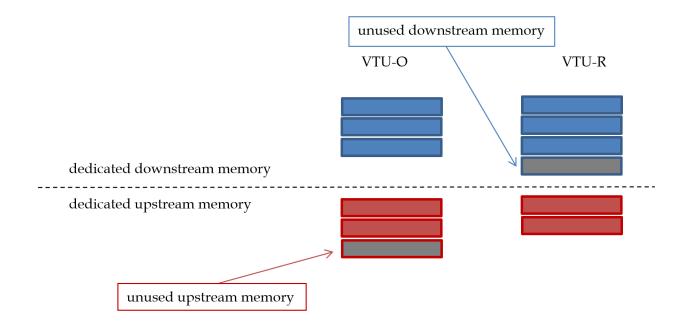

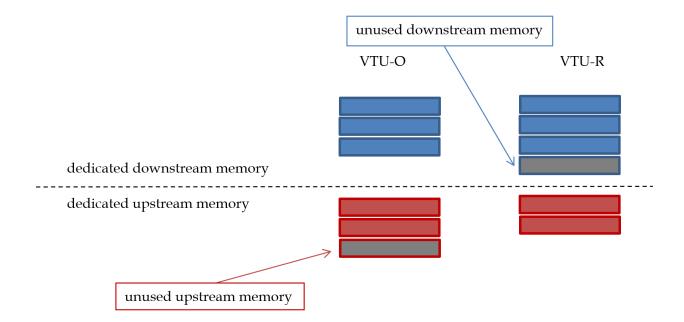

50. Even if each transmitter exchanged their memory capabilities in each direction, the smaller of the transmitter and receiver capabilities in each direction would need to have been chosen. Because the smaller capability is selected, this results in a maximum possible memory allocation as shown below.

- 51. Also, because the smaller of the capabilities of the transmitter or receiver are selected in each direction, unused memory for one function in a transceiver cannot be used for another function, e.g., unused dedicated deinterleaver memory in the VTU-R cannot be used for the interleaving function. In the example above, 10,000 octets of deinterleaver memory within the VTU-R and 10,000 octets of deinterleaver memory in the VTU-O would never be used.

- 52. Under such implementation even though the VTU-R learned about the VTU-O's capabilities downstream, it could not use 10,000 octets of its 40,000 octets of memory that was dedicated to the downstream deinterleaver. Likewise, even though the VTU-O learned about the VTU-R's capabilities upstream, it could not use 10,000 octets of its 30,000 octets of memory that was dedicated to the upstream deinterleaver.

- 53. In this example, if a service provider is providing a VDSL2 service that requires 30,000 octets of memory in each transceiver for the downstream service and 20,000 octets of memory in each transceiver for the upstream service, the transceivers would be able to provide that service. If, however, a service provider is providing a VDSL2 service that requires 30,000 octets of memory in each transceiver for the downstream service and 30,000 octets of memory in each transceiver for the upstream service, the transceivers would NOT be able to meet the requirements of the service.

- 54. The above example can be contrasted with an example implementing the claimed allocation of memory between an interleaving function and a deinterleaving function according to the inventions of the Family 3 patents (Example 2, *infra*).

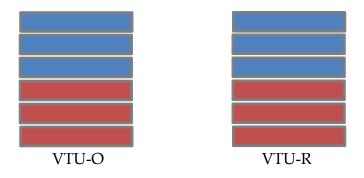

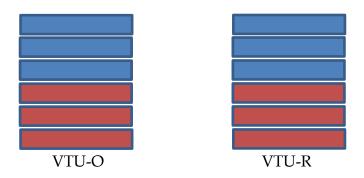

55. Example 2 (Family 3 Patents). Each transceiver supports a total of 60,000 octets of shared interleaver/deinterleaver memory. If the service provider desires to provide a VDSL2 service that requires 30,000 octets of memory in each transceiver for the downstream service and 30,000 octets of memory in each transceiver for the upstream service, the 60,000 octets of memory in each transceiver could be allocated between the interleaver and deinterleaver functions such that 30,000 octets in each transceiver are used for the downstream path and 30,000 octets are used for the upstream path as illustrated below.

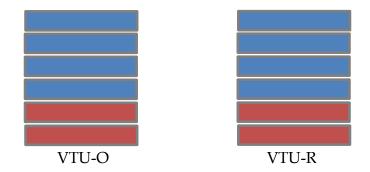

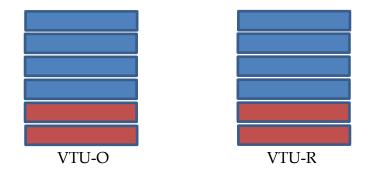

56. On the other hand, if the service provider desires to provide a VDSL2 service that requires 40,000 octets of memory in each transceiver for the downstream service and 20,000 octets of memory in each transceiver for the upstream service, the 60,000 octets of memory in each transceiver could be allocated between the interleaver and deinterleaver functions such that 40,000 octets in each transceiver are used for the downstream path and 20,000 octets are used for the upstream path as illustrated below.

57. Therefore, unlike the prior art systems where 10,000 octets of memory are unused and the service provider could not provide the service to the customer, when shared memory, which can be allocated between the interleaver function or deinterleaver function, is used, memory that would otherwise go unused can be allocated to one function or the other depending on messages that are, in part, dependent on the service requirements. As illustrated by these examples, the VTU-R is capable of allocating 10,000 octets of its memory to the upstream interleaving function at one time but allocating the same 10,000 octets of its memory to the downstream deinterleaving function at another time. This provides flexibility that enables the transceivers to meet different service requirements.

# C. References Cited in Jacobsen Report are Consistent with Implementations that Precede the Inventions of Family 3 Patents

58. Dr. Jacobsen asserts that prior art systems were capable of providing "shared memory that the transceiver can partition between its interleaver and deinterleaver on a per-connection basis. Use of shared memory for interleaving and

deinterleaving, including in DSL, was well known before the priority date of the Family 3 patents." *See* Jacobsen Report at ¶ 72. This is incorrect.

- 59. To support her argument, Dr. Jacobsen cites to several prior art references. Yet, none of these references discloses what she asserts that they do.

- 60. Berkmann does not disclose providing "shared memory that can be partitioned between its interleaver and deinterleaver on a per-connection basis," as Dr. Jacobsen asserts. See Jacobsen Report at ¶ 72. While Berkmann describes using "a combined interleaving and deinterleaving circuit," (id. at Abstract), it further explains that "[o]nly the interleaving function  $\alpha(i)$  (or, alternatively, the inverse deinterleaving function  $\alpha^{-1}(i)$ ) must be implemented, but not both functions" (id. at ¶ 102). Without much further analysis of Berkmann needed, it is clear that regardless of whether the "combined interleaving and deinterleaving circuit" meets a definition of shared memory as construed by the Court (and it does not), it is not being partitioned between the interleaving function and the deinterleaving function, and it is not being partitioned on a per-connection basis. At most, Berkmann discloses a circuit for carrying out interleaving or deinterleaving, but not both, at the same time, which does not disclose shared memory as construed by the Court.

- 61. Fadavi-Ardekani does not disclose providing "shared memory that can be partitioned between its interleaver and deinterleaver on a per-connection basis," as Dr. Jacobsen asserts. *See* Jacobsen Report at ¶ 72. As explained in, for example, Sections VI.C.1 and VI.C.2, *infra*. Fadavi only teaches that the interleaver and deinterleaver are each provided with a size of memory that "is derived by multiplying the maximum

codeword length by the maximum interleaver depth." Fadavi at 7:9-10. Thus, Fadavi teaches using dedicated memories for the interleaving function and deinterleaving function. Also, as explained in those sections, the disclosed "ping-pang" operation does not meet the shared memory requirement, nor is it the memory assigned on perconnection basis.

- 62. Kang does not disclose providing "shared memory that can be partitioned between its interleaver and deinterleaver on a per-connection basis," as Dr. Jacobsen asserts. *See* Jacobsen Report at ¶ 72.

- 63. Mazzoni does not disclose providing "shared memory that can be partitioned between its interleaver and deinterleaver on a per-connection basis," as Dr. Jacobsen asserts. *See* Jacobsen Report at ¶ 72. As explained in, for example, Sections VI.B.1, VI.B.3.a, and VI.B.3.b, *infra*, Mazzoni describes the assignment of interleaver memory and deinterleaver memory for predefined data rate pairs (services) by using predefined I and M parameter values for its interleaving means, and predefined I' and M' parameter values for deinterleaving means for each data rate pair (i.e., service). *Id.* at 5:24-30. Also, as explained in the cited sections, the assignment is performed at the time of an installation of the modem, and not per-connection basis. *See* Mazzoni at 6:51-61.

- 64. Voith does not disclose providing "shared memory that can be partitioned between its interleaver and deinterleaver on a per-connection basis," as Dr. Jacobsen asserts. *See* Jacobsen Report at ¶ 72. As explained in Sections VI.E.1 and VI.E.2, *infra*.

Voith merely teaches use of an external memory. Voith does not teach that the external memory is "shared memory."

### V. THE ASSERTED CLAIMS OF THE FAMILY 3 PATENTS ARE VALID

- 65. As set forth in this Rebuttal Report, it is my opinion and conclusion that each Asserted Claim of the Family 3 Patents are not invalid in view of the alleged prior art as asserted in the Jacobsen Report.

- 66. In performing my analysis, I have compared the limitations of each Asserted Claim with the disclosure in the alleged prior art references. I have also considered the scope and content of the prior art, the differences between the prior art and the claimed invention, the level of ordinary skill in the art at the time of the invention, and whether the differences are such that the claimed invention as a whole would have been obvious to one of ordinary skill in the art at the time the invention was made.

- 67. In my analysis below, I have applied, where applicable, the Court's claim construction. *See* Cooklev Inf. Report at § X.

## A. Claim 19 of the '473 patent is valid under 35 U.S.C. § 112, ¶2

68. Dr. Jacobsen asserts that:

[C]laim 19 of the '473 patent is indefinite. Claim 19 recites the limitation 'wherein at least a portion of the memory <u>may be</u> allocated to the interleaving function or the deinterleaving function at any one particular time depending on the message.' One of ordinary skill in the art would not have known with reasonable certainty whether a portion of the memory actually has to be allocated to an interleaving function at one time, and a deinterleaving function at another, or whether the mere possibility that some portion of the memory could possibly be allocated to

the interleaving or deinterleaving function suffices to meet the claim language."

Jacobsen Report at ¶ 151 (emphasis in original).

- 69. I disagree with Dr. Jacobsen's conclusion as well as with the arguments she presents to support her position as explained below.

- 70. Dr. Jacobsen's arguments are premised on the assertion that the "Court determined that this language should have its plain meaning during claim construction." Jacobsen Report at ¶ 151. While it is true that the Court gave plain meaning to this claim term, the Court also provided context for this claim language, which Dr. Jacobsen ignores in her analysis. Specifically, the Court noted:

The claim language does not require that the message specify amounts of memory. The disputed term's language requires that the amount of memory depend on the message's contents, but it does not require that the message's contents themselves actually specify amounts of memory.

Claim Construction Memorandum for Family 3 Patents (Dec. 18, 2017), D.I. 445, ("CC Memo") at p. 10.

71. Dr. Jacobsen ignores the Court's guidance in reaching her conclusion that:

It is not clear from the intrinsic record, however, whether this allocation actually has to happen, at some point, in order for a device to infringe. For example, a system could use a shared memory in such a way that it is theoretically possible that a portion of the memory is allocated to a deinterleaver or an interleaver, depending on the message, but it might not actually ever happen in practice. One of ordinary skill in the art would not have understood whether such a system would infringe claim 19 of the '473 patent.

Jacobsen Report at  $\P$  152.

72. As an initial matter, Dr. Jacobsen refers to the "claims, specification, and file history" as purportedly supporting her unfounded argument. Yet, Dr. Jacobsen

does not explain how either supports her conclusion. In fact, Dr. Jacobsen does not quote from or cite to the claims, specification, or the file history.

- 73. In any event, Dr. Jacobsen's assertion indicates that she misunderstands the scope of an apparatus claim that defines structure in functional terms. I understand that an apparatus claim is infringed when the accused apparatus is capable of infringement. Therefore, the answer to Dr. Jacobsen's question about the scope of the claim is that the claimed allocation does not actually have to happen in order for the claim to be infringed. Rather, the claim is infringed by transceivers that are capable of allocating at least a portion of the memory to the interleaving function or the deinterleaving function at any one particular time depending on the message.

- 74. A POSITA would understand that this claim language, as even the Court agreed, requires only that the function to which the portion of memory is allocated at one particular time depends on the message's contents. The use of the term "may" does not render the scope of the claim indefinite. Rather, "may" is the most appropriate term given that the claim provides two possibilities on its face that, depending on the message, (1) the portion of memory be allocated to the interleaver function at a particular time, or (2) the portion of memory be allocated to the deinterleaver function at a particular time. A transceiver that is not capable of allocating at least some portion of memory to interleaving at one time and allocating that same portion to deinterleaving at another time would not infringe. A transceiver that is capable of doing so, such as the Accused Products, would infringe. Thus, claim 19 the '473 patent

informs those skilled in the art about the scope of the invention with reasonable certainty.

- 75. I note that 2Wire did not raise this indefiniteness argument during claim construction, and in fact proposed a claim construction that literally included the phrase "memory may be allocated." CC Memo at 9-10 (2Wire's proposed construction: "wherein at least a number of bytes within the memory may be allocated to the [first] interleaving function or the [second interleaving / deinterleaving] function at any one particular time depending on the amounts of memory specified in the message."). While I do not agree that 2Wire's proposed claim construction is accurate, 2Wire and Dr. Jacobsen had no problem proposing a construction that included this phrase verbatim. One must assume that 2Wire would not have proposed an indefinite construction for this claim element.

- 76. For the foregoing reasons, it is my opinion that claim 19 of the '473 patent is definite and that Dr. Jacobsen has not proven otherwise.

## B. Written Description and/or Enablement under 35 U.S.C. § 112, ¶1

77. The Court construed the term "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver / deinterleaver]" to mean "the deinterleaver reads from, writes to, or holds information for deinterleaving in its respective allocation of the shared memory at the same time as the interleaver reads from, writes to, or holds information for interleaving in its respective allocation of the shared memory." Dr. Jacobsen contends

that this term lacks written description and enablement. Jacobsen Report at ¶ 153. I disagree.

78. Dr. Jacobsen acknowledges that "[t]he specification describes sharing resources, such as memory and processing power, as well as ways of allocating those shared resources." Jacobsen Report at ¶ 154. She asserts, however, that the specification purportedly does not "describe or explain how shared memory that is allocated to an interleaver and a deinterleaver can be used at the same time, or even what "used at the same time" even means. As an initial matter, I understand that there is no requirement that the specification describes what "used at the same time means" as long as the plain meaning of the claim language is understood in view of the specification. That is the case here. "Used at the same time" is a common and well understood term in general and one of skill in the art understands what it means to "use" memory. In any event, 2Wire agreed to the Court's construction of this term. CC Memo at p. 9.

79. Further, a POSITA would know how memory that is allocated to two different functions can be "used at the same time." While Dr. Jacobsen asserts that one of skill in the art would not know how this can be done, she does not explain why this is so. In any event, I disagree with her unsupported assertion. The simultaneous use of memory by multiple functions was a well-known process at the time of the inventions. A POSITA at that time would know how two or more functions can simultaneously use the same memory by storing information for a first function at the same time that information for a second function is stored in the memory, or written to the memory, or

read from the memory. This is inherent in any multi-threaded operation that uses the same memory.

- 80. Dr. Jacobsen asserts that the specification does not explain how memory allocated to an interleaver and memory allocated to a deinterleaver can be used at the same time. Jacobsen Report at ¶ 154. I understand that such explanation in the specification is not required. Rather, I understand that a patent need not teach, and preferably omits, what is well known in the art. I also understand that resort to material outside of the specification in order to satisfy the enablement requirement is permissible because it makes no sense to encumber the specification of a patent with all the knowledge of the past concerning how to make and use the claimed invention. Therefore, it was not necessary to provide a full and detailed explanation where, as here, a POSITA would know how to implement the claim.

- 81. As for Dr. Jacobsen's assertion that there is no written description support for "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver / deinterleaver]," I disagree. Jacobsen Report at ¶ 155. 2Wire actually took the opposite position in its claim construction briefing:

Defendants' proposed construction correctly reflects that the shared memory is read to and written from at the same time by the interleaver and the deinterleaver. Defendants' proposed construction is consistent with the specification, which discloses that "the transmitter and/or receiver latency paths of the transceiver can share an interleaver/deinterleaver memory and the shared memory can be allocated to the interleaver and/or deinterleaver of each latency path."

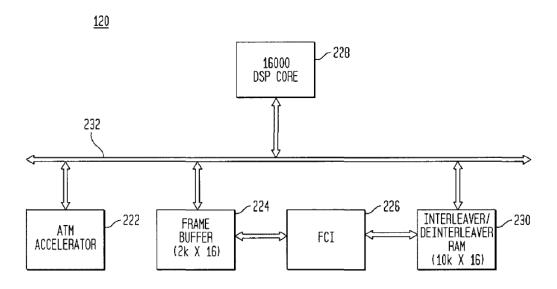

Parties' Joint Claim Construction Brief for the Family 3 Patents, D.I. No. 353, at p. 58. Additional disclosure that shows that the patent applicant had possession of this element of the claimed invention at the time the patent application was filed is found at, e.g., U.S. Patent 7,831,890¹ patent at, e.g., Fig. 1 (illustrating shared memory 120 that services at least two interleaving functions and two deinterleaving functions); 6:56-64 and 7:7-25 (explaining that "the transmitter portion and/or receiver portion latency paths would be reconfigured to utilize the shared memory" and describing simultaneous transmitting/encoding and decoding/receiving of the latency paths); 8:11-39 (describing simultaneous use of different portions of a shared memory for various applications).

82. Dr. Jacobsen also asserts that the Family 3 patents lack written description support "wherein at least a portion of the memory may be allocated to the interleaving function or the deinterleaving function at any one particular time depending on the message." She does not provide any explanation of why this is so. In any event, I disagree. Disclosure that shows that the patent applicant had possession of this element of the claimed invention at the time the patent application was filed is found generally because the specification discloses the use of "shared memory" by an interleaver and a deinterleaver where the Court interpreted shared memory to mean "common memory used by at least two functions, where a portion of the memory can be used by either one of the functions." CC Memo at p. 5. A POSITA would understand from the disclosure

<sup>&</sup>lt;sup>1</sup> The '890 patent is the original, non-provisional application in the chain with the asserted Family 3 patents.

of shared memory that the portion of shared memory that is allocated to an interleaver would not be used at the same time by a deinterleaver but, instead, could be used at alternative times depending on the allocation in effect at the time.

- 83. I reserve the right to address any support or explanation Dr. Jacobsen's attempts to provide for her currently conclusory assertions regarding written description and enablement.

- 84. Based on the foregoing, it is my opinion that the claim 1 of the '048 patent, claim 5 of the '381 patent, and claim 13 of the '882 patent satisfy the written description and enablement requirements.

### C. Certificate of Correction

- 85. I disagree with Dr. Jacobsen's opinion that the "Certificate of Correction changed the scope and meaning of the '381 and '882 patent." Jacobsen Report at ¶ 160. The certificate of correction was properly issued by the patent office to correct obvious typographical errors. Claim 5 of the '381 patent as corrected provides in relevant part:

- 5. A non-transitory computer-readable information storage media having stored thereon instructions, that if executed by a processor, cause to be performed a method for allocating shared memory in a transceiver comprising:

allocating, in the transceiver, a first number of bytes of the shared memory to the deinterleaver to deinterleave a first plurality of Reed Solomon (RS) coded data bytes for transmission reception at a first data rate, wherein the allocated memory for the deinterleaver does not exceed the maximum number of bytes specified in the message;

allocating, in the transceiver, a second number of bytes of the shared memory to an interleaver to interleave a second plurality of RS coded data bytes received transmitted at a second data rate;

- 86. I have reviewed the specification and it is my opinion that based on the specification, it is clear that the errors were clerical or typographical. Specifically, FIG. 1 of the specification depicts an interleaver as being associated with transmitting and the deinterleaver as being associated with reception. On the other hand, the specification is not consistent with Dr. Jacobsen's hypothetical device that deinterleaves RS coded data bytes before transmitting them and receives RS coded data bytes before interleaving them. Indeed, the best Dr. Jacobsen can say is that the Family 3 patents "do not appear to foreclose either of these possibilities."

- 87. Dr. Jacobsen's suggests that the statement in the specification that "the invention can be applied to any transceiver having any number of latency paths" somehow precludes the correction. I disagree. That statement merely means that a transmitter of a transceiver can have any number of latency paths and the receiver of the same transceiver can have any number of latency paths. For example, a CO transmitter could have one or two downstream latency paths to the CPE and one or two upstream latency paths from the CPE.

- 88. Dr. Jacobsen's assertion that "a person of ordinary skill in the art would [not] have considered the terms 'transmission' and 'received' in claim 5 of the '381 patent and claim 13 of the '882 patent to be typographical errors" is not credible, especially so in light of the statements made elsewhere in the Jacobsen Report. For example, at ¶ 55 of the Jacobsen Report, Dr. Jacobsen concedes that "[t]o <u>apply interleaving</u>, the transmitter <u>shuffles consecutive bytes</u> of the data stream in a known and systematic way <u>before transmitting them</u> . . . ." See also, Jacobsen Report at ¶ 60 (".

. . transmitter interleaves the bytes prior to transmission."). Thus, Dr. Jacobsen recognizes that bytes are interleaved prior to being "transmitted." Dr. Jacobsen also admits that "the receiver . . . can reverse the interleaving process by collecting all of the interleaving data elements and using a complementary deinterleaving process." Jacobsen Report at ¶ 58. Thus, Dr. Jacobsen recognizes that bytes are deinterleaved after "reception."

89. Accordingly, her assertion that the errors were not typographical (or that they would not have been recognized as typographical) is meritless.

### VI. ANALYSIS OF THE CITED REFERENCES

### A. The Asserted Claims Are Not Obvious Over LB-031

- 90. It is my opinion and conclusion that LB-031 alone or in combination with other cited references fails to disclose or suggest each element of the Asserted Claims, and hence fails to render the Asserted Claims anticipated or obvious as described in detail, below.

- 91. It is also my opinion that regardless of the disclosure of LB-031 and the other cited references, a person of ordinary skill in the art would not be motivated to combine the teachings of LB-031 with the teachings of the other cited references at least for the reasons described in Section VI.A.2.a, *infra*.

#### 1. Overview of LB-031

92. LB-031 focuses on defining an interleaver delay in units of time to allow reduced interleaver complexity at lower data rates. *See* LB-031 at 3 (2WIRE00030959) ("Therefore, it seems prudent to define the interleaver complexity requirements in a

way that will allow those who want to deploy VDSL2 at lower speeds to do so at a reduced complexity with respect to higher speed implementations. The way to do this and to guarantee some minimum level of performance is to specify the interleaver complexity in terms of the delay in time.").

- 93. LB-031 notes that the delay in time is proportional to the interleaver depth and to the codeword size and inversely proportional to the data rate. *Id*.

- 94. LB-031 describes memory requirements for an "interleaver/deinterleaver pair." See, e.g., LB-031 at 2 (2WIRE00030958) ("The smallest amount of memory required to build an interleaver/deinterleaver pair is equal to the total delay of the interleaver/deinterleaver. Typically, for memory optimized interleavers, the interleaver and deinterleaver memory size is nearly the same."). See also § VI.A.2, infra. The interleaver of this "pair" is located in the transmitter lineup of one transceiver, while the deinterleaver of the "pair" is located in the receiver lineup of the other transceiver. The "pair" are associated with a single latency path and direction, i.e., a single path in the upstream direction or a single path in the downstream direction.

- 95. While LB-031 acknowledges that "[t]he size of the interleaver memory will be a major source of complexity in VDSL2," it does not describe the combined memory requirements of an interleaver associated with one direction (e.g., upstream) and deinterleaver associated with the other direction (e.g., downstream) within a single transceiver. Nor does it describe sharing a memory between an interleaver and deinterleaver in a single transceiver as called for by the Asserted Claims of the Family 3 Patents and as described in more detail in VI.A.2, *infra*, and IV.A-IV.B, *supra*. Instead,

LB-031 focuses on selecting an amount of interleaver or deinterleaver memory for a single direction (i.e., by comparing capabilities of the transmitter on one end of a communication channel with the capabilities of the receiver on the other end). *See, e.g.,* LB-031 at 3 (2WIRE00030959). The relevant portion of LB-031 is quoted below:

For interoperability reasons, the VTU-O and VTU-R must exchange the interleaver delay in terms of octets. The requirement is that the interleaver delay in octets be sufficient to satisfy the smallest maximum delay even at the highest supported data rate. If a VDSL2 implementation supports a larger interleaver memory than is required, it should be free to specify the larger value. The VTU-O and VTU-R would then select the smaller of the transmitter and receiver capabilities, in each direction, as the end-to-end capabilities.

Id.

- 96. Contrary to Dr. Jacobsen's opinion, there is nothing in LB-031 that would suggest to a POSITA that a memory is being shared, or should be shared, between an interleaver and a deinterleaver in a single transceiver.

- 97. At least for these reasons, and for the reasons described in detail below, it is my opinion and conclusion that LB-031 fails to disclose or suggest all element of the Asserted Claims, and hence fails to render the Asserted Claims obvious.

### 2. LB-031 Does Not Render Claim 1 of the '048 Patent Obvious

98. It is my opinion and conclusion that LB-031 alone or in combination with other cited references fails to disclose or suggest each element of claim 1 of the '048 patent, and hence fails to render the Asserted Claims anticipated or obvious as described in detail, below.

### a. LB-031 does not disclose a system that allocates shared memory.

99. Contrary to Dr. Jacobsen's assertion, the LB-031 reference does not disclose a system that allocates shared memory. *See* Jacobsen Report at ¶¶ 179-181. Dr. Jacobsen has not pointed to any portion of LB-031 that states, or that would have disclosed to a POSITA that a transceiver implementing the LB-031 reference allocates shared memory.

100. Dr. Jacobsen points to Eq. 1 and Eq. 5, and corresponding descriptions in the LB-031 reference to assert that a POSITA "would have understood this example to teach allocating memory for interleaving and deinterleaving." See Jacobsen Report at ¶ 180. As an initial matter, this statement is vague because it is not clear whether it is intended to describe the memory of a single transceiver or, on the other hand, the separate memories of a respective interleaver in one transceiver and corresponding deinterleaver in a second transceiver. To the extent she intends the latter, such teaching is not relevant to any asserted claim of the Family 3 patents because the claims are directed to allocating a shared memory between and interleaver and deinterleaver within a single transceiver. To the extent she intends the former, her statement is incorrect.

101. The disclosure of LB-031 Dr. Jacobsen relies on for purportedly disclosing allocating a shared memory is the passage on page 4 of LB-031, which states "[i]f the minimum interleaver delay requirement were 5.23 ms, then, from equation (5) and equation (1), this transceiver must support a delay of at least 29092 octets which corresponds to having an interleaver memory of at least 14546 octets according to

equation (2)." See Jacobsen Report at ¶ 180. This discussion in LB-031, however, has nothing to do with sharing memory or allocating a shared memory. Rather, it is describing the memory requirements for an interleaver in one transceiver and the corresponding memory requirements for a deinterleaver in a second transceiver at the other end of the communication channel. As the reference discloses, for an end-to-end delay of 29092 octets, the interleaver memory in one transceiver would have to be 14546 octets (i.e., bytes). The deinterleaver memory for the corresponding deinterleaver in the transceiver at the other end of the communication channel would also be 14546. The memory requirements are the same for the interleaver and corresponding deinterleaver because the deinterleaver will deinterleave the interleaved byte stream that was interleaved by the interleaver.

102. Yet, Dr. Jacobsen omits the fact that the equations of LB-031 are to be used to separately characterize the delay and memory requirements for a single latency path/direction. *See id.* These equations do not characterize the combined memory requirements for a single transceiver that requires memory for an interleaver for a first latency path/direction and a deinterleaver for a second latency path/direction. The equations are not concerned with the combined memory limit of any single transceiver or with sharing or allocating that combined limit between and interleaver and a deinterleaver. Rather, LB-031 is perfectly consistent with the practice at the time of using a dedicated, fixed-size interleaver memory and a separate, dedicated, fixed-size deinterleaver memory within a transceiver. As explained in Section VI.A.1, *supra*, LB-

031 falls within the category of dedicated interleaver and deinterleaver memory implementations. *See also* § IV.A, *supra*.

103. I note that Dr. Jacobsen understands that DSL transceivers generally transmit/interleave in one direction while they are receiving/deinterleaving in the other direction.<sup>2</sup> *See*, *e.g.*, Jacobsen Report at ¶ 207 ("VDSL transceivers transmit and receive data at the same time (i.e., VTU-O transmits data downstream and receives data upstream at the same time, and the VTU-R transmits data upstream and receives data downstream at the same time."). She ignores or attempts to confuse this fundamental detail, however, when comparing the preamble (and notably all the other elements of the claims, except the last) to the LB-031 reference.

104. The claim construction of the term "shared memory" further supports the fact that LB-031 does not disclose shared memory, or allocating shared and consequently does not disclose a system for allocating shared memory. Specifically, the Court construed "shared memory" to mean "common memory used by at least two functions, where a portion of the memory can be used by either one of the functions." Claim Construction Order for Family 3 Patents (December 28, 2017) ("CC Order") at p. 2.

105. The second portion of the construction (i.e., that "a portion of [the shared] memory can be used by either function") means that the shared memory is a memory of a single transceiver. For example, the two functions in the context of the claim (and in

<sup>&</sup>lt;sup>2</sup> This is not the case, however, when the transceiver provides only half-duplex communications, i.e., the transceiver transmits but does not receive at some times and receives but does not transmit at other times.

the context of the asserted claims of the Family 3 patents generally) are interleaving and deinterleaving. The concept of use of a portion of memory by either one function or the other function has been described in Section VI.A.5.b, *infra. See also* § IV.A, *supra.* As discussed in connection with the '473 patent, *infra*, the interleaving function and corresponding deinterleaving function of the other transceiver specifically discussed in LB-031 use entirely different memories in different transceivers. No portion of memory within a single transceiver is disclosed by LB-031 to be used by an interleaver at one time or a deinterleaver at another time. *See* § VI.A.5.b.

106. Second, Dr. Jacobsen inappropriately extends the actual disclosure and teachings of the LB-031 reference by making an inherency argument that contradicts her other arguments. See Jacobsen Report at ¶ 181. Dr. Jacobsen asserts that "one of ordinary skill in the art would have understood from the disclosures of LB-031 that the allocated memory can be a shared memory." See id. This is incorrect. First, Dr. Jacobsen has not identified any disclosure in LB-031 that requires that a shared memory is used or that any portion of memory within a single transceiver can be used by the interleaver or the deinterleaver. Rather, again, LB-031 is perfectly consistent with the practice of its time, which was to use a dedicated, fixed-size interleaver memory and a separate, dedicated, fixed-size deinterleaver memory in a transceiver. See § VI.A.5.a, infra; see also §§ IV.A, and IV.B, supra. Thus, no portion of a memory can be used by either an interleaver or a deinterleaver (i.e., no portion of the dedicated interleaver memory will ever be used by the deinterleaver and no portion of the dedicated deinterleaver memory will ever be used by the interleaver.).

- 107. Further, Dr. Jacobsen recognizes that LB-031 explains that "[t]he size of the interleaver memory will be a major source of complexity in VDSL2." *See* Jacobsen Report at ¶ 181 (citing LB-031 at 3.). This statement does not state or suggest that size or complexity can be reduced by sharing memory. Rather, this statement would discourage a POSITA from attempting to add further complexity to interleaver memory in VDSL2, such as by proposing a memory sharing scheme. *See also, e.g.*, LB-031 at 3 (2WIRE00030959) ("Therefore, it seems prudent to define interleaver complexity requirement in a way that will allow those who want to deploy VDSL2 at lower speeds to do so that at a reduced complexity with respect to higher speed implementations.").

- 108. Therefore, I do not agree that a POSITA would understand "from the disclosures of LB-031 that the allocated memory can be a shared memory," as Dr. Jacobsen incorrectly asserts, because a shared memory implementation would increase and not decrease the complexity of the implementation proposed by the LB-031 reference. *See* Jacobsen Report at ¶ 181.

- 109. I also disagree with Dr. Jacobsen's assertion that "it was well known by the priority date of the Family 3 patents that an interleaver and deinterleaver memory could share a memory." *See* Jacobsen Report at ¶ 181. I address this in Sections IV.A, IV.B, and IV.C, *supra*. Additionally, and *arguendo*, even if any of the string-cited references in paragraph 182 of the Jacobsen Report disclose a system for sharing memory as construed by the Court (which they do not), Dr. Jacobsen fails to explain why a POSITA would look to any of these references to increase complexity of the implementation of the LB-031 disclosure. Rather, as I have explained immediately

above, a POSITA would be discouraged from adding complexity to the memory requirement specifying scheme of LB-031. Consequently, there would be no motivation to combine any of the references cited in Paragraphs 182 of the Jacobsen Report with LB-031. And Dr. Jacobsen supplies none.

- 110. Because the LB-031 reference does not disclose, teach, or suggest a system that allocates sheared memory, it does not render claim 1 of the '048 patent anticipated or obvious. Also, because a person of ordinary skill in the art would not have understood from the teaching of the LB-031 reference to require a use of a shared memory, the LB-031 reference does not render claim 1 of the '048 patent anticipated or obvious. Finally, because a person of the ordinary sill in the art would not be motivated to combine the teaching of the LB-031 reference with the teaching of any other references cited by Dr. Jacobsen, and in fact, would be discouraged to do so, the LB-031 reference in combination with any of those references or in combination with the knowledge of one of ordinary skill in the art at the time of the invention of the Family 3 patents, does not render claim 1 of the '048 patent obvious.

- b. LB-031 does not disclose determining an amount of memory required by the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes within the shared memory.

- 111. LB-031 does not disclose this claim element.

- 112. Dr. Jacobsen ignores the requirement of this claim element that calls for a "shared memory" and instead irrelevantly quotes the portions of LB-031 describing the memory requirements for an interleaver in one transceiver and a corresponding memory requirement for a deinterleaver in another transceiver (and not an

implementation in a single transceiver with a shared memory). See Jacobsen Report at ¶ 192.

- 113. At least because LB-031 is not directed to allocating shared memory described in § VI.A.1 and § VI.A.2.a, *supra*, the LB-031 reference does not disclose, teach, or suggest this claim element. *See* § VI.A.5.a, *infra*; *see also* §§ IV.A, and IV.B, *supra*.

- 114. Because LB-031 does not disclose, teach, or suggest determining an amount of memory required by the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes within the shared memory, it does not render claim 1 of the '048 Patent obvious.

- c. LB-031 does not disclose allocating a first number of bytes of the shared memory to the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes for transmission at a first data rate.

- 115. LB-031 does not disclose, teach, or suggest this claim element.

- 116. As with the previous claim element, Dr. Jacobsen yet again ignores the requirement of this claim element that calls for a "shared memory." *See* Jacobsen Report at ¶¶ 194-195. The claim overall, and also this element in particular, calls for allocating bytes of a shared memory. LB-031 lacks disclosure of a shared memory as construed by the Court. *See* §§ VI.A.1, VI.A.2.a. *See also* § VI.A.5.a, *infra*; *see also* §§ IV.A, and IV.B, *supra*.

- 117. Dr. Jacobsen relies on a passage from LB-031 describing an exchange between a VTU-O and VTU-R of capabilities (i.e., a VTU-R and VTU-O will select "the