# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD COMMSCOPE, INC. Petitioner v. TQ DELTA, LLC Patent Owner Case No. IPR2023-00066 U.S. Patent No. 7,836,381

DECLARATION OF RICHARD WESEL, Ph.D

# **TABLE OF CONTENTS**

| II.   | Qualifications                                                                                                                                                                                                                                | 2                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| III.  | Scope of the Engagement                                                                                                                                                                                                                       | 4                    |

| IV.   | Legal Standards Relied Upon                                                                                                                                                                                                                   | 6                    |

| V.    | Technical Background  a. Reed-Solomon Coding  b. Interleaving  c. Shared Memory  d. Configuration Messages                                                                                                                                    | 11<br>12<br>16       |

| VI.   | The '381 Patent                                                                                                                                                                                                                               | 19                   |

| VII.  | Prosecution History                                                                                                                                                                                                                           | 21                   |

| VIII. | Prior Decisions by the District Court                                                                                                                                                                                                         | 22                   |

| IX.   | Litigation Related to the '381 Patent                                                                                                                                                                                                         | 23                   |

| X.    | Claim Construction a. "transceiver" b. "shared memory" c. "amount of memory" d. "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver/deinterleaver]" | 24<br>24<br>25       |

| XI.   | Prior Art References  e. Mazzoni Overview  f. Fadavi-Ardekani Overview  g. VDSL1 Overview  h. Motivation to Combine the Prior Art  i. Motivation to Combine Mazzoni and VDSL1  ii. Motivation to Combine VDSL1 and Fadavi-Ardekani            | 25<br>28<br>30<br>33 |

| XII.  | Ground 1: The combination of Mazzoni and VDSL1 renders the challenged claims obvious                                                                                                                                                          | 42                   |

|       | bytes of memory that are available to be allocated to an                       |     |

|-------|--------------------------------------------------------------------------------|-----|

|       | interleaver;                                                                   | 53  |

| iii.  | Claim 1: [1.B] determining, at the transceiver, an amount of                   |     |

|       | memory required by the interleaver to interleave a first                       |     |

|       | plurality of Reed Solomon (RS) coded data bytes within a                       |     |

|       | shared memory;                                                                 | 63  |

| iv.   | Claim 1: [1.C] allocating, in the transceiver, a first number of               |     |

|       | bytes of the shared memory to the interleaver to interleave the                |     |

|       | first plurality of Reed Solomon (RS) coded data bytes for                      |     |

|       | transmission at a first data rate, wherein the allocated memory                |     |

|       | for the interleaver does not exceed the maximum number of                      |     |

|       | bytes specified in the message;                                                | 81  |

| v.    | Claim 1: [1.D] allocating, in the transceiver, a second number                 |     |

| . •   | of bytes of the shared memory to a deinterleaver to                            |     |

|       | deinterleave a second plurality of RS coded data bytes received                |     |

|       | at a second data rate; and                                                     | 90  |

| vi.   | Claim 1: [1.E] interleaving the first plurality of RS coded data               |     |

|       | bytes within the shared memory allocated to the interleaver                    |     |

|       | and deinterleaving the second plurality of RS coded data bytes                 |     |

|       | within the shared memory allocated to the deinterleaver,                       |     |

|       | wherein the shared memory allocated to the interleaver is used                 |     |

|       | at the same time as the shared memory allocated to the                         |     |

|       | deinterleaver.                                                                 | 91  |

| vii.  | Claim 2: The media of claim 1, wherein the determining is                      | > 1 |

| , 224 | based on an impulse noise protection requirement.                              | 94  |

| viii. | Claim 3: The media of claim 1, wherein the determining is                      |     |

|       | based on a latency requirement.                                                | 96  |

| ix.   | Claim 4: The media of claim 1, wherein the determining is                      |     |

|       | based on a bit error requirement.                                              | 98  |

| х.    | Claim 5 [5.pre]: A non-transitory computer-readable                            |     |

|       | information storage media having stored thereon instructions,                  |     |

|       | that if executed by a processor, cause to be performed a                       |     |

|       | method for allocating shared memory in a transceiver                           |     |

|       | comprising:                                                                    | 100 |

| xi.   | Claim 5: [5.A] transmitting or receiving, by the transceiver, a                |     |

|       | message during initialization specifying a maximum number of                   |     |

|       | bytes of memory that are available to be allocated to a                        |     |

|       | deinterleaver;                                                                 | 101 |

| xii.  | Claim 5: [5.B] determining, at the transceiver, an amount of                   | 101 |

| 2224  | memory required by the deinterleaver to deinterleave a first                   |     |

|       | plurality of Reed Solomon (RS) coded data bytes within a                       |     |

|       | shared memory;                                                                 | 102 |

| xiii. | Claim 5: [5.C] allocating, in the transceiver, a first number of               | 102 |

| AIII. | bytes of the shared memory to the deinterleaver to deinterleave                |     |

|       | a first plurality of Reed Solomon (RS) coded data bytes for                    |     |

|       | reception at a first data rate, wherein the allocated memory for               |     |

|       | I COCOMINIA AL A III DI MALA I ALCA MINICI CIII CIIC AIIUCALCA IIICIIIUI V IUI |     |

|       |      |         | the deinterleaver does not exceed the maximum number of          |     |

|-------|------|---------|------------------------------------------------------------------|-----|

|       |      |         | bytes specified in the message;                                  | 102 |

|       |      | xiv.    | Claim 5: [5.D] allocating, in the transceiver, a second number   |     |

|       |      |         | of bytes of the shared memory to an interleaver to interleave a  |     |

|       |      |         | second plurality of RS coded data bytes transmitted at a         |     |

|       |      |         | second data rate; and                                            | 103 |

|       |      | XV.     | Claim 5: [5.E] deinterleaving the first plurality of RS coded    |     |

|       |      |         | data bytes within the shared memory allocated to the             |     |

|       |      |         | deinterleaver and interleaving the second plurality of RS coded  |     |

|       |      |         | data bytes within the [shared] memory allocated to the           |     |

|       |      |         | interleaver, whereinthe shared memory allocated to the           |     |

|       |      |         | deinterleaver is used at the same time as the shared memory      |     |

|       |      |         | allocated to the interleaver.                                    | 103 |

|       |      | xvi.    | Claim 6: The media of claim 5, wherein the determining is        | 103 |

|       |      | A V 1.  | based on an impulse noise protection requirement.                | 103 |

|       |      | xvii.   | Claim 7: The media of claim 5, wherein the determining is        | 103 |

|       |      | XVII.   | based on a latency requirement.                                  | 102 |

|       |      |         | ¥ 4                                                              | 103 |

|       |      | xviii.  | Claim 8: The media of claim 5, wherein the determining is        | 104 |

|       |      |         | based on a bit error rate requirement.                           | 104 |

| XIII. | Cron | nd 2. T | he combination of VDSL1 and Fadavi-Ardekani renders the          |     |

| лш.   |      |         |                                                                  | 104 |

|       | _    | 0       | laims obvious.                                                   |     |

|       | b.   | v       | vsis                                                             | 104 |

|       |      | i.      | Claim 1: [1.pre] A non-transitory computer-readable              |     |

|       |      |         | information storage media having stored thereon instructions,    |     |

|       |      |         | that if executed by a processor, cause to be performed a         |     |

|       |      |         | method for allocating shared memory in a transceiver             | 101 |

|       |      |         | comprising:                                                      | 104 |

|       |      | ii.     | Claim 1: [1.A] transmitting or receiving, by the transceiver, a  |     |

|       |      |         | message during initialization specifying a maximum number of     |     |

|       |      |         | bytes of memory that are available to be allocated to an         |     |

|       |      |         | interleaver;                                                     | 113 |

|       |      | iii.    | Claim 1: [1.B] determining, at the transceiver, an amount of     |     |

|       |      |         | memory required by the interleaver to interleave a first         |     |

|       |      |         | plurality of Reed Solomon (RS) coded data bytes within a         |     |

|       |      |         | shared memory;                                                   | 121 |

|       |      | iv.     | Claim 1: [1.C] allocating, in the transceiver, a first number of |     |

|       |      |         | bytes of the shared memory to the interleaver to interleave the  |     |

|       |      |         | first plurality of Reed Solomon (RS) coded data bytes for        |     |

|       |      |         | transmission at a first data rate, wherein the allocated memory  |     |

|       |      |         | for the interleaver does not exceed the maximum number of        |     |

|       |      |         | bytes specified in the message;                                  | 124 |

|       |      | v.      | Claim 1: [1.D] allocating, in the transceiver, a second number   | -   |

|       |      |         | of bytes of the shared memory to a deinterleaver to              |     |

|       |      |         | deinterleave a second plurality of RS coded data bytes received  |     |

|       |      |         | at a second data rate; and                                       | 129 |

|       |      |         | mi m securit unit i mice milli                                   | 14) |

| vi.    | Claim 1: [1.E] interleaving the first plurality of RS coded data |      |

|--------|------------------------------------------------------------------|------|

|        | bytes within the shared memory allocated to the interleaver      |      |

|        | and deinterleaving the second plurality of RS coded data bytes   |      |

|        | within the shared memory allocated to the deinterleaver,         |      |

|        | wherein the shared memory allocated to the interleaver is used   |      |

|        | at the same time as the shared memory allocated to the           |      |

|        | deinterleaver.                                                   | 130  |

| vii.   | Claim 2: he media of claim 1, wherein the determining is based   |      |

|        | on an impulse noise protection requirement.                      | 132  |

| viii.  | Claim 3: The media of claim 1, wherein the determining is        |      |

|        | based on a latency requirement.                                  | 135  |

| ix.    | Claim 4: The media of claim 1, wherein the determining is        |      |

|        | based on a bit error rate requirement                            | 137  |

| х.     | Claim 5 [5.pre]: A non-transitory computer-readable              |      |

|        | information storage media having stored thereon instructions,    |      |

|        | that if executed by a processor, cause to be performed a         |      |

|        | method for allocating shared memory in a transceiver             |      |

|        | comprising                                                       | 138  |

| xi.    | Claim 5: [5.A] transmitting or receiving, by the transceiver, a  |      |

|        | message during initialization specifying a maximum number of     |      |

|        | bytes of memory that are available to be allocated to a          |      |

|        | deinterleaver;                                                   | 138  |

| xii.   | Claim 5: [5.B] determining, at the transceiver, an amount of     |      |

|        | memory required by the deinterleaver to deinterleave a first     |      |

|        | plurality of Reed Solomon (RS) coded data bytes within a         |      |

|        | shared memory;                                                   | 139  |

| xiii.  | Claim 5: [5.C] allocating, in the transceiver, a first number of |      |

|        | bytes of the shared memory to the deinterleaver to deinterleave  |      |

|        | a first plurality of Reed Solomon (RS) coded data bytes for      |      |

|        | reception at a first data rate, wherein the allocated memory for |      |

|        | the deinterleaver does not exceed the maximum number of          |      |

|        | bytes specified in the message;                                  | 139  |

| xiv.   | Claim 5: [5.D] allocating, in the transceiver, a second number   |      |

|        | of bytes of the shared memory to an interleaver to interleave a  |      |

|        | second plurality of RS coded data bytes transmitted at a         |      |

|        | second data rate; and                                            | 140  |

| XV.    | Claim 5: [5.E] deinterleaving the first plurality of RS coded    |      |

| 11 11  | data bytes within the shared memory allocated to the             |      |

|        | deinterleaver and interleaving the second plurality of RS coded  |      |

|        | data bytes within the shred memory allocated to the              |      |

|        | interleaver, wherein the shared memory allocated to the          |      |

|        | deinterleaver is used at the same time as the shared memory      |      |

|        | allocated to the interleaver.                                    | 140  |

| xvi.   | Claim 6: The media of claim 5, wherein the determining is        | 1 10 |

| A 7 10 | based on an impulse noise protection requirement.                | 140  |

|        | ~ ~~~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~                          | 1 10 |

| xvii. Claim 7: The media of claim 5, wherein the deter |               | Claim 7: The media of claim 5, wherein the determining is |     |

|--------------------------------------------------------|---------------|-----------------------------------------------------------|-----|

|                                                        |               | based on a latency requirement.                           | 140 |

|                                                        | xviii.        | Claim 8: The media of claim 5, wherein the determining is |     |

|                                                        |               | based on a bit error rate requirement.                    | 141 |

|                                                        |               |                                                           |     |

| XIV.                                                   | Revision or S | Supplementation                                           | 141 |

| Exhibit  | Short Name                          | Description                                                                                                                                         |

|----------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1001 | '381 Patent                         | U.S. Patent No. 7,836,381                                                                                                                           |

| Ex. 1002 | '381 File History                   | File History of U.S. Patent No. 7,836,381                                                                                                           |

| Ex. 1003 | Wesel Declaration                   | Declaration of Dr. Richard Wesel, under 37 C.F.R. § 1.68                                                                                            |

| Ex. 1004 | Wesel CV                            | Curriculum Vitae of Dr. Richard Wesel                                                                                                               |

| Ex. 1005 | Mazzoni                             | U.S. Patent No. 7,269,208                                                                                                                           |

| Ex. 1006 | Fadavi-Ardekani                     | U.S. Patent No. 6,707,822                                                                                                                           |

| Ex. 1007 | VDSL1                               | ETSI TS 101 270-2 V1.2.1 Technical Specification                                                                                                    |

| Ex. 1008 | Forney                              | G. David Forney, <i>Burst-Correcting Codes for the Classic Bursty Channel</i> , Vol. Com-19, No. 5, IEEE Transactions on Communications, 772 (1971) |

| Ex. 1009 | Zogakis                             | T. Nicholas Zogakis, <i>A Coded and Shaped Discrete Multitone System</i> , Vol. 43, No. 12, IEEE Transactions on Communications, 2941 (1995)        |

| Ex. 1010 | Kernighan                           | B.W. Kernighan, D. M. Ritchie, <i>The C Programming Language</i> , 1998                                                                             |

| Ex. 1011 | AT&T DSP (1981)                     | J. R. Boddie, <i>Overview: The Device, Support Facilities, and Applications</i> , Vol. 60, The Bell System Technical Journal, 1431 (1981)           |

| Ex. 1012 | AT&T DSP 32<br>(1986)               | J. R. Boddie, <i>The DSP32 Digital Signal Processor</i> and its Application Development Tools, AT&T Technical Journal, 89 (1986)                    |

| Ex. 1013 | Texas Instruments<br>TMS 320 (1994) | Mansoor A. Chishtie, <i>Telecommunications</i> Applications With the TMS320C5x DSPs, Digital Signal Processing Products (1994)                      |

| Ex. 1014 | Maxwell                             | U.S. Patent No. 4,924,456                                                                                                                           |

| Ex. 1015 | V.32 bis                            | ITU Recommendation V.32 bis (1991)                                                                                                                  |

| Ex. 1016 | V.32                                | ITU Recommendation V.32 (1993)                                                                                                                      |

| Ex. 1017 | LB-031                              | ITU Contribution LB-031 (June 2004)                                                                                                                 |

| Exhibit  | Short Name                                | Description                                                                                                                      |

|----------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1018 | Family 3 Claim<br>Construction<br>Opinion | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 445 (D. Del. Dec. 18, 2017) (Claim Construction Opinion)             |

| Ex. 1019 | Family 3 Claim<br>Construction Order      | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 454 (D. Del. Dec. 28, 2017) (Claim Construction Order)               |

| Ex. 1020 | Family 1 Claim<br>Construction<br>Opinion | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No.477 (D. Del. Jan 30, 2018) (Claim Construction Opinion)               |

| Ex. 1021 | Family 4 Claim<br>Construction Order      | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 484 (D. Del. Feb. 6, 2018) (Claim Construction Order)                |

| Ex. 1022 | Family 3 MSJ<br>Opinion                   | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 13-cv-01835-RGA, ECF No. 1106 (D. Del. Apr. 25, 2019) (MSJ Opinion)                    |

| Ex. 1023 | Family 3 Jury Form                        | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 13-cv-01835-RGA, ECF No. 1187 (D. Del. May 23, 2019) (Jury Form)                       |

| Ex. 1024 | '890 Patent                               | U.S. Patent No. 7,831,890                                                                                                        |

| Ex. 1025 | '890 File History                         | File History of U.S. Patent No. 7,831,890                                                                                        |

| Ex. 1026 | Veithen                                   | Veithen et al., A 70 Mbps Variable-Rate DMT-based Modem for VDSL, IEEE International Solid-State Circuits Conference, 248 (1999) |

| Ex. 1027 | Kiss                                      | Kiss et al, A Customizable DSP for DMT-Based<br>ADSL Modem, IEEE, 349 (1998)                                                     |

| Ex. 1028 | Third and Final<br>Scheduling Order       | TQ Delta, LLC v. 2Wire, Inc., No. 1:13-cv-01835, Dkt. No. 117 (D. Del. April 10, 2017) (Third and Final Scheduling Order)        |

| Ex. 1029 | 2Wire Docket                              | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 1:13-cv-01835 (D. Del.) (Docket as of February 25, 2022)                               |

| Ex. 1030 | Sept. 15, 2021<br>Letter                  | TQ Delta, LLC v. 2Wire, Inc., No. 1:13-cv-01835, Dkt. No. 1591 (D. Del. Sept. 15, 2021) (Letter)                                 |

| Exhibit  | Short Name                                                   | Description                                                                              |

|----------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Ex. 1031 | RESERVED                                                     | RESERVED                                                                                 |

| Ex. 1032 | Feb. 24, 2022<br>Letter Regarding<br>ADTRAN Case<br>Schedule | TQ Delta, LLC v. ADTRAN, Inc., No. 1:14-cv-00954, Dkt. No. 1373 (Feb. 24, 2022) (Letter) |

| Ex. 1033 | Hall-Ellis<br>Declaration                                    | Declaration of Sylvia Hall-Ellis                                                         |

# **DECLARATION OF RICHARD WESEL**

I, Richard Wesel, do hereby declare and say as follows:

### I. Introduction

- 1. My name is Dr. Richard Wesel, and I have been retained as a technical expert by counsel for Petitioner CommScope, Inc. ("CommScope") to address certain issues regarding U.S. Patent No. 7,836,381 ("the '381 Patent").

- 2. I have personal knowledge of the facts contained in this Declaration, am of legal age, and am otherwise competent to testify.

- 3. Unless otherwise stated, the matters contained in this Declaration are of my own personal knowledge and, if called as a witness, I could and would testify completely and truthfully with regard to the matters set forth herein.

- 4. My opinions are based on my years of education, research, and experience, as well as my study of the relevant materials. A list of materials I considered is included at the beginning of this Declaration.

- 5. I reserve all available rights to supplement this Declaration if further information becomes available, or if I am asked to consider additional information.

This Declaration represents only those opinions I have formed to date.

- 6. Further, I reserve all available rights to consider and comment on any additional expert statements or testimony of TQ Delta's expert(s) in this matter.

7. I am being compensated at my usual consulting rate of \$600 per hour for my time spent working on issues in this matter. My compensation does not depend on the outcome of this matter or the opinions I express.

### II. Qualifications

- 8. A true and correct copy of my curriculum vitae is attached as Ex. 1004 to this Declaration.

- 9. I have over 30 years of experience in communications and signal processing. I am a professor in the Electrical and Computer Engineering Department of UCLA as well as the Associate Dean for Academic and Student Affairs of the Henry Samueli School of Engineering and Applied Science. After receiving bachelors and master's degrees in Electrical Engineering from MIT in 1989, I worked at AT&T Bell Laboratories from 1989 to 1991 as a Member of Technical Staff performing research and development in telecommunications. I attended Stanford University from 1991 to 1996, receiving my Ph.D. in Electrical Engineering in 1996. Upon receiving my Ph.D. I joined the faculty of the UCLA Electrical Engineering Department, where I have been teaching and doing research on communications and signal processing for the last 24 years.

- 10. I have extensive experience researching and teaching communications techniques including multi-carrier modulation, interleaving, and error control coding in general as well as Reed-Solomon coding in particular. My publications

and patents are listed in my CV. I have published over 200 conference and journal publications, and I am the inventor on nine patents. I have received the National Science Foundation (NSF) CAREER Award and an Okawa Foundation award for research in information theory and telecommunications. I am a Fellow of the Institute of Electrical and Electronics Engineers (IEEE). I previously served as an Associate Editor for Coding and Coded Modulation for the IEEE Transactions on Communications. I currently serve as an Associate Editor for Coding and Decoding for the IEEE Transactions on Information Theory.

11. I authored an Asilomar conference paper in 1995 entitled "Fundamentals of Coding for Broadcast OFDM" that discusses techniques for designing coding and modulation for multicarrier transmission with interleaving. My 1996 Ph.D. dissertation included the design of trellis codes for multicarrier transmission with interleaving. In a 1999 Communications Letter, I presented related results on trellis codes for multicarrier transmission with interleaving. In a 2000 IEEE Transactions on Communications paper, I compared the performance of these new codes to Reed-Solomon codes used on multicarrier transmission with interleaving. I also authored several conference papers in the late 1990's related to coding for multicarrier transmission with interleaving including "Joint Interleaver and Trellis Code Design," "Periodic Symbol Puncturing of Trellis Codes," and "Trellis Codes for Compound Periodic Gaussian Channels."

- 12. I authored the chapter entitled "Error Control" in the book Wireless Multimedia Communications: Networking Video, Voice, and Data in 1997, which discussed the concepts of Reed-Solomon codes and interleaving. This book also discusses multicarrier modulation in Section 3.4 and Section 5.2.

- 13. I am an inventor on U.S. Patent No. 6,125,150 entitled "Transmission System using Code Designed for Transmission with Periodic Interleaving," which discloses, among other things, error control techniques for multicarrier transmission with interleaving. I am also an inventor on U.S. Patent No. 6,158,041 filed in October 1998 entitled "System and method for I/Q Trellis Coded Modulation" which also describes, among other things, error correction coding techniques for multicarrier transmissions using interleaving.

# III. Scope of the Engagement

- 14. I have been retained by Goodwin Procter LLP on CommScope's behalf to provide various analyses and opinions. Among other tasks, I have been asked to address the technology claimed in the '381 Patent and to evaluate whether certain claims of the '381 Patent would have been obvious to a person of ordinary skill in the art.

- 15. All of the opinions I express in this Declaration have been made from the standpoint of a person of ordinary skill in the relevant art at the time of the

invention of the '381 Patent, which I am informed is, for purposes of this matter, the earliest claimed priority date of October 12, 2004.

- 16. I have been asked to identify the level of skill in the art pertinent to the '381 Patent. It is my opinion that a person of ordinary skill in the art pertinent to the '381 Patent would have had at least a Bachelor's degree in electrical engineering, or a related field, and at least 6–7 years of experience in telecommunications or a related field; a master's degree in electrical or computer engineering, or the equivalent, and at least 4–5 years of experience in telecommunications or a related field; or a Ph.D. in electrical or computer engineering, or the equivalent, with at least 1–2 years of experience in telecommunications or a related field. A person with a different degree but with additional relevant experience could still qualify if the additional experience compensates for the different educational background.

- 17. I consider myself a person of ordinary skill in the art as of at least the earliest claimed priority date (October 12, 2004).

- 18. My opinions are based on my experience and knowledge and the information I have reviewed as of the date of this Declaration. In connection with my analysis, I have reviewed the exhibits listed in the above list of exhibits, as well as each of the items referenced herein. My opinions directed to the invalidity of the challenged claims are based, at least in part, on the following prior art publications:

- "Mazzoni" (Ex. 1005), which is US. Patent No. 7,269,208, filed on July 11, 2001 and issued on September 11, 2007;

- "Fadavi-Ardekani" (Ex. 1006), which is U.S. Patent No. 6,707,822, filed on January 7, 2000 and issued on March 16, 2004;

- "VDSL1" (Ex. 1007), which is technical specification ETSI TS 101 270-2 put forth by the European Telecommunications Standards

Institute related to "Very High Speed Digital Subscriber Line (VDSL)." This technical specification was published online by ETSI on July 24, 2003. POSA's at the time of this publication regularly looked to publications from standards organizations, including ETSI, for guidance. Thus, a POSA that was interested in VDSL implementation would have looked to ETSI for publications on technical specifications related to VDSL and would have found, and relied upon, this specification.

# IV. Legal Standards Relied Upon

- 19. For purposes of this Declaration, counsel has instructed me to make the following assumptions:

- 20. Claims are construed from the perspective of a person of ordinary skill in the art ("POSA") as of the effective filing date of the patent application.

Persons of ordinary skill in the art are deemed to read the claims in the context of

the entire patent, including the specification and prosecution history. In other words, the terms are not considered in a vacuum.

- 21. It is my understanding that information that satisfies one of the categories of prior art set forth in 35 U.S.C. § 102 may be used in an invalidity analysis under §§ 102 or 103. If information is not properly classified as prior art under one of the subsections of § 102 of the Patent Act, then it may not form the basis of an anticipation or obviousness determination. It is also my understanding that, for inter partes review, applicable prior art is limited to patents and printed publications.

- 22. I am also informed and understand that a patent claim is invalid under 35 U.S.C. § 103 if the differences between the invention and the prior art are such that the subject matter as a whole would have been obvious at the time of the invention to a person having ordinary skill in the art to which the subject matter pertains. Obviousness, I am informed, is determined based on the scope and content of the prior art, the differences between the prior art and the claim, the level of ordinary skill in the art, and secondary indications of non-obviousness to the extent they exist.

- 23. I understand that whether there are any relevant differences between the prior art and the claimed invention is to be analyzed from the view of a person of ordinary skill in the art at the time of the invention. A person of ordinary skill in

the art is a hypothetical person who is presumed to be aware of all of the relevant art at the time of the invention. The person of ordinary skill is not an automaton, and may be able to fit together the teachings of multiple patents (or other printed publications) by employing ordinary creativity and the common sense that familiar items may have obvious uses in another context or beyond their primary purposes.

- 24. In analyzing the relevance of the differences between the claimed invention and the prior art, I understand that I must consider the impact, if any, of such differences on the obviousness or non-obviousness of the invention as a whole, not merely some portion of it. The person of ordinary skill faced with a problem is able to apply his or her experience and ability to solve the problem and also look to any available prior art to help solve the problem.

- 25. I understand that an invention would have been obvious if a person of ordinary skill in the art, facing the wide range of needs created by developments in the field, would have seen an obvious benefit to the solutions tried by the patent applicant. When there is a design need or market pressure to solve a problem and there are a finite number of identified, predictable solutions, it would have been obvious to a person of ordinary skill to try the known options. If a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that it would improve similar devices in the same way, using the technique would have been obvious.

- 26. I understand that I do not need to look for precise teachings in the prior art directed to the subject matter of the claimed invention. I understand that I may consider the inferences and creative steps that a person of ordinary skill in the art would have employed in reviewing the prior art at the time of the invention. For example, if the claimed invention combines elements that were known in the prior art and if the combination yields results that were predictable to a person of ordinary skill in the art at the time of the invention, then this would make it more likely that the claim was obvious. On the other hand, if the combination of known elements yields unexpected or unpredictable results, or if the prior art teaches away from combining the known elements, then this would make it more likely that the claim that successfully combined those elements was not obvious. I understand that hindsight must not be used when comparing the prior art to the invention during an obviousness analysis.

- 27. I understand that obviousness may be shown by demonstrating that it would have been obvious to modify what is taught in a single piece of prior art to create the patented invention. Obviousness may also be shown by demonstrating that it would have been obvious to combine the teachings of more than one item of prior art. I understand that a claimed invention may be obvious if some teaching, suggestion, or motivation exists that would have led a person of ordinary skill in the art to combine the invalidating references. I also understand that this suggestion

or motivation may come from sources such as explicit statements in the prior art, or from the knowledge of a person having ordinary skill in the art. Alternatively, any need or problem known in the field at the time and addressed by the patent may provide a reason for combining elements of the prior art. I also understand that when there is a design need or market pressure, and there are a finite number of predictable solutions, persons of ordinary skill may be motivated to apply both their skill and common sense in trying to combine the known options in order to solve the problem.

28. I understand that absent evidence of an invention date prior to the filing date of a patent, the invention date of the patent is presumed to be its filing date. A prior invention requires a complete conception of the invention and a reduction to practice of that invention. The patent owner has the burden of establishing by clear and convincing evidence a date of conception earlier than the filing date of the patent.

### V. Technical Background

29. In this technical background, I describe the pertinent technology as it existed as of October 2004, the assumed priority date of the '381 Patent. As I will describe, the ideas of Reed-Solomon coding, interleaving, shared memory, and configuration messages that allow transceivers to exchange capabilities and agree on the parameters that define the communication link (including messages about

maximum available interleaver memory) were all known to a POSA at the time of the alleged invention.

# a. Reed-Solomon Coding

- 30. Reed-Solomon codes are a particular type of error control coding, sometimes called forward error correction (FEC) coding. Error control coding protects a message by using additional bits or symbols called redundancy to produce a codeword that can withstand errors in the channel. The particular Reed-Solomon codes discussed in the patents at issue use 8-bit symbols, which are often called bytes or octets. A Reed Solomon code adds *R* extra symbols, sometimes called the *R* parity bytes or check bytes, to the *K* information symbols. The parameter *R* is referred to as the redundancy.

- 31. Reed-Solomon codes are a particularly powerful form of error correcting code because they achieve the Singleton bound. Such codes have the property that if the code has redundancy R, then the code will be able to correct any error pattern with  $\left\lfloor \frac{R}{2} \right\rfloor$  symbols. For example, a Reed-Solomon code with a redundancy of 16 parity bytes can correct any error pattern with 8 or fewer byte errors. An example of a Reed-Solomon code with 16 parity bytes is the (240,224) Reed-Solomon code with 224 information bytes and 16 parity bytes for a total of 240 bytes in each transmitted codeword.

32. Reed-Solomon coding had long been a tool commonly used by a POSA at the time of the alleged invention. Reed-Solomon codes were discovered by Reed and Solomon in 1960 and are a special case of non-binary BCH codes that were discovered independently by Bose and Ray-Chaudhuri in 1960 and Hocquenghem in 1959.

## b. Interleaving

- 33. Interleaving re-orders (permutes) symbols so that impairments, such as a burst of noise, that impact consecutive transmitted symbols will be spread out over multiple codewords. Each Reed-Solomon codeword has a limit on the number of byte errors that it can correct. With interleaving, a relatively long burst of errors can be spread over multiple Reed-Solomon codewords, allowing all the errors to be corrected.

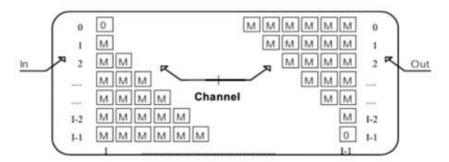

- 34. One type of interleaver is the convolutional interleaver, and one implementation of a convolutional interleaver is the triangular implementation.

Figure B.2: Interleaver/De-interleaver Implementation example

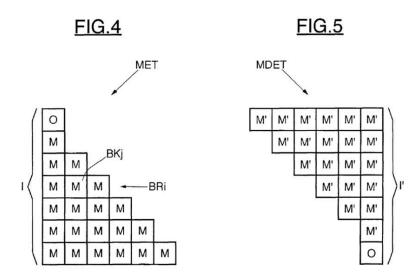

- implementation of an interleaver with parameters I and M. Each box containing the letter M represents M memory elements used to delay bytes written into the interleaver. Figure B.2 shows I rows corresponding to delay lines or shift registers (or virtual shift registers (*See* VDSL1 at 152-153.) implemented, for example, in a random access memory), with indices 0, ..., I-1. At the transmitting transceiver, I Reed-Solomon bytes at a time are written into the interleaver at the left side of each shift register. Then, I bytes are read from the interleaver at the right side of each shift register and are transmitted. Bytes written to the top shift register experience a delay of zero bytes before transmission. Bytes written to the next shift register experience a delay of M bytes. Bytes written to the shift register after that experience a delay of 2M bytes and so on. The bottom shift register is delayed by (I-1)×M bytes before transmission.

- 36. To undo the interleaving, the deinterleaver also uses I shift registers, with indices 0, ..., I-1, which are matched to the shift registers of the interleaver. The top shift register of the deinterleaver will delay its inputs by (I-1)×M bytes, the next shift register delays inputs by (I-2)×M bytes, and so on. In the deinterleaver, the bottom shift register implements a delay of zero bytes. In this way, the overall effect of the combination of the interleaver and deinterleaver is to delay each column by (I-1)×M bytes. Considering that each of the I bytes in a column is

transmitted separately, the overall delay experienced by each byte is exactly  $I\times(I-1)\times M$ . Thus, the deinterleaver returns the interleaved sequence back to its original order, but the combination of interleaving and deinterleaving delays the sequence by  $I\times(I-1)\times M$  bytes.

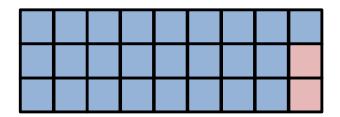

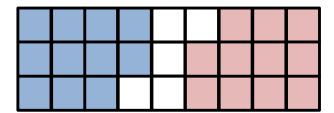

37. To see how a convolutional interleaver spreads a noise burst so that it can be successfully decoded by Reed-Solomon codewords, consider the following simple example. Let's suppose our codewords have length N = 8 and that each codeword can correct two errored bytes. Without interleaving, fourteen consecutive byte errors would certainly cause a decoding error for a sequence of codewords that can each only correct two-byte errors. However, the figure below shows how the convolutional deinterleaver shown in Figure B.2 with I = 7 and M = 1 separates the error burst into isolated pairs of byte errors, where each pair of errors will be corrected by a different codeword.

A sequence of Interleaved Reed-Solomon bytes suffers a noise burst of 14 bytes, shown as red squares.

After deinterleaving, the noisy bytes are distributed over multiple codewords so that they can be corrected.

38. Figure B.2 shows how the parameters I and M precisely determine the amount of memory that needs to be allocated for the triangular implementation of a convolutional interleaver. Each square containing the letter M represents M memory elements used to delay bytes written into the interleaver. Counting up the

boxes, there are I-1 in the first column, I -2 in the second column, and so on until the last column, which has only one box containing M memory elements. Since the sum of  $(I-1)+(I-2)+(I-3)+\cdots+1=\frac{I\times(I-1)}{2}$ , the total amount of memory that we need to allocate for the interleaver is precisely  $M\times\frac{I\times(I-1)}{2}$ . The same argument shows that the associated deinterleaver with parameters I and M also requires an allocation of  $M\times\frac{I\times(I-1)}{2}$  bytes of memory for the specific triangular implementation.

- 39. The concepts of interleaving in general and the interleaving of Reed-Solomon data bytes specifically were well known to a POSA long before the alleged invention. For example, in his 1971 journal paper in the *IEEE*Transactions on Communications, entitled "Burst-Correcting Codes for the Classic Bursty Channel," G. David Forney discussed using convolutional interleaving with error control coding as a way to overcome bursts of noise. Ex. 1008.

- 40. Certainly by 1995, the combined use of Reed-Solomon coding and interleaving was well known. It was used, for example in in the multicarrier transmission system described in the *IEEE Transactions on Communications* article, "A Coded and Shaped Discrete Multitone System" by Zogakis and Aslanis published in December of 1995. Ex. 1009. Figure 9 of that article shows an interleaver processing the Reed-Solomon encoded bytes. Ex. 1009 at 2948.

# c. Shared Memory

41. Computing devices have long utilized common memory used by at least two functions. In fact, to the extent shared memory is construed more narrowly, computing devices have also long utilized common memory used by at least two functions, where a portion of the memory can be used by either one of the functions. The standard libraries defined for the C programming language include functions such as malloc and calloc that obtain blocks of memory dynamically.

See Ex. 1010. Furthermore, standard communications functions including Reed-Solomon coding and interleaving were implemented on digital signal processors (DSPs) such as the AT&T DSP (1981), the AT&T DSP 32 (1986), and the Texas Instruments TMS 320 (1994). See Exs. 1011–1013. These digital signal processing chips all featured common memory used by at least two functions, where a portion of the memory can be used by either one of the functions.

# d. Configuration Messages

42. I understand that a POSA at the time of the invention would have understood that whenever two transceivers have multiple communication configurations from which to choose, the transceivers must have a way to learn each other's capabilities and to agree on the specific configuration that they will use to communicate.

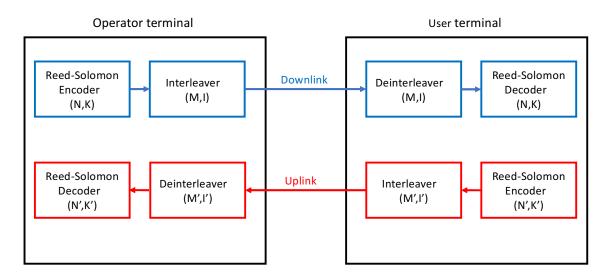

43. Consider the system below with a transceiver at an operator terminal communicating with a transceiver at a user terminal. The communication channel from the operator to the user is called the downlink, and the channel from the user to the operator is called the uplink. In this example system, as in many prior art systems, including ADSL and VDSL1, Reed-Solomon coding and interleaving are used for both the uplink channel and the downlink channel. A POSA would have understood that for the communication link to function properly, the Reed-Solomon decoder and convolutional deinterleaver in the user transceiver for the downlink must use the exact same parameters (N,K,M,I) as the Reed-Solomon encoder and interleaver for the downlink in the operator terminal. Similarly, the operator and user must agree on parameters (N',K',M',I') for the Reed-Solomon coding and interleaving for the uplink.

- 44. A POSA would have known that a common solution is to use configuration messages to exchange capabilities and agree on parameters. Such configuration messages are used in every ADSL standard as well as in the VDSL1 standard. As another example, in U.S. Patent No. 4,924,456 (Ex. 1014), which issued on May 8, 1990, it is explained that a modem uses configuration messages in an "Interactive state . . . to control its operation or to configure its operating characteristics. Ex. 1014 at 11:30–32. Likewise, the V.32 bis (Ex. 1015), and V.32 (Ex. 1016) bis modem standards explicitly handle transceivers with different capabilities since a V.32 bis modem communicating with an older V.32 modem will learn of the limited rate capabilities of the older modem through configuration messages and choose a rate that both modems can implement.

- 45. Such knowledge is in line with the implementation of the VDSL1 standard, which published in July 2003, and discloses communicating the capabilities of the transceiver in a configuration message, including by delivering a message specifying the maximum available interleaver memory. *See, e.g.*, Ex. 1007 at 132. In fact, Contribution LB-31, an ITU-T contribution that followed the VDSL1 standard, acknowledges that one known option for communicating interleaver capabilities was to specify in a message "an amount of memory." *See* Ex. 1017 at 6.

### VI. The '381 Patent

- 46. The '381 Patent relates to sharing a common memory and allocating that common memory between an interleaver and a deinterleaver in digital subscriber line ("DSL") technology. Ex. 1001 at Abstract.

- 47. I understand the filing date of the Provisional Application No. 60/618,269, to which the '381 Patent claims priority, is October 12, 2004.

- 48. The claims of the '381 Patent that are being challenged and that I have been asked to evaluate are claims 1–8. I have reproduced the challenged claims below:

| Claim   | Recitation                                                             |  |  |

|---------|------------------------------------------------------------------------|--|--|

|         | A non-transitory computer-readable information storage media           |  |  |

| [1 D]   | having stored thereon instructions, that if executed by a processor,   |  |  |

| [1.Pre] | cause to be performed a method for allocating shared memory in a       |  |  |

|         | transceiver comprising:                                                |  |  |

|         | transmitting or receiving, by the transceiver, a message during        |  |  |

| [1.A]   | initialization specifying a maximum number of bytes of memory that     |  |  |

|         | are available to be allocated to an interleaver;                       |  |  |

|         | determining, at the transceiver, an amount of memory required by the   |  |  |

| [1.B]   | interleaver to interleave a first plurality of Reed Solomon (RS) coded |  |  |

|         | data bytes within a shared memory;                                     |  |  |

|         | allocating, in the transceiver, a first number of bytes of the shared  |  |  |

|         | memory to the interleaver to interleave the first plurality of Reed    |  |  |

| [1.C]   | Solomon (RS) coded data bytes for transmission at a first data rate,   |  |  |

|         | wherein the allocated memory for the interleaver does not exceed the   |  |  |

|         | maximum number of bytes specified in the message;                      |  |  |

|         | allocating, in the transceiver, a second number of bytes of the shared |  |  |

| [1.D]   | memory to a deinterleaver to deinterleave a second plurality of RS     |  |  |

|         | coded data bytes received at a second data rate; and                   |  |  |

|         | interleaving the first plurality of RS coded data bytes within the     |  |  |

|         | shared memory allocated to the interleaver and deinterleaving the      |  |  |

| [1.E]   | second plurality of RS coded data bytes within the shared memory       |  |  |

| []      | allocated to the deinterleaver, wherein the shared memory allocated to |  |  |

|         | the interleaver is used at the same time as the shared memory          |  |  |

|         | allocated to the deinterleaver.                                        |  |  |

| 2       | The media of claim 1, wherein the determining is based on an impulse   |  |  |

|         | noise protection requirement.                                          |  |  |

| 3       | The media of claim 1, wherein the determining is based on a latency    |  |  |

|         | requirement.                                                           |  |  |

| 4       | The media of claim 1, wherein the determining is based on a bit error  |  |  |

|         | rate requirement.                                                      |  |  |

|         | A non-transitory computer-readable information storage media           |  |  |

| [5.Pre] | having stored thereon instructions, that if executed by a processor,   |  |  |

|         | cause to be performed a method for allocating shared memory in a       |  |  |

|         | transceiver comprising:                                                |  |  |

| [5 A]   | transmitting or receiving, by the transceiver, a message during        |  |  |

| [5.A]   | initialization specifying a maximum number of bytes of memory that     |  |  |

|         | are available to be allocated to a deinterleaver;                      |  |  |

| [5.B]                                                                                                                                                                                                                                                                                                                                  | determining, at the transceiver, an amount of memory required by the deinterleaver to deinterleave a first plurality of Reed Solomon (RS) coded data bytes within a shared memory;                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| allocating, in the transceiver, a first number of bytes of the shared memory to the deinterleaver to deinterleave a first plurality of Reed Solomon (RS) coded data bytes for reception at a first data rate, wherein the allocated memory for the deinterleaver does not exceed the maximum number of bytes specified in the message; |                                                                                                                                                                                                         |  |  |

| [5.D]                                                                                                                                                                                                                                                                                                                                  | allocating, in the transceiver, a second number of bytes of the shared                                                                                                                                  |  |  |

| [5.E]                                                                                                                                                                                                                                                                                                                                  | deinterleaving the first plurality of RS coded data bytes within the shared memory allocated to the deinterleaver and interleaving the second plurality of RS coded data bytes within the shared memory |  |  |

| The media of claim 5, wherein the determining is based on an imp noise protection requirement.                                                                                                                                                                                                                                         |                                                                                                                                                                                                         |  |  |

| 7 The media of claim 5, wherein the determining is based on a latent requirement.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                         |  |  |

| 8                                                                                                                                                                                                                                                                                                                                      | The media of claim 5, wherein the determining is based on a latency requirement                                                                                                                         |  |  |

# VII. Prosecution History

49. U.S. Patent Application No. 12/853,020 was originally filed on August 9, 2010. Ex. 1001. A Notice of Allowance was mailed on October 6, 2010, where the Examiner explained that the independent claims identify "the distinct features of specifying a maximum number of bytes available to be allocated to [a/an] [deinterleaver/interleaver] in a transmitted or received message, determining the amount of memory required by the [deinterleaver/interleaver], and then allocating the bytes of shared memory to the [deinterleaver/interleaver]

wherein the bytes allocated do not exceed the maximum number of available bytes specified in the message." *Id.* at 129-30. The Examiner explained that the "closest prior art, Fadavi-Ardekani" only "discloses sharing a memory between the interleavers and deinterleavers." *Id.*

50. The '381 Patent is a continuation of U.S. Patent Application 11/246,163, granted as U.S. Patent No. 7,831,890 (Ex .1024), which had all of its claims initially rejected under §102 in view of Fadavi-Ardekani. Ex. 1025, 317-33. After canceling all rejected claims, Patent Owner presented new claims, which were allowed for the same reasons the claims of the '381 Patent were allowed. *Id.*, 74-82.

# VIII. Prior Decisions by the District Court

- 51. The '381 Patent was previously considered by the United States

District Court for the District of Delaware in *TQ Delta, LLC v. 2Wire, Inc.*, No. 13-cv-01835-RGA (D. Del.) ("*2Wire*"); *TQ Delta, LLC v. Zhone Technologies, Inc.*,

No. 13-cv-01836-RGA (D. Del.); *TQ Delta, LLC v. ZyXEL Communications, Inc.*,

No. 13-cv-02013-RGA (D. Del.); and *TQ Delta, LLC v. ADTRAN, Inc.*, No. 14-cv-00954-RGA (D. Del.). These four cases were consolidated into lead case *2Wire*.

- 52. The district court issued memoranda and orders construing multiple claim terms of the '381 Patent. Exs. 1018-21. The district court also addressed, on summary judgment, the invalidity of claim 5 of the '381 Patent as obvious in view

of Mazzoni (Ex. 1005) over LB-031 (Ex. 1017), ultimately denying the motion because there was a dispute of material fact regarding the motivation to combine. Ex. 1022. Patent Owner also alleged certain references, including Fadavi-Ardekani (Ex. 1006), failed to disclose a "shared memory." The court granted Patent Owner's motion for no invalidity on this ground as a matter of law, reasoning that the Defendant failed to rebut Plaintiff's argument that Defendant had not proven inherency. *Id.* at 18.

POSA and LB-031 in combination with Mazzoni did not render claim 5 of the '381 Patent invalid as obvious. Ex. 1023. No ground on the basis of Mazzoni in view of VDSL1, or VDSL1 in view of Fadavi-Ardekani was presented to the jury. No dispositive motions related to the '381 Patent have been filed in the *ADTRAN* litigation, and no jury trial has been scheduled.

# IX. Litigation Related to the '381 Patent

54. I understand that the '381 patent is at issue in one litigation, which does not involve Petitioner.

### X. Claim Construction

55. I understand that the in the *2Wire* litigation, terms of the '381 Patent were construed. *See* Exs. 1018–21. The table below provides these constructions.

| Claim Term | Delaware Construction |

|------------|-----------------------|

| "shared memory"               | "common memory used by at least two          |

|-------------------------------|----------------------------------------------|

|                               | functions, where a portion of the memory     |

|                               | can be used by either one of the functions"  |

| "amount of memory"            | Plain meaning, i.e., that is not limited to  |

|                               | number of bytes                              |

| "the shared memory            | "the deinterleaver reads from, writes to, or |

| allocated to the              | holds information for deinterleaving in its  |

| [deinterleaver / interleaver] | respective allocation of the shared memory   |

| is used at the same time as   | at the same time as the interleaver reads    |

| the shared memory allocated   | from, writes to, or holds information for    |

| to the [interleaver/          | interleaving in its respective allocation of |

| deinterleaver]"               | the shared memory"                           |

| "transceiver"                 | "communications device capable of            |

|                               | transmitting and receiving data wherein the  |

|                               | transmitter portion and receiver portion     |

|                               | share at least some common circuitry"        |

### a. "transceiver"

56. All of the challenged claims contain language claiming a "transceiver." The Delaware district court previously construed transceiver to mean "communications device capable of transmitting and receiving data wherein the transmitter portion and receiver portion share at least some common circuitry." In my opinion, this construction too narrowly defines "transceiver," and rather the term should be given its plain and ordinary meaning, which is a "communications device capable of transmitting and receiving data."

# b. "shared memory"

57. All of the challenged claims contain language claiming a "shared memory." The Delaware district court previously construed shared memory to mean "common memory used by at least two functions, where a portion of the

memory can be used by either one of the functions." In my opinion, this construction too narrowly defines "shared memory," and rather the term should be given its plain and ordinary meaning.

# c. "amount of memory"

- 58. All of the challenged claims contain language claiming an "amount of memory." The Delaware district court previously construed amount of memory as the plain meaning, i.e., "that is not limited to number of bytes." In my opinion, this claim language should be construed simply as its plain and ordinary meaning.

- d. "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver/ deinterleaver]"

- 59. All of the challenged claims contain language claiming an "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver/deinterleaver]." The Delaware district court previously construed this term as "the deinterleaver reads from, writes to, or holds information for deinterleaving in its respective allocation of the shared memory at the same time as the interleaver reads from, writes to, or holds information for interleaving in its respective allocation of the shared memory." This construction is consistent with my interpretation of this phrase.

### **XI.** Prior Art References

### e. Mazzoni Overview

- 60. Mazzoni, which issued on September 11, 2007, derives from U.S. Patent Application No. 10/088,387, which was filed on July 11, 2001, and published as US2003/0021338 on January 30, 2003.

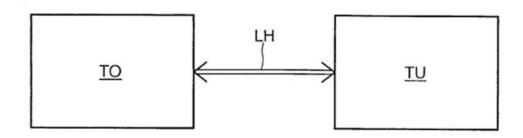

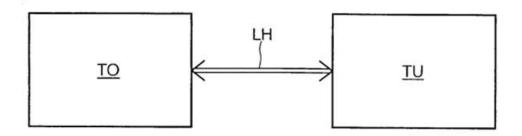

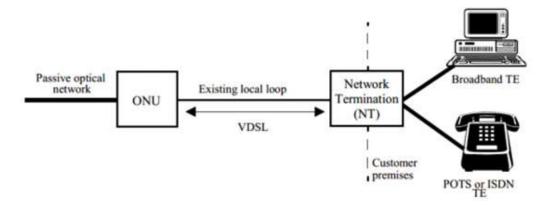

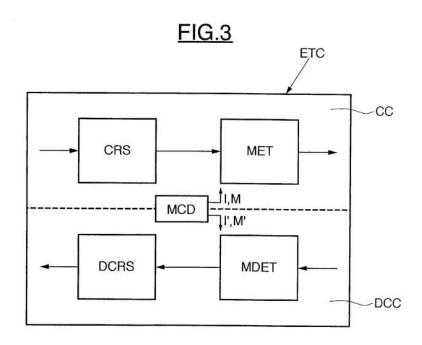

- and receive digital data and that can determine the shared memory capacity used to interleave and deinterleave that data. Ex. 1005 at 1:10–15. Specifically, as shown in Figure 1 below, Mazzoni contemplates two send/receive devices (i.e., transceivers), TU and TO, that communicate by "a very high bit rate communication line LH." *Id.* at 1:60–61.

FIG.1

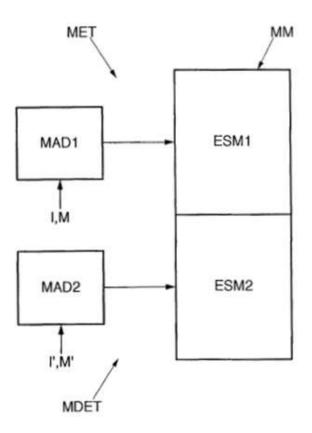

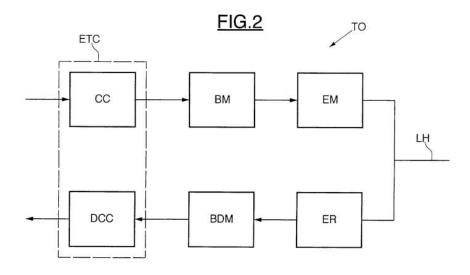

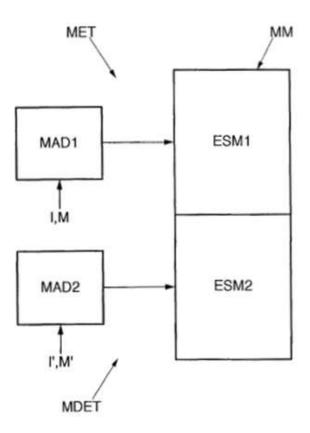

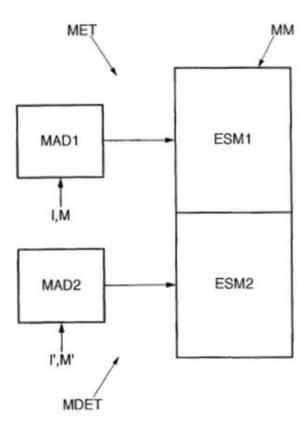

62. Mazzoni further discloses a shared memory "MM" that resides in each transceiver, and that "can be shared between the interleaving means and the deinterleaving means." *Id.* at 1:59–65; 6:6–8. For example, Figure 6 of Mazzoni, shown below, illustrates how the common memory, MM, is allocated to the

interleaver (MET) as ESM1 and deinterleaver (MDET) as ESM2 on just one of the transceivers TO or TU.

FIG.6

MET

MM

ESM1

ESM2

63. Mazzoni explicitly teaches how to determine the required memory allocations for the interleaver and deinterleaver (i.e., the memory size of ESM1 and ESM2) via triangular implementation of convolutional interleaving and deinterleaving. Mazzoni further teaches using Reed-Solomon coding coupled to an interleaver to protect transmitted data. *Id.* at 2:25–30.

- 64. Thus, starting with downstream and upstream bit rates between the TO and TU that are disturbed by an impulsive noise, Mazzoni discloses calculating the number of data bits that are affected by an impulsive noise, the resultant errored bytes, the number of Reed-Solomon codewords needed to correct those errored bytes, and the required interleaver or deinterleaver memory to hold those bytes. *Id.* at 6:11–36.

- 65. Relying on those calculations, Mazzoni also discloses determining the amount of memory required by the interleaver/deinterleaver to interleave/deinterleave the Reed Solomon coded data bytes using parameters I and M. *Id.* at 6:37–38. Mazzoni explains that parameters I and M can be applied to the equation I×(I-1)×M/2 to calculate "the size of the first memory space [ESM1]" for the interleaver, and parameters I' and M' can then be applied to the equation I'×(I'-1)×M'/2 to calculate "the size of the second memory space ESM2" for the deinterleaver. *Id.* at 6:38–44. Mazzoni explains that the common memory required (MM) is the sum of ESM1 and ESM2.

#### f. Fadavi-Ardekani Overview

- 66. Fadavi-Ardekani was filed on January 7, 2000 and issued as a U.S. Patent on March 16, 2004.

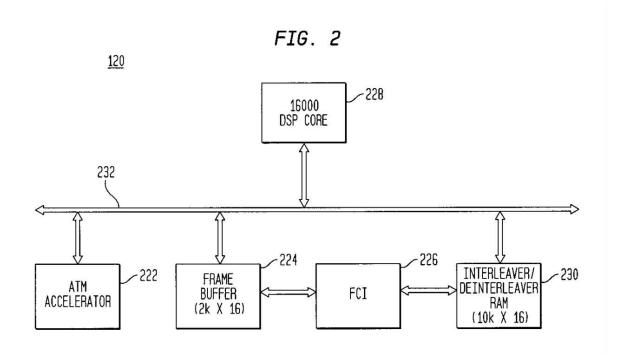

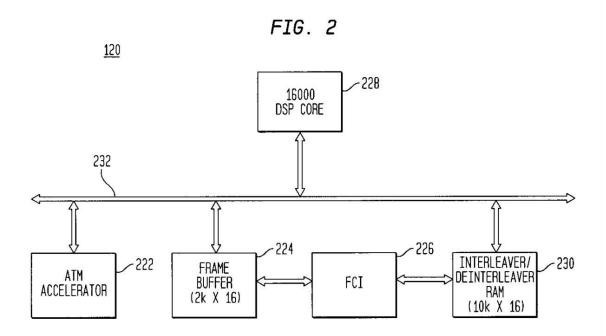

- 67. Fadavi-Ardekani teaches a transceiver that may be implemented in a VDSL communication system with an interleaver and deinterleaver utilizing a

shared memory. Ex. 1006 at 4:19–21. Fadavi-Ardekani discloses a "Framer/Coder/Interleaver" (FCI), which "performs various...including...Reed-Solomon encoding/decoding, and interleaving/de-interleaving." *Id.* at 6:11–16. The memory that supports the FCI is the Interleave/De-Interleave Memory (IDIM), which "allow[s] beneficial performance of various interleave/de-interleave processes." *Id.* at 6:55–65.

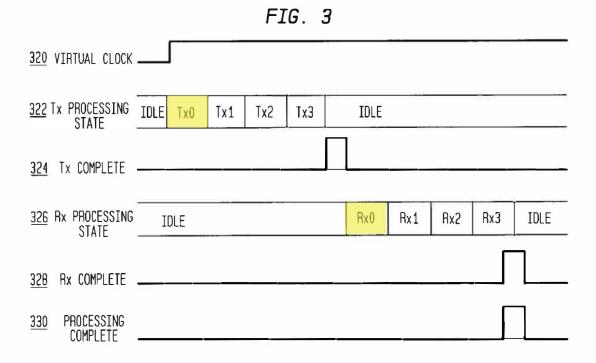

68. Fadavi-Ardekani also teaches that the IDIM may be a shared memory between the interleaver and the deinterleaver. *Id.* at 6:55–58 (The "Interleave/De-Interleave Memory (IDIM)...may be utilized in a ping-pang fashion.)." Fadavi-Ardekani defines "ping-pang" to mean that "areas of the memory buffer are alternately utilized exclusively by one agent (a transceiver component for performing some function) and then by a second agent" and that "[a]s one area of memory is being used by a first agent, another area of memory can be used by a different agent." *Id.* at 5:60–65. For example, Fadavi-Ardekani provides Figure 2, which identifies the interleaver and deinterleaver memory existing on a single RAM.

69. Fadavi-Ardekani teaches two implementations of shared memory: (1) a simple implementation where the memory has enough capacity to implement a session without using some bytes for both interleaving and deinterleaving for that session; and (2) an optimal implementation where the RAM is not large enough to execute a session without using at least some bytes for both interleaving and deinterleaving even for that particular session. *Id.* at 7:25–33. Both the simple and optimal implementations have the property that a portion of the memory can be used by either one of the functions of interleaving or deinterleaving.

## g. VDSL1 Overview

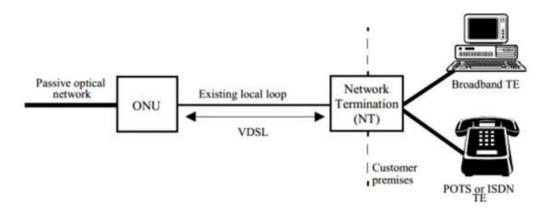

70. VDSL1 was published on July 24, 2003. VDSL1 is an ETSI technical specification produced by "ETSI Technical Committee Transmission and

Multiplexing (TM)" that "specifies requirements for transceivers that provide very high bit-rate digital transmission," or VDSL. Ex. 1007 at 9. VDSL1 teaches incorporating VDSL onto transceivers VTU-O and VTU-R, and then determining the memory allocation for the interleaver and deinterleaver on each transceiver via triangular implementation of convolutional interleaving and deinterleaving. Ex. 1007 at 13, 59–60.

71. Specifically, VDSL1 teaches that "[i]nterleaving shall be used to protect the data against bursts of errors by spreading the errors over a number of Reed-Solomon codewords." *Id.* at 59. To determine the memory required to interleave or deinterleave those bytes, VDSL1 teaches parameters I and M, which can be used to determine the "(De)interleaver memory size" with the equation MxIx(I–1)/2 (see Table 19 below). *Id.* at 60.

Table 19: Characteristics of triangular, convolutional interleaver

| Parameter                  | Value<br>I octets (I must divide N) |  |

|----------------------------|-------------------------------------|--|

| Interleaver block length   |                                     |  |

| Interleaving depth D       | M x I + 1 octets                    |  |

| De)interleaver memory size | M x 1 x (I-1)/2 octats              |  |

| End-to-end delay           | M x I x (I-1) octets                |  |

| Correction capability      | Vq x M x (I+1) octets               |  |

72. VDSL1 then contemplates various "Interleaver Characteristics" in Table 27, including "Interleaver Memory Size," "Erasure Correction (E)," and "End-to-End Delay (DL)." *Id.* at 72.

**Table 27: Interleaver Characteristics**

| Parameter               | Value                                                 | Notes                                 |

|-------------------------|-------------------------------------------------------|---------------------------------------|

| Block Length (I)        | I = N/8, N/4 or N/2, octets                           | N = PS+19, octets                     |

| Depth (D)               | $D = M \times I + 1$ , octets                         | $M = 0 \rightarrow 64$ , programmable |

| Erasure Correction (E)  | $E = [t \times I/N] \times (M \times I + 1)$ , octets | t = 8 (RS error correction ability)   |

| End-to-End Delay (DL)   | $DL = M \times I \times (I - 1)$ , octets             | -                                     |

| Interleaver Memory Size | $MEM = M \times I \times (I - 1) / 2$ , octets        |                                       |

NOTE 1: The interleaver erasure correction E defines the maximum number of corrupted sequential octets could be corrected by RS algorithm when interleaving is applied. Correspondingly, the duration of noise pulses the system is protected from could be calculated as E×8/R, where R is the bit rate of the transmit signal over the line.

NOTE 2: The | symbols indicates the truncation of the value to the lower integer.

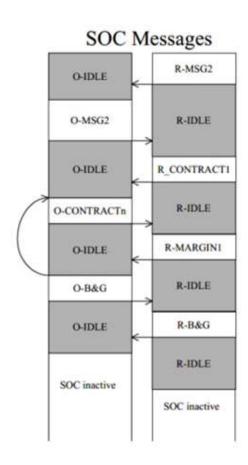

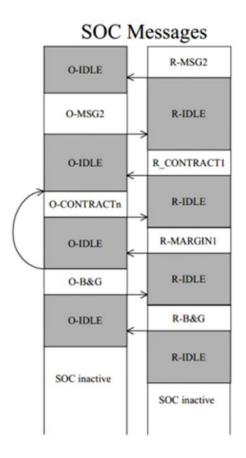

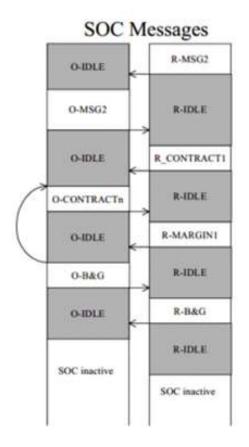

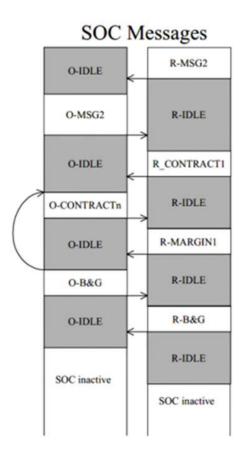

73. VDSL1 also teaches initialization protocols between the VTU-O and VTU-R to set those I and M parameters, including the messages shown below. *Id.* at 127.

74. The first message, R-MSG2, describes the VTU-R's capabilities, including the maximal number of bytes available to be allocated to an interleaver. *Id.* at 132. After the messages R-MSG2, O-MSG2, and R-CONTRACT1, the message O-CONTRACTn, contains a proposed upstream contract and a proposed downstream contract, including contract descriptors for each contract, including the parameters I and M for the upstream interleaver/deinterleaver and a distinct set of parameters I and M for the downstream deinterleaver/interleaver. *Id.* at 129.

#### h. Motivation to Combine the Prior Art

#### i. Motivation to Combine Mazzoni and VDSL1

- 75. Both Mazzoni and VDSL1 are directed to VDSL systems. Indeed, Mazzoni contemplates a transceiver for sending/receiving digital data, "in particular in a VDSL environment," Ex. 1005, and VDSL1 is the technical specification put forth by the European Telecommunications Standards Institute (ETSI) that "specifies requirements for transceivers that provide very high bit-rate digital transmission," i.e., VDSL, Ex. 1007 at 9.

- 76. As explained *supra*, Mazzoni teaches a VDSL transceiver with a shared memory that determines an amount of memory required by an interleaver/deinterleaver to interleave/deinterleave Reed Solomon coded data bytes, that allocates those bytes of the shared memory to the

interleaver/deinterleaver at a particular data rate, and that subsequently interleaves/deinterleaves those bytes.

- 77. Mazzoni does not, however, expressly disclose transmitting or receiving a message during initialization specifying a maximum number of bytes of memory that are available to be allocated to an interleaver or deinterleaver. A POSA would have understood that a transceiver as contemplated in Mazzoni, especially one implemented in a VDSL environment, would perform initialization protocols. Thus, a POSA would have been motivated to look to the VDSL technical specifications available around the same time for those initialization protocols—here, the VDSL1 technical specification.

- 78. VDSL1 disclosed initialization. Ex. 1007 at 111 (disclosing "Initialisation" protocols for the transceiver pair VTU-O and VTU-R, including an "[e]xchange of parameters"); id. at 127–34 (Disclosing a "channel analysis and exchange" state, which discloses the negotiation of interleaver/deinterleaver parameters, including R-MSG2, which specifies a maximum number of bytes of memory available to be allocated to an interleaver, and O-CONTRACTn, which describes the specific parameters I and M for each interleaver/deinterleaver pair. Once the O-CONTRACTn message is confirmed by transmission of the O-B&G message, these parameters indicate the agreed-upon memory allocation between

interleaving and deinterleaving in the context of the triangular implementation of interleaving taught by VDSL1.).

- 79. A POSA thus would have been motivated to combine the initialization protocols of VDSL1 with the transceivers disclosed by Mazzoni using the parameter exchange protocol of the VDSL1 technical specification so as to perform initialization in a VDSL environment. This simple incorporation would have achieved the known benefits of allowing the TO and TU transceivers of Mazzoni to communicate hardware capabilities and negotiate selection of parameters, thus allowing for increased flexibility in parameter selection and confirmation that the hardware is compatible with the executed parameters (e.g., that memory MM has enough storage capacity for the determined interleaver and deinterleaver size). *See, e.g.*, Ex. 1007 at 111.

- 80. There are several reasons to combine Mazzoni and VDSL1. First, Mazzoni expressly instructs that the invention "may advantageously be applied to a very high rate digital subscriber line (VDSL) environment or system." Ex. 1005 at 1:19–21. Thus, the POSA would have been motivated to combine Mazzoni's transceiver with a reference that provided the relevant implementation details that would have allowed it to operate in a VDSL environment—the technical specification. At the relevant time, a POSA looking to build a functioning

transceiver that operated in a VDSL environment would have sought to comply with the VDSL1 technical specification.