#### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_\_

COMMSCOPE, INC.

Petitioner

v.

TQ DELTA, LLC Patent Owner

\_\_\_\_\_

U.S. Patent No. 7,836,381

Issue Date: November 16, 2010

Title: Computer Readable Medium With Instructions For Resource Sharing In A Telecommunications Environment

Case No. IPR2023-00066

# PETITION FOR INTER PARTES REVIEW OF U.S. PATENT NO. 7,836,381

Mail Stop PATENT BOARD

Patent Trial and Appeal Board

United States Patent and Trademark Office

P.O. Box 1450

Alexandria, VA 22313-1450

# TABLE OF CONTENTS

|      |      |       |                                                                 | Page |

|------|------|-------|-----------------------------------------------------------------|------|

| I.   | INT  | RODU  | JCTION                                                          | 1    |

| II.  | OVI  | ERVIE | W OF CHALLENGES AND RELIEF REQUESTED                            | 2    |

| III. | BAC  | CKGR  | OUND                                                            | 2    |

|      | A.   | '381  | PATENT PROSECUTION HISTORY                                      | 4    |

|      | В.   | PRI   | ORITY DATE                                                      | 5    |

|      | C.   | PRI   | OR DECISIONS BY THE DISTRICT COURT                              | 5    |

|      | D.   | CLA   | AIM CONSTRUCTION (37 C.F.R. § 42.104(B)(3))                     | 6    |

|      |      | 1.    | "TRANSCEIVER"                                                   | 7    |

|      |      | 2.    | "SHARED MEMORY"                                                 | 8    |

|      |      | 3.    | "AMOUNT OF MEMORY"                                              | 9    |

|      |      | 4.    | "THE SHARED MEMORY ALLOCATED TO THE                             |      |

|      |      |       | [DEINTERLEAVER / INTERLEAVER] IS USED AT                        |      |

|      |      |       | THE SAME TIME AS THE SHARED MEMORY                              |      |

|      |      |       | ALLOCATED TO THE [INTERLEAVER /                                 |      |

|      |      |       | DEINTERLEAVER]"                                                 | 9    |

| IV.  | PRIC | OR AF | RT REFERENCES                                                   |      |

|      | A.   | U.S.  | PATENT NO. 7,269,208 ("MAZZONI")                                | 9    |

|      | В.   |       | I TS 101 270-2 VERY HIGH SPEED DIGITAL  SSCRIBER LINE ("VDSL1") | 9    |

|      | C.   | U.S.  | PATENT NO. 6,707,822 ("FADAVI-ARDEKANI")                        | 10   |

| V.   | LEV  |       | F ORDINARY SKILL IN THE ART                                     |      |

| VI.  | THF  | Е СНА | LLENGED CLAIMS ARE UNPATENTABLE                                 | 11   |

| A. |    | OUND 1: CLAIMS 1-8 ARE UNPATENTABLE UNDER J.S.C. § 103 OVER MAZZONI IN VIEW OF VDSL1 | 11 |

|----|----|--------------------------------------------------------------------------------------|----|

|    | 1. | OVERVIEW OF GROUND 1                                                                 | 11 |

|    | 2. | CLAIM 1                                                                              | 21 |

|    | 3. | CLAIM 2: THE MEDIA OF CLAIM 1, WHEREIN THE                                           |    |

|    |    | DETERMINING IS BASED ON AN IMPULSE NOISE                                             |    |

|    |    | PROTECTION REQUIREMENT.                                                              | 47 |

|    | 4. | CLAIM 3: THE MEDIA OF CLAIM 1, WHEREIN THE                                           |    |

|    |    | DETERMINING IS BASED ON A LATENCY                                                    |    |

|    |    | REQUIREMENT                                                                          | 48 |

|    | 5. | CLAIM 4: THE SYSTEM OF CLAIM 1, WHEREIN                                              |    |

|    |    | THE DETERMINING IS BASED ON A BIT ERROR                                              |    |

|    |    | RATE REQUIREMENT.                                                                    | 49 |

|    | 6. | CLAIM 5                                                                              | 50 |

|    | 7. | CLAIM 6: THE MEDIA OF CLAIM 5, WHEREIN THE                                           |    |

|    |    | DETERMINING IS BASED ON AN IMPULSE NOISE                                             |    |

|    |    | PROTECTION REQUIREMENT.                                                              | 52 |

|    | 8. | CLAIM 7: THE MEDIA OF CLAIM 5, WHEREIN THE                                           |    |

|    |    | DETERMINING IS BASED ON A LATENCY                                                    |    |

|    |    | REQUIREMENT                                                                          | 52 |

|    | 9. | CLAIM 8: THE MEDIA OF CLAIM 5, WHEREIN THE                                           |    |

|    |    | DETERMINING IS BASED ON A BIT ERROR RATE                                             |    |

|    |    | REQUIREMENT                                                                          | 52 |

| B. |    | OUND 2: CLAIMS 1-8 ARE UNPATENTABLE UNDER                                            |    |

|    |    | I.S.C. § 103 OVER VDSL1 IN VIEW OF FADAVI-<br>DEKANI                                 | 52 |

|    | 1  | OVERVIEW OF GROUND 2                                                                 | 52 |

| U.S.  | Patent | No. 7,  | Petition for Inter Partes Re                                                                  | eview |

|-------|--------|---------|-----------------------------------------------------------------------------------------------|-------|

|       |        | 2.      | CLAIM 1                                                                                       | 58    |

|       |        | 3.      | CLAIM 2:                                                                                      | 72    |

|       |        | 4.      | CLAIM 3:                                                                                      | 72    |

|       |        | 5.      | CLAIM 4:                                                                                      | 72    |

|       |        | 6.      | CLAIM 5                                                                                       | 72    |

|       |        | 7.      | CLAIM 6:                                                                                      | 73    |

|       |        | 8.      | CLAIM 7:                                                                                      | 73    |

|       |        | 9.      | CLAIM 8:                                                                                      | 73    |

| VII.  | DISC   | CRETI   | ONARY ISSUES                                                                                  | 73    |

|       | A.     |         | COPYCAT PETITION DOES NOT PRESENT THE EXERCISE ADDRESSED IN PROSECUTION                       | 73    |

|       | В.     |         | BOARD SHOULD NOT DENY INSTITUTION UNDER                                                       | 75    |

| VIII. | CON    | CLUS    | ION                                                                                           | 77    |

| IX.   | MAN    | NDAT(   | ORY NOTICES FOR INTER PARTES REVIEW – 37                                                      |       |

|       | C.F.F  | R. § 42 | .8(A)(1)                                                                                      | 77    |

|       | A.     |         | L PARTIES IN INTEREST – 37 C.F.R. § 42.8(B)(1)                                                |       |

|       | B.     |         | ATED MATTERS – 37 C.F.R. § 42.8(B)(2)                                                         |       |

|       | C.     | LEA     | D AND BACKUP COUNSEL – 37 C.F.R. § 42.8(B)(3);<br>VICE INFORMATION – 37 C.F.R. § 42.8(B)(4) & |       |

|       |        |         | ER OF ATTORNEY                                                                                |       |

| X.    | CER'   | TIFIC   | ATION OF GROUNDS FOR STANDING                                                                 | 79    |

| ΧI    | PAY    | MENT    | COF FEES = 37 C F R 8 42 15                                                                   | 79    |

# **TABLE OF AUTHORITIES**

| Page                                                                                                            | :(s) |

|-----------------------------------------------------------------------------------------------------------------|------|

| Cases                                                                                                           |      |

| Adobe, Inc. v. Realtime Adaptive Streaming LLC, IPR2019-00712, Paper 9 (PTAB Sept. 12, 2019)                    | .75  |

| Advanced Bionics, LLC v. MED-EL Elektromedizinische Geräte GmbH, IPR2019-01469, Paper 6, 7 (PTAB Feb. 13, 2020) | .73  |

| Apple Inc v. Corephotonics, Ltd., 861 F. App'x 443 (Fed. Cir. 2021)                                             |      |

| Apple Inc. v. Fintiv, Inc.,<br>No. IPR2020-00019, Paper 11 (PTAB Mar. 20, 2020)75, 76,                          | 77   |

| Catalina Mktg. Int'l, Inc. v. Coolsavings.com, Inc., 289 F.3d 801 (Fed. Cir. 2002)                              | .22  |

| Cochlear Bone Anchored Sols. AB v. Oticon Med. AB,<br>958 F.3d 1348 (Fed. Cir. 2020)                            | .22  |

| Enplas Display Device Corp. v. Seoul Semiconductor Co., 909 F.3d 398 (Fed. Cir. 2008)                           | .35  |

| Godbersen-Smith Constr. Co. v. Guntert & Zimmerman Const. Div., Inc. IPR2021-00050, Paper 24 (PTAB May 7, 2021) | .73  |

| Kyocera Wireless Corp. v. ITC,<br>545 F.3d 1340 (Fed. Cir. 2008)                                                | .10  |

| Nokia of Am. Corp. v. TQ Delta, LLC,<br>IPR2022-00665, Paper 10 (PTAB Oct. 3, 2022)1,                           | 76   |

| Oticon Med. AB v. Cochlear Ltd.,<br>IPR2019-00975, Paper 15 (PTAB Oct. 16, 2019)                                | .74  |

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005)                                                        | 6    |

| Progenity, Inc. v. Natera, Inc., IPR2021-00279, Paper 12 (PTAB June 11, 2021)                         | 75     |

|-------------------------------------------------------------------------------------------------------|--------|

| Summit 6, LLC v. Samsung Elecs. Co.,<br>802 F.3d 1283 (Fed. Cir. 2015)                                | 8      |

| SuperGuide Corp. v. DirecTV Enters., 358 F.3d 870 (Fed. Cir. 2004)                                    | 9      |

| Tianma Microelectronics Co, v. Japan Display Inc.,<br>No. IPR2021-01058, Paper 16 (PTAB Jan. 5, 2022) | 74     |

| Statutes                                                                                              |        |

| 35 U.S.C. § 311                                                                                       | 1      |

| 35 U.S.C. § 315(c)                                                                                    | 1      |

| 35 U.S.C. § 325(d)                                                                                    | 73, 75 |

| Other Authorities                                                                                     |        |

| 37 C.F.R. § 42.8(A)(1)                                                                                | 77     |

| 37 C.F.R. § 42.8(b)(1)                                                                                | 77     |

| 37 C.F.R. § 42.8(b)(2)                                                                                | 77     |

| 37 C.F.R. § 42.8(b)(3)                                                                                | 77     |

| 37 C.F.R. § 42.8(b)(4)                                                                                | 78     |

| 37 C.F.R. § 42.8(b)(4) &                                                                              | 77     |

| 37 C.F.R. § 42.15                                                                                     | 79     |

| 37 C.F.R. § 42.15(a)                                                                                  | 79     |

| 37 C.F.R. § 42.100 et seq                                                                             | 1      |

| 37 C.F.R. §42.104(b)(3)                                                                               | 6      |

# **EXHIBIT LIST**

| Exhibit  | Short Name            | Description                                                                                                                                        |

|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1001 | '381 Patent           | U.S. Patent No. 7,836,381                                                                                                                          |

| Ex. 1002 | '381 File History     | File History of U.S. Patent No. 7,836,381                                                                                                          |

| Ex. 1003 | Wesel<br>Declaration  | Declaration of Dr. Richard Wesel, under 37 C.F.R. § 1.68                                                                                           |

| Ex. 1004 | Wesel CV              | Curriculum Vitae of Dr. Richard Wesel                                                                                                              |

| Ex. 1005 | Mazzoni               | U.S. Patent No. 7,269,208                                                                                                                          |

| Ex. 1006 | Fadavi-Ardekani       | U.S. Patent No. 6,707,822                                                                                                                          |

| Ex. 1007 | VDSL1                 | ETSI TS 101 270-2 V1.2.1 Technical Specification                                                                                                   |

| Ex. 1008 | Forney                | G. David Forney, <i>Burst-Correcting Codes</i> for the Classic Bursty Channel, Vol. Com-19, No. 5, IEEE Transactions on Communications, 772 (1971) |

| Ex. 1009 | Zogakis               | T. Nicholas Zogakis, <i>A Coded and Shaped Discrete Multitone System</i> , Vol. 43, No. 12, IEEE Transactions on Communications, 2941 (1995)       |

| Ex. 1010 | Kernighan             | B.W. Kernighan, D. M. Ritchie, <i>The C Programming Language</i> , 1998                                                                            |

| Ex. 1011 | AT&T DSP<br>(1981)    | J. R. Boddie, Overview: The Device, Support Facilities, and Applications, Vol. 60, The Bell System Technical Journal, 1431 (1981)                  |

| Ex. 1012 | AT&T DSP 32<br>(1986) | J. R. Boddie, <i>The DSP32 Digital Signal Processor and its Application Development Tools</i> , AT&T Technical Journal, 89 (1986)                  |

| Exhibit  | Short Name                                | Description                                                                                                                     |

|----------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1013 | Texas<br>Instruments TMS<br>320 (1994)    | Mansoor A. Chishtie, <i>Telecommunications Applications With the TMS320C5x DSPs</i> , Digital Signal Processing Products (1994) |

| Ex. 1014 | Maxwell                                   | U.S. Patent No. 4,924,456                                                                                                       |

| Ex. 1015 | V.32 bis                                  | ITU Recommendation V.32 bis (1991)                                                                                              |

| Ex. 1016 | V.32                                      | ITU Recommendation V.32 (1993)                                                                                                  |

| Ex. 1017 | LB-031                                    | ITU Contribution LB-031 (June 2004)                                                                                             |

| Ex. 1018 | Family 3 Claim<br>Construction<br>Opinion | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 445 (D. Del. Dec. 18, 2017) (Claim Construction Opinion)            |

| Ex. 1019 | Family 3 Claim<br>Construction<br>Order   | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 454 (D. Del. Dec. 28, 2017) (Claim Construction Order)              |

| Ex. 1020 | Family 1 Claim Construction Opinion       | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No.477 (D. Del. Jan 30, 2018) (Claim Construction Opinion)              |

| Ex. 1021 | Family 4 Claim<br>Construction<br>Order   | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF. No. 484 (D. Del. Feb. 6, 2018) (Claim Construction Order)               |

| Ex. 1022 | Family 3 MSJ<br>Opinion                   | TQ Delta, LLC v. 2Wire, Inc., No. 13-cv-01835-RGA, ECF No. 1106 (D. Del. Apr. 25, 2019) (MSJ Opinion)                           |

| Ex. 1023 | Family 3 Jury<br>Form                     | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 13-cv-01835-RGA, ECF No. 1187 (D. Del. May 23, 2019) (Jury Form)                      |

| Ex. 1024 | '890 Patent                               | U.S. Patent No. 7,831,890                                                                                                       |

| Exhibit  | Short Name                                                   | Description                                                                                                                               |

|----------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1025 | '890 File History                                            | File History of U.S. Patent No. 7,831,890                                                                                                 |

| Ex. 1026 | Veithen                                                      | Veithen et al., A 70 Mbps Variable-Rate<br>DMT-based Modem for VDSL, IEEE<br>International Solid-State Circuits Conference,<br>248 (1999) |

| Ex. 1027 | Kiss                                                         | Kiss et al, A Customizable DSP for DMT-Based ADSL Modem, IEEE, 349 (1998)                                                                 |

| Ex. 1028 | Third and Final Scheduling Order                             | TQ Delta, LLC v. 2Wire, Inc., No. 1:13-cv-01835, Dkt. No. 117 (D. Del. April 10, 2017) (Third and Final Scheduling Order)                 |

| Ex. 1029 | 2Wire Docket                                                 | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 1:13-cv-01835 (D. Del.) (Docket as of February 25, 2022)                                        |

| Ex. 1030 | Sept. 15, 2021<br>Letter                                     | <i>TQ Delta, LLC v. 2Wire, Inc.</i> , No. 1:13-cv-01835, Dkt. No. 1591 (D. Del. Sept. 15, 2021) (Letter)                                  |

| Ex. 1031 | RESERVED                                                     | RESERVED                                                                                                                                  |

| Ex. 1032 | Feb. 24, 2022<br>Letter Regarding<br>ADTRAN Case<br>Schedule | TQ Delta, LLC v. ADTRAN, Inc., No. 1:14-cv-00954, Dkt. No. 1373 (Feb. 24, 2022) (Letter)                                                  |

| Ex. 1033 | Hall-Ellis<br>Declaration                                    | Declaration of Sylvia Hall-Ellis                                                                                                          |

#### I. INTRODUCTION

Pursuant to 35 U.S.C. § 311 and 37 C.F.R. § 42.100 *et seq.*, CommScope, Inc. ("CommScope" or "Petitioner") petitions the Board to institute inter partes review of claims 1, 2, 3, 4, 5, 6, 7 and 8 ("the Challenged Claims") of U.S. Patent No. 7,836,381 ("the '381 Patent," Ex. 1001) owned by TQ Delta, LLC ("TQ Delta" or "Patent Owner"). Petitioner's request is supported by the Declaration of Dr. Richard Wesel ("Decl.") (Ex. 1003) and other exhibits submitted herewith.

This Petition is a copycat to the Petition filed by Nokia of America

Corporation in IPR2022-00665 and includes the exact same grounds. *Nokia of Am.*Corp. v. TQ Delta, LLC, IPR2022-00665, Paper 2 (PTAB Mar. 7, 2022) (the "Nokia IPR"). The Board found that the Nokia IPR presented "a compelling unpatentability challenge" and instituted trial on on October 3, 2022. *Nokia of Am. Corp. v. TQ*Delta, LLC, IPR2022-00665, Paper 10, at 7 (PTAB Oct. 3, 2022). In view of the Board's Institution Decision in the Nokia IPR, Petitioner hereby files this copycat petition with an accompanying motion for joinder.

Because (i) the Board instituted trial in the Nokia IPR, (ii) this is a copycat petition to the Nokia Petition; and (iii) CommScope will file an accompanying motion for joinder under 35 U.S.C. § 315(c), the time bar under § 315(b) does not apply to this IPR and the Board should institute trial, join CommScope to the Nokia

IPR, and permit CommScope to proceed in a "silent understudy" role in the Nokia IPR.

#### II. OVERVIEW OF CHALLENGES AND RELIEF REQUESTED

Pursuant to 42.22(a)(1) and 42.104(b)(1)–(2), Petitioner requests cancellation of the Challenged Claims pursuant to the grounds below. Additional support is provided in the Declaration of Dr. Richard Wesel (Ex. 1003).

Ground 1: Claims 1, 2, 3, 4, 5, 6, 7, and 8 are unpatentable under pre-AIA 35 U.S.C. § 103(a) over Mazzoni in view of VDSL1.

Ground 2: Claims 1, 2, 3, 4, 5, 6, 7, and 8 are unpatentable under pre-AIA 35 U.S.C. § 103(a) over VDSL1 in view of Fadavi-Ardekani.

#### III. BACKGROUND

The '381 Patent is directed to sharing a common memory and allocating that common memory between an interleaver and a deinterleaver in digital subscriber line ("DSL") technology. Ex. 1001, Abstract. The '381 Patent admits that interleaving and Reed-Solomon coding were known in the prior art but that the memory requirements were burdensome. *See id.*, 1:46-57. Accordingly, the '381 Patent explains that "an exemplary aspect of this invention relates to sharing memory between one or more interleavers and/or deinterleavers in a transceiver." *Id.*, 1:58–60.

At the time of the invention, Reed-Solomon coding was a well-known type of error control coding that protects a message against errors using additional bits or

symbols to produce a codeword that can withstand errors in the channel. Ex. 1003, ¶¶30-32. Interleaving was also a well-known type of error control, re-ordering symbols so that impairments that impact consecutively transmitted symbols, like impulsive noise bursts, will be spread out over multiple codewords after the symbols are deinterleaved. *Id.*, ¶¶33-40. Those symbols are then re-ordered back to the original order by a deinterleaver on the other end of a transmission. While each Reed-Solomon codeword is limited in the number of byte errors it can correct, interleaving the Reed-Solomon codewords allows for a long burst of errors to be spread over multiple Reed-Solomon codewords. For example, in the below figure, a sequence of interleaved Reed-Solomon coded data bytes suffers a noise burst, but, after those bytes are deinterleaved, the errored bytes are distributed across multiple codewords, and can thus be corrected. *Id.*, ¶¶35-40.

.....

A sequence of Interleaved Reed-Solomon bytes suffers a noise burst of 14 bytes, shown as red squares.

.....

After deinterleaving, the noisy bytes are distributed over multiple codewords so that they can be corrected.

Further, Reed-Solomon coding and interleaving on a shared memory was also a well-known concept at the time of the invention. *Id.*, ¶41. Indeed, computing

devices have long utilized common memory for at least two functions to overcome hardware constraints. *Id*.

The '381 Patent also contemplates an embodiment of the invention that relates to "configuring and initializing" the shared memory between the interleaver and deinterleaver. Ex. 1001, 1:63-64. But setting specific configurations by defining the parameters of two transceivers through an initialization process was a well-known concept at the time of the invention. Ex. 1003, ¶¶42-45. For example, for a communication link to function properly, the user transceiver and the operator transceiver must use the same parameters for the Reed-Solomon encoder/decoder pair and interleaver/deinterleaver pair. *Id.*, ¶43.

Here, the Board should institute review because there is at least a reasonable likelihood that Petitioner will prevail on at least one Challenged Claim.

# A. '381 Patent Prosecution History

U.S. Patent Application No. 12/853,020 was originally filed on August 9, 2010. Ex. 1001. A Notice of Allowance was mailed on October 6, 2010, where the Examiner explained that the independent claims identify "the distinct features of specifying a maximum number of bytes available to be allocated to [a/an] [deinterleaver/interleaver] in a transmitted or received message, determining the amount of memory required by the [deinterleaver/interleaver], and then allocating the bytes of shared memory to the [deinterleaver/interleaver] wherein the bytes allocated

do not exceed the maximum number of available bytes specified in the message." *Id.* at 129-30. The Examiner explained that the "closest prior art, Fadavi- Ardekani" only "discloses sharing a memory between the interleavers and deinterleavers." *Id.*

The '381 Patent is a continuation of U.S. Patent Application 11/246,163, granted as U.S. Patent No. 7,831,890 (Ex .1024), which had all of its claims initially rejected under § 102 in view of Fadavi-Ardekani. Ex. 1025, 317-33. After canceling all rejected claims, Patent Owner presented new claims, which were allowed for the same reasons the claims of the '381 Patent were allowed. *Id.*, 74-82.

#### **B.** Priority Date

The '381 Patent claims priority to U.S. Provisional Application No. 60/618,269, filed on October 12, 2004. For purposes of this action Petitioner assumes (without determining) that the patent is entitled to a priority date of October 12, 2004. If Patent Owner disputes the prior art status of any of Petitioner's cited references, Petitioner reserves the right to challenge the priority date for the '381 Patent.

#### **C.** Prior Decisions by the District Court

The '381 Patent was previously considered by the United States District Court for the District of Delaware in *TQ Delta, LLC v. 2Wire, Inc.*, No. 13-cv-01835-RGA (D. Del.) (the "Delaware Litigation"); *TQ Delta, LLC v. Zhone Technologies, Inc.*, No. 13-cv-01836- RGA (D. Del.); *TQ Delta, LLC v. ZyXEL Communications, Inc.*,

No. 13-cv-02013- RGA (D. Del.); and *TQ Delta, LLC v. ADTRAN, Inc.*, No. 14-cv-00954-RGA (D. Del.). These four cases were consolidated into the lead case against *2Wire*.

The district court issued memoranda and orders construing multiple claim terms of the '381 Patent. Exs. 1018-21. The district court also addressed, on summary judgment, the invalidity of claim 5 of the '381 Patent as obvious in view of Mazzoni (Ex. 1005) over LB-031 (Ex. 1017), ultimately denying the motion because there was a dispute of material fact regarding the motivation to combine. Ex. 1022. Patent Owner also alleged certain references, including Fadavi-Ardekani (Ex. 1006), failed to disclose a "shared memory." The court granted Patent Owner's motion for no invalidity on this ground as a matter of law, reasoning that the Defendant failed to rebut Plaintiff's argument that Defendant had not proven inherency. *Id.* at 18.

A jury subsequently determined that LB-031 as understood by a POSA and LB-031 in combination with Mazzoni did not render claim 5 of the '381 Patent invalid as obvious. Ex. 1023. No ground on the basis of Mazzoni in view of VDSL1, or VDSL1 in view of Fadavi-Ardekani was presented to the jury.

# D. Claim Construction (37 C.F.R. § 42.104(b)(3))

Claim terms are interpreted with the ordinary and customary meaning as understood by a person of ordinary skill in the art ("POSA") under *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005). Certain terms of the '381 Patent were

construed in the Delaware Litigation. *See* Exs. 1018–21. Those claim terms are addressed in the table below. Any other terms should receive their respective plain and ordinary meaning.

| Claim Term              | D. Del. Construction                                        |  |

|-------------------------|-------------------------------------------------------------|--|

| "transceiver"           | "communications device capable of transmitting and          |  |

|                         | receiving data wherein the transmitter portion and          |  |

|                         | receiver portion share at least some common circuitry"      |  |

| "shared memory"         | "common memory used by at least two functions, where        |  |

|                         | a portion of the memory can be used by either one of the    |  |

|                         | functions"                                                  |  |

| "amount of memory"      | Plain meaning, i.e., that is not limited to number of bytes |  |

| "the shared memory      | "the deinterleaver reads from, writes to, or holds          |  |

| allocated to the        | information for deinterleaving in its respective allocation |  |

| [deinterleaver /        | of the shared memory at the same time as the interleaver    |  |

| interleaver] is used at | reads from, writes to, or holds information for             |  |

| the same time as the    | interleaving in its respective allocation of the shared     |  |

| shared memory           | memory"                                                     |  |

| allocated to the        |                                                             |  |

| [interleaver /          |                                                             |  |

| deinterleaver]"         |                                                             |  |

#### 1. "transceiver"

The district court improperly narrowed this term beyond what is contemplated in the specification. Relying on dictionary definitions, the district court concluded that "a POSA would understand the transmitter and receiver portions to share common circuitry or components." Ex. 1020 at 4. But, although the specification discloses sharing memory between a transmitter portion and receiver portion of a transceiver, Ex. 1001, 5:33-39—i.e., sharing common circuitry—it also discloses that "an exemplary transceiver can…allocate a first portion of shared memory 120 to a

first interleaver [] in the *transmitter* portion of the transceiver and allocate a second portion of the shared memory to a second interleaver [] in the *transmitter* portion of the transceiver," *id.*, 5:40-46. Thus, where only the transmitter portions are sharing a memory, the transmitter and receiver portions are **not** sharing a memory, i.e., do not share common circuitry. Narrowing the claim to require that the transmitter and receiver share common circuitry is inapposite to what is expressly disclosed in the specification and is thus inappropriate. *Summit 6, LLC v. Samsung Elecs. Co.*, 802 F.3d 1283, 1290 (Fed. Cir. 2015) (explaining that "[e]xtrinsic evidence may not be used to contradict claim meaning that is unambiguous in light of the intrinsic evidence" (internal quotation marks omitted)).

Petitioner therefore does not adopt the district court's construction and instead advances that the plain and ordinary meaning should control.

Irrespective, the unpatentability of the Challenged Claims in view of the grounds presented below does not turn on whether or not the transmitter and receiver portions of the claimed "transceivers" are required to share common circuitry.

# 2. "shared memory"

Petitioner does not adopt the narrow construction set forth by the district court and believes the claim term "shared memory" should be given its plain and ordinary meaning. Nowhere in the specification is a shared memory so narrowly defined, and it is improper to import such language from the specification into the claims.

SuperGuide Corp. v. DirecTV Enters., 358 F.3d 870, 875 (Fed. Cir. 2004).

Nonetheless, the unpatentability of the Challenged Claims in view of the grounds below does not turn on whether the shared memory must include a portion of the memory that can be used by either one of the functions.

# 3. "amount of memory"

Petitioner does not adopt the construction set forth by the district court and believes the claim term should be given its plain meaning without limitation. Regardless, the unpatentability of the Challenged Claims in view of the grounds presented below does not turn on this construction.

4. "the shared memory allocated to the [deinterleaver / interleaver] is used at the same time as the shared memory allocated to the [interleaver / deinterleaver]"

For purposes of this petition, Petitioner adopts the district court's construction as recited *supra*.

#### IV. PRIOR ART REFERENCES

# A. U.S. Patent No. 7,269,208 ("Mazzoni")

Mazzoni, which issued on September 11, 2007, derives from U.S. Patent Application No. 10/088,387, which was filed on July 11, 2001, and published as US2003/0021338 on January 30, 2003. Mazzoni thus qualifies as prior art under at least pre-AIA 35 U.S.C. § 102(e).

# B. ETSI TS 101 270-2 Very High Speed Digital Subscriber Line ("VDSL1")

VDSL1 is technical specification ETSI TS 101 270-2 related to "Very High Speed Digital Subscriber Line (VDSL)" (hereinafter "VDSL1"). Ex. 1033. This technical specification was published online by ETSI on July 24, 2003. Dr. Hall-Ellis located VDSL1 at http://www.etsi.org, the website for the European Telecommunications Standards Institute (ETSI). *Id.*, ¶¶24-31. She confirmed that VDSL1 was cataloged and indexed and, thus, accessible by July 24, 2003. *Id.* She further states that a POSA would have located this document using reasonable diligence, either through common search terms or using the search engine on the ETSI website. *Id.* at 27–29. Dr. Wesel likewise states that a POSA would have looked to ETSI for a technical specification on VDSL. Ex. 1003, ¶18. Moreover, the Federal Circuit has previously confirmed that ETSI standards are publicly accessible. See Kyocera Wireless Corp. v. ITC, 545 F.3d 1340, 1350-51 (Fed. Cir. 2008). Thus, VDSL1 is prior art under at least pre-AIA 35 U.S.C. § 102(b).

#### C. U.S. Patent No. 6,707,822 ("Fadavi-Ardekani")

Fadavi-Ardekani was filed on January 7, 2000 and issued as a U.S. Patent on March 16, 2004. Fadavi-Ardekani is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (e).

#### V. LEVEL OF ORDINARY SKILL IN THE ART

A person of ordinary skill in the art ("POSA") pertinent to the '381 Patent would have had at least a Bachelor's degree in electrical engineering, or a related field, and at least 6-7 years of experience in telecommunications or related field; a

master's degree in electrical or computer engineering, or the equivalent, and at least 3-4 years of experience in telecommunications or related field; or a Ph.D. in electrical or computer engineering, or the equivalent, with at least 1-2 years of experience in telecommunications or related field. Ex. 1003, ¶16. Additional experience may compensate for less education. *Id*.

#### VI. THE CHALLENGED CLAIMS ARE UNPATENTABLE

A. Ground 1: Claims 1-8 are Unpatentable Under 35 U.S.C. § 103 over Mazzoni in view of VDSL1

#### 1. Overview of Ground 1

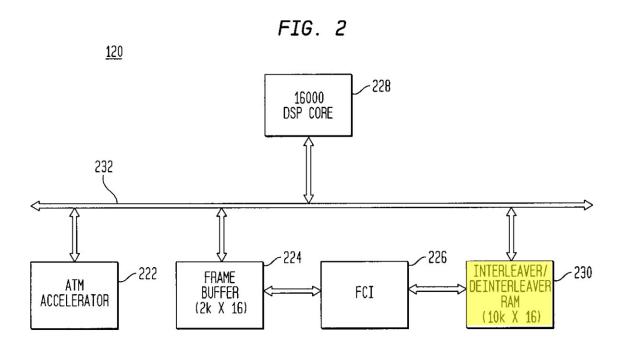

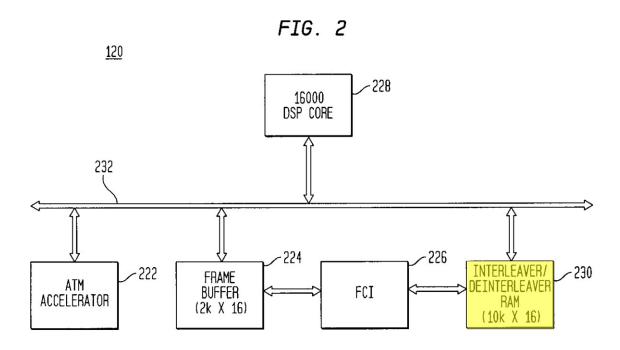

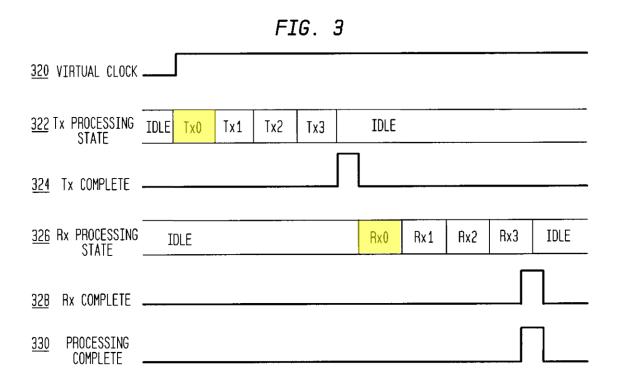

#### i. Mazzoni

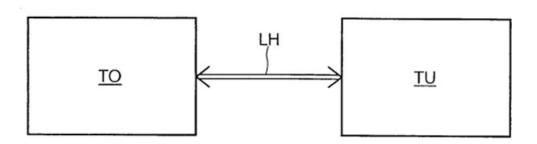

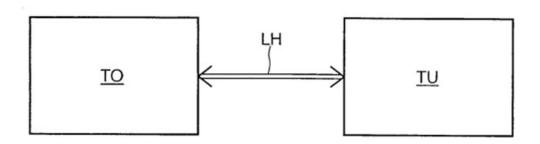

Mazzoni teaches a transceiver in a VDSL environment that can send and receive digital data and that can determine the shared memory capacity used to interleave and deinterleave that data. Ex. 1005, 1:10-15. As shown in Figure 1 below, Mazzoni contemplates two send/receive devices (i.e., transceivers), TU and TO, that communicate by "a very high bit rate communication line LH." *Id.*, 1:60-61.

# <u>FIG.1</u>

*Id.*, Fig. 1.

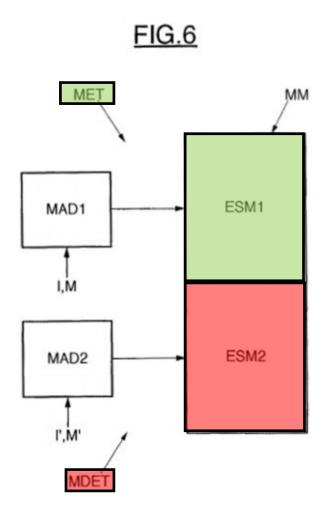

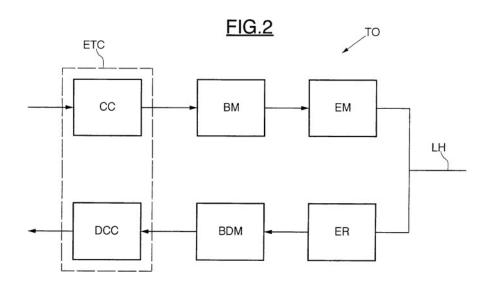

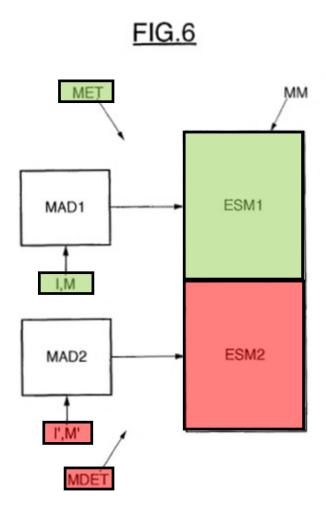

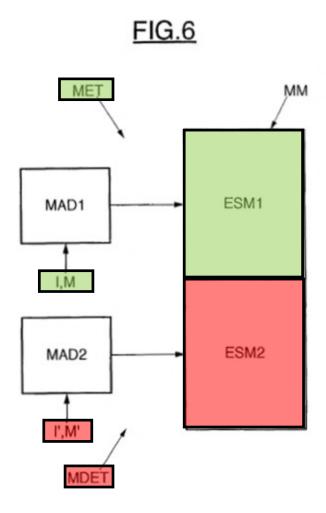

Mazzoni further discloses a shared memory "MM" that resides in each transceiver, and that "can be shared between the interleaving means and the deinterleaving means." *Id.*, 1:59-65; 6:6-8. For example, annotated Figure 6 of Mazzoni, shown below, illustrates how the common memory, MM, is allocated to the interleaver (MET) as ESM1 (green, below) and deinterleaver (MDET) as ESM2 (red, below) on just one of the transceivers TO or TU.

*Id.*, Fig. 6.

Mazzoni teaches how to determine the required memory allocations for the interleaver and deinterleaver (i.e., the memory size of ESM1 and ESM2) via triangular implementation of convolutional interleaving and deinterleaving.

Mazzoni further teaches using Reed-Solomon coding coupled to an interleaver to protect transmitted data. *Id.*, 2:25-30.

Thus, starting with downstream and upstream bit rates between the TO and TU that are disturbed by an impulsive noise, Mazzoni discloses calculating the number of data bits that are affected by an impulsive noise, the resultant errored bytes, the

number of Reed-Solomon codewords needed to correct those errored bytes, and the required interleaver or deinterleaver memory to hold those bytes. *Id.*, 6:11-36.

Relying on those calculations, Mazzoni also discloses determining the amount of memory required by the interleaver/deinterleaver to interleave/deinterleave the Reed Solomon coded data bytes using parameters I and M. *Id.*, 6:37-38. Mazzoni explains that parameters I and M can be applied to the equation I×(I-1)×M/2 to calculate "the size of the first memory space [ESM1]" for the interleaver, and parameters I' and M' can then be applied to the equation I'×(I'-1)×M'/2 to calculate "the size of the second memory space ESM2" for the deinterleaver. *Id.*, 6:38-44. Mazzoni explains that the common memory required (MM) is the sum of ESM1 and ESM2.

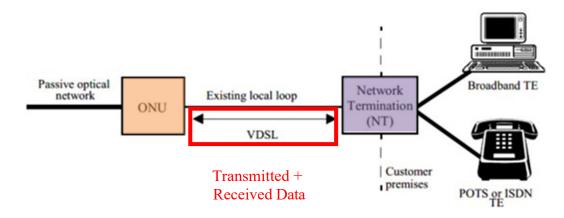

#### ii. VDSL1

VDSL1 is the technical specification for very high speed digital subscriber line transceivers put forth by ETSI. VDSL1 teaches incorporating VDSL onto transceivers VTU-O and VTU-R, and then determining the memory allocation for the interleaver and deinterleaver on each transceiver via triangular implementation of convolutional interleaving and deinterleaving. Ex. 1007, 13, 59-60.

Specifically, VDSL1 teaches that "[i]nterleaving shall be used to protect the data against bursts of errors by spreading the errors over a number of Reed-Solomon codewords." *Id.*, 59. To determine the memory required to interleave or

deinterleave those bytes, VDSL1 teaches parameters I and M, which can be used to determine the "(De)interleaver memory size" with the equation MxIx(I–1)/2 (see Table 19 below). *Id.*, 60.

Table 19: Characteristics of triangular, convolutional interleaver

| Parameter                   | Value                      |  |

|-----------------------------|----------------------------|--|

| Interleaver block length    | I octets (I must divide N) |  |

| Interleaving depth D        | M x I * 1 octets           |  |

| [De]interleaver memory size | M x I x (I-1)/2 actets     |  |

| End-to-end delay            | M x I x (I-1) octets       |  |

| Correction capability       | t/q x M x (1+1) octets     |  |

VDSL1 then contemplates various "Interleaver Characteristics" in Table 27, including "Interleaver Memory Size," "Erasure Correction (E)," and "End-to-End Delay (DL)." *Id.*, 72.

**Table 27: Interleaver Characteristics**

| Parameter               | Value                                                 | Notes                                 |

|-------------------------|-------------------------------------------------------|---------------------------------------|

| Block Length (I)        | I = N/8, N/4 or N/2, octets                           | N = PS+19, octets                     |

| Depth (D)               | $D = M \times I + 1$ , octets                         | $M = 0 \rightarrow 64$ , programmable |

| Erasure Correction (E)  | $E = [t \times I/N] \times (M \times I + 1)$ , octets | t = 8 (RS error correction ability)   |

| End-to-End Delay (DL)   | $DL = M \times I \times (I - 1)$ , octets             |                                       |

| Interleaver Memory Size | $MEM = M \times I \times (I - 1) / 2$ , octets        |                                       |

NOTE 1: The interleaver erasure correction E defines the maximum number of corrupted sequential octets could be corrected by RS algorithm when interleaving is applied. Correspondingly, the duration of noise pulses the system is protected from could be calculated as E×8/R, where R is the bit rate of the transmit signal over the line.

NOTE 2: The symbols indicates the truncation of the value to the lower integer.

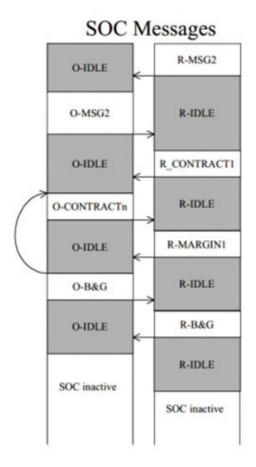

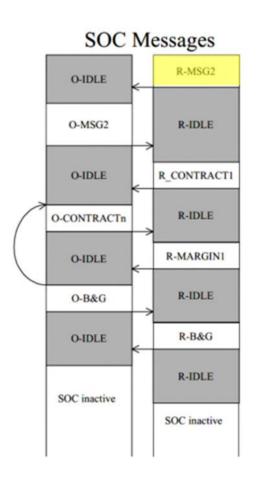

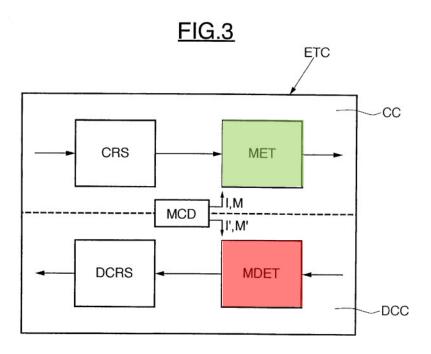

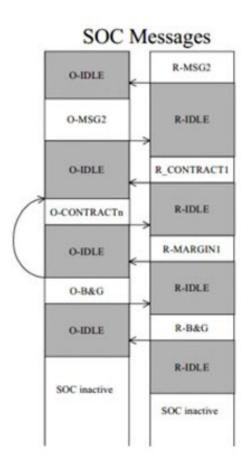

VDSL1 also teaches initialization protocols between the VTU-O and VTU-R to set those I and M parameters, including the messages shown below. *Id.*, 127.

The first message, R-MSG2, describes the VTU-R's capabilities, including the maximal number of bytes available to be allocated to an interleaver. *Id.*, 132.

After the messages R-MSG2, O-MSG2, and R-CONTRACT1, the message O-CONTRACTn, contains a proposed upstream contract and a proposed downstream contract, including contract descriptors for each contract, including the parameters I and M for the upstream interleaver/deinterleaver and a distinct set of parameters I and M for the downstream deinterleaver/interleaver. *Id.*, 129.

#### iii. Motivation to Combine

Both Mazzoni and VDSL1 are directed to VDSL systems. Indeed, Mazzoni contemplates a transceiver for sending/receiving digital data, "in particular in a VDSL environment," Ex. 1005, and VDSL1 is the technical specification put forth by ETSI that "specifies requirements for transceivers that provide very high bit-rate digital transmission," i.e., VDSL, Ex. 1007, 9.

As explained *supra*, Mazzoni teaches a VDSL transceiver with a shared memory that determines an amount of memory required by an interleaver/deinterleaver to interleave/deinterleave Reed Solomon coded data bytes, that allocates those bytes of the shared memory to the interleaver/deinterleaver at a particular data rate, and that subsequently interleaves/deinterleaves those bytes.

Mazzoni does not, however, expressly disclose transmitting or receiving a message during initialization specifying a maximum number of bytes of memory that are available to be allocated to an interleaver or deinterleaver. A POSA would have understood that a transceiver as contemplated in Mazzoni, especially one implemented in a VDSL environment, would perform initialization protocols. Ex. 1003, ¶77. Thus, a POSA would have been motivated to look to the VDSL technical specifications available around the same time for those initialization protocols—here, the VDSL1 technical specification. *Id*.

VDSL1 disclosed initialization. Ex. 1007, 111 (disclosing "Initialisation" protocols for the transceiver pair VTU-O and VTU-R, including an "[e]xchange of

parameters"); *id.*, 127-34 (Disclosing a "channel analysis and exchange" state, which discloses the negotiation of interleaver/deinterleaver parameters, including R- MSG2, which specifies a maximum number of bytes of memory available to be allocated to an interleaver, and O-CONTRACTn, which describes the specific parameters I and M for each interleaver/deinterleaver pair. Once the O- CONTRACTn message is confirmed, these parameters indicate the agreed-upon memory allocation between interleaving and deinterleaving in the context of the triangular implementation of interleaving taught by VDSL1.).

A POSA thus would have been motivated to combine the initialization protocols of VDSL1 with the transceivers disclosed by Mazzoni using the parameter exchange protocol of the VDSL1 technical specification so as to perform initialization in a VDSL environment. Ex. 1003, ¶79. This simple incorporation would have achieved the known benefits of allowing the TO and TU transceivers of Mazzoni to communicate hardware capabilities and negotiate selection of parameters, thus allowing for increased flexibility in parameter selection and confirmation that the hardware is compatible with the executed parameters (e.g., that memory MM has enough storage capacity for the determined interleaver and deinterleaver size). *See, e.g.*, Ex. 1007, 111; Ex. 1003, ¶79.

There are several reasons to combine Mazzoni and VDSL1. First, Mazzoni expressly instructs that the invention "may advantageously be applied to a very high

rate digital subscriber line (VDSL) environment or system." Ex. 1005, 1:19-21. Thus, the POSA would have been motivated to combine Mazzoni's transceiver with a reference that provided the relevant implementation details that would have allowed it to operate in a VDSL environment—the technical specification. At the relevant time, a POSA looking to build a functioning transceiver that operated in a VDSL environment would have sought to comply with the VDSL1 technical specification. Ex. 1003, ¶80.

Second, the POSA would have understood that a VDSL transceiver would have had to perform initialization for the purposes of exchanging relevant information between the office transceiver and the remote transceiver. Ex. 1003, ¶81. For example, VDSL1 explains that one of the initialization tasks between the office and remote transceiver is defining "a common mode of operation," without which the office and remote transceivers would not be able to properly function. Ex. 1007, 111. As a result, the POSA would have been motivated to refer to the standard so as to follow the common and required mechanism for sharing such information between the office and remote. Ex. 1003, ¶81. Indeed, both Mazzoni and VDSL1 disclose additional requirements that would have been established during initialization, including impulse noise requirements, *compare* Ex. 1005, 6:11-18, *with* Ex. 1007, 71, latency requirements, *compare* Ex. 1005, 2:54-56, *with* Ex. 1007, 59,

and bit error rate requirements, *compare* Ex. 1005, 4:53-56, *with* Ex. 1007, 72. Third, the disclosure of Mazzoni explicitly suggests initialization protocols.

For example, in VDSL1, the parameters I, M, I', and M' result from the negotiation between the VTU-R and VTU-O transceivers during the "Channel analysis and exchange" phase, i.e., during initialization. Ex. 1007, 129; Ex. 1003, ¶82. Similarly, Mazzoni explains that "the parameters I, M, I', and M' can be modified, e.g., by software, and are delivered by control means MCD." Ex. 1005, 5:21-24. A POSA would have understood that initialization protocols would have preceded the delivery of M and I parameters by the MCD. Ex. 1003, ¶82. In reading Mazzoni, a POSA thus would have been motivated to look to the VDSL1 technical specification and had a reasonable expectation of success in doing so. *Id.* It is not significant that Mazzoni also discloses reading from a table of values for the parameters I, M, I', and M'. See Ex. 1005, 6:51-61. A POSA would have understood that initialization protocols could instruct which I, M, I', and M' parameters to select from said table, which would still provide the benefits of using initialization protocols as described above. Ex. 1003, ¶82. Alternatively, a POSA would have understood that initialization protocols could substitute for such a table—which is merely one contemplated method of delivering the I and M parameters—to allow for the benefits described above. *Id*.

In addition, because both Mazzoni and VDSL1 contemplate the same implementation of interleaving and deinterleaving—triangular implementation of convolutional interleaving—a POSA would have had a reasonable expectation of success in combining the two references. Compare Ex. 1005, 2:49-56, with Ex. 1007, 60, 152-53; Ex. 1003 ¶83. Particularly, both Mazzoni and VDSL1 contemplate the same parameters to define the interleaver and deinterleaver—I, M, I', and M'. Compare Ex. 1005, 6:37-44, with Ex. 1007, 59-60, 152-53. Likewise, both explain that to determine the interleaver or deinterleaver memory size—a critical element of the challenged claims—the parameters can be applied to the equation I×(I-1)×M/2." Compare Ex. 1005, 6:38-41, with Ex. 1007, 60. A POSA using ordinary creativity would know to implement a memory in the transceiver of Mazzoni of a size sufficient to enable the range of parameters contemplated in VDSL1. Ex. 1003, ¶83. Indeed, Mazzoni expressly instructs a POSA that its example is simply "[a]n application of the invention to a VDSL communication system," and that "the invention is not limited to this application." Ex. 1005, 3:53-55.

For at least these reasons, in reading Mazzoni, a POSA thus would have been motivated to look to the VDSL1 standard and had a reasonable expectation of success in doing so. Ex. 1003, ¶84.

#### 2. Claim 1

# i. Claim 1: [1.pre] A non-transitory computer-readable information storage media having stored thereon instructions, that if executed by a processor, cause to be performed a method for allocating shared memory in a transceiver comprising:

Petitioner does not agree that the preamble in this case is limiting. The language of the preamble does not recite essential structure or steps, nor is it necessary to give life, meaning, and vitality to the claim. *Catalina Mktg. Int'l, Inc. v. Coolsavings.com, Inc.*, 289 F.3d 801, 808 (Fed. Cir. 2002).

"Non-transitory computer-readable information storage media having stored thereon instructions, that if executed by a processor" amounts to nothing more than "language extolling...features of the claimed invention," which "does not limit the claim scope without clear reliance on those benefits or features as patentably significant." *Id.* at 809. Because the limitations of the claim make no reference to—let alone clearly rely on—these features, the language cannot be deemed limiting.

To the extent it is argued that the language "a method for allocating shared memory in a transceiver" is limiting, a "conclusion that some preamble language is limiting does not imply that other preamble language, or the entire preamble is limiting." *Cochlear Bone Anchored Sols. AB v. Oticon Med. AB*, 958 F.3d 1348, 1355 (Fed. Cir. 2020).

As explained *supra*, Petitioner does not agree with the District of Delaware's construction of shared memory, but, under either construction, Mazzoni discloses this limitation.

To the extent it is argued that the preamble is entirely limiting, Mazzoni discloses this limitation. A POSA reading Mazzoni would understand that "the method for allocating shared memory in a transceiver" described in its specification would normally be implemented as a computer program or programmable logic, which would, as a matter of course, require a non-transitory computer-readable information storage media having stored thereon instructions. Ex. 1003, ¶94. For example, Mazzoni discloses a "send/receive device (i.e., modem)" with a memory, Ex. 1005, 1:47–49, as well as cites to a reference that discloses digital signal processors, which a POSA would understand requires the limitation as claimed. Ex. 1003, ¶94; Ex. 1026 (disclosing a "complete bit-true C model of the chip," which a POSA would understand to be instructions stored on a non-transitory computerreadable storage media, that when executed cause to be performed all the methods of the transceiver); see also Exhibit 1027.

Further, Mazzoni discloses that the "memory may be a random access memory." Ex. 1005, 2:57–58. A POSA would understand memories such as Random Access Memories to be a "non-transitory computer-readable information storage media." Ex. 1003, ¶94. Mazzoni then explains that the modem "actually processe[s]" data, Ex. 1005, 1:59–65, which a POSA would understand to mean that the modem includes a processor that executes instructions stored in a memory. Ex. 1003, ¶94. Thus, Mazzoni discloses non-transitory-computer-readable information

storage media having stored thereon instructions for performing the claimed limitations in Claims 1-8 (see *infra*).

Mazzoni also discloses that when those instructions are executed by the processor, a method for allocating shared memory is performed, namely that a system with a common memory that is used by a first function (e.g., the interleaver) and a second function (e.g., the deinterleaver), where a portion of the memory (MM) can be used by either one of the functions. *See* Ex. 1003, ¶94-110. Specifically, Mazzoni discloses "a memory" that "can be shared between the interleaving means and the deinterleaving means, and whose memory allocation can be *reconfigured* in accordance with the bit rate actually processed by the send/receive device (modem)." Ex. 1005, 1:59–65; *see also id.*, 2:3–15.

Annotated Figure 6, shown below, illustrates how the common memory, MM, is allocated to the interleaver (MET), in green, and deinterleaver (MDET), in red.

Ex. 1005, Fig. 6. Mazzoni explains that, "the interleaving means and the deinterleaving means include **common memory means MM**, e.g., a dual-port random access memory." *Id.* at 5:61–64. "The memory space of the memory MM is then **divided into a first memory space ESM1 assigned to the interleaving means MET, and a second memory space ESM2 is assigned to the deinterleaving means MDET."** *Id.* **at 5:64–67.** *See also* **Limitation [1.B] below, which discloses a dynamically allocable shared memory that can be used by either the interleaver or the deinterleaver.**

Thus, Mazzoni discloses a common memory (e.g., MM) used by at least two functions (e.g., the interleaver and the deinterleaver), where a portion of the memory can be used by either one of the functions. Ex. 1003, ¶¶93-110.

Mazzoni and VDSL1 further disclose a transceiver, as described in Limitation 1.A, *infra*.

ii. Claim 1: [1.A] transmitting or receiving, by the transceiver, a message during initialization specifying a maximum number of bytes of memory that are available to be allocated to an interleaver;

As explained *supra*, Petitioner does not agree with the District of Delaware's construction of transceiver, but, under either construction, Mazzoni discloses this limitation.

Mazzoni discloses a communication device capable of transmitting and receiving data (e.g., transceivers with "transmitters and receivers" for "sending and receiving digital data"). Ex. 1005, 1:8-15; Ex. 1003, ¶¶111-115. Specifically, as shown in Figure 1 below, Mazzoni contemplates two send/receive devices (i.e., transceivers), TU and TO, that communicate by "a very high bit rate communication line LH." Ex. 1005, 1:60-61.

# <u>FIG.1</u>

*Id.*, Fig. 1. As is shown in Figure 2, the terminal TO "includes a send system [i.e., transmitter] and a receive system [i.e., receiver] both connected to the transmission line LH." *Id.*, 4:30-32. Thus, the transmitter portion and receiver portion share at least some common circuitry. Ex. 1003, ¶¶112-114.

Mazzoni further discloses a shared memory "MM," wherein the "size of the memory MM is set by the maximum bit rate that the send/receive device can process." Ex. 1005, 6:6-8. The POSA would thus have understood the shared memory of Mazzoni is common circuitry between the "transmitters and receivers." Ex. 1003, ¶114.

Although Mazzoni does not expressly disclose that its transceiver performs transmitting or receiving a message during initialization specifying a maximum number of bytes of memory that may be allocated to an interleaver, a POSA would have understood that, to implement the embodiments disclosed in Mazzoni, transmitting and receiving initialization messages setting parameters would have been necessary. Ex. 1003, ¶115.

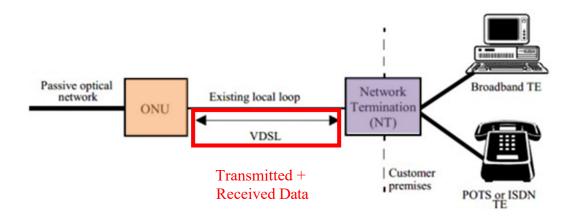

To the extent it is argued that Mazzoni does not disclose this limitation, the VDSL1 standard does so explicitly. Specifically, VDSL1 discloses a message that is transmitted from the VTU-R transceiver and received by the VTU-O transceiver that specifies a maximum number of bytes of memory that are available to be allocated to an (de)interleaver at initialization. *See* Ex. 1007, 13, 132. A POSA would have been motivated to combine Mazzoni with VDSL1 for the reasons described *supra*. Ex. 1003, ¶116.

Similar to Mazzoni, VDSL1 discloses a communication device (e.g., defining "VTU" as "VDSL **Transceiver** Unit"). Ex. 1007, 13. VDSL1 also discloses that

each VTU is capable of transmitting and receiving data. For example, annotated Figure 4 shows how VTU-R transceivers (in purple) transmit and receive data to and from the VTU-O (in orange). Ex. 1007, 16.

Figure 4: General fibre-to-the-node architecture for VDSL

As with Mazzoni, VDSL1 discloses that the transmitter and receiver portion of the VTU share at least some common circuitry (e.g., circuitry that provides power, circuitry that utilizes configuration messages, circuitry that controls timing, and, as in the case of the implementation disclosed by Mazzoni, circuitry of the common memory used for interleaving and deinterleaving). Ex. 1007, 20, 111; Ex. 1003, ¶118-120.

In addition to disclosing a transceiver, the VDSL1 standard discloses how each of its transceivers transmit or receive a message during initialization specifying a maximum number of bytes of memory that are available to be allocated to an interleaver in the "channel analysis and exchange state" of the "initialization

protocol." Ex. 1007, 63; Ex. 1003, ¶¶121-128. VDSL1 provides an overview of the "channel analysis and exchange state" wherein **R-MSG2** (below, highlighted) is communicated.

Ex. 1007, 77.

The VDSL1 technical specification describes the message **R-MSG2** in Table 82 as including the field "**Maximum interleaver memory**," which specifies the maximum number of bytes available to be allocated to an interleaver. *Id.*, 132; Ex.

1003, ¶125.

Table 82: Description of R-MSG2

| Field Field or macro-field typ                        |                                                                           | Remark                                                                                                     |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| Message descriptor                                    | 1 octet                                                                   | See table 49                                                                                               |  |  |

| Maximum constellation size in upstream                | 1 octet                                                                   | Maximum number of bits per tone                                                                            |  |  |

| RS setting supported by VTU-R                         | 1 octet                                                                   | 0x00: only mandatory settings<br>0xFF: all settings (see note 1)                                           |  |  |

| Interleaver setting supported by VTU-R                | 1 octet                                                                   | 0x00: only mandatory settings<br>0xFF: all settings<br>0xNN: NN = number of settings<br>(0x00 < NN < 0xFF) |  |  |

| Detailed interleaver setting description              | 0 octets if NN = 0x00<br>0 octets if NN = 0xFF<br>NN x 4 octets otherwise | See table 74                                                                                               |  |  |

| Maximum power transmitted                             | 1 octet                                                                   | In units of 0,25 dBm                                                                                       |  |  |

| Maximum interleaver memory                            | 3 octets                                                                  | In octets (see note 2)                                                                                     |  |  |

| Maximum number of EOC octets per<br>frame in upstream | 1 octet                                                                   | Number of EOC octets per frame                                                                             |  |  |

| Maximum number of VOC octets per<br>frame in upstream | 1 octet                                                                   | Number of VOC octets per frame                                                                             |  |  |

| Support of express swapping                           | 1 octet                                                                   | 0x00: Not supported<br>0xFF: Supported                                                                     |  |  |

| jmax                                                  | 1 octet                                                                   | Maximum value of j <sub>max</sub> supported by the VTU-R (see note 3)                                      |  |  |

NOTE 3: Specification of j<sub>max</sub> = k means that all values from 0 to k are supported.

The R-MSG2 message is one in a series of messages exchanged between the VTU-O and the VTU-R during initialization. Ex. 1007, 63; Ex. 1003, ¶¶125-127. Therefore, the combination of Mazzoni and VDSL1 discloses a transceiver (e.g., TO or TU in Mazzoni or the VDSL Transceiver Unit or VTU in VDSL1) that performs: transmitting or receiving a message (e.g., R-MSG2) during initialization (e.g., the channel analysis and exchange state) specifying a maximum number of bytes of memory that are available to be allocated to an interleaver (e.g., the parameter "Maximum interleaver memory"). Ex. 1003, ¶128-129.

iii. Claim 1: [1.B] determining, at the transceiver, an amount of memory required by the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes within a

#### shared memory;

As explained *supra*, Petitioner does not agree with the District of Delaware's construction of amount of memory, but, under either construction, Mazzoni discloses this limitation.

Mazzoni discloses determining, at the transceiver (TO or TU), an amount of memory required by the interleaver (MET) in ESM1 (green, below) and the deinterleaver (MDET) in ESM2 (red, below). Ex. 1005, Fig. 6; Ex. 1003, ¶131-132. As described with respect to Limitation [1.pre], Mazzoni discloses memory shared between the interleaver and the deinterleaver.

Moreover, Mazzoni discloses that "Reed-Solomon coding means are associated with the interleaving means" and "[i]n conjunction with subsequent interleaving, the Reed-Solomon coding can correct bursts of errors introduced by the transmission channel." *Id.*, 4:38-41. Indeed, "Reed-Solomon coding is applied...to each of the data packets." *Id.*, 4:42-43.

Mazzoni discloses an example of determining an amount of memory required by the interleaver to interleave a first plurality of Reed-Solomon coded data bytes. In this example, the maximum downstream bit rate is set to 832x64 kbit/s and the

upstream bit rate is set to 32x64 kbit/s, which is "disturbed by an impulsive noise with a duration of 0.25 ms." Ex. 1005, 6:11-36.

To determine the number of Reed-Solomon coded data bytes, Mazzoni calculates the number of bits affected in the downstream by this 0.25ms impulsive noise by multiplying the transmitted bit rate (832x64 kbits/s) by the duration of the noise burst (0.25ms), resulting in 13,312 affected bits. *Id.*, 6:19-23. Next, Mazzoni determines the number of errored bytes by dividing the total number of affected bits by 8, the number of bits in a byte, resulting in 1,664 bytes. *Id.*

Mazzoni then determines the number of Reed-Solomon code words needed, explaining that that number is calculated by dividing the total errored bytes by "the correcting power of the Reed-Solomon code." *Id.*, 6:23-30. Mazzoni discloses "an RS(240,224)," which a POSA would have understood to mean a Reed-Solomon code that communicates 224 bytes of information using a 240-byte codeword, i.e., N=240, thus resulting in 16 *extra* bytes of redundancy, or a correcting power of 8. Ex. 1005, 6:11-26; Ex. 1003, ¶¶147-150. Thus, Mazzoni explains that the number of Reed-Solomon codewords needed to correct the errored bytes is the 1,664 errored bytes divided by 8, or 208 codewords. Ex. 1005, 6:23-26.

Mazzoni next determines the minimum size of memory required to hold the necessary number of RS codewords. Ex. 1005, 6:26-30; Ex. 1003, ¶¶151-163.

Mazzoni explains that the "size of the memory space needed to store this maximum

bit rate is then equal to Nxnrs/2, where N is the size of the Reed-Solomon code (here 240)," and nrs is the number of RS codewords. Ex. 1005, 6:23-30. Accordingly, the resulting memory space size in the downstream is equal to 24,960 bytes. *Id*.

Applying the same methodology in the upstream, where the bit rate is 32x64, the number of bytes affected by the 0.25ms noise duration is 64 bytes (32 x 64 kbits is equal to 2,048,000 bits, multiplied by 0.25ms is 512 bits affected, and divided by 8 bits per byte is 64 bytes). Ex. 1005, 6:31-35; Ex. 1003, ¶151-163. The number of Reed-Solomon codewords needed to correct the errored bytes is the 64 errored bytes divided by 8, or 8 Reed-Solomon codewords. Ex. 1003, ¶151-163. Calculating the memory space size based on Nxnrs/2, it can be determined that the minimum required upstream memory is 960 bytes, although Mazzoni erred and calculated it to be 1,920 bytes. Ex. 1003, ¶156, 162. Relying on Mazzoni's calculation, and

<sup>&</sup>lt;sup>1</sup> Mazzoni improperly applies the equation Nxnrs/2 by failing to divide the number by 2. Ex. 1003 ¶156, 162. Such a minor error does not alter the effect of Mazzoni's disclosure, as a POSA reading Mazzoni would have understood how to modify the reference, i.e., by correcting a single math error applying the correctly disclosed equations, to determine the overall requisite memory between the upstream and downstream. *See Enplas Display Device Corp. v. Seoul Semiconductor Co.*, 909 F.3d 398, 405 (Fed. Cir. 2008); *Apple Inc v. Corephotonics, Ltd.*, 861 F. App'x 443,

adding the required memory from the downstream and the upstream, Mazzoni determines that the "minimum size of the memory MM is therefore 26,880 bytes." Ex. 1005, 6:29-30.

Finally, to determine the minimum amount of memory required by the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes, Mazzoni explains that it is necessary to determine the parameters I, I', M, and M'. Ex. 1005, 6:37-38; Ex. 1003, ¶151-163. Mazzoni states that "parameters I, M, I' and M'...define the sizes of the respective memory spaces assigned to the interleaving means and to the deinterleaving means." Ex. 1005, 5:21-27. Mazzoni explains that "the size of the first memory space [ESM1]...is equal to  $I\times(I-1)\times M/2$ ." Id., 6:38-41. Likewise, "the size of the second memory space ESM2...is equal to I'×(I'-1)×M'/2." Id., 6:41-44. Mazzoni therefore explains that because I×(I-1)×M/2 must be equal to the calculated downlink memory of 24,960 bytes, "it is possible to choose [parameters] I=40 and M=32." *Id.*, 6:45-48. Likewise, because I'×(I'-1)×M'/2 must be at least equal to the calculated upstream memory of 1,920 bytes, "it is possible to choose [parameters] I'=24 and M'=7." *Id.* Because the required memory when I'=24 and M'=7 is 1,932 bytes, Mazzoni explains that the

<sup>450 (</sup>Fed. Cir. 2021) (explaining that modifications to fix an error in the prior art is permissible in an obviousness analysis).

common memory required (MM) is actually 26,892 bytes, with the ESM1 memory being equal to 24,960 bytes and the ESM2 memory being equal to 1,932 bytes. *Id*.

Mazzoni further teaches (de)interleaving Reed Solomon (RS) coded data bytes, Ex. 1005, 2:25-36 ("To make the Reed-Solomon coding more efficient, the coding means may be coupled to the interleaving means" wherein the "interleaving means may then interleave the [Reed-Solomon coded] bytes temporally by modifying the order in which they are transmitted"); *id.*, 5:7-8 (explaining that the embodiment "includes deinterleaving and Reed-Solomon decoding means"), and, as described with respect to Limitation [1.A], does so within a shared memory MM. Ex. 1003, ¶154.

Thus, Mazzoni explicitly discloses determining, at the transceiver (TO or TU), an amount of memory required by the interleaver (e.g., 24,960 bytes) to interleave a first plurality of Reed Solomon (RS) coded data bytes (e.g., at least 208 RS code words) within a shared memory (e.g., MM). *Id*.

Following the methodologies as disclosed by Mazzoni, and as described *infra* in Ground 2 Limitation [1.B], VDSL1 also discloses determining, at the transceiver (TO or TU), an amount of memory required by the interleaver to interleave a first plurality of Reed Solomon (RS) coded data bytes. *Id.* ¶164.

iv. Claim1: [1.C] allocating, in the transceiver, a first number of bytes of the shared memory to the interleaver to interleave the first plurality of Reed Solomon (RS) coded data bytes for transmission at a first data rate, wherein

### the allocated memory for the interleaver does not exceed the maximum number of bytes specified in the message;

The combination of Mazzoni and VDSL1 disclose this limitation for the same reasons as discussed in Limitations [1.A] and [1.B]. *See supra*. Specifically, Mazzoni discloses allocating, in the transceiver (TO or TU), a first number of bytes of the shared memory to the interleaver (in Mazzoni, as described *supra*, 24,690 bytes to ESM1 of shared memory MM) to interleave the first plurality of Reed Solomon (RS) coded data bytes (in Mazzoni, as described *supra*, at least 208 RS code words) for transmission at a first data rate (in Mazzoni, as described *supra*, 832x64 kbit/s in the downlink direction). Ex. 1003, ¶165.

In addition to *determining* an amount of memory required to interleave a first plurality of Reed-Solomon coded data bytes as described *supra*, Mazzoni discloses allocating the required amount to the interleaver. *Id.*, ¶166-181.

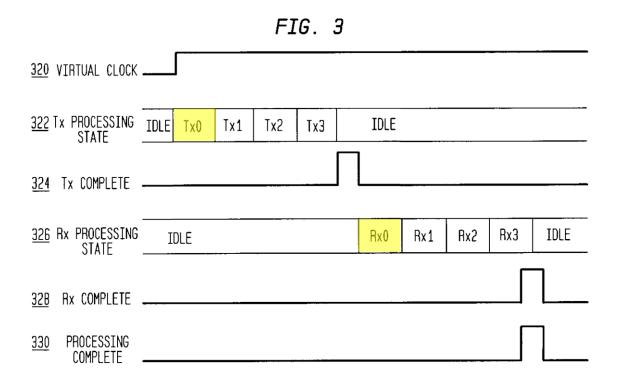

For example, Mazzoni explains that after the values of I, M, I', and M' are determined—which are the values that "define the sizes of the respective memory spaces assigned to the interleaving means and to the deinterleaving means," Ex. 1005, 5:24-27—they are "delivered by control means MCD," *id.*, 5:21-24. As depicted in Figure 3, MCD delivers parameters I, M, I', and M' to "the interleaving means MET" and "deinterleaving means MDET." *Id.*, 5:64-67; Fig. 3.

As depicted in Figure 6, "memory space ESM1 [is] assigned to the interleaving means MET," and "memory space ESM2 [is] assigned to the deinterleaving means MDET." *Id.*, 5:64-67; Fig. 6.

As to wherein the allocated memory for the interleaver does not exceed the maximum number of bytes specified in the message, and as discussed in Limitations [1.A] and [1.B], a POSA would have understood that, to implement the embodiments disclosed in Mazzoni, transmitting and receiving initialization messages setting parameters would have been necessary. Ex. 1003, ¶172-173. Regardless, VDSL1 discloses a transceiver and a message that is transmitted from the VTU-R transceiver and received by the VTU-O transceiver that explicitly specifies a maximum number of bytes of memory that are available to be allocated to an (de)interleaver at

initialization. See Ex. 1007, 132; Ex. 1003, ¶174-180; see also [1.A] and [1.B], supra.

As explained *supra*, VDSL1 discloses that in the "initialization protocol," there is a "channel analysis and exchange state" whereby the modems "agree on a contract that thoroughly defines the communication link." Ex. 1007, 111; Ex. 1003, ¶¶175-176. As depicted in excerpted Figure 56, the "channel analysis and exchange state" includes a number of messages delivered between the VTU-O and VTU-R.

Ex. 1007, 127.

As explained *supra*, the VTU-R and VTU-O begin a series of negotiations to set the parameters for downstream and upstream interleaving and deinterleaving. Ex. 1003, ¶176. As depicted in Table 75, one of those messages, O-CONTRACTn, delivers a contract descriptor message for the downstream contract and upstream contract. Ex. 1007, 129; Ex. 1003, ¶177.

Table 75: Description of O-CONTRACTn

| Field               | Field or macro-field type               |  |

|---------------------|-----------------------------------------|--|

| Message descriptor  | Message code (1 octet)                  |  |

| Downstream contract | Contract Descriptor                     |  |

| Upstream contract   | Contract Descriptor                     |  |

| EOC capacity        | Number of EOC octets per frame (1 oct   |  |

| VOC capacity        | Number of VOC octets per frame (1 octet |  |

As depicted in Table 76, the contract descriptor message for the downstream contract includes the parameters I and M for the interleaver (here, labeled "Interleaver setting"). Ex. 1007, 129; Ex. 1003, ¶178.

**Table 76: Contract Descriptor**

| Field or macro-field type | Remark In multiple of 64 kbps b15 → b8: RS overhead b7 → b0: RS codeword length In multiple of 64 kbps |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| 2 octets                  |                                                                                                        |  |  |

| 2 octets                  |                                                                                                        |  |  |

| 2 octets                  |                                                                                                        |  |  |

| 2 octets                  | b15 → b8: RS overhead<br>b7 → b0: RS codeword length                                                   |  |  |

| 2 octets                  | b15 → b8: M (see note 1)<br>b7 → b0: I                                                                 |  |  |

|                           | 2 octets 2 octets 2 octets 2 octets                                                                    |  |  |

A POSA would have understood that the message delivered by the O-CONTRACTn message, which included the I and M parameters from which the memory will be determined, was the allocation of that memory. Ex. 1003, ¶177.

Indeed, having set the parameters I and M during initialization, VDSL1 discloses, in Table 19, that the interleaving and deinterleaving memory size may be determined, and subsequently allocated, based on the parameters I and M using equation MxI×(I-1)/2. Ex. 1007, 16; Ex. 1003, ¶177.

Table 19: Characteristics of triangular, convolutional interleaver

| Parameter                  | Value                      |  |  |

|----------------------------|----------------------------|--|--|

| Interleaver block length   | I octets (I must divide N) |  |  |

| Interleaving depth D       | M x I + 1 octets           |  |  |

| De)interleaver memory size | M x I x (I-1)/2 octets     |  |  |

| End-to-end delay           | M x I x (I-1) octets       |  |  |

| Correction capability      | t/q x M x (I+1) octets     |  |  |

VDSL1 further explains that the "VTU-R sends the R-MSG2 message to transfer information about its bit allocation capabilities." Ex. 1007, 127. A POSA would have understood that the upstream contract proposed by the VTU-O must comport with the limitations of the VTU-R, including the maximum interleaver memory as communicated in R-MSG2. Ex. 1003, ¶180. As such, a POSA would have understood that the O-CONTRACTn message confirms that the allocated memory for the interleaver does not exceed the maximum number of bytes specified in the R-MSG2 message. *Id*.

The combination of Mazzoni and VDSL1 thus also discloses wherein the allocated memory for the interleaver (in VDSL1, set by message O-CONTRACTn) does not exceed the maximum number of bytes specified in the message (in VDSL1, set by message R-MSG2). Ex. 1003, ¶181.

v. Claim 1: [1.D] allocating, in the transceiver, a second number of bytes of the shared memory to a deinterleaver to deinterleave a second plurality of RS coded data bytes received at a second data rate; and

Mazzoni discloses this limitation for the same reasons as discussed in Limitation [1.C]. Ex. 1003, ¶182. Particularly, Mazzoni discloses a "control means MCD," Ex. 1005, 5:21-24, that delivers parameters I, M, I', and M' to both "the interleaving means MET" and "deinterleaving means MDET," id., 5:64-67; Fig. 3. Also, "memory space ESM1 [is] assigned to the interleaving means MET," and "memory space ESM2 [is] assigned to the deinterleaving means MDET." Id., 5:64-67; Fig. 6.

Mazzoni thus discloses allocating, in the transceiver (TO or TU), a second number of bytes of the shared memory to a deinterleaver (in Mazzoni, as described *supra*, 1,932 bytes to ESM2 of shared memory MM) to deinterleave a second plurality of RS coded data bytes (in Mazzoni, as described *supra*, at least 8 RS code words) received at a second data rate (in Mazzoni, as described *supra*, 32x64 kbit/s in the uplink direction). Ex. 1003, ¶¶182-184.