UNITED STATES PATENT AND TRADEMARK OFFICE

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

SAMSUNG ELECTRONICS CO., LTD.,

SAMSUNG ELECTRONICS AMERICA, INC., AND

QUALCOMM INCORPORATED,

Petitioner

v.

DAEDALUS PRIME LLC, Patent Owner.

DECLARATION OF TREVOR MUDGE IN SUPPORT OF PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 8,775,833

| I.    | INT | RODUCTION                                                       | 1  |

|-------|-----|-----------------------------------------------------------------|----|

|       | A.  | Qualifications                                                  | 1  |

|       | B.  | Materials Considered                                            | 3  |

| II.   | LEG | AL STANDARDS                                                    | 4  |

|       | A.  | Anticipation                                                    | 5  |

|       | B.  | Obviousness                                                     | 6  |

|       | C.  | Level of Ordinary Skill in the Art                              | 9  |

|       | D.  | Claim Construction                                              | 10 |

| III.  | SUM | IMARY OF GROUNDS                                                | 11 |

| IV.   | THE | '833 PATENT                                                     | 12 |

|       | A.  | Overview of the '833 Patent                                     | 12 |

|       | B.  | Prosecution History of the '833 Patent                          | 15 |

| V.    | TEC | HNOLOGY BACKGROUND                                              | 15 |

|       | A.  | Power, voltage, and frequency control approaches                | 17 |

|       | B.  | Multi-core processing approaches                                | 17 |

|       | C.  | NorthBridge – SouthBridge Architecture                          | 18 |

| VI.   | THE | PRIOR ART IN THE APPLIED INVALIDITY GROUNDS                     | 19 |

|       | A.  | Finkelstein                                                     | 19 |

|       | B.  | Conroy                                                          | 21 |

|       | C.  | Nussbaum                                                        | 23 |

|       | D.  | Bose                                                            | 25 |

| VII.  | CLA | IM CONSTRUCTION                                                 | 26 |

| VIII. |     | AILED EXPLANATION OF THE UNPATENTABILITY OUNDS                  | 27 |

|       | A.  | Ground 1: Claims 1-5 and 7 are rendered obvious by Finkelstein. | 27 |

|       |     | 1. Independent claim 1                                          | 27 |

|       |     | a. Element 1[pre]: A processor comprising:                      | 27 |

|    | b.   | Element I[A]: a first domain and a second domain, each of the first and second domains to operate at an independent voltage and frequency;                                                                                                                                                                                               | 28 |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | c.   | Element 1[B]: a memory controller coupled to the first and second domains;                                                                                                                                                                                                                                                               | 31 |

|    | d.   | Element 1[C]: at least one interface; and                                                                                                                                                                                                                                                                                                | 33 |

|    | e.   | Element 1[D.i]: first logic to dynamically allocate a power budget for the processor between the first and second domains at run time                                                                                                                                                                                                    | 35 |

|    | f.   | Element 1[D.ii]: according to a first sharing policy value for the first domain and a second sharing policy value for the second domain, the first and second sharing policy values controllable by user-level software.                                                                                                                 | 27 |

| 2  | Ъ    |                                                                                                                                                                                                                                                                                                                                          |    |

| 2. | Depe | ndent claims 2-5 and 7                                                                                                                                                                                                                                                                                                                   | 40 |

|    | a.   | Claim 2: The processor of claim 1, wherein the first logic is to determine a portion of the power budget to allocate to the first domain based on the first sharing policy value.                                                                                                                                                        | 40 |

|    | b.   | Claim 3: The processor of claim 1, wherein the first logic is to dynamically allocate the power budget further according to a first minimum reservation value for the first domain and a second minimum reservation value for the second domain, the first and second minimum reservation values controllable by the user-level software | 41 |

|    | c.   | Claim 4: The processor of claim 3, wherein the first logic is to provide at least a first portion of the power budget to the first domain, the first portion corresponding to the first minimum reservation value.                                                                                                                       | 43 |

|    |    | d.   | Claim 5: The processor of claim 1, wherein the first logic is to determine the power budget for a current time interval based at least in part on a power budget carried forward from a previous time interval, a power consumed in the previous time interval, and a power budget decay value.                       | 44 |

|----|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |    | e.   | Claim 7: The processor of claim 1, wherein the first logic is to dynamically allocate substantially all of the power budget to the first domain for a first workload, and to dynamically allocate substantially all of the power budget to the second domain for a second workload executed after the first workload. | 46 |

| B. |    |      | Claim 7 is rendered obvious by Finkelstein in further nroy                                                                                                                                                                                                                                                            | 49 |

|    | 1. | Depe | ndent claim 7                                                                                                                                                                                                                                                                                                         | 49 |

|    |    | a.   | Claim 7: The processor of claim 1, wherein the first logic is to dynamically allocate substantially all of the power budget to the first domain for a first workload, and to dynamically allocate substantially all of the power budget to the second domain for a second workload executed after the first workload. | 49 |

| C. |    |      | Claims 13-15 and 17-18 are rendered obvious by                                                                                                                                                                                                                                                                        | 51 |

|    | 1  |      |                                                                                                                                                                                                                                                                                                                       | 51 |

|    | 1. | a.   | Element 13[Pre]: A system comprising:                                                                                                                                                                                                                                                                                 |    |

|    |    | b.   | Element 13[A.i]: a multicore processor having a first domain including a plurality of cores, a second domain including a graphics engine, and                                                                                                                                                                         |    |

|    |    | c.   | Element 13[A.ii(1)]: a third domain including system agent circuitry,                                                                                                                                                                                                                                                 | 55 |

|    |    | d.   | Element 13[A.ii(2)]: the third domain to operate at a fixed power budget and                                                                                                                                                                                                                                          | 58 |

|    | e.    | Element 13[A.ii(3)]: including a power sharing logic to dynamically allocate a variable power budget between the first and second domains59                                                                                                                                                                                                                                                      |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | f.    | Element 13[A.ii(4)]: based at least in part on a first power sharing value for the first domain stored in a first storage and a second power sharing value for the second domain stored in a second storage; and61                                                                                                                                                                               |

|    | g.    | Element 13[B]: a dynamic random access memory (DRAM) coupled to the multicore processor63                                                                                                                                                                                                                                                                                                        |

| 2. | Deper | ndent claims 14-15 and 17-1864                                                                                                                                                                                                                                                                                                                                                                   |

|    | a.    | Claim 14: The system of claim 13, wherein the power sharing logic to determine the variable power budget for a current time interval and to allocate a first portion of the variable power budget to the first domain according to the first power sharing value, and to allocate a second portion of the variable power budget to the second domain according to the second power sharing value |

|    | b.    | Claim 15: The system of claim 14, wherein the power sharing logic is to dynamically allocate substantially all of the variable power budget to the first domain for a first workload, and to dynamically allocate substantially all of the variable power budget to the second domain for a second workload executed after the first workload65                                                  |

|    | c.    | Claim 17: The system of claim 14, wherein the power sharing logic is to further allocate the first portion of the variable power budget according to a first minimum reservation value for the first domain and allocate the second portion of the variable power budget according to a second minimum reservation value for the second domain68                                                 |

|    | d.    | Claim 18: The system of claim 14, wherein the power sharing logic is to further allocate the variable power budget according to a preference value, the preference value to favor the second domain over the first domain                                                                                                                                                                        |

| D. |    | Ground 4: Claim 16 is rendered obvious by Nussbaum in view of Bose |                                                                                                                                                                                                                                                                                                                        |    |  |  |  |

|----|----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

|    | 1. | Depe                                                               | endent claim 16                                                                                                                                                                                                                                                                                                        | 72 |  |  |  |

|    |    | a.                                                                 | Claim 16: The system of claim 14, wherein the power sharing logic is to increment the first power sharing value when a request for a higher frequency for the first domain is not granted, and to increment the second power sharing value when a request for a higher frequency for the second domain is not granted. | 72 |  |  |  |

| E. |    |                                                                    | Claims 13-15 and 17-18 are rendered obvious by                                                                                                                                                                                                                                                                         | 76 |  |  |  |

|    | 1. | •                                                                  | pendent claim 13                                                                                                                                                                                                                                                                                                       |    |  |  |  |

|    |    | a.                                                                 | Element 13[Pre]: A system comprising:                                                                                                                                                                                                                                                                                  |    |  |  |  |

|    |    | b.                                                                 | Element 13[A.i]: a multicore processor having a first domain including a plurality of cores, a second domain including a graphics engine, and                                                                                                                                                                          | 76 |  |  |  |

|    |    | c.                                                                 | Element 13[A.ii(1)]: a third domain including system agent circuitry,                                                                                                                                                                                                                                                  | 80 |  |  |  |

|    |    | d.                                                                 | Element 13[A.ii(2)]: the third domain to operate at a fixed power budget and                                                                                                                                                                                                                                           | 82 |  |  |  |

|    |    | e.                                                                 | Element 13[A.ii(3)]: including a power sharing logic to dynamically allocate a variable power budget between the first and second domains                                                                                                                                                                              | 82 |  |  |  |

|    |    | f.                                                                 | Element 13[A.ii(4)]: based at least in part on a first power sharing value for the first domain stored in a first storage and a second power sharing value for the second domain stored in a second storage; and                                                                                                       |    |  |  |  |

|    |    | g.                                                                 | Element 13[B]: a dynamic random access memory (DRAM) coupled to the multicore processor                                                                                                                                                                                                                                | 87 |  |  |  |

|    | 2. | Depe                                                               | endent claims 14-15 and 17-18                                                                                                                                                                                                                                                                                          | 88 |  |  |  |

|    | a.   | power sharing logic to determine the variable power budget for a current time interval and to allocate a first portion of the variable power budget to the first domain according to the first power sharing value, and to allocate a second portion of the variable power budget to the second domain according to the second power sharing value |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | b.   | Claim 15: The system of claim 14, wherein the power sharing logic is to dynamically allocate substantially all of the variable power budget to the first domain for a first workload, and to dynamically allocate substantially all of the variable power budget to the second domain for a second workload executed after the first workload89    |

|    | c.   | Claim 17: The system of claim 14, wherein the power sharing logic is to further allocate the first portion of the variable power budget according to a first minimum reservation value for the first domain and allocate the second portion of the variable power budget according to a second minimum reservation value for the second domain90   |

|    | d.   | Claim 18: The system of claim 14, wherein the power sharing logic is to further allocate the variable power budget according to a preference value, the preference value to favor the second domain over the first domain                                                                                                                          |

|    |      | Claim 16 is rendered obvious by Conroy in view of                                                                                                                                                                                                                                                                                                  |

| 1. | Depe | ndent claim 1692                                                                                                                                                                                                                                                                                                                                   |

|    | a.   | Claim 16: The system of claim 14, wherein the power sharing logic is to increment the first power sharing value when a request for a higher frequency for the first domain is not granted, and to increment the second power sharing value when a request for a higher frequency for the second domain is not granted                              |

| G. |    |       | Claims 1-5, 7, 13-15, and 17-18 are rendered obvious in view of Finkelstein                                                                                                                                                                                                                                                              | 94   |

|----|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | 1. | of Co | OSITA would be motivated to combine the teachings onroy and Finkelstein, and would have a reasonable ctation of success in doing so.                                                                                                                                                                                                     | 94   |

|    | 2. | Indep | pendent claim 1                                                                                                                                                                                                                                                                                                                          | 96   |

|    |    | a.    | Element 1[Pre]: A processor comprising:                                                                                                                                                                                                                                                                                                  | 96   |

|    |    | b.    | Element 1[A]: a first domain and a second domain, each of the first and second domains to operate at an independent voltage and frequency;                                                                                                                                                                                               | 98   |

|    |    | c.    | Element 1[B]: a memory controller coupled to the first and second domains;                                                                                                                                                                                                                                                               | .102 |

|    |    | d.    | Element 1[C]: at least one interface; and                                                                                                                                                                                                                                                                                                | .105 |

|    |    | e.    | Element 1[D.i]: first logic to dynamically allocate a power budget for the processor between the first and second domains at run time                                                                                                                                                                                                    | .106 |

|    |    | f.    | Element 1[D.ii]: according to a first sharing policy value for the first domain and a second sharing policy value for the second domain, the first and second sharing policy values controllable by user-level software.                                                                                                                 | .107 |

|    | 3. | Depe  | endent claims 2-5 and 7                                                                                                                                                                                                                                                                                                                  | .109 |

|    |    | a.    | Claim 2: The processor of claim 1, wherein the first logic is to determine a portion of the power budget to allocate to the first domain based on the first sharing policy value.                                                                                                                                                        | .109 |

|    |    | b.    | Claim 3: The processor of claim 1, wherein the first logic is to dynamically allocate the power budget further according to a first minimum reservation value for the first domain and a second minimum reservation value for the second domain, the first and second minimum reservation values controllable by the user-level software | .110 |

|    | c.    | first logic is to provide at least a first portion of the power budget to the first domain, the first portion corresponding to the first minimum reservation value                                                                                                                                                        | 1 |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | d.    | Claim 5: The processor of claim 1, wherein the first logic is to determine the power budget for a current time interval based at least in part on a power budget carried forward from a previous time interval, a power consumed in the previous time interval, and a power budget decay value                            | 2 |

|    | e.    | Claim 7: The processor of claim 1, wherein the first logic is to dynamically allocate substantially all of the power budget to the first domain for a first workload, and to dynamically allocate substantially all of the power budget to the second domain for a second workload executed after the first workload.  11 | 4 |

| 4. | Indep | pendent claim 1311                                                                                                                                                                                                                                                                                                        | 4 |

|    | a.    | Element 13[Pre]: A system comprising:11                                                                                                                                                                                                                                                                                   | 4 |

|    | b.    | Element 13[A.i]: a multicore processor having a first domain including a plurality of cores, a second domain including a graphics engine, and11                                                                                                                                                                           | 4 |

|    | c.    | Element 13[A.ii(1)]: a third domain including system agent circuitry,11                                                                                                                                                                                                                                                   | 4 |

|    | d.    | Element 13[A.ii(2)]: the third domain to operate at a fixed power budget and11                                                                                                                                                                                                                                            | 4 |

|    | e.    | Element 13[A.ii(3)]: including a power sharing logic to dynamically allocate a variable power budget between the first and second domains11                                                                                                                                                                               | 5 |

|    | f.    | Element 13[A.ii(4)]: based at least in part on a first power sharing value for the first domain stored in a first storage and a second power sharing value for the second domain stored in a second storage; and11                                                                                                        | 5 |

|    | g.    | Element 13[B]: a dynamic random access memory (DRAM) coupled to the multicore processor11                                                                                                                                                                                                                                 | 5 |

| 5.     | Dep   | endent claims 14-15 and 17-1811:                                                                                                                                                                                                                                                                                                                                                                 | 5 |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|        | a.    | Claim 14: The system of claim 13, wherein the power sharing logic to determine the variable power budget for a current time interval and to allocate a first portion of the variable power budget to the first domain according to the first power sharing value, and to allocate a second portion of the variable power budget to the second domain according to the second power sharing value | 5 |

|        | b.    | Claim 15: The system of claim 14, wherein the power sharing logic is to dynamically allocate substantially all of the variable power budget to the first domain for a first workload, and to dynamically allocate substantially all of the variable power budget to the second domain for a second workload executed after the first workload11                                                  | 6 |

|        | c.    | Claim 17: The system of claim 14, wherein the power sharing logic is to further allocate the first portion of the variable power budget according to a first minimum reservation value for the first domain and allocate the second portion of the variable power budget according to a second minimum reservation value for the second domain110                                                | 6 |

|        | d.    | Claim 18: The system of claim 14, wherein the power sharing logic is to further allocate the variable power budget according to a preference value, the preference value to favor the second domain over the first domain                                                                                                                                                                        | 6 |

| CONCLU | SION. | 110                                                                                                                                                                                                                                                                                                                                                                                              | 6 |

IX.

### I. INTRODUCTION

- 1. I have been retained by Samsung Electronics Co., Ltd. and Samsung Electronics America, Inc. (collectively, "Samsung" or "Petitioner"), as an independent expert in this proceeding before the Patent Trial and Appeal Board ("PTAB" or "Board"). I understand that Samsung is requesting that the Board institute an *inter partes* review ("IPR") proceeding of U.S. Patent No. 8,775,833 ("the '833 Patent") (Ex-1001), currently assigned to Daedalus Prime LLC ("Patent Owner" or "PO").

- 2. I am not and have never been an employee of Samsung. I am being compensated at my usual and customary rate of \$600 per hour. No part of my compensation depends on the outcome of this proceeding, and I have no other interest in this proceeding.

- 3. I have been asked to provide my independent analysis of the '833 Patent in light of the prior art publications cited below. I have also been asked to consider the state of the art and prior art available as of September 6, 2011. Based on the prior art discussed in this declaration, it is my opinion that Claims 1-5, 7, and 13-18 of the '833 Patent are unpatentable for the reasons provided below.

## A. Qualifications

4. I am currently a the Bredt Family Professor of Computer Science and Engineering at the University of Michigan, Ann Arbor. All of my opinions stated in

this declaration are based on my own personal knowledge and professional judgment. In forming my opinions, I have relied on my over 45 years of research, academic, industry, and consulting engineering experience in IC (integrated circuit) processing, semiconductor devices, and computer architecture with an emphasis on power and energy control.

- 5. I am over 18 years of age and, if I am called upon to do so, I would be competent to testify as to the matters set forth herein. I understand that a copy of my current curriculum vitae, which details my education and professional and academic experience, is being submitted by Petitioner as Exhibit 1003. The following provides an overview of some of my experience that is relevant to the matters set forth in this declaration.

- 6. I received the Ph.D. in Computer Science from the University of Illinois, Urbana. I am the Bredt Family Professor of Computer Science and Engineering at the University. I am the author of numerous papers on computer architecture, programming languages, VLSI design, and computer vision. I have chaired 57 Ph.D. theses in these areas. In 2014 I received the ACM/IEEE CS Eckert-Mauchly Award for "pioneering contributions to low-power computer architecture and its interaction with technology." This is known as the computer architecture community's most prestigious award. I also received the University of Illinois

Distinguished Alumni Award. I am a Life Fellow of the IEEE, a Fellow of the ACM, and a member of the IET and the British Computer Society.

7. Based on my experience and education, I believe that I am qualified to opine as to the knowledge and level of skill of one of ordinary skill in the art at the time of the alleged invention of the '833 Patent, as well as the state of the art at that time.

## **B.** Materials Considered

8. In forming my opinions, I have reviewed the following documents:<sup>1</sup>

| Ex-1001 | U.S. Patent No. 8,775,833                                          |

|---------|--------------------------------------------------------------------|

| Ex-1002 | Declaration of Dr. Trevor Mudge                                    |

| Ex-1003 | Curriculum Vitae of Dr. Trevor Mudge                               |

| Ex-1004 | Prosecution History of U.S. Patent No. 8,775,833                   |

| Ex-1005 | U.S. Published Patent Application No. 2010/0115304 ("Finkelstein") |

| Ex-1006 | U.S. Published Patent Application No. 2007/0049133 ("Conroy")      |

| Ex-1007 | U.S. Published Patent Application No. 2011/0022356 ("Nussbaum")    |

| Ex-1008 | U.S. Published Patent Application No. 2009/0089602 ("Bose")        |

| Ex-1009 | INTENTIONALLY LEFT BLANK                                           |

| Ex-1010 | INTENTIONALLY LEFT BLANK                                           |

| Ex-1011 | INTENTIONALLY LEFT BLANK                                           |

| Ex-1012 | INTENTIONALLY LEFT BLANK                                           |

<sup>&</sup>lt;sup>1</sup> Four-digit pin citations that begin with 0 are to the branded numbers added by Samsung in the bottom right corner of the exhibits. All other pin citations are to original page, column, paragraph, or line numbers.

| Ex-1013 | INTENTIONALLY LEFT BLANK                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------|

| Ex-1014 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1015 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1016 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1017 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1018 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1019 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1020 | Claim Mapping Table                                                                                        |

| Ex-1021 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1022 | INTENTIONALLY LEFT BLANK                                                                                   |

| Ex-1023 | U.S. Patent No. 7,263,457 ("White")                                                                        |

| Ex-1024 | U.S. Patent No. 8,438,416 ("Kocev")                                                                        |

| Ex-1025 | U.S. Patent No. 8,984,523 ("Vajda")                                                                        |

| Ex-1026 | U.S. Patent No. 7,779,276 ("Bolan")                                                                        |

| Ex-1027 | Selected pages of Stefanos Kaxiras et al., Computer Architecture<br>Techniques for Power-Efficiency (2008) |

| Ex-1028 | U.S. Published Patent Application No. 2010/0162006 ("Therien")                                             |

# II. LEGAL STANDARDS

9. In forming my opinions and considering the subject matter of the '833 Patent and its claim in light of the prior art, I am relying on certain legal principles that counsel in this case explained to me. My understanding of these concepts is summarized below.

10. I understand that earlier publications and patents may act to render a patent unpatentable for one of two reasons: (1) anticipation, and (2) obviousness.

# A. Anticipation

- 11. It is my understanding that the claims of a patent are anticipated by a prior art reference if each and every element of the claim is found either explicitly or inherently in the reference. I understand that inherency requires a showing that the missing descriptive matter in the claim is necessarily present in the allegedly anticipating reference, and that it would have been so recognized by a person of ordinary skill in the art ("POSITA").

- 12. I understand that when a challenged claim covers several structures, either generically or as alternatives, the claim is deemed anticipated if any of the structures within the scope of the claim is found in the prior art reference.

- 13. Although anticipation typically involves the analysis of a single prior art reference, I understand that additional references may be used to show that the prior art reference has enabling disclosure (i.e., allows a POSITA to make the invention without undue experimentation), to explain the meaning of a term used in the prior art reference, and/or to show that a characteristic is inherent in the prior art reference.

### B. Obviousness

- 14. I understand that a claim is invalid as obvious if it would have been obvious to a person of ordinary skill in the art at the time the alleged invention was made. This means that even if all of the elements of the claim cannot be found in a single prior art reference that would anticipate the claim, a person of ordinary skill in the art who was aware of the prior art would have been able to come up with the claimed invention. This may be the case, for example, where the missing element represents only an insubstantial different over the prior art or a reconfiguration of a known system. I understand that in an obviousness determination, the person of ordinary skill in the art is presumed to have knowledge of all material prior art.

- 15. I understand that an obviousness analysis requires an understanding of the scope and content of the prior art, any differences between the alleged invention and the prior art, and the level of ordinary skill in evaluating the pertinent art.

- 16. I understand that when a product is available, design incentives and other market forces can prompt variations of it, either in the same field or a different one. If a person of ordinary skill in the art can implement a predictable variation, obviousness likely bars its patentability. For the same reason, if a technique has been used to improve one device and a person of ordinary skill in the art would recognize that it would improve similar devices in the same way, using the technique would have been obvious.

- 17. I understand that whether a prior art reference renders a patent claim unpatentable as obvious is determine from the perspective of a person of ordinary skill in the art at the time of the alleged invention. I have been told that there is not requirement that the prior art contain an express suggestion to combine known elements to achieve the claimed invention, but a suggestion to combine known elements to achieve the claimed invention may come from the prior art, as filtered through the knowledge of one skilled in the art. In addition, I have been told that the inferences and creative steps a person of ordinary skill in the art would employ are relevant to the determination of obviousness.

- 18. I understand that one may consider, e.g., whether (1) the change was merely the predictable result of using prior art elements according to their known functions, or whether it was the result of true inventiveness; (2) there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent; (3) the claimed innovation applies a known technique that had been used to improve a similar device or method in a similar way; (4) the claimed invention would have been obvious to try, meaning that the claimed innovation was one of a relatively small number of possible approaches to the problem with a reasonable expectation of success by those skilled in the art; (5) the invention merely substituted one known element for another known element in order to obtain predictable results; (6) the invention merely applies a known technique to

a known device, method, or product to yield predictable results; or (7) known work in one field of endeavor may have prompted variations of it for use in either the same field or a different one based on design incentives or other market forces that would have been predictable to a person of ordinary skill in the art.

- 19. I further understand that certain factors may support or rebut the obviousness of a claim. I understand that such secondary considerations include, among other things, commercial success of the patented invention, skepticism of those having ordinary skill in the art at the time of the invention, unexpected results of the invention, any long-felt but unsolved need in the art that was satisfied by the alleged invention, the failure of others to make the alleged invention, praise of the alleged invention by those having ordinary skill in the art, and copying of the alleged invention by others in the field. I understand that there must be a nexus—that is, a connection—between any such secondary considerations and the alleged invention. I also understand that contemporaneous and independent invention by others is a secondary consideration tending to show obviousness.

- 20. I am not aware of any allegations by the named inventor of the '833 Patent or any assignee of the '833 Patent that any secondary considerations tend to rebut the obviousness of the '833 Patent.

21. Additionally, I understand that in considering obviousness, it is important not to use the benefit of hindsight derived from the patent under consideration.

# C. Level of Ordinary Skill in the Art

- 22. When interpreting a patent, I understand that it is important to identify the relevant art pertaining to that patent, as well as the level of ordinary skill in that art at the time of the claimed invention. The "art" is the field of technology to which the patent is related.

- 23. I am informed and understand that the POSITA is a hypothetical person who is presumed to know the relevant prior art. I understand that the actual inventor's skill is not determinative of the level of ordinary skill. I further understand that factors that may be considered in determining level of skill include: (i) the types of problems encountered in the art; (ii) prior art solutions to those problems; (iii) the rapidity with which innovations are made; (iv) the sophistication of the technology; and (v) the educational level of active workers in the field. I understand that not all such factors may be present in every case, and one or more of them may predominate.

- 24. I understand that a POSITA is one who is presumed to be aware of all pertinent art, thinks along conventional wisdom in the art, and is a person of ordinary creativity. A POSITA would have had knowledge of circuit boards and

microcircuits, including components thereof, and related technologies as of September 6, 2011.

- 25. A person of ordinary skill in the art at the relevant time ("POSITA") would have had a bachelor's degree in electrical engineering, computer science, computer engineering, material science, physics, applied physics, or a related field, and at least two years of experience in the research, design, development, or testing of electronic circuits or components or software for controlling electronic circuits or components, or the equivalent, with additional education substituting for experience and vice versa.

- 26. Based on my education and experience, I would have, at least, met the criteria for a POSITA in September 6, 2011, and I still exceed it today.

#### **D.** Claim Construction

- 27. I understand that the United States Patent and Trademark Office interprets claim terms in an *inter partes* review proceeding under the same claim construction standard that is used in a United States federal court. I understand that under this standard, the meaning of claim terms is considered from the viewpoint of a POSITA at the time of the alleged invention.

- 28. I have been informed that claim terms are generally given their ordinary and customary meaning as understood by one of ordinary skill in the art in light of the specification and the prosecution history pertaining to the patent. I understand,

however, that claims terms are generally not limited by the embodiments described in the specification.

29. I understand that in addition to the claims, specification, and prosecution history, other evidence may be considered to ascertain the meaning of claim terms, including textbooks, encyclopedias, articles, and dictionaries. I have been informed that this other evidence is often less significant and less reliable than the claims, specification, and prosecution history.

## III. SUMMARY OF GROUNDS

30. I understand that Petitioner challenges the validity of Claims 1-5, 7, and 13-18 of the '833 Patent. In particular, I understand that Petitioner asserts the following grounds for challenging the claims of the '833 Patent:

| Ground | Summary                                                                   |

|--------|---------------------------------------------------------------------------|

| 1      | Claims 1-5 and 7 are obvious over Finkelstein (Ex-1005)                   |

| 2      | Claim 7 is obvious over Finkelstein (Ex-1005) in view of Conroy (Ex-1006) |

| 3      | Claims 13-15 and 17-18 are obvious over Nussbaum (Ex-1007)                |

| 4      | Claim 16 is obvious over Nussbaum (Ex-1007) in view of Bose (Ex-1008)     |

| Ground | Summary                                                                                            |

|--------|----------------------------------------------------------------------------------------------------|

| 5      | Claims 13-15 and 17-18 are obvious over Conroy (Ex-1006)                                           |

| 6      | Claim 16 is obvious over Conroy (Ex-1006) in view of Bose (Ex-1008)                                |

| 7      | Claims 1-5, 7, 13-15, and 17-18 are obvious over Conroy (Ex-1006) in view of Finkelstein (Ex-1005) |

## IV. THE '833 Patent

### A. Overview of the '833 Patent

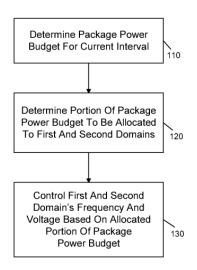

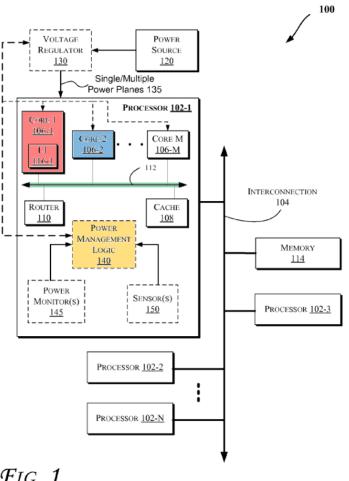

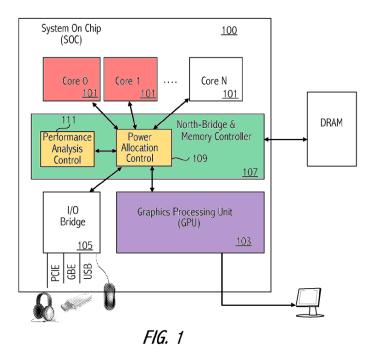

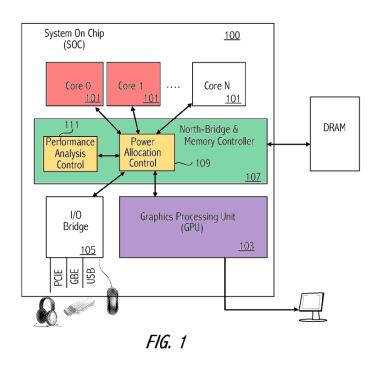

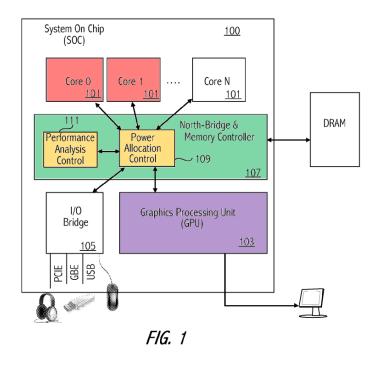

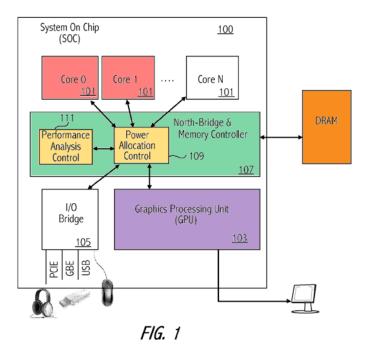

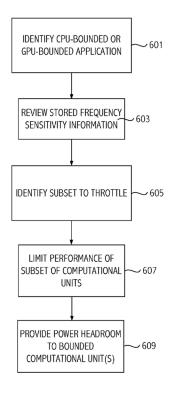

31. The '833 Patent is directed to "a power budget of a processor including multiple domains [that] can be dynamically apportioned at run time." Ex-1001, 1:56-58. Fig. 1, reproduced below, is "a flow diagram of a high level method of performing power budget allocations between multiple domains in accordance with an embodiment of the present invention." *Id.* at 30-32.

FIG. 1

Ex-1001, Fig. 1.

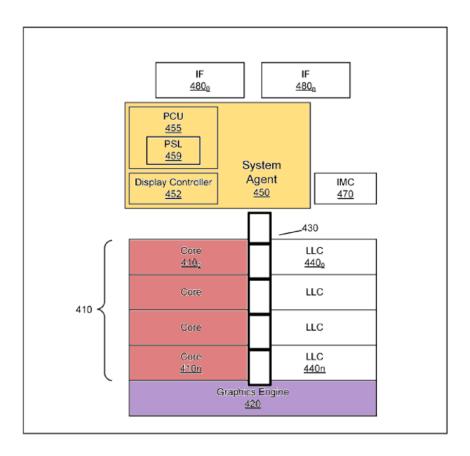

32. In particular, the '833 Patent is directed to allocating power in multicore processors that incorporate additional functional units, and the allocation is based on the respective core workload. *See* Ex-1001, 1:20-26. The patent explains that such processors can be divided into multiple "domains" (also referred to as "planes") where each domain is a "collection of hardware and/or logic that operates at the same voltage and frequency point." *Id.* at 1:56-60, 4:7-21. As shown in annotated Figure 7 below, a multidomain processor may include "a plurality of cores 410a-410n [red], a graphics domain 420 [purple] can include one or more graphics engines, and a system agent domain 450 [yellow]." *Id.* at 9:13-16.

<u>400</u>

FIG. 7

Ex-1001, Fig. 7 (annotated).

33. The '833 Patent describes how multiple domains may share a dynamically re-partitioned power budget, and "[a]s a result, a power budget or power headroom can be reallocated between cores and graphics engine when they are both integrated on the same die." Ex-1001, 3:21-26, 8:26-31, 10:4-24. The '833 Patent further explains: "a user may be provided with control, e.g., by user-level software

to enable the software to determine how package power budget is shared between different domains." *Id.* at 4:1-4.

# B. Prosecution History of the '833 Patent

- 34. I understand the '833 Patent was filed on February 28, 2013, as a continuation of U.S. patent application serial no. 13/225,677, filed on September 6, 2011.

- 35. On February 5, 2014, Applicant responded to non-final §§ 101 and 102 rejections, and amended the claims to their present scope. On February 18, 2014, the Examiner allowed the claims, and the '833 Patent issued on July 8, 2014.

- 36. I understand the prior art relied on in this Petition was not before the PTO during prosecution of the '833 Patent. Thus, I understand that the Petition presents substantially new arguments that were not considered during prosecution.

### V. TECHNOLOGY BACKGROUND

37. To provide background for the element-by-element analysis of the claims to follow, below I will present an overview of the state of the art existing at the time of the alleged invention relating to processors generally, and as it relates to multi-core devices, and power, voltage and frequency management approaches, among other relevant technology. As I will describe below from a high-level functional perspective, in the next section based on specific prior art, and then in subsequent sections on a limitation-by-limitation basis, all of these technologies and

techniques were well-known to those of ordinary skill in the art at the time of the alleged invention claimed in the '833 Patent, and a POSITA would have readily understood the combination of elements of Claim 1-5, 7, and 13-18 to have been obvious.

# A. Power, voltage, and frequency control approaches

- 38. "Limiting power consumption presents a critical issue in computing, particularly in battery powered devices such as laptop computers and cell phones. Limiting power in other computer settings—such as server farms—warehouse-sized buildings filled with Internet service providers' servers—is also important."

- 39. I wrote this in 2000/1 in two review articles, at which time the problem of power consumption was well known and starting to become a design constraint for computer designers. The source of power consumption in integrated circuits is dictated by the voltage that they require and the frequency at which they operate. Power consumption increases in proportion to the frequency at which the core, an integrated circuit, operates but increases as the square of the voltage supply.

- 40. Additionally, increasing frequency improves performance but requires that the voltage also be increased. Thus, to improve performance by increasing frequency requires a quadratic increase in voltage supply. This in turn has a translates to a significant increase in power consumption.

## B. Multi-core processing approaches

- 41. Manufacturers of processor cores, before about the turn of the century, had been able to increase performance by simply increasing frequency. Unfortunately, the fact that power increases as square of the voltage finally caught up with them and meant that increasing frequency quickly became impractical. The solution that began to emerge was to employ multiple processors to do the work of one. The reasoning was that two processors could run at half the frequency, but now the quadratic dependency on supply voltage gave a positive effect, because the voltage supply could be lowered at a quadratic rate. Thus the power consumption of two processors could actually be less than that of one fast processor.

- 42. This observation led the industry to adopt the idea of multiple processors operating at a lower frequency to replace one fast processor. In about 2005, Intel and its rivals began to perform a "right turn", to quote their promotional material, which meant they moved away from using a single fast processor and replaced it with multiple slower cores on an integrated circuit to meet power limitations, while at the same time maintaining performance. The background of the '833 Patent reflects this concept, which discusses a scenario with multiple cores, and was widely employed at the date of the patent. The multiple cores opened up further ways to control power consumption: when not needed some cores could operate at a lower performance stated or could be turned off.

## C. NorthBridge – SouthBridge Architecture

A NorthBridge is a common component of many processors. The NorthBridge may include "separate interfaces to communicate with and route communication from multiple logic cores of an integrated circuit to other sub-systems, components or peripherals external to the integrated circuit." Ex-1023. U.S. Patent No. 8,438,416, filed October 21, 2010 utilizes a NorthBridge and "is directed to a method and apparatus for function-based dynamic power control of a bridge unit, such as a north bridge unit in a computer system." Ex-1024, 2:44-46. The NorthBridge may also include "an interface to an I/O bridge (e.g., a South bridge), a memory controller, and a graphics processing unit." *Id.* at 2:57-59.

### VI. THE PRIOR ART IN THE APPLIED INVALIDITY GROUNDS

### A. Finkelstein

- 44. Finkelstein, titled "Power management for multiple processor cores," published on May 6, 2010. Ex-1005, Cover.

- 45. I understand Finkelstein is prior art under at least 35 U.S.C. § 102(b).

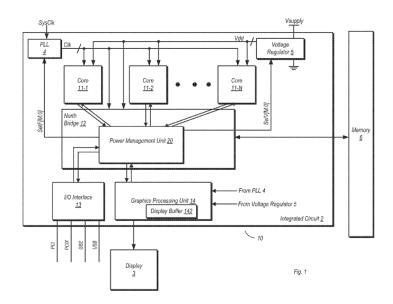

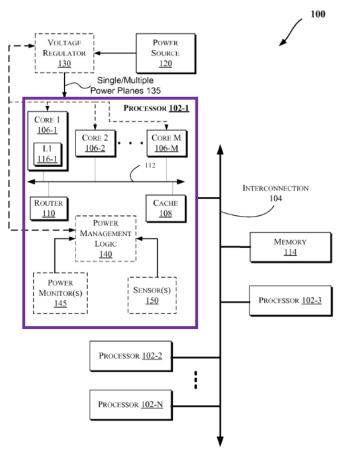

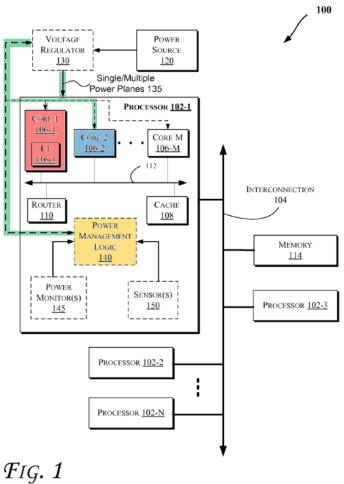

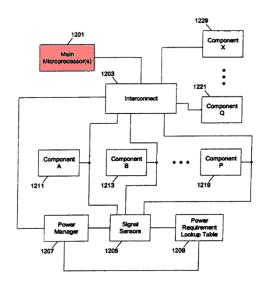

- 46. Finkelstein "relates to power management for multiple processor cores." Ex-1005 ¶1. As shown in annotated Figure 1 below, Finkelstein discloses a system that includes "one or more processors" (purple rectangle) where each processor "may include one or more processor cores" (red). *Id.* ¶¶10-11.

FIG. 1

Ex-1005, Fig. 1 (annotated).

- 47. Finkelstein explains that each processor may communicate with various other components, including memory, voltage regulator(s), and power source(s). Ex-1005 ¶¶13-14. A voltage regulator "may be coupled to a single power plane ... or to multiple power planes ... where each power plane may supply power to a different core or group of cores." *Id.* ¶14. Finkelstein's processors may further "include one or more shared and/or private caches..., buses or interconnections..., graphics and/or memory controllers..., or other components." *Id.* ¶11.

- 48. Finkelstein also discloses "a power management logic 140 [colored yellow in Figure 1, above] to control supply of power to" processor components. Ex-1005 ¶16, 24, 28-36. Finkelstein explains that power management logic 140 "may request the cores 106 to modify their operating frequency, power consumption, etc." *Id.* It may also "consider statistics ... on operating states of the cores" and "select[] technique(s) [that] may be applied to throttle or modify an operational characteristic of one or more of the cores." *Id.* ¶24. Finkelstein also discloses that "a controller budget may be defined (e.g., implemented by the logic 140)" and provides several formulae by which logic 140 may dynamically allocate the power budget between power planes. *Id.* ¶128-36. For example, Finkelstein discloses sharing an "energy budget" so that "unused processor core power" can be used for other cores that may be performing more "intensive workload." *See*, *e.g.*, *id.* ¶26.

Finkelstein further discloses that "user (or application defined) preferences" may be considered in determining power budget allocation. *Id.* ¶34; *see also id.* ¶¶29, 31.

# B. Conroy

- 49. Conroy, titled "Methods and apparatuses for dynamic power control," published on March 1, 2007. Ex-1006, Cover.

- 50. I understand Conroy is prior art under at least 35 U.S.C. § 102(b).

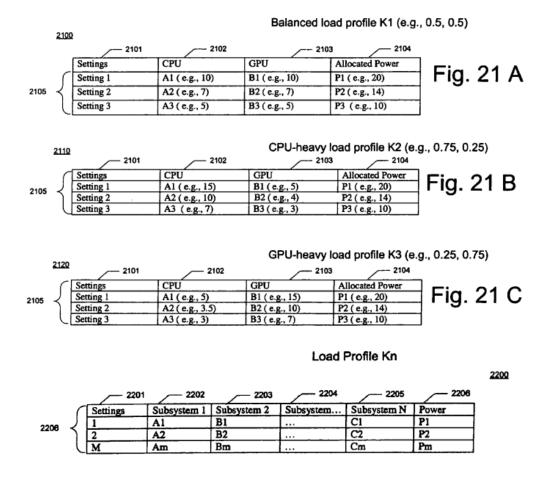

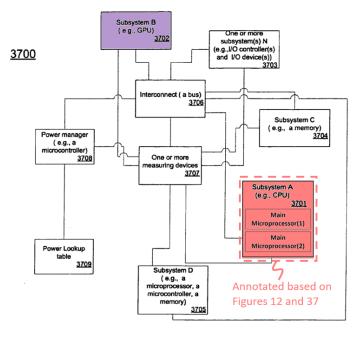

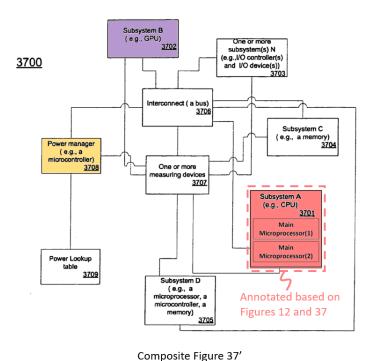

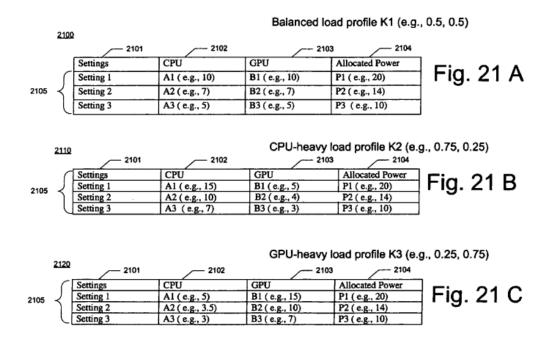

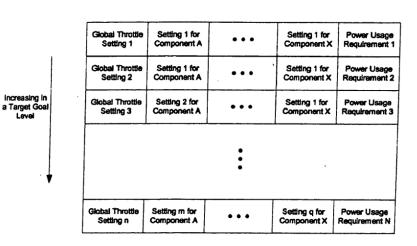

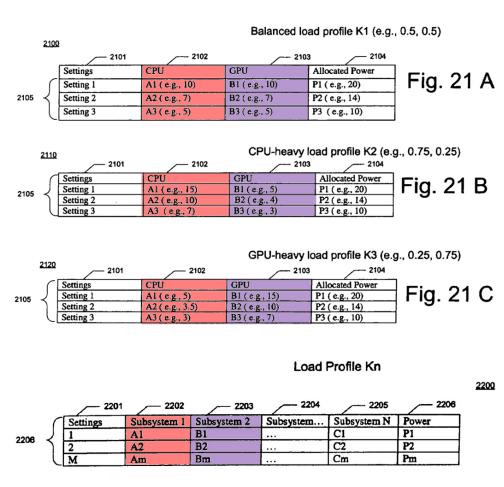

- 51. Conroy discloses "dynamically redistribut[ing] power in a [computer] system that includes a plurality of subsystems." Ex-1006, Abstract. For example, Conroy teaches identifying a "load profile of the system" and redistributing power "between the subsystems while tracking the load profile." *Id.* Conroy discloses that its "subsystems may be, for example, a central processing unit ('CPU') and a graphics processor ('GPU')," and that a "power weighting arrangement between the subsystems may be a power distribution table selected out of a plurality of power distribution tables" that describe, among other things, "the power used by each of the subsystems at various system's settings." *Id.* ¶¶5-6. Examples of power distribution tables are illustrated in Figures 21A-C and 22, copied below.

Fig. 22

Ex-1006 Figs. 21A-21C, 22.

52. Conroy's power distribution table may correspond to various power distribution profiles, including where one subsystem requires most of the power followed by another system requiring most of the power. For example, Conroy explains that during a "CPU-heavy load profile," when CPU workload is intensive, power may be distributed such that "CPU consumes about 75%, while GPU

consumes about 25% of the power allocated for the system." Ex-1006 ¶203. And, if another system, such as the GPU, is engaged in intensive workload after the CPU, "the power of the system is shifted towards GPU" such that, for example, "GPU consumes about 75%, while CPU consumes about 25% of the power allocated for the system." *Id*.

### C. Nussbaum

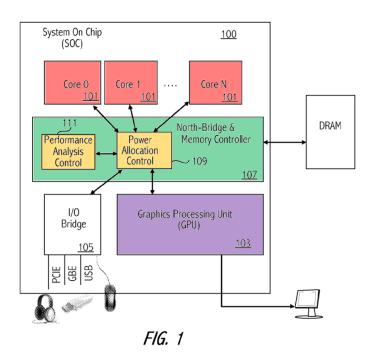

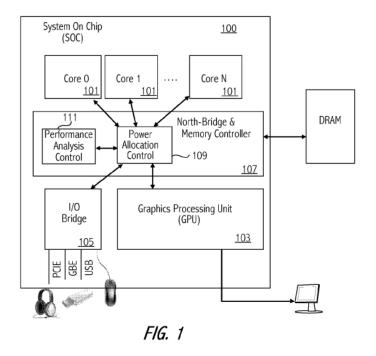

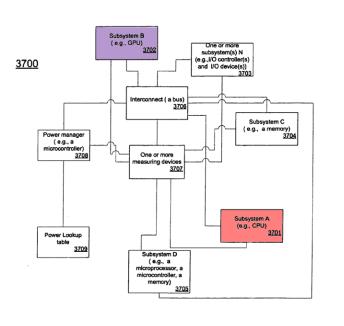

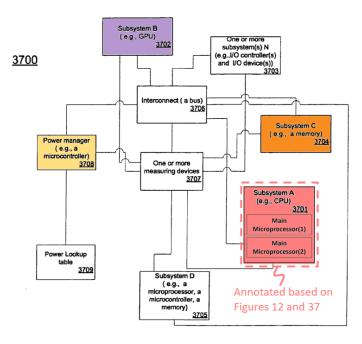

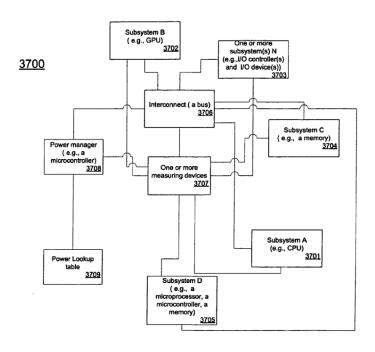

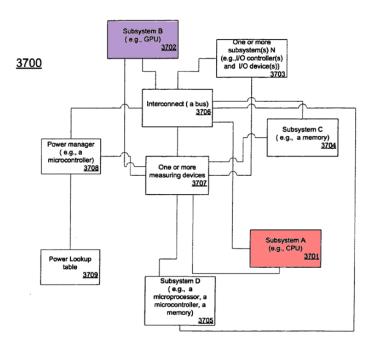

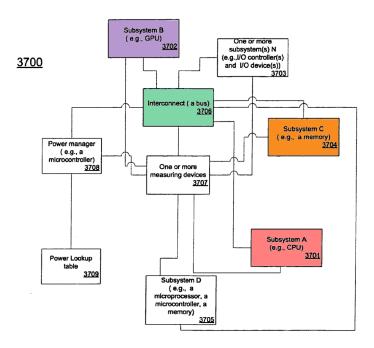

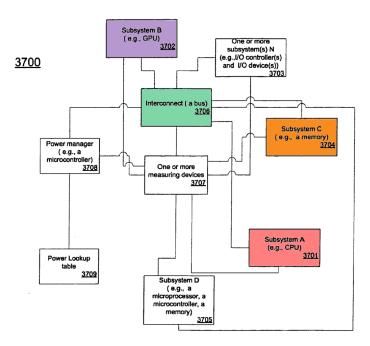

- 53. Nussbaum, titled "Determining performance sensitivities of computational units," published on January 27, 2011 from an application filed on July 24, 2009.

- 54. I understand Nussbaum is prior art under at least 35 U.S.C. §§ 102(a) and 102(e).

- 55. Nussbaum discloses power management of computational units in a "System on a Chip (SOC)" and allocation of "power headroom" to various "on-die or on-platform components." Ex-1007, Abstract, ¶20. As shown in annotated Figure 1, Nussbaum's SOC "includes multiple CPU processing cores 101" (red) operating in a first domain. *Id.* ¶20. Nussbaum's SOC also includes "GPU (Graphics Processing Unit) 103" (purple) operating in a second domain. *Id.* Furthermore, Nussbaum's SOC includes "North-Bridge & Memory Controller 107" (green) operating in a third domain, which may include "performance analysis control logic 111" and "power allocation controller 109" (yellow). *Id.* Nussbaum

explains that "performance analysis control logic 111" and "power allocation controller 109" (yellow) are used to "analyze[] performance sensitivity of the cores and other computational units" and "control[] allocation of the Thermal Design Point (TDP) power headroom to the on-die or on-platform components." *Id.* ¶20, 39.

Ex-1007, Fig. 1 (annotated).

56. Nussbaum also discloses "reallocation of the power from idle or less active components to the busy components by having more power allocated to the busy ones." Ex-1007 ¶23. Nussbaum explains that, for example, "one way to determine how to allocate power between Core0 and Core1 ... is to know which of the two cores, if any, can better exploit an increase in performance capability provided, e.g., by an increase in frequency." *Id.* ¶25. Nussbaum also explains that "performance sensitivity of each computational unit to frequency change, and/or

other change in performance capability, also referred to herein as boost sensitivity, is determined and stored on a computational unit basis." *Id*.

57. Nussbaum further discloses dynamically allocating the power budget according to whether an application is "CPU-bounded or GPU-bounded." Ex-1007 ¶47. If an application is CPU-bounded, for example, cores that are "less sensitive in terms of performance to a reduction in performance capability" are selectively throttled so that the "power headroom" can be reallocated to the computational unit(s) executing the CPU-bounded operation. *Id.* On the other hand, if an application is GPU-bounded, the "power headroom" may be reallocated to the unit(s) executing the GPU-bounded operation. *Id.*

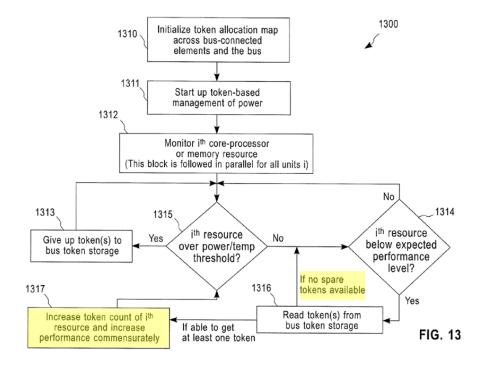

## D. Bose

- 58. Bose, titled "Method and system of peak power enforcement via autonomous token-based control and management," published on April 2, 2009 from an application filed on September 27, 2007.

- 59. I understand Bose is prior art under at least 35 U.S.C. § 102(b).

- 60. Bose discloses "power management of a system of connected components ... wherein each component is assigned a power budget as determined by a number of allocated tokens in the token allocation map." Ex-1008, Abstract. Bose utilizes a "token management unit (TMU)" to manage allocation of tokens to "token-managed units," such as "processor resources," and explains that "[e]ach

managed component, in response to its own operating conditions (as evidenced by its utilization markers) can either attempt to donate one or more token(s)" or "read (receive) one or more token(s)." *Id.* ¶¶38-39, 68. "Each token connotes a pre-specified quantum of power, and as such, the total number of tokens owned by a component determines its own power limit." *Id.* ¶68.

budget of 3 tokens for all other non-managed units (including itself), and distributes the remaining 12 tokens across the 4 managed units." Ex-1008 ¶53. Bose further discloses that if the performance level of a particular resource is "below a predefined minimum performance," a process is initiated to "try and read additional tokens from [a] centralized bus token storage ... to boost up performance" of that particular resource, e.g., "by increasing its voltage and frequency, if allowed by the system architecture." *Id.* ¶86, Fig. 13. Bose explains that if no additional tokens can be allocated to the particular resource at the moment, that particular resource can wait for its token count to be increased in the next iteration of the process. *Id.*

### VII. CLAIM CONSTRUCTION

62. I do not believe that any claim term requires explicit construction to resolve the issues presented in this Petition. I apply the plain and ordinary meaning to each claim term, as that plain and ordinary meaning would have been understood by a POSITA.

63. I reserve the right to offer opinions on any claim constructions proposed in this proceeding or to offer opinions on additional constructions in the district court.

## VIII. DETAILED EXPLANATION OF THE UNPATENTABILITY GROUNDS

- A. Ground 1: Claims 1-5 and 7 are rendered obvious by Finkelstein.

- 1. Independent claim 1

- a. Element 1[pre]: A processor comprising:

- 64. In my opinion, Finkelstein teaches the preamble of Claim 1, to the extent it is limiting.

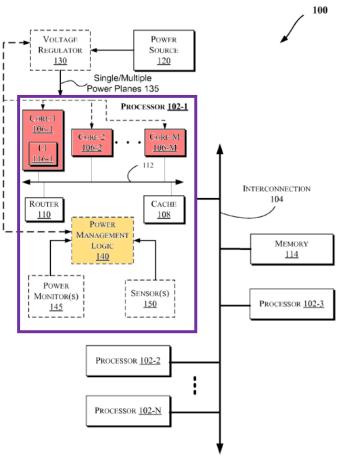

- 65. Finkelstein discloses "processors" that "have corresponding voltage regulator(s) and/or power source(s)" as well as "multiple power planes 135 (e.g., where each power plane may supply power to a different core or group of cores)." Ex-1005 ¶14; see also id. ¶¶11, 16, 24. An example of Finkelstein's processor 102-1 (purple) is shown in annotated Figure 1 below.

FIG. 1

Ex-1005, Fig. 1 (annotated).

- 66. Thus, it is my opinion that Finkelstein discloses a processor as described in the preamble.

- b. Element 1[A]: a first domain and a second domain, each of the first and second domains to operate at an independent voltage and frequency;

- 67. In my opinion, Finkelstein teaches Element 1[A].

- 68. As shown in annotated Figure 1 below, Finkelstein discloses cores in "multiple power planes 135 (e.g., where each power plane may supply power to a different core or group of cores)." Ex-1005 ¶14. A POSITA would have understood

that each "power plane" 135 corresponds to a "domain." Indeed, the '833 Patent itself refers to "domains" as "planes." Ex-1001, 4:7-21. Thus, a POSITA would have understood that a first set of processor cores, e.g., Core 1 (red) in a first power plane, is a "first domain" and another set of cores, e.g., Core 2 (blue) in a second power plane, is a "second domain."

Ex-1005, Fig. 1 (annotated).

Finkelstein further discloses that each of the first and second domains 69. operates at an independent voltage and frequency. Finkelstein uses "power management logic 140 to control supply of power to components of the processor 102 (e.g., cores 106)," and power management logic 140 (above, yellow) "may request the cores [] to modify their operating frequency, power consumption, etc." Ex-1005 ¶16; see also id. ¶31. Logic 140 can also "throttle or modify an operational characteristic of *one* or more of the cores 106 (such as an operating voltage and/or an operating frequency of *a processor core* 106)." *Id.* ¶24.<sup>2</sup> implementing Finkelstein would thus have been motivated to operate Core 1 (in a first domain) and Core 2 (in a second domain) at independent voltages and frequencies by controlling the "operational characteristic of one" of the cores such that logic 140 could modify the operating voltage and/or frequency of either Core 1 or Core 2, without affecting the operating voltage and/or frequency of the other. This independent operation would have allowed for a greater degree of control over one core, while still allowing for increased performance on the other. For example, one core that was operating too hot could be set to a lower frequency, while the other core could continue to operate at a higher frequency and performance. *Id.*; see also id. ¶¶27, 32, 39 (discussing control of power budget "per power plane"); Ex-1027 at 35-40 (describing "independent" voltage and frequency control for each core or domain).

<sup>&</sup>lt;sup>2</sup> Throughout this Declaration, all annotations and emphasis have been added, unless otherwise noted.

- 70. Finkelstein further discloses mechanisms that facilitate independent control of voltage and frequency to different domains. For example, as shown in annotated Figure 1 above, connections (green) are established between logic 140 (yellow) and Cores 1 and 2 (red and blue) through voltage regulator 130, enabling logic 140 to "request the cores [] to modify their operating frequency, power consumption, etc." Ex-1005 ¶16; see also id. ¶31. A POSITA would have understood that Finkelstein teaches operating the first and second domains at an independent voltage and frequency because it discloses fulfilling different voltage and frequency needs for different domains (e.g., the first domain containing Core 1 and the second domain containing Core 2) and discloses mechanisms that facilitate independent control of voltage and frequency to different domains.

- 71. Thus, it is my opinion that Finkelstein teaches a first domain and a second domain, each of the first and second domains to operate at an independent voltage and frequency.

- c. Element 1[B]: a memory controller coupled to the first and second domains;

- 72. In my opinion, Finkelstein teaches Element 1[B].

- 73. Finkelstein discloses that processor cores "may be implemented on a single integrated circuit (IC) chip," which in turn may include "memory controllers (such as those discussed with reference to FIGS. 6-7)." Ex-1005 ¶11. "Moreover,

various components of the processor 102-1 may communicate with the cache 108 directly, through a bus (e.g., the bus 112), *and/or a memory controller or hub*." *Id.* ¶13. It was well known that in implementations where a memory controller is used to facilitate communications between various components of processor 102-1 (including cores 106) and cache 108, each core 106 would be couple to the memory controller so that each core 106 can communicate with cache 108 through the memory controller.

74. An example of this is shown in annotated Figure 7 (referred to in the description of Figure 1), which depicts processors 702 and 704, each including "a local memory controller hub (MCH)" (green). *Id.* ¶49. Finkelstein also explains that processors 702 and 704, each including "a local memory controller hub (MCH)," may include "one or more of the cores 106, logic 140, sensor(s) 150, and/or power monitor(s) 145 of FIG. 1." *Id.* ¶49.

Ex-1005 Fig. 7 (annotated).

Thus, it is my opinion that Finkelstein teaches a memory controller 75. coupled to the first domain (e.g., Core 1) and the second domain (e.g., Core 2).

#### d. Element 1[C]: at least one interface; and

- 76. In my opinion, Finkelstein teaches Element 1[C].

- As illustrated in annotated Figure 1 below, Finkelstein discloses that 77. processor cores "may be implemented on a single integrated circuit (IC) chip," which in turn may include "buses or interconnections (such as a bus or

interconnection 112)." Ex-1005 ¶11. Finkelstein also explains that "various components of the processor 102-1" may communicate with cache 108 and router 110 through interconnection 112 (green). Id. ¶¶11-13, Fig. 1. A POSITA would have understood Finkelstein as teaching an "interface" because an "interconnection" for communications between various components of processor 102-1, cache 108, and router 110 serves as an "interface" between these components. *Id.* ¶¶10-13, 44-52. Indeed, Finkelstein itself discloses using "interfaces" to "interconnect[]" processors, memory, and input/output devices, and a POSITA would have understood to implement interconnection 112 (green) using the same or similar "interfaces." *Id.* ¶¶47-48. The '833 Patent also explains that an "interface" enables "interconnection" between the processor cores and other circuitry. Ex-1001, 9:58-60 ("Multiple interfaces ... may be present to enable interconnection between the processor and other circuitry.").

U.S. Patent No. 8,775,833 Declaration of Trevor Mudge

FIG. 1

Ex-1005 Fig. 1 (annotated).

- 78. Thus, it is my opinion that Finkelstein teaches at least one interface.

- Element 1[D.i]: first logic to dynamically allocate a e. power budget for the processor between the first and second domains at run time

- 79. In my opinion, Finkelstein teaches Element 1[D.i].

- Finkelstein discloses that "if multiple power planes [are] sharing the 80. same power source," then these planes may "share a common package power/energy budget" so that, for example, "unused processor core power" of a core in the first

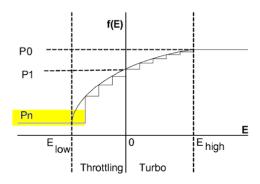

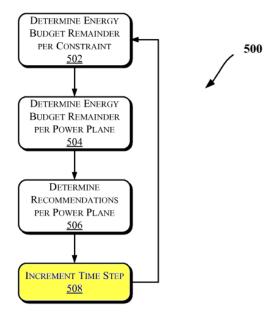

domain (e.g., Core 1) can be used for "more Graphics Effect(s) (GFX) performance in a GFX intensive workload" being performed by a core in the second domain (e.g., Core 2). Ex-1005 \( \) 26. Thus, a POSITA would have recognized that Finkelstein teaches allocating a power budget between the first and second domains "at run time," while the GFX intensive workload is being performed. Id. Moreover, Finkelstein discloses implementations in which an "unused" budget for domain i, defined as a variable  $W_{ki}E^k$ - $E_{high}^i$ , is "distributed among the rest of the power planes [domains] proportionally to their weights," defined as variables  $W_{ki}$ . Id. ¶35. A POSITA would have recognized such an allocation, where the power budget itself is a variable  $(W_{ki}E^k-E_{high}^i)$  and the variable power budget is being distributed based on variable weights  $(W_{ki})$ , as a "dynamic" allocation because the allocation can change during run-time to correspond to the then-present operating conditions. *Id.*; see also id. ¶¶ 19, 22, 24, 26. Furthermore, Finkelstein explains that its power allocation framework handles changes "on-the-fly" and takes into account a "decay component" that "corresponds to [a] window size of seconds [or] much smaller," confirming that Finkelstein allocates power "dynamically" to correspond to the thenpresent operating conditions. *Id.* ¶¶29-31; see also Section VIII.A.1.f.

81. Thus, it is my opinion that Finkelstein teaches a first logic to dynamically allocate a power budget for the processor between the first and second domains at run time.

- f. Element 1[D.ii]: according to a first sharing policy value for the first domain and a second sharing policy value for the second domain, the first and second sharing policy values controllable by user-level software.

- 82. In my opinion, Finkelstein teaches Element 1[D.ii].

- 83. Finkelstein discloses at least two complimentary approaches to dynamically allocate a power budget for the processor according to a first sharing policy value for the first domain and a second sharing policy value for the second domain, wherein the sharing policies are controllable by user-level software.

### (1) First Approach

84. Finkelstein discloses a set of energy sharing policy values for each plane "i," expressed as vectors  $W_{ki}$ , in the following equation used to determine  $E^{k,i}$ , which represents the portion of the power budget plane "i" may obtain:

$$E^{k,i} = W_{ki}E^k \tag{2}$$

Finkelstein explains that "[f]or constraint k, user (or application defined) preferences that describe how budget  $E^k$  is distributed among power planes may be determined." Ex-1005 ¶34. Finkelstein also explains that "such information may be provided as an input in the form of vectors  $W_k$  of length m, such that entry i corresponds to the portion of the budget that goes to power plane i." Id. Thus, in equation (2),  $W_{k1}$  represents a first sharing policy value for the first domain (receiving power from power plane i=1) and  $W_{k2}$  represents a second sharing policy