#### United States Patent and Trademark Office

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450

Alexandria, Virginia 22313-1450 www.uspto.gov

APPLICATION NUMBER FILING or 371(c) DATE GRP ART UNIT

FIL FEE REC'D

ATTY.DOCKET.NO

TOT CLAIMS IND

IND CLAIMS

61/374,593

08/17/2010

DW-1022P

**CONFIRMATION NO. 5805**

**FILING RECEIPT**

\*OC00000043258760\*

Date Mailed: 09/02/2010

54412 Law Offices of James E. Eakin P.O. Box 1250 Menlo Park, CA 94026

Receipt is acknowledged of this provisional patent application. It will not be examined for patentability and will become abandoned not later than twelve months after its filing date. Any correspondence concerning the application must include the following identification information: the U.S. APPLICATION NUMBER, FILING DATE, NAME OF APPLICANT, and TITLE OF INVENTION. Fees transmitted by check or draft are subject to collection. Please verify the accuracy of the data presented on this receipt. If an error is noted on this Filing Receipt, please submit a written request for a Filing Receipt Correction. Please provide a copy of this Filing Receipt with the changes noted thereon. If you received a "Notice to File Missing Parts" for this application, please submit any corrections to this Filing Receipt with your reply to the Notice. When the USPTO processes the reply to the Notice, the USPTO will generate another Filing Receipt incorporating the requested corrections

Applicant(s)

Paul LEMSON, Woodinville, WA; Shawn Patrick STAPLETON, Burnaby, CANADA; Sasa Traiko TRAJKOVIC, Burnaby, CANADA:

Power of Attorney: James Eakin--27874

If Required, Foreign Filing License Granted: 08/27/2010

The country code and number of your priority application, to be used for filing abroad under the Paris Convention,

is US 61/374,593

Projected Publication Date: None, application is not eligible for pre-grant publication

Non-Publication Request: No Early Publication Request: No

\*\* SMALL ENTITY \*\*

Title

NEUTRAL HOST ARCHITECTURE FOR A DISTRIBUTED ANTENNA SYSTEM

#### PROTECTING YOUR INVENTION OUTSIDE THE UNITED STATES

Since the rights granted by a U.S. patent extend only throughout the territory of the United States and have no effect in a foreign country, an inventor who wishes patent protection in another country must apply for a patent in a specific country or in regional patent offices. Applicants may wish to consider the filing of an international application under the Patent Cooperation Treaty (PCT). An international (PCT) application generally has the same effect as a regular national patent application in each PCT-member country. The PCT process **simplifies** the filing page 1 of 3

age 1015

of patent applications on the same invention in member countries, but **does not result** in a grant of "an international patent" and does not eliminate the need of applicants to file additional documents and fees in countries where patent protection is desired.

Almost every country has its own patent law, and a person desiring a patent in a particular country must make an application for patent in that country in accordance with its particular laws. Since the laws of many countries differ in various respects from the patent law of the United States, applicants are advised to seek guidance from specific foreign countries to ensure that patent rights are not lost prematurely.

Applicants also are advised that in the case of inventions made in the United States, the Director of the USPTO must issue a license before applicants can apply for a patent in a foreign country. The filing of a U.S. patent application serves as a request for a foreign filing license. The application's filing receipt contains further information and guidance as to the status of applicant's license for foreign filing.

Applicants may wish to consult the USPTO booklet, "General Information Concerning Patents" (specifically, the section entitled "Treaties and Foreign Patents") for more information on timeframes and deadlines for filing foreign patent applications. The guide is available either by contacting the USPTO Contact Center at 800-786-9199, or it can be viewed on the USPTO website at http://www.uspto.gov/web/offices/pac/doc/general/index.html.

For information on preventing theft of your intellectual property (patents, trademarks and copyrights), you may wish to consult the U.S. Government website, http://www.stopfakes.gov. Part of a Department of Commerce initiative, this website includes self-help "toolkits" giving innovators guidance on how to protect intellectual property in specific countries such as China, Korea and Mexico. For questions regarding patent enforcement issues, applicants may call the U.S. Government hotline at 1-866-999-HALT (1-866-999-4158).

#### LICENSE FOR FOREIGN FILING UNDER

Title 35. United States Code. Section 184

Title 37, Code of Federal Regulations, 5.11 & 5.15

#### **GRANTED**

The applicant has been granted a license under 35 U.S.C. 184, if the phrase "IF REQUIRED, FOREIGN FILING LICENSE GRANTED" followed by a date appears on this form. Such licenses are issued in all applications where the conditions for issuance of a license have been met, regardless of whether or not a license may be required as set forth in 37 CFR 5.15. The scope and limitations of this license are set forth in 37 CFR 5.15(a) unless an earlier license has been issued under 37 CFR 5.15(b). The license is subject to revocation upon written notification. The date indicated is the effective date of the license, unless an earlier license of similar scope has been granted under 37 CFR 5.13 or 5.14.

This license is to be retained by the licensee and may be used at any time on or after the effective date thereof unless it is revoked. This license is automatically transferred to any related applications(s) filed under 37 CFR 1.53(d). This license is not retroactive.

The grant of a license does not in any way lessen the responsibility of a licensee for the security of the subject matter as imposed by any Government contract or the provisions of existing laws relating to espionage and the national security or the export of technical data. Licensees should apprise themselves of current regulations especially with respect to certain countries, of other agencies, particularly the Office of Defense Trade Controls, Department of page 2 of 3

State (with respect to Arms, Munitions and Implements of War (22 CFR 121-128)); the Bureau of Industry and Security, Department of Commerce (15 CFR parts 730-774); the Office of Foreign AssetsControl, Department of Treasury (31 CFR Parts 500+) and the Department of Energy.

#### **NOT GRANTED**

No license under 35 U.S.C. 184 has been granted at this time, if the phrase "IF REQUIRED, FOREIGN FILING LICENSE GRANTED" DOES NOT appear on this form. Applicant may still petition for a license under 37 CFR 5.12, if a license is desired before the expiration of 6 months from the filing date of the application. If 6 months has lapsed from the filing date of this application and the licensee has not received any indication of a secrecy order under 35 U.S.C. 181, the licensee may foreign file the application pursuant to 37 CFR 5.15(b).

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

#### **PROVISIONAL APPLICATION**

5 FOR

#### **UNITED STATES PATENT**

**FOR**

10

#### NEUTRAL HOST ARCHITECTURE FOR A DISTRIBUTED ANTENNA SYSTEM

#### **INVENTORS**

15

Paul Lemson, Citizen of the United States

Shawn Patrick Stapleton, Citizen of Canada

Sasa Trajkovic, Citizen of Canada

20

### **SPECIFICATION**

#### **RELATED APPLICATIONS**

25

#### **FIELD OF THE INVENTION**

**[001]** The present invention generally relates to wireless communication systems employing Distributed Antenna Systems (DAS). More specifically, the present invention relates to a DAS which is part of a distributed wireless network

base station in which all radio-related functions that provide network coverage and/or capacity for a given area are contained in a small single unit that can be deployed in a location remote from the remaining distributed wireless network base station unit or units which are not performing radio-related functions. Multimode radios capable of operating according to GSM, HSPA, LTE, TD-SCDMA, UMTS and WiMAX standards with advanced software configurability are features in the deployment of more flexible and energy-efficient radio networks. The present invention can also serve multiple operators and multi-frequency bands per operator within a single DAS to reduce the costs associated with radio network equipment and radio network deployment.

5

10

15

20

25

#### BACKGROUND OF THE INVENTION

**[002]** Wireless and mobile network operators face the continuing challenge of building networks that effectively manage high data-traffic growth rates. Mobility and an increased level of multimedia content for end users requires end-to-end network adaptations that support both new services and the increased demand for broadband and flat-rate Internet access. In addition, network operators must consider the most cost-effective evolution of the networks towards 4G and other advanced network capabilities. Wireless and mobile technology standards are evolving towards higher bandwidth requirements for both peak rates and cell throughput growth. The latest standards supporting these higher bandwidth requirements are HSPA+, WiMAX, TD-SCDMA and LTE. The network upgrades required to deploy networks based on these standards must deal with the limited availability of new spectrum,

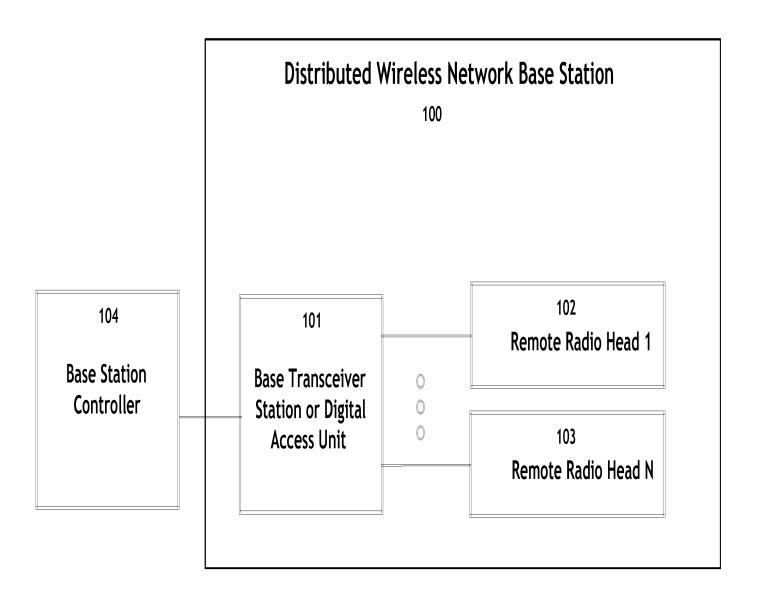

leverage existing spectrum, and ensure operation of all desired wireless technology standards. The processes of scarce resource optimization while ensuring a future-proof implementation must both take place at the same time during the transition phase, which usually spans many years and thus can encompass numerous future developments. Distributed open base station architecture concepts have evolved in parallel with the evolution of the various technology standards to provide a flexible, lower-cost, and more scalable modular environment for managing the radio access evolution. Such advanced base station architectures can generally be appreciated from Figure 1 [PRIOR ART], which shows an architecture for a prior art Distributed Wireless Network Base Station. In Figure 1, 100 is a depiction of a Distributed Wireless Network Base Station. The Base Transceiver Station (BTS) or Digital Access Unit (DAU) 101 coordinates the communication between the Remote Radio Head Units 102, 103 and the Base Station Controller (BSC). The BTS communicates with multiple Remote Radio Heads via optical fiber. For example, the Open Base Station Architecture Initiative (OBSAI), the Common Public Radio Interface (CPRI), and the IR Interface standards introduced publicly-defined interfaces separating the Base Transceiver Station (BTS) or Digital Access Unit and the remote radio head unit (RRU) parts of a base station by employing optical fiber transport.

5

10

15

20

25

**[003]** The RRU concept constitutes a fundamental part of an advanced state-of-the-art base station architecture. RRU-based system implementation is driven by the need to achieve consistent reductions in both Capital Expenses (CAPEX) and Operating Expenses (OPEX), and enable a more optimized, energy-efficient, and greener base deployment. An existing application employs an architecture where a 2G/3G/4G base station is connected to RRUs over

multiple optical fibers. Either CPRI, OBSAI or IR Interfaces may be used to carry RF data to the RRUs to cover a sectorized radio network coverage area corresponding to a radio cell site. A typical implementation for a three-sector cell employs three RRU's. The RRU incorporates a large number of digital interfacing and processing functions. However, commercially available RRU's are power inefficient, costly and inflexible. Their poor DC-to-RF power conversion insures that they will need to have a large mechanical housing to help dissipate the heat generated. The demands from wireless service providers for future RRU's also includes greater flexibility in the RRU platform, which is not presently available. As standards evolve, there will be a need for multi-band RRUs that can accommodate two or more operators using a single wideband power amplifier. Co-locating multiple operators in one DAS system would reduce the infrastructure costs and centralize the Remote Monitoring Function of multiple Operators on the Network. To accommodate multiple operators and multiple bands per operator would require a very high optical data rate to the RRUs which is not achievable with prior art designs.

20

25

15

5

10

#### SUMMARY OF THE INVENTION

[004] The present invention substantially overcomes the limitations of the prior art discussed above. Accordingly, it is an object of the present invention to provide a high performance, cost-effective DAS system, architecture and method for an RRU-based approach which enables each of multiple operators to use multi-frequency bands. The present disclosure enables a RRU to be field reconfigurable, as presented in US Patent application US 61/172,642 (DW-1016P), filed 4/24/2009, entitled Remotely Reconfigurable Power Amplifier

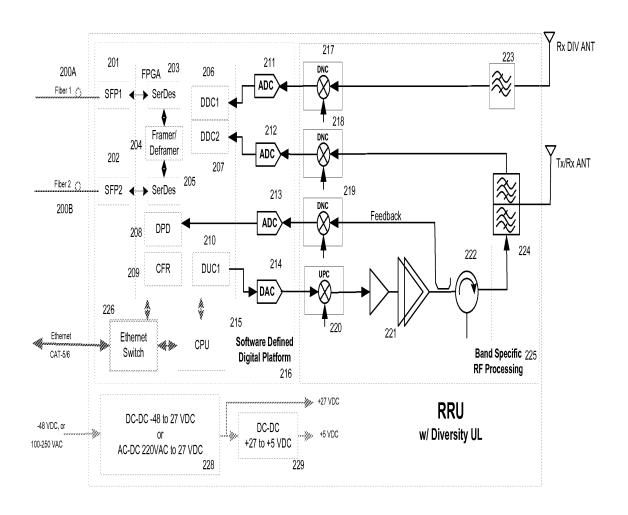

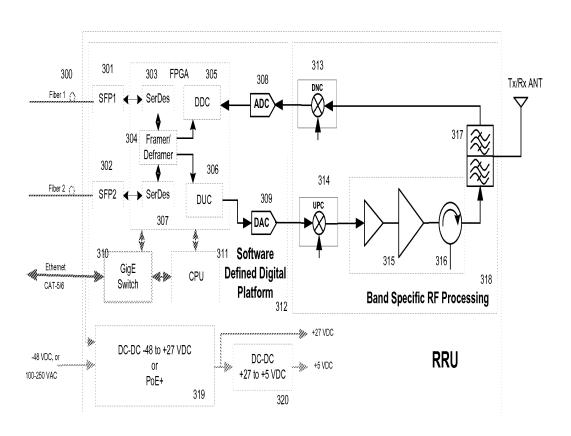

System and Method, US Patent application US 12/108,502 (DW-1011U), filed 4/23/2008, entitled Digital Hybrid Mode Power Amplifier System, US Patent application SN 61/288,838 (DW-1018P), filed 12/21/2009, entitled Multi-band Wideband Power Amplifier Digital Predistortion System, US Patent application SN 61/288,840 (DW-1019P), filed 12/21/2009, entitled Remote Radio Head Unit with Wideband Power Amplifier and Method, US Patent application SN 61/288,844 (DW-1020P), filed 12/21/2009, entitled Modulation Agnostic Digital Hybrid Mode Power Amplifier System, and US Patent application SN 61/288,847 (DW-1021P), filed 12/21/2009, entitled High Efficiency Remotely Reconfigurable Remote Radio Head Unit System and Method for Wireless Communications, all of which are incorporated herein by reference. In addition, the system and method of the present invention supports multi-modulation schemes (modulation-independent ), multi-carriers, multi-frequency bands, and multi-channels. To achieve the above objects, the present invention maximizes the data rate to the Remote Radio Head Unit in a cost effective architecture. Figures 2 and 3 depict a low power RRU and high power RRU. The RRUs depicted in Figures 2 and 3 can be extended to a multi-band and multi-channel configuration. Multi-band implies more than two frequency bands and multichannel implies more than one output to an antenna system. Various embodiments of the invention are disclosed.

5

10

15

20

25

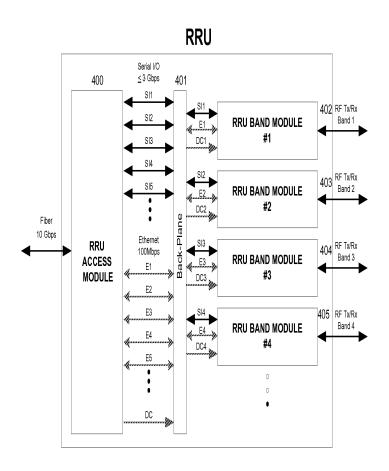

[005] An embodiment of the present invention utilizes a RRU Access Module. The objective of the access module is to de-multiplex and multiplex high speed data to achieve aggregate data rates sufficient for operation of a plurality of RRU Band Modules which are geographically distributed. An alternative embodiment of the present invention utilizes the physical separation of the RRU Band Modules from the RRU Access Module using an optical fiber cable,

Ethernet cables, RF cable and any other form of connection between the modules. In an alternative embodiment, a Remote Radio Unit comprised of one or more RRU Band Modules may be collocated with the antenna or antennas. In a further alternative embodiment, the RRU Access Module can also supply DC power on the interconnection cabling. In other aspects of the invention, control and measurement algorithms are implemented to permit improved network deployment, network management, and optimization.

5

10

15

20

25

**[006]** Applications of the present invention are suitable to be employed with all wireless base-stations, remote radio heads, distributed base stations, distributed antenna systems, access points, repeaters, distributed repeaters, optical repeaters, digital repeaters, mobile equipment and wireless terminals, portable wireless devices, and other wireless communication systems such as microwave and satellite communications. The present invention is also field upgradable through a link such as an Ethernet connection to a remote computing center.

**[007]** Appendix I is a glossary of terms used herein, including acronyms.

#### THE FIGURES

**[008]** Further objects and advantages of the present invention can be more fully understood from the following detailed description taken in conjunction with the accompanying drawings in which:

**[009]** Figure 1 [PRIOR ART] is a block diagram showing the basic structure of a prior art Distributed Wireless Base Station system.

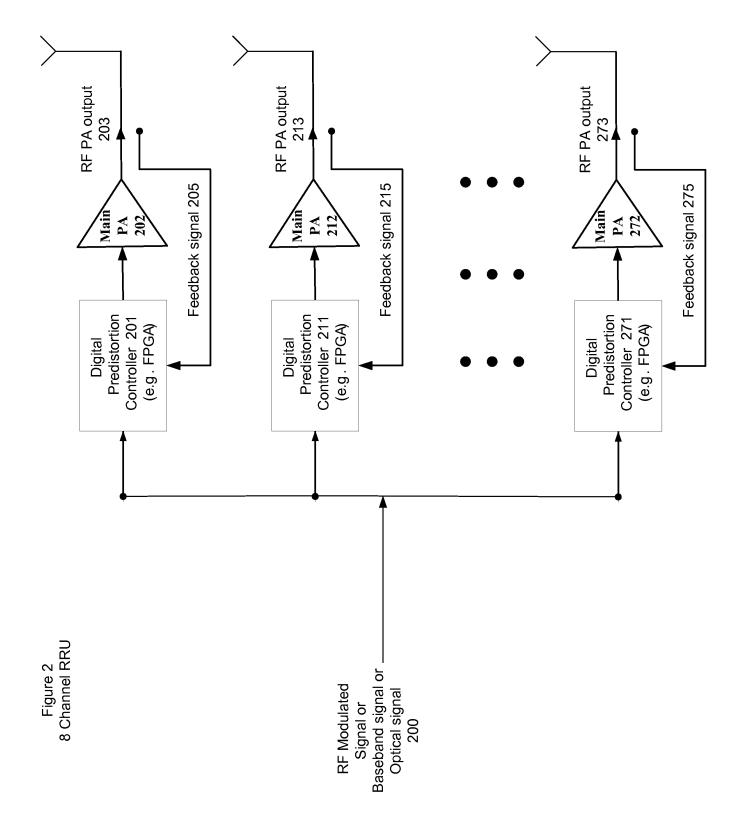

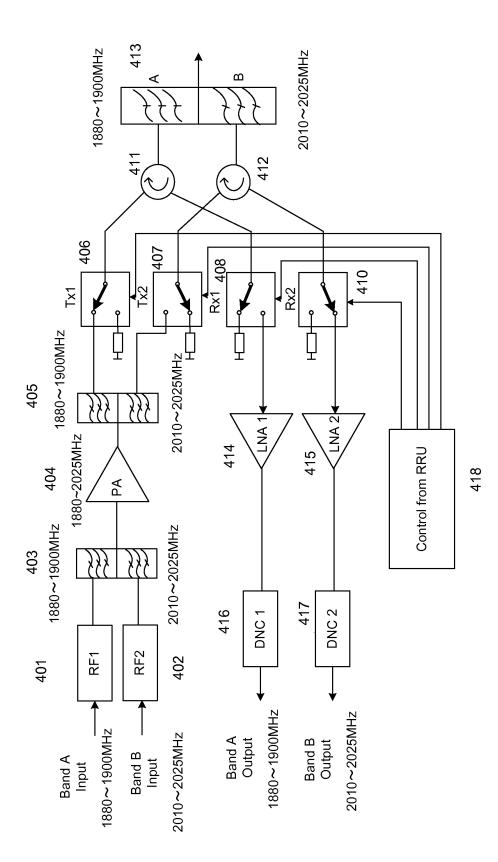

**[0010]** Figure 2 is a block diagram showing a multi-channel High Power Remote Radio Head Unit according to one embodiment of the present invention.

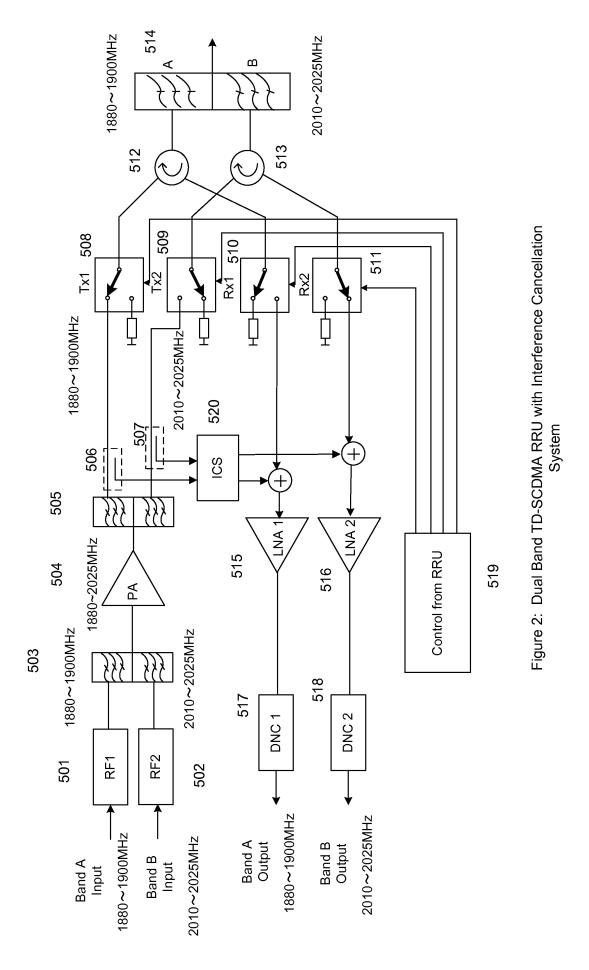

**[0011]** Figure 3 is a block diagram multi-channel High Power Remote Radio Head Unit according to one embodiment of the present invention.

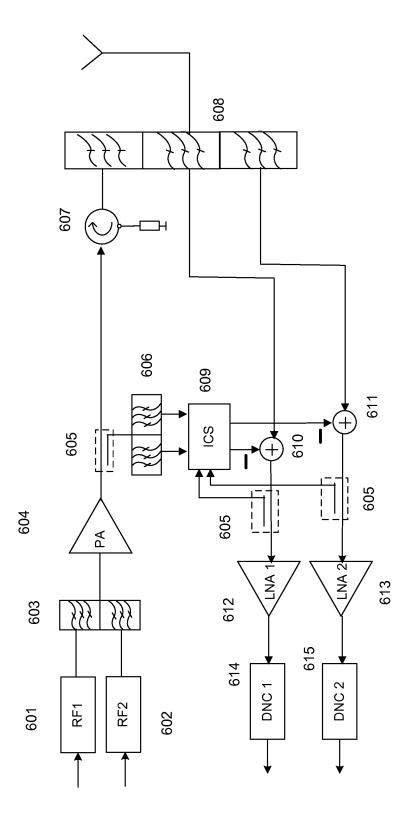

**[0012]** Figure 4 is a block diagram of a Remote Radio Head Unit high level system of the present invention.

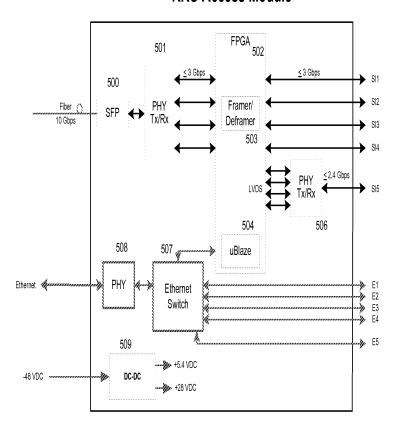

5 [0013] Figure 5 is a block diagram of the Remote Radio Head Unit Access Module of the present invention.

**[0014]** Figure 6 is a Remote Radio Head Unit Band Module according to one embodiment of the present invention.

10

15

20

25

#### **DETAILED DESCRIPTION OF THE INVENTION**

**[0015]** The present invention is a novel Distributed Antenna System that utilizes a high speed Remote Radio Head Unit Access Module interconnected with Remote Radio Head Unit Band Module.

**[0016]** An embodiment of a Remote Radio Head Unit in accordance with the invention is shown in Figure 2. Fiber 1, indicated at 200A, is a high speed fiber cable that transports data between the BTS and the Remote Radio Head Unit. Fiber 2, indicated at 200B, is used to daisy chain other remote radio head units which are thereby interconnected to the BTS or DAU. The software-defined digital platform 216 performs baseband signal processing, typically in an FPGA or equivalent. Building block 203 is a Serializer/Deserializer. The deserializer portion extracts the serial input bit stream from the optical fiber 201 and converts it into a parallel bit stream. The serializer portion performs the inverse operation for sending data from the Remote Radio Head Unit to the BTS. In an embodiment, the two distinct bit streams communicate with the BTS using

different optical wavelengths over one fiber, although multiple fibers can be used in alternative arrangements. The deframer 204 deciphers the structure of the incoming bit stream and sends the deframed data to the Crest Factor Reduction Algorithm 209. The Crest Factor Reduction block 209 reduces the Peak-to-Average Ratio of the incoming signal so as to improve the Power amplifier DCto-RF conversion efficiency. The waveform is then presented to the Digital Predistorter block 208. The digital predistorter compensates for the nonlinearities of the Power Amplifier 221 in an adaptive feedback loop. Digital Upconverter 210 filters and digitally translates the deframed signal to an IF frequency. The Framer 204 takes the data from the two digital downconverters 206, 207 and packs it into a Frame for transmission to the BTS over the optical fiber 201. Elements 211 and 212 are Analog to Digital converters that are used to translate the two analog receive signals into digital signals. The receiver comprises a diversity branch which contains a downconverter 217 and a Band Pass Filter 223. The main branch has a receiver path comprised of a duplexer 224 and a downconverter 218.

5

10

15

20

25

**[0017]** The power amplifier has an output coupler for extracting a replica of the output signal in the feedback path. The feedback signal is frequency-translated by downconverter 219 to either an IF frequency or baseband and presented to an Analog to Digital converter 213. This feedback signal is used in an adaptive loop for performing Digital Predistortion to compensate for any nonlinearities created by the power amplifier.

**[0018]** The Ethernet cable is used to locally communicate with the Remote Radio Head Unit. Switch 226 is used to allow easy access to either the FPGA or the CPU. DC power converters 228 and 229 are used to obtain the desired DC voltages for the Remote Radio Head Unit. Either an external voltage can be

connected directly into the RRU or the DC power may be supplied through the Ethernet cable.

**[0019]** Although the description of the instant embodiment is directed to an application where a second optical fiber connection provides a capability for daisy chaining to other Remote Radio Head Units, an alternative embodiment provides multiple optical fiber connections to support a modified "hybrid star" configuration for appropriate applications which dictate this particular optical transport network configuration.

5

10

15

20

25

**[0020]** Figure 3 depicts a remote radio head unit. In at least some designs, this architecture offers benefits when the RF output power is relatively low. In the embodiment shown in Figure 3, digital predistrortion and crest factor reduction are not employed as was the case in Figure 2. Even though this topology shows a non-diversity configuration, a diversity receive branch can be added along with an additional transmitter path for development of a Multiple Input Multiple Output (MIMO) Remote Radio Head Unit.

**[0021]** The Remote Radio Head Unit high level system is shown in Figure 4. It comprises a Remote Radio Head Unit Access Module 400 which communicates directly with the BTS or DAU. The function of the Remote Radio Head Unit Access Module 400 is to route the high speed data (at any desired speed, e.g., such as 10 Gbps as illustrated in Fig. 4) (the "Data Speed") to the multiple Remote Radio Head Unit Band Modules and allows for local communications with them via Ethernet. A backplane 401 is used to interconnect the Remote Radio Head Unit Access Module 400 with the various Remote Radio Head Unit Band Modules 402,403,404,405 at any speed lower than the Data Speed (e.g., less than or equal to 3Gbps as illustrated in Fig. 4). The output ports of the Remote Radio Head Unit Band Modules are combined

and sent to an antenna for transmission. An alternative embodiment is described as follows. Although the description of instant embodiment is directed to applications for up to four Remote Radio Head Unit Band Modules, an alternative embodiment involves feeding a much larger quantity of Remote Radio Head Unit Band Modules with signals of various bandwidths at various frequency bands covering multiple octaves of frequency range, to support a wide range of applications including location-based services, mobile internet, public safety communications, private enterprise telecommunications and broadband, and other wireless applications. The system can in theory support an infinite quantity of RRUs. Also, the Remote Radio Head Unit Band Modules may be set up remotely to have RF power values selected based on the specific desired applications as well as location-specific radio signal propagation factors. A further alternative embodiment leverages the flexibility of the architecture shown in Figure 4 to provide a capability known as Flexible Simulcast. With Flexible Simulcast, the amount of radio resources (such as RF carriers, CDMA codes or TDMA time slots) assigned to a particular RRU or group of RRUs by each RRU Access Module can be set via software control to meet desired capacity and throughput objectives or wireless subscriber needs.

5

10

15

20 [0022] The detailed topology of the Remote Radio Head Unit Access Module is shown in Figure 5. It comprises a Small form Factor Pluggable optic transceiver (SFP) 500 which operates on two distinct wavelengths, one for communicating from the BTS to the Remote Radio Head Unit Access Module and the other for communicating in the opposite direction. The SFP contains a

25 Laser Diode for converting the electronic signal to a digital optical signal and an Optical detector for converting the digital optical signal into an electronic signal.

A multiplexer/demultiplexer 501 converts the high speed data to multiple lower speed data paths for delivery to a FPGA 502. The multiplexer/demultiplexer 501 performs the opposite function when data is being sent back to the BTS or DAU. The framer/deframer 503 routes the data to the appropriate Remote Radio Head Unit Band Modules. An additional multiplexer/demultiplexer 506 allows for further expansion of lower speed Remote Radio Head Units. The number of Remote Radio Head units is only limited by the capability of the FPGA. Local communication with the Remote Radio Head Unit's Access Module's FPGA or the individual Remote Radio Head Unit Band Modules is via an Ethernet connection 508. Although the description of this embodiment is mainly directed to an application where a BTS and/or DAU (or multiple BTS and/or multiple DAU) feeds the Remote Radio Head Unit Access Module, an alternative embodiment is described as follows. The alternative embodiment is one where the digital optical signals fed to the Remote Radio Head Unit Access Module may be generated by an RF-to-Digital interface which receives RF signals by means of one or more antennas directed to one or more base stations located at some distance from the Remote Radio Head Unit Access Module. A further alternative embodiment is one where the signals fed to the Remote Radio Head Unit Access Module may be generated in a combination of ways; some may be generated by an RF-to-Digital interface and some may be generated by a BTS and/or DAU. Some neutral host applications gain an advantage with regard to cost-effectiveness from employing this further alternative embodiment. Although the optical signals fed to the Remote Radio Head Unit Access Module described in the preferred and alternative embodiments are digital; the optical signals are not limited to digital, and can be analog or a combination of analog and digital. A further alternative embodiment employs transport on one or multiple optical wavelengths fed to the Remote Radio Head Unit Access Module.

5

10

15

20

**[0023]** The Remote Radio Head Unit Band Module is shown in Figure 6. It comprises a Software Defined Digital (SDD) section 610 and an RF section 622. An alternative embodiment employs a Remote Antenna Unit comprising a broadband antenna with RRU Band Module Combiner and multiple plug-in module slots, into which multiple RRU Band Modules intended for operation in different frequency bands are inserted. To provide an overall compact unit with low visual impact, this embodiment employs RRU Band Modules which each have a physically small form factor. One example of a suitably small form factor for the RRU Band Module is the PCMCIA module format. A further alternative embodiment employs RRU Band Modules where each has an integral antenna, and the embodiment does not require a common antenna shared by multiple RRU Band Modules.

5

10

25

15 [0024] In summary, the Neutral Host Distributed Antenna System (NHDAS) of the present invention enables the use of remote radio heads for multi-operator multi-band configurations, which subsequently saves hardware resources and reduces costs. The NHDAS system is also reconfigurable and remotely field-programmable since the algorithms can be adjusted like software in the digital processor at any time.

**[0025]** Moreover, the NHDAS system is flexible with regard to being able to support various modulation schemes such as QPSK, QAM, OFDM, etc. in CDMA, TD-SCDMA, GSM, WCDMA, CDMA2000, LTE and wireless LAN systems. This means that the NHDAS system is capable of supporting multimodulation schemes, multi-bands and multi-operators.

**[0026]** Although the present invention has been described with reference to the preferred embodiments, it will be understood that the invention is not limited to the details described thereof. Various substitutions and modifications have been suggested in the foregoing description, and others will occur to those of ordinary skill in the art. Therefore, all such substitutions and modifications are intended to be embraced within the scope of the invention as defined in the appended claims.

# What is Claimed is:

#### **ABSTRACT**

A remote radio head unit (RRU) system for achieving high data rate communications in a Distributed Antenna System is disclosed. The Distributed Antenna System is configured as a Neutral Host enabling multiple operators to exist on one DAS system. The present disclosure enables a remote radio head unit to be field reconfigurable and support multi-modulation schemes (modulation-independent), multi-carriers, multi-frequency bands and multi-channels. As a result, the remote radio head system is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems.

5

# APPENDIX I

# Glossary of Terms

| 5  | ACLR                              | Adjacent Channel Leakage Ratio                  |  |

|----|-----------------------------------|-------------------------------------------------|--|

|    | ACPR                              | Adjacent Channel Power Ratio                    |  |

|    | ADC                               | Analog to Digital Converter                     |  |

|    | AQDM                              | Analog Quadrature Demodulator                   |  |

|    | AQM                               | Analog Quadrature Modulator                     |  |

| 10 | AQDMC                             | Analog Quadrature Demodulator Corrector         |  |

|    | AQMC                              | Analog Quadrature Modulator Corrector           |  |

|    | BPF                               | Bandpass Filter                                 |  |

|    | CDMACode Division Multiple Access |                                                 |  |

|    | CFR                               | Crest Factor Reduction                          |  |

| 15 | DAC                               | Digital to Analog Converter                     |  |

|    | DET                               | Detector                                        |  |

|    | DHMPA                             | Digital Hybrid Mode Power Amplifier             |  |

|    | DDC                               | Digital Down Converter                          |  |

|    | DNC                               | Down Converter                                  |  |

| 20 | DPA                               | Doherty Power Amplifier                         |  |

|    | DQDM                              | Digital Quadrature Demodulator                  |  |

|    | DQM                               | Digital Quadrature Modulator                    |  |

|    | DSP                               | Digital Signal Processing                       |  |

|    | DUC                               | Digital Up Converter                            |  |

| 25 | EER                               | Envelope Elimination and Restoration            |  |

|    | EF                                | Envelope Following                              |  |

|    | ET                                | Envelope Tracking                               |  |

|    | EVM                               | Error Vector Magnitude                          |  |

|    | FFLPA                             | Feedforward Linear Power Amplifier              |  |

| 30 | FIR                               | Finite Impulse Response                         |  |

|    | FPGA                              | Field-Programmable Gate Array                   |  |

|    | GSM                               | Global System for Mobile communications         |  |

|    | I-Q                               | In-phase / Quadrature                           |  |

|    | IF                                | Intermediate Frequency                          |  |

| 35 | LINC                              | Linear Amplification using Nonlinear Components |  |

|    | LO                                | Local Oscillator                                |  |

|    | LPF                               | Low Pass Filter                                 |  |

|    | MCPA                              | Multi-Carrier Power Amplifier                   |  |

|    | MDS                               | Multi-Directional Search                        |  |

| 40 | OFDM                              | Orthogonal Frequency Division Multiplexing      |  |

|    |                                   |                                                 |  |

PA Power Amplifier

PAPR Peak-to-Average Power Ratio PD Digital Baseband Predistortion

PLL Phase Locked Loop

5 QAM Quadrature Amplitude ModulationQPSK Quadrature Phase Shift Keying

RF Radio Frequency

RRH Remote Radio Head

RRU Remote Radio Head Unit

SAW Surface Acoustic Wave Filter

UMTS Universal Mobile Telecommunications System

UPC Up Converter

WCDMA Wideband Code Division Multiple Access

WLAN Wireless Local Area Network

15

Figure 1: PRIOR ART

Figure 2. Remote Radio Head Unit

Figure 3. Remote Radio Head Unit

Figure 4. Remote Radio Head Unit High Level System

# **RRU Access Module**

Figure 5. Remote Radio Head Unit Access Module

# **RRU Band Module** 613 614 FPGA 600 601 602 Tx/Rx SI1 Framer/ SerDes Deframer 616 607 605 uBlaze RF Section 622 608 609 VDC SDD DC-DC Section

Figure 6. Remote Radio Head Unit Band Module

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

#### **PROVISIONAL APPLICATION**

5 FOR

#### **UNITED STATES PATENT**

**FOR**

10

20

# HIGH EFFICIENCY, REMOTELY RECONFIGURABLE REMOTE RADIO HEAD UNIT SYSTEM AND METHOD FOR WIRELESS COMMUNICATIONS

15 INVENTORS

Wan-Jong Kim, Citizen of Korea

Kyoung-Joon Cho, Citizen of Korea

Shawn Patrick Stapleton, Citizen of Canada

Ying Xiao, Citizen of China

#### **SPECIFICATION**

25 **RELATED APPLICATIONS**

This application claims the benefit of the following applications:

- US Patent Appn SN 12/415,676, filed 3/31/2009, and through it U.S. Patent Appn SN 61/041,164, filed 3/31/2008; which also claims the benefit of U.S. Provisional Patent Application S.N. 61/172,642, filed 4/24/2009;

- US Patent Application SN 12/603,419, filed 10/21/2009, and through it US Patent

- 5 Application SN 12/108,507, filed 4/23/2008, and through it U.S. Patent Application SN 60/925,577, filed 4/23/2007;

- US Patent Application SN 12/330,451 filed 12/8/2008, and through it US Patent Application SN 61/012,416, filed 12/07/2007;

- US Patent Application SN 11/961,969, filed 12/20/2007, and through it US Patent

- 10 Application SN 60/877,035, filed 12/26/2006, and US Patent Application SN 60/925,603, filed 4/23/2007;

- US Patent Application SN 12/108,502, filed 4/23/2008, and through it US Patent Application SN 12/021,241, filed 1/28/2008, and through that to US Patent Application SN 60/897,746, filed 1/26/2007.

- US Patent Application S.N. \_\_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW-1018, entitled MULTI-BAND WIDEBAND POWER AMPLIFIER DIGITAL PREDISTORTION SYSTEM AND METHOD and naming as inventors Wan-Jong Kim, Kyoung-Joon Cho, and Shawn Patrick Stapleton.

- US Patent Application S.N. \_\_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW1019, entitled REMOTE RADIO HEAD UNIT SYSTEM WITH WIDEBAND POWER

AMPLIFIER AND METHOD and naming as inventors Chengxun Wang and Shawn

Patrick Stapleton.

- US Patent Application S.N. \_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW-1020, entitled ADVANCED DIGITAL HYBRID MODE POWER AMPLIFIER

- 25 SYSTEM AND METHOD and naming as inventors Wan-Jong Kim, Kyoung-Joon Cho, Shawn Patrick Stapleton, Ying Xiao.

US Patent Application S.N. \_\_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW-1021, entitled HIGH EFFICIENCY, REMOTELY RECONFIGURABLE REMOTE RADIO HEAD UNIT SYSTEM AND METHOD FOR WIRELESS COMMUNICATIONS and naming as inventors Wan-Jong Kim, Kyoung-Joon Cho, and Shawn Patrick Stapleton, and Ying Xiao.

All of the foregoing are incorporated herein by reference for all purposes.

#### FIELD OF THE INVENTION

10

15

20

25

The present invention generally relates to wireless communication systems using power amplifiers and remote radio head units (RRU or RRH). More specifically, the present invention relates to RRU which are part of a distributed base station in which all radio-related functions are contained in a small single unit that can be deployed in a location remote from the main unit. Multi-mode radios capable of operating according to GSM, HSPA, LTE, and WiMAX standards and advanced software configurability are key features in the deployment of more flexible and energy-efficient radio networks. The present invention can also serve multi-frequency bands within a single RRU to economize the cost of radio network deployment.

# **BACKGROUND OF THE INVENTION**

Wireless and mobile network operators face the continuing challenge of building networks that effectively manage high data-traffic growth rates. Mobility and an increased level of multimedia content for end users require end-to-end network adaptations that support both new services and the increased demand for broadband and flat-rate Internet access. In addition, network operators must consider the most cost-effective evolution of the networks towards 4G. Wireless and mobile technology standards are

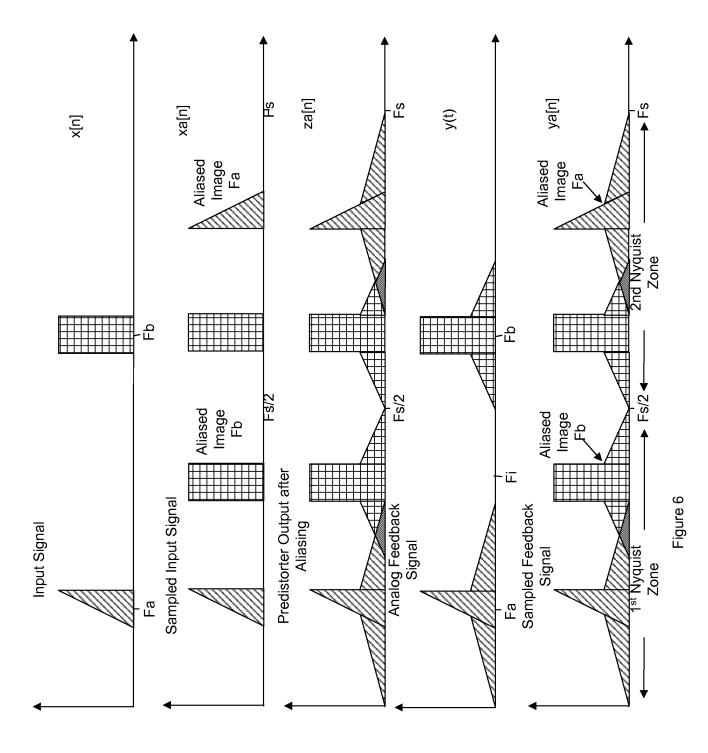

evolving towards higher bandwidth requirements for both peak rates and cell throughput growth. The latest standards supporting this are HSPA+, WiMAX, TD-SCDMA and LTE. The network upgrades required to deploy networks based on these standards must balance the limited availability of new spectrum, leverage existing spectrum, and ensure operation of all desired standards. This all must take place at the same time during the transition phase, which usually spans many years. Distributed open base station architecture concepts have evolved in parallel with the evolution of the standards to provide a flexible, cheaper, and more scalable modular environment for managing the radio access evolution, Figure 6. For example, the Open Base Station Architecture Initiative (OBSAI), the Common Public Radio Interface (CPRI), and the IR Interface standards introduced standardized interfaces separating the Base Station server and the remote radio head part of a base station by an optical fiber.

15

10

5

The RRU concept constitutes a fundamental part of a state-of-the-art base station architecture. However, RRUs to-date are power inefficient, costly and inflexible. Their poor DC to RF power conversion insures that they will have a large mechanical housing. The RRU demands from the service providers are also for greater flexibility in the RRU platform. As standards evolve, there is a need for a software upgradable RRU. Today RRUs lack the flexibility and performance that is required by service providers. The RRU performance limitations are driven in part by the poor power efficiency of the RF amplifiers. Thus there has been a need for an efficient, flexible RRU architecture that is field reconfigurable.

25

#### SUMMARY OF THE INVENTION

the above problems in the prior art, and it is an object of the present invention to provide a high performance and cost effective method of multi-frequency bands RRU systems enabled by high linearity and high efficiency power amplifiers for wideband communication system applications. The present disclosure enables a RRU to be field reconfigurable, and supports multi-modulation schemes (modulation agnostic), multi-carriers, multi-frequency bands, and multi-channels.

5

10

15

20

25

invention, the technique is generally based on the method of adaptive digital predistortion to linearize RF power amplifiers. Various embodiments of the invention are disclosed, including single band, dual band, and multi-band RRU's. Another embodiment is a multi-band multi-channel RRU. In an embodiment, the combination of crest factor reduction, PD, power efficiency boosting techniques as well as coefficient adaptive algorithms are utilized within a PA system. In another embodiment, analog quadrature modulator compensation structure is also utilized to enhance performance.

**[003]** Some embodiments of the present invention are able to monitor the fluctuation of the power amplifier characteristics and to self-adjust by means of a self-adaptation algorithm. One such self-adaptation algorithm presently disclosed is called a digital predistortion algorithm, which is implemented in the digital domain.

Applications of the present invention are suitable for use with all wireless base-stations, remote radio heads, distributed base stations,

distributed antenna systems, access points, mobile equipment and wireless terminals, portable wireless devices, and other wireless communication systems such as microwave and satellite communications. The present invention is also field upgradable through a link such as an Ethernet connection to a remote computing center.

#### THE FIGURES

5

10

15

**[005]** Further objects and advantages of the present invention can be more fully understood from the following detailed description taken in conjunction with the accompanying drawings in which:

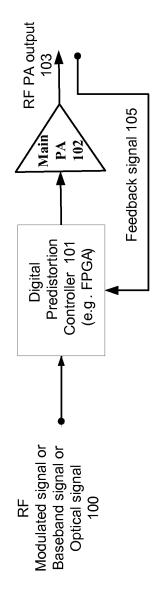

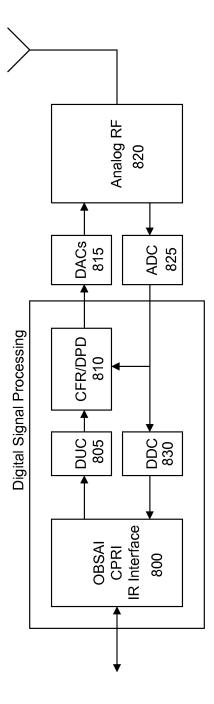

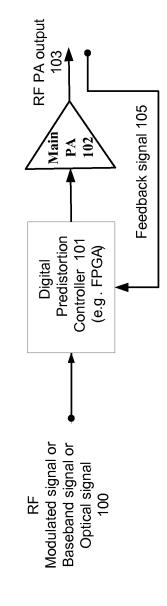

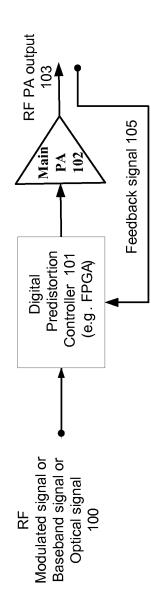

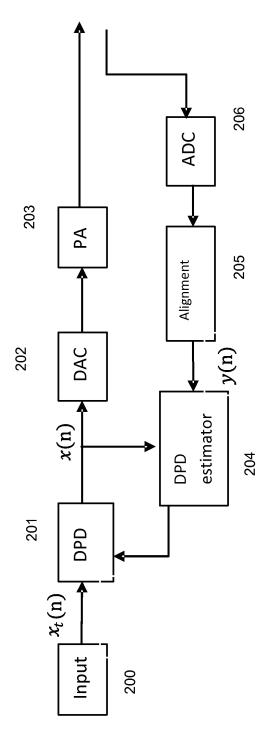

**[006]** Figure 1 is a block diagram showing the basic form of a Remote Radio head unit system.

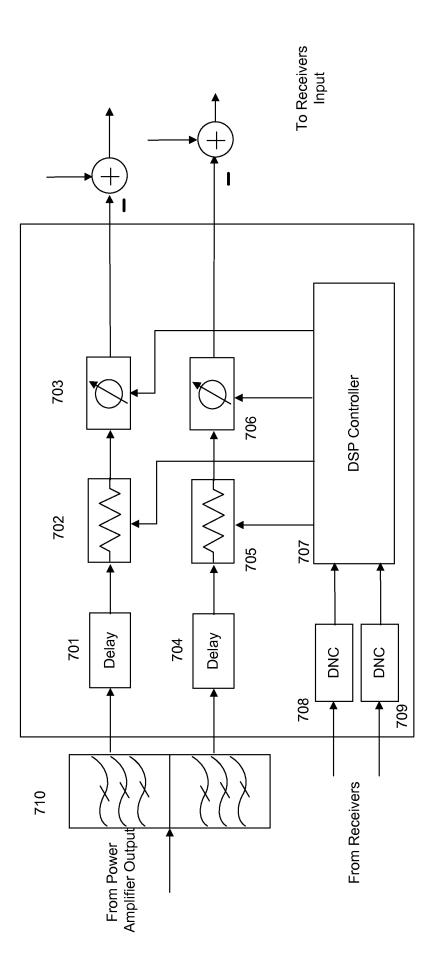

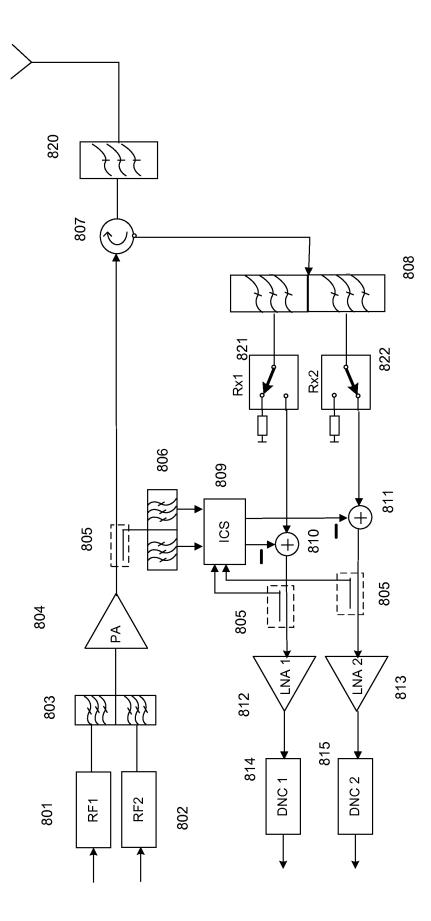

**[007]** Figure 2 is a block diagram showing a multi-channel Remote Radio Head Unit according to one embodiment of the present invention.

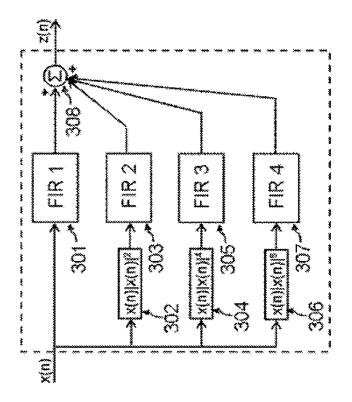

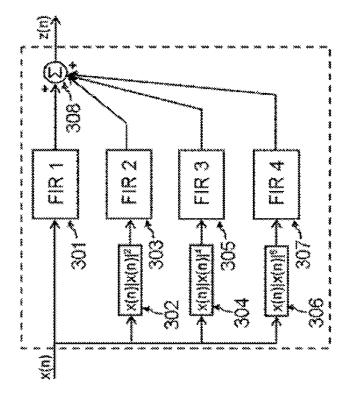

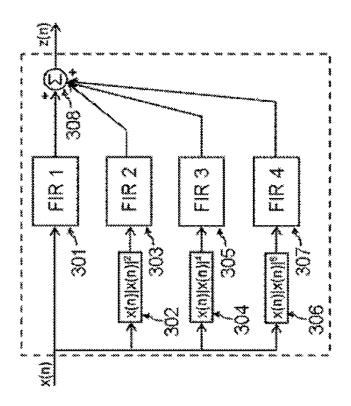

**[007]** Figure 3 is a block diagram showing polynomial based predistortion in a Remote Radio head system of the present invention.

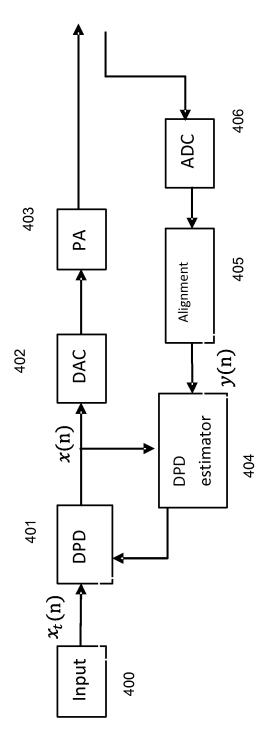

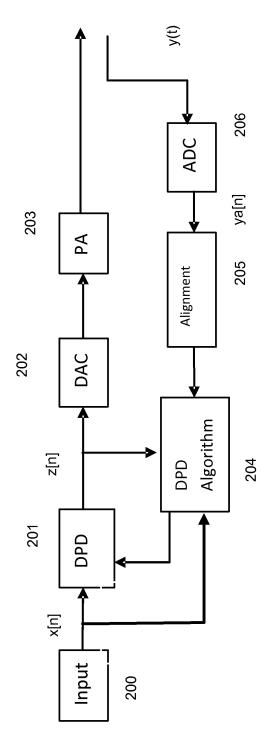

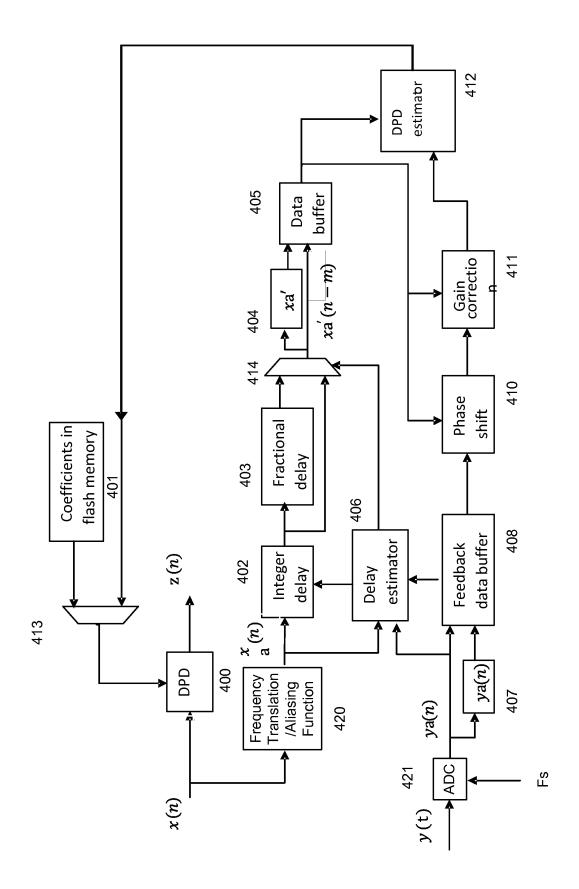

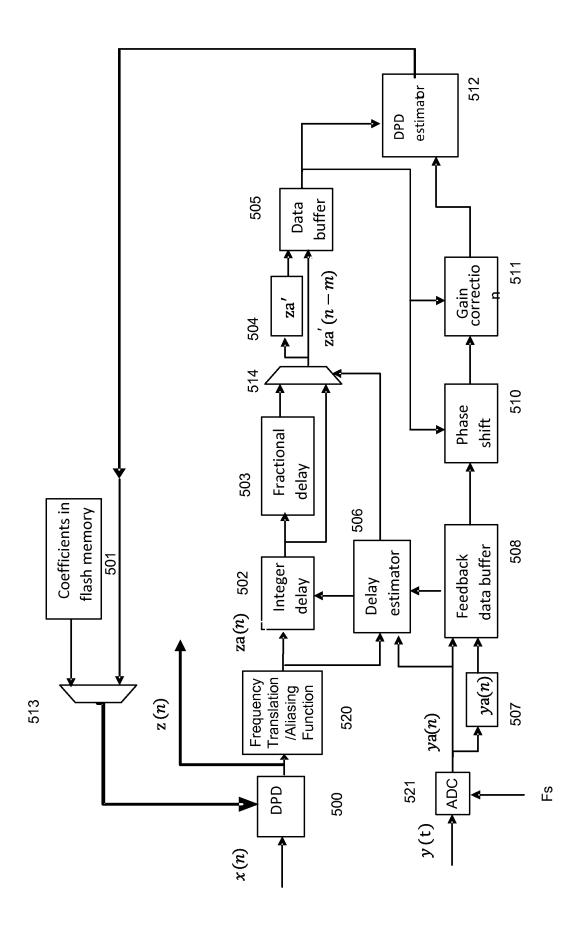

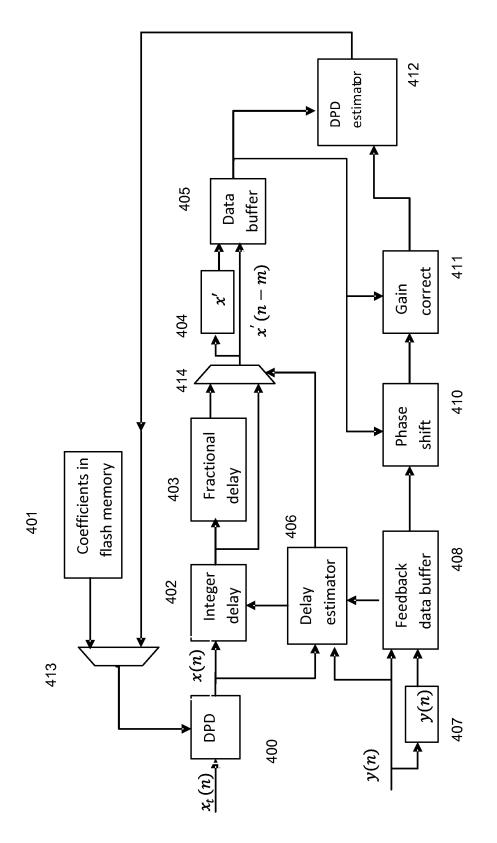

**[008]** Figure 4 is a block diagram of the digital predistortion algorithm applied for self-adaptation in a remote radio head unit system of the present invention.

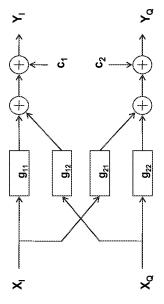

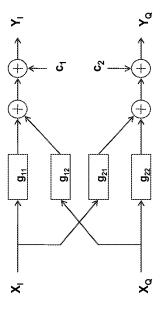

**[009]** Figure 5 illustrates an analog modulator compensation block.

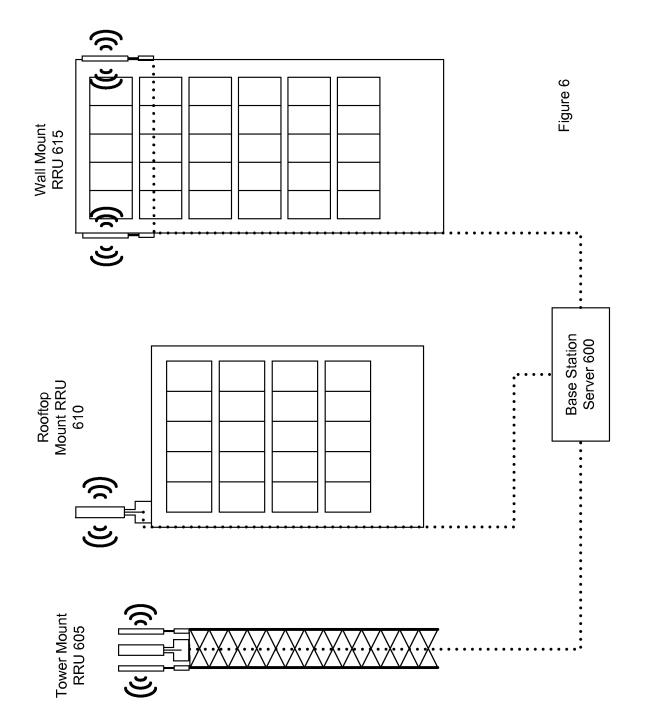

20 **[0010]** Figure 6 depicts schematically a variety of potential installation schemes for an RRU-based system architecture.

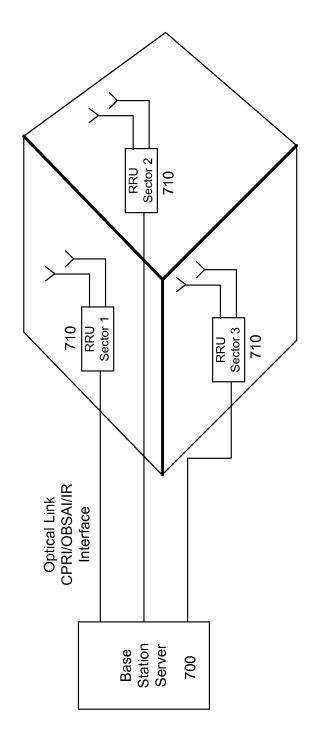

**[0011]** Figure 7 depicts a three-sector arrangement of an RRU system architecture comprising optical links to a base station server.

**[0012]** Figure 8 shows in block diagram form various DSP-based functions including crest factor reduction and digital predistortion.

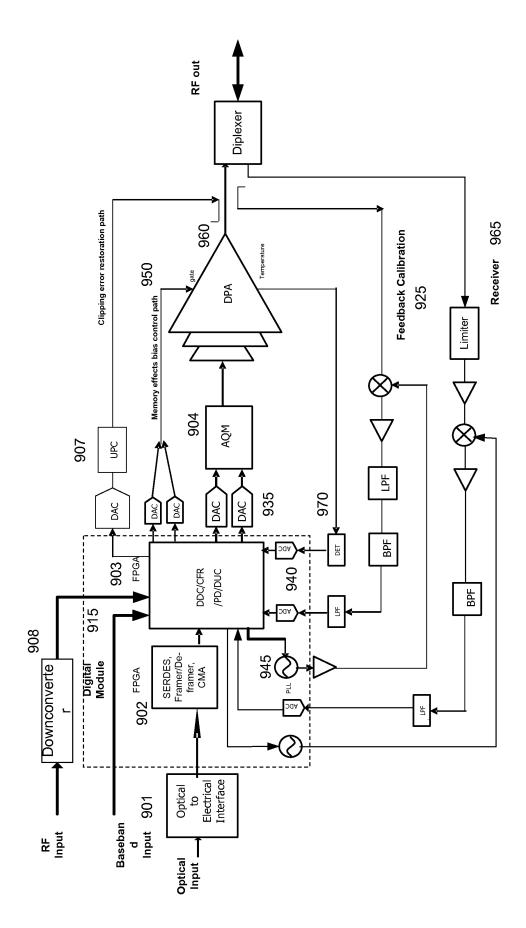

**[0013]** Figure **9** is a Digital Hybrid Module with either an RF input signal or a baseband modulated signal or an optical interface according to another embodiment of the present invention.

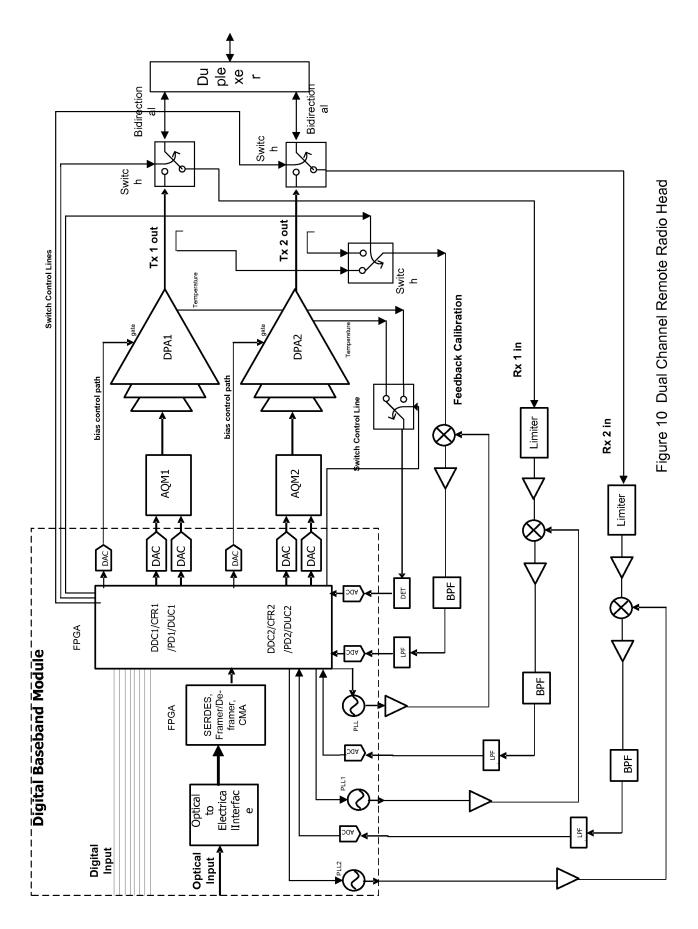

**[0014]** Figure **10** is a Dual Channel Remote Radio head block diagram showing a digital hybrid module with an optical interface according to another embodiment of the present invention.

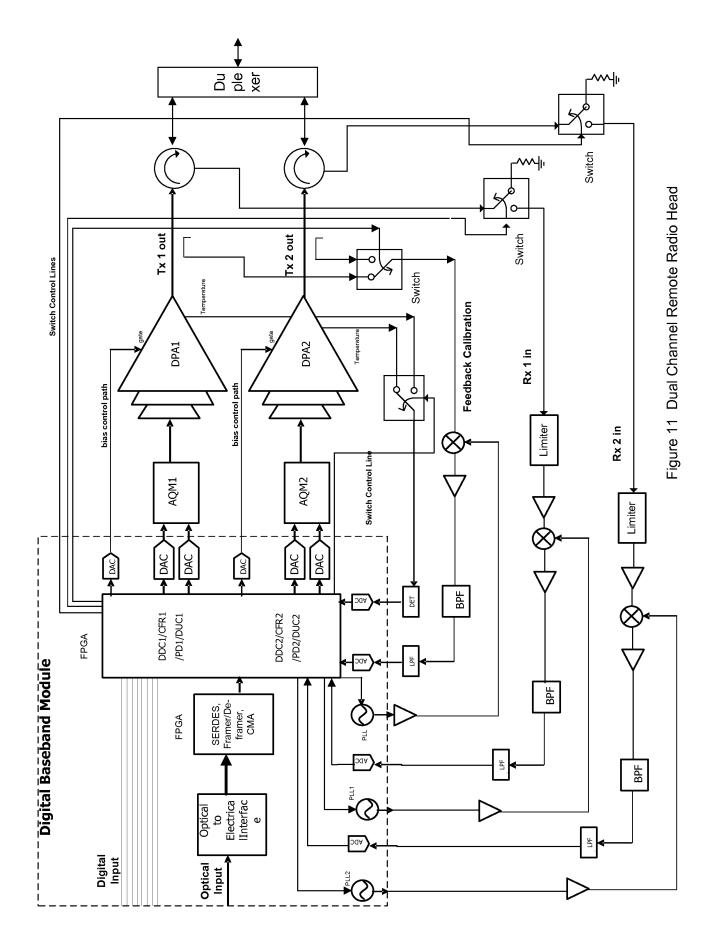

**[0015]** Figure **11** is an alternative Dual Channel Remote Radio Head block diagram showing a digital hybrid module with an optical interface according to another embodiment of the present

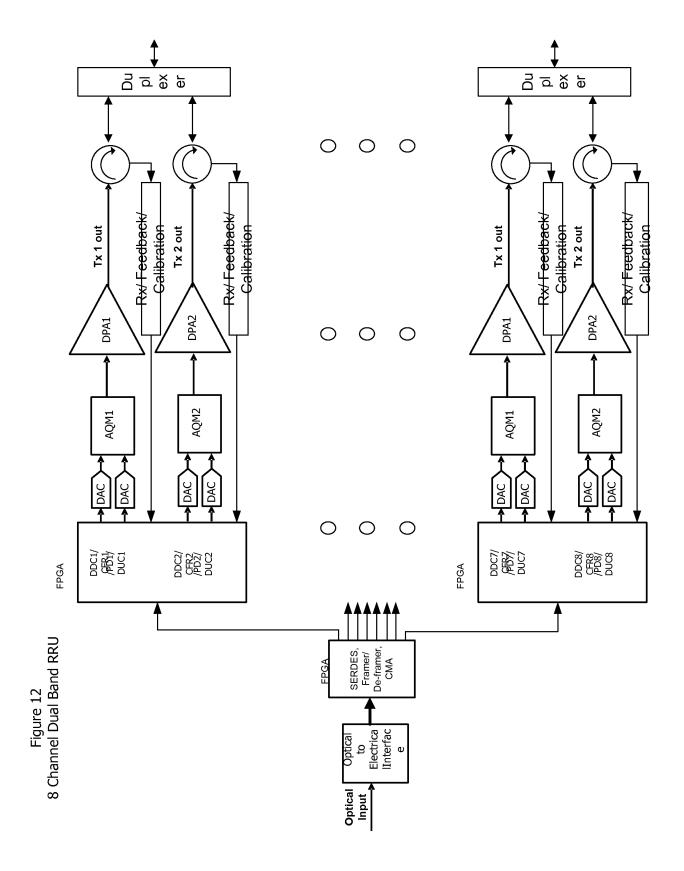

**[0016]** Figure **12** is an 8 channel Dual Band Remote Radio Head block diagram showing a digital hybrid module with an optical interface, and further comprises a calibration algorithm for insuring that each power amplifier output is time-aligned, phase-aligned and amplitude-aligned with respect to each other.

#### **GLOSSARY**

Acronyms used herein have the following meanings:

| 20 | ACLR | Adjacent Channel Leakage Ratio |

|----|------|--------------------------------|

|    | ACPR | Adjacent Channel Power Ratio   |

|    | ADC  | Analog to Digital Converter    |

|    | AQDM | Analog Quadrature Demodulator  |

|    | AQM  | Analog Quadrature Modulator    |

|    |      |                                |

5

10

15

25

**AQDMC**

Analog Quadrature Demodulator Corrector

AQMC Analog Quadrature Modulator Corrector

BPF Bandpass Filter

CDMA Code Division Multiple Access

CFR Crest Factor Reduction

5 DAC Digital to Analog Converter

DET Detector

DHMPA Digital Hybrid Mode Power Amplifier

DDC Digital Down Converter

DNC Down Converter

10 DPA Doherty Power Amplifier

DQDM Digital Quadrature Demodulator

DQM Digital Quadrature Modulator

DSP Digital Signal Processing

DUC Digital Up Converter

15 EER Envelope Elimination and Restoration

EF Envelope Following

ET Envelope Tracking

EVM Error Vector Magnitude

FFLPA Feedforward Linear Power Amplifier

20 FIR Finite Impulse Response

FPGA Field-Programmable Gate Array

GSM Global System for Mobile communications

I-Q In-phase / Quadrature

IF Intermediate Frequency

25 LINC Linear Amplification using Nonlinear Components

LO Local Oscillator

LPF Low Pass Filter

MCPA Multi-Carrier Power Amplifier

MDS Multi-Directional Search

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

5 PAPR Peak-to-Average Power Ratio

PD Digital Baseband Predistortion

PLL Phase Locked Loop

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

10 RF Radio Frequency

RRU Remote Radio Head Unit

SAW Surface Acoustic Wave Filter

SERDES Serializer/Deserializer

UMTS Universal Mobile Telecommunications System

15 UPC Up Converter

WCDMA Wideband Code Division Multiple Access

WLAN Wireless Local Area Network.

#### **DETAILED DESCRIPTION OF THE INVENTION**

20

25

adaptive digital predistortion algorithm. The present invention is a hybrid system of digital and analog modules. The interplay of the digital and analog modules of the hybrid system both linearize the spectral regrowth and enhance the power efficiency of the PA while maintaining or increasing the wide bandwidth. The present invention, therefore, achieves higher efficiency and higher linearity for wideband complex modulation carriers.

[002] Figure 1 is a high level block diagram showing the basic system architecture of what is sometimes referred to as a Remote Radio Head Unit, or RRU, which can be thought of, at least for some embodiments, as comprising digital and analog modules and a feedback path. The digital module is the digital predistortion controller 101 which comprises the PD algorithm, other auxiliary DSP algorithms, and related digital circuitries. The analog module is the main power amplifier 102, other auxiliary analog circuitries such as DPA, and related peripheral analog circuitries of the overall system. The present invention operates as a "black box", plug-andplay type system because it accepts RF modulated signal 100 as its input, and provides a substantially identical but amplified RF signal 103 as its output, therefore, it is RF-in/RF-out. Baseband input signals can be applied directly to the Digital Predistorter Controller according to one embodiment of the present invention. An Optical input signal can be applied directly to the Digital Predistorter Controller according to one embodiment of the present invention. The feedback path essentially provides a representation of the output signal to the predistortion controller 101. The present invention is sometimes referred to as a Remote Radio head Unit (RRU) hereinafter.

embodiment of an eight channel (or n channel) RRU in which an input signal 200 is provided. Depending on the implementation, the input signal can take the form of an RF modulated signal, a baseband signal, or an optical signal. The input signal 200 is fed to a plurality of channels, where each channel includes a digital predistortion (DPD) controller, indicated at 201, 211 and 271, respectively. The DPD can be implemented in an FPGA in at least some embodiments. For each channel, the DPD outputs are fed to

25

20

5

10

associated PA's 202, 212 and 272, respectively, and the PA outputs 203, 213 and 273 are fed back to that channel's DPD's.

[004] Figure 3 illustrates a polynomial-based digital predistorter function in the RRU system of the present invention. The PD in the present invention generally utilizes an adaptive LUT-based digital predistortion system. More specifically, the PD illustrated in FIG. 3, and in embodiments disclosed from Figures 9-12 discussed hereinafter, are processed in the digital processor by an adaptive algorithm, presented in U.S. Patent application S.N. 11/961,969, entitled A Method for Baseband Predistortion Linearization in Multi-Channel Wideband Communication Systems. The PD for the RRU system in FIG. 3. has multiple finite impulse response (FIR) filters, that is, FIR1 301, FIR2 303, FIR3 305, and FIR4 307. The PD also contains the third order product generation block 302, the fifth order product generation block 304, and the seventh order product generation block 306. The output signals from FIR filters are combined in the summation block 308. Coefficients for multiple FIR filters are updated by the digital predistorter algorithm based on the error between the reference input signal and the amplified power output signal.

embodiment including a DPD in accordance with the present invention and is discussed in greater detail hereinafter. In general, the input 400 is provided to the DPD 401. The output of the DPD is fed to a DAC 402 and thence to the PA 403. A feedback signal from the output of the PA is received by ADC 406, and the digital form is supplied to alignment logic 405, after which the aligned signal is provided to DPD estimator logic 404, which also receives an

25

20

5

10

input from the output of the DPD 401. The output of the DPD estimator is then fed back to the DPD 401.

5

10

15

20

25

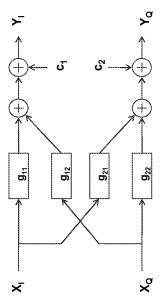

Figure 5 illustrates an analog modulator compensation block. The input signal is separated into an in-phase component  $X_l$  and a quadrature component  $X_Q$ . The analog quadrature modulator compensation structure comprises four real filters {g11 , g12 , g21 , g22} and two DC offset compensation parameters c1, c2. The DC offsets in the AQM will be compensated by the parameters c1, c2 . The frequency dependence of the AQM will be compensated by the filters {g11, g12, g21, g22}. The order of the real filters is dependent on the level of compensation required. The output signals  $Y_l$  and  $Y_Q$  will be presented to an AQM's in-phase and quadrature ports, discussed hereinafter in connection with Figure 9.

Figure 6 illustrates a plurality of possible implementations of an RRU-based system architecture, in with a base station server 600 is connected to, for example, a tower-mounted RRU 605, a rooftop-mounted RRU 610, and/or a wall-mounted RRU 615.

**[008]** Figure 7 illustrates an embodiment of a three-sector implementation of an RRU-based system architecture, in which a base station server 700 is optically linked to a plurality of RRU's 710 to provide adequate coverage for a site.

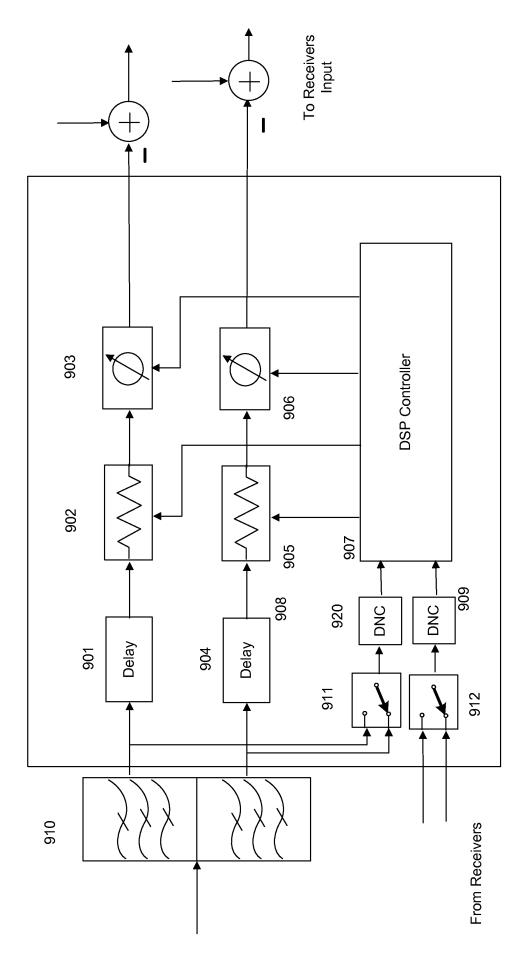

[009] Figure 8 illustrates in simplified form an embodiment of the DSP functionality of some implementations of the present invention. An input signal is fed to an interface 800, which can take several forms including OBSAI, CPRI or IR. The incoming signal is fed to a digital up-converter (DUC) 805 and then to CFR/DPD logic 810, such as an FPGA. The output of

the CFR/DPD logic 810 is then supplied to a DAC 815. The DAC provides an output signal to the analog RF portion 820 of the system, which in turn provides a feedback signal to a ADC 825, and back through the DSP block in the form of inputs to the CFR/DPD and a DDC 830. The DDC outputs a signal to the interface 800, which in turn can provide an output.

5

10

15

20

25

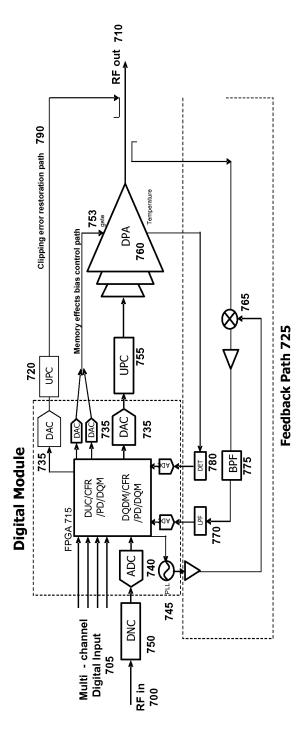

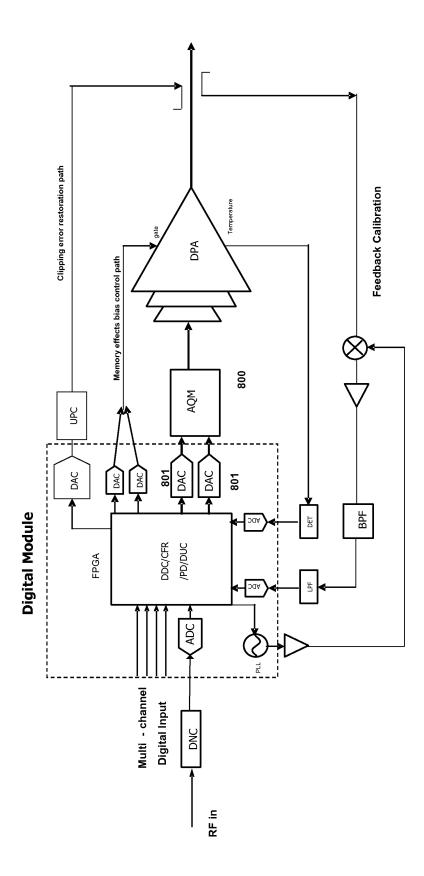

[0010] Figure 9 is a block diagram showing a more sophisticated embodiment of a RRU system, where like elements are indicated with like numerals. The embodiment of Figure 9 applies crest factor reduction (CFR) prior to the PD with an adaptation algorithm in one digital processor, so as to reduce the PAPR, EVM and ACPR and compensate the memory effects and variation of the linearity due to the temperature changing of the PA. The digital processor can take nearly any form; for convenience, an FPGA implementation is shown as an example, but a general purpose processor is also acceptable in many embodiments. The CFR implemented in the digital module of the embodiments is based on the scaled iterative pulse cancellation presented in US patent application SN 61/041,164, filed March 31, 2008, entitled An Efficient Peak Cancellation Method For Reducing The Peak-To-Average Power Ratio In Wideband Communication Systems, incorporated herein by reference. The CFR is included to enhance performance and hence optional. The CFR can be removed from the embodiments without affecting the overall functionality.

**[0011]** Figure 9 is a block diagram showing a RRU system according to one embodiment of the present invention (the "FIG. 9. System"). RRU systems consist of three primary blocks: power amplifiers, baseband processing and an optical interface. The optical interface contains an optical to electrical interface for the transmit/receive mode. The optical interface 901,

shown in Figure 9, is coupled to a FPGA. The FPGA 902 performs the functions of SERDES/Framer/De-Framer/Control and Management. This FPGA 902 interfaces with another FPGA 903 that performs the following Digital Signal Processing tasks: Crest Factor Reduction/ Digital Upconversion/Digital Downconversion and Digital Predistortion. Another embodiment will be to integrate 902 with 903 in a single FPGA. The Serializer/De-serializer (SERDES) module converts the high speed serial bit stream from the optical to electrical receiver to a parallel bit stream. The De-Framer decodes the parallel bit stream and extracts the In-phase and Quadrature (I/Q) modulation and delivers this to the digital signal processing module 903. The Control and Management module extracts the control signals from the parallel bit stream and performs tasks based on the requested information. The received I/Q data from the optical interface is frequency translated to an Intermediate Frequency in the Digital Upconverter Module (DUC). This composite signal then undergoes Crest Factor Reduction (CFR) in order to reduce the peak to average power ratio. The resultant signal is then applied to a Digital Predistorter in order to compensate for the distortion in the Power Amplifier module 905. The RRU operates in a receive mode as well as a transmit mode. The RRU receives the signal from the output duplexer and passes this signal to the Rx path or paths, depending on the number of channels. The received signal is frequency translated to an Intermediate Frequency (IF) in the receiver (Rx1 and Rx2 in Figure 10). The IF signal is further downconverted using a Digital Downconverter (DDC) module and demodulated into the In-phase and quadrature components. The recovered I/Q signal is then sent to the Framer module/ SERDES and prepared for transmission over the optical interface.

5

10

15

20

The FIG. 9. System has a multi-mode of RF or multi-carrier digital signal or optical at the input, and an RF signal at the output 910. The multi-mode of signal input allows maximum flexibility: RF-in (the "RF-in Mode") or baseband digital-in (the "Baseband-in Mode") or optical input (the "Optical-in Mode"). The FIG. 9. System comprises three key portions: a reconfigurable digital (hereinafter referred as "FPGA-based Digital") module 915, a power amplifier module 960, a receiver 965 and a feedback path 925.

5

10

15

20

The FPGA-based Digital part comprises either one of two digital processors 902,903 (e.g. FPGA), digital-to-analog converters 935 (DACs), analog-to-digital converters 940 (ADCs), and a phase-locked loop (PLL) 945. Since the FIG. 9 System has a multi-input mode, the digital processor has three paths of signal processing. For the baseband signal input path, the digital processor has implemented a digital up-converter (DUC), CFR, and a PD. For the optical input path, SERDES, Framer/ Deframer, digital up-converter (DUC), CFR, and PD are implemented. For the RF input path, analog downconverter, DUC, CFR and PD are implemented.

signals. Digital data streams from multi-channels as I-Q signals are coming to the FPGA-based Digital module and are digitally up-converted to digital IF signals by the DUC. These IF signals are then passed through the CFR block so as to reduce the signal's PAPR. This PAPR suppressed signal is digitally predistorted in order to pre-compensate for nonlinear distortions of the power amplifier.

[0015] In either input mode, the memory effects due to selfheating, bias networks, and frequency dependencies of the active device are compensated by the adaptation algorithm in the PD, as well. The coefficients of the PD are adapted by a wideband feedback which requires a very high speed ADC. The predistorted signal is passed through a DQM in order to generate the real signal and then converted to an IF analog signal by the DACs . As disclosed above, the DQM is not required to be implemented in the FPGA, or at all, in all embodiments. If the DQM is not used in the FPGA, then the AQM Implementation can be implemented with two DACs to generate real and imaginary signals 935, respectively. The gate bias voltage 950 of the power amplifier is determined by the adaptation algorithm and then adjusted through the DACs 935 in order to stabilize the linearity fluctuations due to the temperature changes in the power amplifier. The PLL 945 sweeps the local oscillation signal for the feedback part in order to translate the RF output signal to baseband, for processing in the Digital Module.

20

5

10

15

25

The power amplifier part comprises an AQM for real and complex signals (such as depicted in the embodiments shown in Figure 9) from the FPGA-based Digital module, a high power amplifier with multi-stage drive amplifiers, and a temperature sensor. In order to improve the efficiency performance of the DHMPA system, efficiency boosting techniques such as Doherty, Envelope Elimination and Restoration (EER), Envelope Tracking (ET), Envelope Following (EF), and Linear amplification using Nonlinear Components (LINC) can be used, depending upon the embodiment. These power efficiency techniques can be mixed and matched and are optional features to the fundamental RRU system. One such Doherty power amplifier

technique is presented in commonly assigned U.S. Provisional Patent Application SN 60/925,577, filed April 23, 2007, entitled N-Way Doherty Distributed Power Amplifier, incorporated herein by reference. To stabilize the linearity performance of the amplifier, the temperature of the amplifier is monitored by the temperature sensor and then the gate bias of the amplifier is controlled by the FPGA-based Digital part.

5

10

15

20

25

[0017] The feedback portion comprises a directional coupler, a mixer, a low pass filter (LPF), gain amplifiers and, and a band pass filter (BPF),. Depending upon the embodiment, these analog components can be mixed and matched with other analog components. Part of the RF output signal of the amplifier is sampled by the directional coupler and then down converted to an IF analog signal by the local oscillation signal in the mixer. The IF analog signal is passing through the LPF, the gain amplifier, and the BPF which can capture the out-of-band distortions. The output of the BPF is provided to the ADC of the FPGA-based Digital module in order to determine the dynamic parameters of the PD depending on output power levels and asymmetrical distortions due to the memory effects. In addition, temperature is also detected by the DET 970 to calculate the variation of linearity and then adjust gate bias voltage of the PA. More details of the PD algorithm and self-adaptation feedback algorithm can be appreciated from Figure 3, which shows a polynomial-based predistortion algorithm and from Figure 4, which shows the primary adaptive predistorter blocks which can be used in some embodiments of the invention.

In the case of a strict EVM requirement for broadband wireless access such as WiMAX or other OFDM based schemes (EVM < 2.5%), the CFR in the FPGA-based Digital part is only able to achieve a

small reduction of the PAPR in order to meet the strict EVM specification. In general circumstances, this means the CFR's power efficiency enhancement capability is limited. In some embodiments of the present invention, a novel technique is included to compensate the in-band distortions from CFR by use of a "Clipping Error Restoration Path" 907, hence maximizing the RRU system power efficiency in those strict EVM environments. As noted above, the Clipping Error Restoration Path has an additional DAC in the FPGA-based Digital portion and an extra UPC in the power amplifier part. The Clipping Error Restoration Path can allow compensation of in-band distortions resulting from the CFR at the output of the power amplifier. Further, any delay mismatch between the main path and the Clipping Error Restoration Path can be aligned using digital delay in the FPGA.

5

10

15

20

25

**[0019]** FIG. 9. is a block diagram showing a RRU system implemented with AQM according to another embodiment of the present invention (the "FIG. 9 System"). The digital processor of FIG. 9 System has implemented a CFR, a PD, and an analog quadrature modulator corrector (AQMC).

**[0020]** FIG. 9. is a block diagram showing a RRU system implemented with AQM and AQM-based Clipping Error Restoration Path according to another embodiment of the present invention (the "FIG. 9 System"). The Clipping Error Restoration Path in FIG. 9 System has two DACs in the FPGA-based Digital part and an AQM in lieu of the UPC in the power amplifier part.

**[0021]** Figure 10 is a block diagram showing a dual channel RRU implemented with two power amplifiers for two distinct bands. A duplexer is used to combine the two power amplifier outputs. Switches are used to isolate the transmit signals from the received signals as occu<sub>rs</sub> in a Time

Division Synchronous Code Division Multiple Access (TD-SCDMA) modulation. An additional switch is used for calibrating the Digital Predistorter for each power amplifier. Another embodiment of the RRU is extending its applications to multi-frequency bands. In an embodiment, a multi-frequency band (ie. 2 or more bands) implementation comprises adding additional channelized power amplifiers in parallel. The output of the additional power amplifiers will be combined in an N by 1 duplexer and fed to a single antenna, although multiple antenna can also be utilized in some embodiments. Another embodiment of the multi-frequency band RRU combines two or more frequency bands in one or more of the power amplifiers.

Figure 11 is a block diagram showing another embodiment of the dual channel RRU. In this embodiment the Rx switch is placed on the third port of the circulator, thereby reducing the insertion loss between the PA output and the duplexer.

Figure 12 is a block diagram showing an embodiment of an 8 channel RRU. In this embodiment, the feedback path consists of a receiver chain plus a wideband capture chain. The receiver chain is required when the RRU is switched to a receive mode. The wideband capture chain is required for capturing the wideband distortion of the power amplifier. In addition a channel calibration algorithm is required in order to insure that each power amplifier output is time, phase and amplitude aligned to each other.

# Digital Predistorter Algorithm

5

10

15

20

25

Digital Predistortion (DPD) is a technique to linearize a power amplifier (PA).

Figure 1 shows the block diagram of linear digitally predistorted PA. In the DPD block, a memory polynomial model is used as the predistortion function (Figure 3).

$$z(n) = \sum_{i=0}^{n-1} x_i(n-i) \left( \sum_{j=0}^{k-1} a_{ij} | x_i(n-i) |^j \right)$$

5 where  $a_{ii}$  are the DPD coefficients.

In the DPD estimator block, a least square algorithm is utilized to find the DPD coefficients  $a_{ij}$ , and then transfer them to DPD block. The primary DPD blocks are shown in Figure 4.

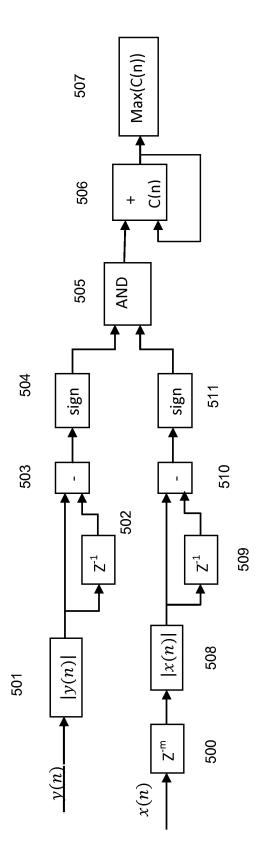

# 10 Delay Estimation Algorithm:

15

The DPD estimator compares x(n) and its corresponding feedback signal  $y(n-\Delta d)$  to find the DPD coefficients, where  $\Delta d$  is the delay of the feedback path. As the feedback path delay is different for each PA, this delay should be identified before the signal arrives at the coefficient estimation. In this design, the amplitude difference correlation function of the transmission, x(n), and feedback data, y(n), is applied to find the feedback path delay. The correlation is given by

$$C(m) = \sum_{i=0}^{N-1} sign(x(i+1) - x(i))sign(y(i+m+1) - y(i+m))$$

$$n(delay) = Max(C(m))$$

The delay n that maximizes the correlation C(m) is the feedback path delay...

Since the feedback path goes through analog circuitry, the delay between the transmission and feedback path could be a fractional sample delay. To synchronize the signals more accurately, fractional delay estimation is

necessary. To simplify the design, only a half-sample delay is considered in this design. Although smaller fractional delays can be utilized.

To get the half-sample delay data, an upsampling approach is the common choice, but in this design, in order to avoid a very high sampling frequency in the FPGA, an interpolation method is used to get the half-sample delay data. The data with integer delay and fractional delay are transferred in parallel.

The interpolation function for fractional delay is

$$y(n) = \sum_{i=0}^{3} c_i x(n+i)$$

In which  $c_i$  is the weight coefficient.

5

20

Whether the fractional delay path or the integer delay path will be chosen is decided by the result of the amplitude difference correlator. If the correlation result is odd, the integer path will be chosen, otherwise the fractional delay path will be chosen.

## 15 Phase offset Estimation and Correction Algorithm:

Phase offset between the transmission signal and the feedback signal exists in the circuit. For a better and faster convergence of the DPD coefficient estimation, this phase offset should be removed.

The transmission signal  $\boldsymbol{x}(n)$  and feedback signal  $\boldsymbol{y}(n)$  can be expressed as

$$x(n) = |x(n)| e^{j\theta_X} \ \text{ and } \ y(n) = |y(n)| e^{j\theta_Y},$$

The phase offset  $\mathrm{e}^{\mathrm{j}(\theta_x-\theta_y)}$  can be calculated through

$$e^{j(\theta_x - \theta_y)} = \frac{x(n)y(n)^*}{|x(n)||y(n)|}$$

So, the phase offset between the transmission and feedback paths is

$$e^{jo_i} = mean\left(\frac{x(n)y(n)^*}{|x(n)||y(n)|}\right)$$

The feedback signal with the phase offset removed can be calculated by

$$\overline{y}(n) = y(n)e^{jhe}$$

Magnitude correction:

5

As the gain of the PA may change slightly, the feedback gain should be corrected to avoid the error from the gain mismatch. The feedback signal is corrected according to the function

$$\bar{y}(n) = y(n) \frac{\sum_{i=1}^{N} |x(i)|}{\sum_{i=1}^{N} |y(i)|}$$

The choice of N will depend on the accuracy desired.

# **QR RLS Adaptive Algorithm:**

The least square solution for DPD coefficient estimation is formulated as

$$F(x(n)) = y(n)$$

$$F(x(n)) = \sum_{i=1}^{N} \sum_{j=0}^{K} a_{ij} x(n-i) |x(n-i)|^{j}$$

Define  $h_k = x(n-i)|x(n-i)|^j$ ,  $w_k = a_{ij}$ , where k = (i-1)N+j. The least square formulation can be expressed as:

$$\sum_{k=1}^{N\times K} w_k h_k = y(n)$$

In this design, QR-RLS algorithm (Haykin, 1996) is implemented to solve this problem. The formulas of QR\_RLS algorithm are

$$\begin{cases} d(i) \triangleq y(i) - h_i \overline{w} \\ \overline{w}_i \triangleq w_i - \overline{w} \\ q_i \triangleq \varphi_i^{*/2} [w_i - \overline{w}] \end{cases}$$

where  $\phi_i$  is a diagonal matrix, and  $q_i$  is a vector.

The QR\_RLS algorithm gets the ith moment  $\phi_i$  and  $q_i$  from its (i-1)th moment through a unitary transformation:

$$A = \begin{bmatrix} \varphi_i^{1/2} & 0 \\ q_i^* & e_a^*(i)\gamma^{\frac{1}{2}}(i) \\ h_i \Phi_i^{-\frac{*}{2}} & \gamma^{\frac{1}{2}}(i) \end{bmatrix} = \begin{bmatrix} \lambda^{1/2}\varphi_{i-1}^{*/2} & h_i^* \\ \lambda^{1/2}q_{i-1}^* & d(i)^* \\ 0 & 1 \end{bmatrix} \theta_i$$

$\boldsymbol{\theta}_i$  is a unitary matrix for unitary transformation.

To apply QR\_RLS algorithm more efficiently in FPGA, a squared-root-free Givens rotation is applied for the unitary transformation process (E.N. Frantzeskakis, 1994)

$$\begin{bmatrix} a_1 & a_2 & \cdots & a_n \\ b_1 & b_2 & \cdots & b_n \end{bmatrix} = \begin{bmatrix} \sqrt{k_a} & 0 \\ 0 & \sqrt{k_b} \end{bmatrix} \begin{bmatrix} a_1' & a_2' & \cdots & a_n' \\ b_1' & b_2' & \cdots & b_n' \end{bmatrix}$$

$$\begin{bmatrix} a_1' & a_2' & \cdots & a_n' \\ b_1' & b_2' & \cdots & b_n' \end{bmatrix} \theta = \begin{bmatrix} \sqrt{k_a'} & 0 \\ 0 & \sqrt{k_b'} \end{bmatrix} \begin{bmatrix} 1 & a_2" & \cdots & a_n" \\ 0 & b_2" & \cdots & b_n" \end{bmatrix}$$

$$k_a' = k_a a_1^2 + k_b b_1^2$$

$$k_b' = \frac{k_a k_b}{k_a'}$$

$$k_b' = \frac{k_a k_b}{k_a'}$$

$$a_j' = (k_a a_1 a_j + k_b b_1 b_j) / k_a'$$

$$b_j' = -b_1 a_j + a_1 b_j$$

For RLS algorithm, the ith moment is achieved as below:

$$\begin{bmatrix} \lambda^{1/2} \varphi_{i-1}^{*/2} & h_i^* \\ \lambda^{1/2} q_{i-1}^* & \overline{d(i)^*} \\ 0 & 1 \end{bmatrix} \theta_i = \begin{bmatrix} \overline{\varphi_i^{1/2}} & \underline{0} \\ \overline{q_i^*} & \overline{e_a^*(i) \gamma^{\frac{1}{2}}(i)} \\ \overline{h_i \Phi_i^{-\frac{*}{2}}} & \overline{\gamma_2^{\frac{1}{2}}(i)} \end{bmatrix} \begin{bmatrix} \sqrt{k_a} & 0 \\ 0 & \sqrt{k_b} \end{bmatrix}$$

wi can be obtained by solving

$$\overline{\Phi^{\frac{*}{2}}}[w_i - \overline{w}] = \overline{q_i}$$

In the iterative process, a block of data (in this design, there is 4096 data in one block) is stored in memory, and the algorithm uses all the data in memory to estimate the DPD coefficient. In order to make the DPD performance more stable, the DPD coefficients are only updated after one block of data are processed. The matrix A will be used for the next iteration process, which will make the convergence faster.

To make sure the stable performance of DPD, a weighting factor f is used when updating the DPD coefficient as

$$w_i = f \times w_{i-1} + (1 - f)w_i$$

The DPD coefficient estimator calculates coefficients  $w_i$  by using QR\_RLS algorithm. These  $w_i$  are copied to the DPD block to linearize the PA.

# **Channel Calibration Algorithm**

5

10

15

20

The 8 channel RRU in Figure 12 has 16 distinct power amplifiers. Half the power amplifiers are designed for one band and the other for a second band. The bands are hereafter referred to as band A and band B, they occupy two distinct frequencies. The 8 channel RRU uses 8 antennas and both bands will coexist on each antenna. In order to maximize performance, each power amplifier's output signal needs to be time, phase and amplitude aligned with respect to each other. The antenna calibration algorithms consist of three distinct approaches: 1) A Pilot Tone is injected into each PA 2) a Reference Modulated signal is transmit through each PA 3) the Real Time I/Q data is used as the reference signal. The Pilot Tone approach requires the injection of a single carrier IF tone that will be tracked in either the feedback calibration path or the individual PA's receiver. Each transmitter

path for band A will be time, phase and amplitude aligned with respect to each other, similarly for band B. The Reference Modulated approach will utilize a stored complex modulated signal which will be transmitted through each of the band A PAs, similarly for the band B PAs. The transmitters will then be time, phase and amplitude aligned with respect to each other. Either the feedback calibration path or the individual receivers can be used for obtaining the PA output signals. The Real Time approach will operate on the real-time transmitted signals. This approach will utilize the DPD time alignment, phase and magnitude offset information to synchronize each PA output with respect to each other.

10

15

20

5

In summary, the RRU system of the present invention could enhance the performance for the efficiency and linearity more effectively since the RRU system is able to implement CFR, DPD and adaptation algorithm in one digital processor, which subsequently saves hardware resources and processing time. The high power efficiency of RF power amplifiers inside the RRU means that less thermal dissipation mechanism such as heat sink is needed; therefore, significantly reducing the size and volume of the mechanical housing. This smaller RRU can then enable service provider to deploy the RRU in areas where heavy or large RRU could not be deployed, such as pole tops, top of street lights, etc. due to lack of real estate, or weight limitation, wind factor, type of safety issues. The RRU system is also reconfigurable and field-programmable since the algorithms and power efficiency enhancing features can be adjusted like software in the digital processor at anytime.

Moreover, the RRU system is agnostic to modulation schemes such as QPSK, QAM, OFDM, etc. in CDMA, TD-SCDMA, GSM, WCDMA, CDMA2000, and wireless LAN systems. This means that the RRU system is capable of supporting multi-modulation schemes, multi-carriers and multi-channels. The multi-frequency bands benefits mean that mobile operators can deploy fewer RRUs to cover more frequency bands for more mobile subscribers; hence significantly reducing CAPEX and OPEX. Other benefits of the RRU system includes correction of PA non-linearities in repeater or indoor coverage systems that do not have the necessary baseband signals information readily available.

5

10

15

Although the present invention has been described with reference to the preferred embodiments, it will be understood that the invention is not limited to the details described thereof. Various substitutions and modifications have been suggested in the foregoing description, and others will occur to those of ordinary skill in the art. Therefore, all such substitutions and modifications are intended to be embraced within the scope of the invention as defined in the appended claims.

## **ABSTRACT**

A remote radio head unit (RRU) system for achieving high efficiency and high linearity in wideband communication systems is disclosed. The present invention is based on the method of adaptive digital predistortion to linearize a power amplifier inside the RRU. The power amplifier characteristics such as variation of linearity and asymmetric distortion of the amplifier output signal are monitored by a wideband feedback path and controlled by the adaptation algorithm in a digital module. Therefore, the present invention could compensate the nonlinearities as well as memory effects of the power amplifier systems and also improve performances, in terms of power added efficiency, adjacent channel leakage ratio and peak-to-average power ratio. The present disclosure enables a power amplifier system to be field reconfigurable and support multi-modulation schemes (modulation agnostic), multi-carriers, multi-frequency bands and multi-channels. As a result, the remote radio head system is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems.

20

15

5

FIG. 1. Remote Radio Head Unit

Figure 3. Polynomial based digital predistorter function

FIG. 4. Digital Predistortion Block Diagram

Figure 7

Figure 8

Figure 9 Digital Hybrid Module

# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

# **PROVISIONAL APPLICATION**

5 FOR

## **UNITED STATES PATENT**

**FOR**

10

# MULTI-BAND WIDEBAND POWER AMPLIFIER DIGITAL PREDISTORTION SYSTEM

15 **INVENTORS**

Wan-Jong Kim, Citizen of Korea

Kyoung-Joon Cho, Citizen of Korea

Shawn Patrick Stapleton, Citizen of Canada

20

# **SPECIFICATION**

25 **RELATED APPLICATIONS**

This application claims the benefit of the following applications:

- US Patent Appn SN 12/415,676, filed 3/31/2009, and through it U.S. Patent Appn SN 61/041,164, filed 3/31/2008; which also claims the benefit of U.S. Provisional Patent Application S.N. 61/172,642, filed 4/24/2009; US Patent Application SN 12/603,419, filed 10/21/2009, and through it US Patent

- 5 Application SN 12/108,507, filed 4/23/2008, and through it U.S. Patent Application SN 60/925,577, filed 4/23/2007;

- US Patent Application SN 12/330,451 filed 12/8/2008, and through it US Patent Application SN 61/012,416, filed 12/07/2007;

- US Patent Application SN 11/961,969, filed 12/20/2007, and through it US Patent Application SN 60/877 035, filed 12/26/2006, and US Patent Application SN

- 10 Application SN 60/877,035, filed 12/26/2006, and US Patent Application SN 60/925,603, filed 4/23/2007;

- US Patent Application SN 12/108,502, filed 4/23/2008, and through it US Patent Application SN 12/021,241, filed 1/28/2008, and through that to US Patent Application SN 60/897,746, filed 1/26/2007.

- US Patent Application S.N. \_\_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW-1018, entitled MULTI-BAND WIDEBAND POWER AMPLIFIER DIGITAL PREDISTORTION SYSTEM AND METHOD and naming as inventors Wan-Jong Kim, Kyoung-Joon Cho, and Shawn Patrick Stapleton.

- US Patent Application S.N. \_\_\_\_\_\_\_, filed 12/21/2009, attorney's docket DW1019, entitled REMOTE RADIO HEAD UNIT SYSTEM WITH WIDEBAND POWER

AMPLIFIER AND METHOD and naming as inventors Chengxun Wang and Shawn

Patrick Stapleton.