| UNITED STATES PATENT AND TRADEMARK OFFICE                                                 |

|-------------------------------------------------------------------------------------------|

| BEFORE THE PATENT TRIAL AND APPEAL BOARD                                                  |

| INNOSCIENCE (ZHUHAI) TECHNOLOGY COMPANY, LTD., AND INNOSCIENCE AMERICA, INC., Petitioner, |

| v.                                                                                        |

| EFFICIENT POWER CONVERSION CORPORATION, Patent Owner.                                     |

| IPR2023-01384<br>U.S. Patent 10,312,335                                                   |

PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT 10,312,335

### TABLE OF CONTENTS

| 1.    | Introd | Introduction1                                                                                                                                     |    |  |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| II.   | Techi  | nological Background                                                                                                                              | 2  |  |

| III.  | The '  | 335 Patent                                                                                                                                        | 8  |  |

|       | A.     | Overview                                                                                                                                          | 8  |  |

|       |        | 1. The alleged invention                                                                                                                          | 8  |  |

|       |        | 2. Self-aligned ledges                                                                                                                            | 11 |  |

|       | B.     | Prosecution History                                                                                                                               | 13 |  |

|       |        | 1. Allowance of the '335 Patent                                                                                                                   | 13 |  |

|       |        | 2. Priority claim                                                                                                                                 | 14 |  |

| IV.   | State  | ment of Precise Relief Requested                                                                                                                  | 16 |  |

|       | A.     | Claims                                                                                                                                            | 16 |  |

|       | B.     | Grounds                                                                                                                                           | 17 |  |

| V.    | State  | ment of Facts                                                                                                                                     | 17 |  |

| VI.   | Level  | l of Ordinary Skill                                                                                                                               | 18 |  |

| VII.  | Clain  | n Construction                                                                                                                                    | 18 |  |

|       | A.     | "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer" | 19 |  |

|       | B.     | "self-aligned" ledges                                                                                                                             |    |  |

| VIII. |        | nds 1 and 2: <i>Saxler</i> , Alone (Ground 1) or in View of <i>Yoshida</i> and 2) Renders Obvious Claims 1-7                                      | 24 |  |

|       | A.     | Overview of Grounds 1 and 2                                                                                                                       | 24 |  |

|       |        | 1. Ground 1: <i>Saxler</i>                                                                                                                        | 25 |  |

|    | 2.    | Yoshida                                                                                                                                                                                                                                                                                                                                                                          | 27 |

|----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 3.    | Ground 2: The combination of Saxler in view of Yoshida                                                                                                                                                                                                                                                                                                                           | 28 |

|    | 4.    | Ground 2: Motivation to Combine                                                                                                                                                                                                                                                                                                                                                  | 29 |

| B. | Inde  | pendent Claim 1                                                                                                                                                                                                                                                                                                                                                                  | 35 |

|    | 1.    | [1p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                                                                                                                                                                             | 35 |

|    | 2.    | [1a] a GaN layer;                                                                                                                                                                                                                                                                                                                                                                | 36 |

|    | 3.    | [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                                                                                                                                                                            | 37 |

|    | 4.    | [1c]: a source contact and a drain contact formed on the barrier layer;                                                                                                                                                                                                                                                                                                          | 38 |

|    | 5.    | [1d]: a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and                                                                                                                                              | 39 |

|    | 6.    | [1e]: a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,                                                                                                                                                                                                                                             | 45 |

|    | 7.    | [1f]: wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively. | 48 |

| C. | _     | im 2]: wherein the pair of horizontal ledges of the p-type material are self-aligned.                                                                                                                                                                                                                                                                                            |    |

| D. |       | im 3]: wherein the barrier layer comprises aluminum                                                                                                                                                                                                                                                                                                                              | 50 |

|    | galli | um nitride (AlGaN).                                                                                                                                                                                                                                                                                                                                                              | 52 |

|     | E. | betwo | m 4]: wherein the p-type gate material has a first width een the side surfaces of the p-type gate material and the metal has a second width between sidewalls of the gate l, the second width being less than the first width | 52 |

|-----|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | F. | Indep | pendent Claim 5                                                                                                                                                                                                               | 52 |

|     |    | 1.    | [5p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                          | 52 |

|     |    | 2.    | [5a] a GaN layer;                                                                                                                                                                                                             | 53 |

|     |    | 3.    | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                         | 53 |

|     |    | 4.    | [5c]: a source contact and a drain contact formed on the barrier layer;                                                                                                                                                       | 53 |

|     |    | 5.    | [5d]: a p-type gate material formed above the barrier layer and between the source and drain contacts;                                                                                                                        | 53 |

|     |    | 6.    | [5e]: a gate metal disposed on the p-type gate material,                                                                                                                                                                      | 53 |

|     |    | 7.    | [5f]: wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and                              | 54 |

|     |    | 8.    | [5g]: (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                                                                                  | 54 |

|     | G. | _     | m 6]: wherein the barrier layer comprises aluminum m nitride (AlGaN)                                                                                                                                                          | 55 |

|     | Н. | _     | m 7]: wherein the pair of self-aligned ledges are symmetric respect to the gate metal.                                                                                                                                        | 55 |

| IX. |    |       | Saxler in View of Yoshida, Beach, and Shenoy Renders aims 2 and 5-7                                                                                                                                                           | 57 |

|     | A. | Over  | view of Ground 3                                                                                                                                                                                                              | 57 |

## Petition for *Inter Partes* Review U.S. Patent 10,312,335

|    | 1.    | Beach                                                                             | 57 |

|----|-------|-----------------------------------------------------------------------------------|----|

|    | 2.    | Shenoy                                                                            | 58 |

|    | 3.    | Motivation to Combine                                                             | 59 |

| B. | [Clai | m 2]                                                                              | 64 |

| C. | Inde  | pendent Claim 5                                                                   | 65 |

|    | 1.    | [5p]                                                                              | 65 |

|    | 2.    | [5a]                                                                              | 65 |

|    | 3.    | [5b]                                                                              | 65 |

|    | 4.    | [5c]                                                                              | 65 |

|    | 5.    | [5d]                                                                              | 66 |

|    | 6.    | [5e]                                                                              | 66 |

|    | 7.    | [5f]                                                                              | 66 |

|    | 8.    | [5g]                                                                              | 66 |

| D. | [Clai | m 6]                                                                              | 66 |

| Ε. | [Clai | m 7]                                                                              | 67 |

|    |       | and 5: <i>Yoshida</i> , Either Alone or In View of <i>Saxler</i> Renders aims 1-7 | 67 |

| A. |       | ınd 4: <i>Yoshida</i> Alone                                                       |    |

| В. | Grou  | ınd 5                                                                             | 68 |

|    | 1.    | Ground 5: The Combination of <i>Yoshida</i> in View of <i>Saxler</i>              | 68 |

|    | 2.    | Ground 5: Motivation to Combine                                                   | 69 |

| C. | Inde  | pendent Claim 1                                                                   | 71 |

|    | 1.    | [1p]                                                                              | 71 |

X.

## Petition for *Inter Partes* Review U.S. Patent 10,312,335

|    | 2.   | [la]                                                                 | 72 |

|----|------|----------------------------------------------------------------------|----|

|    | 3.   | [1b]                                                                 | 72 |

|    | 4.   | [1c]                                                                 | 74 |

|    | 5.   | [1d]                                                                 | 74 |

|    | 6.   | [1e]                                                                 | 81 |

|    | 7.   | [1f]                                                                 | 83 |

| D. | [Cla | im 2]                                                                | 84 |

| E. | [Cla | im 3]                                                                | 84 |

| F. | [Cla | im 4]                                                                | 84 |

| G. | Inde | pendent Claim 5                                                      | 85 |

|    | 1.   | [5p]                                                                 | 85 |

|    | 2.   | [5a]                                                                 | 85 |

|    | 3.   | [5b]                                                                 | 85 |

|    | 4.   | [5c]                                                                 | 85 |

|    | 5.   | [5d]                                                                 | 86 |

|    | 6.   | [5e]                                                                 | 86 |

|    | 7.   | [5f]                                                                 | 86 |

|    | 8.   | [5g]                                                                 | 87 |

| Н. | [Cla | im 6]                                                                | 87 |

| I. | [Cla | im 7]                                                                | 87 |

|    |      | Yoshida in View of Saxler, Beach, and Shenoy Renders laims 2 and 5-7 | 88 |

| Δ  | Ove  | rview of Ground 6                                                    | 88 |

XI.

## Petition for *Inter Partes* Review U.S. Patent 10,312,335

|       |       | 1.       | Motivation to Combine            | 88   |

|-------|-------|----------|----------------------------------|------|

|       | B.    | [Clain   | m 2]                             | 92   |

|       | C.    | Indep    | pendent Claim 5                  | 94   |

|       |       | 1.       | [5p]                             | 94   |

|       |       | 2.       | [5a]                             | 94   |

|       |       | 3.       | [5b]                             | 95   |

|       |       | 4.       | [5c]                             | 95   |

|       |       | 5.       | [5d]                             | 95   |

|       |       | 6.       | [5e]                             | 95   |

|       |       | 7.       | [5f]                             | 95   |

|       |       | 8.       | [5g]                             | 96   |

|       | D.    | [Clain   | m 6]                             | 96   |

|       | E.    | [Clain   | m 7]                             | 97   |

| XII.  | Discr | etionai  | ry Denial Is Not Warranted       | 97   |

|       | A.    | Fintiv   | Denial Is Improper               | 97   |

|       | B.    | 35 U.    | S.C. § 325(d) Denial Is Improper | 98   |

| XIII. | Mand  | latory ] | Notices                          | 98   |

|       | A.    | Real     | Party-in-Interest                | 98   |

|       | B.    | Relat    | ed Matters                       | 98   |

|       | C.    | Lead     | and Back-Up Counsel              | 99   |

| XIV.  | Groui | nds for  | Standing                         | .101 |

| XV.   | Conc  | lusion   |                                  | .101 |

### **Table of Authorities**

|                                                                                         | Page(s)        |

|-----------------------------------------------------------------------------------------|----------------|

| Cases                                                                                   |                |

| CUPP Comput. AS v. Trend Micro Inc. 53 F.4th 1376 (Fed. Cir. 2022)                      | 18             |

| Honeywell Int'l Inc. v. Universal Avionics Sys. Corp., 488 F.3d 982, 9 (Fed. Cir. 2007) |                |

| <i>In re Thorpe</i> 777 F.2d 695 (Fed. Cir. 1985)                                       | passim         |

| Intel Corp. v. PACT XXP Schweiz AG 61 F.4th 1373 (Fed. Cir. 2023)                       | 33, 71         |

| Kamstrup A/S v. Axioma Metering UAB<br>43 F.4th 1374 (Fed. Cir. 2022)                   | passim         |

| KEYnetik, Inc. v. Samsung Elecs. Co.<br>837 F. App'x 786 (Fed. Cir. 2020)               | 20             |

| KSR Int'l Co. v. Teleflex Inc. 550 U.S. 398 (2007)                                      | 33, 71         |

| Phillips v. AWH Corp. 415 F.3d 1303 (Fed. Cir. 2005)                                    | 18             |

| United Therapeutics Corp. v. Liquidia Techs., Inc. 74 F.4th 1360 (Fed. Cir. 2023)       | 24, 51, 54, 64 |

| Statutes                                                                                |                |

| 35 U.S.C. § 102                                                                         | 13             |

| 35 U.S.C. § 102(b)                                                                      | 16             |

| 35 U.S.C. § 103                                                                         | 17             |

| 35 U.S.C. § 311                                                                         | 16             |

|                       | Petition for <i>Inter Partes</i> Review U.S. Patent 10,312,335 |

|-----------------------|----------------------------------------------------------------|

| 35 U.S.C. § 325(d)    | 98                                                             |

| Regulations           |                                                                |

| 37 C.F.R. § 42.100(b) | 18                                                             |

| 37 C.F.R. § 42.22(c)  | 17                                                             |

### TABLE OF EXHIBITS

| Exhibit  | Description                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1001 | U.S. Patent No. 10,312,335 B2 to Cao et al. ("the '335 patent")                                                                                                                                |

| Ex. 1002 | Prosecution History of the '335 patent                                                                                                                                                         |

| Ex. 1003 | Declaration of Dr. James Richard Shealy ("Shealy")                                                                                                                                             |

| Ex. 1004 | Curriculum Vitae of Dr. James Richard Shealy                                                                                                                                                   |

| Ex. 1005 | Japanese Patent Publication No. JP H11-261053 to Yoshida                                                                                                                                       |

| Ex. 1006 | Certified Translation of Japanese Patent Publication No. JP H11-261053 to Yoshida ("Yoshida")                                                                                                  |

| Ex. 1007 | U.S. Patent Application Publication No. US 2006/0108606 A1 to Saxler et al. ("Saxler")                                                                                                         |

| Ex. 1008 | U.S. Patent Application Publication No. US 2007/0007547 A1 to Beach ("Beach")                                                                                                                  |

| Ex. 1009 | R.V. Shenoy and M. Datta, <i>Effect of Mask Wall Angle on Shape Evolution during Through-Mask Electrochemical Micromachining</i> , 143 J. Electrochemical Soc'y, pp. 544-549 (1996) ("Shenoy") |

| Ex. 1010 | U.S. Patent No. 5,905,274 to Ahn et al. ("Ahn")                                                                                                                                                |

| Ex. 1011 | U.S. Patent Application Publication No. US 2010/0258843 A1 to Lidow et al. ("Lidow")                                                                                                           |

| Ex. 1012 | U.S. Patent No. 9,748,347 to Cao et al. ("the '347 patent")                                                                                                                                    |

| Ex. 1013 | Prosecution History of the '347 patent                                                                                                                                                         |

| Ex. 1014 | Chua Xu et al., The Leakage Current of the Schottky Contact on the Mesa Edge of AlGaN/GaN Heterostructure, 28 IEEE Electron Device Letters, pp. 942-944 (2007) ("Xu")                          |

| Ex. 1015 | U.S. Patent Application Publication No. US 2002/0066908 A1 to Smith ("Smith")                                                                                                                  |

| Exhibit  | Description                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1016 | U.S. Patent Application Publication No. US 2006/0273347 A1 to Hikita et al. ("Hikita")                                                                                                                           |

| Ex. 1017 | U.S. Patent Application Publication No. US 2009/0072272 A1 to Suh et al. ("Suh")                                                                                                                                 |

| Ex. 1018 | X. Hu et al., Enhancement mode AlGaN/GaN HFET with selectively grown pn junction gate, 36 Electronics Letters, pp. 753-754 (2000) ("Hu")                                                                         |

| Ex. 1019 | U.S. Patent Application Publication No. US 2005/0087763 A1 to Kanda et al. ("Kanda")                                                                                                                             |

| Ex. 1020 | Yasushiro Uemoto et al., A Normally-off AlGaN/GaN Transistor with $R_{on}A=2.6\Omega cm^2$ and $BV_{ds}=640V$ Using Conductivity Modulation, 2006 International Electron Devices Meeting, IEEE (2006) ("Uemoto") |

| Ex. 1021 | U.S. Patent Application Publication No. US 2006/0019435 A1 to Sheppard et al. ("Sheppard")                                                                                                                       |

| Ex. 1022 | Order Granting Defendants' Unopposed Motion for Stay Pending ITC Proceeding, Case No. 2:23-cv-04026-AB-AS, Central District of California (July 27, 2023)                                                        |

| Ex. 1023 | Dietrich W. Widmann, <i>Metallization for Integrated Circuits Using a Lift-Off Technique</i> , 11 IEEE Journal of Solid-State Circuits, pp. 466-471 (1976) ("Widmann")                                           |

| Ex. 1024 | Reserved                                                                                                                                                                                                         |

| Ex. 1025 | Declaration of Kelley Hayes Greenhill                                                                                                                                                                            |

| Ex. 1026 | Declaration of Shauna Wiest                                                                                                                                                                                      |

| Ex. 1027 | International Publication No. WO 2005/057624 to Beach, published June 23, 2005 (" <i>Beach-II</i> ")                                                                                                             |

| Ex. 1028 | Petitioner and Complainant's Proposed Claim Construction, ITC 337-TA-1366                                                                                                                                        |

| Exhibit  | Description                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1029 | C. S. Suh et al., "p-GaN/AlGaN/GaN Enhancement-Mode HEMTs, 2006 64th Device Research Conference, June 2006, pp. 163-164 ("Suh 2006") |

<sup>\*</sup>Emphasis added unless otherwise noted.

#### I. Introduction

Petitioner request *inter partes* review and cancellation of claims 1-7 of U.S. Patent No. 10,312,335 ("the '335 patent") (Ex. 1001).

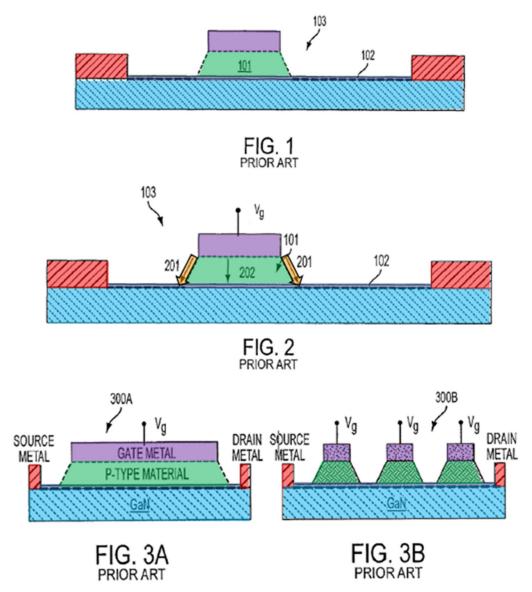

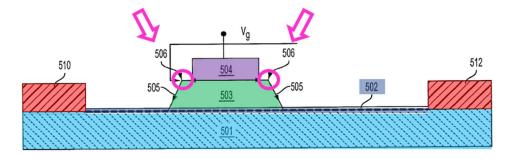

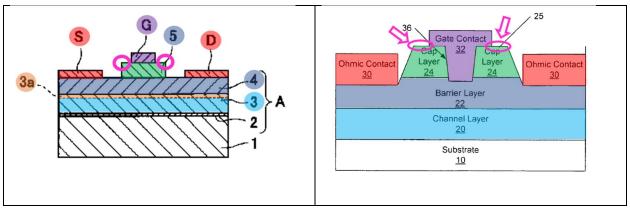

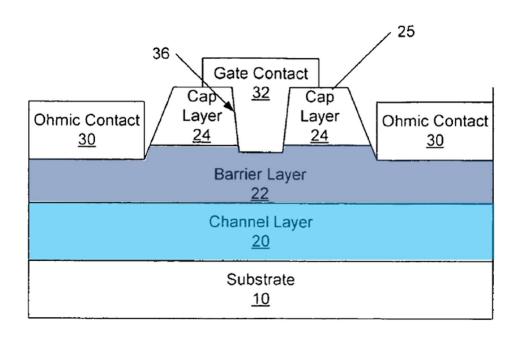

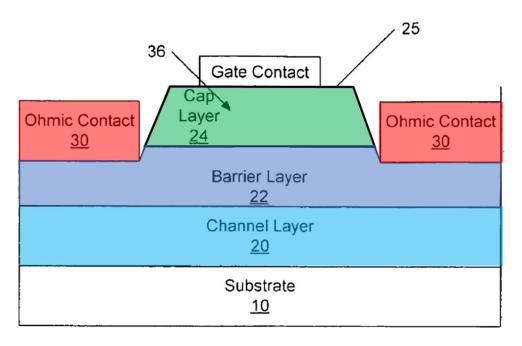

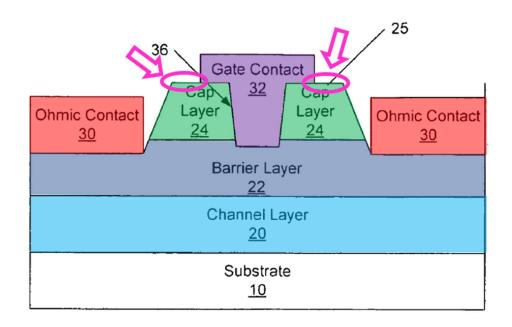

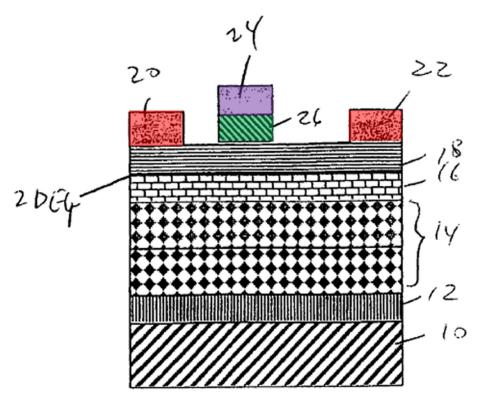

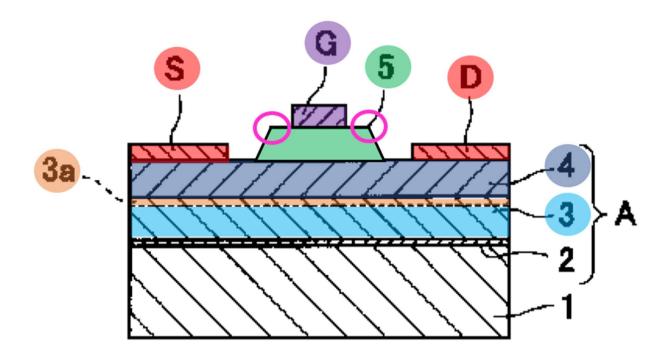

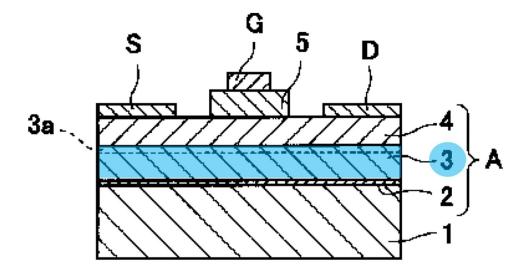

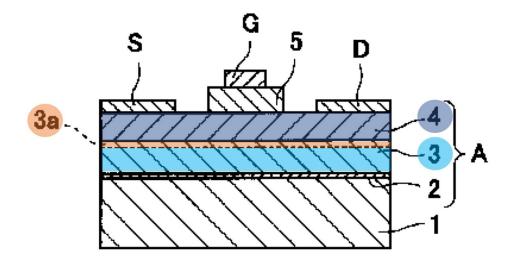

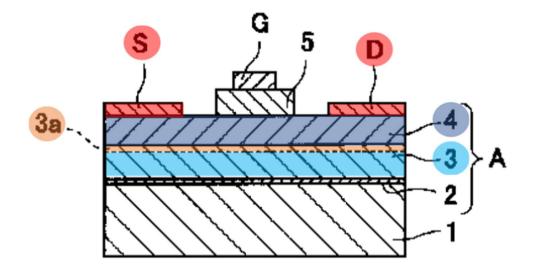

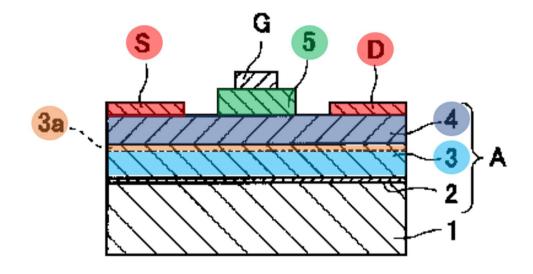

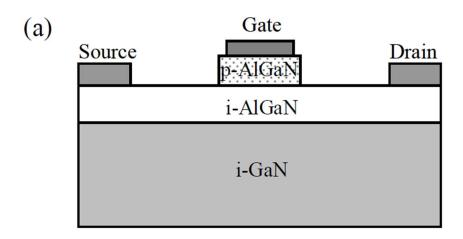

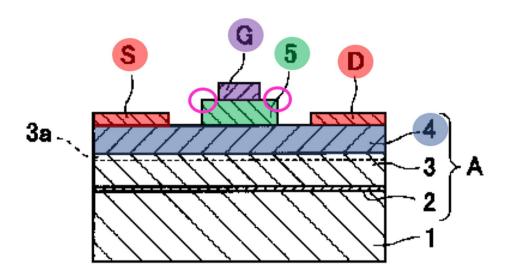

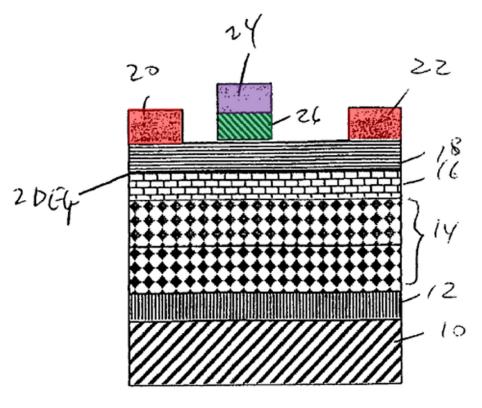

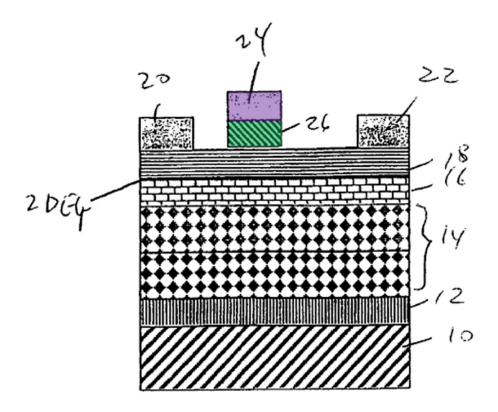

Independent claims 1 and 5 describe a conventional enhancement-mode gallium nitride (GaN) high electron mobility transistor (HEMT) device, including a GaN channel layer below an AlGaN barrier. Ex. 1001, claims 1, 5. The claims require a stacked gate structure resting on the barrier layer between source and drain electrodes. *Id.* That gate structure has two layers: a p-type gate material with sloped sidewalls below an overlying gate metal contact and a two-dimensional electron gas (2DEG) formed when a current is applied to the gate metal. *Id.* The patent admits that *all* these features were conventional. Ex. 1001, 1:21-2:30, Figs. 1-2, 3A-3B; Shealy, [0044]-[0045].

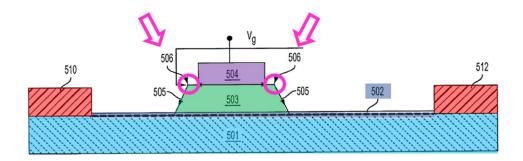

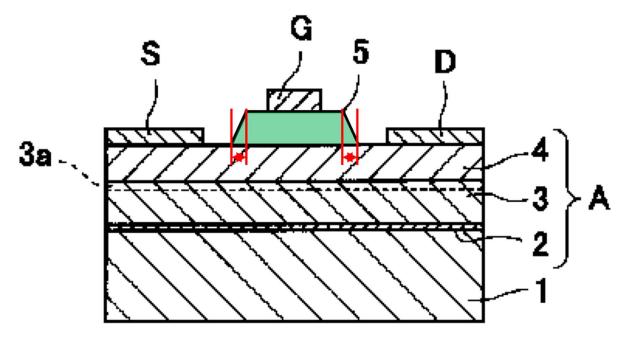

Ex. 1001, Fig. 5.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> All figures in this Petition containing color are annotated.

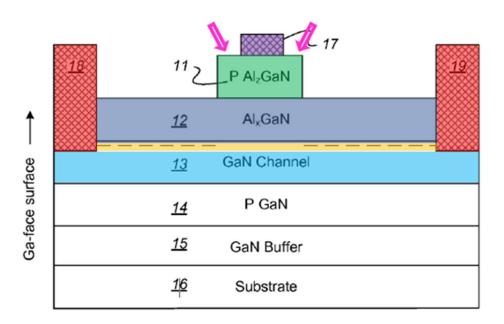

The claims also require that the width of the gate metal is less than the width of the top of p-type gate material, giving rise to a pair of horizontal **ledges** on the p-type gate material's surface to either side of the gate metal. Ex. 1001, claims 1, 5. These **ledges** are the '335 patent's sole point of alleged novelty. But such ledges were *also* well known and conventional, long found in the prior art. *Yoshida* (Ex. 1005; Ex. 1006), published in 1999, shows such ledges in a gate structure of a GaN HEMT consisting of a gate metal stacked on a p-type GaN material (*Yoshida*, Fig. 1). So does *Hu* (Ex. 1018), published in 2000 (*e.g.*, *Hu*, Fig. 1); *Smith* (Ex. 1015), published in 2002 (*e.g.*, *Smith*, Fig. 3); *Saxler* (Ex. 1007), published in 2006 (*e.g.*, *Saxler*, Figs. 1A, 2B, [0052]); and *Suh* (Ex. 1017), published in 2009 (*e.g.*, *Suh*, Fig. 6).

#### II. Technological Background

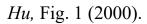

GaN power transistors have a large band gap, which drives up breakdown voltage and makes them attractive for high power applications. Ex. 1001, 1:30-49; Shealy, [055]. They were well known long before the '335 patent. *E.g.*, *Smith*, [0004]-[0010] (discussing "well known" features of GaN HEMT devices). Conventional features of such transistors include a GaN channel and AlGaN barrier layers, at the heterojunction of which a two-dimensional electron gas (2DEG) region forms, as well as source and drain electrodes, and a gate structure

including **GaN gate materials** under a **gate metal**. Ex. 1001, 1:28-2:26; *Yoshida*, Abstract; *Suh*, [0002]-[0005], [0015], Figs. 1, 6-7; Shealy, [055]].

Enhancement-mode GaN transistors are normally off, meaning no drain current flows through the 2DEG without applying positive voltage to the gate. Ex. 1001, 1:50-53, 1:64-2:2; *Hu*, 1; Shealy, [056]. These devices achieve the normally-off state in part with a **GaN layer**, often doped p-type, in the gate structure under a **gate metal**, which increases the gate voltage to a positive value. Ex. 1001, 1:50-53, 1:64-2:2; *Hu*, 1; Shealy, [055].

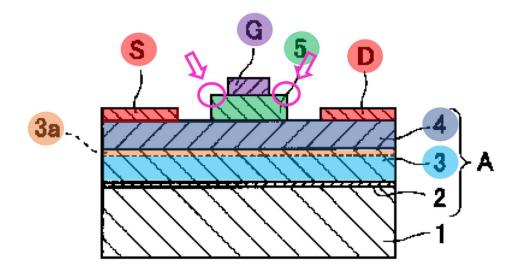

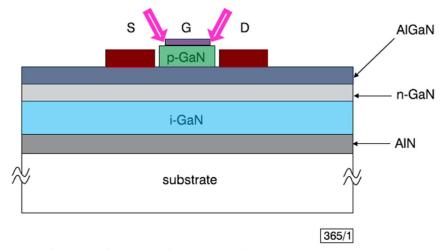

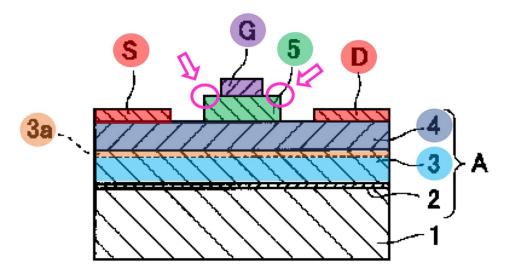

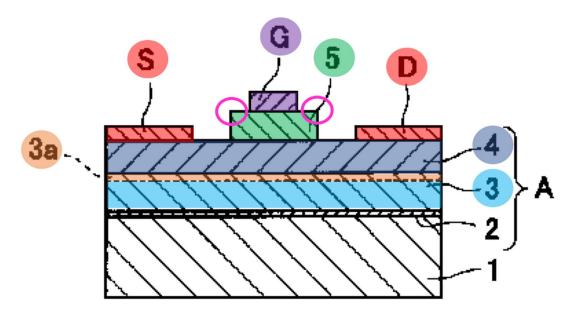

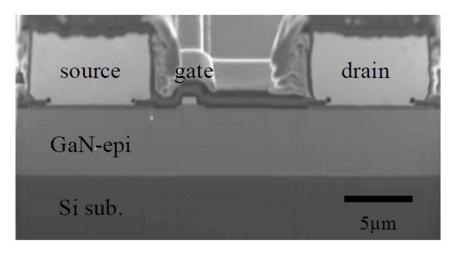

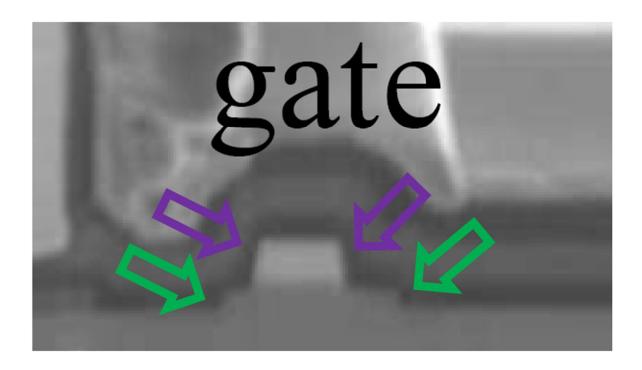

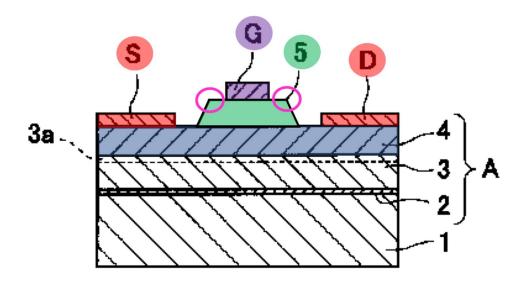

Example GaN HEMT arrangements in publications ranging from 1999 through 2009, the earliest claimed priority date of the '335 patent, are shown below. Shealy, [057]. Note the horizontal ledges at the surface of the p-type GaN gate materials:

Yoshida, Fig. 1 (1999).

Fig. 1 Schematic diagram of structure of pn junction regrown gate HFET

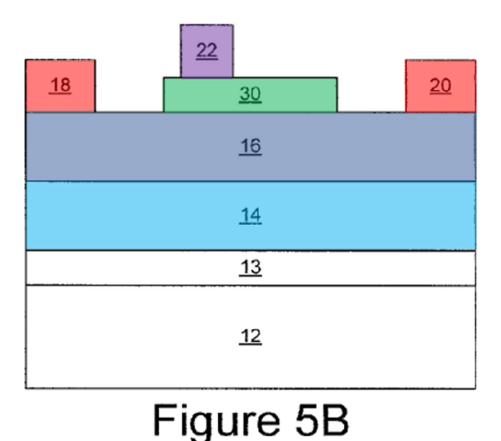

## Figure 5B

Smith, Fig. 5B (2002).

Saxler, Fig. 1A (2006).

Suh, Fig. 6 (2009).

As these examples illustrate, the sole point of alleged novelty of the '335 patent, horizontal ledges at the surface of p-type GaN gate materials, were common—as were the other features of the claims. Shealy, [058].

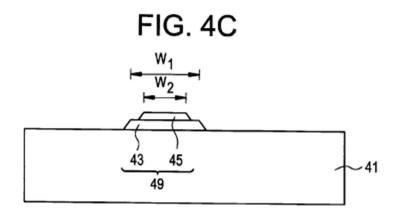

The prior art also included many different methods of manufacturing features of GaN HEMT devices. Shealy, [059] (citing *Beach*, [040]; *Ahn*, *Xu*, *Saxler* [064]; *Sheppard* [0044]). For example, single-mask techniques to self-align stacked gate structures were long known. *Beach*, [0040]; Shealy, [059]. Conventional etching techniques achieved sloped sidewalls, which were known to increase leakage paths. Ex. 1001, 1:64-2:8, Fig. 2; *Saxler*, [0064], Figs. 1A-1B; *Ahn*; *Xu*; *Sheppard*, [0044]; Shealy, [059]. And it was conventional to create undercuts under photomasks to isotropically etch metals. *Shenoy*; Shealy, [059].

A POSITA would have been familiar with many methods of making stepped gate structures with horizontal ledges, including (i) sequential masking and etching steps, (ii) lift off techniques, and (iii) self-aligned techniques. Shealy, [060] (citing Yoshida, [0022]-[0023]; Hu, 1; Smith, [0040]-[041]; Saxler, [0064]-[0066]; Suh, [056]). For example, Yoshida discloses masking and etching the p-type GaN layer 5, then depositing the gate electrode. Yoshida, [0022]-[0023]; Shealy, [060]. Hu grows gate layers in "selective areas defined by openings in an SiO<sub>2</sub> mask." Hu, 1; Shealy, [060]. Smith fabricates its gate structure by patterning the GaN cap layer, using conventional etching to remove portions of it, then forming a gate electrode on the GaN segment. Smith, [0040]-[0041]; Shealy, [060]. Smith also uses "conventional photolithographic techniques and mask alignment tools" to align the edges of a cap layer and gate in some embodiments, i.e., self-alignment. Smith,

[0041]; Shealy, [060]. *Saxler* discloses sequential masking, etching, and deposition steps to form its stacked gate structure. *Saxler*, [0064]-[0066]. *Suh* likewise etches "to define a gate region where the p-type Al<sub>z</sub>GaN cap 11 is located," and depositing the gate on top. *Suh*, [0056].

*Beach* makes a self-aligned two-layer gate structure using a single photomask. *Beach*, [0040], [0045], [0054]; Shealy, [061]. *Ahn*, published in 1999, likewise uses a single mask and further discloses isotropic and anisotropic etching techniques to create stacked gate structures having stepped features and sloped sidewalls, as shown below. *Ahn*, Abstract, 3:41-58, 6:15-26, 7:7-14, Fig. 4C; Shealy, [061].

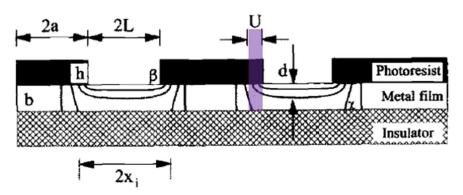

Ahn, Fig. 4C.

In addition, long before the '335 patent, *Shenoy* discloses techniques to isotropically etch and undercut metal layers below masks, which a POSITA would understand would be one method of forming stepped gate structures. *Shenoy*, 2-3; Shealy, [062].

Lift-off had similarly been known for decades for creating stepped structures. Ex. 1023; Shealy, [062].

Typical GaN HEMT devices thus included every feature of the claimed enhancement-mode transistor and they disclosed methods of making such a transistor. Shealy, [0055]-[063].

#### III. The '335 Patent

#### A. Overview

#### 1. The alleged invention

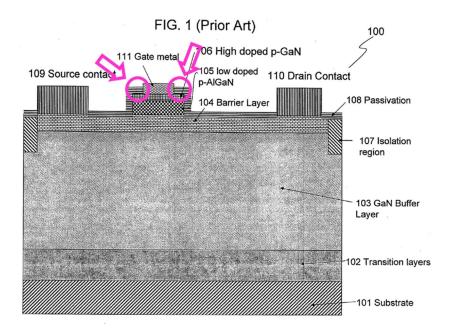

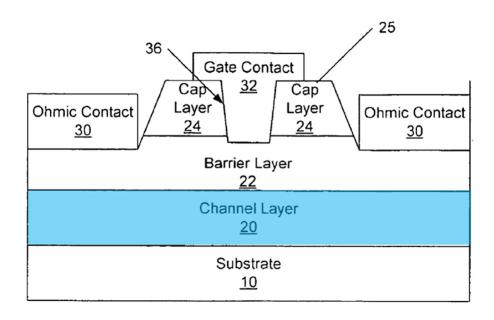

The '335 patent describes and claims an enhancement-mode GaN power transistor. Ex. 1001, 1:21-26, 2:34-57, Fig. 5, claims 1-7; Shealy, [044]. It asserts that conventional prior art GaN HEMT devices suffered from high gate leakage current between the gate and 2DEG region. Ex. 1001, 1:21-2:30; Shealy, [044]. The '335 patent admits that conventional GaN enhancement-mode devices included a GaN channel layer, an AlGaN barrier layer, source and drain electrodes, and a gate structure consisting of a p-type GaN layer with sloped sidewalls and an overlying gate metal—all features that are in the claims of the '335 patent. Ex. 1001, 1:21-2:30, Figs. 1-2, 3A-3B, claims 1-7; Shealy, [044]. The '335 patent even depicts numerous prior art systems with these features and identifies the known leakage paths in Figure 2 (path 201 along the sloped sidewalls, 202 through the p-type GaN layer). Ex. 1001, 1:21-2:30, Figs. 1-2, 3A-3B; Shealy, [044].

Ex. 1001, Figs. 1-2, 3A-3B.

As a purported solution to the problem of gate leakage, the '335 patent declares it adds *just one purportedly novel feature*: a pair of ledges on the p-type gate material, on either side of the gate metal. Ex. 1001, 2:34-57, 3:65-4:12, 4:40-51, Figs. 1-2, 3A-3B, 4-5, 7A-7B, 8, claims 1-7; Shealy, [045].

Ex. 1001, Fig. 5.

But, such ledges were known in the field many years before the '335 patent, and the claims were obvious over the prior art. Shealy, [046], [057]-[058] (citing *Yoshida, Hu, Smith, Saxler, Suh*); *infra* §§VIII-XI (Grounds 1-6). Indeed, the '335 patent's priority application *Lidow* notes this limitation was conventional. *Lidow*, [0006], Fig. 1; Shealy, [046].

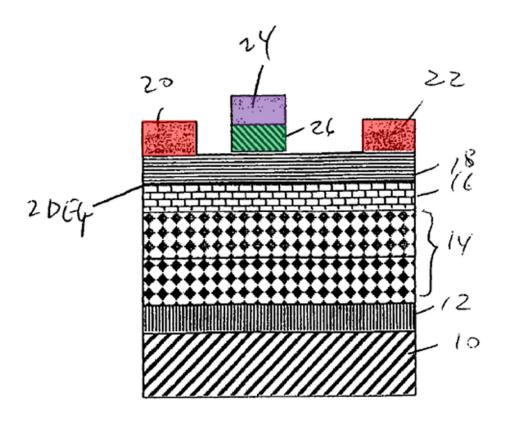

Lidow, Fig. 1.

#### 2. Self-aligned ledges

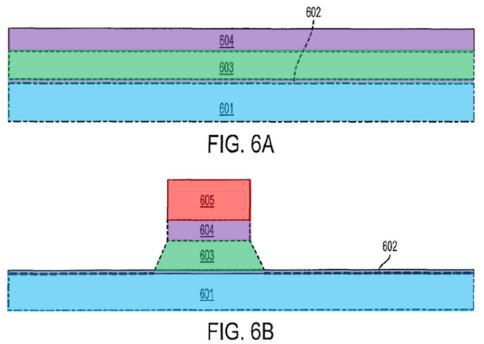

In some claimed embodiments, the '335 patent makes its **ledges** using a self-alignment process. Ex. 1001, 4:14-39, claims 2, 5; Shealy, [047]. Figures 6A-6C disclose a method of making these "self-aligned ledges." Ex. 1001, 4:14-39; Shealy, [047]. Priority applications also disclose "self-aligned gate" structures having symmetric ledges but do not describe the details of Figures 6A-6C. *E.g.*, *Lidow*, Abstract, [0008], [0022]-[0023], [0029]-[0030], [0036], [0038], [0040], [0044], [0046], claims 1, 6, 9, 10, 23; Shealy, [047].

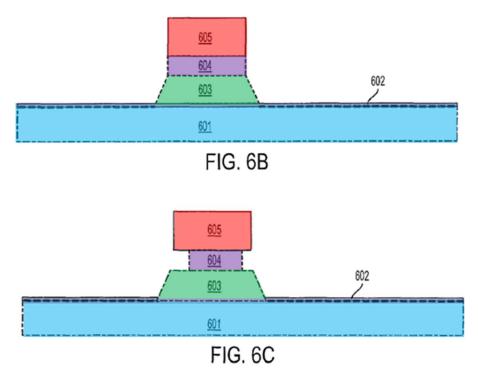

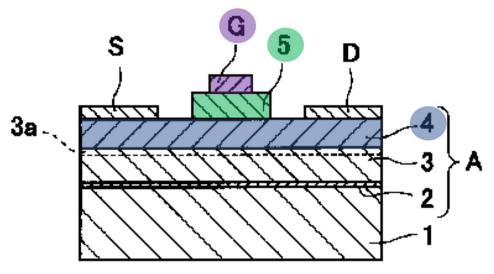

In the '335 patent, the self-aligned method includes forming **GaN layer 601**, **AlGaN layer 602**, and **p-type gate material 603**, then depositing the **gate metal 604** as Figure 6A depicts. Ex. 1001, 4:14-39; Shealy, [048]. The self-aligned method then applies **photoresist 605**, etches the gate metal, and etches the p-type gate material so that the outer walls **p-type gate material 603** and **gate metal** align as shown in Figure 6B. Ex. 1001, 4:14-26; Shealy, [048].

Ex. 1001, Figs. 6A-6B.

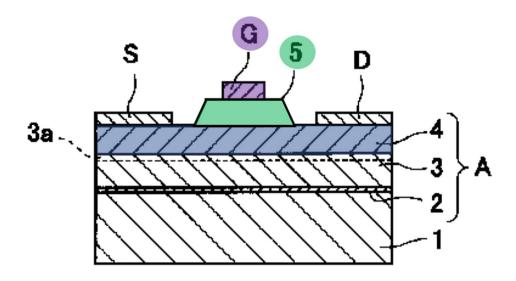

The '335 patent discloses that one way to complete the "self-aligned" ledges is to next "isotropically" etch the **gate metal** and undercut the same **photomask**, as shown in Figures 6B-6C. Ex. 1001, 4:23-39; Shealy, [049].

Ex. 1001, Figs. 6B-6C.

#### **B.** Prosecution History

#### 1. Allowance of the '335 Patent

The '335 patent was filed on July 20, 2017, as U.S. Application 15/655,438. Ex. 1001, cover. The independent claims included the p-type gate metal material, overlying gate metal, and a pair of horizontal ledges, but did not include the sloped sidewall features. Ex. 1002, 77-79. The application received one non-final Office Action rejecting claims 1-3, 5-8, and 10-11 under 35 U.S.C. § 102 as anticipated by *Hikita* (Ex. 1016). Ex. 1002, 36-43. To overcome the rejection, the applicant amended the independent claims to include sloped sidewalls. Ex. 1002, 34-35, 7-15.

The Examiner then allowed the claims, stating that the combination of the sloped sidewalls and horizontal ledges were allowable. Ex. 1002, 12.

#### 2. Priority claim

The '335 patent claimed priority as a division of prior Application No. 14/447,069 (U.S. Patent No. 9,748,347 ("the '347 patent")), which claimed priority to U.S. Provisional Patent Application No. 61/860,976, filed August 1, 2013. Ex. 1001, cover & p. 2. The '347 patent in turn claimed priority as a continuation-in-part to U.S. Application No. 13/838,792, which was a division of U.S. Application No. 12/756,960, filed April 8, 2010, and claimed priority to U.S. Provisional Patent Application No. 61,167,777, filed April 8, 2009. *Id.*; '347 patent, cover & p. 2. However, this second priority claim was only raised after the Examiner rejected the claims over the alleged priority application, *Lidow*, which was, in fact, disclosed as admitted prior art *by the Applicant* before making the belated priority claim.

During prosecution of the parent application that became the '347 patent, the applicant filed a Petition for Unintentional Delayed Priority to obviate a rejection over *Lidow* (U.S. 2010/0258843A1, Ex. 1011), a prior art reference the applicant had previously disclosed to the Patent Office. Ex. 1013, 95-128, 250. Incredibly, despite already admitting the reference was prior art through an IDS, the applicants reversed their previous representation and instead *claimed priority as a*

continuation-in-part to Lidow itself, utilizing a "Petition for Unintentionally Delayed Domestic Benefit Claim," including the required sworn statement by the prosecuting attorney that the "entire delay" was "unintentional," and that the petition was filed "immediately upon discovery." Ex. 1013, 104-05, 118-19. This petition was filed over a year after the applicant corrected domestic priority for errors in the filing receipt on the same day it submitted Lidow as prior art (Ex. 1013, 250, 282-90), and months after the Office cited Lidow as invalidating prior art (Ex. 1013, 227-34). The Office nonetheless granted the Petition without investigating the basis for the attestation of unintentional delay, Ex. 1013, 95-103, and the parent eventually issued as the '347 patent, id., 1.

Because of this history, Petitioner disagree that the present application properly claims priority to U.S. Application Nos. 12/756,960, 13/838,792, and 61/860,976, and contend that this patent is unenforceable for inequitable conduct on the part of the prosecuting attorney for submitting a false petition. But for the acceptance of this false petition, *Lidow* is invalidating prior art. Petitioner intend to challenge this priority claim in a separate *Ex Parte* Reexamination (EPR) proceeding.

For purposes of this petition, however, Petitioner nevertheless assume priority to the filing of the earliest application in the priority claim, which is April 8, 2009.

Also, for purposes of this petition alone, Petitioner assume that the claims find support in that provisional application just as the Examiner found support for the claims of the '347 patent in *Lidow*. Ex. 1013, 52, 75-76, 84-86. The apparatus claims of the '335 patent covers substantially the same subject matter as the resultant structure of the method claims of the '347 patent. Ex. 1001; Ex. 1012; Shealy, [051].

#### IV. Statement of Precise Relief Requested

#### A. Claims

Petitioner request review and cancellation of claims 1-7 under 35 U.S.C. § 311.

#### **Prior Art**

Yoshida (Ex. 1005, Ex. 1006), which published September 24, 1999, is prior art to the '335 patent under pre-AIA 35 U.S.C. § 102(b).

Saxler (Ex. 1007), which published May 25, 2006, is prior art to the '335 patent under pre-AIA 35 U.S.C. § 102(b).

Beach (Ex. 1008), which published January 11, 2007, is prior art to the '335 patent under pre-AIA 35 U.S.C. § 102(b).

Shenoy (Ex. 1009), which published February 22, 1996, is prior art to the '335 patent under pre-AIA 35 U.S.C. § 102(b).

The examiner did not have the benefit of any of these references.

#### B. Grounds

| Ground | Challenged<br>Claims | Basis | Prior Art                                    |

|--------|----------------------|-------|----------------------------------------------|

| 1      | 1-7                  | § 103 | Saxler in view of the knowledge of a POSITA  |

| 2      | 1-7                  | § 103 | Saxler in view of Yoshida                    |

| 3      | 2, 5-7               | § 103 | Saxler in view of Yoshida, Beach, and Shenoy |

| 4      | 1-7                  | § 103 | Yoshida in view of the knowledge of a POSITA |

| 5      | 1-7                  | § 103 | Yoshida in view of Saxler                    |

| 6      | 2, 5-7               | § 103 | Yoshida in view of Saxler, Beach, and Shenoy |

#### V. Statement of Facts

Pursuant to 37 C.F.R. § 42.22(c), the following statement of facts set forth the state of enhancement-mode GaN transistors at the time of the '335 patent's earliest claimed priority date of April 8, 2009.

- 1. Before April 8, 2009, the following were known:

- a. a GaN layer;

- b. an AlGaN barrier layer disposed on the GaN layer;

- c. source and drain electrodes disposed on the AlGaN barrier layer;

- d. a gate structure disposed on the barrier layer between source and drain electrodes;

- e. a gate structure with a p-type GaN layer with sloped sidewalls that extended horizontally towards the source and drain electrodes; and

- f. a gate structure with an overlying gate metal.

- 2. Before April 8, 2009, self-aligned gate structures were known.

#### VI. Level of Ordinary Skill

A person of ordinary skill in the art ("POSITA") with respect to the '335 patent would have possessed at least a four-year degree in electrical engineering, chemical engineering, physics, or material science or a closely related field, and at least two years of experience in semiconductor device design and/or fabrication, including the processing of semiconductor materials, analysis of device operation, or the development of new device topologies. Shealy, [052]-[053]. Additional education could substitute for professional experience and vice versa. *Id.*

#### VII. Claim Construction

The Board construes claims using the standard of *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005) (en banc); 37 C.F.R. § 42.100(b); *CUPP Comput. AS v. Trend Micro Inc.*, 53 F.4th 1376, 1380 (Fed. Cir. 2022). Under this standard, claim terms receive their ordinary and customary meaning as would be understood by one of ordinary skill in the art in the context of the specification, prosecution history, and extrinsic evidence. *Phillips*, 415 F.3d at 1314-19.

# A. "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

Independent claim 1 recites that the p-type gate material has "side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer." Claim 5 includes the same limitation but with "that extend" instead of "extending" and "contact" instead of "contacting." In a related matter, Patent Owner and Petitioner have agreed that these terms should be construed. *See* Ex. 1028. The parties have proposed the following constructions:

| Petitioner's                      | Patent Owner's                    |

|-----------------------------------|-----------------------------------|

| "side surfaces of the p-type gate | "p-type gate material having side |

| material such that the bottom of  | surfaces extending horizontally   |

| the p-type gate material is more  | such that the bottom of the       |

| than 10% wider than the top of    | material is wider than the top of |

| the material, leading to sloped   | the material"                     |

| side surfaces that contact the    |                                   |

| barrier layer"                    |                                   |

The challenged claims are unpatentable under both constructions. But to the extent the Board construes the term, Petitioner's proposed construction should apply. Shealy, [070]-[076].

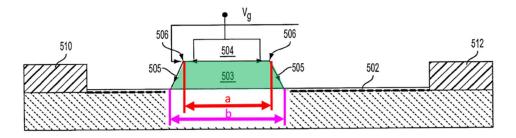

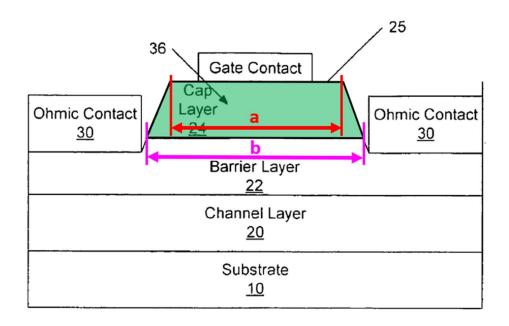

The construction agrees with the disclosure of the prior application, *Lidow*, which provides support for the present claims (§III.B (Prosecution History)). *Lidow* asserts the advantage of using sloped sidewalls in a p-type GaN gate layer to reduce gate leakage. *Lidow*, [0041]-[0042], Fig. 8. *Lidow* specifically teaches that a "base that is more than 10% wider than the top" advantageously "causes a longer path for electrons to travel between the gate metal 17 and the 2DEG along the pGaN side wall," thereby "result[ing] in lower gate leakage." *Id.*, [0042]. *Lidow* depicts the same p-type layer and gate structure as the '335 patent. *Id.*, Fig. 8; Ex. 1001, 3:49-64, Fig. 5; Shealy, [072].

The construction also adheres to the purpose of the '335 patent—reducing gate leakage, including through the conventional method of sloping the sidewalls to increase the length of sidewall leakage path 201. Ex. 1001, Abstract, 1:21-26, 2:20-48, 3:65-4:12, 4:40-51, Figs. 2, 4, 7A-7B, 8; Shealy, [073]. *See Honeywell Int'l Inc. v. Universal Avionics Sys. Corp.* 488 F.3d 982 (Fed. Cir. 2007) (construing claim to be consistent with the "purpose of" the limitation); *see also KEYnetik, Inc. v. Samsung Elecs. Co.*, 837 F. App'x 786, 793 (Fed. Cir. 2020) (reversing Board construction that would "eviscerate[] the purpose of the invention").

Lidow provides no other guidance on how much slope is sufficient to achieve reduced gate leakage. Within the field, at least slightly sloped sidewalls are common—few structures, if any, have perfectly vertical sidewalls in practice, even if depicted as vertical in functional diagrams. Shealy, [074], [203]-[205] (citing Saxler, [0042]; Uemoto, Figs. 1-2, 5); infra §X.C.5 (Ground 4, [1d]). To distinguish its purported invention from the prior art and gain the alleged benefits of lower gate leakage due to a longer leakage path, Lidow unequivocally describes controlling the shape of the p-type GaN material during etching to achieve a base 10% wider than the top. Lidow, [0041]-[0042]. Petitioner's construction makes this distinction clear.

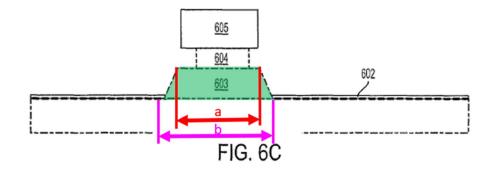

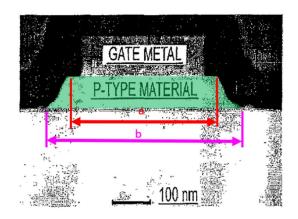

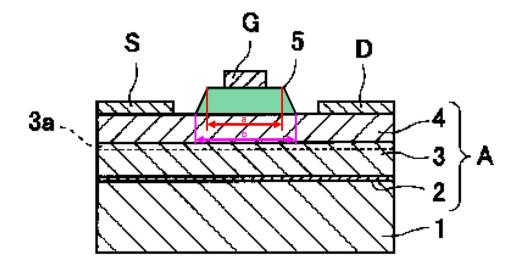

The construction likewise accords with the '335 patent's disclosure. For example, the '335 patent depicts a p-type gate material with sloped side surfaces whose bottom surface is more than 10% wider than the top. Ex. 1001, Figs. 5, 6C, 7B; Shealy, [075].

Ex. 1001, Fig. 5.

Width "b" above is approximately 30% wider than width "a," and the same holds true for Figures 6C and 7B. *Id*.

Ex. 1001, Fig. 6C.

FIG. 7B

Ex. 1001, Fig. 7B.

Examining Patent Owner's construction, any reference that discloses this term under Petitioner's construction will also disclose this term under Patent Owner's. because Petitioner'ss construction also requires that the bottom of the p-type gate material is wider than the top. Shealy, [076]. Therefore, all Petitioner's arguments below will apply under either construction. However, if Patent Owner's broader

construction is accepted, the patent is unpatentable under an additional ground, Ground 4.

#### B. "self-aligned" ledges

Claims 2 and 5 recite a transistor that requires "self-aligned" ledges. These are "product-by-process" limitations. In the '335 patent, a "self-aligned" ledge refers to a process for making the claimed gate structure and does not describe the structure itself. Ex. 1001, 4:14-39; *Lidow*, Abstract, [0008], [0022]-[0023], [0029]-[0030], [0036], [0038], [0040], [0044], [0046], Figs. 6A-6C, claims 1, 6, 9, 10, 23; Shealy, [077]-[085]. The '335 patent unambiguously describes that "the gate contact includes a p-type gate material 503 formed on the barrier layer 502 and includes ledges 506 *that are created by a self-aligned process* at the top corners of the p-type gate material 503." Ex. 1001, 3:49-53; Shealy, [078]. The patent repeatedly refers to this "self-aligned manufacturing *process*." Ex. 1001, 3:13-15, 3:49-53, 3:65-4:39, 4:52-63, Figs. 6A-6B.

Claim 3 of the '347 patent illustrates that "self-aligned" ledges refers to how the ledges are made, not what they are. Shealy, [079]. It recites "[t]he *method* according to claim 1, wherein the pair of ledges of the p-type gate material *are self-aligned*." This is consistent with how a POSITA would have understood the term. Shealy, [080]-[085] (citing *Smith*, [0041]-[0044], Fig. 4C; *Beach*, [0040]; *Suh 2006*, 1, Fig. 1).

Claims 2 and 5 of the '335 patent thus plainly recite product-by-process steps in a device claim, which lend no patentable weight. Ex. 1001, claims 2, 5. "The patentability of a product does not depend on its method of production. If the product in the product-by-process claim is the same as or obvious from a product of the prior art, the claim is unpatentable even though the prior product was made by a different process." *In re Thorpe*, 777 F.2d 695, 697 (Fed. Cir. 1985) (citations omitted); *Kamstrup A/S v. Axioma Metering UAB*, 43 F.4th 1374, 1381-83 (Fed. Cir. 2022) (finding "cast in one piece" in claim to flow meter a product-by-process element that gives no patentable weight); *United Therapeutics Corp. v. Liquidia Techs., Inc.*, 74 F.4th 1360, 1373 (Fed. Cir. 2023) ("As these claims are product claims, they are anticipated by a disclosure of the same product irrespective of the processes by which they are made.").

### VIII. Grounds 1 and 2: Saxler, Alone (Ground 1) or in View of Yoshida (Ground 2) Renders Obvious Claims 1-7

#### A. Overview of Grounds 1 and 2

Saxler discloses the arrangement of semiconductor layers and structures of claims 1-7. In some embodiments its gate metal is not recessed. Saxler, [0052]. These embodiments render obvious claims 1-7 (Ground 1). Shealy, [086]-[0150].

To the extent Patent Owner argues that *Saxler*'s cap layer does not render the claims obvious because its figures depict the recessed gate rather than the non-recessed embodiments, despite the explicit disclosure the recess is optional, *Yoshida*

also discloses and depicts a very similar device with a p-type gate material without a gate recess. The combination of *Saxler* and *Yoshida* renders obvious claims 1-7 (Ground 2). Shealy, [086]-[150].

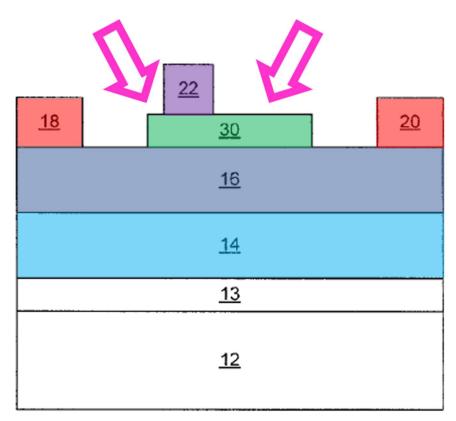

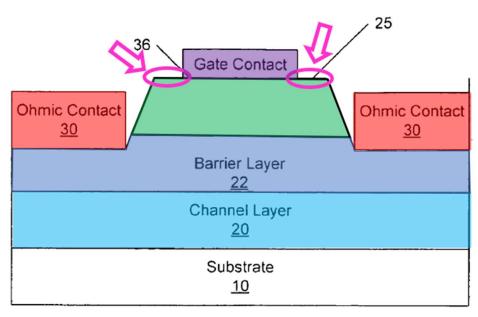

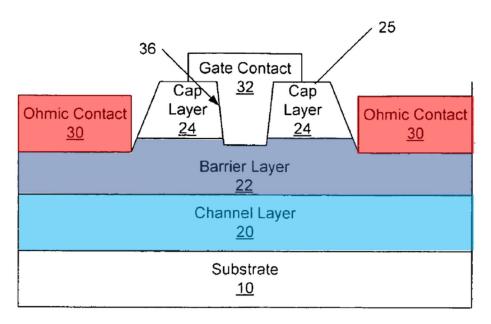

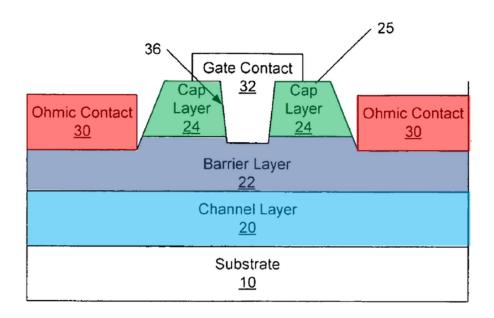

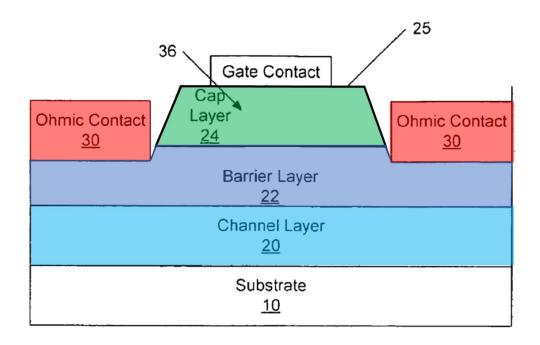

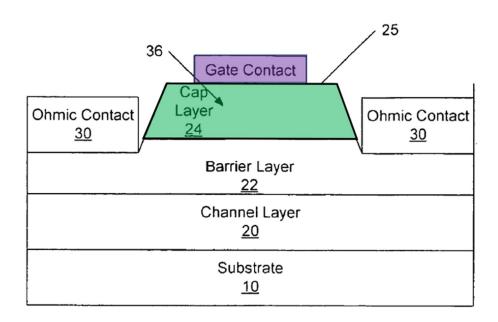

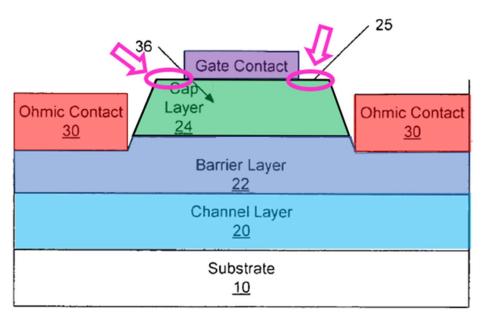

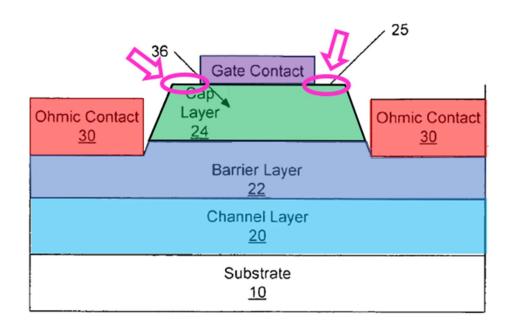

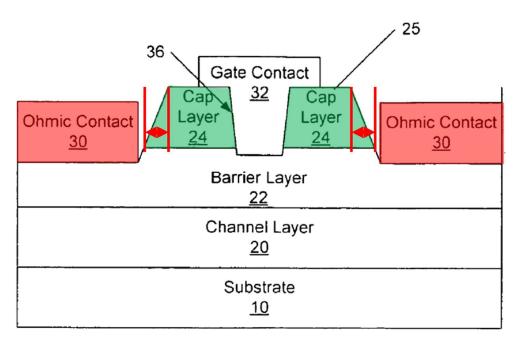

### 1. Ground 1: Saxler

Saxler discloses a GaN transistor with high breakdown voltage. Saxler, [0006], [0007]-[0030], Figs. 1A, 2B; Shealy, [089]. As shown below, Saxler's channel layer 20 is a GaN over silicon, and Saxler's barrier layer 22 is a Group III-nitride that may be AlGaN. Saxler, [0057]-[0060], Figs. 1A, 2B; Shealy, [089]. Saxler discloses "induc[ing] a two-dimensional electron gas" at the interface of these layers. Saxler, [0004], [0059] Shealy, [089]. Saxler discloses source and drain contacts. Saxler, [0065]; Shealy, [089].

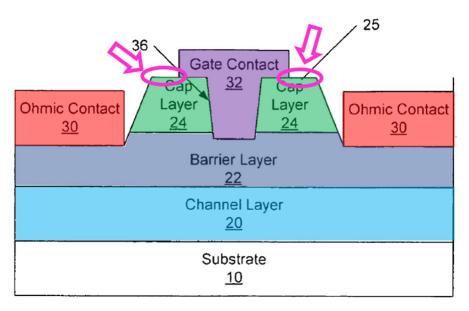

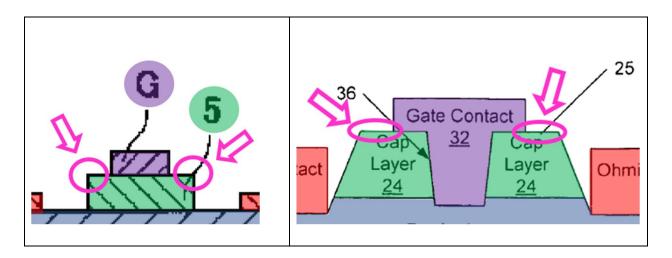

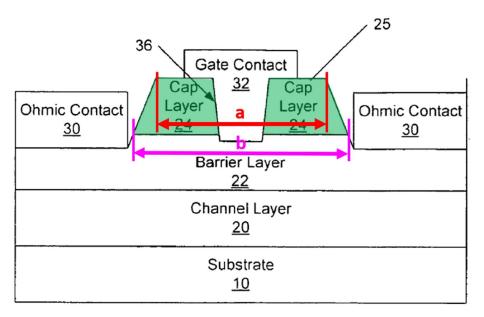

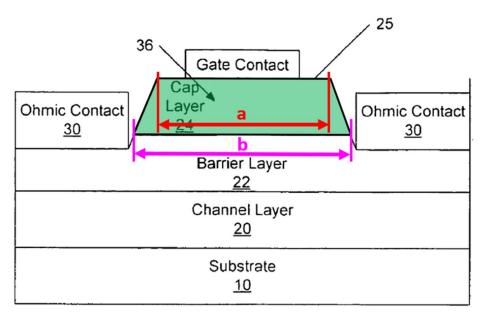

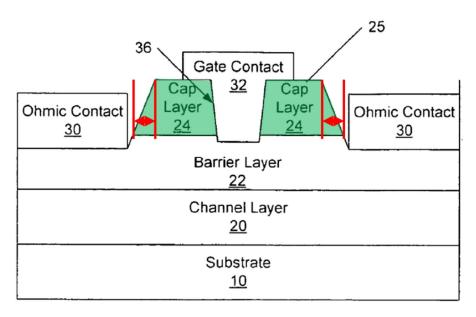

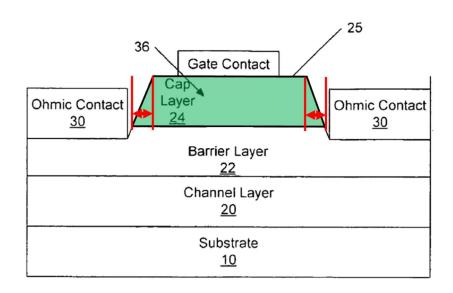

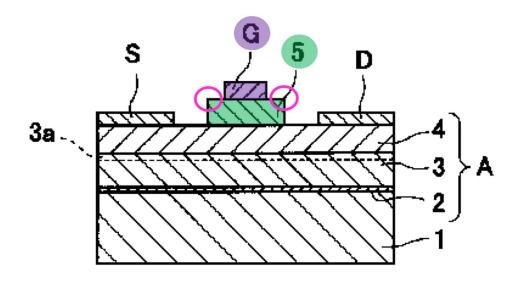

Saxler further discloses a stacked gate structure above the **barrier layer 22** consisting of a **cap layer** and **gate contact** that is metal. Saxler, [0061]-[0063], [0066], [0071]-[0073], [0076], [0087], Figs. 1A, 2B; Shealy, [090]. The **cap** layer may be p-typed doped GaN and doped in a subregion or throughout. Saxler, [0013], [0069], [0071], [0073]; Shealy, [090]. Saxler's gate contact may be recessed or non-recessed (i.e., flat). Saxler, [0052], [0066]. Where utilized, Saxler's recessed contact may be a T-shaped into the cap layer, and in some embodiments, it extends through the cap layer into the barrier layer, while in other embodiments it does not contact the barrier layer. Saxler, [0065]; Shealy, [090].

Saxler, Fig. 1A.

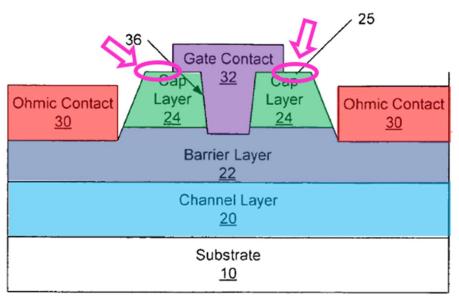

Where the gate recess is not utilized, *Saxler* has the following structure. Shealy, [091].

Saxler, Fig. 1A (modified).

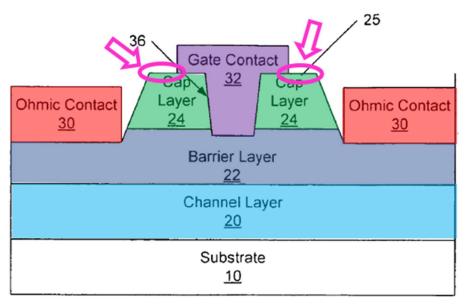

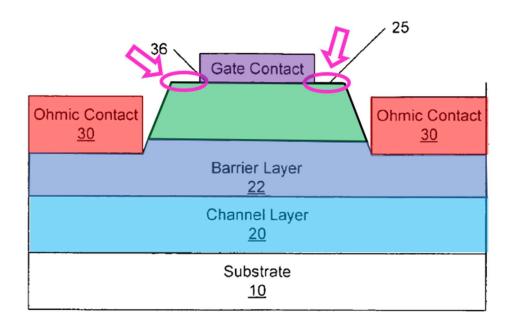

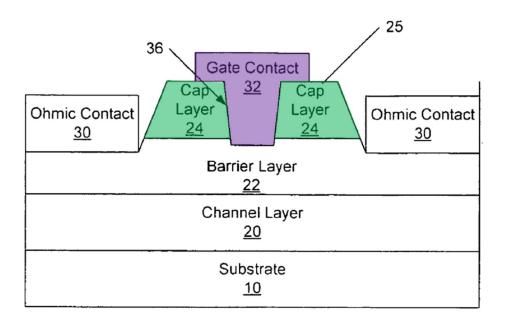

### 2. Yoshida

Yoshida, which published ten years before the earliest possible priority of the '335 patent, also discloses a normally-off enhancement-mode GaN transistor having a p-type GaN layer below the gate that "enables voltage control with a small amount of carrier injection," an arrangement that was conventional by the time of the '335 patent. Yoshida, [0017], [0015], Fig. 1; Shealy, [092]. Yoshida improves breakdown voltages over prior art GaN transistors. Yoshida, [0008]-[0009]; Shealy, [092].

Yoshida's layer 3 is a GaN grown over silicon nitrate like Saxler's, and layer 4 is an n-type semiconductor, with 2DEG 3a forming at their interface. Yoshida, Abstract, [0010], [0013], [0019]; Shealy, [093]. It includes a source and drain contact. Yoshida, Abstract, [0009].

Yoshida also discloses a stacked gate structure consisting of a **doped GaN** layer above the **semiconductor layer 4** and an overlying **gate metal**. Yoshida, Abstract, [0015]; Shealy, [094]. Its gate structure includes a pair of **horizontal** ledges on either side of the gate metal. Yoshida, Fig. 1; Shealy, [094].

Yoshida, Fig. 1.

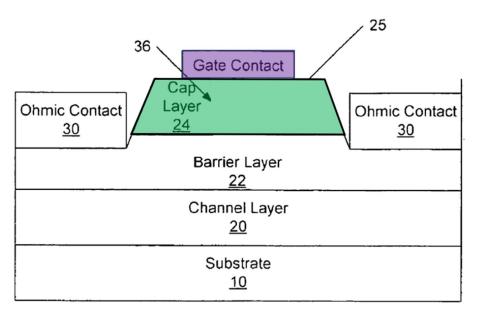

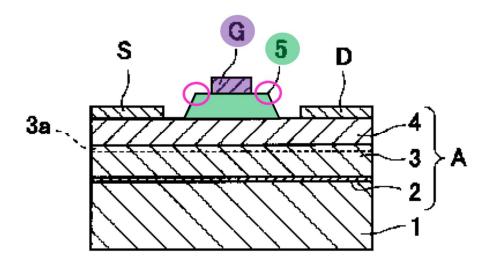

## 3. Ground 2: The combination of *Saxler* in view of *Yoshida*

Implementing *Yoshida*'s non-recessed gate in *Saxler*'s stacked gate structure results in the following combined structure. Shealy, [095]. Note that this results in the same arrangement as *Saxler*'s non-recessed embodiment:

Saxler, Fig. 1A (modified).

### 4. Ground 2: Motivation to Combine

It would have been obvious to implement *Yoshida*'s non-recessed gate in *Saxler*'s stacked gate structure. Shealy, [096]-[106].

Saxler and Yoshida disclose compatible enhancement-mode GaN HEMT devices comprising the same layers performing the same functions, including stacked gate structures having a cap layer and gate metal. Shealy, [097]. Both describe gallium nitride HEMTs with improved breakdown voltages over the prior art. Yoshida, [0008]-[0009]; Saxler, [0006], [0007]-[0030]; Shealy, [097]. Unsurprisingly, these transistors share numerous overlapping features—they use the same arrangement of layers, as the below comparison illustrates. Shealy, [097].

Petition for *Inter Partes* Review U.S. Patent 10,312,335

Yoshida, Fig. 1, Saxler, Fig. 1A (2DEG region present, but not shown).

Yoshida's layer 3 is GaN over a silicon substrate, as is Saxler's channel layer 20. Yoshida, [0012], [0019]; Saxler, [0057]-[0058]; Shealy, [098]. Yoshida's layer 4 is an n-type semiconductor, just like embodiments of Saxler's barrier layer 22. Yoshida, Abstract, [0010], [0013]; Saxler, [0059]-[0060]; Shealy, [098]. Both have 2DEG regions formed at the junction of these two layers. Yoshida, [0016]; Saxler, [0004], [0006], [0008]. Both references have source, drain, and gate metal contacts. Yoshida, Abstract, [0009]; Saxler, [0065]-[0066]. And both disclose a doped layer above the barrier and in contact with the gate metal. Yoshida, Abstract, [0015]; Saxler, [0069], Figs. 1A, 2B; Shealy, [098].

The specific form of their stacked gate differs between references but performs the same function—to control voltage "with a small amount of carrier injection" and "enable[] control of current flowing between channels" at high voltage. *Yoshida*, [0017]; *Saxler*, [0065]; Shealy, [099].

In *Saxler*'s pictured embodiments, the metal occupies a recess in the cap layer extending into the barrier layer, touching the barrier layer, or not touching the barrier layer. *Saxler*, Abstract, [0007]-[0008], Figs. 1A, 2B, Shealy, [100]. *Yoshida*'s gate metal, in contrast, sits flush on top of layer 5. *Yoshida*, Fig. 1; Shealy, [100]. Those structures are shown below.

Yoshida, Fig. 1, Saxler, Fig. 1A.

However, *Saxler* repeatedly discloses that its gate recess is optional. *Saxler*, Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88. While its figures do not explicitly depict a *stacked* gate structure having a gate contact and cap layer isolated from the source and drain contacts and without a gate recess, this disclosure would at a minimum render the claimed structure obvious. Shealy, [101]. To the extent Patent Owner disagrees with *Saxler*'s optional disclosure of the recess renders this structure obvious (Ground 1), *Yoshida* further renders the claimed structure obvious (Ground 2).

A POSITA would have been motivated and found it obvious to combine Saxler's gate structures with Yoshida's gate structure and accompanying fabrication techniques. Shealy, [102]-[106] (citing Saxler, Sheppard, Yoshida, Smith). A POSITA would have been familiar with many methods of making such stacked, stepped structures (§II, Technological Background) and combined Saxler and Yoshida to simplify manufacturing and decrease costs. Shealy, [060]-[062] (citing Beach, Saxler, Ahn, Xu, Sheppard, Smith, Hu, Shenoy), [102]. Saxler references and incorporates Sheppard (Ex. 1021) as disclosing "[s]uitable structures and techniques for fabricating GaN-based HEMTs" according to Saxler's purported invention. Saxler, [0046] (referencing Ser. No. 10/897,726), [0068] (same). Sheppard discloses complicated and exacting manufacturing processes to create a gate recess and deposit the gate metal. *Id.*, [0043], [0046]-[0051], [0053]-[0056], Figs. 1C-1F, 2A-2B, Fig. 3. Its GaN cap layer may be "about 2 nm to 500 nm thick," and the thin AlGaN underlying barrier layer is between "0.1 nm and about 40 nm." GaN. Id., [0040], [0042]; Shealy, [103]. Accordingly, tolerances when manufacturing the gate recess are extremely small. Shealy, [103]. This raises complexity and costs of manufacturing to avoid costly out-of-tolerance defects. Shealy, [103].

To avoid these problems, a POSITA would have been motivated to use Saxler's non-recessed gate contact in its stacked gate structure in combination with Yoshida's gate structure and accompanying fabrication techniques. A POSITA would have recognized this as a suitable option for solving such problems. *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 417 (2007); *Intel Corp. v. PACT XXP Schweiz AG*, 61 F.4th 1373, 1379-81 (Fed. Cir. 2023). A POSITA would have been familiar with a wide variety of stacked gate structures in GAN HEMT devices, including many without recessed gates. Shealy, [104].

A POSITA would have further been motivated to remove the gate recess to turn *Saxler*'s device into an enhancement mode device, thus realizing the benefits of reduced power consumption and suitability for high power applications. *Suh*, 1; Shealy, [057]-[063] (citing *Beach*, *Saxler*, *Ahn*, *Xu*, *Sheppard*, *Smith*, *Hu*, *Shenoy*), [103].

Indeed, *Saxler* recognizes still other HEMT structures would be compatible with its disclosure, including *Smith*'s devices which it incorporates by reference. *Saxler*, [0087]; Shealy, [105]. *Smith* discloses non-recessed gate electrodes in stacked structures similar to *Saxler*'s recessed stacked gate structure. *Smith*, [0033], [0041], Figs. 3, 5B. *Smith* states that "there is no benefit to recessing the gate down to the barrier layer" in GaN HEMT devices "because the top surface of GaN is generally not conductive." *Id.*, [0010]; Shealy, [105]. And although it briefly discloses using T-shaped gate electrodes for "microwave and RF" applications (*Smith*, [0017], [0034], claim 20), *Smith* otherwise only describes and depicts stacked gate structures having a **GaN cap layer** with a non-recessed **gate electrode**

(*id.*, [0033]-[0037], [0039]-[0043], claim 1, Figs. 3, 4A-4C, 5A-5B); Shealy, [105]. Like *Saxler*, *Smith*'s GaN HEMT also includes a **GaN channel layer** and **AlGaN barrier layer** (inducing a **2DEG region**), and **source** and **drain electrodes**. *Smith*, [0030]-[0037], [0041]; Shealy, [105]. A POSITA would thus have understood non-recessed electrodes were a suitable option for *Saxler*'s GaN, which bears substantially the same layers and structure. Shealy, [105].

Smith, Fig. 5B.

In view of the many options for stacked gate structures in GaN HEMT, including *Saxler*'s non-recessed stacked gate structures, a POSITA would have found the combination of *Yoshida*'s non-recessed gate arrangement in *Saxler*'s gate arrangement nothing more than the simple substitution of known elements to predictably yield an enhancement mode GaN HEMT device. Shealy, [057]-[063], [096]-[106].

### B. Independent Claim 1

Saxler in view of the knowledge of a POSITA (Ground 1) and in view of Yoshida (Ground 2) renders obvious claim 1. Shealy, [107]-[134].

## 1. [1p] An enhancement-mode GaN transistor, comprising:

To the extent limiting, *Saxler* discloses or renders obvious the preamble. Shealy, [108]-[109]. *Saxler* discloses a GaN high-mobility transistor that includes a doped GaN cap layer below the gate and above an AlGaN barrier layer. *Saxler*, [0007]-[0010], [0046], [0059]-[0064], Figs. 1A, 1B; Shealy, [108]. This constitutes a normally-off enhancement-mode GaN transistor when the cap is doped p-type. Shealy, [108].

A POSITA would have understood *Saxler*'s transistors to be enhancement-mode GaN transistors at least because of their gate structure. Shealy, [109] (citing *Sheppard*, [0014], [0040], [0042], Fig. 1F). For example, *Sheppard*, which *Saxler* expressly incorporates (*Saxler*, [0046], [0068], (referencing Ser. No. 10/897,726)),

likewise discloses a GaN high-mobility transistor that includes a doped GaN cap layer below the gate and above an AlGaN barrier layer, where the cap layer "moves the top surface of the device physically away from the channel, which may reduce the effects of the surface," constituting a normally-off enhancement-mode GaN transistor when the cap is doped p-type. *Sheppard*, [0014], [0040], [0042], Fig. 1F; Shealy, [109].

### 2. [1a] a GaN layer;

The '335 patent admits [1a] was conventional. Ex. 1001, 1:42-2:26, Figs. 1-2, 3A-3B; Shealy, [110].

Saxler discloses a **GaN channel layer** (Grounds 1-2). Saxler, [0007], [0010], [0016], [0058], [0069], Figs. 1A-1F; Shealy, [110]-[111].

Saxler, Fig. 1A.

## 3. [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

The '335 patent admits [1b] was conventional. Ex. 1001, 1:42-2:26, Figs. 1-2, 3A-3B; Shealy, [112].

Saxler discloses [1b] (Grounds 1-2). Shealy, [112]-[115]. Saxler's barrier layer 22 is disposed on its GaN channel layer. Saxler, Abstract, [0007], [0010], [0016], [0058]-[0059], [0069], Figs. 1A, 2B.

Saxler, Fig. 1A.

Saxler's barrier layer may be an AlGaN layer. Saxler, [0007], [0010], [0016], [0058]-[0059], [0069], Figs. 1A, 2B; Shealy, [114]. The '335 patent likewise discloses that the claimed barrier layer may be an AlGaN layer, which is covered in

the dependent claims. Ex. 1001, 1:42-63, 3:37-48, 4:16-22, claims 3, 6; Shealy, [114].

Saxler further discloses "induc[ing] a two-dimensional electron gas" at the interface of the first GaN layer and second AlGaN layer. Saxler, [0004], [0059] ("induce a significant carrier concentration at the interface between the channel layer 20 and the barrier layer 22"); Shealy, [115].

## 4. [1c]: a source contact and a drain contact formed on the barrier layer;

The '335 patent admits [1c] was conventional. Ex. 1001, 1:64-2:19, Figs. 1-2, 3A-3B; Shealy, [116].

Saxler discloses "ohmic contacts 30" that may "provide source and drain contacts" formed on barrier layer 22 (Grounds 1-2). Saxler, [0065], Figs. 1A, 2B; Shealy, [116]-[117].

Saxler, Fig. 1A.

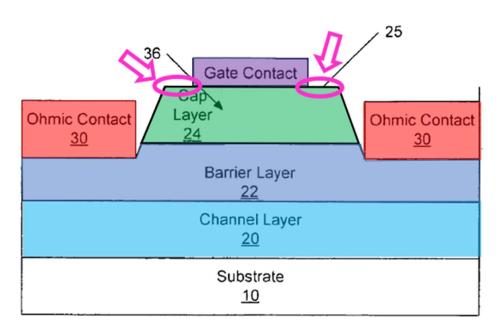

5. [1d]: a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and

The '335 patent admits [1d] was conventional. Ex. 1001, 1:42-2:26, Figs. 1-2, 3A-3B; Shealy, [118].

Saxler alone (Ground 1) and/or in view of Yoshida (Ground 2) renders obvious [1d] under either parties' construction of the side surfaces limitation. Shealy, [118]-[126].

Under Ground 1, Saxler's cap layer discloses a p-type gate material. Saxler, [0013], [0069], [0071], [0073]; Shealy, [120]. The cap layer resides above an

AlGaN barrier layer, as claim 1 of the '335 patent requires. *Saxler*, [0010], [0059]-[0063], Figs. 1A, 2B; Shealy, [120].

Saxler's cap layer has side surfaces extending horizontally towards the source and drain contact, and contacting the barrier layer. Saxler, [0064], Figs. 1A, 2B; Shealy, [121].

Saxler, Fig. 1A.

Saxler discloses "a p-type gate material ... having side surfaces" as recited in claim 1. Although it depicts its gate recess may separate its cap layer into two portions in some embodiments, the recess in Saxler's cap layer 24 need not be present and need not extend through the cap layer 24 and into the barrier layer. Saxler, Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88; Shealy, [122]. Saxler thus discloses or at least renders

obvious a single p-type gate material having two side surfaces that extend horizontally towards the source and drain. Shealy, [123].

Saxler, Fig. 1A (modified).

To the extent Patent Owner argues that *Saxler* does not disclose [1d] because its figures do not depict a single p-type gate material having side surfaces extending towards the source and drain, the *Saxler-Yoshida* combination of Ground 2 renders it obvious. Shealy, [123]. It would have been obvious to combine *Saxler* and *Yoshida*, resulting in the same figure as the *Saxler* non-recessed embodiment. Shealy, [123]; §VIII.A.4 (Ground 2, Motivation to Combine).

Saxler, Fig. 1A (modified).

### **Mapping Under Petitioner's Construction**

Both *Saxler* alone (Ground 1) or *Saxler-Yoshida* in combination (Ground 2) discloses and renders obvious side surfaces of the p-type gate material *such that the bottom of the p-type gate material is more than 10% wider than the top of the material, leading to sloped side surfaces that contact the barrier layer, which is the proper construction. Shealy, [124]; §VII.A (Claim Construction). In either the recess or non-recess <i>Saxler* embodiments, the bottom of the **cap layer** (length "b," below) is more than 10% wider than the top (length "a") (Ground 1). Shealy, [124].

Saxler, Fig. 1A.

Saxler, Fig. 1A (modified).

Likewise, in *Saxler-Yoshida*, the bottom of the **cap layer** (length "b," below) is more than 10% wider than the top (length "a") (Ground 2). Shealy, [125].

Saxler, Fig. 1A (modified).

### **Mapping Under Patent Owner's Construction**

Both *Saxler* alone (Ground 1) or the *Saxler-Yoshida* in combination (Ground 2) discloses and renders obvious side surfaces of the p-type gate material *such that* the bottom of the material is wider than the top of the material under Patent Owner's construction. Shealy, [126].

Saxler, Fig. 1A.

Saxler, Fig. 1A (modified).

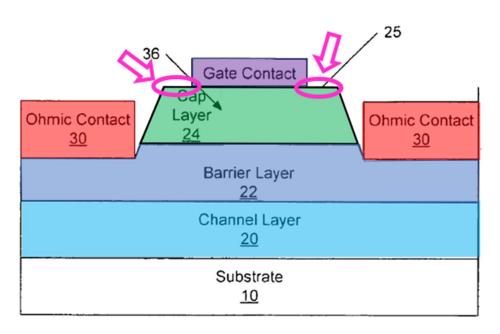

6. [1e]: a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,

The patent admits [1e] was conventional and depicts numerous prior art devices disclosing [1e]. Ex. 1001, 1:28-2:26, Figs. 1-4, 7A; Shealy, [127].

Saxler alone renders obvious [1e] (Ground 1). Shealy, [127]-[130]. Saxler's gate contact is a gate metal (e.g., "Ni, Pt, NiSi<sub>x</sub>, Cu, Pd, Cr, W and/or WsiN") formed on its cap layer. Saxler, [0066], Figs. 1A, 2B; Shealy, [128]. As explained, in some embodiments Saxler lacks a gate recess and does not separate the cap layer into distinct portions. Saxler, Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88; Shealy, [128]; §VIII.B.5 (Grounds 1-2, [1d]). In either embodiment, the sidewalls of its gate contact extend vertically towards the cap layer just as in the recessed embodiments depicted in Figures 1A and 2B. Shealy, [128].

Saxler, Fig. 1A.

Saxler, Fig. 1A (modified).

Saxler in view of Yoshida also renders obvious [1e] (Ground 2). Shealy, [129]-[130]. Like Saxler's gate contact, Yoshida's gate electrode is a metal formed on its p-type GaN layer 5. Yoshida, [0016]; Shealy, [129]; §X.C.6 (Grounds 1-2, [1e]). It would have been for a POSITA to select a suitable metal for the combined Saxler-Yoshida system. Shealy, [129]. Gates were conventional in GaN HEMTS and included in both references, and a POSITA would have selected a metal for the gate as a simple design choice, depending on the properties of the system. Shealy, [129] (citing Yoshida, [0002]-[0006], [0016] (disclosing "Au/Pt, Al, and the like" as examples of Yoshida's gate electrode)).

Further, the sidewalls of *Saxler-Yoshida*'s **gate contact** extend towards the **cap layer**, as required by [1e] and shown below. *Yoshida*, Fig. 1; *Saxler*, Fig. 1F; Shealy, [130].

Saxler, Fig. 1A (modified).

7. [1f]: wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively.

[1f] is the only limitation of independent claim 1 that the '335 patent does not admit is found in the prior art. Ex. 1001, 1:28-2:26, Figs. 1-4, 7A; Shealy, [131]. *Saxler* alone (Ground 1) and/or in view of *Yoshida* (Ground 2) renders it obvious. Shealy, [131]-[134]. Yet the priority application *Lidow* notes this limitation was conventional, stating that ledges in a "conventional enhancement mode transistor"

are made using separate masks for the p-type gate material and gate metal. *Lidow*, [0006], Fig. 1.

Under Ground 1, Saxler depicts its gate contact is narrower than its cap layer, thereby exposing horizontal ledges with substantially equal widths that extend past the respective sidewalls of the gate and toward the source and drain, as shown in Figure 1A below. Saxler, Fig. 1A; Shealy, [132]-[133]. In some embodiments, Saxler's gate recess is not present or does not separate the cap layer into distinct portions. Saxler, Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88; Shealy, [133]; §VIII.B.5 (Grounds 1-2, [1d]). A POSITA would have understood Saxler's gate contact in non-recessed embodiments (or embodiments where the recess did not extend through the cap layer) would similarly be narrower than the cap layer to expose the horizontal ledges. Shealy, [133]. Saxler thereby discloses or at least renders [1f] obvious (Ground 1).Id.

Saxler, Fig. 1A.

Saxler, Fig. 1A (modified).

Saxler in view of Yoshida also renders obvious [1f] (Ground 2). Shealy, [134]. Saxler-Yoshida's gate contact is narrower than its cap layer, thereby exposing horizontal ledges that extend past the respective sidewalls of the gate and toward

the **source** and **drain**. *Yoshida*, [0022]-[0023], Fig. 1; *Saxler*, [0046], Figs. 1A-1F; Shealy, [134]. These ledges are symmetric on either side of the gate (i.e., having substantially equal widths). Shealy, [134].

Saxler, Fig. 1A (modified).

## C. [Claim 2]: wherein the pair of horizontal ledges of the p-type gate material are self-aligned.

Claim 2 is drawn to a device but is a product-by-process claim for "self-aligned" ledges, which lends no patentable weight. §VII.B (Claim Construction); *Thorpe*, 777 F.2d at 697; *Kamstrup*, 43 F.4th at 1381-83; *United Therapeutics*, 74 F.4th at 1373.

For reasons explained for [1f], claim 2 is obvious over *Saxler* alone (Ground 1) and/or in view of *Yoshida* (Ground 2). Shealy, [135]; §VIII.B.7 (Grounds 1-2, [1f]).

### D. [Claim 3]: wherein the barrier layer comprises aluminum gallium nitride (AlGaN).

Saxler discloses claim 3 for the reasons explained for [1b] (Grounds 1-2). Saxler, [0007], [0010], [0016], [0058]-[0059], [0069], Figs. 1A, 2B]; Shealy, [136]; §VIII.B.3 (Grounds 1-2, [1b]).

# E. [Claim 4]: wherein the p-type gate material has a first width between the side surfaces of the p-type gate material and the gate metal has a second width between sidewalls of the gate metal, the second width being less than the first width

Claim 4 recites nothing more than that the gate metal is narrower than the p-type gate material, which is already required by [1f] under either Party's construction. As explained for [1f], *Saxler* alone (Ground 1) and/or in view of *Yoshida* (Ground 2) renders obvious this arrangement. *Yoshida*, [0022]-[0023], Fig. 1; *Saxler*, [0014], [0046], claims 1, 18, 20, 29, Fig. 1F; Shealy, [137]; §VIII.B.7 (Grounds 1-2, [1f]).

### F. Independent Claim 5

Saxler in view of the knowledge of a POSITA (Ground 1) and in view of Yoshida (Ground 2) renders obvious claim 5. Shealy, [138]-[147].

## 1. [5p] An enhancement-mode GaN transistor, comprising:

[5p] is identical to [1p]. *Saxler* discloses or at least renders it obvious for the reasons explained for [1p] (Grounds 1-2). Shealy, [139]; §VIII.B.1 (Grounds 1-2, [1p]).

### 2. [5a] a GaN layer;

[5a] is identical to [1a]. *Saxler* discloses it for the reasons explained for [1a] (Grounds 1-2). Shealy, [140]; §VIII.B.2 (Grounds 1-2, [1a]).

3. [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

[5b] is identical to [1b]. *Saxler* discloses it for the reasons explained for [1b] (Grounds 1-2). Shealy, [141]; §VIII.B.3 (Grounds 1-2, [1b]).

4. [5c]: a source contact and a drain contact formed on the barrier layer;

[5c] is identical to [1c]. *Saxler* discloses it for the reasons explained for [1c] (Grounds 1-2). Shealy, [142]; §VIII.B.4 (Grounds 1-2, [1c]).