## UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_

INNOSCIENCE (ZHUHAI) TECHNOLOGY COMPANY AND INNOSCIENCE AMERICA, INC.,

Petitioner

v.

EFFICIENT POWER

CONVERSION CORPORATION,

Patent Owner

Case No. IPR2023-01384

U.S. Patent No.10,312,335

DECLARATION OF JAMES RICHARD SHEALY, PH.D.

# TABLE OF CONTENTS

| I.    | INTRODUCTION   |                                                                                                                                                   |    |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| II.   | SUM            | MARY OF OPINIONS                                                                                                                                  | 2  |

| III.  | QUA            | LIFICATIONS AND BACKGROUND                                                                                                                        | 2  |

| IV.   | MAT            | ERIALS CONSIDERED                                                                                                                                 | 6  |

| V.    | LEGA           | AL STANDARDS                                                                                                                                      | 9  |

|       | A.             | Level of Ordinary Skill in the Art                                                                                                                | 10 |

|       | B.             | Anticipation                                                                                                                                      | 11 |

|       | C.             | Obviousness                                                                                                                                       | 11 |

| VI.   | OVE            | RVIEW OF THE '335 PATENT                                                                                                                          | 17 |

|       | A.             | The Claims and Specification                                                                                                                      | 17 |

|       | B.             | Prosecution History                                                                                                                               | 22 |

| VII.  | LEVI           | EL OF ORDINARY SKILL IN THE ART                                                                                                                   | 23 |

| VIII. |                | HNOLOGY BACKGROUND AND THE STATE OF THE OR ART                                                                                                    | 24 |

| IX.   | CLA            | IM CONSTRUCTION                                                                                                                                   | 31 |

|       | A.             | "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer" | 33 |

|       | B.             | "self-aligned" ledges                                                                                                                             | 38 |

| Χ.    | VIEV           | UNDS 1 AND 2: <i>SAXLER</i> , ALONE (GROUND 1) OR IN V OF <i>YOSHIDA</i> (GROUND 2) RENDERS OBVIOUS CLAIMS                                        | 43 |

|       | <b>1</b> / ••• |                                                                                                                                                   | 1  |

| A. | Over  | view of Grounds 1 and 2                                                                                                                                                                                                                                                                                                                                                          | 43 |

|----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 1.    | Ground 1: Saxler                                                                                                                                                                                                                                                                                                                                                                 | 44 |

|    | 2.    | Yoshida                                                                                                                                                                                                                                                                                                                                                                          | 46 |

|    | 3.    | Ground 2: The combination of Saxler in view of Yoshida                                                                                                                                                                                                                                                                                                                           | 48 |

|    | 4.    | Ground 2: Motivation to Combine                                                                                                                                                                                                                                                                                                                                                  | 48 |

| B. | Indep | pendent Claim 1                                                                                                                                                                                                                                                                                                                                                                  | 55 |

|    | 1.    | [1p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                                                                                                                                                                             | 55 |

|    | 2.    | [1a] a GaN layer;                                                                                                                                                                                                                                                                                                                                                                | 56 |

|    | 3.    | [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                                                                                                                                                                            | 57 |

|    | 4.    | [1c]: a source contact and a drain contact formed on the barrier layer;                                                                                                                                                                                                                                                                                                          | 58 |

|    | 5.    | [1d]: a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and                                                                                                                                              | 59 |

|    | 6.    | [1e]: a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,                                                                                                                                                                                                                                             | 66 |

|    | 7.    | [1f]: wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively. | 69 |

| C. | _            | material are self-aligned.                                                                                                                                                                                                       | 72 |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| D. |              | im 3]: wherein the barrier layer comprises aluminum um nitride (AlGaN).                                                                                                                                                          | 73 |

| Е. | betw<br>gate | im 4]: wherein the p-type gate material has a first width veen the side surfaces of the p-type gate material and the metal has a second width between sidewalls of the gate al, the second width being less than the first width | 73 |

| F. | Inde         | pendent Claim 5                                                                                                                                                                                                                  | 73 |

|    | 1.           | [5p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                             | 74 |

|    | 2.           | [5a] a GaN layer;                                                                                                                                                                                                                | 74 |

|    | 3.           | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                            | 74 |

|    | 4.           | [5c]: a source contact and a drain contact formed on the barrier layer;                                                                                                                                                          | 74 |

|    | 5.           | [5d]: a p-type gate material formed above the barrier layer and between the source and drain contacts;                                                                                                                           | 75 |

|    | 6.           | [5e]: a gate metal disposed on the p-type gate material,                                                                                                                                                                         | 75 |

|    | 7.           | [5f]: wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and                                 | 75 |

|    | 8.           | [5g]: (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                                                                                     | 76 |

| G. | _            | im 6]: wherein the barrier layer comprises aluminum um nitride (AlGaN)                                                                                                                                                           | 76 |

|     | Н. | _     | im 7]: wherein the pair of self-aligned ledges are symmetric respect to the gate metal                                                                                                          | 77 |

|-----|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| XI. |    |       | 3: <i>SAXLER</i> IN VIEW OF <i>YOSHIDA</i> , <i>BEACH</i> , AND RENDERS OBVIOUS CLAIMS 2 AND 5-7                                                                                                | 79 |

|     | A. | Ove   | rview of Ground 3                                                                                                                                                                               | 79 |

|     |    | 1.    | Beach                                                                                                                                                                                           | 79 |

|     |    | 2.    | Shenoy                                                                                                                                                                                          | 80 |

|     |    | 3.    | Motivation to Combine                                                                                                                                                                           | 81 |

|     | В. | clain | im 2] The enhancement-mode GaN transistor according to n 1, wherein the pair of horizontal ledges of the p-type gate erial are self-aligned.                                                    | 86 |

|     | C. | Inde  | pendent Claim 5                                                                                                                                                                                 | 87 |

|     |    | 1.    | [5p] An enhancement-mode GaN transistor, comprising:                                                                                                                                            | 88 |

|     |    | 2.    | [5a] a GaN layer;                                                                                                                                                                               | 88 |

|     |    | 3.    | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                           | 88 |

|     |    | 4.    | [5c] a source contact and a drain contact disposed on the barrier layer;                                                                                                                        | 88 |

|     |    | 5.    | [5d] a p-type gate material formed above the barrier layer and between the source and drain contacts;                                                                                           | 88 |

|     |    | 6.    | [5e] and a gate metal disposed on the p-type gate material,                                                                                                                                     | 88 |

|     |    | 7.    | [5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and | 89 |

|      |    | 8.    | [5g] side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                          | 89 |

|------|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | D. | claim | m 6] The enhancement-mode GaN transistor according to a 5, wherein the barrier layer comprises aluminum gallium le (AlGaN).                                     | 90 |

|      | E. | claim | m 7] The enhancement-mode GaN transistor according to a 5, wherein the pair of self-aligned ledges are symmetric respect to the gate metal.                     | 90 |

| XII. |    |       | S 4 AND 5: <i>YOSHIDA</i> , EITHER ALONE OR IN VIEW R RENDERS OBVIOUS CLAIMS 1-7                                                                                | 90 |

|      | A. | Grou  | nd 4: Yoshida Alone                                                                                                                                             | 90 |

|      | B. | Grou  | nd 5                                                                                                                                                            | 92 |

|      |    | 1.    | Ground 5: The Combination of <i>Yoshida</i> in View of <i>Saxler</i>                                                                                            | 92 |

|      |    | 2.    | Ground 5: Motivation to Combine                                                                                                                                 | 93 |

|      | C. | Indep | pendent Claim 1                                                                                                                                                 | 95 |

|      |    | 1.    | [1p] An enhancement-mode GaN transistor, comprising:                                                                                                            | 95 |

|      |    | 2.    | [1a] a GaN layer;                                                                                                                                               | 95 |

|      |    | 3.    | [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                           | 96 |

|      |    | 4.    | [1c] source contact and a drain contact formed on the barrier layer;                                                                                            | 97 |

|      |    | 5.    | [1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and |    |

|    |                                                                                                                                                                                                                                                                                                          | layer; and98                                                                                                                                                                                                                                                                                                                                                                    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 6.                                                                                                                                                                                                                                                                                                       | [1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,                                                                                                                                                                                                                                             |

|    | 7.                                                                                                                                                                                                                                                                                                       | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively. |

| D. | claim                                                                                                                                                                                                                                                                                                    | m 2] The enhancement-mode GaN transistor according to 1, wherein the pair of horizontal ledges of the p-type gate rial are self-aligned                                                                                                                                                                                                                                         |

| E. | claim                                                                                                                                                                                                                                                                                                    | m 3] The enhancement-mode GaN transistor according to 1, wherein the barrier layer comprises aluminum gallium e (AlGaN)                                                                                                                                                                                                                                                         |

| F. | [Claim 4] The enhancement-mode GaN transistor according to claim 1, wherein the p-type gate material has a first width between the side surfaces of the p-type gate material and the gate metal has a second width between sidewalls of the gate metal, the second width being less than the first width |                                                                                                                                                                                                                                                                                                                                                                                 |

| G. | Indep                                                                                                                                                                                                                                                                                                    | pendent Claim 5                                                                                                                                                                                                                                                                                                                                                                 |

|    | 1.                                                                                                                                                                                                                                                                                                       | [5p] An enhancement-mode GaN transistor, comprising:110                                                                                                                                                                                                                                                                                                                         |

|    | 2.                                                                                                                                                                                                                                                                                                       | [5a] a GaN layer;110                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.                                                                                                                                                                                                                                                                                                       | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer:                                                                                                                                                                                                                                           |

|       |    | 4.    | [5c] a source contact and a drain contact disposed on the barrier layer;                                                                                                                        | 111 |

|-------|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       |    | 5.    | [5d] a p-type gate material formed above the barrier layer and between the source and drain contacts;                                                                                           | 111 |

|       |    | 6.    | [5e] and a gate metal disposed on the p-type gate material,                                                                                                                                     | 111 |

|       |    | 7.    | [5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and | 111 |

|       |    | 8.    | [5g] (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                                                     | 112 |

|       | H. | claim | m 6] The enhancement-mode GaN transistor according to 5, wherein the barrier layer comprises aluminum gallium e (AlGaN).                                                                        | 113 |

|       | I. | claim | m 7] The enhancement-mode GaN transistor according to 5, wherein the pair of self-aligned ledges are symmetric respect to the gate metal.                                                       | 113 |

| XIII. |    |       | 5: <i>YOSHIDA</i> IN VIEW OF <i>SAXLER</i> , <i>BEACH</i> , AND<br>ENDERS OBVIOUS CLAIMS 2 AND 5-7                                                                                              | 114 |

|       | A. | Overv | view of Ground 6                                                                                                                                                                                | 114 |

|       |    | 1.    | Motivation to Combine                                                                                                                                                                           | 114 |

|       | B. | claim | m 2] The enhancement-mode GaN transistor according to 1, wherein the pair of horizontal ledges of the p-type gate rial are self-aligned.                                                        | 119 |

|       | C. | Indep | pendent Claim 5                                                                                                                                                                                 | 121 |

|       |    | 1.    | [5p] An enhancement-mode GaN transistor, comprising:                                                                                                                                            | 121 |

|      |     | 2.    | [5a] a GaN layer;                                                                                                                                                                               | 121 |

|------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      |     | 3.    | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                           | 121 |

|      |     | 4.    | [5c] a source contact and a drain contact disposed on the barrier layer;                                                                                                                        | 122 |

|      |     | 5.    | [5d] a p-type gate material formed above the barrier layer and between the source and drain contacts;                                                                                           | 122 |

|      |     | 6.    | [5e] and a gate metal disposed on the p-type gate material,                                                                                                                                     | 122 |

|      |     | 7.    | [5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and | 122 |

|      |     | 8.    | [5g] (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                                                     | 123 |

|      | D.  | claim | m 6] enhancement-mode GaN transistor according to 5, wherein the barrier layer comprises aluminum gallium e (AlGaN).                                                                            | 124 |

|      | E.  | claim | m 7] The enhancement-mode GaN transistor according to 5, wherein the pair of self-aligned ledges are symmetric respect to the gate metal.                                                       | 124 |

| XIV. | CON | CLUS  | ION                                                                                                                                                                                             | 124 |

## I. INTRODUCTION

[001] I have been retained by Innoscience (Zhuhai) Technology Company, Ltd., and Innoscience America, Inc. (collectively "Innoscience"), as an independent expert for the above-identified inter partes review proceeding involving U.S. Patent No. 10,312,335 ("the '335 patent").

[002] I am over 21 years of age and, if I am called upon to do so, I would be competent to testify as to the matters set forth herein.

[003] Although I am being compensated for my time in connection with this proceeding at my standard hourly consulting rate and reimbursed for reasonable out-of-pocket expenses, no part of my compensation depends on the outcome of this proceeding, and I have no other interest in this proceeding.

[004] I have been asked to provide my opinion whether the claims of the '335 patent would have been obvious to a person of ordinary skill in the art at the time of the earliest claimed priority date of the '335 patent. In performing my analysis, I have been asked to assume that the priority date is April 8, 2009. My opinions are set forth below.

[005] Throughout this declaration, I refer to specific pages, figures, and/or line numbers of various exhibits. These citations are illustrative and are not

intended to suggest that they are the only support for the propositions for which they are cited.

#### II. SUMMARY OF OPINIONS

**[006]** This declaration analyses claims 1-7 of the '335 patent. Below, I set forth the opinions I have formed, the conclusions I have reached, and the bases for my opinions and conclusions. I believe the statements contained in this declaration to be true and correct to the best of my knowledge.

[007] Based on my experience, knowledge of the art at the time of the applicable priority date (I was told to assume a priority date of April 8, 2009), it is my opinion that claims 1-7 of the '335 patent would have been obvious based on the asserted grounds discussed below.

## III. QUALIFICATIONS AND BACKGROUND

[008] I believe that I am well qualified to serve as a technical expert in this matter based upon my qualifications, discussed in detail below. A copy of my curriculum vitae is attached as Appendix A.

[009] I am competent to write this Declaration.

[010] I have been involved in the science and engineering of high-power compound semiconductor transistors for over 40 years. I have been deeply involved in the research and design of III-V compound semiconductor devices over

the course of my career. I have been a Professor at Cornell University, School of Electrical and Computer Engineering, and have been teaching and conducting research at Cornell since 1987. In 2022, I was granted emeritus status.

[011] I received a B.S. degree from North Carolina State University in 1978, a M.S. from Rensselaer Polytechnic Institute in 1980, and a Ph.D. from Cornell University in 1983. I joined the Cornell faculty in 1987. And I am currently a Full Professor at Cornell's School of Electrical and Computer Engineering.

[012] In 1978, I joined the technical staff of General Electric's Corporate Research and Development Center under an Edison Fellowship. While there, among other work, I developed GaAs epitaxial materials for high voltage electronics. I was the inventor of two patents on Vertical Field Effect Transistors.

[013] In 1980, I transferred to General Electric's Advanced Electronics

Laboratory where I developed materials and processes for the fabrication of

AlGaAs LEDs as well as developing an OMVPE reactor and related processes for

the fabrication of AlGaAs quantum well laser diodes. In 1985, I was designated

Principal Staff Scientist at General Electric in recognition of my research

contributions.

[014] While at General Electric, I was also concurrently working at Cornell.

In 1984, my group at Cornell developed the first single quantum well red laser by

Organometallic Vapor-Phase Epitaxy ("OMVPE"), a technique used for growing semiconductor crystals. The fabrication of these devices involved multi-level metallization and dielectric passivation.

[015] I joined the Cornell faculty in 1987 as a Professor of Electrical and Computer Engineering (ECE) and Materials Science and Engineering (MSE).

While at Cornell I have continued my research in OMVPE, particularly as it relates to high frequency transistors, LEDs, and laser diodes. I have also researched GaN and related materials for both high-power transistors and LEDs.

[016] In 1997, I was named the Director of Cornell's Optoelectronics

Technology Center. In 1998, I was promoted to full professor at Cornell. I have

published over 120 articles and am the inventor of over 19 patents, many of which

deal with GaN-based materials and devices. Over the years, I have received

numerous teaching awards for delivering quality instruction to undergraduates in

Materials Science and Electrical Engineering.

[017] In 1998-99, the research group that I led invented and patented a single temperature method for nucleation and growth of GaN materials on sapphire, SiC, and Si substrates. This technique has become the preferred method for growing GaN-based transistors and LED today. This nucleation method was used to grow AlN/GaN layers on silicon. By mid-1999, my research group had

produced a gallium nitride-on-silicon (GaN-Si) RF transistor, a technology currently used by several GaN companies for high efficiency power convertors and RF amplifiers.

[018] By the early 2000s, my research group produced the first RF integrated circuits with gallium nitride-on-silicon carbide (GaN on SiC) transistors including X Band VCOs, TR switches, frequency doublers, and internally matched power amplifiers. By 2008, my group discovered a new passivation technology (LPCVD of AlSiN, patented) for GaN-based FETs which, when applied to GaNSiC HEMTs, produced the largest power density operation (over 18 Watts/mm at 10 GHz) ever observed on submicron gated devices. These devices also delivered record power-added-efficiencies and linear gain during 10 GHz operation (PAE > 65 %, Gain > 36 dB at 60 V bias). These benchmarks remain unchallenged today.

[019] In 2015, I cofounded Akoustis Technology (AKTS on the NASDAQ), a company which manufactures AlN bulk acoustic wave filters which are required for 5G communications. In 2019, I cofounded Odyssey Semiconductor, a company which is developing GaN Vertical field effect transistors for the emerging power convertor market. Odyssey Semiconductor also recently developed the fabrication techniques and built micro-LED Arrays in both AlGaInP and AlGaInN materials.

[020] I have remained current in the field, as evidenced by my publications listed in my curriculum vitae.

[021] I have also served as an expert in certain legal proceedings relating to GaN transistors, including materials growth, device fabrication, and packaging. A list of cases in which I have testified at trial, hearing, or by deposition is provided in my curriculum vitae.

## IV. MATERIALS CONSIDERED

[022] In forming my opinions, I read and considered the '335 patent and its prosecution history, the exhibits listed in the Exhibit List filed with the petition for *inter partes* review of the '335 patent, as well as any other materials referenced herein. I have reviewed the following at least the following documents:

| Exhibit  | Description                                                                                   |

|----------|-----------------------------------------------------------------------------------------------|

| Ex. 1001 | U.S. Patent No. 10,312,335 B2 to Cao et al. ("the '335 patent")                               |

| Ex. 1002 | Prosecution History of the '335 patent                                                        |

| Ex. 1005 | Japanese Patent Publication No. JP H11-261053 to Yoshida                                      |

| Ex. 1006 | Certified Translation of Japanese Patent Publication No. JP H11-261053 to Yoshida ("Yoshida") |

| Exhibit  | Description                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1007 | U.S. Patent Application Publication No. US 2006/0108606 A1 to Saxler et al. ("Saxler")                                                                                                         |

| Ex. 1008 | U.S. Patent Application Publication No. US 2007/0007547 A1 to Beach ("Beach")                                                                                                                  |

| Ex. 1009 | R.V. Shenoy and M. Datta, <i>Effect of Mask Wall Angle on Shape Evolution during Through-Mask Electrochemical Micromachining</i> , 143 J. Electrochemical Soc'y, pp. 544-549 (1996) ("Shenoy") |

| Ex. 1010 | U.S. Patent No. 5,905,274 to Ahn et al. ("Ahn")                                                                                                                                                |

| Ex. 1011 | U.S. Patent Application Publication No. US 2010/0258843 A1 to Lidow et al. ("Lidow")                                                                                                           |

| Ex. 1012 | U.S. Patent No. 9,748,347 to Cao et al. ("the '347 patent")                                                                                                                                    |

| Ex. 1013 | Prosecution History of the '347 patent                                                                                                                                                         |

| Ex. 1014 | Chuan Xu et al., The Leakage Current of the Schottky Contact on the Mesa Edge of AlGaN/GaN Heterostructure, 28 IEEE Electron Device Letters, pp. 942-944 (2007) ("Xu")                         |

| Ex. 1015 | U.S. Patent Application Publication No. US 2002/0066908 A1 to Smith ("Smith")                                                                                                                  |

| Ex. 1016 | U.S. Patent Application Publication No. US 2006/0273347 A1 to Hikita et al. ("Hikita")                                                                                                         |

| Ex. 1017 | U.S. Patent Application Publication No. US 2009/0072272 A1 to Suh et al. ("Suh")                                                                                                               |

| Exhibit  | Description                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1018 | X. Hu et al., Enhancement mode AlGaN/GaN HFET with selectively grown pn junction gate, 36 Electronics Letters, pp. 753-754 (2000) ("Hu")                                                                         |

| Ex. 1019 | U.S. Patent Application Publication No. US 2005/0087763 A1 to Kanda et al. ("Kanda")                                                                                                                             |

| Ex. 1020 | Yasushiro Uemoto et al., A Normally-off AlGaN/GaN Transistor with $R_{on}A=2.6\Omega cm^2$ and $BV_{ds}=640V$ Using Conductivity Modulation, 2006 International Electron Devices Meeting, IEEE (2006) ("Uemoto") |

| Ex. 1021 | U.S. Patent Application Publication No. US 2006/0019435 A1 to Sheppard et al. ("Sheppard")                                                                                                                       |

| Ex. 1023 | Dietrich W. Widmann, <i>Metallization for Integrated Circuits Using a Lift-Off Technique</i> , 11 IEEE Journal of Solid-State Circuits, pp. 466-471 (1976) ("Widmann")                                           |

| Ex. 1025 | Declaration of Kelley Green Hazel                                                                                                                                                                                |

| Ex. 1026 | Declaration of Shauna Wiest                                                                                                                                                                                      |

| Ex. 1027 | International Publication No. WO 2005/057624 to Beach, published June 23, 2005 ("Beach-II")                                                                                                                      |

| Ex. 1028 | Petitioner and Complainant's Proposed Claim Construction, ITC 337-TA-1366                                                                                                                                        |

| Ex. 1029 | C. S. Suh et al., "p-GaN/AlGaN/GaN Enhancement-Mode HEMTs, 2006 64th Device Research Conference, June 2006, pp. 163-164 ("Suh 2006")                                                                             |

[023] I reserve the right to supplement and amend any of my opinions in this declaration based on documents, testimony, and other information that becomes available to me after the date of this declaration.

## V. LEGAL STANDARDS

[024] I am not a lawyer. My understanding of the legal standards to apply in reaching the conclusions in this declaration is based on discussions with counsel for Petitioner, my experience applying similar standards in other patent-related matters, and my reading of the documents submitted in this proceeding. In preparing this declaration, I have tried to faithfully apply these legal standards to the challenged claims.

[025] I have been informed that there are two ways in which prior art may render a patent claim unpatentable. First, I have been informed that the prior art can "anticipate" a claim. Second, I have been informed that the prior art can render a claim "obvious" to a person of ordinary skill in the art. I understand that a claim is patentable if it was not anticipated and would not have been obvious by the prior art at the effective filing date of the patent.

[026] I have been informed that a dependent claim is a patent claim that refers back to another patent claim. I have been informed that a dependent claim includes all of the limitations of the claim to which it refers.

[027] I have been asked to provide my opinions as to whether the cited prior art teaches or renders obvious claims 1-7 of the '335 patent from the perspective of a person of ordinary skill in the art at the '335 patent's earliest claimed priority date in 2009, as described in more detail below.

[028] I have been informed that in *inter partes* review proceedings, such as this one, the party challenging the patent bears the burden of proving unpatentability by a preponderance of the evidence. I understand that a preponderance of the evidence means "more likely than not."

[029] For purposes of this declaration, I have been asked to provide my opinions on issues regarding unpatentability. I have been informed of the following legal standards, which I have applied in forming my opinions.

# A. Level of Ordinary Skill in the Art

[030] I have been informed a person of ordinary skill in the art is determined by considering several factors, including the (i) type of problems encountered in the art; (ii) prior art solutions to those problems; (iii) rapidity with which innovations are made; (iv) sophistication of the technology; and (v) educational level of active workers in the field.

[031] I have been instructed to assume a person of ordinary skill in the art is not a specific real individual, but rather a hypothetical individual having the qualities reflected by the factors discussed above.

## B. Anticipation

[032] I have been informed that under 35 U.S.C. § 102, a patent claim is unpatentable for anticipation if the claimed subject matter was patented or described in a printed publication before the effective filing date of the claimed invention. I have been informed that this is referred to as unpatentability by anticipation. I have been informed that a patent claim is anticipated under § 102 if a single prior art reference discloses all limitations of the claimed invention.

## C. Obviousness

[033] I have been informed that obviousness under 35 U.S.C. § 103, a patent claim is unpatentable if the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious to a person having ordinary skill in the art to which said subject matter pertains at the time the invention was made. I have been informed that this is referred to as unpatentability by obviousness.

[034] I have been informed that a proper obviousness analysis includes the following:

- a. Determining the scope and content of the prior art;

- b. Ascertaining the differences between the prior art and the claims at issue;

- c. Resolving the level of ordinary skill in the pertinent art; and

- d. Considering evidence of secondary indicia of non-obviousness (if available).

[035] I have been informed that the relevant time for considering whether a claim would have been obvious to a person of ordinary skill in the art is the time of invention. For my obviousness analysis, counsel for Petitioner instructed me to assume that the date of invention for the challenged claims is April 8, 2009. My opinions would not change if I assumed a later date of invention.

[036] I have been informed that a reference may be modified or combined with other references or with a person of ordinary skill in the art's own knowledge if the person would have found the modification or combination obvious. I have also been informed that a person of ordinary skill in the art is presumed to know all the relevant prior art, and the obviousness analysis may take into account the inferences and creative steps that a person of ordinary skill in the art would employ.

[037] I have been informed that whether a prior art reference renders a patent claim obvious is determined from the perspective of a person of ordinary skill in the art. I have also been informed that, while there is no requirement that the prior art contain an express suggestion to combine known elements to achieve the claimed invention, and while a suggestion to combine known elements to achieve the claimed invention may come from the prior art as a whole or individually and may consider the inferences and creative steps a person of ordinary skill in the art would employ, as filtered through the knowledge of one skilled in the art, obviousness grounds cannot be sustained by mere conclusory statements and must include some articulated reasoning with some rational underpinning to support the legal conclusion of obviousness.

[038] In determining whether a prior art reference could have been combined with another prior art reference or other information known to a person having ordinary skill in the art, I have been informed that the following principles may be considered:

- a. A combination of familiar elements according to known methods is likely to be obvious if it yields predictable results;

- b. The substitution of one known element for another is likely to be obvious if it yields predictable results;

- c. The use of a known technique to improve similar items or methods in the same way is likely to be obvious if it yields predictable results;

- d. The application of a known technique to a prior art reference that is ready for improvement to yield predictable results;

- e. Any need or problem known in the field and addressed by the reference can provide a reason for combining the elements in the manner claimed;

- f. A person of ordinary skill often will be able to fit the teachings of multiple references together like a puzzle; and

- g. The proper analysis of obviousness requires a determination of whether a person of ordinary skill in the art would have a "reasonable expectation of success"—but not "absolute predictability" of success—in achieving the claimed invention by combining prior art references.

[039] I have been informed that, when a work is available in one field, design alternatives and other market forces can prompt variations of it, either in the same field or in another. I have been informed that if a person of ordinary skill in the art could have implemented a predictable variation and would have seen the

benefit of doing so, that variation is likely to have been obvious. I have been informed that, in many fields, there may be little discussion of obvious combinations, and in these fields market demand—not scientific literature—may drive design trends. I have been informed that, when there was a design need or market pressure and there are a finite number of predictable solutions, a person of ordinary skill in the art would have had a good reason to pursue those known options.

[040] I have been informed that the law permits the application of "common sense" in examining whether a claimed invention would have been obvious to a person skilled in the art. For example, I have been informed that combining familiar elements according to known methods and in a predictable way may suggest obviousness when such a combination would yield nothing more than predictable results. I understand, however, that a claim is not obvious merely because every claim element is disclosed in the prior art and that a party asserting obviousness must still provide a specific motivation to combine or modify the references as recited in the claims and explain why one skilled in the art would have reasonably expected to succeed in doing so.

[041] I have been informed that there is no rigid rule that a reference or combination of references must contain a "teaching, suggestion, or motivation" to

combine references. But I also understand that the "teaching, suggestion, or motivation" test can be a useful guide in establishing a rationale for combining elements of the prior art. I have been informed that this test poses the question as to whether there is an express or implied teaching, suggestion, or motivation to combine prior art elements in a way that realizes the claimed invention, and that it seeks to counter impermissible hindsight analysis.

[042] I am not aware of any evidence of secondary considerations that would support a determination of non-obviousness of the claimed subject matter in the '335 patent.

[043] I have been informed that, in an obviousness analysis, prior art must be analogous prior art to the patent being considered. I have been informed that a prior art reference is considered to be analogous, or in the same field of art, if the reference is either (1) in the same field of endeavor as the challenged patent, regardless of the problems the challenged patent and the prior art address, or (2) reasonably pertinent to the particular problem being solved by the challenged patent.

## VI. OVERVIEW OF THE '335 PATENT

## A. The Claims and Specification

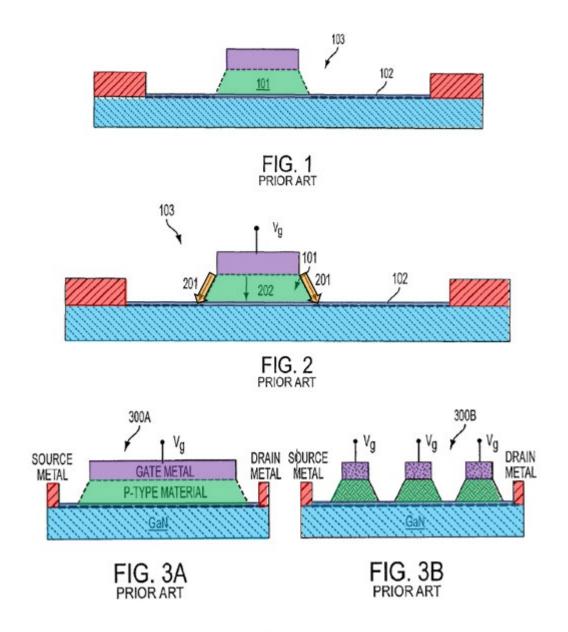

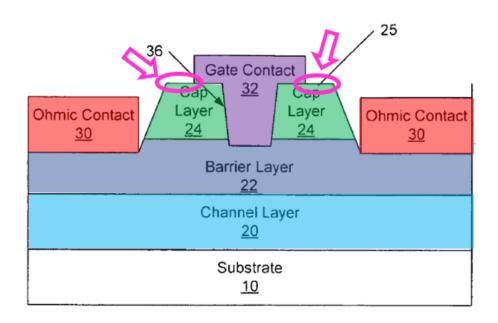

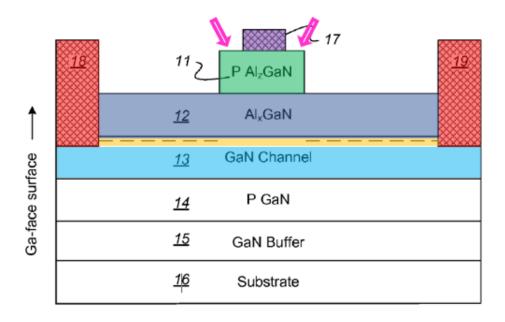

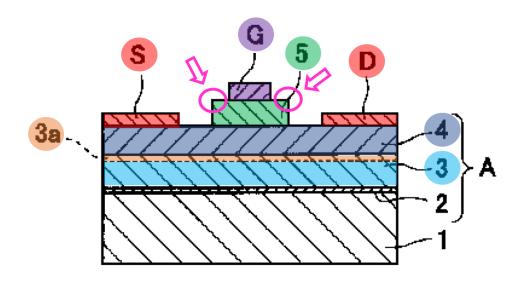

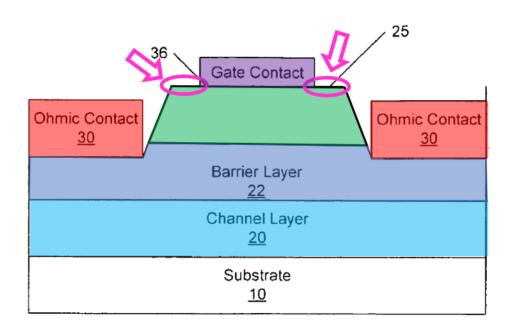

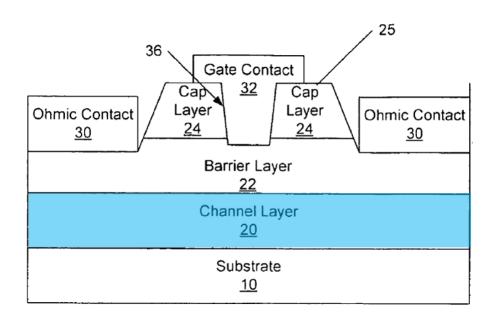

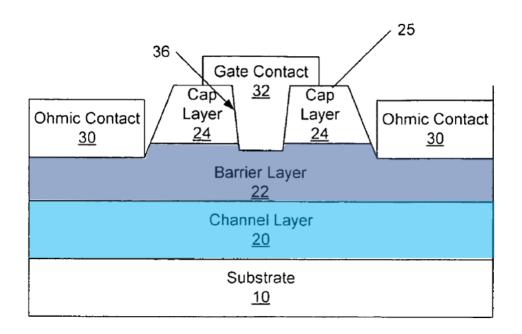

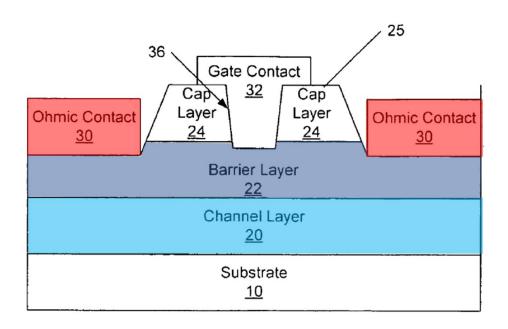

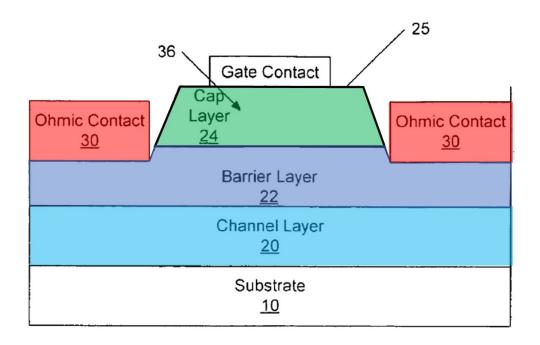

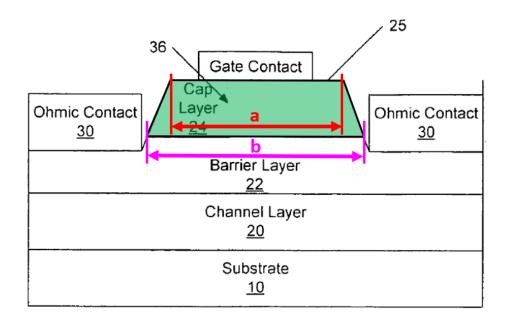

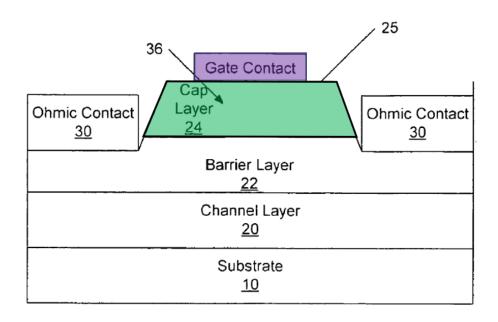

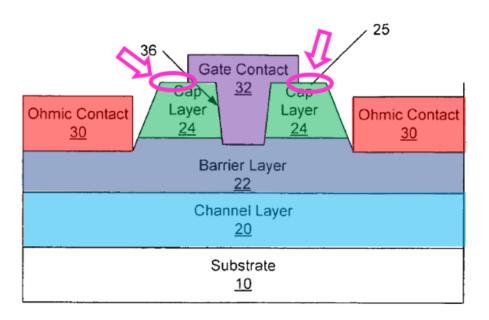

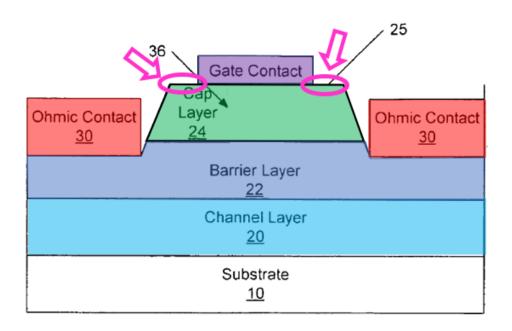

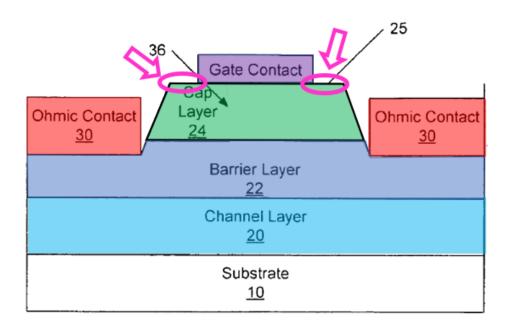

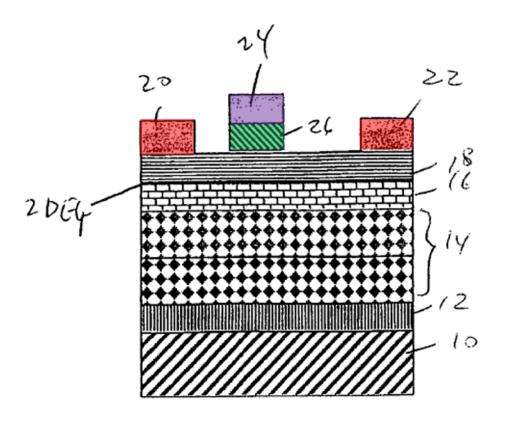

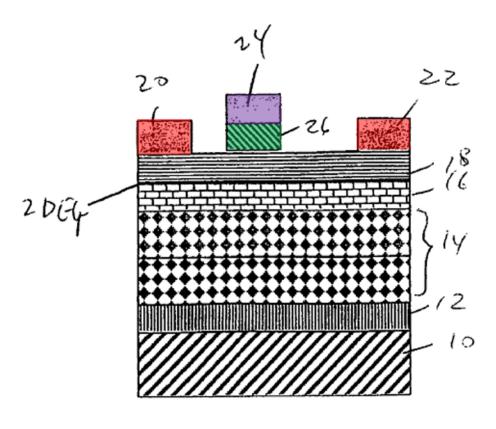

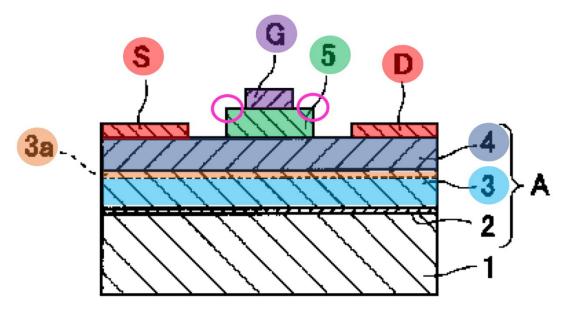

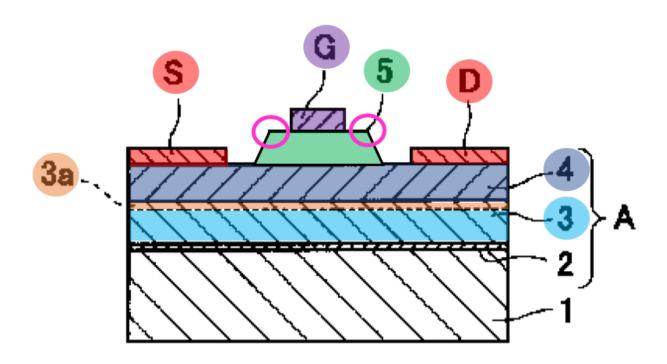

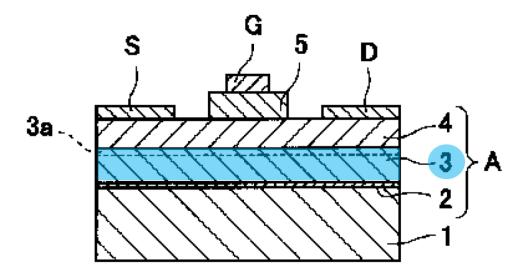

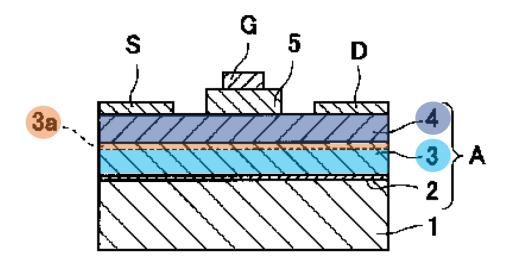

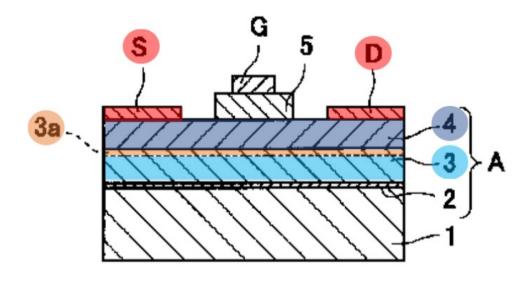

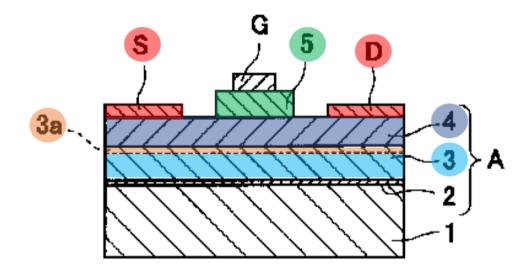

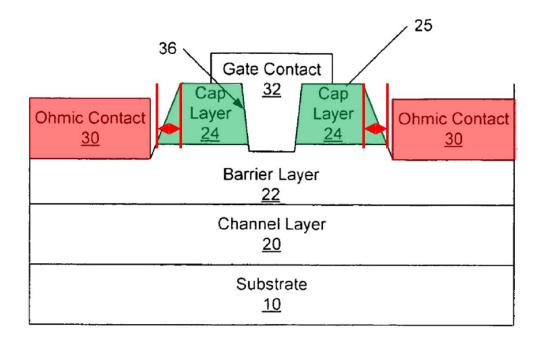

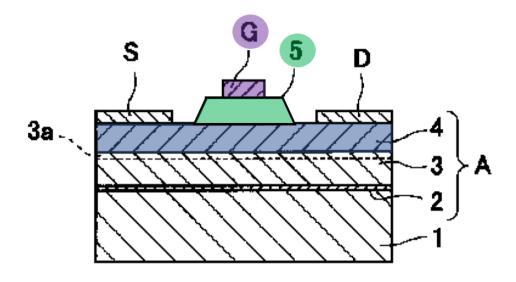

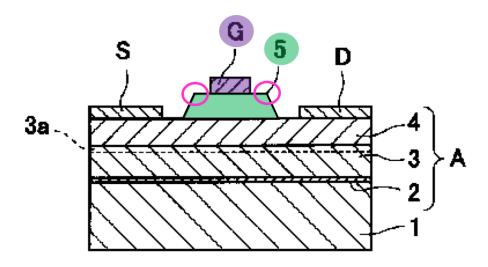

[044] The '335 patent relates to enhancement-mode GaN power transistors. Ex. 1001, 1:21-26, 2:34-57, Fig. 5, claims 1-7. Consistent with my own understanding of the state of the art prior to April 2009, the patent describes that conventional prior art GaN HEMT devices suffered from high gate leakage current between the gate and 2DEG region. Ex. 1001, 1:21-2:30. It admits that conventional GaN enhancement-mode devices included a GaN channel layer, an AlGaN barrier layer, source and drain electrodes, and a gate structure consisting of a p-type GaN layer with sloped sidewalls and an overlying gate metal—all features that are in the claims of the '335 patent. Ex. 1001, 1:21-2:30, Figs. 1-2, 3A-3B, claims 1-7. And the figures show numerous prior art systems with these features. Ex. 1001, 1:21-2:30, Figs. 1-2, 3A-3B. Figure 2 shows surface leakage path 201 along the sloped sidewalls of the p-type GaN layer 202. Id.

Ex. 1001, Figs. 1-2, 3A-3B.

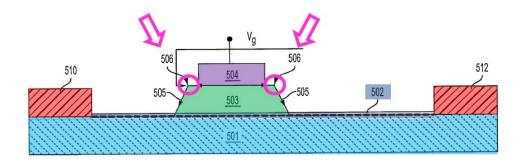

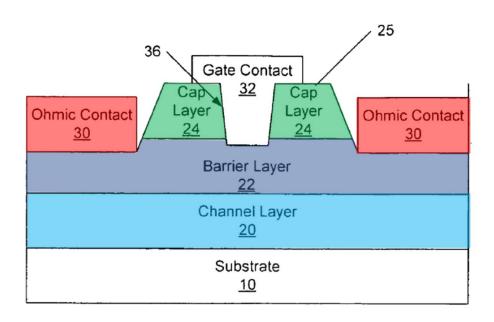

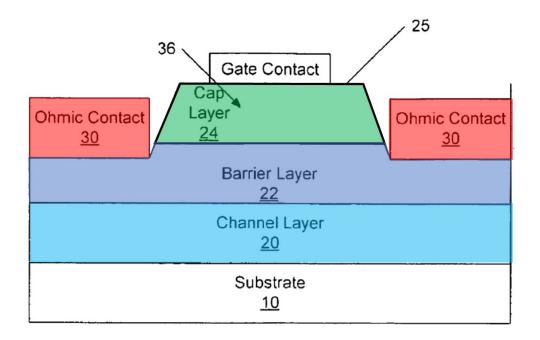

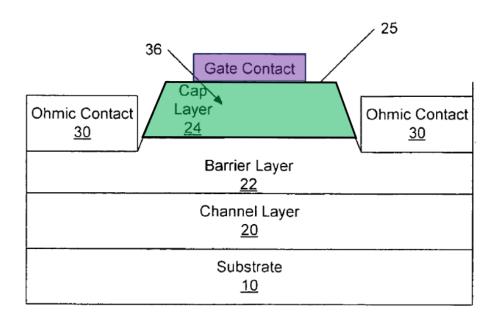

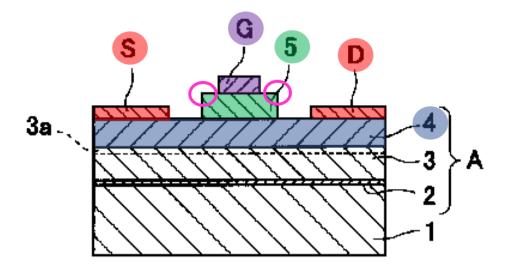

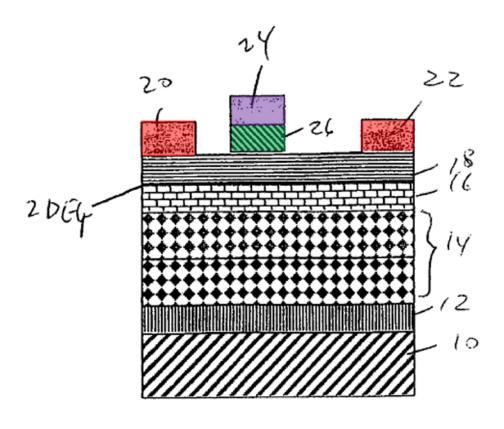

[045] To solve the leakage problem, the '335 patent purports to invent *just* one feature: a pair of ledges on the p-type gate material, on either side of the gate metal. Ex. 1001, 2:34-57, 3:65-4:12, 4:40-51, Figs. 1-2, 3A-3B, 4-5, 7A-7B, 8, claims 1-7.

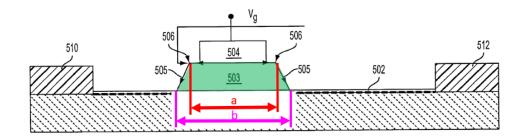

Ex. 1001, Fig. 5.

[046] But, as I will explain in this declaration, the claims were obvious over the prior art. Those ledges were well-known and common going back many years before the '335 patent. *Infra* §§X-XIII (Grounds 1-6). Indeed, the '335 patent's priority application *Lidow* notes such ledges were conventional. *Lidow*, [0006], Fig. 1.

## Lidow, Fig. 1.

[047] In some claimed embodiments, the '335 patent makes its ledges using a self-alignment process. Ex. 1001, 4:14-39, claims 2, 5. Figures 6A-6C disclose a method of making these "self-aligned ledges." Ex. 1001, 4:14-39. Priority applications also disclose "self-aligned gate" structures having symmetric ledges but do not describe the details of Figures 6A-6C. *E.g.*, *Lidow*, Abstract, [0008], [0022]-[0023], [0029]-[0030], [0036], [0038], [0040], [0044], [0046], claims 1, 6, 9, 10, 23.

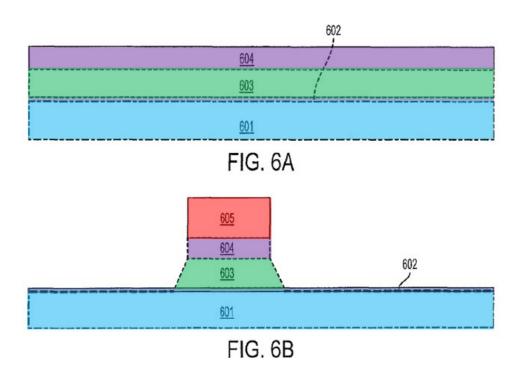

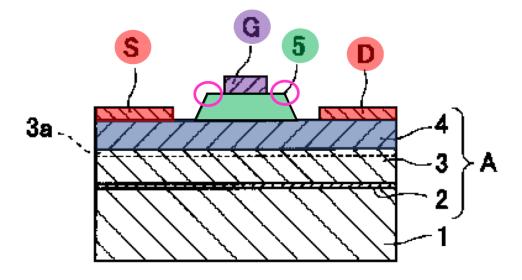

[048] In the '335 patent, the self-aligned method includes forming GaN layer 601, AlGaN layer 602, and p-type gate material 603, then depositing the gate metal 604 as Figure 6A depicts. Ex. 1001, 4:14-39. The self-aligned method then applies photoresist 605, etches the gate metal, and etches the p-type gate material so that the outer walls p-type gate material 603 and gate metal align as shown in Figure 6B. Ex. 1001, 4:14-26.

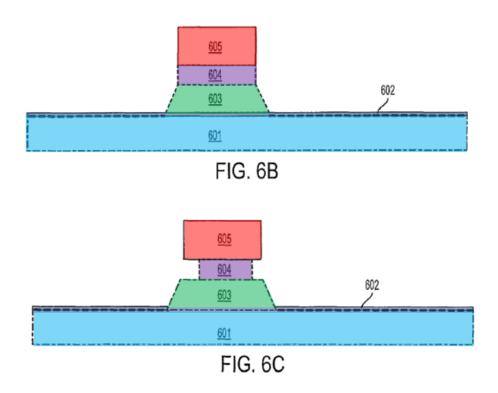

Ex. 1001, Figs. 6A-6B.

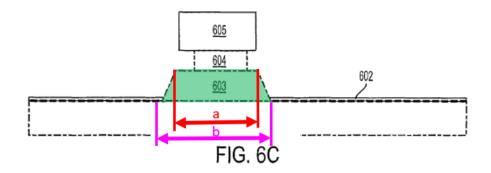

[049] The '335 patent discloses that one way to complete the "self-aligned" ledges is to next "isotropically" etch the **gate metal** and undercut the same **photomask**, as shown in Figures 6B-6C. Ex. 1001, 4:23-39.

Ex. 1001, Figs. 6B-6C.

## **B.** Prosecution History

[050] The '335 patent was filed on July 20, 2017, as U.S.

Application 15/655,438. Ex. 1001, cover. The independent claims included the p-type gate metal material, overlying gate metal, and a pair of horizontal ledges, but did not include the sloped sidewall features. Ex. 1002, 77-79. The application received one non-final Office Action rejecting claims 1-3, 5-8, and 10-11 under 35 U.S.C. § 102, as anticipated by *Hikita* (Ex. 1016). Ex. 1002, 36-43. To overcome the rejection, the applicant amended the independent claims to include sloped sidewalls. Ex. 1002, 34-35, 7-15. The Examiner then allowed the claims, stating

that the combination of the sloped sidewalls and horizontal ledges were allowable. Ex. 1002, 12.

[051] During the examination of the parent application, U.S. Application No. 14/447,069 (U.S. Patent No. 9,748,347 ("the '347 patent")), I understand that the applicant initially received a rejection over prior art reference *Lidow*, then subsequently claimed priority to *Lidow* a continuation-in-part. Ex. 1013, 95-128, 250. The applicant nevertheless next received a rejection over *Lidow* because the claims included the term "isotropically etching," which was not recited in *Lidow*. Ex. 1013, 84-86. The Examiner only found support for the claims of the '347 patent after the applicant broadened the claim to remove the term "isotropically" from the claim. Ex. 1013, 52, 75-76, 85-86. In my opinion, the apparatus claims of the '335 patent covers substantially the same subject matter as the structure which results from the method claims of the '347 patent. Ex. 1001; Ex. 1012. Thus, to the extent the priority claim is valid (which I assume without offering an opinion), Lidow also supports the claims of the '335 patent.

## VII. LEVEL OF ORDINARY SKILL IN THE ART

[052] In rendering the opinions set forth in this declaration, I have been asked to consider the '335 patent's claims and the prior art through the eyes of a person of ordinary skill in the art (which I may also refer to as "one skilled in the

art," "skilled artisan," "POSITA," "POSA" or similar variation). I have considered factors such as the educational level and years of experience of those working in the pertinent art, the types of problems encountered in the art, the teachings of the prior art, patents and publications of other persons or companies, and the sophistication of the technology.

[053] Taking the factors described in the Legal Standards – Level of Ordinary Skill in the Art section into consideration, it is my opinion that a person of ordinary skill in the art for the '335 patent would have had at least a four-year degree in electrical engineering, chemical engineering, physics, or material science or a closely related field and at least two years of experience in semiconductor device design or fabrication, including the processing of semiconductor materials, analysis of device operation, or the development of new device topologies.

Additional education could substitute for professional experience and vice versa.

[054] Based on my educational background and experience, I was at least a person of ordinary skill in the art at the earliest priority date of the '335 patent.

# VIII. TECHNOLOGY BACKGROUND AND THE STATE OF THE PRIOR ART

[055] Power transistors fabricated with GaN have a large band gap which increases the maximum electric field strength, resulting in a large breakdown voltage making them attractive for high power applications. Ex. 1001, 1:30-49.

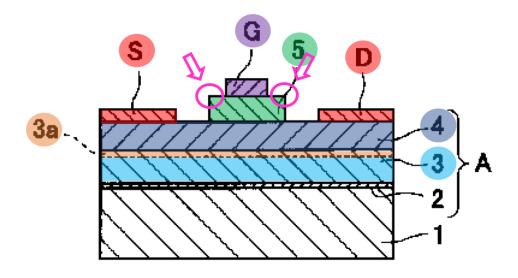

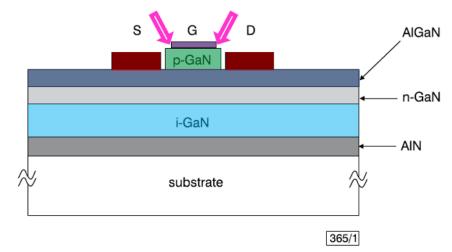

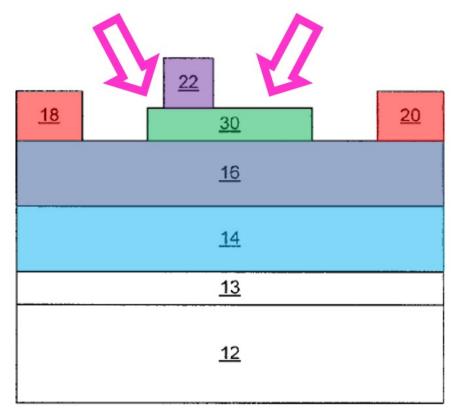

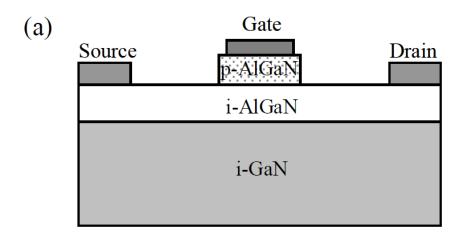

They were well known long before the '335 patent. *E.g.*, *Smith*, [0004]-[0010] (discussing "well known" features of GaN HEMT devices). Conventional features of such transistors include a **GaN channel** and **AlGaN barrier** layers, at the heterojunction of which a **two-dimensional electron gas (2DEG) region** forms, as well as **source** and **drain electrodes**, and a gate structure including **GaN gate materials** under a **gate metal**. Ex. 1001, 1:28-2:26; *Yoshida*, Abstract; *Suh*, [0002]-[0005], [0015], Figs. 1, 6-7.

[056] Enhancement-mode GaN transistors are normally off, meaning no drain current flows through the 2DEG without applying positive voltage to the gate. Ex. 1001, 1:50-53, 1:64-2:2; *Hu*, 1. These devices achieve the normally-off state in part with a **GaN layer**, often doped p-type, in the gate structure under a **gate metal**, which increases the gate voltage (to a positive value) where the gate has a strong influence on the electron concentration in the 2DEG. Ex. 1001, 1:50-53, 1:64-2:2; *Hu*, 1.

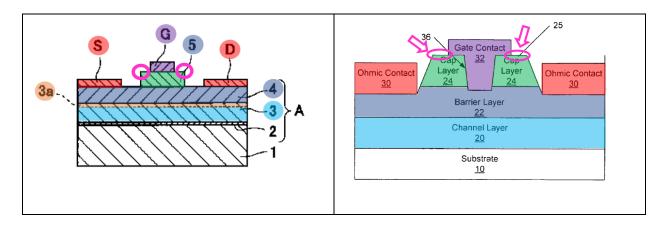

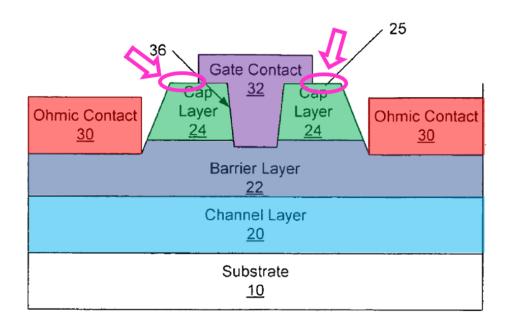

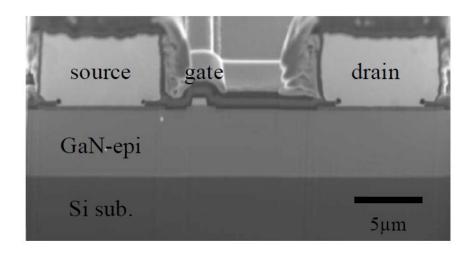

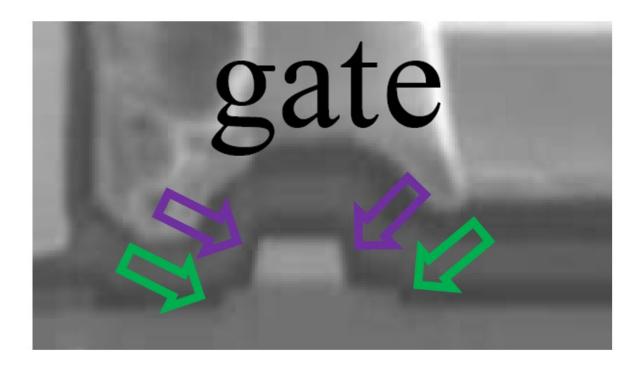

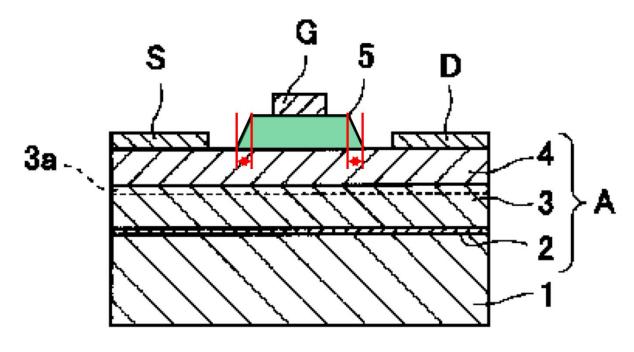

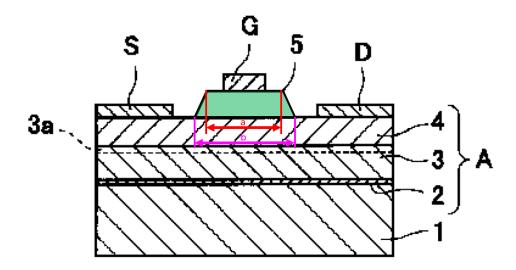

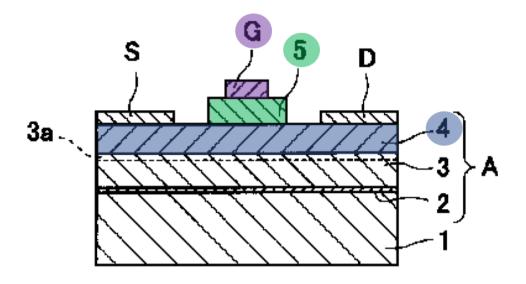

[057] Example GaN HEMT arrangements in publications ranging from 1999 through 2009 (the earliest claimed priority date of the '335 patent), are shown below. I have marked horizontal ledges at the surface of the p-type GaN gate materials:

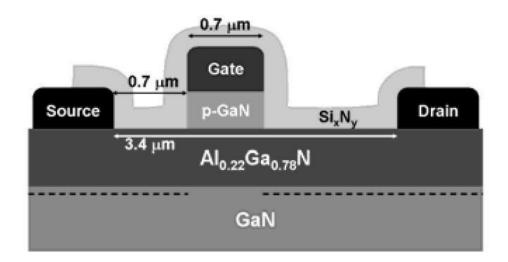

Yoshida, Fig. 1 (1999).

Fig. 1 Schematic diagram of structure of pn junction regrown gate HFET

Hu, Fig. 1 (2000).

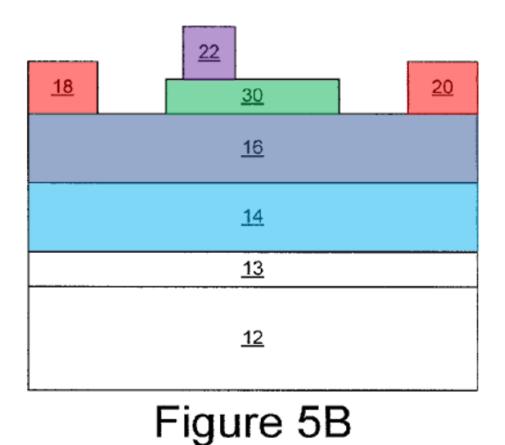

Figure 5B

Smith, Fig. 5B (2002).

Saxler, Fig. 1A (2006).

Suh, Fig. 6 (2009).

[058] As these examples illustrate, the sole point of alleged novelty of the '335 patent, horizontal ledges at the surface of p-type GaN gate materials, were common, just as were the other features of the claims.

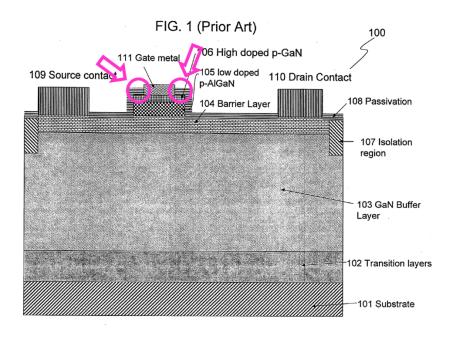

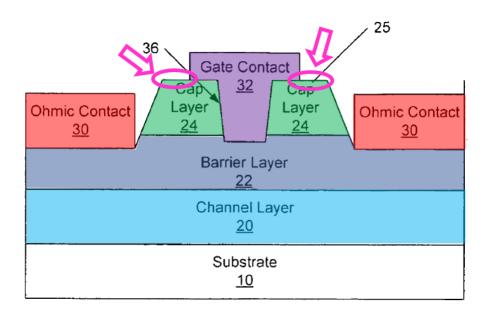

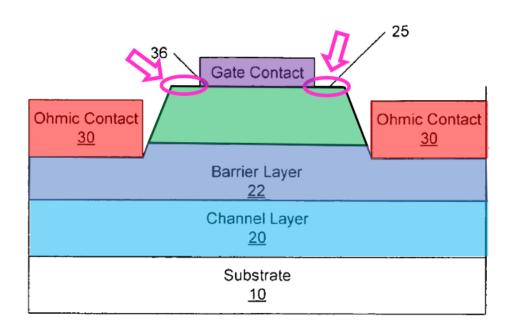

[059] The prior art also included many different methods of manufacturing features of GaN HEMT devices. For example, single-mask techniques to self-align stacked gate structures were long known. *Beach*, [0040]. Conventional etching techniques achieved sloped sidewalls, which were known to increase leakage paths. Ex. 1001, 1:64-2:8, Fig. 2; *Saxler*, [0064], Figs. 1A-1B; *Ahn*; *Xu*; *Sheppard*, [0044]. And it was conventional to create undercuts under photomasks to isotropically etch metals. *Shenoy*.

[060] A POSITA would have been familiar with many methods of making stepped gate structures with horizontal ledges, including (i) sequential masking and etching steps, (ii) lift off techniques, and (iii) self-aligned techniques. For example, *Yoshida* discloses masking and etching the p-type GaN layer 5, then depositing the gate electrode. *Yoshida*, [0022]-[0023]. *Hu* grows gate layers in "selective areas defined by openings in an SiO<sub>2</sub> mask." *Hu*, 1. *Smith* fabricates its gate structure by patterning the GaN cap layer, using conventional etching to remove portions of it, then forming a gate electrode on the GaN segment. *Smith*, [0040]-[0041]. *Smith* also uses "conventional photolithographic techniques and

mask alignment tools" to align the edges of a cap layer and gate in some embodiments, i.e., *self-alignment*. *Smith*, [0041]. *Saxler* discloses sequential masking, etching, and deposition steps to form its stacked gate structure. *Saxler*, [0064]-[0066]. *Suh* likewise etches "to define a gate region where the p-type Al<sub>z</sub>GaN cap 11 is located," and depositing the gate on top. *Suh*, [0056].

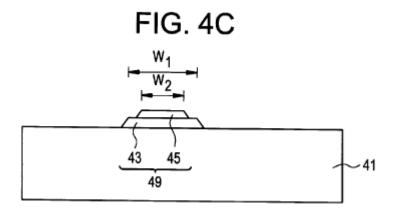

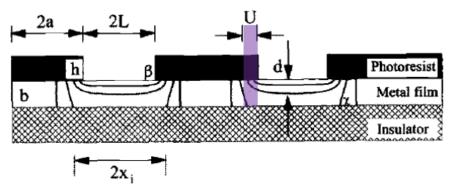

[061] *Beach* makes a self-aligned two-layer gate structure using a single photomask. *Beach*, [0040], [0045], [0054]. *Ahn*, published in 1999, likewise uses a single mask and further discloses isotropic and anisotropic etching techniques to create stacked gate structures having stepped features and sloped sidewalls, as shown below. *Ahn*, Abstract, 3:41-58, 6:15-26, 7:7-14, Fig. 4C.

Ahn, Fig. 4C.

[062] In addition, long before the '335 patent, *Shenoy* discloses techniques to isotropically etch and undercut metal layers below masks, which a POSITA

would understand would be one method of forming stepped gate structures. Shenoy, 2-3. Lift-off had similarly been known for decades for creating stepped metal structures. Ex. 1023.

[063] Typical GaN HEMT devices thus included every feature of the claimed enhancement-mode transistor and they disclosed methods of making such a transistor.

#### IX. CLAIM CONSTRUCTION

[064] I am not an attorney. However, I have been informed by counsel of certain legal standards that apply with respect to claim construction and indefiniteness, and have used those standards, described below in formulating my opinions.

[065] I have been instructed that the "intrinsic record" includes the patent itself, including the claims, description, and figures (Ex. 1001), and the patent's prosecution history—i.e., the record of proceedings at the U.S. Patent and Trademark Office ("Patent Office") concerning the patent (Ex. 1002). I understand that, like the claims and written description, the prosecution history provides evidence to a person of ordinary skill in the art of how the inventor intended his patent to be understood, and how the Patent Office understood the patent. I understand that the inventor is permitted to apply a special definition to the terms

or to limit the scope of claim terms in his patent claims, which may differ from the term's plain and ordinary meaning. That special definition or limitation on scope may be provided in the patent's written description, the patent's prosecution history, or both.

[066] I understand that claim interpretation may also be informed by "extrinsic evidence" (that is, evidence outside of the patent record itself). I have been informed that extrinsic evidence may include dictionaries, technical treatises, and other materials evidencing the meaning of a claim term and the understanding held by a person of ordinary skill in the relevant time period.

[067] I am also informed by counsel that the applicant of the '335 patent can act as their own lexicographer, to set forth a definition of a claim term in the specification. The definition provided by the applicant can differ from the claim term's plain and ordinary meaning. I have also been informed by counsel that when a patent claim uses the term "comprises" as a transitional statement after the preamble, there is a presumption that the claim is open-ended and not limited to the recited elements.

[068] I have been asked for purposes of this declaration to apply the plain and ordinary meaning of the claim terms as they would have been understood by a

person of ordinary skill in the art at the earliest claimed priority date of the '335 patent, other than as identified below.

[069] Based on my review of these materials and my personal knowledge and experience, I have considered the plain and ordinary meaning of each term of the '335 patent as it would have been understood by one skilled in the art at the earliest claimed priority date of the '335 patent of April 8, 2009. I apply the plain and ordinary meaning of each claim term throughout this declaration, other than as identified below.

A. "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

[070] I have been informed that the owner of the '335 patent Efficient Power Conversion Corporation (EPC or Patent Owner) and Petitioner Innoscience have agreed in a related matter that the terms "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer" in claims 1 and 5 of the '335 patent should be construed. *ITC Constructions*, pp. 1, 4, 8-9. The parties proposed the following constructions:

| Petitioners'                      | Patent Owner's                    |

|-----------------------------------|-----------------------------------|

| "side surfaces of the p-type gate | "p-type gate material having side |

| material such that the bottom of  | surfaces extending horizontally   |

| the p-type gate material is more  | such that the bottom of the       |

| than 10% wider than the top of    | material is wider than the top of |

| the material, leading to sloped   | the material"                     |

| side surfaces that contact the    |                                   |

| barrier layer"                    |                                   |

[071] As I explain below, the challenged claims are unpatentable under both constructions. But to the extent the Board constructs the term, Petitioners' proposed construction should apply.

[072] In my view, the construction agrees with the disclosure of the prior application, *Lidow*, which provides support for the present claims (§VI.B (Prosecution History)). *Lidow* discusses the advantage of using sloped sidewalls in a p-type GaN gate layer to reduce gate leakage. *Lidow*, [0041]-[0042], Fig. 8. The only way *Lidow* distinguishes its sidewalls is by indicating that a "base that is more than 10% wider than the top" advantageously "causes a longer path for electrons to

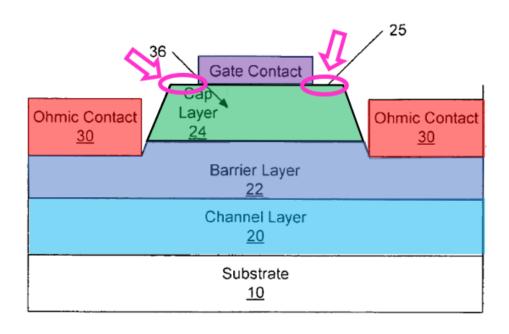

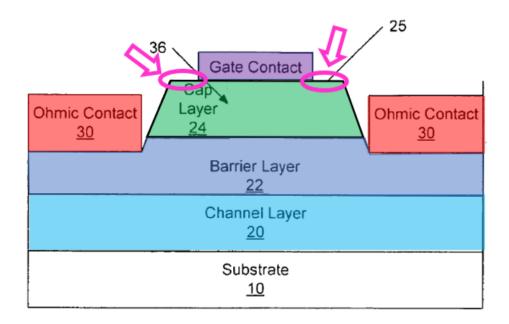

travel between the gate metal 17 and the 2DEG along the pGaN side wall," thereby "result[ing] in lower gate leakage." *Id.*, [0042]. *Lidow*'s depicts and describes the same p-type layer and gate structure that the '335 patent discloses. *Id.*, Fig. 8; Ex. 1001, 3:49-64, Fig. 5.

[073] Petitioner's construction aligns with the purpose of the '335 patent, which is to lower gate leakage, including through the conventional method of sloping the sidewalls to increase the length of sidewall leakage path 201. Ex. 1001, Abstract, 1:21-26, 2:20-48, 3:65-4:12, 4:40-51, Figs. 2, 4, 7A-7B, 8.

[074] Aside from the 10% guidance, *Lidow* provides no other explanation of how much slope would be necessary to achieve the alleged improvement of the '335 patent, reduced gate leakage. Explicit guidance on the amount of slope would be needed to distinguish the claim from the prior art because nearly all layers have at least slightly sloped sidewalls. Few structures, if any, have perfectly vertical sidewalls in practice, even if depicted as vertical in functional diagrams, a point that which *Saxler* notes. *Saxler*, [0042]; *Uemoto*, Figs. 1-2, 5; *infra* §XII.C.5 (Ground 4, Limitation [1d]). *Lidow* controls the shape of the p-type GaN material during etching to achieve a base 10% wider than the top and gain the alleged benefits of lower gate leakage due to a longer leakage path as compared to leakage

rates in the prior art. *Lidow*, [0041]-[0042]. Petitioners' construction makes this distinction clear, unlike Patent Owner's construction.

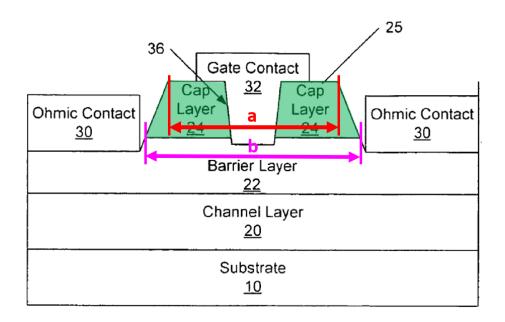

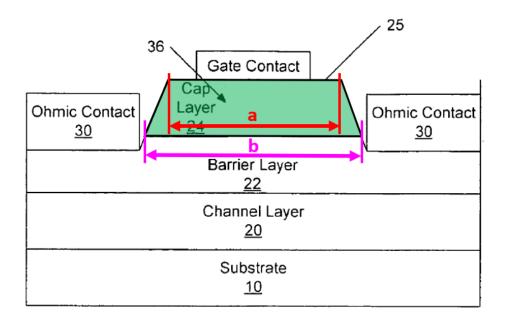

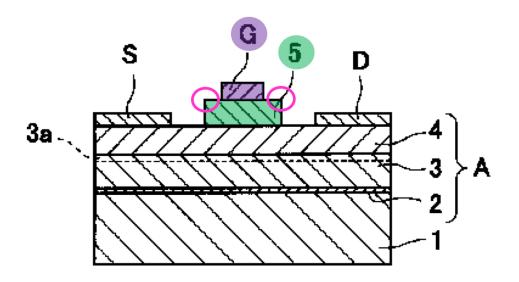

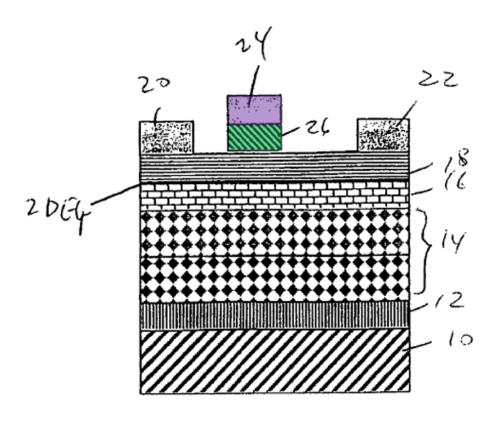

[075] Petitioner's construction likewise agrees with the '335 patent specification. For example, the '335 patent shows a p-type gate material with sloped side surfaces whose bottom surface is more than 10% wider than the top. Ex. 1001, Figs. 5, 6C, 7B.

Ex. 1001, Fig. 5.

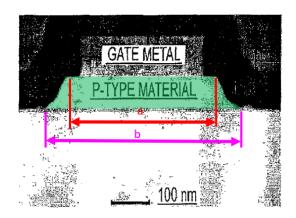

Width "b" above is approximately 1.32 times the width of "a" (~30% wider), and the same holds true for Figures 6C and 7B ("b" is 1.36 times wider than "a" in 6C and 1.34 times wider in 7B). If the Patent Owner argues that Fig. 5 and 6C are schematic diagrams not intended to be drawn to scale, Fig. 7B is an actual image of the etched gate structure, and my measurements confirm it has similar dimensions to Fig. 5 and Fig 6C.

Ex. 1001, Fig. 6C.

FIG. 7B

Ex. 1001, Fig. 7B.

[076] Of course, any reference that discloses this term under Petitioners' construction will also disclose this term under Patent Owner's broader construction, which is satisfied with any amount of slope whatsoever. All my analysis below showing the references disclose or render obvious the claim elements under Petitioner's construction will thus apply to either construction. Further, if Patent Owner's broader construction is accepted, the patent is

unpatentable under an additional ground, Ground 4, because, as I will explain below, a POSITA would have understood that *Yoshida*'s sidewalls would have included at least a slight slope in practice, although it draws its sidewalls vertically.

### B. "self-aligned" ledges

[077] I have been informed that Petitioners proposed that the terms "wherein the pair of horizontal ledges of the p-type gate material are self aligned"/

"a pair of self-aligned ledges," which are recited in dependent claim 2 and independent claim 5, are "product-by-process limitations." ITC Constructions, pp.

1, 4. I agree with Petitioners that these terms describe how the ledges are made, not what the ledges are. As I explain below, "self-aligned" is just one way to make these ledges. There are many other ways to manufacture the ledges described, depicted, and claimed in the '335 patent.

[078] The patent itself admits there are other ways to make the claimed ledges, and a "self-aligned" ledge refers to the process by which the claimed gate structure is made and does not describe the structure itself. Ex. 1001, 4:14-39; Lidow, Abstract, [0008], [0022]-[0023], [0029]-[0030], [0036], [0038], [0040], [0044], [0046], Figs. 6A-6C, claims 1, 6, 9, 10, 23. The '335 patent notes that "the gate contact includes a p-type gate material 503 formed on the barrier layer 502 and includes ledges 506 that are created by a self-aligned process at the top

corners of the p-type gate material 503." Ex. 1001, 3:49-53. The patent repeatedly refers to this "self-aligned manufacturing *process*." Ex. 1001, 3:13-15, 3:49-53, 3:65-4:39, 4:52-63, Figs. 6A-6B.

[079] Claim 3 of the issued parent application, the '347 patent, illustrates that "self-aligned" ledges refers to how the ledges are made, not what they are. It recites "[t]he *method* according to claim 1, wherein the pair of ledges of the p-type gate material *are self-aligned*."

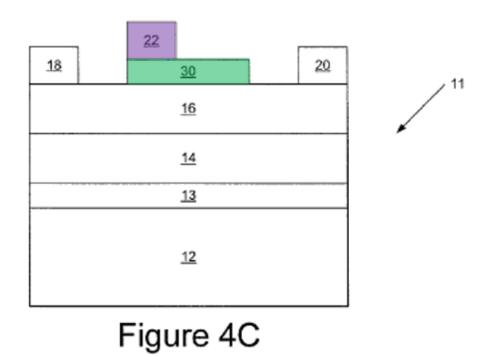

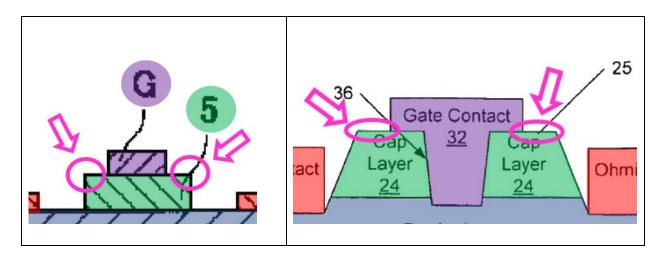

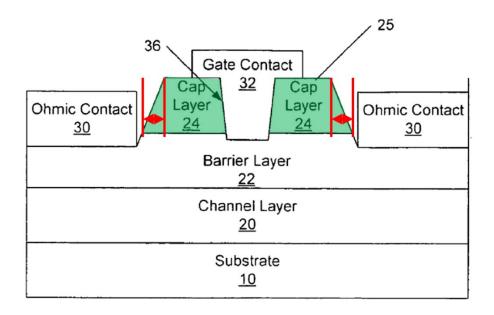

[080] This is consistent with how "self-aligned" would have been understood by a POSITA—as a product made by a process. For example, *Smith*, a 2002 patent publication, discloses making the *same* gate structure two ways—one way uses a process that is not "self-aligned" (Fig. 4C) while the other uses a "self-aligned" process (Fig. 6C).

[081] Referring to Fig. 4C, *Smith* describes a gate structure that is not self-aligned. *Smith*, [0041]. *Smith* states that "[i]n the embodiments shown in FIGS. 4A through 4C, the source-side sidewall of the **gate contact** is aligned with the source-side sidewall of the **GaN cap segment 30** using *conventional photolithographic* techniques and mask alignment tools," and it shows the gate is indeed aligned on one side to the source-side sidewall. *Smith*, [0041], Fig. 4C.

Smith (Fig. 4C, not "self-aligned)

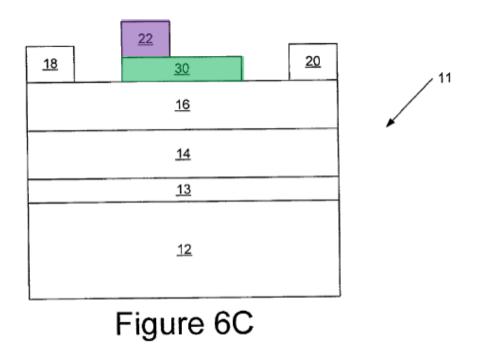

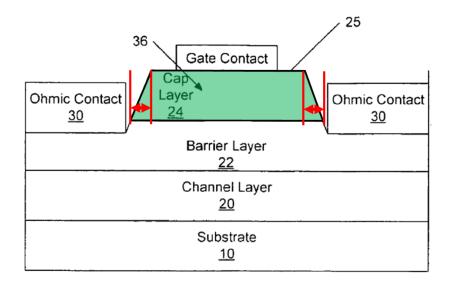

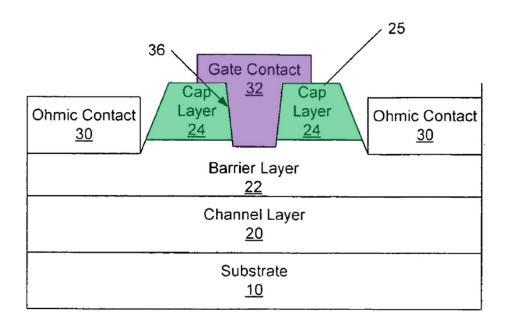

[082] *Smith* also discloses making this selfsame gate structure using a "self-aligned method" in [0042]-[0044] and figures 6A-6C. *Smith* explains this approach involves layering the **gate contact** on the **GaN cap segment**, then etching them both with a single mask:

An etch mask 44 is deposited on the GaN cap layer 30' which partially overlaps the gate metal 22' so as to define the source-side sidewall of the gate electrode 22 and the GaN cap segment 30 and the drain-side sidewall of the GaN cap segment 30.

Smith, [0043].

As illustrated in FIG. 6B, the exposed portion of the GaN cap layer 30' is etched away, leaving one sidewall of the

GaN cap segment 30 self-aligned with a sidewall of gate electrode 22.

Smith, [0044].

Smith (Fig. 6C, "self-aligned")

[083] As another example illustrating that illustrates a POSITA would have understood "self-aligned" ledges only describes that the ledges were made by a "self-aligned" process, *Beach* discloses the method of "pattern[ing]" (applying the mask) and etching the two layers of "the stack," the "gate arrangement 24" and "gate barrier 26," which "results in a self-aligned gate arrangement." *Beach*, [0040]. This reference is by the same Robert Beach that is a co-inventor on the priority application *Lidow*, which further supports that the '335 patent's "self-

aligned" ledges (which allegedly have support in *Lidow*) refers to a process by which the ledges are made. *Beach*, cover; *Lidow*, cover; § VI.B.

[084] Suh 2006 also describes using a "self-aligned" process to make its gate structure. Referring to enhancement-mode HEMT of Fig. 1, it states "The p-GaN in the source/drain regions was etched away prior to ohmic metal deposition using a self-aligned dry etch while the p-GaN in the access regions was etched away using the ohmic contacts and the gate electrode as masks." Suh 2006, 1.