```

(19) [Issuing Country] Japan Patent Office (J2 layer structure P)

```

- (12) [Gazette Type] Published Patent Gazette (A)

- (11) [Publication No.] Patent Publication No. H11-261053

- (43) [Date of Publication] September 24, 1999

- (54) [Title of Invention] High Mobility Transistor

- (51) [International Patent Classification, 6th edition]

H01L 29/778

21/338

29/812

[FI]

H01L 29/80 H

[Request for Examination] Not requested

[Number of Claims] 2

[Application Format] OL

[Total Pages] 4

- (21) [Application No.] Application H10-57070

- (22) [Filing Date] March 9, 1998

- (71) [Applicant]

[Identification Number] 000005290

[Name or Designation] Furukawa Electric Co.

- (72) [Inventor]

- (72) [Name] Seiki YOSHIDA

- (74) [Agent]

[Patent Attorney]

(74) [Name or Designation] Kanji NAGATO

#### (57) Abstract

Problem: To provide a high-mobility transistor (HEMT) to which a high voltage can be applied, comprising a GaN-based compound semiconductor.

Solution Means: A stacked structure 1A, comprised by stacking an i-type semiconductor layer 3 and an n-type semiconductor layer 4 in that order, is formed on a semi-insulating substrate 1; each semiconductor layer comprises a GaN-based compound semiconductor; a gate electrode G is loaded on n-type semiconductor layer 4 via a p-type semiconductor layer 5 comprising GaN-based compound semiconductor, and a source electrode S and drain electrode D are each respectively loaded directly on n-type semiconductor layer 4; p-type semiconductor layer 5 has a single-layer structure comprising a p-type GaN layer or p-type InGaN layer, or a double-layer structure comprising a p-type InGaN layer stacked on a p-type GaN layer.

## Claims Claim 1

A high mobility transistor in which a stacked structure, comprised by stacking an i-type semiconductor layer and an n-type semiconductor layer in that order, is formed on a semi-insulating substrate; each semiconductor layer comprises a GaN-based compound semiconductor; a gate electrode is loaded onto the n-type semiconductor layer via a p-type semiconductor layer comprising a GaN-based compound semiconductor, and a source electrode and drain electrode are each respectively loaded directly onto the n-type semiconductor layer.

#### Claim 2

The high mobility transistor of Claim 1, wherein the p-type semiconductor layer has a single-layer structure comprising either a p-type GaN layer or p-type InGaN layer, or a double-layer structure comprising a p-type InGaN layer stacked on a p-type GaN layer.

# Detailed Description of the Invention [0001]

Technical Field of the Invention

The present invention pertains to high mobility transistors (HEMTs) comprising a GaN-based compound semiconductor, and more particularly to novel HEMTs structures operable under the application of high voltages.

#### [0002]

#### Conventional Art

Use of HEMT is anticipated, for example, as a material for high-power microwave devices; at present these are normally manufactured using GaAs-based compound semiconductors. In one known structure, for example, an i-type GaAs layer and n-type GaAl<sub>x</sub>As<sub>1-x</sub> layer are sequentially deposited on a semi-insulating substrate, a source electrode and drain electrode are loaded onto that n-type GaAl<sub>x</sub>As<sub>1-x</sub> layer; as a further example, a gate electrode is loaded via a p-type GaAs layer.

#### [0003]

In HEMTs with this structure, an energy band diagram at x = 0.25 shows that the heterobarrier ( $\Delta$ Ec) at the heterojunction interface between an n-type GaAl<sub>0.25</sub>As<sub>0.75</sub> layer and an i-type GaAs layer is approximately 0.26 eV, and at thermal equilibrium a 2-dimensional electron gas layer is formed at said junction interface. By then applying a reverse bias voltage of a

predetermined value between the source and drain electrodes and a forward bias voltage between the source and gate electrodes, electrons are supplied from the n-type  $GaAl_xAs_{1-x}$  layer to the i-type GaAs layer located below it, and the supplied electrons form a two-dimensional electron gas layer at the junction interface; electrons trapped within that gas layer then flow at high speed to the drain electrode to achieve HEMT operation. In such circumstances, the stronger the electric field strength immediately under the gate voltage is, the higher the electron trapping effect in the gas layer by 2D electrons will be, thereby facilitating high-speed operation.

#### [0004]

With GaAs-based HEMTs, however, the discontinuity band at the heterojunction interface is about 0.26 eV (when x = 0.25), and its breakdown field value is about  $3 \times 10^5$  V/cm, making it difficult to achieve high-speed operation by applying a high voltage to the gate electrode to create a high electrical field directly underneath it. To address this problem, research with prototype HEMTs using GaN-based compound semiconductors has recently been undertaken.

#### [0005]

This is because the hetero-barrier ( $\Delta Ec$ ) at the heterojunction interface between GaN and GaAl<sub>x</sub>N<sub>1-x</sub> is about 0.67 eV, which is approximately 2.6 times higher than a GaAs system, and its breakdown electric field value is 2 × 10<sup>6</sup> V/cm, which is an order of magnitude higher than the GaAs system, so the 2-D electron trapping effect in the electron gas layer can be increased and, theoretically, electron concentration can be made approximately 10 times higher than in a GaAs system.

#### [0006]

As an example, the following types of GaN-based HEMTs are manufactured using MOCVD. First, an AlN buffer layer is deposited on a semi-insulating sapphire substrate. An i-type GaN layer is then deposited on the AlN buffer layer using trimethyl gallium as the Ga source and ammonia as the N source, and an n-type AlGaN layer is deposited on the i-type GaN layer using trimethyl aluminum as the Al source. After then performing conventional photolithography and etching on the n-type AlGaN layer, a gate electrode, source electrode, and drain electrode are loaded at predetermined locations.

#### [0007]

For GaN-based HEMTs, a two-dimensional electron gas layer is formed at the heterojunction interface between the i-type GaN and n-type AlGaN layers -- specifically at the topmost layer of the i-type GaN layer; here electrons move at high speed to achieve HEMT operation. To accomplish high electron mobility, this i-type GaN layer must be as free as possible from impurities and crystal defects.

#### [8000]

Problems the Invention Seeks to Solve

While it is possible to apply higher voltages to GaN-based HEMTs above as compared to GaAs-based HEMTs, they cannot be said to have sufficient electron mobility to meet recent demands for still higher speed operation. The present invention seeks to solve the above problem[s] regarding conventional GaN-based HEMTs and to provide a new GaN-based HEMT structure with a high breakdown voltage.

#### [0009]

Means for Solving the Problems

To achieve the above object, the present invention provides a high mobility transistor in which a stacked structure, comprised by stacking an i-type semiconductor layer and an n-type semiconductor layer in that order, is formed on a semi-insulating substrate; each semiconductor layer comprises a GaN-based compound semiconductor; a gate electrode is formed on the n-type semiconductor layer via a p-type semiconductor layer comprising GaN-based compound semiconductor, and a source electrode and drain electrode are each respectively loaded directly on the n-type semiconductor layer; in particular, [the invention] provides a high mobility transistor wherein the p-type semiconductor layer has a single-layer structure comprising either a p-type GaN layer or p-type InGaN layer, or a double-layer structure comprising a p-type InGaN layer stacked on a p-type GaN layer.

#### [0010]

**Embodiments of the Invention**

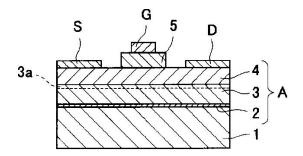

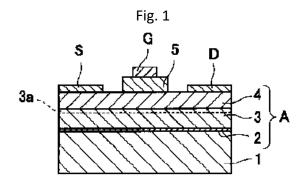

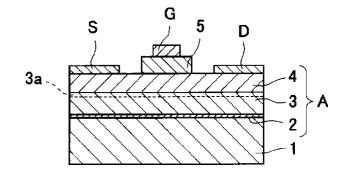

Below we explain details of the HEMT of the invention based on Fig. 1, which depicts its basic structure. A stacked structure A -- comprising a buffer layer 2, an i-type semiconductor layer 3, and an n-type semiconductor layer 4 -- is formed on a semi-insulating substrate 1; a gate electrode G is loaded on the n-type semiconductor layer 4 via a p-type semiconductor layer 6, and a source electrode S and a drain electrode D are also respectively loaded on the n-type semiconductor layer 4.

#### [0011]

The HEMT is manufactured by depositing semiconductor layers of a predetermined composition on a semi-insulating substrate 1 by applying known epitaxial growth methods such as MOCVD and MOMBE to GaN-based compound semiconductors. Semi-insulating substrate 1 would preferably comprise a material that is lattice-matched between each of the semiconductor layers as they are deposited onto it, but because there is no such GaN-based material, a substrate made of a conventionally used semi-insulating material such as sapphire or single crystal Si is acceptable. A GaN layer is also selected as the buffer layer 2.

#### [0012]

i-type GaN, i-type InGaN, and the like are examples of GaN-based compound semiconductors constituting i-type semiconductor layer 3. i-type GaN is particularly preferrable. i-type  $In_xGa_{1-x-y}AlyN$  (0 < x < 1, 0 < y < 0.2) may also be used for the i-type semiconductor layer 3 so long as the band gap energy is less than or equal to that of the high-purity i-type GaN described above.

#### [0013]

n-type AlGaN, n-type GaN, and the like are examples of GaN-based compound semiconductors constituting an n-type semiconductor layer 4. Among these, the n-type AlGaN is favorable. An n-type  $In_uGa_{1-u-v}Al_vN$  (0 < u < 1, 0 < v < 0.5) may also be used as the n-type semiconductor layer so long as the band gap energy is less than or equal to that of the n-type AlGaN above.

#### [0014]

Si metal (if deposited by MBE) or di-silane (if deposited by MOCVD) are examples of n-type dopants used in the deposition of this n-type semiconductor layer 4. Considering that source electrode S and drain electrode D are directly loaded on this n-type semiconductor layer 4, the dopant concentration is preferably set as low as possible to achieve ohmic contact between the two. E.g., if the n-type dopant is Si, the concentration would be about  $5 \times 10^{17}$  to  $5 \times 10^{18}$  cm<sup>-3</sup>.

#### [0015]

Next, p-type GaN and p-type InGaN are examples of GaN-based compound semiconductors to constitute p-type semiconductor layer 5. This p-type semiconductor layer 5 may comprise one layer each of p-type GaN and p-type InGaN, but a double layer structure consisting of a p-type InGaN layer stacked on a p-type GaN layer is preferable. Metal Mg (if deposited by MBE) or cyclopentadienyl magnesium (if deposited by MOCVD) are examples of a p-type dopant when depositing this p-type semiconductor layer 5. The p-type dopant concentration in this case would be about  $5 \times 10^{17}$  to  $5 \times 10^{18}$  cm<sup>-3</sup>.

#### [0016]

Finally, Au/Pt, Al, and the like are examples of materials constituting gate electrode G, while Au, Ti/Al, and the like are [also] examples of materials constituting gate electrode G. HEMT with this structure has a pn junction structure under the gate electrode G. When a voltage is applied from gate electrode G, a two-dimensional electron gas layer 3a is formed at the heterojunction interface between n-type semiconductor layer 4 and i-type semiconductor layer 3, and more specifically at the topmost portion of i-type semiconductor layer 3, where electrons supplied from n-type semiconductor layer 4 are trapped and flow at high speed to drain electrode D, achieving HEMT operation.

#### [0017]

In this case, operation of the pn junction immediately under the gate electrode G enables voltage control with a small amount of carrier injection, and the controlled voltage further enables control of current flowing between channels, such that the 2-dimensional electron gas layer 3a can be controlled at high voltage, increasing the trapping effect on electrons in the 2-dimensional electron gas layer 3a and allowing high-speed electron mobility.

#### [0018]

In particular, if the p-type semiconductor layer 5 has a double layer structure of p-type GaN and p-type InGaN as described above, this stacked structure functions as a kind of

quantum well structure, allowing quantum effect-induced tunnel current flow, which is favorable as it allows gate current to flow easily.

#### [0019]

#### **Embodiments**

An HEMT with the stacked structure shown in Fig. 1 was fabricated by MOMBE as follows. First, a GaN buffer layer 2 with a thickness of 50 Å was deposited on a semi-insulating Si single-crystal substrate 1 by epitaxial growth at a growth temperature of 640°C, using metallic Ga ( $5 \times 10^{-7}$  Torr) as the Ga source and dimethyl hydrazine ( $5 \times 10^{-5}$  Torr) as the N source.

#### [0020]

The N source was then switched over to ammonia ( $5 \times 10^{-5}$  Torr), the growth temperature increased to 850°C, and epitaxial growth resulted in the deposit of an i-type GaN layer 3 with a thickness of 5000Å. Deposition conditions were set so that the carrier concentration at this time was at or below  $5 \times 10^{16}$  cm<sup>-3</sup>.

#### [0021]

Metal Al ( $2 \times 10^{-7}$  Torr) was then supplied, and metal Si ( $2 \times 10^{-9}$  Torr) was supplied as an n-type dopant; epitaxial growth was continued at a growth temperature of 850°C to deposit an n-type AlGaN layer 4 at a thickness of 500Å. Deposition conditions were set to achieve a carrier concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>. The metal Si supply was then cut off, metal Mg ( $5 \times 10^{-9}$  Torr) was supplied as a p-type dopant, and the deposition operation continued to deposit a p-type GaN layer 6 with a thickness of 500 Å on the n-type AlGaN layer 4. Deposition conditions were set so that carrier concentration was  $1 \times 10^{18}$  cm<sup>-3</sup>.

#### [0022]

Dry etching was then performed using a plasma-converted mixture of hydrogen, argon, and methane as an etchant to etch away the p-type GaN layer except where the gate electrode was to be loaded and exposing the n-type InGaN layer 4. An  $SiO_2$  film was then deposited by plasma CVD to cover the entire surface, and after patterning with photoresist, the area including the part where the gate electrode was to be loaded was masked, [leaving] the portion where source and drain electrodes were to be loaded open, and metal Al deposited on the exposed n-type InGaN layer 4 to load source electrode S and drain electrode D.

#### [0023]

Lastly, after etching away the masking and opening the  $SiO_2$  film beneath it, the source electrode S and drain electrode G locations were masked with  $SiO_2$  film, Au was deposited in the opening portions, and gate electrodes G were loaded above the p-type GaN layer 5 to fabricate the HEMT shown in Fig. 1. With this HEMT, a drain current (lds) of 60 mA under an applied gate voltage of 3V and saturation above a drain voltage of 2V were obtained. I.e., a constant value for this saturation characteristic was maintained even when Vds was raised to 100V, and no loss of HEMT functionality occurred.

#### [0024]

Mobility of this HEMT structure at room temperature was  $600 \text{ cm}^2/\text{V} \cdot \text{sec}$ , and a good mobility value of  $7500 \text{ cm}^2/\text{V} \cdot \text{sec}$  was shown at 77 K.

#### [0025]

#### Effect of the Invention

As is clear from the above description, the GaN-based HEMT of the present invention does not fail even when the gate electrode is increased to V, and is able to operate at higher speeds than conventional GaN-based HEMTs. This effect is brought about by use of a pn junction structure between the gate electrode and channel layer, forming a two-dimensional electron gas layer with excellent electron trapping effect at the junction interface between itype and n-type semiconductor layers.

#### **Brief Description of Figures**

Fig. 1: A cross section showing the stacked structure of the HEMT of the invention.

- 1 semi-insulating substrate

- 2 buffer ["bap"] layer (GaN layer)

- 3 i-type semiconductor layer (i-type GaN layer)

- 3a 2D electron gas layer

- 4 n-type semiconductor layer (n-type InGaN layer)

- 5 p-type semiconductor layer (p-type GaN layer)

- S source electrode

- G gate electrode

- D drain electrode

## (19)日本国特許庁(JP) (12) **公開特許公報**(A) (11)特許出願公開番号

### 特開平11 - 261053

(43)公開日 平成11年(1999)9月24日

(51) Int .CI®

識別記号

庁内整理番号

F I

技術表示箇所

H 0 1 L 29/778

H 0 1 L 29/80

H

21/338

21/338

29/812

審査請求 未請求 請求項の数 20 L (全 4 数)

(21)出願番号 特願平10 - 57070 (71)出願人 000005290

(22)出願日 平成10年(1998)3月9日 東京都千代田区丸の内2丁目6番1号

(72)発明者 吉田 清輝

東京都千代田区丸の内2丁目6番1号 古河電

気工業株式会社内

古河電気工業株式会社

(74)代理人 弁理士 長門 侃二

#### (54)【発明の名称】 高移動度トランジスタ

#### (57)【要約】

【課題】 GaN系化合物半導体から成り、高圧印加が可能な高移動度トランジスタ(HEMT)を提供する。 【解決手段】 半絶縁性基板1の上に、i型半導体層3,n型半導体層4をこの順序で積層して成る積層構造1Aが形成され、各半導体層はいずれもGaN系化合物半導体から成り、n型半導体層4の上にはGaN系化合物半導体から成るp型半導体層5を介してゲート電極Gが装荷され、またn型半導体層4の上には直接ソース電極Sとドレイン電極Dがそれぞれ装荷されており、p型半導体層5が、p型GaN層もしくはp型InGaN層の1層構造、またはp型GaN層にp型InGaN層を積層して成る2層構造である。

1

#### 【特許請求の範囲】

【請求項1】 半絶縁性基板の上に、i型半導体層,n 型半導体層をこの順序で積層して成る積層構造が形成さ れ、前記各半導体層はいずれもGaN系化合物半導体か ら成り、前記n型半導体層の上にはGaN系化合物半導 体から成るp型半導体層を介してゲート電極が装荷さ れ、また前記n型半導体層の上には直接ソース電極とド レイン電極がそれぞれ装荷されていることを特徴とする 高移動度トランジスタ。

【請求項2】 前記p型半導体層が、p型GaN層もし10を10倍程度大きくすることができるからである。 くはp型InGaN層の1層構造、またはp型GaN層 にp型InGaN層を積層して成る2層構造である請求 項1の高移動度トランジスタ。

#### 【発明の詳細な説明】

#### [0001]

【発明の属する技術分野】本発明のGaN系化合物半導 体から成る高移動度トランジスタ(HEMT)に関し、 更に詳しくは、高電圧印加の下で作動できる新規な構造 のHEMTに関する。

#### [0002]

【従来の技術】HEMTは、例えば高出力マイクロ波素 子の素材として期待されていて、現在ではGaAs系化 合物半導体を用いて製造されているのが通例である。例 えば、半絶縁性基板の上にi型GaAs層とn型GaA 1、As、、層を順次成膜し、そしてそのn型GaAl、 As 、層の上に、ソース電極とドレイン電極が装荷さ れ、更に例えばp型GaAs層を介してゲート電極が装 荷された構造のものが知られている。

【0003】この構造のHEMTの場合、x=0.25 のときのエネルギーバンド図をみると、n型GaAl 。。25 A S 。 75 層と i 型 G a A S 層のヘテロ接合界面にお けるヘテロ障壁 ( E c ) は約0.26eVになってい て、熱平衡状態においては、当該接合界面に2次元電子 ガス層が形成される状態になっている。そして、ソース 電極とドレイン電極の間に所定値の逆バイアス電圧を印 加し、またソース電極とゲート電極の間に順バイアス電 圧を印加することにより、前記n型GaAl、As、、層 からはその下に位置するi型GaAs層へ電子が供給さ れ、供給された電子は前記接合界面で2次元電子ガス層 を形成し、そのガス層内に閉じ込められた状態で電子は 40 ドレイン電極へと高速で流れてHEMT動作を実現す る。その場合、ゲート電圧の直下における電界強度が強 いほど、2次元電子がガス層への電子の閉じ込め効果は 高まるので、高速動作は実現しやすくなる。

【0004】しかしながら、GaAs系HEMTの場 合、ヘテロ接合界面における不連続バンドは0.26eV 程度(x=0.25のとき)であり、その絶縁破壊電界 値は3×10<sup>5</sup>V/cm程度であるため、ゲート電極に高電 圧を印加してその直下に高電界を形成することにより高 に対処することを目的として、最近、GaN系化合物半 導体を用いたHEMTの試作研究が行われている。

【0005】これは、GaAl、N、L、とGaNとのヘテ 口接合界面におけるヘテロ障壁( Ec)は約0.67e Vであり、GaAs系の場合に比べて約2.6倍と高い不 連続バンドを有し、またその絶縁破壊電界値も2×10 <sup>6</sup>V/cmであり、GaAs系の場合に比べて1桁大きいの で2次元電子ガス層内への電子の閉じ込め効果を高める ことができ、理論的には、GaAs系に比べて電子濃度

【0006】このGaN系HEMTとしては、例えば次 のようなものがMOCVD法を用いて製造されている。 すなわちまず、半絶縁性のサファイア基板の上に、Al Nバッファ層が成膜される。ついで、Ga源としてトリ メチルガリウム,N源としてアンモニアを用いて前記A 1 Nバッファ層の上にi型GaN層が成膜され、更にト リメチルアルミニウムをAl源として前記i型GaN層 の上にn型AlGaN層が成膜される。そして、このn 型A1GaN層に対して常法のホトリソグラフィーとエ 20 ッチングを行ったのち、所定の箇所にゲート電極,ソー ス電極, およびドレイン電極が装荷される。

【0007】このGaN系HEMTの場合、i型GaN 層とn型AlGaN層のヘテロ接合界面、具体的にはi 型GaN層の最上層に2次元電子ガス層が形成され、こ こを電子が高速移動してHEMT動作を実現する。この とき、電子の高移動度を実現するためには、このi型G a N層には不純物や結晶欠陥が極力存在していないこと が必要である。

#### [0008]

【発明が解決しようとする課題】しかしながら、上記し たGaN系HEMTの場合、GaAs系HEMTに比べ れば高い電圧の印加は可能であるが、更なる高速動作が 要求されている昨今の状況に対しては必ずしも充分な電 子移動度を発揮するものとはいいがたい。本発明は従来 のGaN系HEMTにおける上記した問題を解決し、高 耐圧性を備えている新規構造のGaN系HEMTの提供 を目的とする。

#### [0009]

【課題を解決するための手段】上記した目的を達成する ために、本発明においては、半絶縁性基板の上に、i型 半導体層,n型半導体層をこの順序で積層して成る積層 構造が形成され、前記各半導体層はいずれもGaN系化 合物半導体から成り、前記n型半導体層の上にはGaN 系化合物半導体から成るp型半導体層を介してゲート電 極が装荷され、また前記n型半導体層の上には直接ソー ス電極とドレイン電極がそれぞれ装荷されていることを 特徴とする高移動度トランジスタ、とくに、前記p型半 導体層が、p型GaN層もしくはp型InGaN層の1 層構造、またはp型GaN層にp型InGaN層を積層 速動作を実現するという点で難がある。このような問題 50 して成る2層構造である高移動度トランジスタが提供さ

3

れる。

#### [0010]

【発明の実施の形態】以下、本発明のHEMTにつき、 その基本構造を示す図1に基づいて詳細に説明する。本 発明のHEMTは、半絶縁性基板1の上に、バッファ層 2, i型半導体層3, n型半導体層4から成る積層構造 Aが形成され、n型半導体層4の上には、p型半導体層 6を介してゲート電極Gが装荷され、また、ソース電極 S、ドレイン電極Dがそれぞれ装荷された構造になって いる。

【0011】このHEMTは、GaN系化合物半導体に 対してMOCVD法やMOMBE法など公知のエピタキ シャル成長法を適用することにより、半絶縁性基板 1 の 上に所定組成の半導体層を成膜していくことによって製 造される。ここで、半絶縁性基板1としては、この上に 成膜していく各半導体層との間で格子整合している材料 から成ることが本来は好ましいが、GaN系に関しては そのような材料は存在しないので、従来から使用されて いる材料、例えばサファイア、Si単結晶などの半絶縁 性材料の基板であればよい。また、バッファ層2として20 は、GaN層が選択される。

【0012】i型半導体層3を構成するGaN系化合物 半導体としては、例えば、i型GaN,i型InGaN などをあげることができる。とくに、i型GaNは好適 である。また、バンドギャップエネルギーが上記した高 純度なi型GaNのそれよりも小さいかまたは同等であ れば、i型In、Ga<sub>1-x-v</sub>Al<sub>v</sub>N(ただし、0 < x < 1,0<y<0.2)をi型半導体層3として用いること もできる。

【0013】n型半導体層4を構成するGaN系化合物30 半導体としては、例えば、n型AlGaN,n型GaN などをあげることができる。これらのうち、n型AlG aNは好適である。また、バンドギャップエネルギーが 上記n型AlGaNのそれよりも小さいかまたは同等で あれば、n型In』Ga<sub>1-u-v</sub>Al<sub>v</sub>N(ただし、0 < u < 1 , 0 < v < 0.5 ) を n 型半導体層として用いること もできる。

【0014】このn型半導体層4の成膜に用いるn型ド ーパントとしては、例えば金属Si(MBE法で成膜す る場合)やジシラン(MOCVD法で成膜する場合)を 40 あげることができる。このn型半導体層4の上には直接 ソース電極Sとドレイン電極Dを装荷することを考える と、両者間でオーミック接触を実現させるため、できる だけ低抵抗となるようにドーパント濃度を設定すること が好ましい。例えばn型ドーパントがSiである場合に は、5×10<sup>17</sup>~5×10<sup>18</sup>cm<sup>-3</sup>程度の濃度にする。

【0015】次に、p型半導体層5を構成するGaN系 化合物半導体としては、p型GaN,p型InGaNを あげることができる。このp型半導体層5は、p型Ga N層,p型InGaN層のそれぞれ1層から成っていて 50 なるように成膜条件を設定した。ついで、金属Siの供

もよいが、p型GaN層の上に更にp型InGaN層を 積層して成る2層構造にすることが好適である。このp 型半導体層 5 を成膜するときの p 型ドーパントとして は、例えば金属Mg(MBE法で成膜する場合)やシク ロペンタジエニルマグネシウム(MOCVD法で成膜す る場合)などをあげることができる。このときのp型ド ーパントの濃度は5×10<sup>17</sup>~5×10<sup>18</sup>cm<sup>-3</sup>程度にす

【0016】最後に、ゲート電極Gを構成する材料とし 10 ては例えば Au/Pt, Alなどをあげることができ、 またゲート電極Gを構成する材料としては例えばAu, Ti/Alなどをあげることができる。この構造のHE MTは、ゲート電極Gの下がpn接合構造になってい る。そして、ゲート電極Gから電圧印加を行うと、n型 半導体層4と1型半導体層3のヘテロ接合界面、具体的 には、 i 型半導体層 3 の最上層部に 2 次元電子ガス層 3 aが形成され、そこにn型半導体層4から供給された電 子が閉じ込められ、高速でドレイン電極Dへ流れてHE MT動作を実現する。

【0017】その場合、ゲート電極G直下のpn接合の 働きにより少量のキャリア注入で電圧が制御され、かつ 制御された電圧によってチャネル間を流れる電流を制御 することが可能になるので、前記2次元電子ガス層3a を高電圧で制御することが可能になり、2次元電子ガス 層3aへの電子の閉じ込め効果も高くなって電子の高速 移動が可能になる。

【0018】とくに、p型半導体層5が前記したp型G aNとp型InGaNの2層構造になっている場合に は、この積層構造が1種の量子井戸構造として機能し、 その結果、量子効果によるトンネル電流が流れるように なり、ゲート電流は流れやすくなるので好適である。 [0019]

【実施例】図1で示した積層構造のHEMTをMOMB E法により次のようにして製造した。まず、半絶縁性の Si単結晶基板1の上に、Ga源として金属Ga(5×  $10^{-7}$ Torr), N源としてジメチルヒドラジン( $5 \times 1$ 0 <sup>5</sup>Torr)を用い、成長温度640 でエピタキシャル 成長を行い、厚み50 のGaNバッファ層2を成膜し た。

【 0 0 2 0 】ついで、N源をアンモニア(5 × 1 0 <sup>- 5</sup>To rr)に切り換え、成長温度を850 に上昇してエピタ キシャル成長を行い、厚み5000 のi型GaN層3 を成膜した。なお、このときのキャリア濃度は5×10 16cm 3以下となるように成膜条件を設定した。

【0021】ついで、金属Al(2×10<sup>-7</sup>Torr)を供 給し、またn型ドーパントとして金属Si(2×10<sup>-9</sup> Torr)を供給し、成長温度850 でエピタキシャル成 長を継続して、厚みが500 のn型AlGaN層4を 成膜した。このとき、キャリア濃度は1×10<sup>18</sup>cm<sup>-3</sup>と

5

給を絶ち、p型ドーパントとして金属Mg(5×10<sup>-9</sup> Torr)を供給して成膜操作を続け、前記n型AlGaN 層4の上に厚み500 のp型GaN層6を成膜した。 このとき、キャリア濃度は1×10<sup>18</sup>cm<sup>-3</sup>となるように 成膜条件を設定した。

【0022】ついで、水素とアルゴンとメタンの混合ガ スをプラズマ化したものをエッチャントにしてドライエ ッチングを行い、ゲート電極を装荷すべき箇所以外のp 型GaN層をエッチング除去してn型InGaN層4を 表出させた。その後、全体の表面を被覆してSiО。膜 10 型半導体層との接合界面に電子の閉じ込め効果が優れて をプラズマCVD法で成膜し、ホトレジストでパターニ ングしたのちゲート電極を装荷すべき箇所を含む部分を マスキングし、ソース電極とドレイン電極を装荷すべき 箇所は開口し、そこに表出したn型InGaN層4の上 に、金属Alを蒸着することにより、ソース電極Sとド レイン電極Dを装荷した。

【0023】最後、前記マスキングをエッチング除去 し、その下のSiО。膜を開口し、ソース電極Sとドレ イン電極Gの箇所をSiO₂膜でマスキングしたのち、 上記開口部にAuを蒸着してp型GaN層5の上にはゲ203a2次元電子ガス層 ート電極Gを装荷して図1で示したHEMTを製造し た。このHEMTは、ゲート電圧からの印加電圧を3V でドレイン電流(Ids)が60mA,ドレイン電圧2V以 上で飽和するHEMT特性が得られた。すなわち、この 飽和特性はVdsを100Vまであげても一定値を保ち、 HEMTとしての機能を喪失することはなかった。

\*【0024】室温下でのこのHEMT構造の移動度は、 600cm<sup>2</sup>/V·secであり、77Kでの移動度は7500c m<sup>2</sup>/V·secと良好な値を示した。

#### [0025]

【発明の効果】以上の説明で明らかなように、本発明の GaN系HEMTは、ゲート電極をVまで高めても故障 を起こすことがなく、従来のGaN系HEMTに比べて 高速動作をすることができる。これは、ゲート電極とチ ャネル層との間をpn接合構造とし、i型半導体層とn いる2次元電子ガス層が形成されるようにしたことがも たらす効果である。

#### 【図面の簡単な説明】

【図1】本発明のHEMTの層構造を示す断面図であ る。

#### 【符号の説明】

- 半絶縁性基板

- バップ層(GaN層)

- i型半導体層(i型GaN層) 3

- 4 n型半導体層(n型InGaN層)

- 5 p型半導体層(p型GaN層)

- S ソース電極

- G ゲート電極

- D ドレイン電極

【図1】

# Christopher Field Japanese Technical Interpreting and Translation 52 Sherman's Bridge Rd., Wayland MA 01778 Tel. 617-905-6060

www.christopherfield.com

#### CERTIFICATION OF TRANSLATION

I, Christopher L. Field, residing at 52 Sherman's Bridge Rd., Wayland MA, 01778, United States of America, declare and state as follows:

I am well acquainted with the English and Japanese languages. I have translated numerous Japanese documents of legal and/or technical content into English. I am fully accredited by the American Translators Association (ATA) for Japanese to English translation, and my ATA certification number is 423514.

I have personally translated the attached document, entitled "JP1999-261053" from Japanese into English. I hereby certify that the English translation of the attached documents is an accurate translation to the best of my knowledge and ability.

I further declare that all statements made herein of my own knowledge are true, that all statements made on information and belief are believed to be true, and that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Executed at Wayland, Massachusetts, 28 July, 2023.

Signed.

Christopher Field

ATA Certified Translator, Japanese to English, Certificate No. 423514