# A Normally-off AlGaN/GaN Transistor with $R_{on}A=2.6m\Omega cm^2$ and $BV_{ds}=640V$ Using Conductivity Modulation

Yasuhiro Uemoto, Masahiro Hikita, Hiroaki Ueno, Hisayoshi Matsuo, Hidetoshi Ishida, Manabu Yanagihara, Tetsuzo Ueda, Tsuyoshi Tanaka and Daisuke Ueda

Semiconductor Device Research Center, Semiconductor Company, Matsushita Electric - Panasonic 1 Kotari-yakemechi, Nagaokakyo-shi, Kyoto 617-8520, JAPAN Phone: +81-75-956-9083, FAX: +81-75-956-9110, e-mail: uemoto.yasuhiro@jp.panasonic.com

## **Abstract**

We report a normally-off GaN-based transistor using conductivity modulation, which we call GIT (Gate Injection Transistor). This new device principle utilizes hole-injection from p-AlGaN to AlGaN/GaN heterojunction, which increases electron density in the depleted channel resulting in dramatic increase of the drain current owing to the conductivity modulation. The fabricated GIT exhibits the threshold voltage of 1.0V with high maximum drain current of 200mA/mm. The obtained on-state resistance ( $R_{on}\cdot A$ ) and off-state breakdown voltage ( $BV_{ds}$ ) are  $2.6m\Omega\cdot cm^2$  and 640V, respectively. These values are the best ones ever reported for GaN-based normally-off transistors.

## Introduction

AlGaN/GaN heterojunction field effect transistors (HFETs) are widely investigated for high power switching applications. Most of the reported AlGaN/GaN HFETs are normally-on type taking advantage of the inherent high sheet carrier density caused by built-in polarization electric field [1-2]. Aiming at practical applications, normally-off operation is strongly desired for AlGaN/GaN HFETs in order to make the GaN devices compatible with currently used Si-based power MOSFETs / IGBTs for safety operation. Since the interfacial carriers are caused by the difference of the inherent fixed charges between GaN and AlGaN, reduction of the Al mole fraction and the thickness of AlGaN is effective to reduce those carriers and thereby to shift the threshold voltage. This approach results in reduced drain current as well as lower potential barrier to the gate. So far, high enough drain current with normally-off operation for AlGaN/GaN HFETs has never been reported [3-10].

In this paper, we demonstrate a new concept of GaN-based normally-off transistor called GIT (Gate Injection Transistor). The GIT utilizes hole injection from p-type gate to 2DEG region bringing out the conductivity modulation as is observed in IGBTs[11]. This new concept realizes high current driving capability even with normally-off operation.

## **Principle of GIT operation**

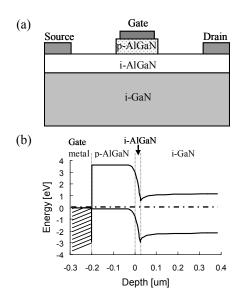

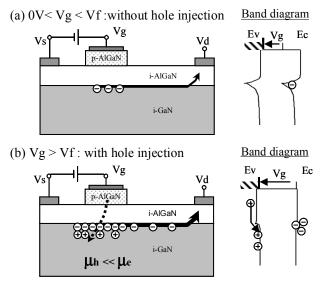

The most notable feature of the GIT is p-AlGaN gate formed over undoped AlGaN/GaN hetero-structure as shown in Fig.1(a). The p-AlGaN lifts up the potential at the channel, which ends up with normally-off operation as shown in the band diagram of Fig.1(b). Fig.2 illustrates the basic operation of the GIT. At the gate voltages up to the forward built-in voltage  $V_f$  of the pn junction at the gate, the GIT is operated as a field effect transistor. Further increase of the gate voltage exceeding the  $V_f$  results in the hole injection to the channel from the p-AlGaN. The injection of the electrons from the channel to the gate is well suppressed by the hetero-barrier at AlGaN/GaN. The injected holes generate the equal numbers of electrons to keep charge neutrality at the channel. The generated electrons are moved by the drain bias with high mobility, while the injected holes

Fig.1 A schematic illustration of (a) GIT structure and (b) calculated band diagram of GIT at the gate bias of 0V. The epitaxial structure is designed to serve normally-off operations.

stay around the gate because the hole mobility is two order of magnitude lower than that of the electron. This results in significant increase of the drain current keeping the low gate current. Fig.3 shows distribution of holes and electrons in the

Fig.2 A schematic illustration of GIT operation varying gate voltages: (a) without hole injection at Vg < Vf, (b) with hole injection at Vg > Vf.

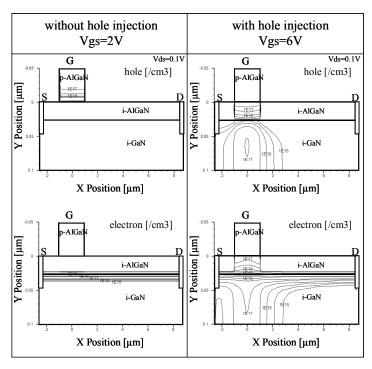

Fig.3 Distribution of holes and electrons in GITs varying gate voltages by 2D simulation: (a) Vgs=2V: without hole injection, (b) Vgs=6V: with hole injection.

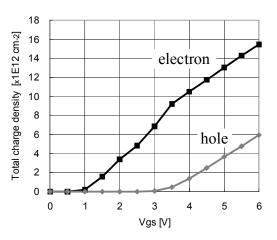

GIT obtained by 2D-simulation at two gate voltages. At  $V_{\rm gs}$  of 6V, hole injection into i-GaN as well as the increase of electron concentration is confirmed, while no hole is injected at  $V_{\rm gs}$  of 2V. Fig.4 is the simulated sheet density of electrons and holes at the channel as a function of gate voltages, which indicates dramatic increase of carrier density at the gate voltages over the  $V_{\rm f}$ .

Fig.4 Calculated total charge density of holes and electrons integrated at entire depth in GIT varying gate voltages. The increased number of electrons are generated by the hole injection at higher gate voltage.

## Device structure and fabrication

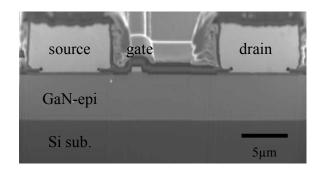

Fig. 5 shows the cross sectional SEM image of the fabricated GIT. A p-AlGaN/AlGaN/GaN hetero-epitaxial structure is grown on a cost-effective silicon substrate. In order to realize the normally-off operation, the Al mole fraction and the thickness of i-AlGaN are optimized to be 15% and 25nm, respectively. The p-type gate is formed by inductively coupled plasma (ICP) dry etching. The used gate

Fig.5 Cross sectional SEM image of GIT on a Si substrate.

and source/drain metals are Pd and Ti/Al, respectively. The gate length defined by the p-AlGaN width is  $2.0\mu m$  and a gate-drain spacing is  $7.5\mu m$ . The device is isolated by ion implantation of Boron.

## **Device Performance**

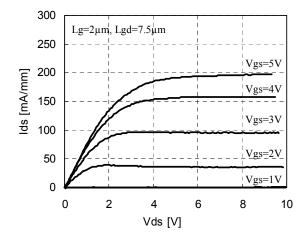

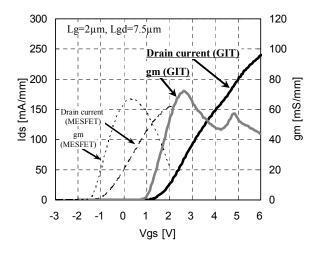

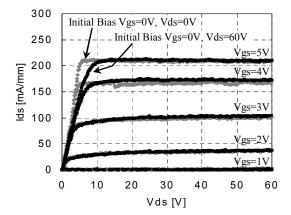

Fig.6 and 7 summarize the DC characteristics of the fabricated GIT comparing with those of the conventional Schottky-gate FET. As shown in the figures, the forward gate voltage of 6V can be applied while the forward gate voltage is limited up to 2V in the conventional FET. No current-offset is observed at zero drain-bias as seen in Fig.6,

Fig.6 Ids-Vds characteristics of fabricated GIT (Ron·A=2.6m $\Omega$ ·cm2, Imax=200mA/mm).

Fig.7 Ids-Vgs and gm-Vgs characteristics of fabricated (a) GIT and (b) MESFET.

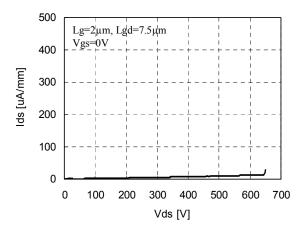

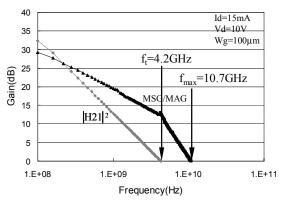

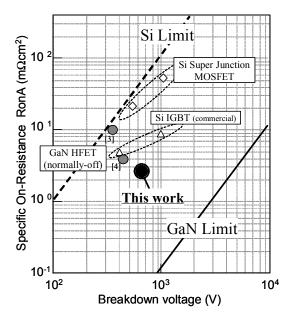

implying the complete suppression of the gate current. The GIT exhibits peculiar transconductance characteristics with two peaks as seen in Fig.7. The device is operated as an FET up to the  $V_{gs}$  of 3V. Further increase of the  $V_{gs}$  superlinearly increases the I<sub>ds</sub> corresponding to the second g<sub>m</sub> peak, which is the direct evidence of the hole injection. Thus, this operation principle enables low on-state resistance with high drain current. The fabricated GIT exhibits the threshold voltage of 1.0V with high maximum drain current of 200mA/mm. The obtained on-state resistance (Ron·A) and off-state breakdown voltage (BV<sub>ds</sub>) are 2.6mΩ·cm<sup>2</sup> and 640 V, respectively as shown in Fig.6 and 8. The cut-off  $(f_T)$ and the maximum frequency of oscillation (fmax) are extracted to be 4.2GHz and 10.7GHz, respectively as shown in Fig.9, which are as comparably high as the reported values of Schottky-gate normally-on AlGaN/GaN power FETs [1].

In addition to the normally-off operation, suppression of the current collapse has been strongly desired for the GaN-

Fig.8 The off-state breakdown characteristics of GIT exhibiting the breakdown voltage of 640V.

Fig.9 Frequency response of GIT. The cut-off and maximum oscillation frequency are extracted to be 4.2GHz and 10.7GHz, respectively.

based power switching devices. Fig.10 shows the results of the pulsed I-V measurements for the GIT with different initial bias conditions. The almost identical I-V characteristics imply that the GIT is operated free from the current collapse phenomena. The GIT is a conductivity modulated device so that it is not affected by the fixed charges trapped either at the surface or in the bulk GaN.

Fig.10 Pulsed Ids-Vds characteristics of fabricated GIT. Two sets of initial bias are used (Vgs=0V, Vds=0V and Vgs=0V, Vds=60V). The used pulse width and period are 0.5μs and 1ms, respectively.

Fig.11 State-of-the-art Ron·A and breakdown voltage of normally-off GaN-based devices comparing with those of Si-based devices. The obtained results for the GIT is the best value among the reported values.

## Conclusion

We have successfully developed a new normally-off AlGaN/GaN transistor with high drain current. The transistor called GIT effectively utilizes hole-injection from the p-AlGaN resulting in dramatic increase of the drain current at high gate voltages owing to the conductivity modulation. The resultant R<sub>on</sub>·A and breakdown voltage are the best values among those of the reported GaN-based normally-off devices as summarized in Fig.11. The presented GIT is advantageous for power switching application replacing with currently used Si-based power MOSFETs and IGBTs.

## References

- M. Hikita, M. Yanagihara, K. Nakazawa, H. Ueno, Y. Hirose, T. Ueda, Y. Uemoto, T. Tanaka, D. Ueda, and T. Egawa, "350V/150A AlGaN/GaN power HFET on Silicon substrate with source-via grounding (SVG) structure," *IEDM Technical Digests*, pp. 803-806, December 2004.

- (2) W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, and H. Ohashi, "High breakdown voltage AlGaN/GaN power-HEMT design and igh current density switching behavior," *IEEE Trans. Electron Devices*, vol.50, no.12, pp.2528-2531, Dec, 2003.

- (3) N. Ikeda, J. Li, and S. Yoshida, "Normally-off operation power AlGaN/GaN HFET," Proceedings of 2004 International Symposium on Power Semiconductor Devices & ICs, pp. 369-372.

- (4) W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, and I. Omura, "Recessed-Gate Structure Approach Toward Normally Off High-Voltage AlGaN/GaN HEMT for Power Electronics Applications," *IEEE Trans. Electron Devices*, vol.53, no.2, pp.356-362, February, 2006.

- (5) M. A. Khan, Q. Chen, C. J. Sun, J. W. Yang, M. Blasingame, M. S. Shur, and H. Park, "Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors," *Appl. Phys. Lett.* vol.68, no.4, pp.514-516, January, 1996.

- (6) W. B. Lanford, T.Tanaka, Y. Otoki, and I. Adesida, "Recessed-gate enhancement-mode GaN HEMT with high threshold voltage," *Electron. Lett.* vol.41, no.7, pp.449-450, March, 2005.

- (7) S. Jia, Y. Cai, D. Wang, B. Zhang, K. M. Lau, and K. J. Chen, "Enhancement-Mode AlGaN/GaN HEMTs on Silicon Substrate," *IEEE Trans. Electron Devices*, vol.53, no.6, pp.1474-1477, June, 2006.

- (8) T.Palacios, C. S. Suh, A. Chakraborty, S. Keller, S. P. DenBaars, U. K. Mishra, "High-Performance E-Mode AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol.27, no.6, pp.428-430, June, 2006.

- (9) X. Hu, G. Simin, J. Yang, M. A. Khan, R. Gaska, and M. S. Shur, "Enhancement-mode AlGaN/GaN HFET with selectively grown pn junction gate," *Electron. Lett.* vol.36, pp.753-754, 2000.

- (10) M. Kuroda, H. Ishida, T. Ueda, T. Tanaka, "Normally-off Operation of Non-polar AlGaN/GaN HFETs Grown on R-plane Sapphire," Ex. Abstract SSDM, pp. 470-471, 2005.

- (11) B. J. Baliga, M. S. Adler, P. V. Gray, and R. P. Love, "The Insulated Gate Rectifier (IGR)," *IEDM Technical Digests*, pp. 264-267, December 1982.